半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、FETを備えた半導体装置に関する。

【背景技術】

【0002】

n型FETはゲート電圧が閾値電圧(Vth)を上回るとオン状態になり、ソースとドレイン間の抵抗が低くなる。通常のFETでは、Vthはオン状態とオフ状態に係わらず一定値である。これに対して、オンするとVthが下がり、オフすると再びVthが上がる機能を持つn型FETが提案されており、この機能は、Vth自己調整機能と呼ばれる。

【0003】

例えば、非特許文献1には、強誘電体膜を応用したVth自己調整機能を持つFET(以下、Vth自己調整FET)を利用したSRAMが開示されている。SRAMをVth自己調整FETで構成することによって、SRAMのデータ保持特性と読み出し特性を共に改善することができる。開示されたVth自己調整FETのゲートスタック部は、シリコン基板上に形成されたHf−Al−Oからなるバッファ層と、バッファ層上に形成されるSrBi2Ta2O9(SBT)強誘電体膜と、SBT膜上に形成されるPtメタル電極とで構成されている。

【0004】

この他、従来の技術として、不揮発メモリTrを使用する不揮発プログラマブルスイッチや、電源スイッチFETを高Vthトランジスタで構成してIoff性能を向上させる技術や、チャージトラップ膜の膜厚を厚くして高エネルギー電子の捕獲確率および保持確率を向上させる技術などが開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公報6,002,610号

【特許文献2】特許第2,631,335号公報

【非特許文献】

【0006】

【非特許文献1】Shuhei Tanakamaru, Teruyoshi Hatanaka, Ryoji Yajima, Mitsue Takahashi, Shigeki Sakai and Ken Takeuchi, IEDM Tech. Dig., p283 (2009).

【非特許文献2】Shosuke Fujii, Naoki Yasuda, Jun Fujiki, “A new method to extract the charge centroid in the program operatIon of metal-oxide-nitride-oxide-semiconductor memories”, Japanese Journal of Applied Physics 49, 04DD06-1 (2010).

【非特許文献3】N. Goel, et.al., “Erase and RetentIon Improvements in Charge Trap Flash Through Engineered Charge Storage Layer”, IEEE Electron Device Letters 30, 216 (2009).

【非特許文献4】Y. Kamigaki, et.al., IEICE trans. Electron. E84-C, 713 (2001).

【発明の概要】

【発明が解決しようとする課題】

【0007】

本実施形態が解決しようとする課題は、FETの駆動力性能や遮断性能などを向上できる半導体装置を提供することである。

【課題を解決するための手段】

【0008】

本発明の一態様では、半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、

前記絶縁膜の上方に配置されるゲート電極と、

前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

【図面の簡単な説明】

【0009】

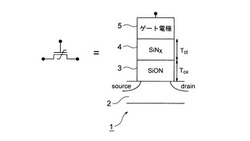

【図1】第1の実施形態による半導体装置の断面図。

【図2】本実施形態によるn型FETの動作原理を説明する図。

【図3】本実施形態によるp型FETの動作原理を説明する図。

【図4】本実施形態によるVth自己調整FET1の動作原理を実証する実験結果を示すグラフ。

【図5】第2の実施形態による半導体装置の回路図であり、より具体的にはSRAMセルの回路図。

【図6】ΔVthとSiNx膜の膜厚Tctとの関係についての実験結果を示すグラフ。

【図7】SiONブロック絶縁膜3とSiNxチャージトラップ膜4からなる積層ゲートスタックについて、ゲートリーク電流JgとSiONブロック絶縁膜3の膜厚Toxの関係を示す図。

【図8】第3の実施形態による半導体装置の回路図。

【図9】第4の実施形態による半導体装置の回路図。

【図10】第5の実施形態による半導体装置の回路図。

【図11】第5の実施形態による他の半導体装置の回路図。

【発明を実施するための形態】

【0010】

以下、図面を参照しながら、本発明の実施形態を説明する。

【0011】

(第1の実施形態)

図1は第1の実施形態による半導体装置の断面図である。図1の半導体装置は、オン状態とオフ状態で閾値電圧Vthを自動的に調整可能なVth自己調整FET1である。図1のVth自己調整FET1は、半導体基板2上に形成されるブロック絶縁膜3と、ブロック絶縁膜3上に形成されるチャージトラップ膜4と、チャージトラップ膜4上に形成されるゲート電極5とを備えている。チャージトラップ膜4は、ブロック絶縁膜3の下部に形成されるチャネルとの間よりも、ゲート電極5との間で、より多くの電子の授受を行なう。

【0012】

チャージトラップ膜4は、SiNx膜であり、xはSiに対するNのモル比であって、0.67<x<1.33の範囲内の値である。チャージトラップ膜4の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値である。

【0013】

ブロック絶縁膜3は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値である。ブロック絶縁膜3の膜厚Toxは、0.64nm<Toxの範囲内の値であり、より好ましくは0.64nm<Tox<2.70nmである。

【0014】

SiNx膜3の化学量論的組成はSi3N4であり、その場合のSiに対するNのモル比はx=1.33となる。x<1.33のSiNx膜は、Siの組成比が大きいSiリッチな組成となり、この場合は、Si原子が未結合手(ダングリングボンド)を所持することになり、このダングリングボンドの存在により、両極性トラップが生成されると考えられる。両極性トラップの密度は、xが1.33よりも低下するに従って増加する。両極性トラップは電子を1つ有する場合が中性で、その電子を放出すると正に帯電し、別個の電子を捕獲して計2つの電子を所持すると負に帯電する。後述するように、Vth自己調整機能を持つには、チャージトラップ膜4が両極性トラップを有することが必須であり、本実施形態では、ブロック絶縁膜3を構成するSiNx膜のx<1.33が必須条件となる。

【0015】

x=0.67は平均的に、Siの4つの結合手の内2つが未結合手となるか、隣接Siと共有結合を形成する組成に相当する。この場合、共有結合が大量に存在することになり、SiNx膜の絶縁性が劣化して、ゲートリーク電流が著しく増大する。従って、0.67<xが望ましい。

【0016】

図2および図3は本実施形態によるVth自己調整FET1の動作原理を説明する図であり、電子の移動方向をFETの断面図とエネルギーバンドを使って図示している。図2は、n型FET1で、ゲート電極5がn+ポリシリコンの例を示している。

【0017】

より詳細には、図2(a)は、ゲート−ソース間電圧Vgs=0Vで、n型FETがオフ状態の場合を示している。図2(a)の場合、チャージトラップ膜4中に電界は印加されない。チャージトラップ膜4中の両極性トラップは電子を保持しているため、中性となる。図2(b)は、Vgs>0で、n型FETがオン状態の場合を示している。この場合、チャージトラップ膜4中には電界が印加されるが、この電界によって両極性トラップの電子がゲート電極5側に引き抜かれる。この結果、チャージトラップ膜4中に正の電荷が発生し、n型FETのVthは低下する。

【0018】

一方、オン状態からVgsを低下させ、再びオフ状態に戻った場合、電子がゲート電極5から再びチャージトラップ膜4に供給され、チャージトラップ膜4中の正電荷は消滅する。この結果、オン状態のVthと比べてオフ状態のVthは大きくなる。

【0019】

図3は、p型FETで、ゲート電極5がp+ポリシリコンの例を示している。より詳細には、図3(a)は、Vgs=0Vで、FETがオフ状態の場合を示している。図3(a)の場合、チャージトラップ膜4中に電界は印加されない。チャージトラップ膜4中の両極性トラップは、電子を保持しているため中性となる。図3(b)は、Vgs<0でp型FETがオン状態の場合を示している。

【0020】

p型FETがオン状態になると、チャージトラップ膜4中に電界が印加され、この電界によってゲート電極5から電子が注入されて、両極性トラップは電子を捕獲する。この結果、チャージトラップ膜4中に負の電荷が発生し、p型FETの|Vth|は低下する。一方、オン状態からVgsを増加させ、再びオフ状態に戻った場合、チャージトラップ膜4が捕獲した電子がゲート電極5へ放出されチャージトラップ膜4中の負電荷は消滅する。この結果、オン状態の|Vth|と比べてオフ状態の|Vth|は大きくなる。

【0021】

このように、n型FETとp型FETのいずれであっても、チャージトラップ膜4は、ゲート電極5と電子授受を行う。この点が本実施形態のVth自己調整FET1の特徴である。本実施形態のチャージトラップ膜4はゲート電極5と直接接している。これは、ゲート電極5と高速に電子授受を行う必要があるためである。また、本実施形態では、チャージトラップ膜4と半導体基板1との間にブロック絶縁膜3を配置している。このブロック絶縁膜3により、半導体基板1の表面付近に形成されるチャネルとチャージトラップ膜との間での電子の授受を抑制できる。

【0022】

以後の説明では、特に断らない限りn型FETを例に挙げて説明する。

【0023】

第1の実施形態では、チャージトラップ膜4の膜厚Tctは0.34<Tct<7nmの範囲である。以下、膜厚Tctがこの範囲に制限される理由を説明する。

【0024】

SiNチャージトラップ膜4の基本構造はSiN4四面体構造であり、またSi−N結合距離は0.17nmである。従って1原子層は0.34nmの厚みを有する。このことから、本実施形態では、0.34nm<Tctを、チャージトラップ膜4の膜厚Tctの下限に関する必須条件としている。

【0025】

チャージトラップ膜4の膜厚Tctが厚い場合、高エネルギー電子の捕獲確率および保持確率が増大する。例えば、非特許文献2では、厚いSiN膜中に注入された高エネルギー電子は注入側から7nmの位置に捕獲される。従って、Tct>7nmの場合、オン状態のときに半導体(チャネル)側から注入された電子がチャージトラップ膜4中に捕獲され、保持される確率が著しく増大する。チャージトラップ膜4中に捕獲された電子は負電荷として作用し、Vthを上昇させる。これは、本実施形態とは逆方向の好ましくないVthの変化である。そこで、本実施形態では、Tct<7nmを、がチャージトラップ膜4の膜厚Tctの上限に関する必須条件としている。

【0026】

また、本実施形態では、以下の1)〜3)の条件を満たすブロック絶縁膜3を備えている。

1)SiNxからなるチャージトラップ膜4とSi基板との間に、SiONからなるブロック絶縁膜3を配置する。

2)ブロック絶縁膜3内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値である。

3)ブロック絶縁膜3の膜厚Toxは、0.64nm<Toxの範囲内の値である。

【0027】

ブロック絶縁膜3がなければ、チャージトラップ膜4はゲート電極5だけでなく半導体基板1内のチャネルとも電子の授受が可能となる。従って、チャネルとの電子授受を阻害もしくは減少させるためにブロック絶縁膜3が必須となる。

【0028】

ブロック絶縁膜3中のNの含有率は、SiとOとNとの合計に対するNのモル比(N/(Si+N+O))で表される。N/(Si+N+O)は、純粋なSiO2膜の場合は0であり、純粋なSi3N4膜の場合は0.57である。通常のCMOS製造工程で使用されるSiONゲート絶縁膜の(N/(Si+N+O))は最小で0、最大で0.35である。また、本実施形態では、SiO2膜をブロック絶縁膜3として使用することも可能である。

【0029】

このように、ブロック絶縁膜3の組成が0≦N/(Si+N+O)<0.35の範囲であるならば、通常のCMOS製造工程で使用されるSiONゲート絶縁膜をそのまま使用でき、製造が容易になる。

【0030】

ブロック絶縁膜3が、チャネルとチャージトラップ膜4との電子授受を阻害もしくは減少させる機能を果たすには、ブロック絶縁膜3の膜厚Toxが上述した3)の条件を満たす必要がある。量子力学的には、チャネル電子の波動関数は0.5nm程度まで絶縁膜中に染み出す。従って、上述した機能を果たすには、2原子層程度の厚さが必要となる。ブロック絶縁膜3は、SiO4四面体、SiN4四面体、またはSiOyN4−y(y:1,2,3)四面体から構成され、Si−O結合距離は0.16nmで、Si−N結合距離は0.17nmである。このことから、ブロック絶縁膜3の1原子層は最小でも0.32nmの厚みを有することになる。

【0031】

このように、上述した3)の条件を満たすことで、ブロック絶縁膜3がチャネルとチャージトラップ膜4との電子授受を阻害もしくは減少させる機能を果たすことになる。この機能は、ゲートリーク電流を低減させる効果とみなすことができる。

【0032】

ブロック絶縁膜3によるゲートリーク電流の低減効果をさらに高めるには、ブロック絶縁膜3の膜厚Toxを、0.64nm<Tox<2.70nmの範囲内の値にするのが望ましい。以下、2.70nmの根拠について説明する。

【0033】

一方、SiNxからなるチャージトラップ膜4は誘電率7.9のhigh−k絶縁膜である。Siの伝導帯に対するSiリッチ組成のSiNxの伝導帯の障壁高さ(ΔEc)は、非特許文献3によれば1.35eVである。通常のLSIの電源電圧VDDは、LSI内のオン状態のFETのゲート絶縁膜の電界Foxが5〜6MV/cmとなるように設計される。

【0034】

図1のFETのように、SiONブロック絶縁膜3とSiNxチャージトラップ膜4の積層構造において、電源電圧VDDのうち、SiONブロック絶縁膜3に印加される電圧をVoxとすると、Vox=Fox×Toxである。Vox<ΔEcであれば、SiNxチャージトラップ膜4も絶縁膜として機能し、ゲートリーク電流の低減に寄与できる。一方、Vox>ΔEcとなると、ゲートリーク電流はSiONブロック絶縁膜3のみによって決定される。従って、ゲートリーク電流低減効果のある臨界ブロック絶縁膜3厚Tox_limitは、Tox_limit<ΔEc/Fox=1.35eV/5[MV/cm]=2.70nmとなる。

【0035】

図4は本実施形態によるVth自己調整FET1の動作原理を実証する実験結果を示すグラフである。

【0036】

図4(a)はn型Vth自己調整FET1のIds−Vgs特性を示している。Tct=2.77nm、x=1.20、Tox=2.92、N/(Si+O+N)=0、ゲート電極5はn+ポリシリコンである。図中0V stdbyと記載されるIV特性は、Vgs=0Vで長時間保持してチャージトラップ膜4を中性状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。一方、VDD stdbyと記載されるIV特性は、Vgs=VDDで長時間保持してチャージトラップ膜4を正の帯電状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。VDDとしてはゲート絶縁膜電界が5.5MV/cmとなるように設定した。図4(a)のグラフから実証されるように、ゲートにVgs>0を印加した状態の方が、ゲートにVgs=0Vを印加した状態よりも、n型FETのVthが低下する。

【0037】

図4(b)はp型Vth自己調整FET1のIds−Vgsを示している。Tct=2.77nm、x=1.20、Tox=2.92,N/(Si+O+N)=0、ゲート電極5はp+ポリシリコンである。図4(a)のn型FETと図4(b)のp型FETは、イオン注入条件を除いて同一の製造プロセスで作製される。図中0V stdbyと記載されるIV特性は、Vgs=0Vで長時間保持しチャージトラップ膜4を中性状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。一方、−VDD stdbyと記載されるIV特性は、Vgs=−VDDで長時間保持してチャージトラップ膜4を負の帯電状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。−VDDとしてはゲート絶縁膜電界が5.5MV/cmとなるように設定した。図4(b)のグラフから実証されるように、ゲートにVgs<0を印加した状態の方が、ゲートにVgs=0Vを印加した状態よりも、p型FETの|Vth|が低下する。

【0038】

図4(a)と図4(b)の実験結果は、n型FETとp型FETの双方に、同一のブロック絶縁膜3と同一のチャージトラップ膜4とを設けることで、チャージトラップ膜4に両極性トラップが生成されて、いずれのFETでも、Vth自己調整機能を持つことを示している。従って、本実施形態によれば、ブロック絶縁膜3とチャージトラップ膜4に関しては、n型FETとp型FETで、製造プロセスを別個に設けなくて済み、少ない工程数でn型FETとp型FETを作製できる。

【0039】

本実施形態によるn型FETとp型FETでは、ゲート電極5の材料として、それぞれn型とp型のポリシリコンを使用することができる。これは通常のFETと同じゲート電極5の材料であり、材料費を抑制できる。

【0040】

あるいは、ゲート電極5として、金属材料を用いても良い。金属材料を用いたメタルゲートは、ゲート電極5内部には原理的に空乏層が発生しないので、多結晶シリコンゲートの場合のように空乏層によるFETの電流駆動力の低下は起きない。また、本実施形態によるFETにメタルゲートを用いると、チャージトラップ膜4とゲート電極5との界面に空乏層が発生しないため、チャージトラップ膜4とゲート電極5間の電子授受をより高速に行うことができる。空乏層を発生させないためには、ゲート電極5のうち、少なくともチャージトラップ膜4と接する部分を金属材料で形成する必要がある。メタルゲートの金属材料としては、TaC、TaN、TiN、TiCN、TiAlN、W、WN、Moなどのタンタル,チタン,タングステン、モリブデンなどの高融点金属、あるいはこれら金属の炭化物、窒化物、Al化合物を使用することができる。

【0041】

上述したように、本実施形態では、ブロック絶縁膜3とチャージトラップ膜4の膜厚、材料および組成を特定しているが、膜厚、材料および組成は、ゲート電極5の表面から半導体基板側の所定位置をFIB(Focused Ion Beam)によるピックアップ法で切り出し、断面を高分解能透過電子顕微鏡(HRTEM)で撮像するか、若しくはエネルギー分散型X線分析(EDX:Energy Dispersive X-ray Analysis)、若しくは電子エネルギー損失分光法(EELS:Electron Energy-Loss Spectroscopy)で分析すれば、明らかにすることができる。

【0042】

例えば、非特許文献4はMNOS(Metal-Nitride-Oxide-Silicon)メモリを開示している。MNOSメモリは、半導体基板2上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されたチャージトラップ膜4と、チャージトラップ膜4上に形成されたゲート電極5とを備え、チャージトラップ膜4はSiN膜で構成され、その膜厚は最低7nm以上で典型的には20nm程度であり、トンネル絶縁膜はSiO2膜で構成され、その膜厚は典型的には1.8nmである。

【0043】

n型MNOSメモリは、書込時には、ゲートに正の高いバイアスを印加し、チャネルから注入された電子を厚いSiN膜中に捕獲する。この結果Vthが上昇する。書込時の電界は通常10MV/cm以上である。一度捕獲された電子は、ゲートバイアスをオフした際もSiN膜中に保持されるため、高いVthはゲートバイアスをオフにしても維持される。消去時には、基板に高い正のバイアスを印加するか、ゲートに高い負のバイアスを印加し、SiN膜に捕獲された電子をチャネル側へ引き抜く。

【0044】

このように、MNOSメモリは、書込/消去時に、チャネルとSiN膜との間で電子授受を行い、書込み時にはVthを上昇させている。これに対して、本実施形態は、チャネルとチャージトラップ膜4との電子の授受をできるだけ制限するために、チャネルとチャージトラップ膜4の間にブロック絶縁膜3を配置し、かつ、チャージトラップ膜4とゲート電極5との間で電子の授受を行なって、n型FETがオン状態のときにはVthを下げている。このように、MNOSメモリと本実施形態によるFETとは、素子の構造と動作原理がいずれも異なっている。

【0045】

MNOSメモリとして機能するには、書込時に高エネルギー電子を捕獲し且つ捕獲電子がゲート電極5側もしくは半導体側へ放出されることを阻止する必要があり、Tct>14nmが必須条件となる。これに対して、本実施形態によるFETでは、Tct<7nmである。

【0046】

また、MNOSメモリにおけるトンネル絶縁膜の膜厚は、書込時に十分な量の注入電子を確保するために、2nm以下、典型的には1.8nm程度とする必要がある。これは、トンネル絶縁膜の膜厚が2nm以下になると直接トンネル電流が著しく増大するためである。これに対して、本実施形態のFETは、チャネル側から電子を引き込まないため、ブロック酸化膜を薄くする必要は特にない。

【0047】

このように、MNOSメモリは、本実施形態によるFETとは構造も全く異なる上に、動作原理も全く異なり、得られる効果も本実施形態とは当然に異なる。

【0048】

上述したように、第1の実施形態では、ブロック絶縁膜3、チャージトラップ膜4およびゲート電極5を積層してVth自己調整FET1を形成し、チャージトラップ膜4とゲート電極5との間で電子の授受を行い、チャージトラップ膜4とチャネルとの間での電子の授受をブロック絶縁膜3で防止するようにしたため、FETがオン状態のときには駆動力性能が向上するようなVthに変化させ、FETがオフ状態のときには遮断性能が向上するようなVthに変化させることができる。

【0049】

(第2の実施形態)

第2の実施形態は、第1の実施形態で説明したFETをSRAM内の一部のトランジスタに適用するものである。

【0050】

図5は第2の実施形態による半導体装置の回路図であり、より具体的にはSRAMセルの回路図である。

【0051】

図5のSRAMセル10は、第1の電源線VSSおよび第2の電源線VDDの間に直列に接続される第1のn型FET11および第1のp型FET12と、第1の電源線VSSおよび第2の電源線VDDの間に直列に接続される第2のn型FET13および第2のp型FET14と、第1のn型FET11および第1のp型FET12の間の第1の接合部j1と、第2のn型FET13および第2のp型FET14の間の第2の接合部j2と、第2のn型FET13のゲート、第2のp型FET14のゲート、および第1の接合部j1に接続される第1のデータノードn1と、第1のn型FET11のゲート、第1のp型FET12のゲート、および第2の接合部j2に接続される第2のデータノードn2と、第1のデータノードn1および第1のデータ線BLの間に接続される第3のn型FET15と、第2のデータノードn2および第2のデータ線BLBの間に接続される第4のn型FET16と、を備えている。

【0052】

このように、図5のSRAMセル10は、6個のFET11〜16からなり、そのうちの4個のFET11〜14はフリップフロップ(FF)を構成している。より詳細には、SRAMセル10内のフリップフロップは、2個のn型FET11,13からなるプルダウントランジスタPDと、2個のp型FET12,14からなるプルアップトランジスタPUとを有する。

【0053】

SRAMセル10内のフリップフロップ以外の2個のFET15,16は、トランスファゲートTGを構成している。

【0054】

本実施形態では、2個のプルダウントランジスタPDを、図1と同一の構造、材料、組成範囲および膜厚範囲を持つVth自己調整FET1で構成することにより、SRAMのデータ保持特性と読出し特性を共に改善することができる。

【0055】

2個のプルダウントランジスタPDは、SRAMセル10の保持データの論理に応じて、相補的にオン状態もしくはオフ状態となる。SRAMセル10内の第1および第2のデータノードn1,n2に保持されるデータの安定性は、オフ状態のプルダウントランジスタPDのVthが高いほうが高くなる。

【0056】

一方、SRAMの読み出し速度は、オン状態のプルダウントランジスタPDのVthが低い方が速くなる。SRAMセル10内のプルダウントランジスタPDをVth自己調整FET1で構成すると、保持データの論理に応じてプルダウントランジスタPDのVthが動的に変化する。このため、保持データの論理に関係なく、常にオフ状態のPDのVthが高く、オン状態のPDのVthが低いSRAMセル10を実現でき、SRAMのデータ保持特性と読み出し特性が共に改善されうる。

【0057】

SRAMセル10内の2個のプルダウントランジスタPDだけでなく、2個のトランスファゲートTGも、図1と同一の構造のn型Vth自己調整FET1で構成してもよい。これにより、SRAMのデータ書き込み特性をも同時に改善することができる。

【0058】

書き込み特性の改善には、トランスファゲートTGの駆動力向上が重要である。トランスファゲートTGをVth自己調整FET1で構成すると、トランスファゲートTGのオン状態でのVthが低下するため、駆動力の向上が図れる。

【0059】

また、SRAMセル10内のプルダウントランジスタPDとトランスファゲートTGに加えて、2個のプルアップトランジスタPUも、図1と同一の構造のp型Vth自己調整FET1で構成してもよい。これにより、SRAMのスタティックリーク電流を低減することができる。

【0060】

データ保持状態では、VDDとVSSの間に直列に接続されるn型FETとp型FETは、片方がオン状態、もう片方がオフ状態となる。PUをVth自己調整FET1で構成することにより、オフ状態におけるp型FETのVthを上昇させて遮断性能を向上させることができる。これにより、第1および第2の電源線VDD,VSSとの間を流れるリーク電流を低減することができる。

【0061】

さらにまた、SRAMセル10を構成するすべてのトランジスタPD、PU、TGを図1と同一の構造のVth自己調整FET1で構成してもよい。この場合、各トランジスタのブロック絶縁膜3はすべて同一構造になり、チャージトラップ膜4も同一構造である。したがって、SRAMセル10内の全トランジスタのブロック絶縁膜3を一つの工程で作製でき、同様にチャージトラップ膜4も一つの工程で作製できる。よって、SRAMセル10の製造工程数を大幅に削減でき、製造コストの削減が図れる。

【0062】

この第2の実施形態では、チャージトラップ膜4の膜厚Tctは0.45<Tct<2.45nmの範囲であること、より好ましくは0.72nm<Tct<2.00nmである。以下、これらの数値範囲の根拠について説明する。

【0063】

少なくとも一部のトランジスタを図1のVth自己調整FET1で構成したSRAMセル10において、好ましいVth変調量(ΔVth)は、50mV<ΔVth<200mVの範囲内であり、好ましくは100mV程度である。

【0064】

SRAMを構成するFETのVthのバラツキは典型的にはσVth=50mVである。Vth自己調整機能により有意な効果を得るには、ΔVth>σVth=50mVである必要がある。非特許文献1によれば、Vth自己調整FET1で構成したSRAMにおいて最適なΔVthは100mV程度である。一方ΔVthが200mV以上であると書込特性が劣化する。

【0065】

図6はΔVthとSiNx膜の膜厚Tctとの関係についての実験結果を示すグラフである。図6(a)はx=1.07とx=1.20のSiNx膜を有するn型Vth自己調整FET1について、ΔVthとTctの関係を示すグラフである。図6(b)は、x=1.20のSiNx膜を有するn型Vth自己調整FET(nFET)とp型Vth自己調整FET(pFET)について、ΔVthとTctの関係を示すグラフである。

【0066】

図6(a)のグラフによれば、n型FETでΔVth=50mV,100mV,200mVを与えるSiNx膜厚Tctは、x=1.20の場合はそれぞれTct=0.83nm,1.66nm,2.45nmであり、x=1.07の場合はそれぞれTct=0.45nm,0.90nm、1.80nmである。

【0067】

図6(a)のグラフから、Vth自己調整FET1で構成したSRAMでは、0.45nm<Tct<2.45nmであることが望ましい。さらに最適ΔVthである100mVの±20%を得ようとする場合、0.72nm<Tct<2.00nmであることが望ましいことがわかる。

【0068】

第2の実施形態では、SiONブロック絶縁膜3の膜厚Toxは0.64nm<Tox<2.70nmの範囲であること、より好ましくは0.87nm<Tox<2.70nmの範囲であること、さらにより好ましくは1.09nm<Tox<2.70nmの範囲であることが望ましい。以下、これらの数値範囲の根拠について説明する。

【0069】

図7は、SiONブロック絶縁膜3とSiNxチャージトラップ膜4からなる積層ゲートスタックについて、ゲートリーク電流JgとSiONブロック絶縁膜3の膜厚Toxの関係を示す図である。図7(a)は、SiNxチャージトラップ膜4の膜厚Tctが0.45nmと0.83nmの2つの場合について、Jg−Toxのグラフを示している。図7(b)は、上述した積層ゲートスタックのエネルギーバンド図である。

【0070】

図7(a)では、ゲートリーク電流JgはWKB近似を用い、ΔEc(SiNx)=1.35eV、ΔEc(SiO2)=3.1eVを仮定して計算した。SRAMのゲートリーク電流Jgは10A/cm2以下にする必要がある。図7(a)によれば、Jg=10A/cm2となるには、Tct=0.83nmであればTox=0.87nmとなり、Tct=0.45nmであればTox=1.09nmとなる。従って、0.83nm<ToxであればTctが0.83nmであってもJg<10A/cm2となる。さらに、1.09nm<ToxであればTctが0.45nmであってもJg<10A/cm2となる。

【0071】

第2の実施形態では、プルダウントランジスタPDとトランスファゲートTGのn型FETのボディコンタクト(基板電位)をVSSに、プルアップトランジスタPUのp型FETのボディコンタクトをVDDに接続する。従って、基板とソース、もしくは基板とドレインの間のpn接合は逆方向バイアス条件を満たすことになり、大きなリーク電流が流れることはない。これに対して、上述した非特許文献1では、SRAMセル内のフリップフロップのn型FETのボディコンタクトがVDDに、p型FETのボディコンタクトがVSSに接続されており、基板からソース/ドレイン領域に大きなリーク電流が流れてしまう。

【0072】

また、第2の実施形態では、プルダウントランジスタPDとトランスファゲートTGを構成するn型FETのゲート電極5をn型ポリシリコン膜とし、プルアップトランジスタPUのp型FETのゲート電極5をp型ポリシリコン膜とすることを想定しており、ゲート電極5の材料に関しては通常のSRAMセル10と同じである。第1の実施形態で既に説明したように、ゲート電極5をポリシリコン膜で形成しても、図1のVth自己調整FET1を作製できる。したがって、第2の実施形態によるSRAMセル10は安価な材料で作製でき、材料費を含めた製造コストを抑制できる。

【0073】

ただし、ゲート電極5の材料は、必ずしもポリシリコンには限定されない。例えば、プルダウントランジスタPDとトランスファゲートTGのn型FETおよびプルアップトランジスタPUのp型FETのゲート電極5を金属材料で形成してもよい。この場合、TaC、TaN、TiN、TiCN、TiAlN、W、WN、Moなどのチタン,モリブデン,タングステン、タンタルなどの高融点金属およびその炭化物、窒化物からなるメタルゲートを使用し得る。

【0074】

このように、第2の実施形態では、SRAMセル10を構成する6個のトランジスタのうち、少なくとも一部のトランジスタを図1のVth自己調整FET1で構成するため、SRAMのデータ保持特性、データ読出し特性、およびデータ書き込み特性などを必要に応じて向上でき、また、リーク電流を低減することも可能である。

【0075】

(第3の実施形態)

第3の実施形態は、図1のVth自己調整FET1を用いてプログラマブルスイッチを実現するものである。プログラマブルスイッチとは、スイッチとして機能するFETのゲートにメモリを接続して、メモリの保持データによって、FETのオン/オフ状態を切替制御するものである。典型的なFPGA(Field Programmable Gate Array)はロジックエレメントとプログラマブルスイッチのアレーで構成されている。各プログラマブルスイッチはロジックエレメントを選択的に接続する役割を担う。

【0076】

図8は第3の実施形態による半導体装置の回路図である。図8の半導体装置はプログラマブルスイッチ20であり、オン/オフ切替用のn型FET(以下、スイッチFET)17と、このスイッチFET17のゲートに印加すべきデータを記憶するSRAMセル10aとを備えている。

【0077】

スイッチFET17は、SRAMセル10a内に保持されたデータの論理によって、オンまたはオフする。SRAMセル10aの保持データは書換え可能であるため、図8の回路はプログラマブルスイッチ20として機能する。

【0078】

図8のSRAMセル10aは、回路構成としては図5と同じであるが、SRAMセル10a内のトランジスタをVth自己調整FET1で構成する必要はなく、通常のSRAMセル10aでよい。

【0079】

図8のスイッチFET17は、図1のVth自己調整FET1であり、このFET内のチャージトラップ膜4とブロック絶縁膜3の材料、組成および膜厚は第1の実施形態で説明したものと同じである。スイッチFET17を図1のVth自己調整FET1にすることで、SRAMセル10aにオン状態がプログラムされている場合はスイッチFET17のVthを自動的に低下させ、オフ状態がプログラムされている場合はスイッチFET17のVthを自動的に高くすることができる。この結果、オン状態にプログラムされたスイッチFET17の駆動力性能は向上し、オフ状態にプログラムされたスイッチFET17の遮断性能も向上する。

【0080】

なお、第2の実施形態と同様に、図8のSRAMセル10a内の少なくとも一部のトランジスタを、図1のVth自己調整FET1にしてもよい。この場合、第2の実施形態の効果と第3の実施形態の効果を併せ持つプログラマブルスイッチ20を実現できる。

【0081】

このように、第3の実施形態では、SRAMセル10aとスイッチFET17を用いたプログラマブルスイッチ20を作製する際に、スイッチFET17の駆動力性能と遮断性能を向上できる。

【0082】

(第4の実施形態)

第4の実施形態は、SRAMではなく、不揮発性メモリを用いてプログラマブルスイッチ20を実現するものである。

【0083】

図9は第4の実施形態による半導体装置の回路図であり、2個の不揮発性メモリセル(第1および第2の不揮発FET)21,22と、図1のVth自己調整FET1で構成されるn型FET(以下、スイッチFET)23とで、プログラマブルスイッチ20aを構成している。

【0084】

図9の回路において、一方の不揮発性メモリセル21は第1のデータ線BLとデータノードn1との間に接続され、他方の不揮発性メモリセル22は第2のデータ線BLBとデータノードn1との間に接続されている。データノードn1は、スイッチFET23のゲートに接続されている。

【0085】

図9のプログラマブルスイッチ20aにおいても、スイッチFET23をVth自己調整FET1で構成することで、スイッチFET23の駆動力性能と遮断性能を共に改善することができる。

【0086】

また、スイッチFET23をVth自己調整FET1で構成することで、スイッチFET23の高耐圧性能をも改善することができる。例えば、不揮発性メモリセル21,22がFN(Fowler-Nordheim)型書込方式を採用する場合、スイッチFET23は高耐圧でなければならない。これは、FN型書込方式で選択書込を行う場合は、非選択セルのスイッチFET23のゲートに高い電圧が印加されるためである。高いバイアスによる破壊を回避するため通常はスイッチFET23のゲート絶縁膜の膜厚を厚くする必要がある。しかし、この場合スイッチFET23の駆動力性能が劣化する。スイッチFET23をVth自己調整FET1で構成することにより、ゲート絶縁膜の膜厚を厚くした場合と同等の高耐圧性能を維持したまま駆動力性能を改善できる。

【0087】

第4の実施形態では、不揮発メモリとして、例えばSONOS型不揮発FETを用いることができる。SONOS型不揮発FETは、半導体基板2上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されたチャージトラップ膜と、チャージトラップ膜上に形成されたブロック絶縁膜と、ブロック絶縁膜上に形成されたキャップ膜と、キャップ膜上に形成されたゲート電極とを備えている。

【0088】

SONOS型不揮発FETのトンネル膜としては、例えばSiO2/SiNx/SiO2からなるONOスタックを使用することができる。チャージトラップ膜としては、例えばSiリッチ組成のSiNx膜を使用することができる。ブロック絶縁膜としては、例えばSiO2/SiNx/SiO2からなるONOスタックを使用することができる。また、ブロック絶縁膜としては、例えばAl2O3膜を使用することもできる。キャップ膜としては、SiN膜を使用することができる。ゲート電極としては、n型ポリシリコンを使用することができる。

【0089】

なお、第4の実施形態における不揮発性メモリの他の具体例としては、FG(Floating Gate)型の不揮発FETを用いてもよい。

【0090】

このように、第4の実施形態では、不揮発性メモリに記憶されたオン/オフ情報に基づいて切替動作を行なうプログラマブルスイッチ20a内のスイッチFET23を図1のVth自己調整FET1で構成するため、不揮発性メモリへの書き込み時に印加される高電圧にも耐えうる高耐圧性能をスイッチFET23に持たせることができ、かつスイッチFET23の駆動力性能と遮断性能を向上できる。

【0091】

(第5の実施形態)

第5の実施形態は、図1のVth自己調整FET1をパワーゲーティング回路に適用したものである。

【0092】

図10および図11は第5の実施形態による半導体装置の回路図であり、パワーゲーティング回路30の回路構成を示している。

【0093】

パワーゲーティング回路30は、LSIの消費電力を抑制するために用いられる。より具体的には、LSI内部の論理回路部を、独立した電源制御が可能な複数のサブ論理回路ブロック24に分割し、各サブ論理回路ブロック24に電源電圧を供給するか否かをパワーゲーティング回路30で制御することにより、LSIの消費電力を抑制する。

【0094】

図10および図11に示すように、各サブ論理回路ブロック24は仮想電源線Virtual-VDD(仮想接地線Virtual-VSS)に接続されている。各サブ論理回路ブロック24ごとにパワーゲーティング回路30が設けられ、パワーゲーティング回路30は、LSIの電源線VDD(接地線VSS)と仮想電源線Virtual-VDD(仮想接地線Virtual-VSS)との間に接続されている。

【0095】

図10のパワーゲーティング回路30は、LSIの電源線VDDの電圧を仮想電源線VDDに供給するか否かを切り替えるp型FET(以下、電源スイッチFET)25を有し、この電源スイッチFET25はイネーブル信号ENによりオン/オフ制御される。また、図11のパワーゲーティング回路30は、LSIの接地線VSSと仮想接地線VSSとの間にn型FET(電源スイッチFET)26を接続している。

【0096】

図10および図11に示す電源スイッチFET25,26は、図1のVth自己調整FET1で構成されており、このFET内のチャージトラップ膜4とブロック絶縁膜3の材料、組成および膜厚は第1の実施形態で説明したものと同じである。

【0097】

電源スイッチFET25,26のオフ時のリーク電流Ioffがアイドル時のリーク電流を決めるため、電源スイッチFET25,26には極めて高い遮断性能、即ち極めて低いIoff性能が必要である。一方、電源スイッチFET25,26のオン時の抵抗が電源線VDDと擬似電源線Virtual-VDD間、あるいは擬似接地線Virtual-Vssと接地線Vss間の電圧降下量を決めるため、電源スイッチFET25,26のオン抵抗は極めて低く、即ち極めて高いIon性能が必要である。

【0098】

本実施形態によるパワーゲーティング回路30では、電源スイッチFET25,26を図1のVth自己調整FET1で構成するため、電源スイッチFET25,26のオン時にはオンし易くして、オフ時には遮断性をよくすることができ、上述したIon性能とIoff性能を共に向上できる。

【0099】

これに対して、特許文献2には、電源スイッチFETを高Vthトランジスタで構成することによりIoff性能を向上させる手法が開示されている。ところが、電源スイッチFET25,26には極めて低いIoff性能のみならず、極めて高いIon性能をも必要とされるが、特許文献2にはIon性能の向上は念頭に置いておらず、Ion性能を向上させる手法も開示されていない。

【0100】

このように、第5の実施形態では、パワーゲーティング回路30内の電源スイッチFET25,26を図1のVth自己調整FET1で構成するため、Ion性能とIoff性能を共に向上できる。

【0101】

ところで、電源スイッチFET25,26をVth自己調整FET1で構成すると、通常のFETと比べて、オン/オフの切替に時間がかかる。これは、チャージトラップ膜4とゲート電極5との間で主に電子の授受を行なうためである。ところが、パワーゲーティング回路30の場合、対応するサブ論理回路ブロック24の電源状態を頻繁に切り替えることはなく、逆に高速に電源状態を切り替えると、サブ論理回路ブロック24内に突入電流が流れるという問題がある。本実施形態のように、電源スイッチFET25,26をVth自己調整FET1で構成すると、電源状態を切り替えるのに時間はかかるものの、サブ論理回路ブロック24内に突入電流が流れるおそれはなく、各サブ論理回路ブロック24をより安定に動作させることができる。

【0102】

本発明の態様は、上述した個々の実施形態に限定されるものではなく、当業者が想定しうる種々の変形も含むものであり、本発明の効果も上述した内容に限定されない。すなわち、特許請求の範囲に規定された内容およびその均等物から導き出される本発明の概念的な思想と趣旨を逸脱しない範囲で種々の追加、変更および部分的削除が可能である。

【符号の説明】

【0103】

1 Vth自己調整FET、3 ブロック絶縁膜、4 チャージトラップ膜、5 ゲート電極、10 SRAMセル、11,13 プルダウントランジスタPD、12,14 プルアップトランジスタPU、15,16 トランスファゲートTG、20,20a プログラマブルスイッチ、30 パワーゲーティング回路

【技術分野】

【0001】

本発明の実施形態は、FETを備えた半導体装置に関する。

【背景技術】

【0002】

n型FETはゲート電圧が閾値電圧(Vth)を上回るとオン状態になり、ソースとドレイン間の抵抗が低くなる。通常のFETでは、Vthはオン状態とオフ状態に係わらず一定値である。これに対して、オンするとVthが下がり、オフすると再びVthが上がる機能を持つn型FETが提案されており、この機能は、Vth自己調整機能と呼ばれる。

【0003】

例えば、非特許文献1には、強誘電体膜を応用したVth自己調整機能を持つFET(以下、Vth自己調整FET)を利用したSRAMが開示されている。SRAMをVth自己調整FETで構成することによって、SRAMのデータ保持特性と読み出し特性を共に改善することができる。開示されたVth自己調整FETのゲートスタック部は、シリコン基板上に形成されたHf−Al−Oからなるバッファ層と、バッファ層上に形成されるSrBi2Ta2O9(SBT)強誘電体膜と、SBT膜上に形成されるPtメタル電極とで構成されている。

【0004】

この他、従来の技術として、不揮発メモリTrを使用する不揮発プログラマブルスイッチや、電源スイッチFETを高Vthトランジスタで構成してIoff性能を向上させる技術や、チャージトラップ膜の膜厚を厚くして高エネルギー電子の捕獲確率および保持確率を向上させる技術などが開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公報6,002,610号

【特許文献2】特許第2,631,335号公報

【非特許文献】

【0006】

【非特許文献1】Shuhei Tanakamaru, Teruyoshi Hatanaka, Ryoji Yajima, Mitsue Takahashi, Shigeki Sakai and Ken Takeuchi, IEDM Tech. Dig., p283 (2009).

【非特許文献2】Shosuke Fujii, Naoki Yasuda, Jun Fujiki, “A new method to extract the charge centroid in the program operatIon of metal-oxide-nitride-oxide-semiconductor memories”, Japanese Journal of Applied Physics 49, 04DD06-1 (2010).

【非特許文献3】N. Goel, et.al., “Erase and RetentIon Improvements in Charge Trap Flash Through Engineered Charge Storage Layer”, IEEE Electron Device Letters 30, 216 (2009).

【非特許文献4】Y. Kamigaki, et.al., IEICE trans. Electron. E84-C, 713 (2001).

【発明の概要】

【発明が解決しようとする課題】

【0007】

本実施形態が解決しようとする課題は、FETの駆動力性能や遮断性能などを向上できる半導体装置を提供することである。

【課題を解決するための手段】

【0008】

本発明の一態様では、半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、

前記絶縁膜の上方に配置されるゲート電極と、

前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態による半導体装置の断面図。

【図2】本実施形態によるn型FETの動作原理を説明する図。

【図3】本実施形態によるp型FETの動作原理を説明する図。

【図4】本実施形態によるVth自己調整FET1の動作原理を実証する実験結果を示すグラフ。

【図5】第2の実施形態による半導体装置の回路図であり、より具体的にはSRAMセルの回路図。

【図6】ΔVthとSiNx膜の膜厚Tctとの関係についての実験結果を示すグラフ。

【図7】SiONブロック絶縁膜3とSiNxチャージトラップ膜4からなる積層ゲートスタックについて、ゲートリーク電流JgとSiONブロック絶縁膜3の膜厚Toxの関係を示す図。

【図8】第3の実施形態による半導体装置の回路図。

【図9】第4の実施形態による半導体装置の回路図。

【図10】第5の実施形態による半導体装置の回路図。

【図11】第5の実施形態による他の半導体装置の回路図。

【発明を実施するための形態】

【0010】

以下、図面を参照しながら、本発明の実施形態を説明する。

【0011】

(第1の実施形態)

図1は第1の実施形態による半導体装置の断面図である。図1の半導体装置は、オン状態とオフ状態で閾値電圧Vthを自動的に調整可能なVth自己調整FET1である。図1のVth自己調整FET1は、半導体基板2上に形成されるブロック絶縁膜3と、ブロック絶縁膜3上に形成されるチャージトラップ膜4と、チャージトラップ膜4上に形成されるゲート電極5とを備えている。チャージトラップ膜4は、ブロック絶縁膜3の下部に形成されるチャネルとの間よりも、ゲート電極5との間で、より多くの電子の授受を行なう。

【0012】

チャージトラップ膜4は、SiNx膜であり、xはSiに対するNのモル比であって、0.67<x<1.33の範囲内の値である。チャージトラップ膜4の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値である。

【0013】

ブロック絶縁膜3は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値である。ブロック絶縁膜3の膜厚Toxは、0.64nm<Toxの範囲内の値であり、より好ましくは0.64nm<Tox<2.70nmである。

【0014】

SiNx膜3の化学量論的組成はSi3N4であり、その場合のSiに対するNのモル比はx=1.33となる。x<1.33のSiNx膜は、Siの組成比が大きいSiリッチな組成となり、この場合は、Si原子が未結合手(ダングリングボンド)を所持することになり、このダングリングボンドの存在により、両極性トラップが生成されると考えられる。両極性トラップの密度は、xが1.33よりも低下するに従って増加する。両極性トラップは電子を1つ有する場合が中性で、その電子を放出すると正に帯電し、別個の電子を捕獲して計2つの電子を所持すると負に帯電する。後述するように、Vth自己調整機能を持つには、チャージトラップ膜4が両極性トラップを有することが必須であり、本実施形態では、ブロック絶縁膜3を構成するSiNx膜のx<1.33が必須条件となる。

【0015】

x=0.67は平均的に、Siの4つの結合手の内2つが未結合手となるか、隣接Siと共有結合を形成する組成に相当する。この場合、共有結合が大量に存在することになり、SiNx膜の絶縁性が劣化して、ゲートリーク電流が著しく増大する。従って、0.67<xが望ましい。

【0016】

図2および図3は本実施形態によるVth自己調整FET1の動作原理を説明する図であり、電子の移動方向をFETの断面図とエネルギーバンドを使って図示している。図2は、n型FET1で、ゲート電極5がn+ポリシリコンの例を示している。

【0017】

より詳細には、図2(a)は、ゲート−ソース間電圧Vgs=0Vで、n型FETがオフ状態の場合を示している。図2(a)の場合、チャージトラップ膜4中に電界は印加されない。チャージトラップ膜4中の両極性トラップは電子を保持しているため、中性となる。図2(b)は、Vgs>0で、n型FETがオン状態の場合を示している。この場合、チャージトラップ膜4中には電界が印加されるが、この電界によって両極性トラップの電子がゲート電極5側に引き抜かれる。この結果、チャージトラップ膜4中に正の電荷が発生し、n型FETのVthは低下する。

【0018】

一方、オン状態からVgsを低下させ、再びオフ状態に戻った場合、電子がゲート電極5から再びチャージトラップ膜4に供給され、チャージトラップ膜4中の正電荷は消滅する。この結果、オン状態のVthと比べてオフ状態のVthは大きくなる。

【0019】

図3は、p型FETで、ゲート電極5がp+ポリシリコンの例を示している。より詳細には、図3(a)は、Vgs=0Vで、FETがオフ状態の場合を示している。図3(a)の場合、チャージトラップ膜4中に電界は印加されない。チャージトラップ膜4中の両極性トラップは、電子を保持しているため中性となる。図3(b)は、Vgs<0でp型FETがオン状態の場合を示している。

【0020】

p型FETがオン状態になると、チャージトラップ膜4中に電界が印加され、この電界によってゲート電極5から電子が注入されて、両極性トラップは電子を捕獲する。この結果、チャージトラップ膜4中に負の電荷が発生し、p型FETの|Vth|は低下する。一方、オン状態からVgsを増加させ、再びオフ状態に戻った場合、チャージトラップ膜4が捕獲した電子がゲート電極5へ放出されチャージトラップ膜4中の負電荷は消滅する。この結果、オン状態の|Vth|と比べてオフ状態の|Vth|は大きくなる。

【0021】

このように、n型FETとp型FETのいずれであっても、チャージトラップ膜4は、ゲート電極5と電子授受を行う。この点が本実施形態のVth自己調整FET1の特徴である。本実施形態のチャージトラップ膜4はゲート電極5と直接接している。これは、ゲート電極5と高速に電子授受を行う必要があるためである。また、本実施形態では、チャージトラップ膜4と半導体基板1との間にブロック絶縁膜3を配置している。このブロック絶縁膜3により、半導体基板1の表面付近に形成されるチャネルとチャージトラップ膜との間での電子の授受を抑制できる。

【0022】

以後の説明では、特に断らない限りn型FETを例に挙げて説明する。

【0023】

第1の実施形態では、チャージトラップ膜4の膜厚Tctは0.34<Tct<7nmの範囲である。以下、膜厚Tctがこの範囲に制限される理由を説明する。

【0024】

SiNチャージトラップ膜4の基本構造はSiN4四面体構造であり、またSi−N結合距離は0.17nmである。従って1原子層は0.34nmの厚みを有する。このことから、本実施形態では、0.34nm<Tctを、チャージトラップ膜4の膜厚Tctの下限に関する必須条件としている。

【0025】

チャージトラップ膜4の膜厚Tctが厚い場合、高エネルギー電子の捕獲確率および保持確率が増大する。例えば、非特許文献2では、厚いSiN膜中に注入された高エネルギー電子は注入側から7nmの位置に捕獲される。従って、Tct>7nmの場合、オン状態のときに半導体(チャネル)側から注入された電子がチャージトラップ膜4中に捕獲され、保持される確率が著しく増大する。チャージトラップ膜4中に捕獲された電子は負電荷として作用し、Vthを上昇させる。これは、本実施形態とは逆方向の好ましくないVthの変化である。そこで、本実施形態では、Tct<7nmを、がチャージトラップ膜4の膜厚Tctの上限に関する必須条件としている。

【0026】

また、本実施形態では、以下の1)〜3)の条件を満たすブロック絶縁膜3を備えている。

1)SiNxからなるチャージトラップ膜4とSi基板との間に、SiONからなるブロック絶縁膜3を配置する。

2)ブロック絶縁膜3内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値である。

3)ブロック絶縁膜3の膜厚Toxは、0.64nm<Toxの範囲内の値である。

【0027】

ブロック絶縁膜3がなければ、チャージトラップ膜4はゲート電極5だけでなく半導体基板1内のチャネルとも電子の授受が可能となる。従って、チャネルとの電子授受を阻害もしくは減少させるためにブロック絶縁膜3が必須となる。

【0028】

ブロック絶縁膜3中のNの含有率は、SiとOとNとの合計に対するNのモル比(N/(Si+N+O))で表される。N/(Si+N+O)は、純粋なSiO2膜の場合は0であり、純粋なSi3N4膜の場合は0.57である。通常のCMOS製造工程で使用されるSiONゲート絶縁膜の(N/(Si+N+O))は最小で0、最大で0.35である。また、本実施形態では、SiO2膜をブロック絶縁膜3として使用することも可能である。

【0029】

このように、ブロック絶縁膜3の組成が0≦N/(Si+N+O)<0.35の範囲であるならば、通常のCMOS製造工程で使用されるSiONゲート絶縁膜をそのまま使用でき、製造が容易になる。

【0030】

ブロック絶縁膜3が、チャネルとチャージトラップ膜4との電子授受を阻害もしくは減少させる機能を果たすには、ブロック絶縁膜3の膜厚Toxが上述した3)の条件を満たす必要がある。量子力学的には、チャネル電子の波動関数は0.5nm程度まで絶縁膜中に染み出す。従って、上述した機能を果たすには、2原子層程度の厚さが必要となる。ブロック絶縁膜3は、SiO4四面体、SiN4四面体、またはSiOyN4−y(y:1,2,3)四面体から構成され、Si−O結合距離は0.16nmで、Si−N結合距離は0.17nmである。このことから、ブロック絶縁膜3の1原子層は最小でも0.32nmの厚みを有することになる。

【0031】

このように、上述した3)の条件を満たすことで、ブロック絶縁膜3がチャネルとチャージトラップ膜4との電子授受を阻害もしくは減少させる機能を果たすことになる。この機能は、ゲートリーク電流を低減させる効果とみなすことができる。

【0032】

ブロック絶縁膜3によるゲートリーク電流の低減効果をさらに高めるには、ブロック絶縁膜3の膜厚Toxを、0.64nm<Tox<2.70nmの範囲内の値にするのが望ましい。以下、2.70nmの根拠について説明する。

【0033】

一方、SiNxからなるチャージトラップ膜4は誘電率7.9のhigh−k絶縁膜である。Siの伝導帯に対するSiリッチ組成のSiNxの伝導帯の障壁高さ(ΔEc)は、非特許文献3によれば1.35eVである。通常のLSIの電源電圧VDDは、LSI内のオン状態のFETのゲート絶縁膜の電界Foxが5〜6MV/cmとなるように設計される。

【0034】

図1のFETのように、SiONブロック絶縁膜3とSiNxチャージトラップ膜4の積層構造において、電源電圧VDDのうち、SiONブロック絶縁膜3に印加される電圧をVoxとすると、Vox=Fox×Toxである。Vox<ΔEcであれば、SiNxチャージトラップ膜4も絶縁膜として機能し、ゲートリーク電流の低減に寄与できる。一方、Vox>ΔEcとなると、ゲートリーク電流はSiONブロック絶縁膜3のみによって決定される。従って、ゲートリーク電流低減効果のある臨界ブロック絶縁膜3厚Tox_limitは、Tox_limit<ΔEc/Fox=1.35eV/5[MV/cm]=2.70nmとなる。

【0035】

図4は本実施形態によるVth自己調整FET1の動作原理を実証する実験結果を示すグラフである。

【0036】

図4(a)はn型Vth自己調整FET1のIds−Vgs特性を示している。Tct=2.77nm、x=1.20、Tox=2.92、N/(Si+O+N)=0、ゲート電極5はn+ポリシリコンである。図中0V stdbyと記載されるIV特性は、Vgs=0Vで長時間保持してチャージトラップ膜4を中性状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。一方、VDD stdbyと記載されるIV特性は、Vgs=VDDで長時間保持してチャージトラップ膜4を正の帯電状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。VDDとしてはゲート絶縁膜電界が5.5MV/cmとなるように設定した。図4(a)のグラフから実証されるように、ゲートにVgs>0を印加した状態の方が、ゲートにVgs=0Vを印加した状態よりも、n型FETのVthが低下する。

【0037】

図4(b)はp型Vth自己調整FET1のIds−Vgsを示している。Tct=2.77nm、x=1.20、Tox=2.92,N/(Si+O+N)=0、ゲート電極5はp+ポリシリコンである。図4(a)のn型FETと図4(b)のp型FETは、イオン注入条件を除いて同一の製造プロセスで作製される。図中0V stdbyと記載されるIV特性は、Vgs=0Vで長時間保持しチャージトラップ膜4を中性状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。一方、−VDD stdbyと記載されるIV特性は、Vgs=−VDDで長時間保持してチャージトラップ膜4を負の帯電状態にした上で、その帯電状態を変化させないように高速パルスIV測定で取得したものである。−VDDとしてはゲート絶縁膜電界が5.5MV/cmとなるように設定した。図4(b)のグラフから実証されるように、ゲートにVgs<0を印加した状態の方が、ゲートにVgs=0Vを印加した状態よりも、p型FETの|Vth|が低下する。

【0038】

図4(a)と図4(b)の実験結果は、n型FETとp型FETの双方に、同一のブロック絶縁膜3と同一のチャージトラップ膜4とを設けることで、チャージトラップ膜4に両極性トラップが生成されて、いずれのFETでも、Vth自己調整機能を持つことを示している。従って、本実施形態によれば、ブロック絶縁膜3とチャージトラップ膜4に関しては、n型FETとp型FETで、製造プロセスを別個に設けなくて済み、少ない工程数でn型FETとp型FETを作製できる。

【0039】

本実施形態によるn型FETとp型FETでは、ゲート電極5の材料として、それぞれn型とp型のポリシリコンを使用することができる。これは通常のFETと同じゲート電極5の材料であり、材料費を抑制できる。

【0040】

あるいは、ゲート電極5として、金属材料を用いても良い。金属材料を用いたメタルゲートは、ゲート電極5内部には原理的に空乏層が発生しないので、多結晶シリコンゲートの場合のように空乏層によるFETの電流駆動力の低下は起きない。また、本実施形態によるFETにメタルゲートを用いると、チャージトラップ膜4とゲート電極5との界面に空乏層が発生しないため、チャージトラップ膜4とゲート電極5間の電子授受をより高速に行うことができる。空乏層を発生させないためには、ゲート電極5のうち、少なくともチャージトラップ膜4と接する部分を金属材料で形成する必要がある。メタルゲートの金属材料としては、TaC、TaN、TiN、TiCN、TiAlN、W、WN、Moなどのタンタル,チタン,タングステン、モリブデンなどの高融点金属、あるいはこれら金属の炭化物、窒化物、Al化合物を使用することができる。

【0041】

上述したように、本実施形態では、ブロック絶縁膜3とチャージトラップ膜4の膜厚、材料および組成を特定しているが、膜厚、材料および組成は、ゲート電極5の表面から半導体基板側の所定位置をFIB(Focused Ion Beam)によるピックアップ法で切り出し、断面を高分解能透過電子顕微鏡(HRTEM)で撮像するか、若しくはエネルギー分散型X線分析(EDX:Energy Dispersive X-ray Analysis)、若しくは電子エネルギー損失分光法(EELS:Electron Energy-Loss Spectroscopy)で分析すれば、明らかにすることができる。

【0042】

例えば、非特許文献4はMNOS(Metal-Nitride-Oxide-Silicon)メモリを開示している。MNOSメモリは、半導体基板2上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されたチャージトラップ膜4と、チャージトラップ膜4上に形成されたゲート電極5とを備え、チャージトラップ膜4はSiN膜で構成され、その膜厚は最低7nm以上で典型的には20nm程度であり、トンネル絶縁膜はSiO2膜で構成され、その膜厚は典型的には1.8nmである。

【0043】

n型MNOSメモリは、書込時には、ゲートに正の高いバイアスを印加し、チャネルから注入された電子を厚いSiN膜中に捕獲する。この結果Vthが上昇する。書込時の電界は通常10MV/cm以上である。一度捕獲された電子は、ゲートバイアスをオフした際もSiN膜中に保持されるため、高いVthはゲートバイアスをオフにしても維持される。消去時には、基板に高い正のバイアスを印加するか、ゲートに高い負のバイアスを印加し、SiN膜に捕獲された電子をチャネル側へ引き抜く。

【0044】

このように、MNOSメモリは、書込/消去時に、チャネルとSiN膜との間で電子授受を行い、書込み時にはVthを上昇させている。これに対して、本実施形態は、チャネルとチャージトラップ膜4との電子の授受をできるだけ制限するために、チャネルとチャージトラップ膜4の間にブロック絶縁膜3を配置し、かつ、チャージトラップ膜4とゲート電極5との間で電子の授受を行なって、n型FETがオン状態のときにはVthを下げている。このように、MNOSメモリと本実施形態によるFETとは、素子の構造と動作原理がいずれも異なっている。

【0045】

MNOSメモリとして機能するには、書込時に高エネルギー電子を捕獲し且つ捕獲電子がゲート電極5側もしくは半導体側へ放出されることを阻止する必要があり、Tct>14nmが必須条件となる。これに対して、本実施形態によるFETでは、Tct<7nmである。

【0046】

また、MNOSメモリにおけるトンネル絶縁膜の膜厚は、書込時に十分な量の注入電子を確保するために、2nm以下、典型的には1.8nm程度とする必要がある。これは、トンネル絶縁膜の膜厚が2nm以下になると直接トンネル電流が著しく増大するためである。これに対して、本実施形態のFETは、チャネル側から電子を引き込まないため、ブロック酸化膜を薄くする必要は特にない。

【0047】

このように、MNOSメモリは、本実施形態によるFETとは構造も全く異なる上に、動作原理も全く異なり、得られる効果も本実施形態とは当然に異なる。

【0048】

上述したように、第1の実施形態では、ブロック絶縁膜3、チャージトラップ膜4およびゲート電極5を積層してVth自己調整FET1を形成し、チャージトラップ膜4とゲート電極5との間で電子の授受を行い、チャージトラップ膜4とチャネルとの間での電子の授受をブロック絶縁膜3で防止するようにしたため、FETがオン状態のときには駆動力性能が向上するようなVthに変化させ、FETがオフ状態のときには遮断性能が向上するようなVthに変化させることができる。

【0049】

(第2の実施形態)

第2の実施形態は、第1の実施形態で説明したFETをSRAM内の一部のトランジスタに適用するものである。

【0050】

図5は第2の実施形態による半導体装置の回路図であり、より具体的にはSRAMセルの回路図である。

【0051】

図5のSRAMセル10は、第1の電源線VSSおよび第2の電源線VDDの間に直列に接続される第1のn型FET11および第1のp型FET12と、第1の電源線VSSおよび第2の電源線VDDの間に直列に接続される第2のn型FET13および第2のp型FET14と、第1のn型FET11および第1のp型FET12の間の第1の接合部j1と、第2のn型FET13および第2のp型FET14の間の第2の接合部j2と、第2のn型FET13のゲート、第2のp型FET14のゲート、および第1の接合部j1に接続される第1のデータノードn1と、第1のn型FET11のゲート、第1のp型FET12のゲート、および第2の接合部j2に接続される第2のデータノードn2と、第1のデータノードn1および第1のデータ線BLの間に接続される第3のn型FET15と、第2のデータノードn2および第2のデータ線BLBの間に接続される第4のn型FET16と、を備えている。

【0052】

このように、図5のSRAMセル10は、6個のFET11〜16からなり、そのうちの4個のFET11〜14はフリップフロップ(FF)を構成している。より詳細には、SRAMセル10内のフリップフロップは、2個のn型FET11,13からなるプルダウントランジスタPDと、2個のp型FET12,14からなるプルアップトランジスタPUとを有する。

【0053】

SRAMセル10内のフリップフロップ以外の2個のFET15,16は、トランスファゲートTGを構成している。

【0054】

本実施形態では、2個のプルダウントランジスタPDを、図1と同一の構造、材料、組成範囲および膜厚範囲を持つVth自己調整FET1で構成することにより、SRAMのデータ保持特性と読出し特性を共に改善することができる。

【0055】

2個のプルダウントランジスタPDは、SRAMセル10の保持データの論理に応じて、相補的にオン状態もしくはオフ状態となる。SRAMセル10内の第1および第2のデータノードn1,n2に保持されるデータの安定性は、オフ状態のプルダウントランジスタPDのVthが高いほうが高くなる。

【0056】

一方、SRAMの読み出し速度は、オン状態のプルダウントランジスタPDのVthが低い方が速くなる。SRAMセル10内のプルダウントランジスタPDをVth自己調整FET1で構成すると、保持データの論理に応じてプルダウントランジスタPDのVthが動的に変化する。このため、保持データの論理に関係なく、常にオフ状態のPDのVthが高く、オン状態のPDのVthが低いSRAMセル10を実現でき、SRAMのデータ保持特性と読み出し特性が共に改善されうる。

【0057】

SRAMセル10内の2個のプルダウントランジスタPDだけでなく、2個のトランスファゲートTGも、図1と同一の構造のn型Vth自己調整FET1で構成してもよい。これにより、SRAMのデータ書き込み特性をも同時に改善することができる。

【0058】

書き込み特性の改善には、トランスファゲートTGの駆動力向上が重要である。トランスファゲートTGをVth自己調整FET1で構成すると、トランスファゲートTGのオン状態でのVthが低下するため、駆動力の向上が図れる。

【0059】

また、SRAMセル10内のプルダウントランジスタPDとトランスファゲートTGに加えて、2個のプルアップトランジスタPUも、図1と同一の構造のp型Vth自己調整FET1で構成してもよい。これにより、SRAMのスタティックリーク電流を低減することができる。

【0060】

データ保持状態では、VDDとVSSの間に直列に接続されるn型FETとp型FETは、片方がオン状態、もう片方がオフ状態となる。PUをVth自己調整FET1で構成することにより、オフ状態におけるp型FETのVthを上昇させて遮断性能を向上させることができる。これにより、第1および第2の電源線VDD,VSSとの間を流れるリーク電流を低減することができる。

【0061】

さらにまた、SRAMセル10を構成するすべてのトランジスタPD、PU、TGを図1と同一の構造のVth自己調整FET1で構成してもよい。この場合、各トランジスタのブロック絶縁膜3はすべて同一構造になり、チャージトラップ膜4も同一構造である。したがって、SRAMセル10内の全トランジスタのブロック絶縁膜3を一つの工程で作製でき、同様にチャージトラップ膜4も一つの工程で作製できる。よって、SRAMセル10の製造工程数を大幅に削減でき、製造コストの削減が図れる。

【0062】

この第2の実施形態では、チャージトラップ膜4の膜厚Tctは0.45<Tct<2.45nmの範囲であること、より好ましくは0.72nm<Tct<2.00nmである。以下、これらの数値範囲の根拠について説明する。

【0063】

少なくとも一部のトランジスタを図1のVth自己調整FET1で構成したSRAMセル10において、好ましいVth変調量(ΔVth)は、50mV<ΔVth<200mVの範囲内であり、好ましくは100mV程度である。

【0064】

SRAMを構成するFETのVthのバラツキは典型的にはσVth=50mVである。Vth自己調整機能により有意な効果を得るには、ΔVth>σVth=50mVである必要がある。非特許文献1によれば、Vth自己調整FET1で構成したSRAMにおいて最適なΔVthは100mV程度である。一方ΔVthが200mV以上であると書込特性が劣化する。

【0065】

図6はΔVthとSiNx膜の膜厚Tctとの関係についての実験結果を示すグラフである。図6(a)はx=1.07とx=1.20のSiNx膜を有するn型Vth自己調整FET1について、ΔVthとTctの関係を示すグラフである。図6(b)は、x=1.20のSiNx膜を有するn型Vth自己調整FET(nFET)とp型Vth自己調整FET(pFET)について、ΔVthとTctの関係を示すグラフである。

【0066】

図6(a)のグラフによれば、n型FETでΔVth=50mV,100mV,200mVを与えるSiNx膜厚Tctは、x=1.20の場合はそれぞれTct=0.83nm,1.66nm,2.45nmであり、x=1.07の場合はそれぞれTct=0.45nm,0.90nm、1.80nmである。

【0067】

図6(a)のグラフから、Vth自己調整FET1で構成したSRAMでは、0.45nm<Tct<2.45nmであることが望ましい。さらに最適ΔVthである100mVの±20%を得ようとする場合、0.72nm<Tct<2.00nmであることが望ましいことがわかる。

【0068】

第2の実施形態では、SiONブロック絶縁膜3の膜厚Toxは0.64nm<Tox<2.70nmの範囲であること、より好ましくは0.87nm<Tox<2.70nmの範囲であること、さらにより好ましくは1.09nm<Tox<2.70nmの範囲であることが望ましい。以下、これらの数値範囲の根拠について説明する。

【0069】

図7は、SiONブロック絶縁膜3とSiNxチャージトラップ膜4からなる積層ゲートスタックについて、ゲートリーク電流JgとSiONブロック絶縁膜3の膜厚Toxの関係を示す図である。図7(a)は、SiNxチャージトラップ膜4の膜厚Tctが0.45nmと0.83nmの2つの場合について、Jg−Toxのグラフを示している。図7(b)は、上述した積層ゲートスタックのエネルギーバンド図である。

【0070】

図7(a)では、ゲートリーク電流JgはWKB近似を用い、ΔEc(SiNx)=1.35eV、ΔEc(SiO2)=3.1eVを仮定して計算した。SRAMのゲートリーク電流Jgは10A/cm2以下にする必要がある。図7(a)によれば、Jg=10A/cm2となるには、Tct=0.83nmであればTox=0.87nmとなり、Tct=0.45nmであればTox=1.09nmとなる。従って、0.83nm<ToxであればTctが0.83nmであってもJg<10A/cm2となる。さらに、1.09nm<ToxであればTctが0.45nmであってもJg<10A/cm2となる。

【0071】

第2の実施形態では、プルダウントランジスタPDとトランスファゲートTGのn型FETのボディコンタクト(基板電位)をVSSに、プルアップトランジスタPUのp型FETのボディコンタクトをVDDに接続する。従って、基板とソース、もしくは基板とドレインの間のpn接合は逆方向バイアス条件を満たすことになり、大きなリーク電流が流れることはない。これに対して、上述した非特許文献1では、SRAMセル内のフリップフロップのn型FETのボディコンタクトがVDDに、p型FETのボディコンタクトがVSSに接続されており、基板からソース/ドレイン領域に大きなリーク電流が流れてしまう。

【0072】

また、第2の実施形態では、プルダウントランジスタPDとトランスファゲートTGを構成するn型FETのゲート電極5をn型ポリシリコン膜とし、プルアップトランジスタPUのp型FETのゲート電極5をp型ポリシリコン膜とすることを想定しており、ゲート電極5の材料に関しては通常のSRAMセル10と同じである。第1の実施形態で既に説明したように、ゲート電極5をポリシリコン膜で形成しても、図1のVth自己調整FET1を作製できる。したがって、第2の実施形態によるSRAMセル10は安価な材料で作製でき、材料費を含めた製造コストを抑制できる。

【0073】

ただし、ゲート電極5の材料は、必ずしもポリシリコンには限定されない。例えば、プルダウントランジスタPDとトランスファゲートTGのn型FETおよびプルアップトランジスタPUのp型FETのゲート電極5を金属材料で形成してもよい。この場合、TaC、TaN、TiN、TiCN、TiAlN、W、WN、Moなどのチタン,モリブデン,タングステン、タンタルなどの高融点金属およびその炭化物、窒化物からなるメタルゲートを使用し得る。

【0074】

このように、第2の実施形態では、SRAMセル10を構成する6個のトランジスタのうち、少なくとも一部のトランジスタを図1のVth自己調整FET1で構成するため、SRAMのデータ保持特性、データ読出し特性、およびデータ書き込み特性などを必要に応じて向上でき、また、リーク電流を低減することも可能である。

【0075】

(第3の実施形態)

第3の実施形態は、図1のVth自己調整FET1を用いてプログラマブルスイッチを実現するものである。プログラマブルスイッチとは、スイッチとして機能するFETのゲートにメモリを接続して、メモリの保持データによって、FETのオン/オフ状態を切替制御するものである。典型的なFPGA(Field Programmable Gate Array)はロジックエレメントとプログラマブルスイッチのアレーで構成されている。各プログラマブルスイッチはロジックエレメントを選択的に接続する役割を担う。

【0076】

図8は第3の実施形態による半導体装置の回路図である。図8の半導体装置はプログラマブルスイッチ20であり、オン/オフ切替用のn型FET(以下、スイッチFET)17と、このスイッチFET17のゲートに印加すべきデータを記憶するSRAMセル10aとを備えている。

【0077】

スイッチFET17は、SRAMセル10a内に保持されたデータの論理によって、オンまたはオフする。SRAMセル10aの保持データは書換え可能であるため、図8の回路はプログラマブルスイッチ20として機能する。

【0078】

図8のSRAMセル10aは、回路構成としては図5と同じであるが、SRAMセル10a内のトランジスタをVth自己調整FET1で構成する必要はなく、通常のSRAMセル10aでよい。

【0079】

図8のスイッチFET17は、図1のVth自己調整FET1であり、このFET内のチャージトラップ膜4とブロック絶縁膜3の材料、組成および膜厚は第1の実施形態で説明したものと同じである。スイッチFET17を図1のVth自己調整FET1にすることで、SRAMセル10aにオン状態がプログラムされている場合はスイッチFET17のVthを自動的に低下させ、オフ状態がプログラムされている場合はスイッチFET17のVthを自動的に高くすることができる。この結果、オン状態にプログラムされたスイッチFET17の駆動力性能は向上し、オフ状態にプログラムされたスイッチFET17の遮断性能も向上する。

【0080】

なお、第2の実施形態と同様に、図8のSRAMセル10a内の少なくとも一部のトランジスタを、図1のVth自己調整FET1にしてもよい。この場合、第2の実施形態の効果と第3の実施形態の効果を併せ持つプログラマブルスイッチ20を実現できる。

【0081】

このように、第3の実施形態では、SRAMセル10aとスイッチFET17を用いたプログラマブルスイッチ20を作製する際に、スイッチFET17の駆動力性能と遮断性能を向上できる。

【0082】

(第4の実施形態)

第4の実施形態は、SRAMではなく、不揮発性メモリを用いてプログラマブルスイッチ20を実現するものである。

【0083】

図9は第4の実施形態による半導体装置の回路図であり、2個の不揮発性メモリセル(第1および第2の不揮発FET)21,22と、図1のVth自己調整FET1で構成されるn型FET(以下、スイッチFET)23とで、プログラマブルスイッチ20aを構成している。

【0084】

図9の回路において、一方の不揮発性メモリセル21は第1のデータ線BLとデータノードn1との間に接続され、他方の不揮発性メモリセル22は第2のデータ線BLBとデータノードn1との間に接続されている。データノードn1は、スイッチFET23のゲートに接続されている。

【0085】

図9のプログラマブルスイッチ20aにおいても、スイッチFET23をVth自己調整FET1で構成することで、スイッチFET23の駆動力性能と遮断性能を共に改善することができる。

【0086】

また、スイッチFET23をVth自己調整FET1で構成することで、スイッチFET23の高耐圧性能をも改善することができる。例えば、不揮発性メモリセル21,22がFN(Fowler-Nordheim)型書込方式を採用する場合、スイッチFET23は高耐圧でなければならない。これは、FN型書込方式で選択書込を行う場合は、非選択セルのスイッチFET23のゲートに高い電圧が印加されるためである。高いバイアスによる破壊を回避するため通常はスイッチFET23のゲート絶縁膜の膜厚を厚くする必要がある。しかし、この場合スイッチFET23の駆動力性能が劣化する。スイッチFET23をVth自己調整FET1で構成することにより、ゲート絶縁膜の膜厚を厚くした場合と同等の高耐圧性能を維持したまま駆動力性能を改善できる。

【0087】

第4の実施形態では、不揮発メモリとして、例えばSONOS型不揮発FETを用いることができる。SONOS型不揮発FETは、半導体基板2上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されたチャージトラップ膜と、チャージトラップ膜上に形成されたブロック絶縁膜と、ブロック絶縁膜上に形成されたキャップ膜と、キャップ膜上に形成されたゲート電極とを備えている。

【0088】

SONOS型不揮発FETのトンネル膜としては、例えばSiO2/SiNx/SiO2からなるONOスタックを使用することができる。チャージトラップ膜としては、例えばSiリッチ組成のSiNx膜を使用することができる。ブロック絶縁膜としては、例えばSiO2/SiNx/SiO2からなるONOスタックを使用することができる。また、ブロック絶縁膜としては、例えばAl2O3膜を使用することもできる。キャップ膜としては、SiN膜を使用することができる。ゲート電極としては、n型ポリシリコンを使用することができる。

【0089】

なお、第4の実施形態における不揮発性メモリの他の具体例としては、FG(Floating Gate)型の不揮発FETを用いてもよい。

【0090】

このように、第4の実施形態では、不揮発性メモリに記憶されたオン/オフ情報に基づいて切替動作を行なうプログラマブルスイッチ20a内のスイッチFET23を図1のVth自己調整FET1で構成するため、不揮発性メモリへの書き込み時に印加される高電圧にも耐えうる高耐圧性能をスイッチFET23に持たせることができ、かつスイッチFET23の駆動力性能と遮断性能を向上できる。

【0091】

(第5の実施形態)

第5の実施形態は、図1のVth自己調整FET1をパワーゲーティング回路に適用したものである。

【0092】

図10および図11は第5の実施形態による半導体装置の回路図であり、パワーゲーティング回路30の回路構成を示している。

【0093】

パワーゲーティング回路30は、LSIの消費電力を抑制するために用いられる。より具体的には、LSI内部の論理回路部を、独立した電源制御が可能な複数のサブ論理回路ブロック24に分割し、各サブ論理回路ブロック24に電源電圧を供給するか否かをパワーゲーティング回路30で制御することにより、LSIの消費電力を抑制する。

【0094】

図10および図11に示すように、各サブ論理回路ブロック24は仮想電源線Virtual-VDD(仮想接地線Virtual-VSS)に接続されている。各サブ論理回路ブロック24ごとにパワーゲーティング回路30が設けられ、パワーゲーティング回路30は、LSIの電源線VDD(接地線VSS)と仮想電源線Virtual-VDD(仮想接地線Virtual-VSS)との間に接続されている。

【0095】

図10のパワーゲーティング回路30は、LSIの電源線VDDの電圧を仮想電源線VDDに供給するか否かを切り替えるp型FET(以下、電源スイッチFET)25を有し、この電源スイッチFET25はイネーブル信号ENによりオン/オフ制御される。また、図11のパワーゲーティング回路30は、LSIの接地線VSSと仮想接地線VSSとの間にn型FET(電源スイッチFET)26を接続している。

【0096】

図10および図11に示す電源スイッチFET25,26は、図1のVth自己調整FET1で構成されており、このFET内のチャージトラップ膜4とブロック絶縁膜3の材料、組成および膜厚は第1の実施形態で説明したものと同じである。

【0097】

電源スイッチFET25,26のオフ時のリーク電流Ioffがアイドル時のリーク電流を決めるため、電源スイッチFET25,26には極めて高い遮断性能、即ち極めて低いIoff性能が必要である。一方、電源スイッチFET25,26のオン時の抵抗が電源線VDDと擬似電源線Virtual-VDD間、あるいは擬似接地線Virtual-Vssと接地線Vss間の電圧降下量を決めるため、電源スイッチFET25,26のオン抵抗は極めて低く、即ち極めて高いIon性能が必要である。

【0098】

本実施形態によるパワーゲーティング回路30では、電源スイッチFET25,26を図1のVth自己調整FET1で構成するため、電源スイッチFET25,26のオン時にはオンし易くして、オフ時には遮断性をよくすることができ、上述したIon性能とIoff性能を共に向上できる。

【0099】

これに対して、特許文献2には、電源スイッチFETを高Vthトランジスタで構成することによりIoff性能を向上させる手法が開示されている。ところが、電源スイッチFET25,26には極めて低いIoff性能のみならず、極めて高いIon性能をも必要とされるが、特許文献2にはIon性能の向上は念頭に置いておらず、Ion性能を向上させる手法も開示されていない。

【0100】

このように、第5の実施形態では、パワーゲーティング回路30内の電源スイッチFET25,26を図1のVth自己調整FET1で構成するため、Ion性能とIoff性能を共に向上できる。

【0101】

ところで、電源スイッチFET25,26をVth自己調整FET1で構成すると、通常のFETと比べて、オン/オフの切替に時間がかかる。これは、チャージトラップ膜4とゲート電極5との間で主に電子の授受を行なうためである。ところが、パワーゲーティング回路30の場合、対応するサブ論理回路ブロック24の電源状態を頻繁に切り替えることはなく、逆に高速に電源状態を切り替えると、サブ論理回路ブロック24内に突入電流が流れるという問題がある。本実施形態のように、電源スイッチFET25,26をVth自己調整FET1で構成すると、電源状態を切り替えるのに時間はかかるものの、サブ論理回路ブロック24内に突入電流が流れるおそれはなく、各サブ論理回路ブロック24をより安定に動作させることができる。

【0102】

本発明の態様は、上述した個々の実施形態に限定されるものではなく、当業者が想定しうる種々の変形も含むものであり、本発明の効果も上述した内容に限定されない。すなわち、特許請求の範囲に規定された内容およびその均等物から導き出される本発明の概念的な思想と趣旨を逸脱しない範囲で種々の追加、変更および部分的削除が可能である。

【符号の説明】

【0103】

1 Vth自己調整FET、3 ブロック絶縁膜、4 チャージトラップ膜、5 ゲート電極、10 SRAMセル、11,13 プルダウントランジスタPD、12,14 プルアップトランジスタPU、15,16 トランスファゲートTG、20,20a プログラマブルスイッチ、30 パワーゲーティング回路

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、

前記絶縁膜の上方に配置されるゲート電極と、

前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有することを特徴とする半導体装置。

【請求項2】

前記チャージトラップ膜は、SiNx膜であり、前記xは、Siに対するNのモル比であって、0.67<x<1.33の範囲内の値であり、

前記チャージトラップ膜の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Toxの範囲内の値であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板上に形成される絶縁膜と、

前記絶縁膜上に形成されるチャージトラップ膜と、

前記チャージトラップ膜上に接触するように配置されるゲート電極と、を有し、

前記チャージトラップ膜は、SiNx膜であり、前記xは、Siに対するNのモル比であって、0.67<x<1.33の範囲内の値であり、

前記チャージトラップ膜の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Toxの範囲内の値であることを特徴とする半導体装置。

【請求項4】

前記チャージトラップ膜は、

前記半導体素子がn型FETの場合には、前記半導体素子がオフ状態のときに、前記ゲート電極内の電子を取り込んで中性状態となって前記閾値電圧を第1の電圧レベルに設定し、前記半導体素子がオン状態のときに、電子を前記ゲート電極に与えて前記閾値電圧を前記第1の電圧レベルよりも低い第2の電圧レベルに設定し、

前記半導体素子がp型FETの場合には、前記半導体素子がオフ状態のときに、前記ゲート電極に余分の電子を与えて中性状態となって前記閾値電圧の絶対値を第3の電圧レベルに設定し、前記半導体素子がオン状態のときに、前記ゲート電極内の電子を取り込んで前記閾値電圧の絶対値を前記第3の電圧レベルよりも低い第4の電圧レベルに設定することを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

【請求項5】

前記絶縁膜の膜厚Toxは、0.64nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記ゲート電極は、前記半導体素子がn型のときはn型ポリシリコン膜であり、前記半導体素子がp型のときはp型ポリシリコン膜であることを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

【請求項7】

前記ゲート電極と前記チャージトラップ膜とは接触しており、

前記ゲート電極中の前記チャージトラップ膜との接触界面の材料は、TaC、TaN、TiN、TiCN、TiAlN、W、WNおよびMoの少なくとも一つを含むことを特徴とする請求項1乃至6のいずれかに記載の半導体装置。

【請求項8】

第1の電源線および第2の電源線の間に直列に接続される第1のn型FETおよび第1のp型FETと、

前記第1の電源線および前記第2の電源線の間に直列に接続される第2のn型FETおよび第2のp型FETと、

前記第1のn型FETおよび前記第1のp型FETの間の第1の接合部と、

前記第2のn型FETおよび前記第2のp型FETの間の第2の接合部と、

前記第2のn型FETのゲート、前記第2のp型FETのゲート、および前記第1の接合部に接続される第1のデータノードと、

前記第1のn型FETのゲート、前記第1のp型FETのゲート、および前記第2の接合部に接続される第2のデータノードと、

前記第1のデータノードおよび第1のデータ線の間に接続される第3のn型FETと、

前記第2のデータノードおよび第2のデータ線の間に接続される第4のn型FETと、を備え、

前記第1のn型FETおよび前記第2のn型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第1のn型FETおよび前記第2のn型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項9】

前記第1のn型FETおよび前記第2のn型FETのそれぞれが有する前記チャージトラップ膜の膜厚Tctは、0.45nm<Tct<2.45nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記チャージトラップ膜の膜厚Tctは、0.72nm<Tct<2.00nmの範囲内の値であることを特徴とする請求項9に記載の半導体装置。

【請求項11】

前記絶縁膜の膜厚Toxは、0.87nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項9または10に記載の半導体装置。

【請求項12】

前記絶縁膜の膜厚Toxは、1.09nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項11に記載の半導体装置。

【請求項13】

前記第3のn型FETおよび前記第4のn型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第3のn型FETおよび前記第4のn型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項8乃至12のいずれかに記載の半導体装置。

【請求項14】

前記第1のp型FETおよび前記第2のp型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第1のp型FETおよび前記第2のp型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項8乃至13のいずれかに記載の半導体装置。

【請求項15】

前記第1および第2のn型FETの基板電位は接地電位に設定され、前記第1および第2のp型FETの基板電位は電源電位に設定されることを特徴とする請求項8乃至14のいずれかに記載の半導体素子。

【請求項16】

第1の電源線および第2の電源線の間に直列に接続される第1のn型FETおよび第1のp型FETと、

前記第1の電源線および前記第2の電源線の間に直列に接続される第2のn型FETおよび第2のp型FETと、

前記第1のn型FETおよび前記第1のp型FETの間の第1の接合部と、

前記第2のn型FETおよび前記第2のp型FETの間の第2の接合部と、

前記第2のn型FETのゲート、前記第2のp型FETのゲート、および前記第1の接合部に接続される第1のデータノードと、

前記第1のn型FETのゲート、前記第1のp型FETのゲート、および前記第2の接合部に接続される第2のデータノードと、

前記第1のデータノードおよび第1のデータ線の間に接続される第3のn型FETと、

前記第2のデータノードおよび第2のデータ線の間に接続される第4のn型FETと、を備え、

ゲートが前記第1のデータノードに接続される第5のn型FETを備え、

前記第5のn型FETは、前記半導体素子と同一の層構造を有し、前記第5のn型FETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項17】

第1のデータ線および第2のデータ線の間に直列に接続され、対応するデータ線から与えられたデータビットを不揮発で記憶可能な第1の不揮発FETおよび第2の不揮発FETと、

前記第1の不揮発FETおよび前記第2の不揮発FETの間の接合部と、

ゲートが前記接合部に接続され、前記第1および第2の不揮発FETに記憶されたデータに応じてオンまたはオフするスイッチFETと、を備え、

前記スイッチFETは、前記半導体素子と同一の層構造を有し、前記スイッチFETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項18】

複数のFETからなる論理回路ブロックと、

前記論理回路ブロックの基準電源端子に接続される擬似電源線と、

前記擬似電源線を所定の基準電圧に設定するか否かを切り替える電源スイッチFETと、を備え、

前記電源スイッチFETは、前記半導体素子と同一の層構造を有し、前記電源スイッチFETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項1】

半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、

前記絶縁膜の上方に配置されるゲート電極と、

前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有することを特徴とする半導体装置。

【請求項2】

前記チャージトラップ膜は、SiNx膜であり、前記xは、Siに対するNのモル比であって、0.67<x<1.33の範囲内の値であり、

前記チャージトラップ膜の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Toxの範囲内の値であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体基板と、

前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備え、

前記半導体素子は、

前記半導体基板上に形成される絶縁膜と、

前記絶縁膜上に形成されるチャージトラップ膜と、

前記チャージトラップ膜上に接触するように配置されるゲート電極と、を有し、

前記チャージトラップ膜は、SiNx膜であり、前記xは、Siに対するNのモル比であって、0.67<x<1.33の範囲内の値であり、

前記チャージトラップ膜の膜厚Tctは、0.34nm<Tct<7nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Toxの範囲内の値であることを特徴とする半導体装置。

【請求項4】

前記チャージトラップ膜は、

前記半導体素子がn型FETの場合には、前記半導体素子がオフ状態のときに、前記ゲート電極内の電子を取り込んで中性状態となって前記閾値電圧を第1の電圧レベルに設定し、前記半導体素子がオン状態のときに、電子を前記ゲート電極に与えて前記閾値電圧を前記第1の電圧レベルよりも低い第2の電圧レベルに設定し、

前記半導体素子がp型FETの場合には、前記半導体素子がオフ状態のときに、前記ゲート電極に余分の電子を与えて中性状態となって前記閾値電圧の絶対値を第3の電圧レベルに設定し、前記半導体素子がオン状態のときに、前記ゲート電極内の電子を取り込んで前記閾値電圧の絶対値を前記第3の電圧レベルよりも低い第4の電圧レベルに設定することを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

【請求項5】

前記絶縁膜の膜厚Toxは、0.64nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記ゲート電極は、前記半導体素子がn型のときはn型ポリシリコン膜であり、前記半導体素子がp型のときはp型ポリシリコン膜であることを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

【請求項7】

前記ゲート電極と前記チャージトラップ膜とは接触しており、

前記ゲート電極中の前記チャージトラップ膜との接触界面の材料は、TaC、TaN、TiN、TiCN、TiAlN、W、WNおよびMoの少なくとも一つを含むことを特徴とする請求項1乃至6のいずれかに記載の半導体装置。

【請求項8】

第1の電源線および第2の電源線の間に直列に接続される第1のn型FETおよび第1のp型FETと、

前記第1の電源線および前記第2の電源線の間に直列に接続される第2のn型FETおよび第2のp型FETと、

前記第1のn型FETおよび前記第1のp型FETの間の第1の接合部と、

前記第2のn型FETおよび前記第2のp型FETの間の第2の接合部と、

前記第2のn型FETのゲート、前記第2のp型FETのゲート、および前記第1の接合部に接続される第1のデータノードと、

前記第1のn型FETのゲート、前記第1のp型FETのゲート、および前記第2の接合部に接続される第2のデータノードと、

前記第1のデータノードおよび第1のデータ線の間に接続される第3のn型FETと、

前記第2のデータノードおよび第2のデータ線の間に接続される第4のn型FETと、を備え、

前記第1のn型FETおよび前記第2のn型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第1のn型FETおよび前記第2のn型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項9】

前記第1のn型FETおよび前記第2のn型FETのそれぞれが有する前記チャージトラップ膜の膜厚Tctは、0.45nm<Tct<2.45nmの範囲内の値であり、

前記絶縁膜は、SiON膜であり、このSiON膜内のSi、OおよびNの合計に対するNのモル比{N/(Si+O+N)}は、0≦{N/(Si+O+N)}<0.35の範囲内の値であり、

前記絶縁膜の膜厚Toxは、0.64nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項8に記載の半導体装置。

【請求項10】

前記チャージトラップ膜の膜厚Tctは、0.72nm<Tct<2.00nmの範囲内の値であることを特徴とする請求項9に記載の半導体装置。

【請求項11】

前記絶縁膜の膜厚Toxは、0.87nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項9または10に記載の半導体装置。

【請求項12】

前記絶縁膜の膜厚Toxは、1.09nm<Tox<2.70nmの範囲内の値であることを特徴とする請求項11に記載の半導体装置。

【請求項13】

前記第3のn型FETおよび前記第4のn型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第3のn型FETおよび前記第4のn型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項8乃至12のいずれかに記載の半導体装置。

【請求項14】

前記第1のp型FETおよび前記第2のp型FETはそれぞれ、前記半導体素子と同一の層構造を有し、前記第1のp型FETおよび前記第2のp型FETのそれぞれにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項8乃至13のいずれかに記載の半導体装置。

【請求項15】

前記第1および第2のn型FETの基板電位は接地電位に設定され、前記第1および第2のp型FETの基板電位は電源電位に設定されることを特徴とする請求項8乃至14のいずれかに記載の半導体素子。

【請求項16】

第1の電源線および第2の電源線の間に直列に接続される第1のn型FETおよび第1のp型FETと、

前記第1の電源線および前記第2の電源線の間に直列に接続される第2のn型FETおよび第2のp型FETと、

前記第1のn型FETおよび前記第1のp型FETの間の第1の接合部と、

前記第2のn型FETおよび前記第2のp型FETの間の第2の接合部と、

前記第2のn型FETのゲート、前記第2のp型FETのゲート、および前記第1の接合部に接続される第1のデータノードと、

前記第1のn型FETのゲート、前記第1のp型FETのゲート、および前記第2の接合部に接続される第2のデータノードと、

前記第1のデータノードおよび第1のデータ線の間に接続される第3のn型FETと、

前記第2のデータノードおよび第2のデータ線の間に接続される第4のn型FETと、を備え、

ゲートが前記第1のデータノードに接続される第5のn型FETを備え、

前記第5のn型FETは、前記半導体素子と同一の層構造を有し、前記第5のn型FETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項17】

第1のデータ線および第2のデータ線の間に直列に接続され、対応するデータ線から与えられたデータビットを不揮発で記憶可能な第1の不揮発FETおよび第2の不揮発FETと、

前記第1の不揮発FETおよび前記第2の不揮発FETの間の接合部と、

ゲートが前記接合部に接続され、前記第1および第2の不揮発FETに記憶されたデータに応じてオンまたはオフするスイッチFETと、を備え、

前記スイッチFETは、前記半導体素子と同一の層構造を有し、前記スイッチFETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【請求項18】

複数のFETからなる論理回路ブロックと、

前記論理回路ブロックの基準電源端子に接続される擬似電源線と、

前記擬似電源線を所定の基準電圧に設定するか否かを切り替える電源スイッチFETと、を備え、

前記電源スイッチFETは、前記半導体素子と同一の層構造を有し、前記電源スイッチFETにおける前記チャージトラップ膜および前記絶縁膜の材料、組成範囲および膜厚範囲は、前記半導体素子と同一であることを特徴とする請求項1乃至7のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−8801(P2013−8801A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2011−139794(P2011−139794)

【出願日】平成23年6月23日(2011.6.23)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成23年6月23日(2011.6.23)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]