半導体装置

【課題】トンネルトランジスタの高電圧での駆動力を向上させることが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層を備える。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルトランジスタが精力的に研究されている。トンネルトランジスタは、そのSファクターの値が低く、低電圧動作に適しているが、高電圧での駆動力向上が課題となっている。一方、MOSFETは、高電圧での駆動力は大きいが、そのSファクターの値が高く、低電圧動作には不向きである。そこで、低電圧動作にも高電圧動作にも適したトランジスタを実現すべく、トンネルトランジスタの高電圧での駆動力向上が求められている。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Chenming Hu et al. "Green Transistor - A VDD Scaling Path for Future Low Power ICs" VLSI-TSA2008

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルトランジスタの高電圧での駆動力を向上させることが可能な半導体装置を提供する。

【課題を解決するための手段】

【0005】

一の実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層を備える。

【図面の簡単な説明】

【0006】

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態のトンネルトランジスタの動作原理を示した断面図である。

【図3】第1実施形態のトンネルトランジスタの動作特性を示したグラフである。

【図4】第2実施形態の半導体装置の製造方法を示す断面図(1/3)である。

【図5】第2実施形態の半導体装置の製造方法を示す断面図(2/3)である。

【図6】第2実施形態の半導体装置の製造方法を示す断面図(3/3)である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

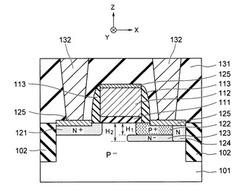

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルトランジスタの構成要素として、基板101と、ゲート絶縁膜111と、ゲート電極112と、側壁絶縁膜113と、ドレイン領域121と、ソース領域122と、第1の拡散層123と、第2の拡散層124と、シリサイド層125などを備えている。

【0010】

基板101は例えば、シリコン基板などの半導体基板である。図1には、基板101の主面に平行で、互いに垂直なX方向およびY方向と、基板101の主面に垂直なZ方向が示されている。本実施形態では、基板101は、低濃度のP型不純物を含むP−型基板である。なお、基板101は、低濃度のN型不純物を含むN−型基板でもよい。また、基板101は、SOI(Semiconductor On Insulator)基板でもよい。図1にはさらに、基板101内に形成された素子分離絶縁膜102が示されている。

【0011】

ゲート絶縁膜111は、基板101上に形成されている。また、ゲート電極112は、基板101上にゲート絶縁膜111を介して形成されている。さらに、側壁絶縁膜113は、ゲート電極112の側面に形成されている。ゲート絶縁膜111は、例えばシリコン酸化膜である。また、ゲート電極112は、例えばポリシリコン層である。さらに、側壁絶縁膜113は、例えばシリコン酸化膜またはシリコン窒化膜である。

【0012】

ドレイン領域121とソース領域122は、基板101内に、ゲート電極112を挟むように形成されている。本実施形態では、ドレイン領域121はN+型領域であり、ソース領域122はP+型領域である。ドレイン領域121とソース領域122は、それぞれ第1の主端子領域、第2の主端子領域の例である。また、N導電型とP導電型は、それぞれ第1導電型と第2導電型の例である。

【0013】

第1の拡散層123は、基板101内において、ソース領域122の下面に接する位置に形成されており、かつ、ドレイン領域121と離間された位置に形成されている。本実施形態では、第1の拡散層123は、N−型拡散層であり、ソース領域122の導電型と逆導電型となっている。

【0014】

符号H1は、基板101の表面から、ソース領域122と第1の拡散層123とのPN接合面までの深さを示す。また、符号H2は、基板101の表面から、第1の拡散層123の下面までの深さを示す。本実施形態では、深さH1は、例えば10〜100nmに設定されている。また、深さH2は、例えば20〜150nmに設定されている。本実施形態では、第1の拡散層123の厚さは、ソース領域122の厚さ以下に設定されており、よって、深さH2は、深さH1の2倍以下に設定されている。

【0015】

また、本実施形態では、第1の拡散層123のドレイン領域121側の側面が、ソース領域122のドレイン領域121側の側面よりも突出している。この第1の拡散層123の突出部分の作用については、後述する。本実施形態では、この突出部分の先端が、ドレイン領域121とソース領域122との間の中間地点よりも、ソース領域122側に位置している。

【0016】

第2の拡散層124は、基板101内において、ソース領域122の側面と第1の拡散層123の側面とに接する位置に形成されている。本実施形態では、第2の拡散層124は、N型拡散層であり、ソース領域122の導電型と逆導電型となっている。第2の拡散層124は、ソース領域122と第1の拡散層123の、ドレイン領域121とは逆側の側面に接している。本実施形態では、第2の拡散層124のX方向の幅は、ソース領域122や第1の拡散層123のX方向の幅よりも短く設定されている。

【0017】

なお、本実施形態では、第2の拡散層124の下面は、第1の拡散層123の下面よりも下方に位置していても上方に位置していてもよい。すなわち、第2の拡散層124は、第1の拡散層123を貫通していてもよいし、第1の拡散層123を貫通していなくてもよい。

【0018】

シリサイド層125は、ゲート電極112の上面に形成されている。また、シリサイド層125は、ドレイン領域121の上面に形成されている。さらに、シリサイド層125は、ソース領域122の上面と第2の拡散層124の上面に連続して形成されている。本実施形態のシリサイド層125は、Ti(チタン)、Co(コバルト)、Ni(ニッケル)、Pt(白金)の少なくともいずれかを含有している。

【0019】

図1の半導体装置はさらに、基板101上にトンネルトランジスタを覆うように形成された層間絶縁膜131と、層間絶縁膜131内に形成されたコンタクトプラグ132とを備えている。

【0020】

図1に示す2本のコンタクトプラグ132のうち、一方は、ドレイン領域121上のシリサイド層125上に形成されており、他方は、ソース領域122および第2の拡散層124上のシリサイド層125上に形成されている。前者のコンタクトプラグ132は、ドレイン領域121に電圧を印加するために使用され、後者のコンタクトプラグ132は、ソース領域122と第2の拡散層124に共通の電圧(本実施形態ではグラウンド電圧)を印加するために使用される。後者の共通の電圧は、第2の拡散層124を介して第1の拡散層123にも印加される。

【0021】

なお、本実施形態では、ドレイン領域121、ソース領域122、第1、第2の拡散層123、124の不純物濃度は、例えば次のように設定される。

【0022】

ドレイン領域121の不純物濃度と、ソース領域122の不純物濃度は、ほぼ同じ値に設定される。第1の拡散層123の不純物濃度は、ドレイン領域121やソース領域122の不純物濃度よりも低く設定される。第2の拡散層124の不純物濃度は、ドレイン領域121やソース領域122の不純物濃度よりも高く設定される。

【0023】

(1)トンネルトランジスタの動作

次に、図2と図3を参照し、第1実施形態のトンネルトランジスタの動作について説明する。

【0024】

図2は、第1実施形態のトンネルトランジスタの動作原理を示した断面図である。

【0025】

ドレイン領域121に正の電圧を印加した状態で、ゲート電極112に正の電圧を印加すると、図2(a)に示すように、ソース領域122とドレイン領域121との間に反転層201が生じる。本実施形態では、基板101がP−型基板であるため、反転層201はN型層である。そして、ソース領域122内の電子が、トンネル現象により反転層201内に流れ込み、その結果、チャネル領域にトンネル電流が流れる。こうして、本実施形態のトランジスタは、トンネルトランジスタとして機能する。

【0026】

ゲート電圧を増大させると、図2(b)に示すように、反転層201が下方へと広がっていく。よって、ゲート電圧を増大させると、トンネル電流が増加する。しかしながら、基板101内のポテンシャルは、基板101の表面からの距離の2乗に反比例して減少するため、ゲート電圧の増大に応じて、トンネル電流の増加率は減少していく。よって、トンネルトランジスタの高電圧での駆動力は、MOSFETに比べて小さくなる。

【0027】

しかしながら、本実施形態では、ゲート電圧を増大させると、図2(c)に示すように、反転層201がやがて第1の拡散層123に到達する。その結果、本実施形態のトランジスタは、第1の拡散層123をソース領域とするMOSFETのように動作する。これにより、本実施形態のトランジスタは、高電圧での駆動力が高くなる。

【0028】

このように、本実施形態では、ソース領域122の下部に第1の拡散層123を設けることで、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0029】

図3は、第1実施形態のトンネルトランジスタの動作特性を示したグラフである。

【0030】

図3において、横軸はゲート電圧を示し、縦軸はドレイン電流を示す。図3は、本実施形態のトンネルトランジスタに関するシミュレーション結果を示す。

【0031】

曲線C1は、ドレイン領域121とソース領域122によるトンネルトランジスタの動作特性を示す。また、曲線C2は、ドレイン領域121と第1の拡散層123によるMOSFETの動作特性を示す。

【0032】

図3に示すように、ゲート電圧が低いときには、トンネルトランジスタの駆動力が支配的である。一方、ゲート電圧が高くなると、MOSFETの駆動力が支配的となる。よって、本実施形態によれば、高電圧においてトンネルトランジスタがMOSFETのように動作することで、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0033】

(2)第1実施形態の半導体装置の作用効果

次に、再び図1を参照し、第1実施形態の半導体装置の作用効果について説明する。

【0034】

以上のように、本実施形態では、トンネルトランジスタのソース領域122の下部に、ソース領域122の導電型と逆導電型の第1の拡散層123を形成する。よって、本実施形態によれば、トンネルトランジスタを高電圧においてMOSFETのように動作させ、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0035】

また、本実施形態では、ソース領域122と第1の拡散層123の側方に、ソース領域122の導電型と逆導電型の第2の拡散層124を形成する。よって、第1の拡散層123に対し、コンタクトプラグ132から第2の拡散層124を介して電圧を印加することが可能となる。よって、本実施形態によれば、第1の拡散層123を、MOSFETのソース領域のように機能させることが可能となる。

【0036】

また、本実施形態では、ソース領域122と第2の拡散層124は、共通のコンタクトプラグ132に電気的に接続されている。よって、本実施形態によれば、ソース領域122に印加する電圧と、第1、第2の拡散層123、124に印加する電圧を、共通化することが可能となる。

【0037】

また、本実施形態では、シリサイド層125が、ソース領域122の上面と第2の拡散層124の上面に連続して形成されている。よって、本実施形態によれば、コンタクトプラグ132の設置位置がシリサイド層125上でずれてしまっても、コンタクトプラグ132をソース領域122と第2の拡散層124に電気的に接続することが可能となる。よって、本実施形態によれば、コンタクトホールを形成しやすくなる。

【0038】

また、本実施形態では、第1の拡散層123のドレイン領域121側の側面が、ソース領域122のドレイン領域121側の側面よりも突出している。このような構造には、反転層201が下方に広がった際、反転層201が第1の拡散層123に接しやすくなるという利点がある。

【0039】

また、本実施形態では、基板101の表面から、ソース領域122と第1の拡散層123とのPN接合面までの深さH1が、10〜100nmに設定されている。深さH1が小さすぎると、低過ぎるゲート電圧で反転層201が第1の拡散層123に到達してしまうという問題がある。また、深さH1が大きすぎると、十分にゲート電圧を高くしても反転層201が第1の拡散層123に到達しないという問題がある。よって、本実施形態では、これらの問題を避けるため、深さH1を10〜100nmに設定している。ただし、深さH1の上限と下限は、半導体装置やトンネルトランジスタの構造に応じて、違う値に設定してもよい。

【0040】

また、本実施形態では、基板101の表面から、第1の拡散層123の下面までの深さH2が、20〜150nmに設定されている。深さH2が小さすぎると、例えば、反転層201と第1の拡散層123との接触面積が小さすぎるという問題がある。また、深さH2が大きすぎると、例えば、ドレイン領域121の下面付近と第1の拡散層123の先端付近との間にチャネルが生じるおそれがあるという問題がある。よって、本実施形態では、これらの問題を避けるため、深さH2を20〜150nmに設定している。ただし、深さH2の上限と下限は、半導体装置やトンネルトランジスタの構造に応じて、違う値に設定してもよい。

【0041】

以上のように、本実施形態によれば、トンネルトランジスタの高電圧での駆動力を向上させることが可能となる。

【0042】

(第2実施形態)

図4から図6は、第2実施形態の半導体装置の製造方法を示す断面図である。第2実施形態の方法は、図1の半導体装置を製造する方法の一例に相当する。

【0043】

まず、図4(a)に示すように、基板101内に素子分離絶縁膜102を形成する。素子分離絶縁膜102は、基板101内に素子分離溝を形成し、素子分離溝内に絶縁膜を埋め込み、この絶縁膜の表面をCMP(Chemical Mechanical Polishing)により平坦化することで形成可能である。本実施形態の素子分離絶縁膜102は、STI(Shallow Trench Isolation)絶縁膜に相当する。

【0044】

次に、図4(b)に示すように、基板101上に、ゲート絶縁膜111を介してゲート電極112を形成する。ゲート電極112は、基板101上に、ゲート絶縁膜111となる絶縁膜を形成し、この絶縁膜上に、ゲート電極112となる電極材を形成し、この電極材をRIE(Reactive Ion Etching)によりエッチングすることで形成可能である。

【0045】

次に、図4(c)に示すように、イオン注入により、基板101内に、ドレイン領域121となるN+型層を形成する。このN+型層用のN型不純物の例としては、リン(P)やヒ素(As)が挙げられる。

【0046】

次に、図5(a)に示すように、イオン注入により、基板101内のソース側に、第1の拡散層123となるN−型層を形成する。このN−型層用のN型不純物の例としては、リンやヒ素が挙げられる。

【0047】

次に、図5(b)に示すように、イオン注入により、基板101内に、ソース領域122となるP+型層を形成する。このP+型層用のP型不純物の例としては、ボロン(B)が挙げられる。

【0048】

次に、図5(c)に示すように、イオン注入により、基板101内のソース側に、第2の拡散層124となるN型層を形成する。このN型層用のN型不純物の例としては、リンやヒ素が挙げられる。

【0049】

本実施形態では、図4(c)から図5(c)の工程等を経て、基板101内に、ドレイン領域121、ソース領域122、第1の拡散層123、第2の拡散層124が形成される。本実施形態では、第1の拡散層123をソース領域122よりも深い位置に形成するため、図5(a)の工程での加速電圧は、図5(b)の工程での加速電圧よりも高く設定される。

【0050】

また、図5(c)の工程において、第2の拡散層124は、第1の拡散層123を貫通するよう形成していてもよいし、第1の拡散層123を貫通しないよう形成してもよい。前者の方法には、第2の拡散層124を、確実に第1の拡散層123に接触させることができるという利点がある。また、後者の方法には、図5(c)の工程におけるイオン注入量や加速電圧を低く抑えることができるという利点がある。

【0051】

なお、図4(c)から図5(c)の工程は、上記の順番と異なる順番で実施してもよい。例えば、図4(c)の工程と図5(a)の工程は、逆の順番で実施してもよい。

【0052】

次に、図6(a)に示すように、エッチバックにより、ゲート電極112の側面に側壁絶縁膜113を形成する。

【0053】

次に、図6(b)に示すように、サリサイド工程により、ゲート電極112、ドレイン領域121、ソース領域122、第2の拡散層124の上面に、シリサイド層125を形成する。シリサイド層125の例としては、チタンシリサイド層、コバルトシリサイド層、ニッケルシリサイド層、白金シリサイド層などが挙げられる。

【0054】

次に、図6(c)に示すように、CVD(Chemical Vapor Deposition)により、基板101上の全面に層間絶縁膜131を形成する。次に、図6(c)に示すように、リソグラフィとエッチングにより、層間絶縁膜131内にコンタクトプラグ132を形成する。コンタクトプラグ132は、ドレイン領域121上のシリサイド層125上と、ソース領域122および第2の拡散層124上のシリサイド層125上に形成される。図6(c)の工程では、コンタクトプラグ132をさらに、ゲート電極112上のシリサイド層125上に形成してもよい。

【0055】

その後、本実施形態では、基板101上に、層間絶縁膜、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0056】

以上のように、本実施形態の方法では、トンネルトランジスタ用のソース領域122の下部に、ソース領域122の導電型とは逆導電型の第1の拡散層123を配置する。よって、本実施形態によれば、第1実施形態で説明したように、高電圧においてMOSFETのように動作するトンネルトランジスタを製造することができる。よって、本実施形態によれば、トンネルトランジスタの高電圧での駆動力を向上させることが可能となる。

【0057】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0058】

101:基板、102:素子分離絶縁膜、

111:ゲート絶縁膜、112:ゲート電極、113:側壁絶縁膜、

121:ドレイン領域、122:ソース領域、

123:第1の拡散層、124:第2の拡散層、125:シリサイド層、

131:層間絶縁膜、132:コンタクトプラグ、

201:反転層

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルトランジスタが精力的に研究されている。トンネルトランジスタは、そのSファクターの値が低く、低電圧動作に適しているが、高電圧での駆動力向上が課題となっている。一方、MOSFETは、高電圧での駆動力は大きいが、そのSファクターの値が高く、低電圧動作には不向きである。そこで、低電圧動作にも高電圧動作にも適したトランジスタを実現すべく、トンネルトランジスタの高電圧での駆動力向上が求められている。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Chenming Hu et al. "Green Transistor - A VDD Scaling Path for Future Low Power ICs" VLSI-TSA2008

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルトランジスタの高電圧での駆動力を向上させることが可能な半導体装置を提供する。

【課題を解決するための手段】

【0005】

一の実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層を備える。

【図面の簡単な説明】

【0006】

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態のトンネルトランジスタの動作原理を示した断面図である。

【図3】第1実施形態のトンネルトランジスタの動作特性を示したグラフである。

【図4】第2実施形態の半導体装置の製造方法を示す断面図(1/3)である。

【図5】第2実施形態の半導体装置の製造方法を示す断面図(2/3)である。

【図6】第2実施形態の半導体装置の製造方法を示す断面図(3/3)である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルトランジスタの構成要素として、基板101と、ゲート絶縁膜111と、ゲート電極112と、側壁絶縁膜113と、ドレイン領域121と、ソース領域122と、第1の拡散層123と、第2の拡散層124と、シリサイド層125などを備えている。

【0010】

基板101は例えば、シリコン基板などの半導体基板である。図1には、基板101の主面に平行で、互いに垂直なX方向およびY方向と、基板101の主面に垂直なZ方向が示されている。本実施形態では、基板101は、低濃度のP型不純物を含むP−型基板である。なお、基板101は、低濃度のN型不純物を含むN−型基板でもよい。また、基板101は、SOI(Semiconductor On Insulator)基板でもよい。図1にはさらに、基板101内に形成された素子分離絶縁膜102が示されている。

【0011】

ゲート絶縁膜111は、基板101上に形成されている。また、ゲート電極112は、基板101上にゲート絶縁膜111を介して形成されている。さらに、側壁絶縁膜113は、ゲート電極112の側面に形成されている。ゲート絶縁膜111は、例えばシリコン酸化膜である。また、ゲート電極112は、例えばポリシリコン層である。さらに、側壁絶縁膜113は、例えばシリコン酸化膜またはシリコン窒化膜である。

【0012】

ドレイン領域121とソース領域122は、基板101内に、ゲート電極112を挟むように形成されている。本実施形態では、ドレイン領域121はN+型領域であり、ソース領域122はP+型領域である。ドレイン領域121とソース領域122は、それぞれ第1の主端子領域、第2の主端子領域の例である。また、N導電型とP導電型は、それぞれ第1導電型と第2導電型の例である。

【0013】

第1の拡散層123は、基板101内において、ソース領域122の下面に接する位置に形成されており、かつ、ドレイン領域121と離間された位置に形成されている。本実施形態では、第1の拡散層123は、N−型拡散層であり、ソース領域122の導電型と逆導電型となっている。

【0014】

符号H1は、基板101の表面から、ソース領域122と第1の拡散層123とのPN接合面までの深さを示す。また、符号H2は、基板101の表面から、第1の拡散層123の下面までの深さを示す。本実施形態では、深さH1は、例えば10〜100nmに設定されている。また、深さH2は、例えば20〜150nmに設定されている。本実施形態では、第1の拡散層123の厚さは、ソース領域122の厚さ以下に設定されており、よって、深さH2は、深さH1の2倍以下に設定されている。

【0015】

また、本実施形態では、第1の拡散層123のドレイン領域121側の側面が、ソース領域122のドレイン領域121側の側面よりも突出している。この第1の拡散層123の突出部分の作用については、後述する。本実施形態では、この突出部分の先端が、ドレイン領域121とソース領域122との間の中間地点よりも、ソース領域122側に位置している。

【0016】

第2の拡散層124は、基板101内において、ソース領域122の側面と第1の拡散層123の側面とに接する位置に形成されている。本実施形態では、第2の拡散層124は、N型拡散層であり、ソース領域122の導電型と逆導電型となっている。第2の拡散層124は、ソース領域122と第1の拡散層123の、ドレイン領域121とは逆側の側面に接している。本実施形態では、第2の拡散層124のX方向の幅は、ソース領域122や第1の拡散層123のX方向の幅よりも短く設定されている。

【0017】

なお、本実施形態では、第2の拡散層124の下面は、第1の拡散層123の下面よりも下方に位置していても上方に位置していてもよい。すなわち、第2の拡散層124は、第1の拡散層123を貫通していてもよいし、第1の拡散層123を貫通していなくてもよい。

【0018】

シリサイド層125は、ゲート電極112の上面に形成されている。また、シリサイド層125は、ドレイン領域121の上面に形成されている。さらに、シリサイド層125は、ソース領域122の上面と第2の拡散層124の上面に連続して形成されている。本実施形態のシリサイド層125は、Ti(チタン)、Co(コバルト)、Ni(ニッケル)、Pt(白金)の少なくともいずれかを含有している。

【0019】

図1の半導体装置はさらに、基板101上にトンネルトランジスタを覆うように形成された層間絶縁膜131と、層間絶縁膜131内に形成されたコンタクトプラグ132とを備えている。

【0020】

図1に示す2本のコンタクトプラグ132のうち、一方は、ドレイン領域121上のシリサイド層125上に形成されており、他方は、ソース領域122および第2の拡散層124上のシリサイド層125上に形成されている。前者のコンタクトプラグ132は、ドレイン領域121に電圧を印加するために使用され、後者のコンタクトプラグ132は、ソース領域122と第2の拡散層124に共通の電圧(本実施形態ではグラウンド電圧)を印加するために使用される。後者の共通の電圧は、第2の拡散層124を介して第1の拡散層123にも印加される。

【0021】

なお、本実施形態では、ドレイン領域121、ソース領域122、第1、第2の拡散層123、124の不純物濃度は、例えば次のように設定される。

【0022】

ドレイン領域121の不純物濃度と、ソース領域122の不純物濃度は、ほぼ同じ値に設定される。第1の拡散層123の不純物濃度は、ドレイン領域121やソース領域122の不純物濃度よりも低く設定される。第2の拡散層124の不純物濃度は、ドレイン領域121やソース領域122の不純物濃度よりも高く設定される。

【0023】

(1)トンネルトランジスタの動作

次に、図2と図3を参照し、第1実施形態のトンネルトランジスタの動作について説明する。

【0024】

図2は、第1実施形態のトンネルトランジスタの動作原理を示した断面図である。

【0025】

ドレイン領域121に正の電圧を印加した状態で、ゲート電極112に正の電圧を印加すると、図2(a)に示すように、ソース領域122とドレイン領域121との間に反転層201が生じる。本実施形態では、基板101がP−型基板であるため、反転層201はN型層である。そして、ソース領域122内の電子が、トンネル現象により反転層201内に流れ込み、その結果、チャネル領域にトンネル電流が流れる。こうして、本実施形態のトランジスタは、トンネルトランジスタとして機能する。

【0026】

ゲート電圧を増大させると、図2(b)に示すように、反転層201が下方へと広がっていく。よって、ゲート電圧を増大させると、トンネル電流が増加する。しかしながら、基板101内のポテンシャルは、基板101の表面からの距離の2乗に反比例して減少するため、ゲート電圧の増大に応じて、トンネル電流の増加率は減少していく。よって、トンネルトランジスタの高電圧での駆動力は、MOSFETに比べて小さくなる。

【0027】

しかしながら、本実施形態では、ゲート電圧を増大させると、図2(c)に示すように、反転層201がやがて第1の拡散層123に到達する。その結果、本実施形態のトランジスタは、第1の拡散層123をソース領域とするMOSFETのように動作する。これにより、本実施形態のトランジスタは、高電圧での駆動力が高くなる。

【0028】

このように、本実施形態では、ソース領域122の下部に第1の拡散層123を設けることで、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0029】

図3は、第1実施形態のトンネルトランジスタの動作特性を示したグラフである。

【0030】

図3において、横軸はゲート電圧を示し、縦軸はドレイン電流を示す。図3は、本実施形態のトンネルトランジスタに関するシミュレーション結果を示す。

【0031】

曲線C1は、ドレイン領域121とソース領域122によるトンネルトランジスタの動作特性を示す。また、曲線C2は、ドレイン領域121と第1の拡散層123によるMOSFETの動作特性を示す。

【0032】

図3に示すように、ゲート電圧が低いときには、トンネルトランジスタの駆動力が支配的である。一方、ゲート電圧が高くなると、MOSFETの駆動力が支配的となる。よって、本実施形態によれば、高電圧においてトンネルトランジスタがMOSFETのように動作することで、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0033】

(2)第1実施形態の半導体装置の作用効果

次に、再び図1を参照し、第1実施形態の半導体装置の作用効果について説明する。

【0034】

以上のように、本実施形態では、トンネルトランジスタのソース領域122の下部に、ソース領域122の導電型と逆導電型の第1の拡散層123を形成する。よって、本実施形態によれば、トンネルトランジスタを高電圧においてMOSFETのように動作させ、トンネルトランジスタの高電圧での駆動力を向上させることができる。

【0035】

また、本実施形態では、ソース領域122と第1の拡散層123の側方に、ソース領域122の導電型と逆導電型の第2の拡散層124を形成する。よって、第1の拡散層123に対し、コンタクトプラグ132から第2の拡散層124を介して電圧を印加することが可能となる。よって、本実施形態によれば、第1の拡散層123を、MOSFETのソース領域のように機能させることが可能となる。

【0036】

また、本実施形態では、ソース領域122と第2の拡散層124は、共通のコンタクトプラグ132に電気的に接続されている。よって、本実施形態によれば、ソース領域122に印加する電圧と、第1、第2の拡散層123、124に印加する電圧を、共通化することが可能となる。

【0037】

また、本実施形態では、シリサイド層125が、ソース領域122の上面と第2の拡散層124の上面に連続して形成されている。よって、本実施形態によれば、コンタクトプラグ132の設置位置がシリサイド層125上でずれてしまっても、コンタクトプラグ132をソース領域122と第2の拡散層124に電気的に接続することが可能となる。よって、本実施形態によれば、コンタクトホールを形成しやすくなる。

【0038】

また、本実施形態では、第1の拡散層123のドレイン領域121側の側面が、ソース領域122のドレイン領域121側の側面よりも突出している。このような構造には、反転層201が下方に広がった際、反転層201が第1の拡散層123に接しやすくなるという利点がある。

【0039】

また、本実施形態では、基板101の表面から、ソース領域122と第1の拡散層123とのPN接合面までの深さH1が、10〜100nmに設定されている。深さH1が小さすぎると、低過ぎるゲート電圧で反転層201が第1の拡散層123に到達してしまうという問題がある。また、深さH1が大きすぎると、十分にゲート電圧を高くしても反転層201が第1の拡散層123に到達しないという問題がある。よって、本実施形態では、これらの問題を避けるため、深さH1を10〜100nmに設定している。ただし、深さH1の上限と下限は、半導体装置やトンネルトランジスタの構造に応じて、違う値に設定してもよい。

【0040】

また、本実施形態では、基板101の表面から、第1の拡散層123の下面までの深さH2が、20〜150nmに設定されている。深さH2が小さすぎると、例えば、反転層201と第1の拡散層123との接触面積が小さすぎるという問題がある。また、深さH2が大きすぎると、例えば、ドレイン領域121の下面付近と第1の拡散層123の先端付近との間にチャネルが生じるおそれがあるという問題がある。よって、本実施形態では、これらの問題を避けるため、深さH2を20〜150nmに設定している。ただし、深さH2の上限と下限は、半導体装置やトンネルトランジスタの構造に応じて、違う値に設定してもよい。

【0041】

以上のように、本実施形態によれば、トンネルトランジスタの高電圧での駆動力を向上させることが可能となる。

【0042】

(第2実施形態)

図4から図6は、第2実施形態の半導体装置の製造方法を示す断面図である。第2実施形態の方法は、図1の半導体装置を製造する方法の一例に相当する。

【0043】

まず、図4(a)に示すように、基板101内に素子分離絶縁膜102を形成する。素子分離絶縁膜102は、基板101内に素子分離溝を形成し、素子分離溝内に絶縁膜を埋め込み、この絶縁膜の表面をCMP(Chemical Mechanical Polishing)により平坦化することで形成可能である。本実施形態の素子分離絶縁膜102は、STI(Shallow Trench Isolation)絶縁膜に相当する。

【0044】

次に、図4(b)に示すように、基板101上に、ゲート絶縁膜111を介してゲート電極112を形成する。ゲート電極112は、基板101上に、ゲート絶縁膜111となる絶縁膜を形成し、この絶縁膜上に、ゲート電極112となる電極材を形成し、この電極材をRIE(Reactive Ion Etching)によりエッチングすることで形成可能である。

【0045】

次に、図4(c)に示すように、イオン注入により、基板101内に、ドレイン領域121となるN+型層を形成する。このN+型層用のN型不純物の例としては、リン(P)やヒ素(As)が挙げられる。

【0046】

次に、図5(a)に示すように、イオン注入により、基板101内のソース側に、第1の拡散層123となるN−型層を形成する。このN−型層用のN型不純物の例としては、リンやヒ素が挙げられる。

【0047】

次に、図5(b)に示すように、イオン注入により、基板101内に、ソース領域122となるP+型層を形成する。このP+型層用のP型不純物の例としては、ボロン(B)が挙げられる。

【0048】

次に、図5(c)に示すように、イオン注入により、基板101内のソース側に、第2の拡散層124となるN型層を形成する。このN型層用のN型不純物の例としては、リンやヒ素が挙げられる。

【0049】

本実施形態では、図4(c)から図5(c)の工程等を経て、基板101内に、ドレイン領域121、ソース領域122、第1の拡散層123、第2の拡散層124が形成される。本実施形態では、第1の拡散層123をソース領域122よりも深い位置に形成するため、図5(a)の工程での加速電圧は、図5(b)の工程での加速電圧よりも高く設定される。

【0050】

また、図5(c)の工程において、第2の拡散層124は、第1の拡散層123を貫通するよう形成していてもよいし、第1の拡散層123を貫通しないよう形成してもよい。前者の方法には、第2の拡散層124を、確実に第1の拡散層123に接触させることができるという利点がある。また、後者の方法には、図5(c)の工程におけるイオン注入量や加速電圧を低く抑えることができるという利点がある。

【0051】

なお、図4(c)から図5(c)の工程は、上記の順番と異なる順番で実施してもよい。例えば、図4(c)の工程と図5(a)の工程は、逆の順番で実施してもよい。

【0052】

次に、図6(a)に示すように、エッチバックにより、ゲート電極112の側面に側壁絶縁膜113を形成する。

【0053】

次に、図6(b)に示すように、サリサイド工程により、ゲート電極112、ドレイン領域121、ソース領域122、第2の拡散層124の上面に、シリサイド層125を形成する。シリサイド層125の例としては、チタンシリサイド層、コバルトシリサイド層、ニッケルシリサイド層、白金シリサイド層などが挙げられる。

【0054】

次に、図6(c)に示すように、CVD(Chemical Vapor Deposition)により、基板101上の全面に層間絶縁膜131を形成する。次に、図6(c)に示すように、リソグラフィとエッチングにより、層間絶縁膜131内にコンタクトプラグ132を形成する。コンタクトプラグ132は、ドレイン領域121上のシリサイド層125上と、ソース領域122および第2の拡散層124上のシリサイド層125上に形成される。図6(c)の工程では、コンタクトプラグ132をさらに、ゲート電極112上のシリサイド層125上に形成してもよい。

【0055】

その後、本実施形態では、基板101上に、層間絶縁膜、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0056】

以上のように、本実施形態の方法では、トンネルトランジスタ用のソース領域122の下部に、ソース領域122の導電型とは逆導電型の第1の拡散層123を配置する。よって、本実施形態によれば、第1実施形態で説明したように、高電圧においてMOSFETのように動作するトンネルトランジスタを製造することができる。よって、本実施形態によれば、トンネルトランジスタの高電圧での駆動力を向上させることが可能となる。

【0057】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0058】

101:基板、102:素子分離絶縁膜、

111:ゲート絶縁膜、112:ゲート電極、113:側壁絶縁膜、

121:ドレイン領域、122:ソース領域、

123:第1の拡散層、124:第2の拡散層、125:シリサイド層、

131:層間絶縁膜、132:コンタクトプラグ、

201:反転層

【特許請求の範囲】

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域と、

前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層と、

前記基板内において、前記第2の主端子領域の側面と前記第1の拡散層の側面に接する位置に形成された、前記第1導電型の第2の拡散層と、

前記第2の主端子領域の上面と前記第2の拡散層の上面に連続して形成されたシリサイド層とを備え、

前記基板の表面から、前記第2の主端子領域と前記第1の拡散層との接合面までの深さは、10nm〜100nmであり、

前記基板の表面から、前記第1の拡散層の下面までの深さは、20nm〜150nmであり、

前記第1の拡散層の前記第1の主端子領域側の側面は、前記第2の主端子領域の前記第1の主端子領域側の側面よりも突出している、

半導体装置。

【請求項2】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域と、

前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層と、

を備える半導体装置。

【請求項3】

さらに、前記基板内において、前記第2の主端子領域の側面と前記第1の拡散層の側面に接する位置に形成された、前記第1導電型の第2の拡散層を備える、請求項2に記載の半導体装置。

【請求項4】

さらに、前記第2の主端子領域の上面と前記第2の拡散層の上面に連続して形成されたシリサイド層を備える、請求項3に記載の半導体装置。

【請求項5】

前記基板の表面から、前記第2の主端子領域と前記第1の拡散層との接合面までの深さは、10nm〜100nmである、請求項2から4のいずれか1項に記載の半導体装置。

【請求項6】

前記基板の表面から、前記第1の拡散層の下面までの深さは、20nm〜150nmである、請求項2から5のいずれか1項に記載の半導体装置。

【請求項7】

前記第1の拡散層の前記第1の主端子領域側の側面は、前記第2の主端子領域の前記第1の主端子領域側の側面よりも突出している、請求項2から6のいずれか1項に記載の半導体装置。

【請求項1】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域と、

前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層と、

前記基板内において、前記第2の主端子領域の側面と前記第1の拡散層の側面に接する位置に形成された、前記第1導電型の第2の拡散層と、

前記第2の主端子領域の上面と前記第2の拡散層の上面に連続して形成されたシリサイド層とを備え、

前記基板の表面から、前記第2の主端子領域と前記第1の拡散層との接合面までの深さは、10nm〜100nmであり、

前記基板の表面から、前記第1の拡散層の下面までの深さは、20nm〜150nmであり、

前記第1の拡散層の前記第1の主端子領域側の側面は、前記第2の主端子領域の前記第1の主端子領域側の側面よりも突出している、

半導体装置。

【請求項2】

基板と、

前記基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域と、

前記基板内において、前記第2の主端子領域の下面に接し、前記第1の主端子領域と離間された位置に形成された、前記第1導電型の第1の拡散層と、

を備える半導体装置。

【請求項3】

さらに、前記基板内において、前記第2の主端子領域の側面と前記第1の拡散層の側面に接する位置に形成された、前記第1導電型の第2の拡散層を備える、請求項2に記載の半導体装置。

【請求項4】

さらに、前記第2の主端子領域の上面と前記第2の拡散層の上面に連続して形成されたシリサイド層を備える、請求項3に記載の半導体装置。

【請求項5】

前記基板の表面から、前記第2の主端子領域と前記第1の拡散層との接合面までの深さは、10nm〜100nmである、請求項2から4のいずれか1項に記載の半導体装置。

【請求項6】

前記基板の表面から、前記第1の拡散層の下面までの深さは、20nm〜150nmである、請求項2から5のいずれか1項に記載の半導体装置。

【請求項7】

前記第1の拡散層の前記第1の主端子領域側の側面は、前記第2の主端子領域の前記第1の主端子領域側の側面よりも突出している、請求項2から6のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−89618(P2013−89618A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−225650(P2011−225650)

【出願日】平成23年10月13日(2011.10.13)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月13日(2011.10.13)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]