半導体装置

【課題】高耐圧を確保できながら、逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】その表面12にショットキーメタル22が形成されたエピタキシャル層6を備えるショットキーバリアダイオード1において、エピタキシャル層6の表面12に沿う方向に互いに間隔を空けて配列され、それぞれが表面12から裏面11へ向かってエピタキシャル層6の厚さ方向に延びるp型ピラー層17を形成することにより、エピタキシャル層6にスーパージャンクション構造を形成する。また、エピタキシャル層6の表面12の近傍に、p型ピラー層17よりも不純物濃度の高い電界緩和層19を選択的に形成する。

【解決手段】その表面12にショットキーメタル22が形成されたエピタキシャル層6を備えるショットキーバリアダイオード1において、エピタキシャル層6の表面12に沿う方向に互いに間隔を空けて配列され、それぞれが表面12から裏面11へ向かってエピタキシャル層6の厚さ方向に延びるp型ピラー層17を形成することにより、エピタキシャル層6にスーパージャンクション構造を形成する。また、エピタキシャル層6の表面12の近傍に、p型ピラー層17よりも不純物濃度の高い電界緩和層19を選択的に形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ワイドバンドギャップ半導体からなるショットキーバリアダイオードを備える半導体装置に関する。

【背景技術】

【0002】

従来、モータ制御システム、電力変換システムなど、各種パワーエレクトロニクス分野におけるシステムに主として使用される半導体装置(半導体パワーデバイス)が注目されている。

たとえば、特許文献1は、SiCが採用されたショットキーバリアダイオードを開示している。当該ショットキーバリアダイオードは、n型4H−SiCバルク基板と、バルク基板上に成長したn型のエピタキシャル層と、エピタキシャル層の表面に形成され、エピタキシャル層の表面を部分的に露出させる酸化膜と、酸化膜の開口内に形成され、エピタキシャル層に対してショットキー接合するショットキー電極とを備えている。

【0003】

また、特許文献1は、SiCが採用された縦型MIS電界効果トランジスタを開示している。当該縦型MIS電界効果トランジスタは、n型4H−SiCバルク基板と、バルク基板上に成長したn型のエピタキシャル層と、エピタキシャル層の表層部に形成されたn型不純物領域(ソース領域)と、当該n型不純物領域の両サイドに隣接して形成されたp型ウェル領域と、エピタキシャル層の表面に形成されたゲート酸化膜と、ゲート酸化膜を介してp型ウェル領域に対向するゲート電極とを備えている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−79339号公報

【特許文献2】特開2011−9797号公報

【発明の概要】

【課題を解決するための手段】

【0005】

本発明の半導体装置は、表面および裏面を有する第1導電型のワイドバンドギャップ半導体からなる半導体層と、前記半導体層の前記表面に接するように形成されたショットキー電極とを含み、前記半導体層には、前記表面に沿う方向に互いに間隔を空けて配列され、それぞれが前記表面から前記裏面へ向かって前記半導体層の厚さ方向に延びる柱状であり、前記半導体層の第1導電型の他の部分と協働して前記半導体層にスーパージャンクション構造を形成する第2導電型の複数のピラー層と、前記表面の近傍に選択的に形成され、前記表面における電界強度を緩和するための電界緩和部とが形成されている。

【0006】

本発明の半導体装置によれば、高耐圧を確保できながら、逆方向リーク電流および順方向電圧(VF:Forward Voltage)の低減を達成することができる。

半導体装置の耐圧は、半導体層の不純物濃度や厚さに関係しており、半導体層の不純物濃度を低くしたり、厚さを大きくしたりすると向上する傾向がある。

一方、半導体装置の順方向電圧は、半導体層の不純物濃度を高くしたり厚さを小さくしたりしてオン抵抗を低減するか、またはショットキー電極と半導体層との間のショットキー障壁の高さ(バリアハイト)を低くすると低減する傾向がある。つまり、半導体層の不純物濃度および厚さに関しては、耐圧の向上および順方向電圧の低減は背反の関係にある。

【0007】

そこで、本発明の半導体装置によれば、半導体層の厚さ方向にそれぞれ延びる第2導電型ピラー層と、半導体層の第1導電型の他の部分とが協働して、前記半導体層にスーパージャンクション構造が形成されている。このスーパージャンクション構造により、半導体層におけるピラー層との界面に沿う方向(つまり、半導体層の厚さ方向)に当該界面全体に空乏層を広げることができる。これにより、半導体層中の電界強度を均一にすることができる。その結果、半導体層の不純物濃度および厚さが同条件である下では、スーパージャンクション構造が形成されていない半導体装置に比べて耐圧を向上させることができる。従って、従来に比べて、不純物濃度が高くて厚さが小さい半導体層でも十分な耐圧を確保できるので、半導体層の不純物濃度および厚さを適切に設計することにより、高耐圧を確保できながら、順方向電圧を低減することができる。

【0008】

さらに、本発明の半導体装置によれば、半導体層の表面近傍に電界緩和部が形成されており、半導体層の表面における電界強度を緩和することができる。そのため、ショットキー電極と半導体層との間のバリアハイトを低くしても、逆方向リーク電流を低減することができる。その結果、逆方向リーク電流を低減できながら、バリアハイトを低くして順方向電圧を低減することができる。

【0009】

なお、本発明においてショットキー電極とは、半導体層との間にショットキー障壁を形成する金属電極、半導体層のバンドギャップとは異なるバンドギャップを有する異種半導体からなり、半導体層に対してヘテロ接合(バンドギャップ差を利用して半導体層との間に電位障壁を形成する接合)する半導体電極のいずれをも含む概念である。以下、この項においては、ショットキー接合およびヘテロ接合を総称して「ショットキー接合」とし、ショットキー障壁およびヘテロ接合により形成される電位障壁(ヘテロ障壁)を総称して「ショットキー障壁」とし、金属電極および半導体電極を総称して「ショットキー電極」とする。

【0010】

また、本発明の半導体装置では、前記電界緩和部は、前記ピラー層の上端部に形成されていることが好ましい。

また、本発明の半導体装置では、前記電界緩和部は、前記半導体層の前記表面に前記半導体層の一部を利用して形成され、前記ピラー層よりも不純物濃度の高い第2導電型を示す、電界緩和層を含んでいてもよい。

【0011】

電界緩和層は、前記半導体層の残りの部分よりも高い抵抗を有する高抵抗層を含んでいてもよい。その場合、前記高抵抗層は、前記半導体層の前記表面から不純物イオンを注入した後、1500℃未満のアニール処理をすることによって形成されることが好ましい。

この構成によれば、アニール処理の際のワイドバンドギャップ半導体の昇華量を低減することができる。その結果、半導体層の表面の平坦性を良好に維持することができる。

【0012】

なお、この1500℃未満のアニール処理とは、注入された不純物イオンの衝突によりワイドバンドギャップ半導体の結晶構造に生じた欠陥を回復させるが(結晶性回復)、注入された不純物イオンを活性化させない程度のアニール処理のことを意味している。

また、本発明の半導体装置では、前記高抵抗層の不純物の活性化率は、5%未満であることが好ましい。また、前記高抵抗層のシート抵抗は、1MΩ/□以上であることが好ましい。

【0013】

また、本発明の半導体装置では、前記電界緩和部は、前記半導体層の前記表面から掘り下がったトレンチを含んでいてもよい。

その場合、前記トレンチの側面と底面とが交わって形成されたトレンチのエッジ部は、下記式(1)を満たす曲率半径Rを有することが好ましい。

0.01L<R<10L・・・(1)

(ただし、式(1)において、Lはトレンチの幅方向に沿って対向するエッジ部間の直線距離を示している。)

この構成によれば、トレンチのエッジ部に集中する電界を緩和して、耐圧を向上させることができる。

【0014】

また、本発明の半導体装置では、前記電界緩和部は、前記トレンチの前記底面および前記エッジ部に前記半導体層の一部を利用して形成された第2導電型の底部緩和層をさらに含むことが好ましく、前記底部緩和層と一体的であり、前記トレンチの前記側面に前記半導体層の一部を利用して形成された第2導電型の側部緩和層をさらに含むことがさらに好ましい。この場合、前記側部緩和層は、前記トレンチの前記側面に沿って前記トレンチの開口端に至るように形成されていることが、とりわけ好ましい。

【0015】

また、本発明の半導体装置では、前記トレンチは、平面形状の底面および当該平面形状の底面に対して90°を超える角度で傾斜した側面を有するテーパトレンチを含むことが好ましい。

テーパトレンチであれば、側面が底面に対して90°で直角に立つ場合よりも、半導体装置の耐圧を一層向上させることができる。

【0016】

さらに、テーパトレンチでは、底面だけでなく、側面の全部または一部もトレンチの開放端に対して対向することとなる。そのため、たとえばトレンチを介して第2導電型の不純物を半導体層に注入する場合に、トレンチの開放端からトレンチ内に入射した不純物を、トレンチの側面に確実に当てることができる。その結果、前述の側部緩和部を容易に形成することができる。

【0017】

なお、テーパトレンチとは、側面の全部が底面に対して90°を超える角度で傾斜しているトレンチ、側面の一部(たとえば、トレンチのエッジ部を形成する部分)が底面に対して90°を超える角度で傾斜しているトレンチのいずれをも含む概念である。

また、本発明の半導体装置では、前記ショットキー電極は、前記トレンチに埋め込まれるように形成されており、前記半導体層における前記トレンチの底面を形成する部分には、前記トレンチに埋め込まれた前記ショットキー電極との間にオーミック接合を形成する第2導電型のコンタクト層がさらに形成されていることが好ましい。

【0018】

この構成により、コンタクト層(第2導電型)と半導体層(第1導電型)とのpn接合を有するpnダイオードに対してショットキー電極をオーミック接合させることができる。このpnダイオードは、ショットキー電極と半導体層とのショットキー接合を有するショットキーバリアダイオード(ヘテロダイオード)に対して並列に設けられる。これにより、半導体装置にサージ電流が流れても、当該サージ電流の一部を内蔵pnダイオードに流すことができる。その結果、ショットキーバリアダイオードに流れるサージ電流を低減できるので、サージ電流によるショットキーバリアダイオードの熱破壊を防止することができる。

【0019】

また、本発明の半導体装置では、前記半導体層は、逆方向電圧印加時に第1電界がかかる第1部分および当該第1電界に対して相対的に高い第2電界がかかる第2部分を、前記電界緩和部とは異なる部分に有している場合、前記ショットキー電極は、前記第1部分との間に第1ショットキー障壁を形成する第1電極と、前記第2部分との間に前記第1ショットキー障壁に対して相対的に高い第2ショットキー障壁を形成する第2電極とを含むことが好ましい。

【0020】

本発明では、半導体層の第1部分と第2部分との関係のように、相対的に電界強度が高い部分と低い部分とが存在する場合がある。

そこで上記のように、逆方向電圧印加時における半導体層の電界分布に応じてショットキー電極を適正に選択しておけば、逆方向電圧印加時に相対的に高い第2電界がかかる第2部分では、比較的高い第2ショットキー障壁により逆リーク電流を抑制することができる。一方、相対的に低い第1電界がかかる第1部分では、ショットキー障壁の高さを低くしても逆方向リーク電流が当該ショットキー障壁を越えるおそれが少ないので、比較的低い第1ショットキー障壁とすることにより、順方向電圧印加時に低い電圧で優先的に電流を流すことができる。よって、この構成により、逆方向リーク電流および順方向電圧の低減を効率よく行うことができる。

【0021】

また、本発明の半導体装置では、前記半導体層は、第1不純物濃度を有するベースドリフト層と、前記ベースドリフト層上に形成され、前記第1不純物濃度に対して相対的に高い第2不純物濃度を有する低抵抗ドリフト層とを含む場合、前記電界緩和部は、その最深部が前記低抵抗ドリフト層に達するように形成され、前記半導体層の一部を単位セルとして区画していることが好ましい。

【0022】

電界緩和部で区画された単位セルでは電流を流すことができる領域(電流経路)が制約されるので、半導体層における単位セルを形成する部分の不純物濃度が低いと、単位セルの抵抗値が高くなるおそれがある。そこで上記のように、最深部が低抵抗ドリフト層に達するように電界緩和部を形成することにより、単位セルの全部もしくは一部を低抵抗ドリフト層で形成することができる。そのため、当該低抵抗ドリフト層が形成された部分では、電流経路がたとえ狭められても、比較的高い第2不純物濃度を有する低抵抗ドリフト層により抵抗値の上昇を抑制することができる。その結果、単位セルの低抵抗化を図ることができる。

【0023】

また、前記ベースドリフト層の前記第1不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少していてもよい。また、前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって一定であってもよいし、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少していてもよい。

【0024】

また、本発明の半導体装置では、前記半導体層は、前記低抵抗ドリフト層上に形成され、前記第2不純物濃度に対して相対的に低い第3不純物濃度を有する表面ドリフト層をさらに含むことが好ましい。

この構成により、半導体層の表面近傍の不純物濃度を小さくすることができるので、逆方向電圧印加時に半導体層の表面にかかる電界強度を低減することができる。その結果、逆方向リーク電流を一層低減することができる。

【0025】

また、本発明の半導体装置が、前記半導体層を支持する第1導電型のワイドバンドギャップ半導体からなる基板をさらに含む場合、前記半導体層は、前記基板上に形成され、前記第1不純物濃度に対して相対的に高い第4不純物濃度を有するバッファ層をさらに含んでいてもよい。

また、本発明の半導体装置では、前記ピラー層の下端部は、前記バッファ層に接していてもよいし、前記バッファ層に対して間隔が空くように位置していてもよい。

【0026】

また、本発明の半導体装置において、ワイドバンドギャップ半導体(バンドギャップが2eV以上)は、たとえば絶縁破壊電界が1MV/cmよりも大きい半導体であって、具体的には、SiC(たとえば、4H−SiC 絶縁破壊電界が約2.8MV/cmであり、バンドギャップの幅が約3.26eV)、GaN(絶縁破壊電界が約3MV/cmであり、バンドギャップの幅が約3.42eV)、ダイヤモンド(絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約5.47eV)などである。

【図面の簡単な説明】

【0027】

【図1】本発明の第1実施形態に係るショットキーバリアダイオードの模式的な平面図である。

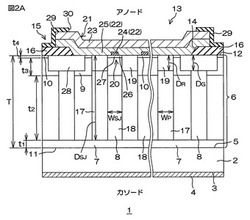

【図2A】図1のショットキーバリアダイオードの断面図であって、図1の切断線II−IIでの切断面を示す。

【図2B】図2Aの電界緩和層の形状の一例を示す図である。

【図2C】図2Aの電界緩和層の形状の他の例を示す図である。

【図3】スーパージャンクション構造の導入効果を証明するためのシミュレーション実験に用いたショットキーバリアダイオードの概略構成図である。

【図4】エピタキシャル層の厚さと電界強度との関係を示すグラフである。

【図5】高抵抗層の導入効果を証明するためのシミュレーション実験に用いたショットキーバリアダイオードの概略構成図である。

【図6】エピタキシャル層の厚さと電界強度との関係を示すグラフである。

【図7】4H−SiCの結晶構造のユニットセルを表した模式図である。

【図8】p型ピラー層のストライプ方向を示す図である。

【図9】単位セルの表面の各部と電界強度との関係を示すグラフである。

【図10】基板およびエピタキシャル層の不純物濃度を説明するための図である。

【図11A】図2Aのショットキーバリアダイオードの製造工程の一部を示す図である。

【図11B】図11Aの次の工程を示す図である。

【図11C】図11Bの次の工程を示す図である。

【図11D】図11Cの次の工程を示す図である。

【図11E】図11Dの次の工程を示す図である。

【図11F】図11Eの次の工程を示す図である。

【図11G】図11Fの次の工程を示す図である。

【図12】本発明の第2実施形態に係るショットキーバリアダイオードの断面図である。

【図13】図12のトレンチの拡大図である。

【図14】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、トレンチ構造なしの場合を示す。

【図15】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、矩形トレンチ構造ありの場合を示す。

【図16】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、U字トレンチ構造ありの場合を示す。

【図17】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造ありの場合を示す。

【図18】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造+底面p型層ありの場合を示す。

【図19】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造+側面p型層ありの場合を示す。

【図20】ショットキーバリアダイオードの電流−電圧(I−V)曲線を示すグラフである。

【図21A】図12のショットキーバリアダイオードの製造工程の一部を示す図である。

【図21B】図21Aの次の工程を示す図である。

【図21C】図21Bの次の工程を示す図である。

【図21D】図21Cの次の工程を示す図である。

【図21E】図21Dの次の工程を示す図である。

【図21F】図21Eの次の工程を示す図である。

【図21G】図21Fの次の工程を示す図である。

【図21H】図21Gの次の工程を示す図である。

【図21I】図21Hの次の工程を示す図である。

【図21J】図21Iの次の工程を示す図である。

【図22】図22(a)(b)(c)(d)(e)(f)は、トレンチの断面形状の変形例を示す図であって、図22(a)が第1変形例、図22(b)が第2変形例、図22(c)が第3変形例、図22(d)が第4変形例、図22(e)が第5変形例、図22(f)が第6変形例をそれぞれ示す。

【図23】図2Aのショットキーバリアダイオードの第1変形例を示す図である。

【図24】図2Aのショットキーバリアダイオードの第2変形例を示す図である。

【図25】図2Aのショットキーバリアダイオードの第3変形例を示す図である。

【発明を実施するための形態】

【0028】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

<第1実施形態に係るショットキーバリアダイオードの全体構成>

図1は、本発明の第1実施形態に係るショットキーバリアダイオード1の模式的な平面図である。図2Aは、図1のショットキーバリアダイオード1の断面図であって、図1の切断線II−IIでの切断面を示す。

【0029】

半導体装置としてのショットキーバリアダイオード1は、4H−SiC(絶縁破壊電界が約2.8MV/cmであり、バンドギャップの幅が約3.26eVのワイドバンドギャップ半導体)が採用されたショットキーバリアダイオードであり、たとえば、平面視正方形のチップ状である。チップ状のショットキーバリアダイオード1は、図1の紙面における上下左右方向の長さがそれぞれ数mm程度である。

【0030】

ショットキーバリアダイオード1は、n+型のSiCからなる基板2(オフ角が4°の基板)を備えている。基板2の厚さは、たとえば、50μm〜600μmである。なお、n型不純物としては、たとえば、N(窒素)、P(リン)、As(ひ素)などを使用できる。

基板2の裏面3((000−1)C面)には、その全域を覆うようにオーミック電極としてのカソード電極4が形成されている。カソード電極4は、n型のSiCとオーミック接触する金属(たとえば、Ti/Ni/Ag、Ti/Ni/Au/Ag)からなる。

【0031】

基板2の表面5((0001)Si面)には、半導体層の一例としてのn型エピタキシャル層6が形成されている。

エピタキシャル層6は、バッファ層7と、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10の3層構造のドリフト層とが基板2の表面5からこの順に積層されて形成された構造を有している。バッファ層7は、エピタキシャル層6の裏面11((000−1)C面)を形成しており、基板2の表面5に接している。一方、表面ドリフト層10は、エピタキシャル層6の表面12((0001)Si面)を形成している。

【0032】

エピタキシャル層6の総厚さTは、たとえば、3μm〜100μmである。また、バッファ層7の厚さt1は、たとえば、0.1μm〜1μmである。ベースドリフト層8の厚さt2は、たとえば、2μm〜100μmである。低抵抗ドリフト層9の厚さt3は、たとえば、1μm〜3μmである。表面ドリフト層10の厚さt4は、たとえば、0.2μm〜0.5μmである。

【0033】

エピタキシャル層6の表面12には、エピタキシャル層6の一部を活性領域13として露出させるコンタクトホール14を有し、当該活性領域13を取り囲むフィールド領域15を覆うフィールド絶縁膜16が形成されている。フィールド絶縁膜16は、たとえば、SiO2(酸化シリコン)からなる。また、フィールド絶縁膜16の厚さは、たとえば、0.5μm〜3μmである。

【0034】

エピタキシャル層6には、当該表面12からドリフト層8〜10を貫通して、最深部がバッファ層7とベースドリフト層8との界面に位置するストライプ状のp型ピラー層17が形成されている。

ストライプ状のp型ピラー層17は、ショットキーバリアダイオード1の一組の対辺の対向方向に沿って直線状に延びる複数のp型ピラー層17が、互いに間隔を空けて、活性領域13およびフィールド領域15にわたって平行に配列されることによって形成されている。互いに隣り合うp型ピラー層17の距離WSJは、たとえば、2μm〜20μmである。また、各p型ピラー層17の長手方向に直交する幅WPは、たとえば、0.1μm〜10μmである。また、各p型ピラー層17の深さDSJは、たとえば、3μm〜25μmである。なお、p型ピラー層17を形成するための不純物としては、たとえば、B(ホウ素)、Al(アルミニウム)などを使用できる。

【0035】

p型ピラー層17を形成することによって、エピタキシャル層6には、ストライプ状のp型ピラー層17と、互いに隣り合うp型ピラー層17の間に挟まれ、エピタキシャル層6の導電型が維持されたn型ピラー層18とがエピタキシャル層6の表面12に沿う方向に交互に配列されてスーパージャンクション構造が形成されている。

活性領域13において各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中に位置する電界緩和層19が形成されている。電界緩和層19の深さDR(エピタキシャル層6の表面12から電界緩和層19の最深部までの距離)は、たとえば、1000Å〜10000Åである。

【0036】

これにより、エピタキシャル層6には、互いに隣り合う電界緩和層19で挟まれることによって区画された単位セル20(ラインセル)がストライプ状に形成されている。各単位セル20は、その大半の領域を占めるベース部が低抵抗ドリフト層9により形成され、ベース部に対して表面12側の表層部が表面ドリフト層10により形成されている。

単位セル20を区画する電界緩和層19は、p型ピラー層17の不純物濃度よりも高い不純物濃度を有し、各ドリフト層8〜10よりも高い抵抗を有する層である。たとえば、電界緩和層19のシート抵抗は、1MΩ/□以上である。

【0037】

なお、電界緩和層19は、p型ピラー層17の不純物濃度よりも高い不純物濃度を有するが、高抵抗ではないp型層であってもよい。

電界緩和層19が高抵抗層の場合、たとえば、1×1016cm−3〜5×1020cm−3の濃度で含有されている電界緩和層19の不純物の活性化率を5%未満、好ましくは、0%〜0.1%にすることにより、上記した範囲のシート抵抗は達成されている。なお、不純物の活性化率とは、ショットキーバリアダイオード1の製造工程においてエピタキシャル層6に注入した不純物イオンの全数に対して、活性化した不純物イオンの個数の割合を示している。

【0038】

また、電界緩和層19は、たとえば、図2Bに示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の内側に収まるように、p型ピラー層17よりも幅狭に形成されていてもよいし、図2Cに示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の外側にはみ出すように、p型ピラー層17よりも幅広に形成されていてもよい。電界緩和層19が高抵抗ではないp型層の場合には、図2Bの幅狭形状が好ましく、電界緩和層19が高抵抗層である場合には、図2Cの幅広形状が好ましい。

【0039】

フィールド絶縁膜16上には、アノード電極21が形成されている。アノード電極21は、フィールド絶縁膜16のコンタクトホール14内でエピタキシャル層6に接合された、ショットキー電極の一例としてのショットキーメタル22と、このショットキーメタル22に積層されたコンタクトメタル23との2層構造を有している。

ショットキーメタル22は、各単位セル20の表面12に形成された第1電極の一例としての第1メタル24と、互いに隣り合う電界緩和層19の間に跨り、それらの電界緩和層19で挟まれる単位セル20の表面12の第1メタル24を覆うように形成された第2電極の一例としての第2メタル25とを含んでいる。

【0040】

第1メタル24は、電界緩和層19に隣接する各単位セル20の周縁部26で挟まれた中央部27において、電界緩和層19の長手方向に沿って直線状に形成されている。

第2メタル25は、活性領域13全体を覆うように形成され、フィールド絶縁膜16のコンタクトホール14に埋め込まれている。第2メタル25は、各単位セル20の表面12の周縁部26に接している。また、第2メタル25は、フィールド絶縁膜16におけるコンタクトホール14の周縁部を上から覆うように、当該コンタクトホール14の外方へフランジ状に張り出している。すなわち、フィールド絶縁膜16の周縁部は、エピタキシャル層6(表面ドリフト層10)および第2メタル25により、全周にわたってその上下両側から挟まれている。したがって、エピタキシャル層6におけるショットキー接合の外周領域(すなわち、フィールド領域15の内縁部)は、SiCからなるフィールド絶縁膜16の周縁部により覆われることとなる。

【0041】

コンタクトメタル23は、アノード電極21において、ショットキーバリアダイオード1の最表面に露出して、ボンディングワイヤなどが接合される部分である。コンタクトメタル23は、たとえば、Al(アルミニウム)からなる。また、コンタクトメタル23は、ショットキーメタル22(第2メタル25)と同様に、フィールド絶縁膜16におけるコンタクトホール14の周縁部を上から覆うように、当該コンタクトホール14の外方へフランジ状に張り出している。

【0042】

フィールド領域15において各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、エピタキシャル層6の表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中に位置する高抵抗のガードリング28が形成されている。このガードリング28は、平面視において、フィールド絶縁膜16のコンタクトホール14の内外に跨るように(活性領域13およびフィールド領域15に跨るように)、当該コンタクトホール14の輪郭に沿って環状に形成されている。ガードリング28のエピタキシャル層6の表面12からの深さDGは、たとえば、電界緩和層19と同じ深さ(たとえば、1000Å〜10000Å)である。

【0043】

また、ガードリング28は、電界緩和層19と同様の特性を示す層である。たとえば、電界緩和層19が高抵抗層の場合には、ガードリング28は、当該高抵抗層と同様に、各ドリフト層8〜10よりも高い抵抗を有する層であり、シート抵抗が1MΩ/□以上であり、不純物の活性化率が5%未満(好ましくは、0%〜0.1%)である。

ショットキーバリアダイオード1の最表面には、たとえば窒化シリコン(SiN)からなる表面保護膜29が形成されている。表面保護膜29の中央部には、アノード電極21(コンタクトメタル23)を露出させる開口30が形成されている。ボンディングワイヤなどは、この開口30を介してコンタクトメタル23に接合される。

【0044】

このショットキーバリアダイオード1では、アノード電極21に正電圧、カソード電極4に負電圧が印加される順方向バイアス状態になることにより、カソード電極4からアノード電極21へと、エピタキシャル層6の活性領域13を介して電子(キャリア)が移動して電流が流れる。<スーパージャンクション構造の導入効果>

次に、図3および図4を参照して、エピタキシャル層6にスーパージャンクション構造を形成することによる耐圧の向上効果について説明する。

【0045】

スーパージャンクション構造として、図3のように設計した。図3において、図2Aに示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付している。なお、p型ピラー層17の距離WSJ(n型ピラー層18の幅)は5μm、p型ピラー層17の幅WPは3.5μm、ショットキーメタル22とエピタキシャル層6とのバリアハイトSBは1.4eVとした。また、p型ピラー層17の深さDSJは可変の値とした。

【0046】

そして、図3のアノード−カソード間に逆方向電圧(1200V)を印加したときのエピタキシャル層6内の電界強度分布が、スーパージャンクション構造の有無および深さDSJの違いによって如何に変化するかをシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。結果を図4に示す。

図4に示すように、スーパージャンクション構造が形成されていないショットキーバリアダイオード(従来)では、エピタキシャル層6の裏面11から表面12へ向かうにしたがって電界強度が比例して強くなり、エピタキシャル層6の表面12で最大(1.15×106V/cm程度)となった。

【0047】

これに対し、スーパージャンクション構造が形成されたショットキーバリアダイオード1では、スーパージャンクション構造がない場合に比べて、裏面11から表面12へ向かって電界強度を均一にすることができた。とりわけ、p型ピラー層17の深さDSJが5μm、10μm、15μm、20μmと深くなるほど、その効果が大きかった。たとえば、DSJ=20μmの場合には、電界強度が6.0×105V/cm程度でほぼ一定であった。

【0048】

これらの結果、エピタキシャル層6の不純物濃度および厚さが同条件である下では、スーパージャンクション構造が形成されていない従来構造に比べて耐圧を向上させることができることを確認できた。従って、本実施形態のショットキーバリアダイオード1によれば、従来に比べて、不純物濃度が高くて厚さが小さいエピタキシャル層6でも十分な耐圧を確保できるので、エピタキシャル層6の不純物濃度および厚さを適切に設計することにより、高耐圧を確保できながら、順方向電圧を低減することができることを確認できた。

<電界緩和層19の導入効果>

図5および図6を参照して、エピタキシャル層6に電界緩和層19を形成することによる逆方向リーク電流および順方向電圧の低減効果について説明する。

【0049】

電界緩和層19を有するショットキーバリアダイオードとして、図3の構造のショットキーバリアダイオード1(WSJ=5μm、WP=3.5μm、DSJ=20μm)のエピタキシャル層6の表面12に、アルミニウム(Al)を不純物として含む電界緩和層19(Al層)が形成された構造とした。なお、電界緩和層(Al層)19の深さDRは1μmとし、電界緩和層19の不純物濃度は可変の値とした。

【0050】

そして、図5のアノード−カソード間に逆方向電圧(1200V)を印加したときのエピタキシャル層6内の電界強度分布が、電界緩和層19の有無および電界緩和層19の不純物濃度の違いによって如何に変化するかをシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。結果を図6に示す。

図6に示すように、電界緩和層19が形成されたショットキーバリアダイオード1では、電界緩和層19がない場合に比べて、エピタキシャル層6の表面12での電界強度を低減することができた。とりわけ、電界緩和層19の濃度が1×1016cm−3、3×1016cm−3、1×1017cm−3と高くなるほど、その効果が大きかった。たとえば、濃度=1×1016cm−3の場合には、エピタキシャル層6の表面12での電界強度が6.3×105V/cm程度であったのに対し、濃度=1×1017cm−3の場合には、その電界強度を5.5×105V/cm程度にまで低減することができた。

【0051】

この結果、本実施形態のショットキーバリアダイオード1では、エピタキシャル層6の表面12(単位セル20の表面)に接するアノード電極21(ショットキーメタル22)とエピタキシャル層6との間のバリアハイトを低くしても、降伏電圧に近い逆方向電圧が印加されたときの表面12での電界強度が弱いので、バリアハイトを越える逆方向リーク電流を低減することができることを確認できた。すなわち、逆方向リーク電流を低減できながら、バリアハイトを低くして順方向電圧を低減できることを確認できた。

<p型ピラー層17のストライプ方向とSiC結晶構造との関係>

次に、図7および図8を参照して、p型ピラー層17のストライプ方向とSiC結晶構造との関係について説明する。

【0052】

図7は、4H−SiCの結晶構造のユニットセルを表した模式図である。図8は、p型ピラー層17のストライプ方向を示す図である。なお、図7の下部に示したSiC結晶構造の斜視図については、その横に示したSiC積層構造の4層のうち2層のみを抜き出して示している。また、図8の左側に示した図は、図7のユニットセルを(0001)面の真上から見た図である。

【0053】

本実施形態のショットキーバリアダイオード1に使用されるSiCには、結晶構造の違いにより、3C−SiC、4H−SiC、6H−SiCなどの種類がある。

これらのうち、4H−SiCの結晶構造は、図7および図8に示すように、六方晶系で近似することができ、1つのシリコン原子に対して4つの炭素原子が結合している。4つの炭素原子は、シリコン原子を中央に配置した正四面体の4つの頂点に位置している。これらの4つの炭素原子は、1つのシリコン原子が炭素原子に対して[0001]軸方向に位置し、他の3つの炭素原子がシリコン原子に対して[000−1]軸側に位置している。

【0054】

[0001]軸および[000−1]軸は六角柱の軸方向に沿い、この[0001]軸を法線とする面(六角柱の頂面)が(0001)面(Si面)である。一方、[000−1]軸を法線とする面(六角柱の下面)が(000−1)面(C面)である。

また、[0001]軸に垂直であり、かつ(0001)面の真上から見た場合において六角注の互いに隣り合わない頂点を通る方向がそれぞれ、a1軸[2−1−10]、a2軸[−12−10]およびa3軸[−1−120]である。

【0055】

図8に示すように、a1軸とa2軸との間の頂点を通る方向が[11−20]軸であり、a2軸とa3軸との間の頂点を通る方向が[−2110]軸であり、a3軸とa1軸との間の頂点を通る方向が[1−210]軸である。

六角注の各頂点を通る上記6本の軸の各間において、その両側の各軸に対して30°の角度で傾斜していて、六角注の各側面の法線となる軸がそれぞれ、a1軸と[11−20]軸との間から時計回りに順に、[10−10]軸、[1−100]軸、[0−110]軸、[−1010]軸、[−1100]軸および[01−10]軸である。これらの軸を法線とする各面(六角柱の側面)は、(0001)面および(000−1)面に対して直角な結晶面である。

【0056】

そして、本実施形態では、(0001)面を主面(表面5)とする基板2を用い、その上に(0001)面が主面となるようにエピタキシャル層6を成長させている。また、p型ピラー層17のストライプ方向の例としては、たとえば、[1−100]軸と平行(0°)、[1−100]軸に垂直(90°)、[1−100]軸に対して45°傾斜等の様々なパターンが挙げられる。なお、図8に示したストライプパターンは一例に過ぎず、必要に応じて様々なストライプパターンを採用することができる。

<2つのショットキー電極(第1メタル24および第2メタル25)>

次に、図9を参照して、2つのショットキー電極(第1メタル24および第2メタル25)を設けたことによる逆方向リーク電流および順方向電圧の低減の効率化について説明する。

【0057】

図9は、単位セル20の表面12の各部と電界強度との関係を示すグラフである。

本実施形態のショットキーバリアダイオード1では、前述の<電界緩和層19の導入効果>で示したシミュレーションの結果、図9に示すように、単位セル20の表面12には、相対的に電界強度が高い部分(単位セル20の中央部27)と低い部分(単位セル20の周縁部26)とが存在することが分かった。

【0058】

具体的には、図9に示すように、半導体層の第1部分の一例としての単位セル20の周縁部26には1.0×105V/cm〜1.3×106V/cmの電界強度が分布し、半導体層の第2部分の一例としての単位セル20の中央部27には1.5×106V/cm程度の電界強度が分布している。逆方向電圧印加時の電界強度分布は、単位セル20の中央部27の電界強度(第2電界)が、単位セル20の周縁部26の電界強度(第1電界)に比べて高くなっている。

【0059】

そこで、相対的に高い電界がかかる単位セル20の中央部27には、比較的高い電位障壁(たとえば、1.4eV)を形成するp型ポリシリコンなどを第1メタル24としてショットキー接合させる。なお、電極がポリシリコンのような半導体電極の場合には、ショットキー接合に代えて、互いにバンドギャップの異なる半導体同士のヘテロ接合ということがある。

【0060】

一方、相対的に低い電界がかかる単位セル20の周縁部26には、比較的低い電位障壁(たとえば0.7eV)を形成するアルミニウム(Al)などを第2メタル25としてショットキー接合させる。

これにより、逆方向電圧印加時に相対的に高い電界がかかる単位セル20の中央部27では、第1メタル24(ポリシリコン)とエピタキシャル層6との間の高いショットキー障壁(第2ショットキー障壁)により逆方向リーク電流を抑制することができる。

【0061】

一方、相対的に低い電界がかかる単位セル20の周縁部26では、第2メタル25(アルミニウム)とエピタキシャル層6との間のショットキー障壁の高さを低くしても逆方向リーク電流が当該ショットキー障壁を越えるおそれが少ない。したがって、低いショットキー障壁(第1ショットキー障壁)とすることにより、順方向電圧印加時に低い電圧で優先的に電流を流すことができる。また、この第2メタル25は、コンタクトメタル23を省略することにより、コンタクトメタル23を兼ねることができる。

【0062】

このように、逆方向電圧印加時における単位セル20の電界強度の分布に応じてアノード電極21(ショットキー電極)を適正に選択することにより、逆方向リーク電流および順方向電圧の低減を効率よく行うことができることを確認できた。

<エピタキシャル層6の不純物濃度>

次に、図10を参照して、基板2およびエピタキシャル層6の不純物濃度の大きさについて説明する。

【0063】

図10は、基板2およびエピタキシャル層6の不純物濃度を説明するための図である。

図10に示すように、基板2およびエピタキシャル層6は、いずれもn型不純物を含有するn型SiCからなる。それらの不純物濃度の大小関係は、基板2>バッファ層7>ドリフト層8〜10である。

基板2の濃度は、たとえば、その厚さ方向に沿って5×1018〜5×1019cm−3でほぼ一定である。バッファ層7の濃度は、たとえば、その厚さ方向に沿って、1×1017〜5×1018cm−3で一定または表面5に沿って濃度が薄い。

【0064】

ドリフト層8〜10の濃度は、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10それぞれの界面を境に段階的に変化している。つまり、各界面に対して表面12側の層と裏面11側の層との間に濃度差がある。

ベースドリフト層8の濃度は、たとえば、その厚さ方向に沿って、5×1014〜5×1016cm−3で一定である。なお、ベースドリフト層8の濃度は、図10の破線で示すように、エピタキシャル層6の裏面11から表面12へ向かうにしたがって、約3×1016cm−3から約5×1015cm−3まで連続的に減少していてもよい。

【0065】

低抵抗ドリフト層9の濃度は、ベースドリフト層8の濃度よりも高く、たとえば、その厚さ方向に沿って、5×1015〜5×1017cm−3で一定である。なお、低抵抗ドリフト層9の濃度は、図10の破線で示すように、エピタキシャル層6の裏面11から表面12へ向かうにしたがって、約3×1017cm−3から約1×1016cm−3まで連続的に減少していてもよい。

【0066】

表面ドリフト層10の濃度は、ベースドリフト層8および低抵抗ドリフト層9の濃度よりも低く、たとえば、その厚さ方向に沿って、5×1014〜1×1016cm−3で一定である。

図2Aに示すように、ストライプ状の電界緩和層19で区画された単位セル20(ラインセル)では電流を流すことができる領域(電流経路)が、互いに隣り合う電界緩和層19の距離(つまり、p型ピラー層17の距離WSJ)に制約されるので、エピタキシャル層6における単位セル20を形成する部分の不純物濃度が低いと、単位セル20の抵抗値が高くなるおそれがある。

【0067】

そこで図10に示すように、単位セル20のベース部を形成する低抵抗ドリフト層9の濃度をベースドリフト層8よりも高くすることにより、電流経路が電界緩和層19の距離WSJに制約されていても、比較的高い濃度を有する低抵抗ドリフト層9により単位セル20の抵抗値の上昇を抑制することができる。その結果、単位セル20の低抵抗化を図ることができる。

【0068】

一方、ショットキーメタル22に接する単位セル20の表層部には、比較的低い濃度を有する表面ドリフト層10を設けることにより、逆方向電圧印加時にエピタキシャル層6の表面12にかかる電界強度を低減することができる。その結果、逆方向リーク電流を一層低減することができる。

<ショットキーバリアダイオード1(第1実施形態)の製造方法>

次に、図11A〜図11Gを参照して、図2Aのショットキーバリアダイオード1の製造方法について説明する。

【0069】

まず、図11Aに示すように、基板2の上に、バッファ層7、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10をこの順にエピタキシャル成長させる。

次に、図11Bに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク31を形成する。ハードマスク31の厚さは、好ましくは、1.5μm〜10μmである。次に、ハードマスク31をパターニングした後、当該ハードマスク31を介して、エピタキシャル層6をドライエッチングする。これにより、バッファ層7に達するストライプ状のトレンチ32を形成する。トレンチ32の深さは、p型ピラー層17の深さDSJに合わせて適宜設定する。また、トレンチ32は、深さDSJに応じて、ハードマスクを形成する工程、当該ハードマスクを用いてドライエッチングする工程およびドライエッチング後に当該ハードマスクを除去する工程を複数回繰り返すことにより形成してもよい。

【0070】

次に、ハードマスク31を除去した後、図11Cに示すように、そのトレンチ32内部からエピタキシャル層6の表面12が覆われるまで、p型のSiC層33をエピタキシャル成長させる。

次に、図11Dに示すように、エピタキシャル層6の表面12を覆うトレンチ32外のSiC層33を、たとえばエッチバックにより除去する。これにより、トレンチ32に埋め込まれたp型ピラー層17が形成され、同時に、互いに隣り合うp型ピラー層17の間にn型ピラー層18が形成される。

【0071】

次に、図11Eに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク34を形成する。ハードマスク34の厚さは、好ましくは、1.5μm〜3μmである。次に、ハードマスク34をパターニングした後、当該ハードマスク34を介して、エピタキシャル層6の表面12へ向かってp型不純物(ホウ素イオン)を注入(1段注入)する。これにより、エピタキシャル層6の表層部に、ホウ素イオンが高濃度に注入された高濃度不純物層35が形成される。なお、イオン注入の際に表面12を覆うマスクとしては、ハードマスク34に代えてフォトレジストを用いてもよい。

【0072】

次に、図11Fに示すように、ハードマスク34を剥離し、1500℃未満の温度、好ましくは、1100℃〜1400℃の温度でエピタキシャル層6をアニール処理する。これにより、高濃度不純物層35が電界緩和層19(高抵抗層)およびガードリング28に変質して、各p型ピラー層17の上端部に電界緩和層19が形成され、同時にガードリング28が形成される。このようなホウ素イオンのイオン注入法では、ホウ素イオンが比較的軽いイオンであるため、表面12から深い位置にまで簡単に注入することができる。そのため、電界緩和層19の深さDRを、エピタキシャル層6の表面12に対して浅い位置から深い位置までの幅広い範囲で簡単に制御することができる。

【0073】

なお、図11Eおよび図11Fでは、高抵抗層としての電界緩和層19の形成方法を示しているが、高抵抗層ではないp型層としての電界緩和層19を形成するには、たとえば、図11Eの工程において、ハードマスク34を介してエピタキシャル層6の表面12へ向かってp型不純物(アルミニウムイオン)を注入する。次に、図11Fの工程において、ハードマスク34を剥離し、1500℃〜1800℃の温度でエピタキシャル層6をアニール処理する。これにより、当該p型層を形成することができる。

【0074】

その後、図11Gに示すように、フィールド絶縁膜16、アノード電極21、表面保護膜29、カソード電極4等を形成する。

以上の工程を経て、図2Aのショットキーバリアダイオード1が得られる。

<第2実施形態に係るショットキーバリアダイオードの全体構成>

図12は、本発明の第2実施形態に係るショットキーバリアダイオード41の断面図である。また、図13は、図12のトレンチ42の拡大図である。図12において、図2Aに示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付し、その説明を省略する。

【0075】

第2実施形態のショットキーバリアダイオード41の活性領域13において、各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中部に達するトレンチ42が形成されている。トレンチ42は、その長手方向に直交する幅方向に沿って切断したときの断面視が逆台形状のトレンチであり、p型ピラー層17の上端部に沿って直線状に延びている。

【0076】

これにより、エピタキシャル層6には、互いに隣り合う台形トレンチ42で挟まれることによって区画された単位セル20(ラインセル)がストライプ状に形成されている。

各台形トレンチ42は、エピタキシャル層6の表面12に対して平行な底面43と、当該底面43に対して傾斜する側面44とによって区画されている。側面44の傾斜角θ1は、たとえば、45°〜85°である。また、各台形トレンチ42の深さ(エピタキシャル層6の表面12から台形トレンチ42の底面43までの距離)は、たとえば、0.3Å〜15000Åである。また、各台形トレンチ42の長手方向に直交する幅WT(最深部の幅)は、0.3μm〜10μmである。

【0077】

また、図13に示すように、各台形トレンチ42の側面44と底面43とが交わって形成されたエッジ部45は、台形トレンチ42の外方へ向かって湾曲する形状に形成されており、各台形トレンチ42の底部は断面視U字状に形成されている。このような形状のエッジ部45の内面(湾曲面)の曲率半径Rは、下記式(1)を満たす。

0.01L<R<10L・・・(1)

式(1)において、Lはトレンチ42の幅方向に沿って対向するエッジ部45間の直線距離を示している(単位は、μm、nm、m等、長さの単位であれば特に制限されない)。具体的には、エピタキシャル層6の表面12に対して平行な底面43の幅であって、トレンチ42の幅WTからエッジ部45の幅を差し引いた値である。

【0078】

また、エッジ部45の曲率半径Rは、0.02L<R<1L・・・(2)を満たすことが好ましい。

曲率半径Rは、たとえば、台形トレンチ42の断面をSEM(Scanning Electron Microscope:走査型電子顕微鏡)で撮影し、得られたSEM画像のエッジ部45の曲率を測定することにより求めることができる。

【0079】

台形トレンチ42の底面43および側面44には、台形トレンチ42の内面に沿って電界緩和部としてのp型層46が形成されている。p型層46は、台形トレンチ42の底面43からエッジ部45を経て台形トレンチ42の開口端に至るまで形成されている。また、p型層46は、たとえば、図13に示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の内側に収まるように、p型ピラー層17よりも幅狭に形成されている。また、p型層46は、n型のエピタキシャル層6との間にpn接合部を形成している。これにより、ショットキーバリアダイオード41には、p型層46およびn型エピタキシャル層6(低抵抗ドリフト層9)によって構成されるpnダイオード47が内蔵されることとなる。

【0080】

p型層46の厚さ(台形トレンチ42の内面からの深さ)は、図13に示すように、台形トレンチ42の深さ方向(エピタキシャル層6の表面12に垂直な方向)に沿って測定される台形トレンチ42の底面43からの第1厚さt5が、台形トレンチ42の幅方向(エピタキシャル層6の表面12に平行な方向)に沿って測定される台形トレンチ42の側面44からの第2厚さt6よりも大きい。具体的には、第1厚さt5は、たとえば、0.3μm〜0.7μmであり、第2厚さt6は、たとえば、0.1μm〜0.5μmである。

【0081】

また、p型層46には、p型層46の他の部分よりも高濃度に不純物が注入されたp+型のコンタクト層48が、台形トレンチ42の底面43の一部に形成されている。たとえば、コンタクト層48の不純物濃度は、1×1020〜1×1021cm−3であり、コンタクト層48を除くp型層46の他の部分の不純物濃度は、1×1017〜5×1018cm−3である。

【0082】

コンタクト層48は、台形トレンチ42の長手方向に沿って直線状に形成されており、台形トレンチ42の底面43からp型層46の深さ方向途中までの深さ(たとえば、0.05μm〜0.2μm)を有している。

また、ショットキーバリアダイオード41のフィールド領域15において、各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中部に達する環状トレンチ69が形成されている。環状トレンチ69は、活性領域13を取り囲むように形成されている。

【0083】

また、環状トレンチ69の底面70および側面71には、環状トレンチ69の内面に露出するように当該内面に沿ってガードリング72が形成されている。ガードリング72は、p型層46と同一の工程で形成されるものであって、p型層46と同じ不純物濃度(たとえば、1×1017〜5×1018cm−3)および厚さを有している。

なお、ガードリング72は、その外周部に、不純物濃度がp型層46(ガードリング72の残りの部分)よりも低く、p型ピラー層17よりも高い部分を有していてもよい。

<トレンチ42構造の導入効果>

次に、図14〜図19を参照して、エピタキシャル層6に台形トレンチ42およびp型層46を形成することによる逆方向リーク電流および順方向電圧を低減効果について説明する。なお、図15のトレンチは矩形トレンチ42´であり、図16のトレンチはU字トレンチ42´´である。

【0084】

図14〜図19は、逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、図14がトレンチ構造なしの場合、図15が矩形トレンチ構造ありの場合、図16がU字トレンチ構造(θ1=90°、R=0.125Lまたは1/(1×107)(m))ありの場合、図17が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))ありの場合、図18が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))+底面p型層ありの場合、図19が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))+側面p型層ありの場合をそれぞれ示す。図14〜図19において、図12および図13に示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付している。

【0085】

まず、図14〜図19の構造を、以下のように設計した。

・n+型基板2:濃度が1×1019cm−3 厚さが1μm

・n−型エピタキシャル層6:濃度が1×1016cm−3 厚さが5μm

・トレンチ42,42´,42´´:深さが1.05μm

・トレンチ42,42´,42´´のエッジ部45の曲率半径R:

・p型層46:濃度が1×1018cm−3

そして、図14〜図19それぞれの構造を有するショットキーバリアダイオード41のアノード−カソード間に逆方向電圧(600V)を印加したときの、エピタキシャル層6内の電界強度分布をシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。

【0086】

図14に示すように、いかなる形状のトレンチ構造も形成されておらず、エピタキシャル層6の表面12が平らなショットキーバリアダイオードでは、エピタキシャル層6の裏面11から表面12へ向かうにしたがって電界強度が強くなり、エピタキシャル層6の表面12で最大(1.5×106V/cm程度)であった。

また、図15に示すように、エッジ部45が鋭利な形状の矩形トレンチ42´構造が形成されたショットキーバリアダイオードでは、矩形トレンチ42´構造の形成により、互いに隣り合う矩形トレンチ42´で挟まれる部分(単位セル20)での電界強度を弱めることができた。たとえば、単位セル20の中央部27の電界強度を、9×105V/cm程度にまで弱めることができた。

【0087】

また、図16および図17に示すように、U字トレンチ42´´および台形トレンチ42構造が形成され、これらのトレンチ42,42´´の内面にp型層46が形成されていないショットキーバリアダイオードでは、トレンチ42,42´´構造の形成により、互いに隣り合う台形トレンチ42で挟まれる部分(単位セル20)での電界強度が弱められており、さらに、電界強度が最大となる部分が台形トレンチ42の底面43全体にシフトしていた。具体的には、単位セル20の中央部27の電界強度が9×105V/cm程度、単位セル20の周縁部26の電界強度が3×105V/cm程度にまで弱められており、台形トレンチ42の底面43全体の電界強度が1.5×106V/cm程度で最大であった。

【0088】

また、図18に示すように、台形トレンチ42の底面43およびエッジ部45にp型層46が形成されたショットキーバリアダイオードでは、台形トレンチ42の底面43での電界強度が弱められており、電界強度が最大となる部分が台形トレンチ42の側面44にシフトしていた。具体的には、台形トレンチ42の底面43の電界強度が3×105V/cm以下にまで弱められており、台形トレンチ42の側面44の下部の電界強度が1.5×106V/cmで最大であった。

【0089】

さらに、図12と同様の構成である図19のショットキーバリアダイオードでは、台形トレンチ42の側面44にもp型層46が形成されていることにより、台形トレンチ42の側面44での電界強度が弱められており、電界集中部分を台形トレンチ42の内面から遠ざけていることを確認できた。具体的には、台形トレンチ42の側面44の電界強度が3×105V/cm以下にまで弱められており、台形トレンチ42の内面の周囲には、電界強度が1.5×106V/cmとなる領域がなかった。

【0090】

これらの結果、とりわけ図12のショットキーバリアダイオード41では、ショットキーバリアダイオード41全体としての逆方向リーク電流を確実に低減できることを確認できた。すなわち、図12の構造を有するショットキーバリアダイオード41では、降伏電圧に近い逆方向電圧を印加しても逆方向リーク電流を確実に低減できるので、ワイドバンドギャップ半導体の耐圧性能を十分に活かすことができる。

【0091】

しかも、後述する図21Fの工程のように、台形トレンチ42をドライエッチングで形成する場合、台形トレンチ42の側面44がエッチング時にダメージを受け、当該側面44とアノード電極21との間にショットキー障壁を設計通りに形成できない場合がある。そこで本実施形態のショットキーバリアダイオード41では、エッチング時にハードマスク52(後述)で覆われて保護された(後述する図21Eの工程)エピタキシャル層6の表面12を主としてショットキー界面とし、ダメージを受けた側面44にはp型層46を形成している。これにより、台形トレンチ42の側面44を有効利用することができる。また、台形トレンチ42の側面44における電界強度の高い部分に障壁の高いpn接合を形成し、リーク電流を低減することができる。

<SiC−pnダイオード47内蔵の効果>

次に、図20を参照して、p型層46にコンタクト層48を形成して、エピタキシャル層6にpnダイオード47を内蔵させたときの効果について説明する。

【0092】

図20は、ショットキーバリアダイオード41の電流−電圧(I−V)曲線を示すグラフである。

図12の構造のショットキーバリアダイオード41に対して、順方向電圧を1V〜7Vまで変化させながら印加することにより通電試験を行った。そして、印加電圧を1V〜7Vまで変化させたときのショットキーバリアダイオード41のpn接合部に流れる電流の変化量を評価した。

【0093】

一方、p型層46のコンタクト層48を形成していないこと以外は、図12の構造と同じショットキーバリアダイオード41に対して、上記と同様の通電試験を行い、pn接合部に流れる電流の変化量を評価した。

図20に示すように、p型層46にコンタクト層48が形成されていないpn接合部では、印加電圧が4Vを超えるあたりから電流がほとんど増加せずにほぼ一定であった。

【0094】

これに対し、p型層46にコンタクト層48が形成され、pnダイオード47が内蔵されたショットキーバリアダイオード41では、印加電圧が4Vを超えるあたりからの電流の増加割合が、4V以下までの増加割合に比べて急激に増えていた。

これにより、図12において、ショットキーバリアダイオード41に並列に設けられたpnダイオード47にアノード電極21(ショットキー電極)をオーミック接合させておけば、ショットキーバリアダイオード41に大きなサージ電流が流れても、内蔵pnダイオード47をオンさせて、当該サージ電流の一部を内蔵pnダイオード47に流すことができることを確認できた。その結果、ショットキーバリアダイオード41に流れるサージ電流を低減できるので、サージ電流によるショットキーバリアダイオード41の熱破壊を防止することができることを確認できた。

<ショットキーバリアダイオード41(第2実施形態)の製造方法>

次に、図21A〜図21Jを参照して、図12のショットキーバリアダイオード41の製造方法について説明する。

【0095】

まず、図21Aに示すように、基板2の上に、バッファ層7、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10をこの順にエピタキシャル成長させる。

次に、図21Bに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク49を形成する。ハードマスク49の厚さは、好ましくは、1.5μm〜10μmである。次に、ハードマスク49をパターニングした後、当該ハードマスク49を介して、エピタキシャル層6をドライエッチングする。これにより、バッファ層7に達するストライプ状のトレンチ50を形成する。トレンチ50の深さは、p型ピラー層17の深さDSJに合わせて適宜設定する。また、トレンチ50は、深さDSJに応じて、ハードマスクを形成する工程、当該ハードマスクを用いてドライエッチングする工程およびドライエッチング後に当該ハードマスクを除去する工程を複数回繰り返すことにより形成してもよい。

【0096】

次に、ハードマスク49を除去した後、図21Cに示すように、そのトレンチ50内部からエピタキシャル層6の表面12が覆われるまで、p型のSiC層51をエピタキシャル成長させる。

次に、図21Dに示すように、エピタキシャル層6の表面12を覆うトレンチ50外のSiC層51を、たとえばエッチバックにより除去する。これにより、トレンチ50に埋め込まれたp型ピラー層17が形成され、同時に、互いに隣り合うp型ピラー層17の間にn型ピラー層18が形成される。

【0097】

次に、図21Eに示すように、たとえばCVD法より、エピタキシャル層6の表面12にSiO2からなるハードマスク52を形成する。ハードマスク52の厚さは、好ましくは、1μm〜3μmである。次に、ハードマスク52をパターニングする。このとき、ハードマスク52の厚さに対してエッチング量(厚さ)が1〜1.5倍となるようにエッチング条件を設定する。具体的には、ハードマスク52の厚さが1μm〜3μmである場合には、エッチング量が1μm〜4.5μmとなるように、エッチング条件(ガス種、エッチング温度)を設定する。これにより、エピタキシャル層6に対するオーバーエッチング量を一般的な量よりも少なくすることができるので、エッチング後のハードマスク52の開口53の側面下部に、エピタキシャル層6の表面12に対して角度θ1(100°〜170°>90°)で傾斜するエッジ部54を形成することができる。

【0098】

次に、図21Fに示すように、当該ハードマスク52を介して、エピタキシャル層6を表面12から最深部が低抵抗ドリフト層9の途中部に達する深さまでドライエッチングすることにより、各p型層46の上端部に台形トレンチ42および環状トレンチ69を同時に形成する。このときのエッチング条件は、ガス種:O2+SF6+HBr、バイアス:20W〜100W、装置内圧力:1Pa〜10Paとする。これにより、台形トレンチ42のエッジ部45を湾曲する形状に形成することができる。また、ハードマスク52の開口53の側面下部に所定角度θ1のエッジ部54が形成されているので、台形トレンチ42の側面44を、台形トレンチ42の底面43に対して角度θ1で傾斜させることができる。

【0099】

次に、図21Gに示すように、台形トレンチ42の形成に使用したハードマスク52を残存させたまま、環状トレンチ69におけるガードリング72を形成すべき部分以外の部分を覆うレジスト73を形成する。そして、当該レジスト73およびハードマスク52を介して、台形トレンチ42へ向かってp型不純物(たとえば、アルミニウム(Al))を注入する。p型不純物のドーピングは、たとえば、エピタキシャル層6の表面12に対して深い位置から順に、注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法により達成される。

【0100】

本実施形態では、たとえば、5段階にわたって注入する。各段階の注入エネルギ(keV)およびドーズ量(cm−2)は、1段目:380keV 2.0×1013cm−2、2段目:260keV 1.5×1013cm−2、3段目:160keV 1.0×1013cm−2、4段目:60keV 2.0×1015cm−2、5段目:30keV 1.0×1015cm−2である。

【0101】

次に、図21Hに示すように、所定パターンのハードマスク55を形成し、このハードマスク55を介して、台形トレンチ42へ向かってp型不純物(たとえば、アルミニウム(Al))を注入する。p型不純物のドーピングは、図21Gの工程と同様に、エピタキシャル層6の表面12に対して深い位置から順に、注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法により達成される。本実施形態では、前述と同じ条件の5段階注入を採用する。注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法を採用することにより、p型層46およびコンタクト層48に対してオーミックコンタクトを形成しやすくすることができる。

【0102】

不純物のドーピングの後、図21Iに示すように、たとえば、1700℃でアニール処理することにより、p型層46、コンタクト層48およびガードリング72が同時に形成される。

その後、図21Jに示すように、フィールド絶縁膜16、アノード電極21、表面保護膜29、カソード電極4等を形成する。

【0103】

以上の工程を経て、図12のショットキーバリアダイオード41が得られる。

このような形成方法によれば、台形トレンチ42の形成時に使用したハードマスク52を用いてイオン注入するので、p型層46を形成するにあたって、マスクを形成する工程を増やす必要がない。

また、ハードマスク52の厚さを適切に調整することにより、設計通りの台形トレンチ42を精密に形成できるとともに、イオン注入の際には、台形トレンチ42以外の箇所(たとえば、単位セル20の頂部)に不純物が注入されることを防止することができる。よって、アノード電極21とのショットキー接合のためのn型の領域を確保することができる。

【0104】

しかも、台形トレンチ42では、底面43だけでなく側面44の全部も台形トレンチ42の開放端に対して対向することとなる。そのため、台形トレンチ42を介してp型不純物をエピタキシャル層6に注入する場合に、台形トレンチ42の開放端から台形トレンチ42内に入射した不純物を、台形トレンチ42の側面44に確実に当てることができる。その結果、p型層46を容易に形成することができる。

<トレンチの断面形状の変形例>

次に、図22(a)〜図22(f)を参照して、台形トレンチ42の断面形状の変形例について説明する。

【0105】

図22(a)〜図22(f)は、トレンチの断面形状の変形例を示す図であって、図22(a)が第1変形例、図22(b)が第2変形例、図22(c)が第3変形例、図22(d)が第4変形例、図22(e)が第5変形例、図22(f)が第6変形例をそれぞれ示す。

台形トレンチ42では、たとえば、図22(a)に示すように、コンタクト層48が、p型層46と同様に、底面43からエッジ部45を経て台形トレンチ42の開口端に至るまで、台形トレンチ42の内面全体にわたって形成されていてもよい。

【0106】

また、図12および図13の説明では、台形トレンチ42の断面形状として、各台形トレンチ42の側面44が底面43に対して角度θ1(>90°)で傾斜する場合のみを例に挙げたが、トレンチの断面形状は、これに限らない。

たとえば、台形トレンチ42は、側面44の全部が傾斜している必要はなく、たとえば、図22(b)(c)の選択的台形トレンチ56のように、側面57の一部(側面の下部58)が選択的に台形(テーパ形状)になっており、側面57の他の部分(側面の上部59)は、底面60に対して90°の角度を形成していてもよい。この場合、p型層46は、選択的台形トレンチ56の底面60からエッジ部61を経て側面の下部58(台形部)のみに形成されている。また、コンタクト層48は、図22(b)に示すように、選択的台形トレンチ56の底面60のみに形成されていてもよいし、図22(c)に示すように、p型層46と同様に、選択的台形トレンチ56の底面60からエッジ部61を経て側面の下部58の上端に至るまで形成されていてもよい。

【0107】

そして、図22(b)(c)の構造においても、側面の下部58が選択的台形トレンチ56の開放端に対して対向することとなるので、p型層46を容易に形成することができる。

また、トレンチは、側面が傾斜している必要はなく、たとえば、図22(d)(e)(f)のU字トレンチ62のように、底面63に対して側面64が90°(垂直)であってもよい。この場合、p型層46は、図22(d)(e)に示すように、U字トレンチ62の底面63からエッジ部65を経てU字トレンチ62の開口端に至るまで形成されていてもよいし、図22(f)に示すように、U字トレンチ62の底面63およびエッジ部65のみに形成されていてもよい。また、コンタクト層48は、図22(d)(f)に示すように、U字トレンチ62の底面63のみに形成されていてもよいし、図22(e)に示すように、p型層46と同様に、U字トレンチ62の底面63からエッジ部65を経てU字トレンチ62の開口端に至るまで形成されていてもよい。

【0108】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、図2Aのショットキーバリアダイオード1において、p型ピラー層17は、図23に示すように、その最深部がバッファ層7の厚さ方向途中に位置していてもよいし、図24に示すように、バッファ層7に対して間隔が空くように位置していてもよい。

また、エピタキシャル層6は、図25に示すように、その表面12に沿ってp型ピラー層17を横切る方向にn型の中間層66をさらに含んでいてもよい。これにより、p型ピラー層17は、中間層66に対してエピタキシャル層6の表面12側の上側部分67と、エピタキシャル層6の裏面11側の下側部分68とに分割されていてもよい。なお、図23〜図25の変形例については、図12のショットキーバリアダイオード41にも採用することができる。

【0109】

また、前述のショットキーバリアダイオード1,41の各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、ショットキーバリアダイオード1,41において、p型の部分がn型であり、n型の部分がp型であってもよい。

また、エピタキシャル層6は、SiCからなるエピタキシャル層に限らず、SiC以外のワイドバンドギャップ半導体、たとえば絶縁破壊電界が2MV/cmよりも大きい半導体であって、具体的には、GaN(絶縁破壊電界が約3MV/cmであり、バンドギャップの幅が約3.42eV)、ダイヤモンド(絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約5.47eV)などであってもよい。

【0110】

また、p型ピラー層17の平面形状は、ストライプ状である必要はなく、たとえば、行列状、千鳥状であってもよい。ただし、ストライプ状のp型ピラー層17であれば、p型ピラー層17を形成するときのトレンチ32の側面の面方位が行列状および千鳥状の場合に比べて少なくなり(4面→2面になる)、注入するp型不純物の濃度を制御し易いので好ましい。

【0111】

また、アノード電極21としては、たとえば、前述のアルミニウム、ポリシリコンの他、たとえば、モリブデン(Mo)、チタン(Ti)などを使用することにより、エピタキシャル層6に対してショットキー接合(ヘテロ接合)させることができる。

また、電界緩和層19を形成するためのp型不純物としては、たとえば、Al(アルミニウム)などを使用することもできる。

【0112】

本発明の半導体装置(半導体パワーデバイス)は、たとえば、電気自動車(ハイブリッド車を含む)、電車、産業用ロボットなどの動力源として利用される電動モータを駆動するための駆動回路を構成するインバータ回路に用いられるパワーモジュールに組み込むことができる。また、太陽電池、風力発電機その他の発電装置(とくに自家発電装置)が発生する電力を商用電源の電力と整合するように変換するインバータ回路に用いられるパワーモジュールにも組み込むことができる。

【0113】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0114】

1 ショットキーバリアダイオード

2 基板

3 (基板の)裏面

4 カソード電極

5 (基板の)表面

6 エピタキシャル層

7 バッファ層

8 ベースドリフト層

9 低抵抗ドリフト層

10 表面ドリフト層

11 (エピタキシャル層の)裏面

12 (エピタキシャル層の)表面

13 活性領域

14 コンタクトホール

15 フィールド領域

16 フィールド絶縁膜

17 p型ピラー層

18 n型ピラー層

19 電界緩和層

20 単位セル

21 アノード電極

22 ショットキーメタル

23 コンタクトメタル

24 第1メタル

25 第2メタル

26 (単位セルの)周縁部

27 (単位セルの)中央部

28 ガードリング

29 表面保護膜

30 開口

31 ハードマスク

32 トレンチ

33 SiC層

34 ハードマスク

35 高濃度不純物層

41 ショットキーバリアダイオード

42 台形トレンチ

43 (トレンチの)底面

44 (トレンチの)側面

45 (トレンチの)エッジ部

46 p型層

47 pnダイオード

48 コンタクト層

49 ハードマスク

50 トレンチ

51 SiC層

52 ハードマスク

53 (ハードマスクの)開口

54 (ハードマスクの)エッジ部

55 ハードマスク

56 選択的台形トレンチ

57 (選択的台形トレンチの)側面

58 (選択的台形トレンチの)側面の下部

59 (選択的台形トレンチの)側面の上部

60 (選択的台形トレンチの)底面

61 (選択的台形トレンチの)エッジ部

62 U字トレンチ

63 (U字トレンチの)底面

64 (U字トレンチの)側面

65 (U字トレンチの)エッジ部

66 中間層

67 (p型ピラー層の)上側部分

68 (p型ピラー層の)下側部分

69 環状トレンチ

70 (環状トレンチの)底面

71 (環状トレンチの)側面

72 ガードリング

73 レジスト

【技術分野】

【0001】

本発明は、ワイドバンドギャップ半導体からなるショットキーバリアダイオードを備える半導体装置に関する。

【背景技術】

【0002】

従来、モータ制御システム、電力変換システムなど、各種パワーエレクトロニクス分野におけるシステムに主として使用される半導体装置(半導体パワーデバイス)が注目されている。

たとえば、特許文献1は、SiCが採用されたショットキーバリアダイオードを開示している。当該ショットキーバリアダイオードは、n型4H−SiCバルク基板と、バルク基板上に成長したn型のエピタキシャル層と、エピタキシャル層の表面に形成され、エピタキシャル層の表面を部分的に露出させる酸化膜と、酸化膜の開口内に形成され、エピタキシャル層に対してショットキー接合するショットキー電極とを備えている。

【0003】

また、特許文献1は、SiCが採用された縦型MIS電界効果トランジスタを開示している。当該縦型MIS電界効果トランジスタは、n型4H−SiCバルク基板と、バルク基板上に成長したn型のエピタキシャル層と、エピタキシャル層の表層部に形成されたn型不純物領域(ソース領域)と、当該n型不純物領域の両サイドに隣接して形成されたp型ウェル領域と、エピタキシャル層の表面に形成されたゲート酸化膜と、ゲート酸化膜を介してp型ウェル領域に対向するゲート電極とを備えている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−79339号公報

【特許文献2】特開2011−9797号公報

【発明の概要】

【課題を解決するための手段】

【0005】

本発明の半導体装置は、表面および裏面を有する第1導電型のワイドバンドギャップ半導体からなる半導体層と、前記半導体層の前記表面に接するように形成されたショットキー電極とを含み、前記半導体層には、前記表面に沿う方向に互いに間隔を空けて配列され、それぞれが前記表面から前記裏面へ向かって前記半導体層の厚さ方向に延びる柱状であり、前記半導体層の第1導電型の他の部分と協働して前記半導体層にスーパージャンクション構造を形成する第2導電型の複数のピラー層と、前記表面の近傍に選択的に形成され、前記表面における電界強度を緩和するための電界緩和部とが形成されている。

【0006】

本発明の半導体装置によれば、高耐圧を確保できながら、逆方向リーク電流および順方向電圧(VF:Forward Voltage)の低減を達成することができる。

半導体装置の耐圧は、半導体層の不純物濃度や厚さに関係しており、半導体層の不純物濃度を低くしたり、厚さを大きくしたりすると向上する傾向がある。

一方、半導体装置の順方向電圧は、半導体層の不純物濃度を高くしたり厚さを小さくしたりしてオン抵抗を低減するか、またはショットキー電極と半導体層との間のショットキー障壁の高さ(バリアハイト)を低くすると低減する傾向がある。つまり、半導体層の不純物濃度および厚さに関しては、耐圧の向上および順方向電圧の低減は背反の関係にある。

【0007】

そこで、本発明の半導体装置によれば、半導体層の厚さ方向にそれぞれ延びる第2導電型ピラー層と、半導体層の第1導電型の他の部分とが協働して、前記半導体層にスーパージャンクション構造が形成されている。このスーパージャンクション構造により、半導体層におけるピラー層との界面に沿う方向(つまり、半導体層の厚さ方向)に当該界面全体に空乏層を広げることができる。これにより、半導体層中の電界強度を均一にすることができる。その結果、半導体層の不純物濃度および厚さが同条件である下では、スーパージャンクション構造が形成されていない半導体装置に比べて耐圧を向上させることができる。従って、従来に比べて、不純物濃度が高くて厚さが小さい半導体層でも十分な耐圧を確保できるので、半導体層の不純物濃度および厚さを適切に設計することにより、高耐圧を確保できながら、順方向電圧を低減することができる。

【0008】

さらに、本発明の半導体装置によれば、半導体層の表面近傍に電界緩和部が形成されており、半導体層の表面における電界強度を緩和することができる。そのため、ショットキー電極と半導体層との間のバリアハイトを低くしても、逆方向リーク電流を低減することができる。その結果、逆方向リーク電流を低減できながら、バリアハイトを低くして順方向電圧を低減することができる。

【0009】

なお、本発明においてショットキー電極とは、半導体層との間にショットキー障壁を形成する金属電極、半導体層のバンドギャップとは異なるバンドギャップを有する異種半導体からなり、半導体層に対してヘテロ接合(バンドギャップ差を利用して半導体層との間に電位障壁を形成する接合)する半導体電極のいずれをも含む概念である。以下、この項においては、ショットキー接合およびヘテロ接合を総称して「ショットキー接合」とし、ショットキー障壁およびヘテロ接合により形成される電位障壁(ヘテロ障壁)を総称して「ショットキー障壁」とし、金属電極および半導体電極を総称して「ショットキー電極」とする。

【0010】

また、本発明の半導体装置では、前記電界緩和部は、前記ピラー層の上端部に形成されていることが好ましい。

また、本発明の半導体装置では、前記電界緩和部は、前記半導体層の前記表面に前記半導体層の一部を利用して形成され、前記ピラー層よりも不純物濃度の高い第2導電型を示す、電界緩和層を含んでいてもよい。

【0011】

電界緩和層は、前記半導体層の残りの部分よりも高い抵抗を有する高抵抗層を含んでいてもよい。その場合、前記高抵抗層は、前記半導体層の前記表面から不純物イオンを注入した後、1500℃未満のアニール処理をすることによって形成されることが好ましい。

この構成によれば、アニール処理の際のワイドバンドギャップ半導体の昇華量を低減することができる。その結果、半導体層の表面の平坦性を良好に維持することができる。

【0012】

なお、この1500℃未満のアニール処理とは、注入された不純物イオンの衝突によりワイドバンドギャップ半導体の結晶構造に生じた欠陥を回復させるが(結晶性回復)、注入された不純物イオンを活性化させない程度のアニール処理のことを意味している。

また、本発明の半導体装置では、前記高抵抗層の不純物の活性化率は、5%未満であることが好ましい。また、前記高抵抗層のシート抵抗は、1MΩ/□以上であることが好ましい。

【0013】

また、本発明の半導体装置では、前記電界緩和部は、前記半導体層の前記表面から掘り下がったトレンチを含んでいてもよい。

その場合、前記トレンチの側面と底面とが交わって形成されたトレンチのエッジ部は、下記式(1)を満たす曲率半径Rを有することが好ましい。

0.01L<R<10L・・・(1)

(ただし、式(1)において、Lはトレンチの幅方向に沿って対向するエッジ部間の直線距離を示している。)

この構成によれば、トレンチのエッジ部に集中する電界を緩和して、耐圧を向上させることができる。

【0014】

また、本発明の半導体装置では、前記電界緩和部は、前記トレンチの前記底面および前記エッジ部に前記半導体層の一部を利用して形成された第2導電型の底部緩和層をさらに含むことが好ましく、前記底部緩和層と一体的であり、前記トレンチの前記側面に前記半導体層の一部を利用して形成された第2導電型の側部緩和層をさらに含むことがさらに好ましい。この場合、前記側部緩和層は、前記トレンチの前記側面に沿って前記トレンチの開口端に至るように形成されていることが、とりわけ好ましい。

【0015】

また、本発明の半導体装置では、前記トレンチは、平面形状の底面および当該平面形状の底面に対して90°を超える角度で傾斜した側面を有するテーパトレンチを含むことが好ましい。

テーパトレンチであれば、側面が底面に対して90°で直角に立つ場合よりも、半導体装置の耐圧を一層向上させることができる。

【0016】

さらに、テーパトレンチでは、底面だけでなく、側面の全部または一部もトレンチの開放端に対して対向することとなる。そのため、たとえばトレンチを介して第2導電型の不純物を半導体層に注入する場合に、トレンチの開放端からトレンチ内に入射した不純物を、トレンチの側面に確実に当てることができる。その結果、前述の側部緩和部を容易に形成することができる。

【0017】

なお、テーパトレンチとは、側面の全部が底面に対して90°を超える角度で傾斜しているトレンチ、側面の一部(たとえば、トレンチのエッジ部を形成する部分)が底面に対して90°を超える角度で傾斜しているトレンチのいずれをも含む概念である。

また、本発明の半導体装置では、前記ショットキー電極は、前記トレンチに埋め込まれるように形成されており、前記半導体層における前記トレンチの底面を形成する部分には、前記トレンチに埋め込まれた前記ショットキー電極との間にオーミック接合を形成する第2導電型のコンタクト層がさらに形成されていることが好ましい。

【0018】

この構成により、コンタクト層(第2導電型)と半導体層(第1導電型)とのpn接合を有するpnダイオードに対してショットキー電極をオーミック接合させることができる。このpnダイオードは、ショットキー電極と半導体層とのショットキー接合を有するショットキーバリアダイオード(ヘテロダイオード)に対して並列に設けられる。これにより、半導体装置にサージ電流が流れても、当該サージ電流の一部を内蔵pnダイオードに流すことができる。その結果、ショットキーバリアダイオードに流れるサージ電流を低減できるので、サージ電流によるショットキーバリアダイオードの熱破壊を防止することができる。

【0019】

また、本発明の半導体装置では、前記半導体層は、逆方向電圧印加時に第1電界がかかる第1部分および当該第1電界に対して相対的に高い第2電界がかかる第2部分を、前記電界緩和部とは異なる部分に有している場合、前記ショットキー電極は、前記第1部分との間に第1ショットキー障壁を形成する第1電極と、前記第2部分との間に前記第1ショットキー障壁に対して相対的に高い第2ショットキー障壁を形成する第2電極とを含むことが好ましい。

【0020】

本発明では、半導体層の第1部分と第2部分との関係のように、相対的に電界強度が高い部分と低い部分とが存在する場合がある。

そこで上記のように、逆方向電圧印加時における半導体層の電界分布に応じてショットキー電極を適正に選択しておけば、逆方向電圧印加時に相対的に高い第2電界がかかる第2部分では、比較的高い第2ショットキー障壁により逆リーク電流を抑制することができる。一方、相対的に低い第1電界がかかる第1部分では、ショットキー障壁の高さを低くしても逆方向リーク電流が当該ショットキー障壁を越えるおそれが少ないので、比較的低い第1ショットキー障壁とすることにより、順方向電圧印加時に低い電圧で優先的に電流を流すことができる。よって、この構成により、逆方向リーク電流および順方向電圧の低減を効率よく行うことができる。

【0021】

また、本発明の半導体装置では、前記半導体層は、第1不純物濃度を有するベースドリフト層と、前記ベースドリフト層上に形成され、前記第1不純物濃度に対して相対的に高い第2不純物濃度を有する低抵抗ドリフト層とを含む場合、前記電界緩和部は、その最深部が前記低抵抗ドリフト層に達するように形成され、前記半導体層の一部を単位セルとして区画していることが好ましい。

【0022】

電界緩和部で区画された単位セルでは電流を流すことができる領域(電流経路)が制約されるので、半導体層における単位セルを形成する部分の不純物濃度が低いと、単位セルの抵抗値が高くなるおそれがある。そこで上記のように、最深部が低抵抗ドリフト層に達するように電界緩和部を形成することにより、単位セルの全部もしくは一部を低抵抗ドリフト層で形成することができる。そのため、当該低抵抗ドリフト層が形成された部分では、電流経路がたとえ狭められても、比較的高い第2不純物濃度を有する低抵抗ドリフト層により抵抗値の上昇を抑制することができる。その結果、単位セルの低抵抗化を図ることができる。

【0023】

また、前記ベースドリフト層の前記第1不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少していてもよい。また、前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって一定であってもよいし、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少していてもよい。

【0024】

また、本発明の半導体装置では、前記半導体層は、前記低抵抗ドリフト層上に形成され、前記第2不純物濃度に対して相対的に低い第3不純物濃度を有する表面ドリフト層をさらに含むことが好ましい。

この構成により、半導体層の表面近傍の不純物濃度を小さくすることができるので、逆方向電圧印加時に半導体層の表面にかかる電界強度を低減することができる。その結果、逆方向リーク電流を一層低減することができる。

【0025】

また、本発明の半導体装置が、前記半導体層を支持する第1導電型のワイドバンドギャップ半導体からなる基板をさらに含む場合、前記半導体層は、前記基板上に形成され、前記第1不純物濃度に対して相対的に高い第4不純物濃度を有するバッファ層をさらに含んでいてもよい。

また、本発明の半導体装置では、前記ピラー層の下端部は、前記バッファ層に接していてもよいし、前記バッファ層に対して間隔が空くように位置していてもよい。

【0026】

また、本発明の半導体装置において、ワイドバンドギャップ半導体(バンドギャップが2eV以上)は、たとえば絶縁破壊電界が1MV/cmよりも大きい半導体であって、具体的には、SiC(たとえば、4H−SiC 絶縁破壊電界が約2.8MV/cmであり、バンドギャップの幅が約3.26eV)、GaN(絶縁破壊電界が約3MV/cmであり、バンドギャップの幅が約3.42eV)、ダイヤモンド(絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約5.47eV)などである。

【図面の簡単な説明】

【0027】

【図1】本発明の第1実施形態に係るショットキーバリアダイオードの模式的な平面図である。

【図2A】図1のショットキーバリアダイオードの断面図であって、図1の切断線II−IIでの切断面を示す。

【図2B】図2Aの電界緩和層の形状の一例を示す図である。

【図2C】図2Aの電界緩和層の形状の他の例を示す図である。

【図3】スーパージャンクション構造の導入効果を証明するためのシミュレーション実験に用いたショットキーバリアダイオードの概略構成図である。

【図4】エピタキシャル層の厚さと電界強度との関係を示すグラフである。

【図5】高抵抗層の導入効果を証明するためのシミュレーション実験に用いたショットキーバリアダイオードの概略構成図である。

【図6】エピタキシャル層の厚さと電界強度との関係を示すグラフである。

【図7】4H−SiCの結晶構造のユニットセルを表した模式図である。

【図8】p型ピラー層のストライプ方向を示す図である。

【図9】単位セルの表面の各部と電界強度との関係を示すグラフである。

【図10】基板およびエピタキシャル層の不純物濃度を説明するための図である。

【図11A】図2Aのショットキーバリアダイオードの製造工程の一部を示す図である。

【図11B】図11Aの次の工程を示す図である。

【図11C】図11Bの次の工程を示す図である。

【図11D】図11Cの次の工程を示す図である。

【図11E】図11Dの次の工程を示す図である。

【図11F】図11Eの次の工程を示す図である。

【図11G】図11Fの次の工程を示す図である。

【図12】本発明の第2実施形態に係るショットキーバリアダイオードの断面図である。

【図13】図12のトレンチの拡大図である。

【図14】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、トレンチ構造なしの場合を示す。

【図15】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、矩形トレンチ構造ありの場合を示す。

【図16】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、U字トレンチ構造ありの場合を示す。

【図17】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造ありの場合を示す。

【図18】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造+底面p型層ありの場合を示す。

【図19】逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、台形トレンチ構造+側面p型層ありの場合を示す。

【図20】ショットキーバリアダイオードの電流−電圧(I−V)曲線を示すグラフである。

【図21A】図12のショットキーバリアダイオードの製造工程の一部を示す図である。

【図21B】図21Aの次の工程を示す図である。

【図21C】図21Bの次の工程を示す図である。

【図21D】図21Cの次の工程を示す図である。

【図21E】図21Dの次の工程を示す図である。

【図21F】図21Eの次の工程を示す図である。

【図21G】図21Fの次の工程を示す図である。

【図21H】図21Gの次の工程を示す図である。

【図21I】図21Hの次の工程を示す図である。

【図21J】図21Iの次の工程を示す図である。

【図22】図22(a)(b)(c)(d)(e)(f)は、トレンチの断面形状の変形例を示す図であって、図22(a)が第1変形例、図22(b)が第2変形例、図22(c)が第3変形例、図22(d)が第4変形例、図22(e)が第5変形例、図22(f)が第6変形例をそれぞれ示す。

【図23】図2Aのショットキーバリアダイオードの第1変形例を示す図である。

【図24】図2Aのショットキーバリアダイオードの第2変形例を示す図である。

【図25】図2Aのショットキーバリアダイオードの第3変形例を示す図である。

【発明を実施するための形態】

【0028】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

<第1実施形態に係るショットキーバリアダイオードの全体構成>

図1は、本発明の第1実施形態に係るショットキーバリアダイオード1の模式的な平面図である。図2Aは、図1のショットキーバリアダイオード1の断面図であって、図1の切断線II−IIでの切断面を示す。

【0029】

半導体装置としてのショットキーバリアダイオード1は、4H−SiC(絶縁破壊電界が約2.8MV/cmであり、バンドギャップの幅が約3.26eVのワイドバンドギャップ半導体)が採用されたショットキーバリアダイオードであり、たとえば、平面視正方形のチップ状である。チップ状のショットキーバリアダイオード1は、図1の紙面における上下左右方向の長さがそれぞれ数mm程度である。

【0030】

ショットキーバリアダイオード1は、n+型のSiCからなる基板2(オフ角が4°の基板)を備えている。基板2の厚さは、たとえば、50μm〜600μmである。なお、n型不純物としては、たとえば、N(窒素)、P(リン)、As(ひ素)などを使用できる。

基板2の裏面3((000−1)C面)には、その全域を覆うようにオーミック電極としてのカソード電極4が形成されている。カソード電極4は、n型のSiCとオーミック接触する金属(たとえば、Ti/Ni/Ag、Ti/Ni/Au/Ag)からなる。

【0031】

基板2の表面5((0001)Si面)には、半導体層の一例としてのn型エピタキシャル層6が形成されている。

エピタキシャル層6は、バッファ層7と、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10の3層構造のドリフト層とが基板2の表面5からこの順に積層されて形成された構造を有している。バッファ層7は、エピタキシャル層6の裏面11((000−1)C面)を形成しており、基板2の表面5に接している。一方、表面ドリフト層10は、エピタキシャル層6の表面12((0001)Si面)を形成している。

【0032】

エピタキシャル層6の総厚さTは、たとえば、3μm〜100μmである。また、バッファ層7の厚さt1は、たとえば、0.1μm〜1μmである。ベースドリフト層8の厚さt2は、たとえば、2μm〜100μmである。低抵抗ドリフト層9の厚さt3は、たとえば、1μm〜3μmである。表面ドリフト層10の厚さt4は、たとえば、0.2μm〜0.5μmである。

【0033】

エピタキシャル層6の表面12には、エピタキシャル層6の一部を活性領域13として露出させるコンタクトホール14を有し、当該活性領域13を取り囲むフィールド領域15を覆うフィールド絶縁膜16が形成されている。フィールド絶縁膜16は、たとえば、SiO2(酸化シリコン)からなる。また、フィールド絶縁膜16の厚さは、たとえば、0.5μm〜3μmである。

【0034】

エピタキシャル層6には、当該表面12からドリフト層8〜10を貫通して、最深部がバッファ層7とベースドリフト層8との界面に位置するストライプ状のp型ピラー層17が形成されている。

ストライプ状のp型ピラー層17は、ショットキーバリアダイオード1の一組の対辺の対向方向に沿って直線状に延びる複数のp型ピラー層17が、互いに間隔を空けて、活性領域13およびフィールド領域15にわたって平行に配列されることによって形成されている。互いに隣り合うp型ピラー層17の距離WSJは、たとえば、2μm〜20μmである。また、各p型ピラー層17の長手方向に直交する幅WPは、たとえば、0.1μm〜10μmである。また、各p型ピラー層17の深さDSJは、たとえば、3μm〜25μmである。なお、p型ピラー層17を形成するための不純物としては、たとえば、B(ホウ素)、Al(アルミニウム)などを使用できる。

【0035】

p型ピラー層17を形成することによって、エピタキシャル層6には、ストライプ状のp型ピラー層17と、互いに隣り合うp型ピラー層17の間に挟まれ、エピタキシャル層6の導電型が維持されたn型ピラー層18とがエピタキシャル層6の表面12に沿う方向に交互に配列されてスーパージャンクション構造が形成されている。

活性領域13において各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中に位置する電界緩和層19が形成されている。電界緩和層19の深さDR(エピタキシャル層6の表面12から電界緩和層19の最深部までの距離)は、たとえば、1000Å〜10000Åである。

【0036】

これにより、エピタキシャル層6には、互いに隣り合う電界緩和層19で挟まれることによって区画された単位セル20(ラインセル)がストライプ状に形成されている。各単位セル20は、その大半の領域を占めるベース部が低抵抗ドリフト層9により形成され、ベース部に対して表面12側の表層部が表面ドリフト層10により形成されている。

単位セル20を区画する電界緩和層19は、p型ピラー層17の不純物濃度よりも高い不純物濃度を有し、各ドリフト層8〜10よりも高い抵抗を有する層である。たとえば、電界緩和層19のシート抵抗は、1MΩ/□以上である。

【0037】

なお、電界緩和層19は、p型ピラー層17の不純物濃度よりも高い不純物濃度を有するが、高抵抗ではないp型層であってもよい。

電界緩和層19が高抵抗層の場合、たとえば、1×1016cm−3〜5×1020cm−3の濃度で含有されている電界緩和層19の不純物の活性化率を5%未満、好ましくは、0%〜0.1%にすることにより、上記した範囲のシート抵抗は達成されている。なお、不純物の活性化率とは、ショットキーバリアダイオード1の製造工程においてエピタキシャル層6に注入した不純物イオンの全数に対して、活性化した不純物イオンの個数の割合を示している。

【0038】

また、電界緩和層19は、たとえば、図2Bに示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の内側に収まるように、p型ピラー層17よりも幅狭に形成されていてもよいし、図2Cに示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の外側にはみ出すように、p型ピラー層17よりも幅広に形成されていてもよい。電界緩和層19が高抵抗ではないp型層の場合には、図2Bの幅狭形状が好ましく、電界緩和層19が高抵抗層である場合には、図2Cの幅広形状が好ましい。

【0039】

フィールド絶縁膜16上には、アノード電極21が形成されている。アノード電極21は、フィールド絶縁膜16のコンタクトホール14内でエピタキシャル層6に接合された、ショットキー電極の一例としてのショットキーメタル22と、このショットキーメタル22に積層されたコンタクトメタル23との2層構造を有している。

ショットキーメタル22は、各単位セル20の表面12に形成された第1電極の一例としての第1メタル24と、互いに隣り合う電界緩和層19の間に跨り、それらの電界緩和層19で挟まれる単位セル20の表面12の第1メタル24を覆うように形成された第2電極の一例としての第2メタル25とを含んでいる。

【0040】

第1メタル24は、電界緩和層19に隣接する各単位セル20の周縁部26で挟まれた中央部27において、電界緩和層19の長手方向に沿って直線状に形成されている。

第2メタル25は、活性領域13全体を覆うように形成され、フィールド絶縁膜16のコンタクトホール14に埋め込まれている。第2メタル25は、各単位セル20の表面12の周縁部26に接している。また、第2メタル25は、フィールド絶縁膜16におけるコンタクトホール14の周縁部を上から覆うように、当該コンタクトホール14の外方へフランジ状に張り出している。すなわち、フィールド絶縁膜16の周縁部は、エピタキシャル層6(表面ドリフト層10)および第2メタル25により、全周にわたってその上下両側から挟まれている。したがって、エピタキシャル層6におけるショットキー接合の外周領域(すなわち、フィールド領域15の内縁部)は、SiCからなるフィールド絶縁膜16の周縁部により覆われることとなる。

【0041】

コンタクトメタル23は、アノード電極21において、ショットキーバリアダイオード1の最表面に露出して、ボンディングワイヤなどが接合される部分である。コンタクトメタル23は、たとえば、Al(アルミニウム)からなる。また、コンタクトメタル23は、ショットキーメタル22(第2メタル25)と同様に、フィールド絶縁膜16におけるコンタクトホール14の周縁部を上から覆うように、当該コンタクトホール14の外方へフランジ状に張り出している。

【0042】

フィールド領域15において各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、エピタキシャル層6の表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中に位置する高抵抗のガードリング28が形成されている。このガードリング28は、平面視において、フィールド絶縁膜16のコンタクトホール14の内外に跨るように(活性領域13およびフィールド領域15に跨るように)、当該コンタクトホール14の輪郭に沿って環状に形成されている。ガードリング28のエピタキシャル層6の表面12からの深さDGは、たとえば、電界緩和層19と同じ深さ(たとえば、1000Å〜10000Å)である。

【0043】

また、ガードリング28は、電界緩和層19と同様の特性を示す層である。たとえば、電界緩和層19が高抵抗層の場合には、ガードリング28は、当該高抵抗層と同様に、各ドリフト層8〜10よりも高い抵抗を有する層であり、シート抵抗が1MΩ/□以上であり、不純物の活性化率が5%未満(好ましくは、0%〜0.1%)である。

ショットキーバリアダイオード1の最表面には、たとえば窒化シリコン(SiN)からなる表面保護膜29が形成されている。表面保護膜29の中央部には、アノード電極21(コンタクトメタル23)を露出させる開口30が形成されている。ボンディングワイヤなどは、この開口30を介してコンタクトメタル23に接合される。

【0044】

このショットキーバリアダイオード1では、アノード電極21に正電圧、カソード電極4に負電圧が印加される順方向バイアス状態になることにより、カソード電極4からアノード電極21へと、エピタキシャル層6の活性領域13を介して電子(キャリア)が移動して電流が流れる。<スーパージャンクション構造の導入効果>

次に、図3および図4を参照して、エピタキシャル層6にスーパージャンクション構造を形成することによる耐圧の向上効果について説明する。

【0045】

スーパージャンクション構造として、図3のように設計した。図3において、図2Aに示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付している。なお、p型ピラー層17の距離WSJ(n型ピラー層18の幅)は5μm、p型ピラー層17の幅WPは3.5μm、ショットキーメタル22とエピタキシャル層6とのバリアハイトSBは1.4eVとした。また、p型ピラー層17の深さDSJは可変の値とした。

【0046】

そして、図3のアノード−カソード間に逆方向電圧(1200V)を印加したときのエピタキシャル層6内の電界強度分布が、スーパージャンクション構造の有無および深さDSJの違いによって如何に変化するかをシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。結果を図4に示す。

図4に示すように、スーパージャンクション構造が形成されていないショットキーバリアダイオード(従来)では、エピタキシャル層6の裏面11から表面12へ向かうにしたがって電界強度が比例して強くなり、エピタキシャル層6の表面12で最大(1.15×106V/cm程度)となった。

【0047】

これに対し、スーパージャンクション構造が形成されたショットキーバリアダイオード1では、スーパージャンクション構造がない場合に比べて、裏面11から表面12へ向かって電界強度を均一にすることができた。とりわけ、p型ピラー層17の深さDSJが5μm、10μm、15μm、20μmと深くなるほど、その効果が大きかった。たとえば、DSJ=20μmの場合には、電界強度が6.0×105V/cm程度でほぼ一定であった。

【0048】

これらの結果、エピタキシャル層6の不純物濃度および厚さが同条件である下では、スーパージャンクション構造が形成されていない従来構造に比べて耐圧を向上させることができることを確認できた。従って、本実施形態のショットキーバリアダイオード1によれば、従来に比べて、不純物濃度が高くて厚さが小さいエピタキシャル層6でも十分な耐圧を確保できるので、エピタキシャル層6の不純物濃度および厚さを適切に設計することにより、高耐圧を確保できながら、順方向電圧を低減することができることを確認できた。

<電界緩和層19の導入効果>

図5および図6を参照して、エピタキシャル層6に電界緩和層19を形成することによる逆方向リーク電流および順方向電圧の低減効果について説明する。

【0049】

電界緩和層19を有するショットキーバリアダイオードとして、図3の構造のショットキーバリアダイオード1(WSJ=5μm、WP=3.5μm、DSJ=20μm)のエピタキシャル層6の表面12に、アルミニウム(Al)を不純物として含む電界緩和層19(Al層)が形成された構造とした。なお、電界緩和層(Al層)19の深さDRは1μmとし、電界緩和層19の不純物濃度は可変の値とした。

【0050】

そして、図5のアノード−カソード間に逆方向電圧(1200V)を印加したときのエピタキシャル層6内の電界強度分布が、電界緩和層19の有無および電界緩和層19の不純物濃度の違いによって如何に変化するかをシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。結果を図6に示す。

図6に示すように、電界緩和層19が形成されたショットキーバリアダイオード1では、電界緩和層19がない場合に比べて、エピタキシャル層6の表面12での電界強度を低減することができた。とりわけ、電界緩和層19の濃度が1×1016cm−3、3×1016cm−3、1×1017cm−3と高くなるほど、その効果が大きかった。たとえば、濃度=1×1016cm−3の場合には、エピタキシャル層6の表面12での電界強度が6.3×105V/cm程度であったのに対し、濃度=1×1017cm−3の場合には、その電界強度を5.5×105V/cm程度にまで低減することができた。

【0051】

この結果、本実施形態のショットキーバリアダイオード1では、エピタキシャル層6の表面12(単位セル20の表面)に接するアノード電極21(ショットキーメタル22)とエピタキシャル層6との間のバリアハイトを低くしても、降伏電圧に近い逆方向電圧が印加されたときの表面12での電界強度が弱いので、バリアハイトを越える逆方向リーク電流を低減することができることを確認できた。すなわち、逆方向リーク電流を低減できながら、バリアハイトを低くして順方向電圧を低減できることを確認できた。

<p型ピラー層17のストライプ方向とSiC結晶構造との関係>

次に、図7および図8を参照して、p型ピラー層17のストライプ方向とSiC結晶構造との関係について説明する。

【0052】

図7は、4H−SiCの結晶構造のユニットセルを表した模式図である。図8は、p型ピラー層17のストライプ方向を示す図である。なお、図7の下部に示したSiC結晶構造の斜視図については、その横に示したSiC積層構造の4層のうち2層のみを抜き出して示している。また、図8の左側に示した図は、図7のユニットセルを(0001)面の真上から見た図である。

【0053】

本実施形態のショットキーバリアダイオード1に使用されるSiCには、結晶構造の違いにより、3C−SiC、4H−SiC、6H−SiCなどの種類がある。

これらのうち、4H−SiCの結晶構造は、図7および図8に示すように、六方晶系で近似することができ、1つのシリコン原子に対して4つの炭素原子が結合している。4つの炭素原子は、シリコン原子を中央に配置した正四面体の4つの頂点に位置している。これらの4つの炭素原子は、1つのシリコン原子が炭素原子に対して[0001]軸方向に位置し、他の3つの炭素原子がシリコン原子に対して[000−1]軸側に位置している。

【0054】

[0001]軸および[000−1]軸は六角柱の軸方向に沿い、この[0001]軸を法線とする面(六角柱の頂面)が(0001)面(Si面)である。一方、[000−1]軸を法線とする面(六角柱の下面)が(000−1)面(C面)である。

また、[0001]軸に垂直であり、かつ(0001)面の真上から見た場合において六角注の互いに隣り合わない頂点を通る方向がそれぞれ、a1軸[2−1−10]、a2軸[−12−10]およびa3軸[−1−120]である。

【0055】

図8に示すように、a1軸とa2軸との間の頂点を通る方向が[11−20]軸であり、a2軸とa3軸との間の頂点を通る方向が[−2110]軸であり、a3軸とa1軸との間の頂点を通る方向が[1−210]軸である。

六角注の各頂点を通る上記6本の軸の各間において、その両側の各軸に対して30°の角度で傾斜していて、六角注の各側面の法線となる軸がそれぞれ、a1軸と[11−20]軸との間から時計回りに順に、[10−10]軸、[1−100]軸、[0−110]軸、[−1010]軸、[−1100]軸および[01−10]軸である。これらの軸を法線とする各面(六角柱の側面)は、(0001)面および(000−1)面に対して直角な結晶面である。

【0056】

そして、本実施形態では、(0001)面を主面(表面5)とする基板2を用い、その上に(0001)面が主面となるようにエピタキシャル層6を成長させている。また、p型ピラー層17のストライプ方向の例としては、たとえば、[1−100]軸と平行(0°)、[1−100]軸に垂直(90°)、[1−100]軸に対して45°傾斜等の様々なパターンが挙げられる。なお、図8に示したストライプパターンは一例に過ぎず、必要に応じて様々なストライプパターンを採用することができる。

<2つのショットキー電極(第1メタル24および第2メタル25)>

次に、図9を参照して、2つのショットキー電極(第1メタル24および第2メタル25)を設けたことによる逆方向リーク電流および順方向電圧の低減の効率化について説明する。

【0057】

図9は、単位セル20の表面12の各部と電界強度との関係を示すグラフである。

本実施形態のショットキーバリアダイオード1では、前述の<電界緩和層19の導入効果>で示したシミュレーションの結果、図9に示すように、単位セル20の表面12には、相対的に電界強度が高い部分(単位セル20の中央部27)と低い部分(単位セル20の周縁部26)とが存在することが分かった。

【0058】

具体的には、図9に示すように、半導体層の第1部分の一例としての単位セル20の周縁部26には1.0×105V/cm〜1.3×106V/cmの電界強度が分布し、半導体層の第2部分の一例としての単位セル20の中央部27には1.5×106V/cm程度の電界強度が分布している。逆方向電圧印加時の電界強度分布は、単位セル20の中央部27の電界強度(第2電界)が、単位セル20の周縁部26の電界強度(第1電界)に比べて高くなっている。

【0059】

そこで、相対的に高い電界がかかる単位セル20の中央部27には、比較的高い電位障壁(たとえば、1.4eV)を形成するp型ポリシリコンなどを第1メタル24としてショットキー接合させる。なお、電極がポリシリコンのような半導体電極の場合には、ショットキー接合に代えて、互いにバンドギャップの異なる半導体同士のヘテロ接合ということがある。

【0060】

一方、相対的に低い電界がかかる単位セル20の周縁部26には、比較的低い電位障壁(たとえば0.7eV)を形成するアルミニウム(Al)などを第2メタル25としてショットキー接合させる。

これにより、逆方向電圧印加時に相対的に高い電界がかかる単位セル20の中央部27では、第1メタル24(ポリシリコン)とエピタキシャル層6との間の高いショットキー障壁(第2ショットキー障壁)により逆方向リーク電流を抑制することができる。

【0061】

一方、相対的に低い電界がかかる単位セル20の周縁部26では、第2メタル25(アルミニウム)とエピタキシャル層6との間のショットキー障壁の高さを低くしても逆方向リーク電流が当該ショットキー障壁を越えるおそれが少ない。したがって、低いショットキー障壁(第1ショットキー障壁)とすることにより、順方向電圧印加時に低い電圧で優先的に電流を流すことができる。また、この第2メタル25は、コンタクトメタル23を省略することにより、コンタクトメタル23を兼ねることができる。

【0062】

このように、逆方向電圧印加時における単位セル20の電界強度の分布に応じてアノード電極21(ショットキー電極)を適正に選択することにより、逆方向リーク電流および順方向電圧の低減を効率よく行うことができることを確認できた。

<エピタキシャル層6の不純物濃度>

次に、図10を参照して、基板2およびエピタキシャル層6の不純物濃度の大きさについて説明する。

【0063】

図10は、基板2およびエピタキシャル層6の不純物濃度を説明するための図である。

図10に示すように、基板2およびエピタキシャル層6は、いずれもn型不純物を含有するn型SiCからなる。それらの不純物濃度の大小関係は、基板2>バッファ層7>ドリフト層8〜10である。

基板2の濃度は、たとえば、その厚さ方向に沿って5×1018〜5×1019cm−3でほぼ一定である。バッファ層7の濃度は、たとえば、その厚さ方向に沿って、1×1017〜5×1018cm−3で一定または表面5に沿って濃度が薄い。

【0064】

ドリフト層8〜10の濃度は、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10それぞれの界面を境に段階的に変化している。つまり、各界面に対して表面12側の層と裏面11側の層との間に濃度差がある。

ベースドリフト層8の濃度は、たとえば、その厚さ方向に沿って、5×1014〜5×1016cm−3で一定である。なお、ベースドリフト層8の濃度は、図10の破線で示すように、エピタキシャル層6の裏面11から表面12へ向かうにしたがって、約3×1016cm−3から約5×1015cm−3まで連続的に減少していてもよい。

【0065】

低抵抗ドリフト層9の濃度は、ベースドリフト層8の濃度よりも高く、たとえば、その厚さ方向に沿って、5×1015〜5×1017cm−3で一定である。なお、低抵抗ドリフト層9の濃度は、図10の破線で示すように、エピタキシャル層6の裏面11から表面12へ向かうにしたがって、約3×1017cm−3から約1×1016cm−3まで連続的に減少していてもよい。

【0066】

表面ドリフト層10の濃度は、ベースドリフト層8および低抵抗ドリフト層9の濃度よりも低く、たとえば、その厚さ方向に沿って、5×1014〜1×1016cm−3で一定である。

図2Aに示すように、ストライプ状の電界緩和層19で区画された単位セル20(ラインセル)では電流を流すことができる領域(電流経路)が、互いに隣り合う電界緩和層19の距離(つまり、p型ピラー層17の距離WSJ)に制約されるので、エピタキシャル層6における単位セル20を形成する部分の不純物濃度が低いと、単位セル20の抵抗値が高くなるおそれがある。

【0067】

そこで図10に示すように、単位セル20のベース部を形成する低抵抗ドリフト層9の濃度をベースドリフト層8よりも高くすることにより、電流経路が電界緩和層19の距離WSJに制約されていても、比較的高い濃度を有する低抵抗ドリフト層9により単位セル20の抵抗値の上昇を抑制することができる。その結果、単位セル20の低抵抗化を図ることができる。

【0068】

一方、ショットキーメタル22に接する単位セル20の表層部には、比較的低い濃度を有する表面ドリフト層10を設けることにより、逆方向電圧印加時にエピタキシャル層6の表面12にかかる電界強度を低減することができる。その結果、逆方向リーク電流を一層低減することができる。

<ショットキーバリアダイオード1(第1実施形態)の製造方法>

次に、図11A〜図11Gを参照して、図2Aのショットキーバリアダイオード1の製造方法について説明する。

【0069】

まず、図11Aに示すように、基板2の上に、バッファ層7、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10をこの順にエピタキシャル成長させる。

次に、図11Bに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク31を形成する。ハードマスク31の厚さは、好ましくは、1.5μm〜10μmである。次に、ハードマスク31をパターニングした後、当該ハードマスク31を介して、エピタキシャル層6をドライエッチングする。これにより、バッファ層7に達するストライプ状のトレンチ32を形成する。トレンチ32の深さは、p型ピラー層17の深さDSJに合わせて適宜設定する。また、トレンチ32は、深さDSJに応じて、ハードマスクを形成する工程、当該ハードマスクを用いてドライエッチングする工程およびドライエッチング後に当該ハードマスクを除去する工程を複数回繰り返すことにより形成してもよい。

【0070】

次に、ハードマスク31を除去した後、図11Cに示すように、そのトレンチ32内部からエピタキシャル層6の表面12が覆われるまで、p型のSiC層33をエピタキシャル成長させる。

次に、図11Dに示すように、エピタキシャル層6の表面12を覆うトレンチ32外のSiC層33を、たとえばエッチバックにより除去する。これにより、トレンチ32に埋め込まれたp型ピラー層17が形成され、同時に、互いに隣り合うp型ピラー層17の間にn型ピラー層18が形成される。

【0071】

次に、図11Eに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク34を形成する。ハードマスク34の厚さは、好ましくは、1.5μm〜3μmである。次に、ハードマスク34をパターニングした後、当該ハードマスク34を介して、エピタキシャル層6の表面12へ向かってp型不純物(ホウ素イオン)を注入(1段注入)する。これにより、エピタキシャル層6の表層部に、ホウ素イオンが高濃度に注入された高濃度不純物層35が形成される。なお、イオン注入の際に表面12を覆うマスクとしては、ハードマスク34に代えてフォトレジストを用いてもよい。

【0072】

次に、図11Fに示すように、ハードマスク34を剥離し、1500℃未満の温度、好ましくは、1100℃〜1400℃の温度でエピタキシャル層6をアニール処理する。これにより、高濃度不純物層35が電界緩和層19(高抵抗層)およびガードリング28に変質して、各p型ピラー層17の上端部に電界緩和層19が形成され、同時にガードリング28が形成される。このようなホウ素イオンのイオン注入法では、ホウ素イオンが比較的軽いイオンであるため、表面12から深い位置にまで簡単に注入することができる。そのため、電界緩和層19の深さDRを、エピタキシャル層6の表面12に対して浅い位置から深い位置までの幅広い範囲で簡単に制御することができる。

【0073】

なお、図11Eおよび図11Fでは、高抵抗層としての電界緩和層19の形成方法を示しているが、高抵抗層ではないp型層としての電界緩和層19を形成するには、たとえば、図11Eの工程において、ハードマスク34を介してエピタキシャル層6の表面12へ向かってp型不純物(アルミニウムイオン)を注入する。次に、図11Fの工程において、ハードマスク34を剥離し、1500℃〜1800℃の温度でエピタキシャル層6をアニール処理する。これにより、当該p型層を形成することができる。

【0074】

その後、図11Gに示すように、フィールド絶縁膜16、アノード電極21、表面保護膜29、カソード電極4等を形成する。

以上の工程を経て、図2Aのショットキーバリアダイオード1が得られる。

<第2実施形態に係るショットキーバリアダイオードの全体構成>

図12は、本発明の第2実施形態に係るショットキーバリアダイオード41の断面図である。また、図13は、図12のトレンチ42の拡大図である。図12において、図2Aに示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付し、その説明を省略する。

【0075】

第2実施形態のショットキーバリアダイオード41の活性領域13において、各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中部に達するトレンチ42が形成されている。トレンチ42は、その長手方向に直交する幅方向に沿って切断したときの断面視が逆台形状のトレンチであり、p型ピラー層17の上端部に沿って直線状に延びている。

【0076】

これにより、エピタキシャル層6には、互いに隣り合う台形トレンチ42で挟まれることによって区画された単位セル20(ラインセル)がストライプ状に形成されている。

各台形トレンチ42は、エピタキシャル層6の表面12に対して平行な底面43と、当該底面43に対して傾斜する側面44とによって区画されている。側面44の傾斜角θ1は、たとえば、45°〜85°である。また、各台形トレンチ42の深さ(エピタキシャル層6の表面12から台形トレンチ42の底面43までの距離)は、たとえば、0.3Å〜15000Åである。また、各台形トレンチ42の長手方向に直交する幅WT(最深部の幅)は、0.3μm〜10μmである。

【0077】

また、図13に示すように、各台形トレンチ42の側面44と底面43とが交わって形成されたエッジ部45は、台形トレンチ42の外方へ向かって湾曲する形状に形成されており、各台形トレンチ42の底部は断面視U字状に形成されている。このような形状のエッジ部45の内面(湾曲面)の曲率半径Rは、下記式(1)を満たす。

0.01L<R<10L・・・(1)

式(1)において、Lはトレンチ42の幅方向に沿って対向するエッジ部45間の直線距離を示している(単位は、μm、nm、m等、長さの単位であれば特に制限されない)。具体的には、エピタキシャル層6の表面12に対して平行な底面43の幅であって、トレンチ42の幅WTからエッジ部45の幅を差し引いた値である。

【0078】

また、エッジ部45の曲率半径Rは、0.02L<R<1L・・・(2)を満たすことが好ましい。

曲率半径Rは、たとえば、台形トレンチ42の断面をSEM(Scanning Electron Microscope:走査型電子顕微鏡)で撮影し、得られたSEM画像のエッジ部45の曲率を測定することにより求めることができる。

【0079】

台形トレンチ42の底面43および側面44には、台形トレンチ42の内面に沿って電界緩和部としてのp型層46が形成されている。p型層46は、台形トレンチ42の底面43からエッジ部45を経て台形トレンチ42の開口端に至るまで形成されている。また、p型層46は、たとえば、図13に示すように、p型ピラー層17とエピタキシャル層6との界面に対してp型ピラー層17の内側に収まるように、p型ピラー層17よりも幅狭に形成されている。また、p型層46は、n型のエピタキシャル層6との間にpn接合部を形成している。これにより、ショットキーバリアダイオード41には、p型層46およびn型エピタキシャル層6(低抵抗ドリフト層9)によって構成されるpnダイオード47が内蔵されることとなる。

【0080】

p型層46の厚さ(台形トレンチ42の内面からの深さ)は、図13に示すように、台形トレンチ42の深さ方向(エピタキシャル層6の表面12に垂直な方向)に沿って測定される台形トレンチ42の底面43からの第1厚さt5が、台形トレンチ42の幅方向(エピタキシャル層6の表面12に平行な方向)に沿って測定される台形トレンチ42の側面44からの第2厚さt6よりも大きい。具体的には、第1厚さt5は、たとえば、0.3μm〜0.7μmであり、第2厚さt6は、たとえば、0.1μm〜0.5μmである。

【0081】

また、p型層46には、p型層46の他の部分よりも高濃度に不純物が注入されたp+型のコンタクト層48が、台形トレンチ42の底面43の一部に形成されている。たとえば、コンタクト層48の不純物濃度は、1×1020〜1×1021cm−3であり、コンタクト層48を除くp型層46の他の部分の不純物濃度は、1×1017〜5×1018cm−3である。

【0082】

コンタクト層48は、台形トレンチ42の長手方向に沿って直線状に形成されており、台形トレンチ42の底面43からp型層46の深さ方向途中までの深さ(たとえば、0.05μm〜0.2μm)を有している。

また、ショットキーバリアダイオード41のフィールド領域15において、各p型ピラー層17の上端部(エピタキシャル層6の表面12近傍)には、当該表面12から表面ドリフト層10を貫通して、最深部が低抵抗ドリフト層9の途中部に達する環状トレンチ69が形成されている。環状トレンチ69は、活性領域13を取り囲むように形成されている。

【0083】

また、環状トレンチ69の底面70および側面71には、環状トレンチ69の内面に露出するように当該内面に沿ってガードリング72が形成されている。ガードリング72は、p型層46と同一の工程で形成されるものであって、p型層46と同じ不純物濃度(たとえば、1×1017〜5×1018cm−3)および厚さを有している。

なお、ガードリング72は、その外周部に、不純物濃度がp型層46(ガードリング72の残りの部分)よりも低く、p型ピラー層17よりも高い部分を有していてもよい。

<トレンチ42構造の導入効果>

次に、図14〜図19を参照して、エピタキシャル層6に台形トレンチ42およびp型層46を形成することによる逆方向リーク電流および順方向電圧を低減効果について説明する。なお、図15のトレンチは矩形トレンチ42´であり、図16のトレンチはU字トレンチ42´´である。

【0084】

図14〜図19は、逆方向電圧印加時の電界強度の分布図(シミュレーションデータ)であって、図14がトレンチ構造なしの場合、図15が矩形トレンチ構造ありの場合、図16がU字トレンチ構造(θ1=90°、R=0.125Lまたは1/(1×107)(m))ありの場合、図17が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))ありの場合、図18が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))+底面p型層ありの場合、図19が台形トレンチ構造(θ1=115°>90°、R=0.125Lまたは1/(1×107)(m))+側面p型層ありの場合をそれぞれ示す。図14〜図19において、図12および図13に示す各部に相当する部分には、それらの各部に付した参照符号と同一の参照符号を付している。

【0085】

まず、図14〜図19の構造を、以下のように設計した。

・n+型基板2:濃度が1×1019cm−3 厚さが1μm

・n−型エピタキシャル層6:濃度が1×1016cm−3 厚さが5μm

・トレンチ42,42´,42´´:深さが1.05μm

・トレンチ42,42´,42´´のエッジ部45の曲率半径R:

・p型層46:濃度が1×1018cm−3

そして、図14〜図19それぞれの構造を有するショットキーバリアダイオード41のアノード−カソード間に逆方向電圧(600V)を印加したときの、エピタキシャル層6内の電界強度分布をシミュレーションした。なお、シミュレータとして、Synopsys社製のTCAD(製品名)を使用した。

【0086】

図14に示すように、いかなる形状のトレンチ構造も形成されておらず、エピタキシャル層6の表面12が平らなショットキーバリアダイオードでは、エピタキシャル層6の裏面11から表面12へ向かうにしたがって電界強度が強くなり、エピタキシャル層6の表面12で最大(1.5×106V/cm程度)であった。

また、図15に示すように、エッジ部45が鋭利な形状の矩形トレンチ42´構造が形成されたショットキーバリアダイオードでは、矩形トレンチ42´構造の形成により、互いに隣り合う矩形トレンチ42´で挟まれる部分(単位セル20)での電界強度を弱めることができた。たとえば、単位セル20の中央部27の電界強度を、9×105V/cm程度にまで弱めることができた。

【0087】

また、図16および図17に示すように、U字トレンチ42´´および台形トレンチ42構造が形成され、これらのトレンチ42,42´´の内面にp型層46が形成されていないショットキーバリアダイオードでは、トレンチ42,42´´構造の形成により、互いに隣り合う台形トレンチ42で挟まれる部分(単位セル20)での電界強度が弱められており、さらに、電界強度が最大となる部分が台形トレンチ42の底面43全体にシフトしていた。具体的には、単位セル20の中央部27の電界強度が9×105V/cm程度、単位セル20の周縁部26の電界強度が3×105V/cm程度にまで弱められており、台形トレンチ42の底面43全体の電界強度が1.5×106V/cm程度で最大であった。

【0088】

また、図18に示すように、台形トレンチ42の底面43およびエッジ部45にp型層46が形成されたショットキーバリアダイオードでは、台形トレンチ42の底面43での電界強度が弱められており、電界強度が最大となる部分が台形トレンチ42の側面44にシフトしていた。具体的には、台形トレンチ42の底面43の電界強度が3×105V/cm以下にまで弱められており、台形トレンチ42の側面44の下部の電界強度が1.5×106V/cmで最大であった。

【0089】

さらに、図12と同様の構成である図19のショットキーバリアダイオードでは、台形トレンチ42の側面44にもp型層46が形成されていることにより、台形トレンチ42の側面44での電界強度が弱められており、電界集中部分を台形トレンチ42の内面から遠ざけていることを確認できた。具体的には、台形トレンチ42の側面44の電界強度が3×105V/cm以下にまで弱められており、台形トレンチ42の内面の周囲には、電界強度が1.5×106V/cmとなる領域がなかった。

【0090】

これらの結果、とりわけ図12のショットキーバリアダイオード41では、ショットキーバリアダイオード41全体としての逆方向リーク電流を確実に低減できることを確認できた。すなわち、図12の構造を有するショットキーバリアダイオード41では、降伏電圧に近い逆方向電圧を印加しても逆方向リーク電流を確実に低減できるので、ワイドバンドギャップ半導体の耐圧性能を十分に活かすことができる。

【0091】

しかも、後述する図21Fの工程のように、台形トレンチ42をドライエッチングで形成する場合、台形トレンチ42の側面44がエッチング時にダメージを受け、当該側面44とアノード電極21との間にショットキー障壁を設計通りに形成できない場合がある。そこで本実施形態のショットキーバリアダイオード41では、エッチング時にハードマスク52(後述)で覆われて保護された(後述する図21Eの工程)エピタキシャル層6の表面12を主としてショットキー界面とし、ダメージを受けた側面44にはp型層46を形成している。これにより、台形トレンチ42の側面44を有効利用することができる。また、台形トレンチ42の側面44における電界強度の高い部分に障壁の高いpn接合を形成し、リーク電流を低減することができる。

<SiC−pnダイオード47内蔵の効果>

次に、図20を参照して、p型層46にコンタクト層48を形成して、エピタキシャル層6にpnダイオード47を内蔵させたときの効果について説明する。

【0092】

図20は、ショットキーバリアダイオード41の電流−電圧(I−V)曲線を示すグラフである。

図12の構造のショットキーバリアダイオード41に対して、順方向電圧を1V〜7Vまで変化させながら印加することにより通電試験を行った。そして、印加電圧を1V〜7Vまで変化させたときのショットキーバリアダイオード41のpn接合部に流れる電流の変化量を評価した。

【0093】

一方、p型層46のコンタクト層48を形成していないこと以外は、図12の構造と同じショットキーバリアダイオード41に対して、上記と同様の通電試験を行い、pn接合部に流れる電流の変化量を評価した。

図20に示すように、p型層46にコンタクト層48が形成されていないpn接合部では、印加電圧が4Vを超えるあたりから電流がほとんど増加せずにほぼ一定であった。

【0094】

これに対し、p型層46にコンタクト層48が形成され、pnダイオード47が内蔵されたショットキーバリアダイオード41では、印加電圧が4Vを超えるあたりからの電流の増加割合が、4V以下までの増加割合に比べて急激に増えていた。

これにより、図12において、ショットキーバリアダイオード41に並列に設けられたpnダイオード47にアノード電極21(ショットキー電極)をオーミック接合させておけば、ショットキーバリアダイオード41に大きなサージ電流が流れても、内蔵pnダイオード47をオンさせて、当該サージ電流の一部を内蔵pnダイオード47に流すことができることを確認できた。その結果、ショットキーバリアダイオード41に流れるサージ電流を低減できるので、サージ電流によるショットキーバリアダイオード41の熱破壊を防止することができることを確認できた。

<ショットキーバリアダイオード41(第2実施形態)の製造方法>

次に、図21A〜図21Jを参照して、図12のショットキーバリアダイオード41の製造方法について説明する。

【0095】

まず、図21Aに示すように、基板2の上に、バッファ層7、ベースドリフト層8、低抵抗ドリフト層9および表面ドリフト層10をこの順にエピタキシャル成長させる。

次に、図21Bに示すように、たとえばCVD法により、エピタキシャル層6の表面12にSiO2からなるハードマスク49を形成する。ハードマスク49の厚さは、好ましくは、1.5μm〜10μmである。次に、ハードマスク49をパターニングした後、当該ハードマスク49を介して、エピタキシャル層6をドライエッチングする。これにより、バッファ層7に達するストライプ状のトレンチ50を形成する。トレンチ50の深さは、p型ピラー層17の深さDSJに合わせて適宜設定する。また、トレンチ50は、深さDSJに応じて、ハードマスクを形成する工程、当該ハードマスクを用いてドライエッチングする工程およびドライエッチング後に当該ハードマスクを除去する工程を複数回繰り返すことにより形成してもよい。

【0096】

次に、ハードマスク49を除去した後、図21Cに示すように、そのトレンチ50内部からエピタキシャル層6の表面12が覆われるまで、p型のSiC層51をエピタキシャル成長させる。

次に、図21Dに示すように、エピタキシャル層6の表面12を覆うトレンチ50外のSiC層51を、たとえばエッチバックにより除去する。これにより、トレンチ50に埋め込まれたp型ピラー層17が形成され、同時に、互いに隣り合うp型ピラー層17の間にn型ピラー層18が形成される。

【0097】

次に、図21Eに示すように、たとえばCVD法より、エピタキシャル層6の表面12にSiO2からなるハードマスク52を形成する。ハードマスク52の厚さは、好ましくは、1μm〜3μmである。次に、ハードマスク52をパターニングする。このとき、ハードマスク52の厚さに対してエッチング量(厚さ)が1〜1.5倍となるようにエッチング条件を設定する。具体的には、ハードマスク52の厚さが1μm〜3μmである場合には、エッチング量が1μm〜4.5μmとなるように、エッチング条件(ガス種、エッチング温度)を設定する。これにより、エピタキシャル層6に対するオーバーエッチング量を一般的な量よりも少なくすることができるので、エッチング後のハードマスク52の開口53の側面下部に、エピタキシャル層6の表面12に対して角度θ1(100°〜170°>90°)で傾斜するエッジ部54を形成することができる。

【0098】

次に、図21Fに示すように、当該ハードマスク52を介して、エピタキシャル層6を表面12から最深部が低抵抗ドリフト層9の途中部に達する深さまでドライエッチングすることにより、各p型層46の上端部に台形トレンチ42および環状トレンチ69を同時に形成する。このときのエッチング条件は、ガス種:O2+SF6+HBr、バイアス:20W〜100W、装置内圧力:1Pa〜10Paとする。これにより、台形トレンチ42のエッジ部45を湾曲する形状に形成することができる。また、ハードマスク52の開口53の側面下部に所定角度θ1のエッジ部54が形成されているので、台形トレンチ42の側面44を、台形トレンチ42の底面43に対して角度θ1で傾斜させることができる。

【0099】

次に、図21Gに示すように、台形トレンチ42の形成に使用したハードマスク52を残存させたまま、環状トレンチ69におけるガードリング72を形成すべき部分以外の部分を覆うレジスト73を形成する。そして、当該レジスト73およびハードマスク52を介して、台形トレンチ42へ向かってp型不純物(たとえば、アルミニウム(Al))を注入する。p型不純物のドーピングは、たとえば、エピタキシャル層6の表面12に対して深い位置から順に、注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法により達成される。

【0100】

本実施形態では、たとえば、5段階にわたって注入する。各段階の注入エネルギ(keV)およびドーズ量(cm−2)は、1段目:380keV 2.0×1013cm−2、2段目:260keV 1.5×1013cm−2、3段目:160keV 1.0×1013cm−2、4段目:60keV 2.0×1015cm−2、5段目:30keV 1.0×1015cm−2である。

【0101】

次に、図21Hに示すように、所定パターンのハードマスク55を形成し、このハードマスク55を介して、台形トレンチ42へ向かってp型不純物(たとえば、アルミニウム(Al))を注入する。p型不純物のドーピングは、図21Gの工程と同様に、エピタキシャル層6の表面12に対して深い位置から順に、注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法により達成される。本実施形態では、前述と同じ条件の5段階注入を採用する。注入エネルギが段階的に小さくなり、ドーズ量が段階的に大きくなるようにp型不純物イオンを複数段にわたって注入する多段注入法を採用することにより、p型層46およびコンタクト層48に対してオーミックコンタクトを形成しやすくすることができる。

【0102】

不純物のドーピングの後、図21Iに示すように、たとえば、1700℃でアニール処理することにより、p型層46、コンタクト層48およびガードリング72が同時に形成される。

その後、図21Jに示すように、フィールド絶縁膜16、アノード電極21、表面保護膜29、カソード電極4等を形成する。

【0103】

以上の工程を経て、図12のショットキーバリアダイオード41が得られる。

このような形成方法によれば、台形トレンチ42の形成時に使用したハードマスク52を用いてイオン注入するので、p型層46を形成するにあたって、マスクを形成する工程を増やす必要がない。

また、ハードマスク52の厚さを適切に調整することにより、設計通りの台形トレンチ42を精密に形成できるとともに、イオン注入の際には、台形トレンチ42以外の箇所(たとえば、単位セル20の頂部)に不純物が注入されることを防止することができる。よって、アノード電極21とのショットキー接合のためのn型の領域を確保することができる。

【0104】

しかも、台形トレンチ42では、底面43だけでなく側面44の全部も台形トレンチ42の開放端に対して対向することとなる。そのため、台形トレンチ42を介してp型不純物をエピタキシャル層6に注入する場合に、台形トレンチ42の開放端から台形トレンチ42内に入射した不純物を、台形トレンチ42の側面44に確実に当てることができる。その結果、p型層46を容易に形成することができる。

<トレンチの断面形状の変形例>

次に、図22(a)〜図22(f)を参照して、台形トレンチ42の断面形状の変形例について説明する。

【0105】

図22(a)〜図22(f)は、トレンチの断面形状の変形例を示す図であって、図22(a)が第1変形例、図22(b)が第2変形例、図22(c)が第3変形例、図22(d)が第4変形例、図22(e)が第5変形例、図22(f)が第6変形例をそれぞれ示す。

台形トレンチ42では、たとえば、図22(a)に示すように、コンタクト層48が、p型層46と同様に、底面43からエッジ部45を経て台形トレンチ42の開口端に至るまで、台形トレンチ42の内面全体にわたって形成されていてもよい。

【0106】

また、図12および図13の説明では、台形トレンチ42の断面形状として、各台形トレンチ42の側面44が底面43に対して角度θ1(>90°)で傾斜する場合のみを例に挙げたが、トレンチの断面形状は、これに限らない。

たとえば、台形トレンチ42は、側面44の全部が傾斜している必要はなく、たとえば、図22(b)(c)の選択的台形トレンチ56のように、側面57の一部(側面の下部58)が選択的に台形(テーパ形状)になっており、側面57の他の部分(側面の上部59)は、底面60に対して90°の角度を形成していてもよい。この場合、p型層46は、選択的台形トレンチ56の底面60からエッジ部61を経て側面の下部58(台形部)のみに形成されている。また、コンタクト層48は、図22(b)に示すように、選択的台形トレンチ56の底面60のみに形成されていてもよいし、図22(c)に示すように、p型層46と同様に、選択的台形トレンチ56の底面60からエッジ部61を経て側面の下部58の上端に至るまで形成されていてもよい。

【0107】

そして、図22(b)(c)の構造においても、側面の下部58が選択的台形トレンチ56の開放端に対して対向することとなるので、p型層46を容易に形成することができる。

また、トレンチは、側面が傾斜している必要はなく、たとえば、図22(d)(e)(f)のU字トレンチ62のように、底面63に対して側面64が90°(垂直)であってもよい。この場合、p型層46は、図22(d)(e)に示すように、U字トレンチ62の底面63からエッジ部65を経てU字トレンチ62の開口端に至るまで形成されていてもよいし、図22(f)に示すように、U字トレンチ62の底面63およびエッジ部65のみに形成されていてもよい。また、コンタクト層48は、図22(d)(f)に示すように、U字トレンチ62の底面63のみに形成されていてもよいし、図22(e)に示すように、p型層46と同様に、U字トレンチ62の底面63からエッジ部65を経てU字トレンチ62の開口端に至るまで形成されていてもよい。

【0108】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、図2Aのショットキーバリアダイオード1において、p型ピラー層17は、図23に示すように、その最深部がバッファ層7の厚さ方向途中に位置していてもよいし、図24に示すように、バッファ層7に対して間隔が空くように位置していてもよい。

また、エピタキシャル層6は、図25に示すように、その表面12に沿ってp型ピラー層17を横切る方向にn型の中間層66をさらに含んでいてもよい。これにより、p型ピラー層17は、中間層66に対してエピタキシャル層6の表面12側の上側部分67と、エピタキシャル層6の裏面11側の下側部分68とに分割されていてもよい。なお、図23〜図25の変形例については、図12のショットキーバリアダイオード41にも採用することができる。

【0109】

また、前述のショットキーバリアダイオード1,41の各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、ショットキーバリアダイオード1,41において、p型の部分がn型であり、n型の部分がp型であってもよい。

また、エピタキシャル層6は、SiCからなるエピタキシャル層に限らず、SiC以外のワイドバンドギャップ半導体、たとえば絶縁破壊電界が2MV/cmよりも大きい半導体であって、具体的には、GaN(絶縁破壊電界が約3MV/cmであり、バンドギャップの幅が約3.42eV)、ダイヤモンド(絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約5.47eV)などであってもよい。

【0110】

また、p型ピラー層17の平面形状は、ストライプ状である必要はなく、たとえば、行列状、千鳥状であってもよい。ただし、ストライプ状のp型ピラー層17であれば、p型ピラー層17を形成するときのトレンチ32の側面の面方位が行列状および千鳥状の場合に比べて少なくなり(4面→2面になる)、注入するp型不純物の濃度を制御し易いので好ましい。

【0111】

また、アノード電極21としては、たとえば、前述のアルミニウム、ポリシリコンの他、たとえば、モリブデン(Mo)、チタン(Ti)などを使用することにより、エピタキシャル層6に対してショットキー接合(ヘテロ接合)させることができる。

また、電界緩和層19を形成するためのp型不純物としては、たとえば、Al(アルミニウム)などを使用することもできる。

【0112】

本発明の半導体装置(半導体パワーデバイス)は、たとえば、電気自動車(ハイブリッド車を含む)、電車、産業用ロボットなどの動力源として利用される電動モータを駆動するための駆動回路を構成するインバータ回路に用いられるパワーモジュールに組み込むことができる。また、太陽電池、風力発電機その他の発電装置(とくに自家発電装置)が発生する電力を商用電源の電力と整合するように変換するインバータ回路に用いられるパワーモジュールにも組み込むことができる。

【0113】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0114】

1 ショットキーバリアダイオード

2 基板

3 (基板の)裏面

4 カソード電極

5 (基板の)表面

6 エピタキシャル層

7 バッファ層

8 ベースドリフト層

9 低抵抗ドリフト層

10 表面ドリフト層

11 (エピタキシャル層の)裏面

12 (エピタキシャル層の)表面

13 活性領域

14 コンタクトホール

15 フィールド領域

16 フィールド絶縁膜

17 p型ピラー層

18 n型ピラー層

19 電界緩和層

20 単位セル

21 アノード電極

22 ショットキーメタル

23 コンタクトメタル

24 第1メタル

25 第2メタル

26 (単位セルの)周縁部

27 (単位セルの)中央部

28 ガードリング

29 表面保護膜

30 開口

31 ハードマスク

32 トレンチ

33 SiC層

34 ハードマスク

35 高濃度不純物層

41 ショットキーバリアダイオード

42 台形トレンチ

43 (トレンチの)底面

44 (トレンチの)側面

45 (トレンチの)エッジ部

46 p型層

47 pnダイオード

48 コンタクト層

49 ハードマスク

50 トレンチ

51 SiC層

52 ハードマスク

53 (ハードマスクの)開口

54 (ハードマスクの)エッジ部

55 ハードマスク

56 選択的台形トレンチ

57 (選択的台形トレンチの)側面

58 (選択的台形トレンチの)側面の下部

59 (選択的台形トレンチの)側面の上部

60 (選択的台形トレンチの)底面

61 (選択的台形トレンチの)エッジ部

62 U字トレンチ

63 (U字トレンチの)底面

64 (U字トレンチの)側面

65 (U字トレンチの)エッジ部

66 中間層

67 (p型ピラー層の)上側部分

68 (p型ピラー層の)下側部分

69 環状トレンチ

70 (環状トレンチの)底面

71 (環状トレンチの)側面

72 ガードリング

73 レジスト

【特許請求の範囲】

【請求項1】

表面および裏面を有する第1導電型のワイドバンドギャップ半導体からなる半導体層と、

前記半導体層の前記表面に接するように形成されたショットキー電極とを含み、

前記半導体層には、

前記表面に沿う方向に互いに間隔を空けて配列され、それぞれが前記表面から前記裏面へ向かって前記半導体層の厚さ方向に延びる柱状であり、前記半導体層の第1導電型の他の部分と協働して前記半導体層にスーパージャンクション構造を形成する第2導電型の複数のピラー層と、

前記表面の近傍に選択的に形成され、前記表面における電界強度を緩和するための電界緩和部とが形成されている、半導体装置。

【請求項2】

前記電界緩和部は、前記ピラー層の上端部に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記電界緩和部は、前記半導体層の前記表面に前記半導体層の一部を利用して形成され、前記ピラー層よりも不純物濃度の高い第2導電型を示す、電界緩和層を含む、請求項1または2に記載の半導体装置。

【請求項4】

前記電界緩和層は、前記半導体層の残りの部分よりも高い抵抗を有する高抵抗層を含む、請求項3に記載の半導体装置。

【請求項5】

前記高抵抗層は、前記半導体層の前記表面から不純物イオンを注入した後、1500℃未満のアニール処理をすることによって形成される、請求項4に記載の半導体装置。

【請求項6】

前記高抵抗層の不純物の活性化率は、5%未満である、請求項4または5に記載の半導体装置。

【請求項7】

前記高抵抗層のシート抵抗は、1MΩ/□以上である、請求項4〜6のいずれか一項に記載の半導体装置。

【請求項8】

前記電界緩和部は、前記半導体層の前記表面から掘り下がったトレンチを含む、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記トレンチの側面と底面とが交わって形成されたトレンチのエッジ部は、下記式(1)を満たす曲率半径Rを有する、請求項8に記載の半導体装置。

0.01L<R<10L・・・(1)

(ただし、式(1)において、Lはトレンチの幅方向に沿って対向するエッジ部間の直線距離を示している。)

【請求項10】

前記電界緩和部は、前記トレンチの前記底面および前記エッジ部に前記半導体層の一部を利用して形成された第2導電型の底部緩和層をさらに含む、請求項9に記載の半導体装置。

【請求項11】

前記電界緩和部は、前記底部緩和層と一体的であり、前記トレンチの前記側面に前記半導体層の一部を利用して形成された第2導電型の側部緩和層をさらに含む、請求項10に記載の半導体装置。

【請求項12】

前記側部緩和層は、前記トレンチの前記側面に沿って前記トレンチの開口端に至るように形成されている、請求項11に記載の半導体装置。

【請求項13】

前記トレンチは、平面形状の底面および当該平面形状の底面に対して90°を超える角度で傾斜した側面を有するテーパトレンチを含む、請求項8〜12のいずれか一項に記載の半導体装置。

【請求項14】

前記ショットキー電極は、前記トレンチに埋め込まれるように形成されており、

前記半導体層における前記トレンチの底面を形成する部分には、前記トレンチに埋め込まれた前記ショットキー電極との間にオーミック接合を形成する第2導電型のコンタクト層がさらに形成されている、請求項8〜13のいずれか一項に記載の半導体装置。

【請求項15】

前記半導体層は、逆方向電圧印加時に第1電界がかかる第1部分および当該第1電界に対して相対的に高い第2電界がかかる第2部分を、前記電界緩和部とは異なる部分に有しており、

前記ショットキー電極は、前記第1部分との間に第1ショットキー障壁を形成する第1電極と、前記第2部分との間に前記第1ショットキー障壁に対して相対的に高い第2ショットキー障壁を形成する第2電極とを含む、請求項1〜14のいずれか一項に記載の半導体装置。

【請求項16】

前記半導体層は、第1不純物濃度を有するベースドリフト層と、前記ベースドリフト層上に形成され、前記第1不純物濃度に対して相対的に高い第2不純物濃度を有する低抵抗ドリフト層とを含み、

前記電界緩和部は、その最深部が前記低抵抗ドリフト層に達するように形成され、前記半導体層の一部を単位セルとして区画している、請求項1〜15のいずれか一項に記載の半導体装置。

【請求項17】

前記ベースドリフト層の前記第1不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少している、請求項16に記載の半導体装置。

【請求項18】

前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって一定である、請求項16または17に記載の半導体装置。

【請求項19】

前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少している、請求項16または17に記載の半導体装置。

【請求項20】

前記半導体層は、前記低抵抗ドリフト層上に形成され、前記第2不純物濃度に対して相対的に低い第3不純物濃度を有する表面ドリフト層をさらに含む、請求項16〜19のいずれか一項に記載の半導体装置。

【請求項21】

前記半導体層を支持する第1導電型のワイドバンドギャップ半導体からなる基板をさらに含み、

前記半導体層は、前記基板上に形成され、前記第1不純物濃度に対して相対的に高い第4不純物濃度を有するバッファ層をさらに含む、請求項16〜20のいずれか一項に記載の半導体装置。

【請求項22】

前記ピラー層の下端部は、前記バッファ層に接している、請求項21に記載の半導体装置。

【請求項23】

前記ピラー層の下端部は、前記バッファ層に対して間隔が空くように位置している、請求項21に記載の半導体装置。

【請求項24】

前記ワイドバンドギャップ半導体の絶縁破壊電界が1MV/cmよりも大きい、請求項1〜23のいずれか一項に記載の半導体装置。

【請求項25】

前記ワイドバンドギャップ半導体が、SiC、GaNまたはダイヤモンドである、請求項1〜24のいずれか一項に記載の半導体装置。

【請求項1】

表面および裏面を有する第1導電型のワイドバンドギャップ半導体からなる半導体層と、

前記半導体層の前記表面に接するように形成されたショットキー電極とを含み、

前記半導体層には、

前記表面に沿う方向に互いに間隔を空けて配列され、それぞれが前記表面から前記裏面へ向かって前記半導体層の厚さ方向に延びる柱状であり、前記半導体層の第1導電型の他の部分と協働して前記半導体層にスーパージャンクション構造を形成する第2導電型の複数のピラー層と、

前記表面の近傍に選択的に形成され、前記表面における電界強度を緩和するための電界緩和部とが形成されている、半導体装置。

【請求項2】

前記電界緩和部は、前記ピラー層の上端部に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記電界緩和部は、前記半導体層の前記表面に前記半導体層の一部を利用して形成され、前記ピラー層よりも不純物濃度の高い第2導電型を示す、電界緩和層を含む、請求項1または2に記載の半導体装置。

【請求項4】

前記電界緩和層は、前記半導体層の残りの部分よりも高い抵抗を有する高抵抗層を含む、請求項3に記載の半導体装置。

【請求項5】

前記高抵抗層は、前記半導体層の前記表面から不純物イオンを注入した後、1500℃未満のアニール処理をすることによって形成される、請求項4に記載の半導体装置。

【請求項6】

前記高抵抗層の不純物の活性化率は、5%未満である、請求項4または5に記載の半導体装置。

【請求項7】

前記高抵抗層のシート抵抗は、1MΩ/□以上である、請求項4〜6のいずれか一項に記載の半導体装置。

【請求項8】

前記電界緩和部は、前記半導体層の前記表面から掘り下がったトレンチを含む、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記トレンチの側面と底面とが交わって形成されたトレンチのエッジ部は、下記式(1)を満たす曲率半径Rを有する、請求項8に記載の半導体装置。

0.01L<R<10L・・・(1)

(ただし、式(1)において、Lはトレンチの幅方向に沿って対向するエッジ部間の直線距離を示している。)

【請求項10】

前記電界緩和部は、前記トレンチの前記底面および前記エッジ部に前記半導体層の一部を利用して形成された第2導電型の底部緩和層をさらに含む、請求項9に記載の半導体装置。

【請求項11】

前記電界緩和部は、前記底部緩和層と一体的であり、前記トレンチの前記側面に前記半導体層の一部を利用して形成された第2導電型の側部緩和層をさらに含む、請求項10に記載の半導体装置。

【請求項12】

前記側部緩和層は、前記トレンチの前記側面に沿って前記トレンチの開口端に至るように形成されている、請求項11に記載の半導体装置。

【請求項13】

前記トレンチは、平面形状の底面および当該平面形状の底面に対して90°を超える角度で傾斜した側面を有するテーパトレンチを含む、請求項8〜12のいずれか一項に記載の半導体装置。

【請求項14】

前記ショットキー電極は、前記トレンチに埋め込まれるように形成されており、

前記半導体層における前記トレンチの底面を形成する部分には、前記トレンチに埋め込まれた前記ショットキー電極との間にオーミック接合を形成する第2導電型のコンタクト層がさらに形成されている、請求項8〜13のいずれか一項に記載の半導体装置。

【請求項15】

前記半導体層は、逆方向電圧印加時に第1電界がかかる第1部分および当該第1電界に対して相対的に高い第2電界がかかる第2部分を、前記電界緩和部とは異なる部分に有しており、

前記ショットキー電極は、前記第1部分との間に第1ショットキー障壁を形成する第1電極と、前記第2部分との間に前記第1ショットキー障壁に対して相対的に高い第2ショットキー障壁を形成する第2電極とを含む、請求項1〜14のいずれか一項に記載の半導体装置。

【請求項16】

前記半導体層は、第1不純物濃度を有するベースドリフト層と、前記ベースドリフト層上に形成され、前記第1不純物濃度に対して相対的に高い第2不純物濃度を有する低抵抗ドリフト層とを含み、

前記電界緩和部は、その最深部が前記低抵抗ドリフト層に達するように形成され、前記半導体層の一部を単位セルとして区画している、請求項1〜15のいずれか一項に記載の半導体装置。

【請求項17】

前記ベースドリフト層の前記第1不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少している、請求項16に記載の半導体装置。

【請求項18】

前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって一定である、請求項16または17に記載の半導体装置。

【請求項19】

前記低抵抗ドリフト層の前記第2不純物濃度は、前記半導体層の前記裏面から前記表面へ向かうにしたがって減少している、請求項16または17に記載の半導体装置。

【請求項20】

前記半導体層は、前記低抵抗ドリフト層上に形成され、前記第2不純物濃度に対して相対的に低い第3不純物濃度を有する表面ドリフト層をさらに含む、請求項16〜19のいずれか一項に記載の半導体装置。

【請求項21】

前記半導体層を支持する第1導電型のワイドバンドギャップ半導体からなる基板をさらに含み、

前記半導体層は、前記基板上に形成され、前記第1不純物濃度に対して相対的に高い第4不純物濃度を有するバッファ層をさらに含む、請求項16〜20のいずれか一項に記載の半導体装置。

【請求項22】

前記ピラー層の下端部は、前記バッファ層に接している、請求項21に記載の半導体装置。

【請求項23】

前記ピラー層の下端部は、前記バッファ層に対して間隔が空くように位置している、請求項21に記載の半導体装置。

【請求項24】

前記ワイドバンドギャップ半導体の絶縁破壊電界が1MV/cmよりも大きい、請求項1〜23のいずれか一項に記載の半導体装置。

【請求項25】

前記ワイドバンドギャップ半導体が、SiC、GaNまたはダイヤモンドである、請求項1〜24のいずれか一項に記載の半導体装置。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図11C】

【図11D】

【図11E】

【図11F】

【図11G】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21A】

【図21B】

【図21C】

【図21D】

【図21E】

【図21F】

【図21G】

【図21H】

【図21I】

【図21J】

【図22】

【図23】

【図24】

【図25】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図11C】

【図11D】

【図11E】

【図11F】

【図11G】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21A】

【図21B】

【図21C】

【図21D】

【図21E】

【図21F】

【図21G】

【図21H】

【図21I】

【図21J】

【図22】

【図23】

【図24】

【図25】

【公開番号】特開2013−89723(P2013−89723A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−227965(P2011−227965)

【出願日】平成23年10月17日(2011.10.17)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月17日(2011.10.17)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]