半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

【発明の詳細な説明】

【技術分野】

【0001】

技術分野は、半導体装置、半導体装置の駆動方法、及び半導体装置の作製方法に関する。半導体装置としては、特に、トランジスタ等の半導体素子を有する半導体集積回路に関する。

【背景技術】

【0002】

半導体集積回路の一つとして、プログラマブルロジックデバイス(Programmable Logic Device(PLD))がある。PLDは、製造後に内部の回路構成等について、決定・変更等が可能(再構成可能)な集積回路である(特許文献1参照)。

【0003】

PLDは、従来のASIC(Application Specific Integrated Circuit)などに比べて、開発期間の短縮が可能であり、設計仕様の変更に柔軟に対応できるなどの利点を有しており、様々な装置への利用が進んでいる。

【0004】

PLDは、例えば、複数の論理回路部と、論理回路部間の配線と、を有する。各論理回路部内の回路構成を変更、又は、論理回路部間の接続関係を変更することで、PLDの機能を変更することができる。

【0005】

更に、PLDは、記憶回路を有してもよく、当該記憶回路により論理回路部内の回路構成の情報や論理回路部間の接続関係の情報を記憶しておくことができる。

【0006】

なお、上記論理回路部としては、例えば演算論理ユニット(Arithmetic Logic Unit(ALU))が用いられる。ALUは、一般的に、加算器や減算器等を組み合わせた算術演算部と、AND回路やOR回路等を組み合わせた論理演算部と、シフト回路を有するシフト演算部と、それらを選択して出力するマルチプレクサ等の選択回路と、によって構成されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平11−317659号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記記憶回路としてSRAM又はDRAMを用いる場合、ALU間の接続関係の変更、又は各ALU内の回路構成の変更などを高速に行うことができる。しかし、SRAMやDRAMは揮発性であるため、電源電圧の供給を停止すると、記憶されていた情報が失われてしまう。

【0009】

また、上記記憶回路としてフラッシュメモリを用いる場合、不揮発性であるため、電源電圧の供給を停止しても情報を維持することができる。しかし、駆動電圧が高いため、高速動作や消費電力の低減を行うことは困難である。

【0010】

以上を鑑み、本発明の一様態では、電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を長時間維持できる半導体装置を提供することを課題の一とする。

【0011】

また、本発明の一様態では、論理回路部間の接続関係の変更、又は、各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0012】

本発明の一態様は、回路構成等の情報を記憶する記憶回路を有し、当該記憶回路内に酸化物半導体を用いた半導体素子を有する半導体装置である。具体的には、半導体装置はPLD(Programmable Logic Device)であり、論理回路部と、記憶回路と、を有する。そして、当該記憶回路に記憶されたデータに応じて論理回路部内の回路構成を維持する。

【0013】

また、半導体装置は、上記論理回路部を複数個有することが好ましく、その場合、上記記憶回路は、各論理回路部の回路構成、又は、論理回路部間の接続関係を維持する。論理回路部は、ALU(Arithmetic Logic Unit)を用いることができ、演算回路や選択回路等を有してもよい。

【0014】

なお、本明細書ではPLDのことを、再構成可能な回路とも呼ぶ。

【0015】

また、本明細書において、半導体装置とは、半導体を利用することで機能する物(素子、装置など)全般を指す。半導体装置は、半導体素子(トランジスタ、ダイオード等)、その半導体素子を搭載した電気装置(電子回路、表示装置、発光装置等)、およびその電気装置を搭載した電子機器をその範疇とする。

【0016】

本発明の他の一態様は、複数の演算回路と、選択回路と、記憶回路と、を有し、記憶回路は、トランジスタと、容量素子と、を有し、記憶回路は、トランジスタを介して容量素子及び選択回路にデータを入力し、選択回路は、データに応じて、複数の演算回路の演算結果の内の一つ又は複数を選択し、トランジスタのチャネル形成領域には、酸化物半導体が用いられている半導体装置である。

【0017】

本発明の他の一態様は、複数の論理回路部と、接続部と、を有し、接続部は、記憶回路と、第1のトランジスタと、を有し、第1のトランジスタのソース又はドレインの一方は、複数の論理回路部のうちの一つと電気的に接続され、第1のトランジスタのソース又はドレインの他方は、複数の論理回路部のうちの他の一つと電気的に接続され、記憶回路は、第2のトランジスタと、容量素子と、を有し、記憶回路は、第2のトランジスタを介して容量素子及び第1のトランジスタのゲートにデータを入力し、第1のトランジスタは、データに応じて、複数の論理回路部のうちの一つと他の一つとの電気的な接続を制御し、第2のトランジスタのチャネル形成領域には、酸化物半導体が用いられている半導体装置である。

【0018】

本発明の他の一態様は、複数の論理回路部と、第1の記憶回路と、接続部と、を有し、複数の論理回路部は、複数の演算回路と、選択回路と、を有し、第1の記憶回路は、第1のトランジスタと、第1の容量素子と、を有し、第1の記憶回路は、第1のトランジスタを介して第1の容量素子及び選択回路に第1のデータを入力し、選択回路は、第1のデータに応じて、複数の演算回路の演算結果の内の一つ又は複数を選択し、接続部は、第2の記憶回路と、第2のトランジスタと、を有し、第2のトランジスタのソース又はドレインの一方は、複数の論理回路部のうちの一つと電気的に接続され、第2のトランジスタのソース又はドレインの他方は、複数の論理回路部のうちの他の一つと電気的に接続され、第2の記憶回路は、第3のトランジスタと、第2の容量素子と、を有し、第2の記憶回路は、第3のトランジスタを介して第2の容量素子及び第2のトランジスタのゲートにデータを入力し、第2のトランジスタは、データに応じて、複数の論理回路部のうちの一つと他の一つとの電気的な接続を制御し、第1のトランジスタ及び第3のトランジスタは、チャネル形成領域に酸化物半導体が用いられている半導体装置である。

【発明の効果】

【0019】

本発明の一様態により、電源電圧の供給を停止しても、論理回路部間の接続関係の情報、又は、各論理回路部内の回路構成の情報を長時間保持できる半導体装置を提供することができる。

【0020】

また、本発明の一様態により、論理回路部間の接続関係の変更、又は各論理回路部の回路構成の変更を、高速又は低消費電力で行うことが可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0021】

【図1】半導体装置の一例を説明するための図。

【図2】半導体装置の一例を説明するための図。

【図3】半導体装置の一例を説明するための図。

【図4】半導体装置の一例を説明するための図。

【図5】半導体装置の一例を説明するための図。

【図6】半導体装置の一例を説明するための図。

【図7】半導体装置の一例を説明するための図。

【図8】CAACの一例を説明するための図。

【図9】CAACの一例を説明するための図。

【図10】CAACの一例を説明するための図。

【図11】半導体装置の作製方法の一例を説明するための図。

【図12】トランジスタのゲート電圧と電界効果移動度との関係を説明するための図。

【図13】半導体装置の断面構造の一例を説明するための図。

【図14】半導体装置における電気特性の計算結果を説明するための図。

【図15】半導体装置における電気特性の計算結果を説明するための図。

【図16】半導体装置における電気特性の計算結果を説明するための図。

【図17】半導体装置における電気特性の測定結果を説明するための図。

【図18】半導体装置における電気特性の測定結果を説明するための図。

【図19】半導体装置における電気特性の測定結果を説明するための図。

【図20】半導体装置における酸化物半導体膜のXRD測定結果を説明するための図。

【図21】半導体装置の特性を説明するための図。

【図22】半導体装置の特性を説明するための図。

【図23】半導体装置の特性を説明するための図。

【図24】演算処理装置の一例を説明するための図。

【図25】電子機器の一例を説明するための図。

【図26】CAACの一例を説明するための図。

【図27】半導体装置の一例を説明するための図。

【発明を実施するための形態】

【0022】

以下では、実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0023】

なお、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れかわることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れかえて用いることができるものとする。

【0024】

「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限はない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【0025】

回路図上は独立している構成要素どうしが電気的に接続しているように図示されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0026】

「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

【0027】

図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0028】

「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものである。

【0029】

(実施の形態1)

本実施の形態では、半導体装置の一例について説明する。

【0030】

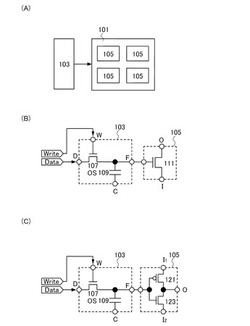

図1(A)に、半導体装置のブロック図の一例を示す。

【0031】

図1(A)の半導体装置は、論理回路部101と、記憶回路103と、を有する。論理回路部101は、複数の論理回路105を有する。そして、半導体装置では、記憶回路103に記憶されたデータ(信号ともいう)に応じて、複数の論理回路105のうちの一つ又は複数が選択され、論理回路部101内の回路構成が決定される。

【0032】

論理回路部101の一例として、ALUなどが挙げられる。複数の論理回路105としては、加算器、減算器、乗算器、AND回路、OR回路、NOT回路、XOR回路、又はシフト回路等の演算回路、マルチプレクサ等の選択回路などが挙げられる。また、論理回路105は、一つのトランジスタなど一つの素子で構成されていてもよい。論理回路105は、スイッチとしての機能を有する素子(トランジスタ等)を、一つ又は複数個を有する回路とも言える。

【0033】

そして、論理回路部101は、記憶回路103に記憶されたデータに応じて、例えば加算器として用いる、又は、AND回路として用いるなど、適宜回路構成を変更することができる。

【0034】

更に、記憶回路103においてデータを保持することで、論理回路部101の回路構成を維持することができる。なお、論理回路部101の内部に記憶回路103を有していてもよい。以下に、半導体装置の具体的な回路構成及び駆動方法を説明する。

【0035】

(記憶回路103及び論理回路105の回路構成)

図1(B)に、記憶回路103及び論理回路105について、具体的な回路構成の一例を示す。

【0036】

記憶回路103は、トランジスタ107と、容量素子109と、を有する。なお、記憶回路103は複数設けられていてもよく、その個数は、論理回路部101の構成に応じて決定すればよい。複数設けられている場合、その集合を単に記憶回路と呼ぶ場合や、記憶回路部と呼ぶ場合もある。また、抵抗や、ダイオード等の素子を有していてもよい。

【0037】

トランジスタ107には、酸化物半導体が用いられている。特に、トランジスタ107のチャネル形成領域に酸化物半導体が用いられている。なお、図1(B)では、トランジスタ107に酸化物半導体が用いられていることを示すため、「OS」の符号を付している。

【0038】

トランジスタ107のゲートは端子Wと電気的に接続され、トランジスタ107のソース又はドレインの一方は端子Dと電気的に接続され、トランジスタ107のソース又はドレインの他方は端子F及び容量素子109の一対の電極のうちの一方と電気的に接続される。容量素子109の一対の電極のうちの他方は、端子Cと電気的に接続される。ここで、各端子は、配線や電極と電気的に接続される構成とすることができる。なお、端子Cには、一定の電位、例えば、低電源電位が入力される構成とすることができる。

【0039】

一方、論理回路105は、トランジスタ111を有する。ここでは、簡単のためトランジスタが一つの場合について説明するが、他の構成を用いてもよい。

【0040】

トランジスタ111のゲートは記憶回路103の端子Fと電気的に接続される。すなわち、当該ゲートはトランジスタ107のソース又はドレインの他方及び容量素子109の一対の電極のうちの一方と電気的に接続される。トランジスタ111のソース又はドレインの一方は、端子Iと電気的に接続され、トランジスタ111のソース又はドレインの他方は端子Oと電気的に接続される。

【0041】

トランジスタ111には、元素周期表における第14族の半導体(シリコンなど)を含有する半導体、有機半導体、化合物半導体、又は酸化物半導体等の様々な半導体を用いることができる。また、非晶質半導体、微結晶半導体、多結晶半導体、又は単結晶半導体等を用いることができる。特に、トランジスタ111のチャネル形成領域にこれらの半導体が用いられている。

【0042】

なお、単結晶半導体を用いたトランジスタとしては、単結晶半導体基板を用いたバルクトランジスタ、SOI基板を用いた薄膜トランジスタ等が挙げられる。SOI基板のベース基板としては、ガラス基板や半導体基板等が挙げられる。非晶質半導体、微結晶半導体、又は多結晶半導体を用いたトランジスタとしては、ガラス基板又は半導体基板などの上に設けられた薄膜トランジスタ等が挙げられる。

【0043】

(記憶回路103及び論理回路105の駆動方法)

図1(B)に示した記憶回路103及び論理回路105の駆動方法について説明する。

【0044】

記憶回路103へのデータの記憶(格納ともいう)は以下の方法で行われる。まず、トランジスタ107が、ゲートに入力される制御信号Write(端子Wに入力される制御信号)によってオン状態に選択される。そして、オン状態のトランジスタ107を介して、データDataに対応する信号電位(端子Dに入力される信号電位)が容量素子109の一対の電極のうちの一方に入力される。すなわち、記憶回路103は、トランジスタ107を介して容量素子109にデータDataを入力する機能を有する。

【0045】

その後、トランジスタ107が、ゲートに入力される制御信号Write(端子Wに入力される制御信号)によってオフ状態に選択されることで、容量素子109の一対の電極のうちの一方に当該信号電位が保持される。その際、端子Fにも当該信号電位が保持される。このようにして、記憶回路103にデータDataを記憶することができる。

【0046】

ここで、トランジスタ107には、酸化物半導体が用いられており、例えばシリコン系のトランジスタに比べてオフ電流(リーク電流ともいう)が著しく小さい。そのため、記憶回路103は、トランジスタ107がオフ状態である場合に、容量素子109の一対の電極のうちの一方及び端子Fに、上記信号電位を長期間にわたって保持することができる。そのため、記憶回路103は、例えば半導体装置への電源電圧の供給を停止した後も、データDataを長時間保持することができる。

【0047】

また、酸化物半導体を用いたトランジスタ107を有する記憶回路103は、例えばシリコン系のトランジスタを用いたフラッシュメモリ等に比べて駆動電圧が低い。そのため、当該フラッシュメモリ等に比べて高速動作及び消費電力の低減が可能である。

【0048】

一方、図1(B)の論理回路105では、上記信号電位がトランジスタ111のゲートに入力され、トランジスタ111のオン/オフが制御される。すなわち、端子Iと端子Oとの導通が制御される。そして、記憶回路103がデータDataを長時間保持できるため、半導体装置への電源電圧の供給を停止した後も論理回路105の回路構成を維持することができる。図1(B)において論理回路105の回路構成を維持するとは、トランジスタ111のオン状態又はオフ状態(端子Iと端子Oとの導通又は非導通)を維持することを意味する。

【0049】

ここで、トランジスタ111は、高速に動作することが望ましいため、移動度が高い結晶性半導体を用いるとよい。特に、単結晶半導体を用いることが好ましく、また、結晶性の向上が容易であるシリコンを含有する半導体を用いることが好ましい。すなわち、トランジスタ111は、単結晶シリコンを用いることが好ましい。

【0050】

また、トランジスタ107とトランジスタ111とを積層することで、回路面積を縮小することができる。例えば、図7(C)のようにトランジスタ111上にトランジスタ107を設ければよい。その場合、単結晶シリコンを用いたトランジスタ111上に、酸化物半導体を用いたトランジスタ107を設ける構造が好ましい。図7(D)に、積層させた場合の断面構造の具体的な一例を示す。

【0051】

図7(D)の断面構造は、図1(B)の回路構成に対応するものであり、単結晶シリコンを用いたトランジスタ111上に、酸化物半導体を用いたトランジスタ107と、容量素子109とが、設けられている構造を示している。

【0052】

トランジスタ111は、単結晶シリコン層131と、ゲート絶縁層133と、ゲート電極135と、を有している。トランジスタ107は、酸化物半導体層137と、ゲート絶縁層139と、ゲート電極141と、を有している。容量素子109は、一対の電極のうち一方の電極143及び他方の電極145と、誘電体層となる絶縁層147と、を有している。そして、トランジスタ111のゲート電極135は、容量素子109の一方の電極143、及び、トランジスタ107のソース電極又はドレイン電極の一方の電極149に電気的に接続されている。

【0053】

図7(D)の例において、容量素子109の一方の電極143は、トランジスタ107のソース電極又はドレイン電極の一方の電極149が延伸されたものである。また、容量素子109の誘電体層となる絶縁層147は、トランジスタ107のゲート絶縁層139が延伸されたものである。また、容量素子109の他方の電極145は、トランジスタ107のゲート電極141が設けられている層と同じ層上に設けられている。このような構造の一部又は全部を用いることで、各素子が有する膜や電極等を、同じ材料を用いて同じ工程で形成することができ、コスト及び工程数を削減することができる。

【0054】

図7(D)のような構造を有する半導体装置は、高速動作、データの保持、回路面積の縮小、並びにコスト及び工程数の削減の全てを実現することができる。なお、半導体装置の断面構造は、図7(C)、(D)に限定されず、トランジスタ107上にトランジスタ111を設けてもよい。また、図7(D)では、トランジスタ107の一部がトランジスタ111と重なっているが、トランジスタ107の全部がトランジスタ111と重なっていていてもよい。また、トランジスタ111とトランジスタ107とを積層しなくてもよく、トランジスタ107と容量素子109とを積層させる構造や、トランジスタ111と容量素子109とを積層させる構造などとしてもよい。

【0055】

以上のように、記憶回路103に記憶されたデータDataに応じて論理回路105を制御することができる。

【0056】

なお、図1(B)では、論理回路105としてトランジスタが一つの場合を示したが、他の回路構成としてもよい。例えば、図1(C)のように、論理回路105は、インバータなどのCMOS回路を有していてもよい。図1(C)の動作も図1(B)の動作と同様に、記憶回路103に記憶されたデータDataに応じて、トランジスタ121及びトランジスタ123のオン/オフを制御する。すなわち、端子I1と端子Oとの導通、又は、端子I2と端子Oとの導通を選択する。なお、端子I1には高電源電位が入力され、端子I2には低電源電位が入力される構成とすることができる。

【0057】

(記憶回路103及び論理回路部101の回路構成及び駆動方法)

図2(A)に、記憶回路103及び論理回路部101の回路構成の一例を示す。

【0058】

論理回路部101は、図1(A)の論理回路105に相当するものとして、加算器201と、AND回路203と、選択回路205と、を有する。すなわち、論理回路部101は、加算器201及びAND回路203等の演算回路と、選択回路205と、を有する。上述した他の論理回路を用いてもよい。また、抵抗や、ダイオード等の素子を有していてもよい。

【0059】

加算器201及びAND回路203としては、公知の回路を用いればよい。加算器201及びAND回路203は、端子A及び端子Bからの入力に基づき演算を行い、演算結果を選択回路205に入力する機能を有する。

【0060】

選択回路205の一例として、マルチプレクサ等が挙げられる。選択回路205は、記憶回路103の端子Fに電気的に接続され、選択信号Sとして記憶回路103のデータDataが入力される。そして、選択回路205は、当該データDataに応じて、加算器201又はAND回路203からの入力のうちの一方を選択して、端子Oに出力する。すなわち、選択回路205は、当該データDataに応じて加算器201やAND回路203等の演算回路の演算結果のうちの一つを選択する機能を有する。また、論理回路部101の構成によっては、演算回路を複数選択するようにすることもできる。

【0061】

図2(B)に、記憶回路103及び選択回路205の具体的な回路構成を示す。

【0062】

選択回路205は、2つの入力(AND回路からの入力及び加算器からの入力)を有するマルチプレクサの一例であり、トランジスタ207と、トランジスタ209と、インバータ211と、を有する。ここでは、トランジスタ207とトランジスタ209とは、極性が同じものを用いている。なお、選択回路205の回路構成は、トランジスタによって演算回路と端子Oとの電気的な接続を制御できればよく、図2(B)に限定されない。

【0063】

トランジスタ207のゲートはインバータ211を介して端子Fに電気的に接続され、トランジスタ207のソース又はドレインの一方はAND回路203に電気的に接続され、トランジスタ209のゲートは端子Fに電気的に接続され、トランジスタ209のソース又はドレインの一方は加算器201に電気的に接続され、トランジスタ207のソース又はドレインの他方及びトランジスタ209のソース又はドレインの他方は端子Oに電気的に接続される。なお、マルチプレクサの入力は、論理回路部101の構成に応じて、任意のm(mは正の整数)個に適宜変更すればよい。また、選択信号Sの数は、入力の数に応じて決定すればよい。また、記憶回路103の数は、選択信号Sの数に応じて決定すればよい。例えば、4つの入力(m=4:I0、I1、I2、I3)を有する場合、端子Oからの出力が4通りなので、2つの選択信号S0、S1(「S0S1」=「00」、「01」、「10」、「11」の4通り)を用い、2つの選択信号S0、S1のそれぞれに対応する2つの記憶回路103を設ければよい(図27(A)、(B)参照)。

【0064】

図2(B)の回路の駆動は、図1(B)、(C)の回路と同様に行えばよい。まず、記憶回路103は、トランジスタ107を介して選択信号SとなるデータDataを選択回路205に入力する。次に、選択回路205は、当該データDataに応じてトランジスタ209のオン/オフを制御し、当該データDataの反転データに応じてトランジスタ207のオン/オフを制御する。そして、トランジスタ207がオン状態でトランジスタ209がオフ状態の場合、AND回路203からの入力が選択され、端子Oに出力される。また、トランジスタ209がオン状態でトランジスタ207がオフ状態の場合、加算器201からの入力が選択され、端子Oに出力される。

【0065】

このように、記憶回路103のデータDataに応じて、選択回路205が制御され、加算器201又はAND回路203の演算結果のうちの一方が選択される。なお、図2では、簡単のため、論理回路部101の論理回路105として、加算器201、AND回路203、及び選択回路205のみ示したが、他の構成としてもよい。図3に、より実用的な構成を示す。

【0066】

図3は、論理回路部101として一般的なALUを用いた場合のブロック図である。論理回路部101は、加算器や減算器等を組み合わせた算術演算部301と、AND回路やOR回路等を組み合わせた論理演算部303と、シフト回路を有するシフト演算部305と、それらを選択して出力するマルチプレクサ等の選択回路205と、を有する。また、各演算部301、303、305は、マルチプレクサ等の選択回路307、309、311を有しており、各演算部内の論理回路の回路構成の組み合わせを変更することができる。

【0067】

各演算部内の選択回路307、309、311は、選択回路205と同様に、選択信号Sとなる記憶回路103のデータDataに応じて制御される。図3の場合、記憶回路103は、図1(B)のようなトランジスタ107と容量素子109との組を複数組設けた記憶回路部とし、端子F1〜F4からデータDataが出力されるようにすればよい。なお、当該組の数は、選択回路205、307、309、311の入力の数によって決定すればよい。また、端子F1〜端子F4から同じデータDataが出力される場合、図1(B)のような記憶回路103を選択回路205、307、309、311で共有してもよく、半導体装置の小型化が可能である。

【0068】

そして、記憶回路103がデータDataを長時間保持することができるため、半導体装置への電源電圧の供給を停止した後も、論理回路部101の回路構成を維持することができる。また、図3のように回路構成が複雑になるのに伴い、記憶回路103の高速動作や消費電力を低減する効果が一層顕著になる。

【0069】

なお、図2や図3のような回路を複数設けることで、端子A及び端子Bから入力される信号のビット数を増やすことができる。すなわち、任意のn(nは正の整数)ビットの論理回路部101を構成することができる。

【0070】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0071】

(実施の形態2)

本実施の形態では、実施の形態1と異なる半導体装置の一例を説明する。

【0072】

図4(A)、(B)に、図1(B)の変形例を示す。

【0073】

まず、図4(A)の例について説明する。記憶回路103は、図1(B)等と同様である。

【0074】

図4(A)の論理回路105は、トランジスタ111と、トランジスタ401と、インバータ403と、を有する。トランジスタ111とトランジスタ401とは、端子Iと端子Oとの間に並列に電気的に接続される。すなわち、トランジスタ111のソース又はドレインの一方及びトランジスタ401のソース又はドレインの一方が端子Iに電気的に接続され、トランジスタ111のソース又はドレインの他方及びトランジスタ401のソース又はドレインの他方が端子Oに電気的に接続される。

【0075】

トランジスタ111と、トランジスタ401とは、一方がNチャネル型で他方がPチャネル型であり、極性が異なるものを用いる。そして、トランジスタ111のゲートには記憶回路103のデータDataが入力され、トランジスタ401のゲートには当該データDataの反転データが入力される。図4(A)のように極性の異なるトランジスタ111、401を用いることで、トランジスタ111、401の閾値電圧分の電圧変動を抑制することができる。

【0076】

次に、図4(B)の例について説明する。

【0077】

図4(B)の記憶回路103は、トランジスタ107と、容量素子109と、トランジスタ405と、容量素子407と、インバータ409と、を有する。トランジスタ107及び容量素子109については、図1(B)等と同様である。そして、トランジスタ405のゲートが端子Wに電気的に接続され、トランジスタ405のソース又はドレインの一方がインバータ409を介して端子Dに電気的に接続され、トランジスタ405のソース又はドレインの他方が容量素子407の一対の電極のうちの一方及び端子F2に電気的に接続される。

【0078】

図4(B)の論理回路105は、図4(A)と同様に、極性の異なるトランジスタ111とトランジスタ401とが端子Iと端子Oとの間に並列に電気的に接続されている。そして、トランジスタ111のゲートには記憶回路103のデータDataが入力され、トランジスタ401のゲートには当該データDataの反転データが入力される。図4(A)と同様に極性の異なるトランジスタ111、401を用いることで、トランジスタ111、401の閾値電圧分の電圧変動を抑制することができる。

【0079】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0080】

(実施の形態3)

本実施の形態では、上記実施の形態とは異なる半導体装置の一例を説明する。

【0081】

図5(A)の半導体装置は、複数の論理回路部101と、接続部501と、を有する。論理回路部101については、図1〜図3と同様であり、ALU等を用いることができる。

【0082】

接続部501は、複数の論理回路部101間を電気的に接続する配線503の導通を制御する機能を有する。図5(B)にその詳細を示す。

【0083】

図5(B)の接続部501の回路構成及び駆動方法は、図1(B)と同様であり、記憶回路103のデータDataに応じて、トランジスタ111のオン/オフが制御される。すなわち、端子Iと端子Oとの導通が制御される。端子Iと端子Oとは、それぞれ異なる論理回路部101と電気的に接続されており、端子Iと端子Oとの導通の制御により、論理回路部101間の電気的な接続が制御される。なお、論理回路105は、トランジスタ111を一つ有する回路に限定されず、スイッチとしての機能を有する素子(トランジスタ等)を一つ又は複数個を有する回路でもよい。

【0084】

このように、接続部501のトランジスタ111は、当該データDataに応じて、複数の論理回路部101のうちの一つと他の一つとの電気的な接続を制御する機能を有する。また、端子Iと端子Oとは、それぞれ一つの論理回路部101の端子Aと端子O(図3等参照)とに電気的に接続されるようにしてもよい。すなわち、一つの論理回路部101の出力が入力に帰還する構成としてもよい。なお、接続部501の外部に記憶回路103を有していてもよい。

【0085】

図5(C)は、複数の論理回路部101間の電気的な接続の一例を示す図である。図5(C)の半導体装置は、メモリ505と、選択回路507と、を有する。メモリ505には、制御信号Write及びデータData等の情報a〜情報nが格納されている。選択回路507は、マルチプレクサ等であり、当該情報を選択して接続部501の記憶回路103に出力する。

【0086】

図5(C)では、情報aが選択され、論理回路部101間の配線503が矢印のように接続される様子を示している。また、情報b〜情報nが選択された場合に、接続関係が変更されるようにすればよい。なお、図5(C)では、接続された配線503のみ示している。

【0087】

そして、図5(C)の半導体装置は、接続部501が有する記憶回路103においてデータDataを長時間保持することができるため、半導体装置への電源電圧の供給を停止した後も、複数の論理回路部101間の接続関係を維持することができる。また、接続部501が有する酸化物半導体を用いたトランジスタ107は駆動電圧が低い。そのため、接続関係を変更する際に、例えばフラッシュメモリ等に比べて高速動作及び消費電力の低減が可能である。

【0088】

なお、メモリ505に記憶回路103を用いてもよい。その場合、メモリ505も高速かつ低消費電力で動作させることができる。また、接続部501の回路構成として、図4(A)、(B)を用いてもよい。

【0089】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0090】

(実施の形態4)

本実施の形態は、実施の形態1及び実施の形態3を組み合わせた半導体装置の一例を説明する。

【0091】

図6(A)の半導体装置は、複数の論理回路部101(「+」や「AND」などを付した部分)と、接続部501と、記憶回路103と、メモリ505と、選択回路507と、を有する。半導体装置の外部にメモリ505及び選択回路507を有していてもよい。

【0092】

記憶回路103は、実施の形態1等で説明したように、複数の論理回路部101の回路構成を維持する機能を有する。

【0093】

接続部501は、実施の形態3等で説明したように、複数の論理回路部101間の接続関係を維持する機能を有する。

【0094】

そして、メモリ505に格納されている情報a〜情報nのそれぞれは、当該回路構成及び接続関係の両方の情報を有している。その情報を記憶回路103及び接続部501に保持させることで、半導体装置は、電源電圧の供給を停止した後も、当該回路構成及び接続関係の両方を維持することができる。また、記憶回路103が有する酸化物半導体を用いたトランジスタは駆動電圧が低い。そのため、当該回路構成や接続関係の変更を高速かつ低消費電力で行うことができる。

【0095】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0096】

(実施の形態5)

本実施の形態では、半導体装置の消費電力を低減する構成の一例を示す。

【0097】

図6(B)に、半導体装置において使用しない回路への電源電圧の供給を停止する構成を示す。なお、論理回路部101(論理回路部101a及び論理回路部101b)、接続部501、記憶回路103等の構成は他の実施の形態と同様である。

【0098】

使用する論理回路部101a、記憶回路103のうち論理回路部101aにデータDataを供給する部分、及び、接続部501のうち論理回路部101aの接続関係を制御する記憶回路には、電源電圧が供給される。

【0099】

一方、使用しない論理回路部101b、記憶回路103のうち論理回路部101bにデータDataを供給する部分、及び、接続部501のうち論理回路部101bの接続関係を制御する記憶回路には、電源電圧の供給を停止する。また、それらのいずれかへの電源電圧の供給を停止するようにしてもよい。すなわち、使用しない論理回路部101bのみ電源電圧の供給を停止するようにしてもよい。

【0100】

電源電圧の供給を停止する一例として、図1(C)の論理回路105として示したインバータでは、端子I1及び端子I2と電源線との電気的な接続をスイッチ等で遮断することにより、高電源電位の供給及び低電源電位の供給を停止することができる。図2(A)の加算器201、AND回路203、及び選択回路205等も同様に、スイッチ等を用いて高電源電位の供給や低電源電位の供給を停止することができる。

【0101】

このように、使用しない回路への電源電圧の供給を停止することで、半導体装置の消費電力を低減することができる。

【0102】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0103】

(実施の形態6)

本実施の形態では、上記実施の形態に示す記憶回路のトランジスタに適用可能な酸化物半導体層を含む電界効果トランジスタの例について説明する。

【0104】

本実施の形態におけるトランジスタの一例について、図7(A)、(B)を用いて説明する。

【0105】

図7(A)に示すトランジスタは、導電層601_aと、絶縁層602_aと、半導体層603_aと、導電層605a_aと、導電層605b_aと、を含む。

【0106】

半導体層603_aは、領域604a_a及び領域604b_aを含む。領域604a_a及び領域604b_aは、互いに離間し、それぞれドーパントが添加された領域である。なお、領域604a_a及び領域604b_aの間の領域がチャネル形成領域になる。半導体層603_aは、被素子形成層600_aの上に設けられる。なお、必ずしも領域604a_a及び領域604b_aを設けなくてもよい。

【0107】

導電層605a_a及び導電層605b_aは、半導体層603_aの上に設けられ、半導体層603_aに電気的に接続される。また、導電層605a_a及び導電層605b_aの側面は、テーパ状である。

【0108】

また、導電層605a_aは、領域604a_aの一部に重畳するが、必ずしもこれに限定されない。導電層605a_aを領域604a_aの一部に重畳させることにより、導電層605a_a及び領域604a_aの間の抵抗値を小さくすることができる。また、導電層605a_aに重畳する半導体層603_aの領域の全てが領域604a_aである構造にしてもよい。

【0109】

また、導電層605b_aは、領域604b_aの一部に重畳するが、必ずしもこれに限定されない。導電層605b_aを領域604b_aの一部に重畳させることにより、導電層605b_a及び領域604b_aの間の抵抗を小さくすることができる。また、導電層605b_aに重畳する半導体層603_aの領域の全てが領域604b_aである構造にしてもよい。

【0110】

絶縁層602_aは、半導体層603_a、導電層605a_a、及び導電層605b_aの上に設けられる。

【0111】

導電層601_aは、絶縁層602_aの一部の上に設けられ、絶縁層602_aを介して半導体層603_aに重畳する。絶縁層602_aを介して導電層601_aと重畳する半導体層603_aの領域がチャネル形成領域になる。

【0112】

また、図7(B)に示すトランジスタは、導電層601_bと、絶縁層602_bと、半導体層603_bと、導電層605a_bと、導電層605b_bと、絶縁層606aと、絶縁層606bと、絶縁層607と、を含む。

【0113】

半導体層603_bは、領域604a_b及び領域604b_bを含む。領域604a_b及び領域604b_bは、互いに離間し、それぞれドーパントが添加された領域である。半導体層603_bは、例えば導電層605a_b、導電層605b_b、及び被素子形成層600_bの上に設けられ、導電層605a_b及び導電層605b_bに電気的に接続される。なお、必ずしも領域604a_b及び領域604b_bを設けなくてもよい。

【0114】

絶縁層602_bは、半導体層603_bの一部の上に設けられる。

【0115】

導電層601_bは、絶縁層602_bの一部の上に設けられ、絶縁層602_bを介して半導体層603_bに重畳する。なお、絶縁層602_bを介して導電層601_bと重畳する半導体層603_bの領域がトランジスタのチャネル形成領域になる。なお、導電層601_bの上に絶縁層が設けられていてもよい。

【0116】

絶縁層606aは、絶縁層602_bの上に設けられ、導電層601_bにおける一対の側面の一方に接する。

【0117】

絶縁層606bは、絶縁層602_bの上に設けられ、導電層601_bにおける一対の側面の他方に接する。

【0118】

なお、絶縁層602_bを介して絶縁層606a及び絶縁層606bに重畳する領域604a_b及び領域604b_bの部分のドーパントの濃度は、絶縁層606a及び絶縁層606bに重畳しない領域604a_b及び領域604b_bの部分のドーパントの濃度より低くてもよい。

【0119】

導電層605a_b及び導電層605b_bは、半導体層603_bの上に設けられる。

【0120】

導電層605a_bは、領域604a_bに電気的に接続される。また、導電層605a_bは、絶縁層606aに接する。

【0121】

導電層605b_bは、領域604b_bに電気的に接続される。また、導電層605b_bは、絶縁層606bに接する。

【0122】

絶縁層607は、導電層601_b、導電層605a_b、導電層605b_b、絶縁層606a、及び絶縁層606bの上に設けられる。

【0123】

さらに、図7(A)及び図7(B)に示す各構成要素について説明する。

【0124】

被素子形成層600_a及び被素子形成層600_bとしては、例えば絶縁層、又は絶縁表面を有する基板などを用いることができる。また、予め素子が形成された層を被素子形成層600_a及び被素子形成層600_bとして用いることもできる。

【0125】

導電層601_a及び導電層601_bのそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタのゲートとしての機能を有する層をゲート電極又はゲート配線ともいう。

【0126】

導電層601_a及び導電層601_bとしては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層601_a及び導電層601_bに適用可能な材料の積層により、導電層601_a及び導電層601_bを構成することもできる。

【0127】

絶縁層602_a及び絶縁層602_bのそれぞれは、トランジスタのゲート絶縁層としての機能を有する。

【0128】

絶縁層602_a及び絶縁層602_bとしては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ハフニウム層、又は酸化ランタン層を用いることができる。また、絶縁層602_a及び絶縁層602_bに適用可能な材料の積層により絶縁層602_a及び絶縁層602_bを構成することもできる。

【0129】

また、絶縁層602_a及び絶縁層602_bとしては、例えば元素周期表における第13族元素及び酸素元素を含む材料の絶縁層を用いることもできる。例えば、半導体層603_a及び半導体層603_bが第13族元素を含む場合に、半導体層603_a及び半導体層603_bに接する絶縁層として第13族元素を含む絶縁層を用いることにより、該絶縁層と酸化物半導体層との界面の状態を良好にすることができる。

【0130】

第13族元素及び酸素元素を含む材料としては、例えば酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどが挙げられる。なお、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多い物質のことをいい、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上の物質のことをいう。例えば、Al2Ox(x=3+α、αは0より大きく1より小さい値)、Ga2Ox(x=3+α、αは0より大きく1より小さい値)、又はGaxAl2−xO3+α(xは0より大きく2より小さい値、αは0より大きく1より小さい値)で表記される材料を用いることもできる。

【0131】

また、絶縁層602_a及び絶縁層602_bに適用可能な材料の層の積層により絶縁層602_a及び絶縁層602_bを構成することもできる。例えば、複数のGa2Oxで表記される酸化ガリウムを含む層の積層により絶縁層602_a及び絶縁層602_bを構成してもよい。また、Ga2Oxで表記される酸化ガリウムを含む絶縁層及びAl2Oxで表記される酸化アルミニウムを含む絶縁層の積層により絶縁層602_a及び絶縁層602_bを構成してもよい。

【0132】

半導体層603_a及び半導体層603_bのそれぞれは、トランジスタのチャネルが形成される層としての機能を有する。半導体層603_a及び半導体層603_bに適用可能な酸化物半導体としては、例えばIn系酸化物(例えば酸化インジウムなど)、Sn系酸化物(例えば酸化スズなど)、又はZn系酸化物(例えば酸化亜鉛など)などを用いることができる。

【0133】

また、上記金属酸化物としては、例えば、四元系金属酸化物、三元系金属酸化物、二元系金属酸化物などの金属酸化物を用いることもできる。なお、上記酸化物半導体として適用可能な金属酸化物は、特性のばらつきを減らすためのスタビライザーとしてガリウム、スズ、ハフニウム、及びアルミニウムの一つまたは複数を含んでいてもよい。また、上記酸化物半導体として適用可能な金属酸化物は、上記スタビライザーとして、ランタノイドである、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムの一つ又は複数を含んでいてもよい。また、上記酸化物半導体として適用可能な金属酸化物は、酸化シリコンを含んでいてもよい。

【0134】

例えば、四元系金属酸化物としては、例えばIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物などを用いることができる。

【0135】

また、三元系金属酸化物としては、例えばIn−Ga−Zn系酸化物(IGZOともいう)、In−Sn−Zn系酸化物、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、又はIn−Lu−Zn系酸化物などを用いることができる。

【0136】

また、二元系金属酸化物としては、例えばIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Sn系酸化物、又はIn−Ga系酸化物などを用いることができる。

【0137】

なお、例えばIn−Ga−Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0138】

また、酸化物半導体としては、InLO3(ZnO)m(mは0より大きい数)で表記される材料を用いることもできる。InLO3(ZnO)mのLは、Ga、Al、Mn、及びCoから選ばれた一つ又は複数の金属元素を示す。

【0139】

例えば、酸化物半導体としては、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)又はIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。また、酸化物半導体としては、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)又はIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いることができる。

【0140】

しかし、これらに限られず、必要とする半導体特性(移動度、閾値電圧、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0141】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0142】

また、半導体層603_a及び半導体層603_bとしては、c軸に配向し、かつab面、表面又は界面の方向から見て三角形状又は六角形状の原子配列を有し、c軸において金属原子が層状又は金属原子と酸素原子とが層状に配列しており、ab面においてa軸又はb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物半導体(CAAC−OS:C Axis Aligned Crystalline Oxide Semiconductorともいう)の層を用いることができる。

【0143】

CAACとは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含むものをいう。

【0144】

CAACは、単結晶ではないが、非晶質のみから形成されている材料でもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0145】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は、一定の方向(例えば、CAACが形成される基板面、CAACの表面などに垂直な方向)に揃っていてもよい。又は、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACが形成される基板面、CAACの表面などに垂直な方向)を向いていてもよい。

【0146】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0147】

このようなCAACの例としては、例えば膜状に形成され、膜表面又は基板面に垂直な方向から観察すると三角形又は六角形の原子配列が認められ、かつその膜断面を観察すると金属原子又は金属原子及び酸素原子(又は窒素原子)の層状配列が認められる結晶を挙げることもできる。

【0148】

また、酸化物半導体としては、c軸方向に配向する結晶領域の組成がIn1+σGa1−σO3(ZnO)M(ただし、0<σ<1、M=1以上3以下の数)で表され、c軸方向に配向する結晶領域を含む全体の半導体層の組成がInPGaQOR(ZnO)M(ただし、0<P<2、0<Q<2、M=1以上3以下の数)で表される材料を用いることもできる。

【0149】

また、例えば、半導体層603_a及び半導体層603_bがCAACの酸化物半導体層の場合において、トランジスタのチャネル長を30nmとするとき、半導体層603_a及び半導体層603_bの厚さを例えば5nm程度にしてもトランジスタにおける短チャネル効果を抑制することができる。

【0150】

ここで、CAACに含まれる結晶構造の一例について図8乃至図10を用いてさらに説明する。なお、特に断りがない限り、図8乃至図10は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図8において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0151】

図8(A)では、1個の6配位のインジウム原子(6配位のInともいう)と6配位のInに近接する6個の4配位の酸素原子(4配位のOともいう)と、を有する構造を示す。なお、Inなどの1個の金属原子と該金属原子に近接する酸素原子により構成される部分を小グループという。また、図8(A)では、便宜のため、八面体構造を平面構造で示している。また、図8(A)の上半分及び下半分には、それぞれ3個ずつ4配位のOがある。また、図8(A)に示す小グループの電荷は0である。

【0152】

図8(B)では、1個の5配位のGaと、5配位のGaに近接する3個の3配位の酸素原子(3配位のOともいう)と、5配位のGaに近接する2個の4配位のOと、を有する構造を示す。3個の3配位のOのそれぞれは、いずれもab面に存在する。また、図8(B)の上半分及び下半分のそれぞれには、1個ずつ4配位のOがある。また、インジウム原子には、6配位だけではなく、5配位のインジウム原子(5配位のIn)も存在するため、5配位のInと、3個の3配位のOと、2個の4配位のOにより、図8(B)に示す構造を構成することもできる。また、図8(B)に示す小グループの電荷は0である。

【0153】

図8(C)では、1個の4配位の亜鉛原子(4配位のZnともいう)と、4配位のZnに近接する4個の4配位のOと、を有する構造を示す。図8(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。なお、図8(C)に示す小グループの電荷は0である。

【0154】

図8(D)では、1個の6配位のスズ原子(6配位のSnともいう)と、6配位のSnに近接する6個の4配位のOと、を有する構造を示す。図8(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。なお、図8(D)に示す小グループの電荷は+1となる。

【0155】

図8(E)では、2個の亜鉛原子を含む小グループを示す。図8(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図8(E)に示す小グループの電荷は−1となる。

【0156】

なお、複数の小グループの集合体を中グループといい、複数の中グループの集合体を大グループ(ユニットセルともいう)という。

【0157】

ここで、上記小グループ同士が結合する規則について説明する。例えば、6配位のInの上半分における3個の4配位のOは、下方向に近接する3個の6配位のInに結合し、下半分における3個の4配位のOは、上方向に近接する3個の6配位のInに結合する。また、5配位のGaの上半分における1個の3配位のOは、下方向に近接する1個の5配位のGaに結合し、下半分における1個の3配位のOは、上方向に近接する1個の5配位のGaに結合する。また、4配位のZnの上半分における1個の4配位のOは、下方向に近接する1個の4配位のZnに結合し、下半分における3個の4配位のOは、上方向に近接する3個の4配位のZnに結合する。このように、金属原子の上方向における4配位のOの数と、そのOの下方向に近接する金属原子の数は等しく、同様に金属原子の下方向における4配位のOの数と、そのOの上方向に近接する金属原子の数は等しい。このとき、Oは4配位なので、下方向に近接する金属原子の数と、上方向に近接する金属原子の数の和は4になる。従って、金属原子の上方向における4配位のOの数と、別の金属原子の下方向における4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は、結合することができる。例えば、6配位の金属原子(In又はSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子又は4配位の金属原子と結合することになる。

【0158】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、この他にも、層構造の合計の電荷が0となるように、複数の小グループが結合して中グループを構成する。

【0159】

さらに、図9(A)では、In−Sn−Zn系の層構造を構成する中グループのモデル図を示す。また、図9(B)では、3つの中グループで構成される大グループを示す。また、図9(C)では、図9(B)に示す層構造をc軸方向から観察した場合の原子配列を示す。

【0160】

なお、図9(A)では、便宜のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分及び下半分のそれぞれに3個ずつ4配位のOがあることを、丸枠の3として示している。同様に、図9(A)において、Inの上半分及び下半分のそれぞれには、1個ずつ4配位のOがあることを、丸枠の1として示している。また、同様に、図9(A)では、下半分に1個の4配位のOがあり、上半分に3個の4配位のOがあるZnと、上半分に1個の4配位のOがあり、下半分に3個の4配位のOがあるZnと、を示している。

【0161】

図9(A)において、In−Sn−Zn系の層構造を構成する中グループでは、上から順に以下の構造を有している。4配位のOが3個ずつ上半分及び下半分にあるSnが、4配位のOが1個ずつ上半分及び下半分にあるInに結合している。該Inが、上半分に3個の4配位のOがあるZnに結合している。該Znは、該Znの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分及び下半分にあるInと結合している。該Inは、上半分に1個の4配位のOがあるZn2個からなる小グループと結合している。該小グループは、該小グループの下半分における1個の4配位のOを介して4配位のOが3個ずつ上半分及び下半分にあるSnと結合している。複数の上記中グループが結合することにより、大グループが構成される。

【0162】

ここで、3配位のO及び4配位のOの場合、結合1本当たりの電荷は、それぞれ−0.667、−0.5と考えることができる。例えば、In(6配位又は5配位)、Zn(4配位)、Sn(5配位又は6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループの電荷は+1となる。そのため、Snを含む層構造を形成するためには、+1である電荷を打ち消す−1の電荷が必要となる。電荷が−1となる構造として、図8(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0163】

さらに、図9(B)に示す大グループが繰り返された構造にすることにより、In−Sn−Zn系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn系の層構造は、In2SnZn2O7(ZnO)m(mは0又は自然数)とする組成式で表すことができる。

【0164】

また、本実施の形態に示す他の四元系金属酸化物、三元系金属酸化物、二元系金属酸化物、その他の金属酸化物などを用いた場合も同様である。

【0165】

例えば、In−Ga−Zn系の層構造を構成する中グループのモデル図を図10(A)に示す。

【0166】

図10(A)において、In−Ga−Zn系の層構造を構成する中グループは、上から順に以下の構造を有している。4配位のOが3個ずつ上半分及び下半分にあるInが、4配位のOが1個上半分にあるZnに結合している。該Znは、該Znの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分及び下半分にあるGaに結合している。該Gaは、該Gaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分及び下半分にあるInに結合している。複数の上記中グループが結合することにより、大グループが構成される。

【0167】

図10(B)では、3つの中グループで構成される大グループを示す。また、図10(B)に示す層構造をc軸方向から観察した場合の原子配列を図10(C)に示す。

【0168】

ここで、In(6配位又は5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、Zn及びGaのいずれかを含む小グループの電荷は0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0169】

なお、In−Ga−Zn系の層構造を構成する中グループは、図10(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせて大グループを構成することもできる。

【0170】

具体的には、図10(B)に示した大グループが繰り返されることで、In−Ga−Zn系の結晶を得ることができる。なお、得られるIn−Ga−Zn系の層構造は、InGaO3(ZnO)n(nは自然数)とする組成式で表すことができる。

【0171】

n=1(InGaZnO4)の場合は、例えば、図26(A)に示す結晶構造を取りうる。なお、図26(A)に示す結晶構造において、図8(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0172】

また、n=2(InGaZn2O5)の場合は、例えば、図26(B)に示す結晶構造を取りうる。なお、図26(B)に示す結晶構造において、図8(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0173】

以上がCAACの構造の一例の説明である。CAACのように結晶性を有する酸化物半導体は、バルク内の欠陥が低い。

【0174】

さらに、図7(A)及び図7(B)に示す領域604a_a、領域604b_a、領域604a_b、及び領域604b_bは、ドーパントが添加され、トランジスタのソース又はドレインとしての機能を有する。ドーパントとしては、例えば元素周期表における13族の元素(例えば硼素など)、元素周期表における15族の元素(例えば窒素、リン、及び砒素の一つ又は複数)、及び希ガス元素(例えばヘリウム、アルゴン、及びキセノンの一つ又は複数)の一つ又は複数を用いることができる。なお、トランジスタのソースとしての機能を有する領域をソース領域ともいい、トランジスタのドレインとしての機能を有する領域をドレイン領域ともいう。領域604a_a、領域604b_a、領域604a_b、及び領域604b_bにドーパントを添加することにより導電層との間の抵抗を小さくすることができるため、トランジスタを微細化することができる。

【0175】

導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bのそれぞれは、トランジスタのソース又はドレインとしての機能を有する。なお、トランジスタのソースとしての機能を有する層をソース電極又はソース配線ともいい、トランジスタのドレインとしての機能を有する層をドレイン電極又はドレイン配線ともいう。

【0176】

導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bとしては、例えばアルミニウム、マグネシウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタングステンなどの金属材料、又はこれらの金属材料を主成分とする合金材料の層を用いることができる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層により、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bを構成することができる。また、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bに適用可能な材料の積層により、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bを構成することもできる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層と銅を含む層の積層により、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bを構成することができる。

【0177】

また、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bとしては、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例えば酸化インジウム、酸化スズ、酸化亜鉛、酸化インジウム酸化スズ、又は酸化インジウム酸化亜鉛を用いることができる。なお、導電層605a_a、導電層605b_a、導電層605a_b、及び導電層605b_bに適用可能な導電性の金属酸化物は、酸化シリコンを含んでいてもよい。

【0178】

絶縁層606a及び絶縁層606bとしては、例えば絶縁層602_a及び絶縁層602_bに適用可能な材料の層を用いることができる。また、絶縁層606a及び絶縁層606bに適用可能な材料の積層により、絶縁層606a及び絶縁層606bを構成してもよい。

【0179】

絶縁層607は、トランジスタへの不純物の侵入を抑制する保護絶縁層としての機能を有する。

【0180】

絶縁層607としては、例えば絶縁層602_a及び絶縁層602_bに適用可能な材料の層を用いることができる。また、絶縁層607に適用可能な材料の積層により、絶縁層607を構成してもよい。例えば、酸化シリコン層、酸化アルミニウム層などにより、絶縁層607を構成してもよい。例えば、酸化アルミニウム層を用いることにより、半導体層603_bへの不純物の侵入抑制効果をより高めることができ、また、半導体層603_b中の酸素の脱離抑制効果を高めることができる。

【0181】

なお、本実施の形態のトランジスタを、チャネル形成層としての機能を有する酸化物半導体層の一部の上に絶縁層を含み、該絶縁層を介して酸化物半導体層に重畳するように、ソース又はドレインとしての機能を有する導電層を含む構造としてもよい。上記構造である場合、絶縁層は、トランジスタのチャネル形成層を保護する層(チャネル保護層ともいう)としての機能を有する。チャネル保護層としての機能を有する絶縁層としては、例えば絶縁層602_a及び絶縁層602_bに適用可能な材料の層を用いることができる。また、絶縁層602_a及び絶縁層602_bに適用可能な材料の積層によりチャネル保護層としての機能を有する絶縁層を構成してもよい。

【0182】

また、被素子形成層600_a及び被素子形成層600_bの上に下地層を形成し、該下地層の上にトランジスタを形成してもよい。このとき、下地層としては、例えば絶縁層602_a及び絶縁層602_bに適用可能な材料の層を用いることができる。また、絶縁層602_a及び絶縁層602_bに適用可能な材料の積層により下地層を構成してもよい。例えば、酸化アルミニウム層及び酸化シリコン層の積層により下地層を構成することにより、下地層に含まれる酸素が半導体層603_a及び半導体層603_bを介して脱離するのを抑制することができる。

【0183】

さらに、本実施の形態におけるトランジスタの作製方法の一例として、図7(A)に示すトランジスタの作製方法の一例について、図11を用いて説明する。図11は、図7(A)に示すトランジスタの作製方法を説明するための断面模式図である。

【0184】

まず、図11(A)に示すように、被素子形成層600_aを準備し、被素子形成層600_aの上に半導体層603_aを形成する。

【0185】

例えば、スパッタリング法を用いて半導体層603_aに適用可能な酸化物半導体材料の膜(酸化物半導体膜ともいう)を成膜することにより、半導体層603_aを形成することができる。なお、上記酸化物半導体膜を成膜した後に、該酸化物半導体膜の一部をエッチングしてもよい。また、希ガス雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で酸化物半導体膜を成膜してもよい。

【0186】

また、スパッタリングターゲットとして、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の組成比である酸化物ターゲットを用いて酸化物半導体膜を成膜することができる。また、例えば、In2O3:Ga2O3:ZnO=1:1:2[mol数比]、4:2:3[mol数比]、3:1:2[mol数比]、2:1:3[mol数比]、3:1:4[mol数比]の組成比である酸化物ターゲットを用いて酸化物半導体膜を成膜してもよい。

【0187】

また、スパッタリングターゲットとして、In:Sn:Zn=1:2:2[原子数比]、2:1:3[原子数比]、1:1:1[原子数比]、又は20:45:35[原子数比]の組成比である酸化物ターゲットを用いて酸化物半導体膜を成膜してもよい。このような組成比である酸化物ターゲットを用いることにより、結晶性の高い酸化物半導体膜を成膜することができる。特に、In:Sn:Zn=2:1:3の組成比である酸化物ターゲットを用いることにより、より結晶性の高い酸化物半導体膜を成膜することができる。

【0188】

また、スパッタリングターゲットとして、In:Zn=50:1乃至In:Zn=1:2(モル数比に換算するとIn2O3:ZnO=25:1乃至In2O3:ZnO=1:4)、好ましくはIn:Zn=20:1乃至In:Zn=1:1(モル数比に換算するとIn2O3:ZnO=10:1乃至In2O3:ZnO=1:2)、さらに好ましくはIn:Zn=15:1乃至In:Zn=1.5:1(モル数比に換算するとIn2O3:ZnO=15:2乃至In2O3:ZnO=3:4)の組成比である酸化物ターゲットを用いてIn−Zn系酸化物の膜を成膜してもよい。例えば、In−Zn系酸化物半導体膜の成膜に用いるターゲットは、原子数比がIn:Zn:O=S:U:Rのとき、R>1.5S+Uとする。Inの量を多くすることにより、トランジスタの電界効果移動度(単に移動度ともいう)を向上させることができる。

【0189】

また、スパッタリング法を用いる場合、例えば、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で半導体層603_aを形成する。このとき、希ガスと酸素の混合雰囲気下で半導体層603_aを形成する場合には、希ガスの量に対して酸素の量が多い方が好ましい。

【0190】

また、スパッタリング法を用いた成膜を行う場合、堆積される膜中に水素、水、水酸基、又は水素化物(水素化合物ともいう)などの不純物が含まれないように、成膜室外部からのリークや成膜室内の内壁からの脱ガスを十分抑えることが好ましい。

【0191】

例えば、スパッタリング法を用いて膜を成膜する前に、スパッタリング装置の予備加熱室において予備加熱処理を行ってもよい。上記予備加熱処理を行うことにより、上記不純物を脱離することができる。

【0192】

また、スパッタリング法を用いて成膜する前に、例えばアルゴン、窒素、ヘリウム、又は酸素雰囲気下で、ターゲット側に電圧を印加せずに、基板側にRF電源を用いて電圧を印加し、プラズマを形成して被形成面を改質する処理(逆スパッタともいう)を行ってもよい。逆スパッタを行うことにより、被形成面に付着している粉状物質(パーティクル、ごみともいう)を除去することができる。

【0193】

また、スパッタリング法を用いて成膜する場合、吸着型の真空ポンプなどを用いて、膜を成膜する成膜室内の残留水分を除去することができる。吸着型の真空ポンプとしては、例えばクライオポンプ、イオンポンプ、又はチタンサブリメーションポンプなどを用いることができる。また、コールドトラップを設けたターボ分子ポンプを用いて成膜室内の残留水分を除去することもできる。上記真空ポンプを用いることにより、上記不純物を含む排気の逆流を低減することができる。

【0194】

また、スパッタリングガスとして、例えば上記不純物が除去された高純度ガスを用いることにより、形成される膜の上記不純物の濃度を低減することができる。例えば、スパッタリングガスとして、露点−70℃以下であるガスを用いることが好ましい。

【0195】

また、本実施の形態におけるトランジスタの作製方法の一例において、膜の一部をエッチングして層を形成する場合、例えば、フォトリソグラフィ工程により膜の一部の上にレジストマスクを形成し、レジストマスクを用いて膜をエッチングすることにより、層を形成することができる。なお、この場合、層の形成後にレジストマスクを除去する。

【0196】

また、半導体層603_aとしてCAACである酸化物半導体層を形成する場合、スパッタリング法を用い、酸化物半導体膜が形成される被素子形成層の温度を100℃以上500℃以下、好ましくは200℃以上350℃以下にして酸化物半導体膜を成膜する。また、被素子形成層の温度を高くして酸化物半導体膜を成膜することにより、作製されるトランジスタの電界効果移動度を向上させ、ゲートバイアス・ストレスに対する安定性を高めることができる。

【0197】

また、このとき、被素子形成層600_aは平坦であることが好ましい。例えば、被素子形成層600_aの平均面粗さは、1nm以下、さらには0.3nm以下であることが好ましい。被素子形成層600_aの平坦性を向上させることにより、アモルファス状態の酸化物半導体以上に移動度を向上させることができる。例えば、化学的機械研磨(CMP)処理及びプラズマ処理の一つ又は複数により、被素子形成層600_aを平坦化することができる。このとき、プラズマ処理には、希ガスイオンで表面をスパッタリングする処理やエッチングガスを用いて表面をエッチングする処理も含まれる。

【0198】

次に、図11(B)に示すように、半導体層603_aの上に導電層605a_a及び導電層605b_aを形成する。

【0199】

例えば、スパッタリング法などを用いて導電層605a_a及び導電層605b_aに適用可能な材料の膜を第1の導電膜として成膜し、該第1の導電膜の一部をエッチングすることにより導電層605a_a及び導電層605b_aを形成することができる。

【0200】

次に、図11(C)に示すように、半導体層603_aに接するように絶縁層602_aを形成する。

【0201】

例えば、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下で、スパッタリング法を用いて絶縁層602_aに適用可能な膜を成膜することにより、絶縁層602_aを形成することができる。スパッタリング法を用いて絶縁層602_aを形成することにより、トランジスタのバックチャネルとしての機能を有する半導体層603_aの部分における抵抗の低下を抑制することができる。また、絶縁層602_aを形成する際の被素子形成層600_aの温度は、室温以上300℃以下であることが好ましい。

【0202】

また、絶縁層602_aを形成する前にN2O、N2、又はArなどのガスを用いたプラズマ処理を行い、露出している半導体層603_aの表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、その後、大気に触れることなく、絶縁層602_aを形成することが好ましい。

【0203】

次に、絶縁層602_aの上に導電層601_aを形成する。

【0204】

例えば、スパッタリング法などを用いて導電層601_aに適用可能な材料の膜を第2の導電膜として成膜し、該第2の導電膜の一部をエッチングすることにより導電層601_aを形成することができる。

【0205】

また、図7(A)に示すトランジスタの作製方法の一例では、例えば600℃以上750℃以下、又は600℃以上基板の歪み点未満の温度で加熱処理を行う。例えば、酸化物半導体膜を成膜した後、酸化物半導体膜の一部をエッチングした後、第1の導電膜を成膜した後、第1の導電膜の一部をエッチングした後、絶縁層602_aを形成した後、第2の導電膜を成膜した後、又は第2の導電膜の一部をエッチングした後に上記加熱処理を行う。上記加熱処理を行うことにより、水素、水、水酸基、又は水素化物などの不純物が半導体層603_aから排除される。

【0206】

なお、上記加熱処理を行う加熱処理装置としては、電気炉、又は抵抗発熱体などの発熱体からの熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えばGRTA(Gas Rapid Thermal Anneal)装置又はLRTA(Lamp Rapid Thermal Anneal)装置などのRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、例えばハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、又は高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。また、GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスとしては、例えば希ガス、又は加熱処理によって被処理物と反応しない不活性気体(例えば窒素)を用いることができる。

【0207】

また、上記加熱処理を行った後、その加熱温度を維持しながら又はその加熱温度から降温する過程で該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エア(露点が−40℃以下、好ましくは−60℃以下の雰囲気)を導入してもよい。このとき、酸素ガス又はN2Oガスは、水、水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又はN2Oガスの純度を、6N以上、好ましくは7N以上、すなわち、酸素ガス又はN2Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下とすることが好ましい。酸素ガス又はN2Oガスの作用により、半導体層603_aに酸素が供給され、半導体層603_a中の酸素欠乏に起因する欠陥を低減することができる。なお、上記高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エアの導入は、上記加熱処理時に行ってもよい。

【0208】

また、図7(A)に示すトランジスタの作製方法の一例では、半導体層603_a形成後、導電層605a_a及び導電層605b_a形成後、絶縁層602_a形成後、導電層601_a形成後、又は上記加熱処理後に酸素プラズマによる酸素ドーピング処理など、酸素イオンを電界で加速させる方法を用いて酸化物半導体膜に酸素を注入してもよい。例えば2.45GHzの高密度プラズマにより酸素ドーピング処理を行ってもよい。また、イオン注入法を用いて酸素ドーピング処理を行ってもよい。酸素ドーピング処理を行うことにより、作製されるトランジスタの電気特性のばらつきを低減することができる。例えば、酸素ドーピング処理を行い、絶縁層602_aを、化学量論的組成比より酸素が多い状態にする。

【0209】

半導体層603_aに接する絶縁層中の酸素を過剰にすることにより、半導体層603_aに酸素が供給されやすくなる。よって、半導体層603_a中、又は絶縁層602_aと、半導体層603_aとの界面における酸素欠陥を低減することができるため、半導体層603_aのキャリア濃度をより低減することができる。また、これに限定されず、製造過程により半導体層603_aに含まれる酸素を過剰にした場合であっても、半導体層603_aに接する上記絶縁層により、半導体層603_aからの酸素の脱離を抑制することができる。

【0210】

例えば、絶縁層602_aとして、酸化ガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムの組成をGa2Oxにすることができる。

【0211】

また、絶縁層602_aとして、酸化アルミニウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化アルミニウムの組成をAl2Oxにすることができる。

【0212】

また、絶縁層602_aとして、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムを含む絶縁層を形成する場合、該絶縁層に酸素を供給し、酸化ガリウムアルミニウム又は酸化アルミニウムガリウムの組成をGaxAl2−xO3+αとすることができる。

【0213】

以上の工程によって、半導体層603_aから、水素、水、水酸基、又は水素化物(水素化合物ともいう)などの不純物を排除し、且つ半導体層603_aに酸素を供給することにより、酸化物半導体層を高純度化させることができる。

【0214】

さらに、上記加熱処理とは別に、絶縁層602_aを形成した後に、不活性ガス雰囲気下、又は酸素ガス雰囲気下で加熱処理(好ましくは200℃以上600℃以下、例えば250℃以上350℃以下)を行ってもよい。

【0215】

上記に示す被素子形成層600_aの意図的な加熱温度又は酸化物半導体膜の成膜後の加熱処理の温度は、150℃以上、好ましくは200℃以上、より好ましくは400℃以上である。酸化物半導体膜の成膜後の加熱処理では、300℃以上であれば膜中に含まれる水素等の不純物を放出させ、該不純物を除去すること(脱水化、脱水素化)ができる。

【0216】

上記加熱処理は酸素雰囲気中で行うことができるが、上記のように脱水化・脱水素化を窒素雰囲気又は減圧下で行ってから、酸素雰囲気中で熱処理をするように2段階で行うようにしてもよい。脱水化・脱水素化後に酸素を含む雰囲気中で熱処理することにより、酸化物半導体中に酸素を加えることも可能となり、上記加熱処理の効果をより高めることができる。また、上記加酸化処理を、酸化物半導体層に接するように絶縁層を設けた状態で熱処理を行ってもよい。例えば酸化物半導体層中及び酸化物半導体層に積層する層との界面には、酸素欠損による欠陥が生成されやすいが、上記加熱処理により酸化物半導体中に酸素を過剰に含ませることにより、定常的に生成される酸素欠損を過剰な酸素によって補償することができる。上記過剰な酸素は、主に格子間に存在する酸素であり、その酸素濃度を1×1016/cm3以上2×1020/cm3以下にすることにより、例えば結晶化した場合であっても結晶に歪みなどを与えることなく酸化物半導体層中に酸素を含ませることができる。

【0217】

また、酸化物半導体膜の成膜後に加熱処理を行うことにより、作製されるトランジスタのゲートバイアス・ストレスに対する安定性を高めることができる。また、トランジスタの電界効果移動度を向上させることもできる。

【0218】

さらに、図11(E)に示すように、導電層601_aが形成される側から半導体層603_aにドーパントを添加することにより、絶縁層602_aを介して自己整合で領域604a_a及び領域604b_aを形成する。

【0219】

例えば、イオンドーピング装置又はイオン注入装置を用いてドーパントを添加することができる。

【0220】

なお、図7(A)に示すトランジスタの作製方法の一例を示したが、これに限定されず、例えば図7(B)に示す各構成要素において、名称が図7(A)に示す各構成要素と同じであり且つ機能の少なくとも一部が図7(A)に示す各構成要素と同じであれば、図7(A)に示すトランジスタの作製方法の一例の説明を適宜援用することができる。

【0221】

図7乃至図11を用いて説明したように、本実施の形態におけるトランジスタの一例では、ゲートとしての機能を有する導電層と、ゲート絶縁層としての機能を有する絶縁層と、ゲート絶縁層としての機能を有する絶縁層を介してゲートとしての機能を有する導電層に重畳し、チャネルが形成される酸化物半導体層と、酸化物半導体層に電気的に接続され、ソース又はドレインの一方としての機能を有する導電層と、酸化物半導体層に電気的に接続され、ソース又はドレインの他方としての機能を有する導電層と、を含む構成にすることにより、トランジスタを構成することができる。

【0222】

また、本実施の形態におけるトランジスタの一例では、酸化物半導体層のキャリア濃度を1×1014/cm3未満、好ましくは1×1012/cm3未満、さらに好ましくは1×1011/cm3未満にすることができる。

【0223】

酸化物半導体をトランジスタに適用するにはキャリア密度を1×1018/cm3以下にすることが好ましい。InあるいはZnを含む酸化物半導体は、GaやSnを酸化物半導体を構成する一元素として含ませることのみならず、上記のように酸化物半導体膜の高純度化(水素等の除去)を図ることや、成膜後の熱処理をすることによってキャリア密度を1×1018/cm3以下にすることができる。

【0224】

また、酸化物半導体膜を成膜する際の加熱処理及び成膜後の加熱処理の一つ又は複数を行うことにより、トランジスタの閾値電圧をプラスシフトさせ、ノーマリ・オフ化させることができ、また、チャネル幅1μmあたりのオフ電流を、10aA(1×10−17A)以下、さらには1aA(1×10−18A)以下、さらには10zA(1×10−20A)以下、さらには1zA(1×10−21A)以下、さらには100yA(1×10−22A)以下にすることができる。トランジスタのオフ電流は、低ければ低いほどよいが、本実施の形態におけるトランジスタのオフ電流の下限値は、約10−30A/μmであると見積もられる。

【0225】

本実施の形態の酸化物半導体層を含むトランジスタを、例えば上記実施の形態における記憶回路のトランジスタに用いることにより、記憶回路におけるデータの保持時間を長くすることができる。

【0226】

また、本実施の形態におけるトランジスタの一例は、他のトランジスタ(例えば、元素周期表における第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタ)と積層させることができる。よって、同一基板上に上記酸化物半導体層を含むトランジスタ及び上記他のトランジスタを形成しつつ、回路面積を縮小することができる。

【0227】

実施の形態1でも説明したように、単結晶シリコンを用いたトランジスタ(図1(B)等のトランジスタ111に相当)上に、酸化物半導体を用いたトランジスタ(図1(B)等のトランジスタ107に相当)を設ける構造が好ましい。当該構造は、高速動作、データの保持、及び回路面積の縮小の全てを実現することができる。

【0228】

また、上記酸化物半導体を用いたトランジスタは、非晶質又は結晶のいずれの場合であっても比較的高い電界効果移動度を得ることができる。このような電界効果移動度の向上は、脱水化・脱水素化による不純物の除去のみならず、高密度化により原子間距離が短くなるためとも推定される。また、酸化物半導体膜から不純物を除去して高純度化することにより、結晶化を図ることもできる。例えば、In−Sn−Zn系酸化物半導体では31cm2/Vsec超、好ましくは39cm2/Vsec超、より好ましくは60cm2/Vsec超の電界効果移動度を得ることも可能である。また、高純度化された非単結晶酸化物半導体は、理想的には100cm2/Vsecを超える電界効果移動度を実現することも可能になると示唆される。また、本実施の形態におけるトランジスタの一例では、酸化物半導体層の欠陥密度が少ないほどトランジスタの電界効果移動度が高くなると示唆される。その理由について以下に説明する。

【0229】

酸化物半導体層を含む電界効果トランジスタに限らず、実際に測定される電界効果トランジスタの電界効果移動度は、様々な理由によって本来の電界効果移動度よりも低くなる。電界効果移動度を低下させる要因としては、半導体層内部の欠陥や半導体層と絶縁層との界面の欠陥がある。例えば、Levinsonモデルを用いると、酸化物半導体層に欠陥がないと仮定した場合のトランジスタの電界効果移動度を理論的に導き出すことができる。

【0230】

半導体層本来の電界効果移動度をμ0とし、測定される電界効果移動度をμとし、半導体層中に何らかのポテンシャル障壁(粒界等)が存在すると仮定すると、測定される電界効果移動度であるμは、下記の式(1)で表される。

【0231】

【数1】

【0232】

上記式(1)において、Eはポテンシャル障壁の高さであり、kがボルツマン定数、Tは絶対温度である。また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinsonモデルにおいて、ポテンシャル障壁の高さであるEは、下記の式(2)で表される。

【0233】

【数2】

【0234】

上記式(2)において、eは電気素量、Nはチャネル内の単位面積当たりの平均欠陥密度、εは半導体の誘電率、nはチャネルのキャリア面密度、Coxは単位面積当たりの容量、Vgはゲート電圧、tはチャネルの厚さである。なお、厚さ30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。さらに、線形領域におけるドレイン電流Idは、下記の式(3)で表される。

【0235】

【数3】

【0236】

上記式(3)において、Lはチャネル長、Wはチャネル幅であり、ここでは、L=W=10μmである。また、Vdはドレイン電圧である。さらに、上式の両辺をVgで割り、更に両辺の対数を取ると、式(3)を下記の式(4)に変換することができる。

【0237】

【数4】

【0238】

上記式(4)において、右辺はVgの関数である。式(4)からわかるように、縦軸をln(Id/Vg)、横軸を1/Vgとして実測値をプロットして得られるグラフの直線の傾きから欠陥密度Nが求められる。すなわち、トランジスタのId―Vg特性から、欠陥密度を評価することができる。例えば、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)の比率が、In:Ga:Zn=1:1:1[原子数比]である酸化物半導体膜の欠陥密度Nは、1×1012/cm2程度である。

【0239】

上記の方法により求めた欠陥密度などをもとに、上記の式(1)及び式(2)を用いて本来の半導体層の電界効果移動度であるμ0を求めると、μ0=120cm2/Vsとなる。通常、欠陥のあるIn−Ga−Zn系酸化物で測定される電界効果移動度は、40cm2/Vs程度であるが、しかし、半導体内部及び半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度μ0は120cm2/Vsとなると予想できる。このことから、欠陥が少ないほど酸化物半導体の移動度、さらにはトランジスタの電界効果移動度は高いことがわかる。例えばCAACなどの酸化物半導体層は、欠陥密度が低い。

【0240】

ただし、半導体層内部に欠陥がなくても、チャネルとゲート絶縁層との界面での散乱によってトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁物界面からxだけ離れた場所における移動度μ1は、下記の式(5)で表される。

【0241】

【数5】

【0242】

上記式(5)において、Dはゲート方向の電界、B、lは定数である。B及びlは、実際の測定結果より求めることができ、上記の測定結果では、B=2.38×107cm/s、l=10nm(界面散乱が及ぶ深さ)となる。式(5)では、Dが増加する(すなわち、ゲート電圧が高くなる)と式(5)の第2項が増加するため、Dが増加すると移動度μ1は低下することがわかる。

【0243】

半導体層内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度μ2の計算結果を図12に示す。なお、上記計算には、シノプシス社製デバイスシミュレーションソフト、Sentaurus Deviceを使用する。また、酸化物半導体層において、バンドギャップを2.8電子ボルトとし、電子親和力を4.7電子ボルトとし、比誘電率を15とし、厚さを15nmとする。さらに、トランジスタにおいて、ゲート、ソース、ドレインの仕事関数をそれぞれ、5.5電子ボルト、4.6電子ボルト、4.6電子ボルトとする。また、ゲート絶縁層において、厚さを100nmとし、比誘電率を4.1とする。さらに、トランジスタにおいて、チャネル長及びチャネル幅をともに10μmとし、ドレイン電圧Vdを0.1Vとする。

【0244】

図12に示すように、ゲート電圧VGが1V付近のときの電界効果移動度は、100cm2/Vs以上と高いが、ゲート電圧VGがさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること(Atomic Layer Flatnessともいう)が望ましい。

【0245】

さらに、上記のように高い電界効果移動度の酸化物半導体を用いた、微細なトランジスタにおける電気特性の計算結果を以下に示す。

【0246】

まず、計算に用いたトランジスタの断面構造を図13に示す。図13に示すトランジスタは酸化物半導体層にN型の半導体領域653a及び653b、並びに半導体領域653cを有する。半導体領域653a及び半導体領域653bの抵抗率は2×10−3Ωcmとする。

【0247】

図13(A)に示すトランジスタは、下地絶縁物651及び埋め込み絶縁物652の上に設けられる。埋め込み絶縁物652は、酸化アルミニウムを用いて下地絶縁物651に埋め込まれるように設けられる。

【0248】

また、図13(A)に示すトランジスタは、半導体領域653aと、半導体領域653bと、半導体領域653cと、ゲート絶縁層654と、ゲート電極655と、側壁絶縁物656aと、側壁絶縁物656bと、絶縁層657と、ソース電極658aと、ドレイン電極658bと、を含む。

【0249】

半導体領域653cは、半導体領域653a及び半導体領域653bの間に挟まれて設けられる。半導体領域653cは、チャネル形成領域となる真性の半導体領域である。

【0250】

ゲート電極655は、ゲート絶縁層654の上に設けられる。なお、ゲート電極655の幅を33nmとする。

【0251】

側壁絶縁物656a及び側壁絶縁物656bは、ゲート電極655の側面に接するように設けられる。図13(A)に示すトランジスタでは、側壁絶縁物656aの下の半導体領域は、N型の半導体領域653aに含まれ、側壁絶縁物656bの下の半導体領域は、N型の半導体領域653bに含まれる。なお、側壁絶縁物656a及び側壁絶縁物656bのそれぞれの幅を5nmとする。

【0252】

絶縁層657は、ゲート電極655の上に設けられる。絶縁層657は、ゲート電極655と他の配線との短絡を防止する機能を有する。

【0253】

ソース電極658aは、半導体領域653aに接する。

【0254】

ドレイン電極658bは、半導体領域653bに接する。

【0255】

なお、図13(A)に示すトランジスタにおけるチャネル幅を40nmとする。

【0256】

また、図13(B)に示すトランジスタは、図13(A)に示すトランジスタと比較して、側壁絶縁物656a及び側壁絶縁物656bの下の半導体領域の導電型が異なる。図13(B)に示すトランジスタでは、側壁絶縁物656a及び側壁絶縁物656bの下の半導体領域は、真性の半導体領域653cに含まれる。すなわち、図13(B)に示すトランジスタは、半導体領域653aとゲート電極655が重ならない領域及び半導体領域653cとゲート電極655が重ならない領域を含む。この領域のそれぞれをオフセット領域といい、その幅をオフセット長(Loffともいう)という。図13(B)において、オフセット長は、側壁絶縁物656a及び側壁絶縁物656bのそれぞれの幅と同じである。

【0257】

なお、計算に使用するその他のパラメータは上記のとおりである。また、計算には、シノプシス社製デバイス計算ソフト、Sentaurus Deviceを使用した。

【0258】

図14は、図13(A)に示される構造のトランジスタのドレイン電流(Id、実線)及び移動度(μ、点線)のゲート電圧(Vg、ゲートとソースの電位差)依存性を示す図である。ドレイン電流Idは、ドレイン電圧(ドレインとソースの電位差)を+1Vとし、電界効果移動度μはドレイン電圧を+0.1Vとして計算したものである。

【0259】

図14(A)は、ゲート絶縁層654の厚さが15nmであるトランジスタの場合の図であり、図14(B)は、ゲート絶縁層654の厚さが10nmであるトランジスタの場合の図であり、図14(C)は、ゲート絶縁層654の厚さが5nmであるトランジスタの場合の図である。図14(A)乃至図14(C)に示すように、ゲート絶縁層654が薄くなるほど、特にオフ状態でのドレイン電流Id(オフ電流)が顕著に低下する。一方、電界効果移動度μのピーク値やオン状態でのドレイン電流Id(オン電流)には目立った変化が無い。また、ゲート電圧1V前後で、ドレイン電流の値は、記憶回路などで必要とされる10μAを超える。

【0260】

図15は、図13(B)に示す構造で、オフセット長(Loff)を5nmであるトランジスタのドレイン電流Id(実線)及び移動度μ(点線)のゲート電圧Vg依存性を示す図である。ここでは、ドレイン電圧を+1Vとしてドレイン電流Idを計算し、ドレイン電圧を+0.1Vとして電界効果移動度μを計算する。さらに、図15(A)は、ゲート絶縁層654の厚さが15nmである場合の図であり、図15(B)は、ゲート絶縁層654の厚さが10nmである場合の図であり、図15(C)は、ゲート絶縁層654の厚さが5nmである場合の図である。

【0261】

また、図16は、図13(B)に示される構造のトランジスタで、オフセット長Loffを15nmとしたもののドレイン電流Id(実線)及び移動度μ(点線)のゲート電圧依存性を示す。ここでは、ドレイン電流Idを、ドレイン電圧を+1Vとして計算し、移動度μはドレイン電圧を+0.1Vとして計算する。図16(A)は、ゲート絶縁層654の厚さが15nmである場合の図であり、図16(B)は、ゲート絶縁層654の厚さが10nmである場合の図であり、図16(C)は、ゲート絶縁層654の厚さが5nmの場合の図である。

【0262】

図14乃至図16からわかるように、いずれもゲート絶縁層654が薄くなるほど、トランジスタのオフ電流が顕著に低下する一方、移動度μのピーク値やトランジスタのオン電流には目立った変化が無い。

【0263】

なお、電界効果移動度μのピークは、図14では80cm2/Vs程度であるが、図15では60cm2/Vs程度であり、図16では40cm2/Vs程度であることから、オフセット長(Loff)が増加するほど低下する。また、トランジスタのオフ電流も同様な傾向がある。一方、トランジスタのオン電流は、オフセット長(Loff)が増加すると共に減少するが、トランジスタのオフ電流の減少に比べるとはるかに緩やかである。また、いずれのトランジスタもゲート電圧1V前後で、ドレイン電流は、例えば記憶回路などで必要とされる10μAを超える。

【0264】

上記に示すように、酸化物半導体を含むトランジスタでは、電界効果移動度を高くすることもできるため、上記実施の形態における記憶回路を支障なく動作させることができる。

【0265】

さらに、上記トランジスタの一例として、チャネル形成層としてIn、Sn、Znを含有する酸化物半導体層を含むトランジスタの例について説明する。

【0266】

例えば、In、Sn、及びZnを主成分とする酸化物半導体層と、厚さ100nmのゲート絶縁層を含み、チャネル長Lが3μm、チャネル幅Wが10μmであるトランジスタの特性を図17(A)乃至図17(C)に示す。なお、Vdは10Vとする。

【0267】

図17(A)は、被素子形成層を意図的に加熱せず、スパッタリング法を用いてIn、Sn、Znを主成分とする酸化物半導体膜を成膜して酸化物半導体層を形成したときにおけるトランジスタの特性を示す図である。図17(A)において、電界効果移動度は18.8cm2/Vsecである。一方、図17(B)は、基板を200℃に加熱してIn、Sn、Znを主成分とする酸化物半導体膜を成膜して酸化物半導体層を形成したときのトランジスタの特性を示す図である。図17(B)において、電界効果移動度は32.2cm2/Vsecである。よって、意図的に加熱することにより、トランジスタの電界効果移動度が向上することがわかる。

【0268】

また、図17(C)は、In、Sn、及びZnを主成分とする酸化物半導体膜を200℃でスパッタリング法を用いて成膜して酸化物半導体層を形成した後、650℃で加熱処理をしたときのトランジスタの特性を示す図である。図17(C)において、電界効果移動度は34.5cm2/Vsecである。よって、酸化物半導体膜を成膜した後に加熱処理をすることによって、上記電界効果移動度が高くなることがわかる。

【0269】

なお、In、Sn、及びZnを主成分とする酸化物半導体層に酸素イオンを注入し、加熱処理により該酸化物半導体に含まれる水素、水、水酸基、又は水素化物などの不純物を放出させ、その加熱処理と同時に又はその後の加熱処理により酸化物半導体層を結晶化させても良い。上記結晶化又は再結晶化の処理により結晶性の良い非単結晶酸化物半導体層を得ることができる。

【0270】

また、被素子形成層を意図的に加熱しないで形成されたIn、Sn、及びZnを主成分とする酸化物半導体層を含むトランジスタは、例えば図17(A)に示すように、閾値電圧がマイナスシフトしてしまう傾向がある。しかし、被素子形成層を意図的に加熱して形成された酸化物半導体層を用いた場合、例えば図17(B)に示すように、閾値電圧はトランジスタがノーマリ・オフとなる方向にシフトする。よって、酸化物半導体膜を成膜する際の加熱及び成膜後の加熱処理の一つ又は複数により、トランジスタがノーマリ・オフになりやすくなることがわかる。

【0271】

また、In、Sn及びZnの比率を変えることによってもトランジスタの閾値電圧を制御することができる。例えば、酸化物半導体膜の組成比をIn:Sn:Zn=2:1:3とすることにより、トランジスタをノーマリ・オフ型にしやすくすることができる。

【0272】

さらに、例えば、2MV/cm、150℃、1時間印加の条件において、ゲートバイアス・ストレス試験(BT試験ともいう)を行うと、ドリフトが±1.5V未満、好ましくは±1.0V未満となる。よって、酸化物半導体膜を成膜する際の加熱及び成膜後の加熱処理の一つ又は複数を行うことにより、ゲートバイアス・ストレスに対する安定性が高くなることがわかる。ここで、酸化物半導体膜成膜後に加熱処理を行っていない試料1と、650℃の加熱処理を行った試料2のトランジスタにおけるBT試験の結果を図18及び図19に示す。なお、BT試験としては、プラスBT試験とマイナスBT試験を行った。

【0273】

プラスBT試験としては、まず被素子形成層(基板)の温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids特性の測定を行った。次に、被素子形成層(基板)の温度を150℃とし、Vdsを0.1Vとした。次に、ゲート絶縁層に印加される電界強度が2MV/cmとなるようにVgsに20Vを印加し、そのまま1時間保持した。次に、Vgsを0Vとした。次に、被素子形成層(基板)の温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids測定を行った。

【0274】

また、マイナスBT試験としては、まず被素子形成層(基板)の温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids特性の測定を行った。次に、被素子形成層(基板)の温度を150℃とし、Vdsを0.1Vとした。次に、ゲート絶縁層に印加される電界強度が−2MV/cmとなるようにVgsに−20Vを印加し、そのまま1時間保持した。次に、Vgsを0Vとした。次に、被素子形成層(基板)の温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids測定を行った。

【0275】

試料1のプラスBT試験の結果を図18(A)に示し、試料1のマイナスBT試験の結果を図18(B)に示す。また、試料2のプラスBT試験の結果を図19(A)に示し、試料2のマイナスBT試験の結果を図19(B)に示す。

【0276】

図18(A)及び図18(B)に示すように、試料1のプラスBT試験及びマイナスBT試験によるトランジスタの閾値電圧の変動は、それぞれ1.80V及び−0.42Vであった。また、図19(A)及び図19(B)に示すように、試料2のプラスBT試験及びマイナスBT試験によるトランジスタの閾値電圧の変動は、それぞれ0.79V及び0.76Vであった。よって、試料1及び試料2の両方において、BT試験前後におけるトランジスタの閾値電圧の変動が小さく、信頼性が高いことがわかる。

【0277】

さらに、組成比がIn:Sn:Zn=1:1:1である金属酸化物のターゲットを用いて、被素子形成層を意図的に加熱せずにスパッタリング法を用いて成膜した酸化物半導体膜は、X線回折(XRD:X−Ray Diffraction)でハローパターンが観測される。しかし、上記酸化物半導体膜を加熱処理することにより結晶化させることができる。このときの加熱処理温度は任意であるが、例えば650℃の加熱処理を行うことで、X線回折により明確な回折ピークを観測することができる。

【0278】

ここで、In−Sn−Zn−O膜のXRD分析の結果を以下に示す。なお、XRD分析では、Bruker AXS社製X線回折装置D8 ADVANCEを用いてOut−of−Plane法で測定した。

【0279】

XRD分析を行った試料として、試料A及び試料Bを用意した。以下に試料A及び試料Bの作製方法を説明する。

【0280】

脱水素化処理済みの石英基板上にIn−Sn−Zn−O膜を100nmの厚さで成膜した。

【0281】

当該In−Sn−Zn−O膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。このときのターゲットとして、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いた。なお、成膜時の加熱温度は200℃とした。上記工程により作製した試料を試料Aとする。

【0282】

次に、試料Aと同様の方法で作製した試料に対し、650℃の温度で加熱処理を行った。ここでは、窒素雰囲気で1時間の加熱処理を行い、温度を下げずに酸素雰囲気でさらに1時間の加熱処理を行った。上記工程により作製した試料を試料Bとする。

【0283】

試料A及び試料BのXRDスペクトルを図20に示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2θが35deg近傍及び37deg〜38degに結晶由来のピークが観測された。よって、In、Sn、Znを主成分とする酸化物半導体膜を成膜する際の加熱、及び成膜後の加熱処理の一つ又は複数を行うことにより、酸化物半導体層の結晶性が向上することがわかる。

【0284】

酸化物半導体膜を成膜する際の加熱、及び成膜後の加熱処理の一つ又は複数を行うことにより、作製したトランジスタのチャネル幅1μmあたりのオフ電流は、例えば図21に示すように、被素子形成層(基板)の温度が125℃の場合には、1aA(1×10−18A)以下、85℃の場合には100zA(1×10−19A)以下、室温(27℃)の場合には1zA(1×10−21A)以下である。また、上記トランジスタのチャネル幅1μmあたりのオフ電流を、好ましくは、125℃において0.1aA(1×10−19A)以下、85℃において10zA(1×10−20A)以下、室温において0.1zA(1×10−22A)以下にすることもできる。

【0285】

なお、In、Sn、Znを主成分とする酸化物半導体膜は、加熱処理によって膜中の水素を除去することができるが、In、Ga、Znを主成分とする酸化物半導体膜と比べて水分の放出温度が高いため、好ましくは最初から不純物の含まれない膜を形成しておくことが好ましい。

【0286】

さらに、酸化物半導体膜の成膜後に650℃の加熱処理を行った試料Bのトランジスタにおいて、被素子形成層(基板)の温度と電気的特性の関係について評価した。

【0287】

測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、Lovが片側3μm(合計6μm)、dWが0μmのトランジスタである。なお、Vdsは10Vとした。また、被素子形成層(基板)の温度が、−40℃、−25℃、25℃、75℃、125℃、及び150℃である6条件で上記評価を行った。なお、Lovとは、ゲート電極と一対の電極との重畳する幅のことをいい、dWとは、酸化物半導体膜に対する一対の電極のはみ出しのことをいう。

【0288】

図22に、Ids(実線)及び電界効果移動度(点線)のVgs依存性を示す。また、図23(A)に被素子形成層(基板)の温度と閾値電圧の関係を示し、図23(B)に被素子形成層(基板)の温度と電界効果移動度の関係を示す。

【0289】

図22及び図23(A)より、被素子形成層(基板)の温度が高いほど閾値電圧が低くなることがわかる。なお、その範囲は−40℃〜150℃で1.09V〜−0.23Vであった。

【0290】

また、図22及び図23(B)より、被素子形成層(基板)の温度が高いほど電界効果移動度が低くなることがわかる。なお、その範囲は−40℃〜150℃で36cm2/Vs〜32cm2/Vsであった。従って、上述の温度範囲において電気的特性の変動が小さいことがわかる。

【0291】

以上がIn、Sn、Znを含有する酸化物半導体層を含むトランジスタの説明である。

【0292】

上記In、Sn、Znを主成分とする上記酸化物半導体層を含むトランジスタでは、オフ電流を1aA/μm以下に保ちつつ、電界効果移動度を30cm2/Vsec以上、好ましくは40cm2/Vsec以上、より好ましくは60cm2/Vsec以上とし、LSIで要求されるオン電流の値を満たすことができる。例えば、L/W=33nm/40nmのトランジスタにおいて、ゲート電圧が2.7Vでドレイン電圧が1.0Vのときに、12μA以上のオン電流を流すことができる。また、トランジスタの動作に求められる温度範囲においても、十分な電気的特性を確保することができる。このような特性であれば、第14族の半導体(シリコンなど)を含有する半導体層を含むトランジスタを用いた回路の中に上記酸化物半導体層を含むトランジスタを混載しても、動作速度を犠牲にすることなく新たな機能を有する回路を提供することができる。

【0293】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0294】

(実施の形態7)

本実施の形態では、半導体装置の一例として、CPUなどの演算処理装置について説明する。

【0295】

図24に、演算処理装置の一例を示す。

【0296】

図24の演算処理装置は、バスインターフェース(IFともいう)801と、制御装置(CTLともいう)802と、キャッシュメモリ(CACHEともいう)803と、命令デコーダ(IDecoderともいう)805と、処理回路806と、を有する。

【0297】

バスインターフェース801は、外部との信号のやりとり、及び演算処理装置内の各回路との信号のやりとりなどを行う機能を有する。

【0298】

制御装置802は、演算処理装置内の各回路の動作を制御する機能を有する。

【0299】

キャッシュメモリ803は、制御装置802により制御され、演算処理装置における動作時のデータを一時的に保持する機能を有する。なお、例えば、1次キャッシュ及び2次キャッシュとして、演算処理装置にキャッシュメモリ803を複数設けてもよい。

【0300】

命令デコーダ805は、読み込んだ命令信号を翻訳する機能を有する。翻訳された命令信号は、制御装置802に入力され、制御装置802は命令信号に応じた制御信号を処理回路806に出力する。

【0301】

処理回路806は、制御装置802により制御され、入力された命令信号に応じて演算処理を行う機能を有する。処理回路806は、ALU等を有する部分であり、図1〜図6の論理回路部101及び記憶回路103を設けることができる。

【0302】

なお、演算処理装置にメモリとしてレジスタ等を設けてもよい。このときメモリは、制御装置802により制御される。例えば、複数のメモリを演算処理装置に設け、あるメモリを処理回路806用のメモリとし、別のメモリを命令デコーダ805用のレジスタとしてもよい。

【0303】

また、制御装置802や命令デコーダ805内に、図1〜図6の記憶回路103を設けてもよい。そうすることで、制御装置802や命令デコーダ805において、集積回路のトランジスタに入力されるデータを当該記憶回路に記憶することができ、データの保持、高速動作、消費電力の低減を行うことができる。

【0304】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0305】

(実施の形態8)

本実施の形態では、上記実施の形態7における演算処理装置を備えた電子機器の例について説明する。

【0306】

本実施の形態における電子機器の一例について、図25(A)〜図25(D)を用いて説明する。

【0307】

図25(A)に示す電子機器は、携帯型情報端末の一例である。図25(A)に示す情報端末は、筐体1001aと、筐体1001aに設けられた表示部1002aと、を具備する。

【0308】

なお、筐体1001aの側面1003aに外部機器に接続させるための接続端子、及び図25(A)に示す携帯型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0309】

図25(A)に示す携帯型情報端末は、筐体1001aの中に、CPUと、メモリと、外部機器とCPU及びメモリとの信号の送受信を行うインターフェースと、外部機器との信号の送受信を行うアンテナと、を備える。

【0310】

図25(A)に示す携帯型情報端末は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

【0311】

図25(B)に示す電子機器は、折り畳み式の携帯型情報端末の例である。図25(B)に示す携帯型情報端末は、筐体1001bと、筐体1001bに設けられた表示部1002bと、筐体1004と、筐体1004に設けられた表示部1005と、筐体1001b及び筐体1004を接続する軸部1006と、を具備する。

【0312】

また、図25(B)に示す携帯型情報端末では、軸部1006により筐体1001b又は筐体1004を動かすことにより、筐体1001bを筐体1004に重畳させることができる。

【0313】

なお、筐体1001bの側面1003b又は筐体1004の側面1007に外部機器に接続させるための接続端子、及び図25(B)に示す携帯型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0314】

また、表示部1002b及び表示部1005に、互いに異なる画像又は一続きの画像を表示させてもよい。なお、表示部1005を必ずしも設けなくてもよく、表示部1005の代わりに、入力装置であるキーボードを設けてもよい。

【0315】

図25(B)に示す携帯型情報端末は、筐体1001b又は筐体1004の中に、CPUと、メモリと、外部機器とCPU及びメモリとの信号の送受信を行うインターフェースと、を備える。なお、図25(B)に示す携帯型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0316】

図25(B)に示す携帯型情報端末は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

【0317】

図25(C)に示す電子機器は、設置型情報端末の例である。図25(C)に示す設置型情報端末は、筐体1001cと、筐体1001cに設けられた表示部1002cと、を具備する。

【0318】

なお、表示部1002cを、筐体1001cにおける甲板部1008に設けることもできる。

【0319】

また、図25(C)に示す設置型情報端末は、筐体1001cの中に、CPUと、メモリと、外部機器とCPU及びメモリとの信号の送受信を行うインターフェースと、を備える。なお、図25(C)に示す設置型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0320】

さらに、図25(C)に示す設置型情報端末における筐体1001cの側面1003cに券などを出力する券出力部、硬貨投入部、及び紙幣挿入部の一つ又は複数を設けてもよい。

【0321】

図25(C)に示す設置型情報端末は、例えば現金自動預け払い機、券などの注文をするための情報通信端末(マルチメディアステーションともいう)、又は遊技機としての機能を有する。

【0322】

図25(D)は、設置型情報端末の例である。図25(D)に示す設置型情報端末は、筐体1001dと、筐体1001dに設けられた表示部1002dと、を具備する。なお、筐体1001dを支持する支持台を設けてもよい。

【0323】

なお、筐体1001dの側面1003dに外部機器に接続させるための接続端子、及び図25(D)に示す設置型情報端末を操作するためのボタンの一つ又は複数を設けてもよい。

【0324】

また、図25(D)に示す設置型情報端末は、筐体1001dの中に、CPUと、メモリと、外部機器とCPU及びメモリとの信号の送受信を行うインターフェースと、を備えてもよい。なお、図25(D)に示す設置型情報端末に、外部との信号の送受信を行うアンテナを設けてもよい。

【0325】

図25(D)に示す設置型情報端末は、例えばデジタルフォトフレーム、モニタ、又はテレビジョン装置としての機能を有する。

【0326】

上記実施の形態の演算処理装置は、図25(A)乃至図25(D)に示す電子機器のCPUとして用いられる。

【0327】

図25を用いて説明したように、本実施の形態における電子機器の一例は、CPUとして上記実施の形態における演算処理装置を具備する構成である。

【0328】

また、本実施の形態における電子機器の一例では、上記実施の形態における記憶回路及び論理回路を用いることにより、演算処理装置の消費電力を抑制しつつ、長時間データの保持を行うことができる。また、上記実施の形態における記憶回路及び論理回路を用いることにより、演算処理装置の面積を小さくすることができる。

【0329】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0330】

101 論理回路部

101a 論理回路部

101b 論理回路部

103 記憶回路

105 論理回路

107 トランジスタ

109 容量素子

111 トランジスタ

121 トランジスタ

123 トランジスタ

131 単結晶シリコン層

133 ゲート絶縁層

135 ゲート電極

137 酸化物半導体層

139 ゲート絶縁層

141 ゲート電極

143 電極

145 電極

147 絶縁層

149 電極

201 加算器

203 AND回路

205 選択回路

207 トランジスタ

209 トランジスタ

211 インバータ

301 算術演算部

303 論理演算部

305 シフト演算部

307 選択回路

309 選択回路

311 選択回路

401 トランジスタ

403 インバータ

405 トランジスタ

407 容量素子

409 インバータ

501 接続部

503 配線

505 メモリ

507 選択回路

600 被素子形成層

601 導電層

602 絶縁層

603 半導体層

604a 領域

604b 領域

605a 導電層

605b 導電層

606a 絶縁層

606b 絶縁層

607 絶縁層

651 下地絶縁物

652 埋め込み絶縁物

653a 半導体領域

653b 半導体領域

653c 半導体領域

654 ゲート絶縁層

655 ゲート電極

656a 側壁絶縁物

656b 側壁絶縁物

657 絶縁層

658a ソース電極

658b ドレイン電極

801 バスインターフェース

802 制御装置

803 キャッシュメモリ

805 命令デコーダ

806 処理回路

1001a 筐体

1001b 筐体

1001c 筐体

1001d 筐体

1002a 表示部

1002b 表示部

1002c 表示部

1002d 表示部

1003a 側面

1003b 側面

1003c 側面

1003d 側面

1004 筐体

1005 表示部

1006 軸部

1007 側面

1008 甲板部

【技術分野】

【0001】

技術分野は、半導体装置、半導体装置の駆動方法、及び半導体装置の作製方法に関する。半導体装置としては、特に、トランジスタ等の半導体素子を有する半導体集積回路に関する。

【背景技術】

【0002】

半導体集積回路の一つとして、プログラマブルロジックデバイス(Programmable Logic Device(PLD))がある。PLDは、製造後に内部の回路構成等について、決定・変更等が可能(再構成可能)な集積回路である(特許文献1参照)。

【0003】

PLDは、従来のASIC(Application Specific Integrated Circuit)などに比べて、開発期間の短縮が可能であり、設計仕様の変更に柔軟に対応できるなどの利点を有しており、様々な装置への利用が進んでいる。

【0004】

PLDは、例えば、複数の論理回路部と、論理回路部間の配線と、を有する。各論理回路部内の回路構成を変更、又は、論理回路部間の接続関係を変更することで、PLDの機能を変更することができる。

【0005】

更に、PLDは、記憶回路を有してもよく、当該記憶回路により論理回路部内の回路構成の情報や論理回路部間の接続関係の情報を記憶しておくことができる。

【0006】

なお、上記論理回路部としては、例えば演算論理ユニット(Arithmetic Logic Unit(ALU))が用いられる。ALUは、一般的に、加算器や減算器等を組み合わせた算術演算部と、AND回路やOR回路等を組み合わせた論理演算部と、シフト回路を有するシフト演算部と、それらを選択して出力するマルチプレクサ等の選択回路と、によって構成されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平11−317659号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記記憶回路としてSRAM又はDRAMを用いる場合、ALU間の接続関係の変更、又は各ALU内の回路構成の変更などを高速に行うことができる。しかし、SRAMやDRAMは揮発性であるため、電源電圧の供給を停止すると、記憶されていた情報が失われてしまう。

【0009】

また、上記記憶回路としてフラッシュメモリを用いる場合、不揮発性であるため、電源電圧の供給を停止しても情報を維持することができる。しかし、駆動電圧が高いため、高速動作や消費電力の低減を行うことは困難である。

【0010】

以上を鑑み、本発明の一様態では、電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を長時間維持できる半導体装置を提供することを課題の一とする。

【0011】

また、本発明の一様態では、論理回路部間の接続関係の変更、又は、各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0012】

本発明の一態様は、回路構成等の情報を記憶する記憶回路を有し、当該記憶回路内に酸化物半導体を用いた半導体素子を有する半導体装置である。具体的には、半導体装置はPLD(Programmable Logic Device)であり、論理回路部と、記憶回路と、を有する。そして、当該記憶回路に記憶されたデータに応じて論理回路部内の回路構成を維持する。

【0013】

また、半導体装置は、上記論理回路部を複数個有することが好ましく、その場合、上記記憶回路は、各論理回路部の回路構成、又は、論理回路部間の接続関係を維持する。論理回路部は、ALU(Arithmetic Logic Unit)を用いることができ、演算回路や選択回路等を有してもよい。

【0014】

なお、本明細書ではPLDのことを、再構成可能な回路とも呼ぶ。

【0015】

また、本明細書において、半導体装置とは、半導体を利用することで機能する物(素子、装置など)全般を指す。半導体装置は、半導体素子(トランジスタ、ダイオード等)、その半導体素子を搭載した電気装置(電子回路、表示装置、発光装置等)、およびその電気装置を搭載した電子機器をその範疇とする。

【0016】

本発明の他の一態様は、複数の演算回路と、選択回路と、記憶回路と、を有し、記憶回路は、トランジスタと、容量素子と、を有し、記憶回路は、トランジスタを介して容量素子及び選択回路にデータを入力し、選択回路は、データに応じて、複数の演算回路の演算結果の内の一つ又は複数を選択し、トランジスタのチャネル形成領域には、酸化物半導体が用いられている半導体装置である。

【0017】

本発明の他の一態様は、複数の論理回路部と、接続部と、を有し、接続部は、記憶回路と、第1のトランジスタと、を有し、第1のトランジスタのソース又はドレインの一方は、複数の論理回路部のうちの一つと電気的に接続され、第1のトランジスタのソース又はドレインの他方は、複数の論理回路部のうちの他の一つと電気的に接続され、記憶回路は、第2のトランジスタと、容量素子と、を有し、記憶回路は、第2のトランジスタを介して容量素子及び第1のトランジスタのゲートにデータを入力し、第1のトランジスタは、データに応じて、複数の論理回路部のうちの一つと他の一つとの電気的な接続を制御し、第2のトランジスタのチャネル形成領域には、酸化物半導体が用いられている半導体装置である。

【0018】

本発明の他の一態様は、複数の論理回路部と、第1の記憶回路と、接続部と、を有し、複数の論理回路部は、複数の演算回路と、選択回路と、を有し、第1の記憶回路は、第1のトランジスタと、第1の容量素子と、を有し、第1の記憶回路は、第1のトランジスタを介して第1の容量素子及び選択回路に第1のデータを入力し、選択回路は、第1のデータに応じて、複数の演算回路の演算結果の内の一つ又は複数を選択し、接続部は、第2の記憶回路と、第2のトランジスタと、を有し、第2のトランジスタのソース又はドレインの一方は、複数の論理回路部のうちの一つと電気的に接続され、第2のトランジスタのソース又はドレインの他方は、複数の論理回路部のうちの他の一つと電気的に接続され、第2の記憶回路は、第3のトランジスタと、第2の容量素子と、を有し、第2の記憶回路は、第3のトランジスタを介して第2の容量素子及び第2のトランジスタのゲートにデータを入力し、第2のトランジスタは、データに応じて、複数の論理回路部のうちの一つと他の一つとの電気的な接続を制御し、第1のトランジスタ及び第3のトランジスタは、チャネル形成領域に酸化物半導体が用いられている半導体装置である。

【発明の効果】

【0019】

本発明の一様態により、電源電圧の供給を停止しても、論理回路部間の接続関係の情報、又は、各論理回路部内の回路構成の情報を長時間保持できる半導体装置を提供することができる。

【0020】

また、本発明の一様態により、論理回路部間の接続関係の変更、又は各論理回路部の回路構成の変更を、高速又は低消費電力で行うことが可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0021】

【図1】半導体装置の一例を説明するための図。

【図2】半導体装置の一例を説明するための図。

【図3】半導体装置の一例を説明するための図。

【図4】半導体装置の一例を説明するための図。

【図5】半導体装置の一例を説明するための図。

【図6】半導体装置の一例を説明するための図。

【図7】半導体装置の一例を説明するための図。

【図8】CAACの一例を説明するための図。

【図9】CAACの一例を説明するための図。

【図10】CAACの一例を説明するための図。

【図11】半導体装置の作製方法の一例を説明するための図。

【図12】トランジスタのゲート電圧と電界効果移動度との関係を説明するための図。

【図13】半導体装置の断面構造の一例を説明するための図。

【図14】半導体装置における電気特性の計算結果を説明するための図。

【図15】半導体装置における電気特性の計算結果を説明するための図。

【図16】半導体装置における電気特性の計算結果を説明するための図。

【図17】半導体装置における電気特性の測定結果を説明するための図。

【図18】半導体装置における電気特性の測定結果を説明するための図。

【図19】半導体装置における電気特性の測定結果を説明するための図。

【図20】半導体装置における酸化物半導体膜のXRD測定結果を説明するための図。

【図21】半導体装置の特性を説明するための図。

【図22】半導体装置の特性を説明するための図。

【図23】半導体装置の特性を説明するための図。

【図24】演算処理装置の一例を説明するための図。

【図25】電子機器の一例を説明するための図。

【図26】CAACの一例を説明するための図。

【図27】半導体装置の一例を説明するための図。

【発明を実施するための形態】

【0022】

以下では、実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0023】

なお、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れかわることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れかえて用いることができるものとする。

【0024】

「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限はない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【0025】

回路図上は独立している構成要素どうしが電気的に接続しているように図示されている場合であっても、実際には、例えば配線の一部が電極としても機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0026】

「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

【0027】

図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0028】

「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものである。

【0029】

(実施の形態1)

本実施の形態では、半導体装置の一例について説明する。

【0030】

図1(A)に、半導体装置のブロック図の一例を示す。

【0031】

図1(A)の半導体装置は、論理回路部101と、記憶回路103と、を有する。論理回路部101は、複数の論理回路105を有する。そして、半導体装置では、記憶回路103に記憶されたデータ(信号ともいう)に応じて、複数の論理回路105のうちの一つ又は複数が選択され、論理回路部101内の回路構成が決定される。

【0032】

論理回路部101の一例として、ALUなどが挙げられる。複数の論理回路105としては、加算器、減算器、乗算器、AND回路、OR回路、NOT回路、XOR回路、又はシフト回路等の演算回路、マルチプレクサ等の選択回路などが挙げられる。また、論理回路105は、一つのトランジスタなど一つの素子で構成されていてもよい。論理回路105は、スイッチとしての機能を有する素子(トランジスタ等)を、一つ又は複数個を有する回路とも言える。

【0033】

そして、論理回路部101は、記憶回路103に記憶されたデータに応じて、例えば加算器として用いる、又は、AND回路として用いるなど、適宜回路構成を変更することができる。

【0034】

更に、記憶回路103においてデータを保持することで、論理回路部101の回路構成を維持することができる。なお、論理回路部101の内部に記憶回路103を有していてもよい。以下に、半導体装置の具体的な回路構成及び駆動方法を説明する。

【0035】

(記憶回路103及び論理回路105の回路構成)

図1(B)に、記憶回路103及び論理回路105について、具体的な回路構成の一例を示す。

【0036】

記憶回路103は、トランジスタ107と、容量素子109と、を有する。なお、記憶回路103は複数設けられていてもよく、その個数は、論理回路部101の構成に応じて決定すればよい。複数設けられている場合、その集合を単に記憶回路と呼ぶ場合や、記憶回路部と呼ぶ場合もある。また、抵抗や、ダイオード等の素子を有していてもよい。

【0037】

トランジスタ107には、酸化物半導体が用いられている。特に、トランジスタ107のチャネル形成領域に酸化物半導体が用いられている。なお、図1(B)では、トランジスタ107に酸化物半導体が用いられていることを示すため、「OS」の符号を付している。

【0038】

トランジスタ107のゲートは端子Wと電気的に接続され、トランジスタ107のソース又はドレインの一方は端子Dと電気的に接続され、トランジスタ107のソース又はドレインの他方は端子F及び容量素子109の一対の電極のうちの一方と電気的に接続される。容量素子109の一対の電極のうちの他方は、端子Cと電気的に接続される。ここで、各端子は、配線や電極と電気的に接続される構成とすることができる。なお、端子Cには、一定の電位、例えば、低電源電位が入力される構成とすることができる。

【0039】

一方、論理回路105は、トランジスタ111を有する。ここでは、簡単のためトランジスタが一つの場合について説明するが、他の構成を用いてもよい。

【0040】

トランジスタ111のゲートは記憶回路103の端子Fと電気的に接続される。すなわち、当該ゲートはトランジスタ107のソース又はドレインの他方及び容量素子109の一対の電極のうちの一方と電気的に接続される。トランジスタ111のソース又はドレインの一方は、端子Iと電気的に接続され、トランジスタ111のソース又はドレインの他方は端子Oと電気的に接続される。

【0041】

トランジスタ111には、元素周期表における第14族の半導体(シリコンなど)を含有する半導体、有機半導体、化合物半導体、又は酸化物半導体等の様々な半導体を用いることができる。また、非晶質半導体、微結晶半導体、多結晶半導体、又は単結晶半導体等を用いることができる。特に、トランジスタ111のチャネル形成領域にこれらの半導体が用いられている。

【0042】

なお、単結晶半導体を用いたトランジスタとしては、単結晶半導体基板を用いたバルクトランジスタ、SOI基板を用いた薄膜トランジスタ等が挙げられる。SOI基板のベース基板としては、ガラス基板や半導体基板等が挙げられる。非晶質半導体、微結晶半導体、又は多結晶半導体を用いたトランジスタとしては、ガラス基板又は半導体基板などの上に設けられた薄膜トランジスタ等が挙げられる。

【0043】

(記憶回路103及び論理回路105の駆動方法)

図1(B)に示した記憶回路103及び論理回路105の駆動方法について説明する。

【0044】

記憶回路103へのデータの記憶(格納ともいう)は以下の方法で行われる。まず、トランジスタ107が、ゲートに入力される制御信号Write(端子Wに入力される制御信号)によってオン状態に選択される。そして、オン状態のトランジスタ107を介して、データDataに対応する信号電位(端子Dに入力される信号電位)が容量素子109の一対の電極のうちの一方に入力される。すなわち、記憶回路103は、トランジスタ107を介して容量素子109にデータDataを入力する機能を有する。

【0045】

その後、トランジスタ107が、ゲートに入力される制御信号Write(端子Wに入力される制御信号)によってオフ状態に選択されることで、容量素子109の一対の電極のうちの一方に当該信号電位が保持される。その際、端子Fにも当該信号電位が保持される。このようにして、記憶回路103にデータDataを記憶することができる。

【0046】

ここで、トランジスタ107には、酸化物半導体が用いられており、例えばシリコン系のトランジスタに比べてオフ電流(リーク電流ともいう)が著しく小さい。そのため、記憶回路103は、トランジスタ107がオフ状態である場合に、容量素子109の一対の電極のうちの一方及び端子Fに、上記信号電位を長期間にわたって保持することができる。そのため、記憶回路103は、例えば半導体装置への電源電圧の供給を停止した後も、データDataを長時間保持することができる。

【0047】

また、酸化物半導体を用いたトランジスタ107を有する記憶回路103は、例えばシリコン系のトランジスタを用いたフラッシュメモリ等に比べて駆動電圧が低い。そのため、当該フラッシュメモリ等に比べて高速動作及び消費電力の低減が可能である。

【0048】

一方、図1(B)の論理回路105では、上記信号電位がトランジスタ111のゲートに入力され、トランジスタ111のオン/オフが制御される。すなわち、端子Iと端子Oとの導通が制御される。そして、記憶回路103がデータDataを長時間保持できるため、半導体装置への電源電圧の供給を停止した後も論理回路105の回路構成を維持することができる。図1(B)において論理回路105の回路構成を維持するとは、トランジスタ111のオン状態又はオフ状態(端子Iと端子Oとの導通又は非導通)を維持することを意味する。

【0049】

ここで、トランジスタ111は、高速に動作することが望ましいため、移動度が高い結晶性半導体を用いるとよい。特に、単結晶半導体を用いることが好ましく、また、結晶性の向上が容易であるシリコンを含有する半導体を用いることが好ましい。すなわち、トランジスタ111は、単結晶シリコンを用いることが好ましい。

【0050】

また、トランジスタ107とトランジスタ111とを積層することで、回路面積を縮小することができる。例えば、図7(C)のようにトランジスタ111上にトランジスタ107を設ければよい。その場合、単結晶シリコンを用いたトランジスタ111上に、酸化物半導体を用いたトランジスタ107を設ける構造が好ましい。図7(D)に、積層させた場合の断面構造の具体的な一例を示す。

【0051】

図7(D)の断面構造は、図1(B)の回路構成に対応するものであり、単結晶シリコンを用いたトランジスタ111上に、酸化物半導体を用いたトランジスタ107と、容量素子109とが、設けられている構造を示している。

【0052】

トランジスタ111は、単結晶シリコン層131と、ゲート絶縁層133と、ゲート電極135と、を有している。トランジスタ107は、酸化物半導体層137と、ゲート絶縁層139と、ゲート電極141と、を有している。容量素子109は、一対の電極のうち一方の電極143及び他方の電極145と、誘電体層となる絶縁層147と、を有している。そして、トランジスタ111のゲート電極135は、容量素子109の一方の電極143、及び、トランジスタ107のソース電極又はドレイン電極の一方の電極149に電気的に接続されている。

【0053】

図7(D)の例において、容量素子109の一方の電極143は、トランジスタ107のソース電極又はドレイン電極の一方の電極149が延伸されたものである。また、容量素子109の誘電体層となる絶縁層147は、トランジスタ107のゲート絶縁層139が延伸されたものである。また、容量素子109の他方の電極145は、トランジスタ107のゲート電極141が設けられている層と同じ層上に設けられている。このような構造の一部又は全部を用いることで、各素子が有する膜や電極等を、同じ材料を用いて同じ工程で形成することができ、コスト及び工程数を削減することができる。

【0054】

図7(D)のような構造を有する半導体装置は、高速動作、データの保持、回路面積の縮小、並びにコスト及び工程数の削減の全てを実現することができる。なお、半導体装置の断面構造は、図7(C)、(D)に限定されず、トランジスタ107上にトランジスタ111を設けてもよい。また、図7(D)では、トランジスタ107の一部がトランジスタ111と重なっているが、トランジスタ107の全部がトランジスタ111と重なっていていてもよい。また、トランジスタ111とトランジスタ107とを積層しなくてもよく、トランジスタ107と容量素子109とを積層させる構造や、トランジスタ111と容量素子109とを積層させる構造などとしてもよい。

【0055】

以上のように、記憶回路103に記憶されたデータDataに応じて論理回路105を制御することができる。

【0056】

なお、図1(B)では、論理回路105としてトランジスタが一つの場合を示したが、他の回路構成としてもよい。例えば、図1(C)のように、論理回路105は、インバータなどのCMOS回路を有していてもよい。図1(C)の動作も図1(B)の動作と同様に、記憶回路103に記憶されたデータDataに応じて、トランジスタ121及びトランジスタ123のオン/オフを制御する。すなわち、端子I1と端子Oとの導通、又は、端子I2と端子Oとの導通を選択する。なお、端子I1には高電源電位が入力され、端子I2には低電源電位が入力される構成とすることができる。

【0057】

(記憶回路103及び論理回路部101の回路構成及び駆動方法)

図2(A)に、記憶回路103及び論理回路部101の回路構成の一例を示す。

【0058】

論理回路部101は、図1(A)の論理回路105に相当するものとして、加算器201と、AND回路203と、選択回路205と、を有する。すなわち、論理回路部101は、加算器201及びAND回路203等の演算回路と、選択回路205と、を有する。上述した他の論理回路を用いてもよい。また、抵抗や、ダイオード等の素子を有していてもよい。

【0059】

加算器201及びAND回路203としては、公知の回路を用いればよい。加算器201及びAND回路203は、端子A及び端子Bからの入力に基づき演算を行い、演算結果を選択回路205に入力する機能を有する。

【0060】

選択回路205の一例として、マルチプレクサ等が挙げられる。選択回路205は、記憶回路103の端子Fに電気的に接続され、選択信号Sとして記憶回路103のデータDataが入力される。そして、選択回路205は、当該データDataに応じて、加算器201又はAND回路203からの入力のうちの一方を選択して、端子Oに出力する。すなわち、選択回路205は、当該データDataに応じて加算器201やAND回路203等の演算回路の演算結果のうちの一つを選択する機能を有する。また、論理回路部101の構成によっては、演算回路を複数選択するようにすることもできる。

【0061】

図2(B)に、記憶回路103及び選択回路205の具体的な回路構成を示す。

【0062】

選択回路205は、2つの入力(AND回路からの入力及び加算器からの入力)を有するマルチプレクサの一例であり、トランジスタ207と、トランジスタ209と、インバータ211と、を有する。ここでは、トランジスタ207とトランジスタ209とは、極性が同じものを用いている。なお、選択回路205の回路構成は、トランジスタによって演算回路と端子Oとの電気的な接続を制御できればよく、図2(B)に限定されない。

【0063】

トランジスタ207のゲートはインバータ211を介して端子Fに電気的に接続され、トランジスタ207のソース又はドレインの一方はAND回路203に電気的に接続され、トランジスタ209のゲートは端子Fに電気的に接続され、トランジスタ209のソース又はドレインの一方は加算器201に電気的に接続され、トランジスタ207のソース又はドレインの他方及びトランジスタ209のソース又はドレインの他方は端子Oに電気的に接続される。なお、マルチプレクサの入力は、論理回路部101の構成に応じて、任意のm(mは正の整数)個に適宜変更すればよい。また、選択信号Sの数は、入力の数に応じて決定すればよい。また、記憶回路103の数は、選択信号Sの数に応じて決定すればよい。例えば、4つの入力(m=4:I0、I1、I2、I3)を有する場合、端子Oからの出力が4通りなので、2つの選択信号S0、S1(「S0S1」=「00」、「01」、「10」、「11」の4通り)を用い、2つの選択信号S0、S1のそれぞれに対応する2つの記憶回路103を設ければよい(図27(A)、(B)参照)。

【0064】

図2(B)の回路の駆動は、図1(B)、(C)の回路と同様に行えばよい。まず、記憶回路103は、トランジスタ107を介して選択信号SとなるデータDataを選択回路205に入力する。次に、選択回路205は、当該データDataに応じてトランジスタ209のオン/オフを制御し、当該データDataの反転データに応じてトランジスタ207のオン/オフを制御する。そして、トランジスタ207がオン状態でトランジスタ209がオフ状態の場合、AND回路203からの入力が選択され、端子Oに出力される。また、トランジスタ209がオン状態でトランジスタ207がオフ状態の場合、加算器201からの入力が選択され、端子Oに出力される。

【0065】

このように、記憶回路103のデータDataに応じて、選択回路205が制御され、加算器201又はAND回路203の演算結果のうちの一方が選択される。なお、図2では、簡単のため、論理回路部101の論理回路105として、加算器201、AND回路203、及び選択回路205のみ示したが、他の構成としてもよい。図3に、より実用的な構成を示す。

【0066】

図3は、論理回路部101として一般的なALUを用いた場合のブロック図である。論理回路部101は、加算器や減算器等を組み合わせた算術演算部301と、AND回路やOR回路等を組み合わせた論理演算部303と、シフト回路を有するシフト演算部305と、それらを選択して出力するマルチプレクサ等の選択回路205と、を有する。また、各演算部301、303、305は、マルチプレクサ等の選択回路307、309、311を有しており、各演算部内の論理回路の回路構成の組み合わせを変更することができる。

【0067】

各演算部内の選択回路307、309、311は、選択回路205と同様に、選択信号Sとなる記憶回路103のデータDataに応じて制御される。図3の場合、記憶回路103は、図1(B)のようなトランジスタ107と容量素子109との組を複数組設けた記憶回路部とし、端子F1〜F4からデータDataが出力されるようにすればよい。なお、当該組の数は、選択回路205、307、309、311の入力の数によって決定すればよい。また、端子F1〜端子F4から同じデータDataが出力される場合、図1(B)のような記憶回路103を選択回路205、307、309、311で共有してもよく、半導体装置の小型化が可能である。

【0068】

そして、記憶回路103がデータDataを長時間保持することができるため、半導体装置への電源電圧の供給を停止した後も、論理回路部101の回路構成を維持することができる。また、図3のように回路構成が複雑になるのに伴い、記憶回路103の高速動作や消費電力を低減する効果が一層顕著になる。

【0069】

なお、図2や図3のような回路を複数設けることで、端子A及び端子Bから入力される信号のビット数を増やすことができる。すなわち、任意のn(nは正の整数)ビットの論理回路部101を構成することができる。

【0070】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0071】

(実施の形態2)

本実施の形態では、実施の形態1と異なる半導体装置の一例を説明する。

【0072】

図4(A)、(B)に、図1(B)の変形例を示す。

【0073】

まず、図4(A)の例について説明する。記憶回路103は、図1(B)等と同様である。

【0074】

図4(A)の論理回路105は、トランジスタ111と、トランジスタ401と、インバータ403と、を有する。トランジスタ111とトランジスタ401とは、端子Iと端子Oとの間に並列に電気的に接続される。すなわち、トランジスタ111のソース又はドレインの一方及びトランジスタ401のソース又はドレインの一方が端子Iに電気的に接続され、トランジスタ111のソース又はドレインの他方及びトランジスタ401のソース又はドレインの他方が端子Oに電気的に接続される。

【0075】

トランジスタ111と、トランジスタ401とは、一方がNチャネル型で他方がPチャネル型であり、極性が異なるものを用いる。そして、トランジスタ111のゲートには記憶回路103のデータDataが入力され、トランジスタ401のゲートには当該データDataの反転データが入力される。図4(A)のように極性の異なるトランジスタ111、401を用いることで、トランジスタ111、401の閾値電圧分の電圧変動を抑制することができる。

【0076】

次に、図4(B)の例について説明する。

【0077】

図4(B)の記憶回路103は、トランジスタ107と、容量素子109と、トランジスタ405と、容量素子407と、インバータ409と、を有する。トランジスタ107及び容量素子109については、図1(B)等と同様である。そして、トランジスタ405のゲートが端子Wに電気的に接続され、トランジスタ405のソース又はドレインの一方がインバータ409を介して端子Dに電気的に接続され、トランジスタ405のソース又はドレインの他方が容量素子407の一対の電極のうちの一方及び端子F2に電気的に接続される。

【0078】

図4(B)の論理回路105は、図4(A)と同様に、極性の異なるトランジスタ111とトランジスタ401とが端子Iと端子Oとの間に並列に電気的に接続されている。そして、トランジスタ111のゲートには記憶回路103のデータDataが入力され、トランジスタ401のゲートには当該データDataの反転データが入力される。図4(A)と同様に極性の異なるトランジスタ111、401を用いることで、トランジスタ111、401の閾値電圧分の電圧変動を抑制することができる。

【0079】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0080】

(実施の形態3)

本実施の形態では、上記実施の形態とは異なる半導体装置の一例を説明する。

【0081】

図5(A)の半導体装置は、複数の論理回路部101と、接続部501と、を有する。論理回路部101については、図1〜図3と同様であり、ALU等を用いることができる。

【0082】

接続部501は、複数の論理回路部101間を電気的に接続する配線503の導通を制御する機能を有する。図5(B)にその詳細を示す。

【0083】

図5(B)の接続部501の回路構成及び駆動方法は、図1(B)と同様であり、記憶回路103のデータDataに応じて、トランジスタ111のオン/オフが制御される。すなわち、端子Iと端子Oとの導通が制御される。端子Iと端子Oとは、それぞれ異なる論理回路部101と電気的に接続されており、端子Iと端子Oとの導通の制御により、論理回路部101間の電気的な接続が制御される。なお、論理回路105は、トランジスタ111を一つ有する回路に限定されず、スイッチとしての機能を有する素子(トランジスタ等)を一つ又は複数個を有する回路でもよい。

【0084】

このように、接続部501のトランジスタ111は、当該データDataに応じて、複数の論理回路部101のうちの一つと他の一つとの電気的な接続を制御する機能を有する。また、端子Iと端子Oとは、それぞれ一つの論理回路部101の端子Aと端子O(図3等参照)とに電気的に接続されるようにしてもよい。すなわち、一つの論理回路部101の出力が入力に帰還する構成としてもよい。なお、接続部501の外部に記憶回路103を有していてもよい。

【0085】

図5(C)は、複数の論理回路部101間の電気的な接続の一例を示す図である。図5(C)の半導体装置は、メモリ505と、選択回路507と、を有する。メモリ505には、制御信号Write及びデータData等の情報a〜情報nが格納されている。選択回路507は、マルチプレクサ等であり、当該情報を選択して接続部501の記憶回路103に出力する。

【0086】

図5(C)では、情報aが選択され、論理回路部101間の配線503が矢印のように接続される様子を示している。また、情報b〜情報nが選択された場合に、接続関係が変更されるようにすればよい。なお、図5(C)では、接続された配線503のみ示している。

【0087】

そして、図5(C)の半導体装置は、接続部501が有する記憶回路103においてデータDataを長時間保持することができるため、半導体装置への電源電圧の供給を停止した後も、複数の論理回路部101間の接続関係を維持することができる。また、接続部501が有する酸化物半導体を用いたトランジスタ107は駆動電圧が低い。そのため、接続関係を変更する際に、例えばフラッシュメモリ等に比べて高速動作及び消費電力の低減が可能である。

【0088】

なお、メモリ505に記憶回路103を用いてもよい。その場合、メモリ505も高速かつ低消費電力で動作させることができる。また、接続部501の回路構成として、図4(A)、(B)を用いてもよい。

【0089】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0090】

(実施の形態4)

本実施の形態は、実施の形態1及び実施の形態3を組み合わせた半導体装置の一例を説明する。

【0091】

図6(A)の半導体装置は、複数の論理回路部101(「+」や「AND」などを付した部分)と、接続部501と、記憶回路103と、メモリ505と、選択回路507と、を有する。半導体装置の外部にメモリ505及び選択回路507を有していてもよい。

【0092】

記憶回路103は、実施の形態1等で説明したように、複数の論理回路部101の回路構成を維持する機能を有する。

【0093】

接続部501は、実施の形態3等で説明したように、複数の論理回路部101間の接続関係を維持する機能を有する。

【0094】

そして、メモリ505に格納されている情報a〜情報nのそれぞれは、当該回路構成及び接続関係の両方の情報を有している。その情報を記憶回路103及び接続部501に保持させることで、半導体装置は、電源電圧の供給を停止した後も、当該回路構成及び接続関係の両方を維持することができる。また、記憶回路103が有する酸化物半導体を用いたトランジスタは駆動電圧が低い。そのため、当該回路構成や接続関係の変更を高速かつ低消費電力で行うことができる。

【0095】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0096】

(実施の形態5)

本実施の形態では、半導体装置の消費電力を低減する構成の一例を示す。

【0097】

図6(B)に、半導体装置において使用しない回路への電源電圧の供給を停止する構成を示す。なお、論理回路部101(論理回路部101a及び論理回路部101b)、接続部501、記憶回路103等の構成は他の実施の形態と同様である。

【0098】

使用する論理回路部101a、記憶回路103のうち論理回路部101aにデータDataを供給する部分、及び、接続部501のうち論理回路部101aの接続関係を制御する記憶回路には、電源電圧が供給される。

【0099】

一方、使用しない論理回路部101b、記憶回路103のうち論理回路部101bにデータDataを供給する部分、及び、接続部501のうち論理回路部101bの接続関係を制御する記憶回路には、電源電圧の供給を停止する。また、それらのいずれかへの電源電圧の供給を停止するようにしてもよい。すなわち、使用しない論理回路部101bのみ電源電圧の供給を停止するようにしてもよい。

【0100】

電源電圧の供給を停止する一例として、図1(C)の論理回路105として示したインバータでは、端子I1及び端子I2と電源線との電気的な接続をスイッチ等で遮断することにより、高電源電位の供給及び低電源電位の供給を停止することができる。図2(A)の加算器201、AND回路203、及び選択回路205等も同様に、スイッチ等を用いて高電源電位の供給や低電源電位の供給を停止することができる。

【0101】

このように、使用しない回路への電源電圧の供給を停止することで、半導体装置の消費電力を低減することができる。

【0102】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0103】

(実施の形態6)

本実施の形態では、上記実施の形態に示す記憶回路のトランジスタに適用可能な酸化物半導体層を含む電界効果トランジスタの例について説明する。

【0104】

本実施の形態におけるトランジスタの一例について、図7(A)、(B)を用いて説明する。

【0105】

図7(A)に示すトランジスタは、導電層601_aと、絶縁層602_aと、半導体層603_aと、導電層605a_aと、導電層605b_aと、を含む。

【0106】

半導体層603_aは、領域604a_a及び領域604b_aを含む。領域604a_a及び領域604b_aは、互いに離間し、それぞれドーパントが添加された領域である。なお、領域604a_a及び領域604b_aの間の領域がチャネル形成領域になる。半導体層603_aは、被素子形成層600_aの上に設けられる。なお、必ずしも領域604a_a及び領域604b_aを設けなくてもよい。

【0107】

導電層605a_a及び導電層605b_aは、半導体層603_aの上に設けられ、半導体層603_aに電気的に接続される。また、導電層605a_a及び導電層605b_aの側面は、テーパ状である。

【0108】

また、導電層605a_aは、領域604a_aの一部に重畳するが、必ずしもこれに限定されない。導電層605a_aを領域604a_aの一部に重畳させることにより、導電層605a_a及び領域604a_aの間の抵抗値を小さくすることができる。また、導電層605a_aに重畳する半導体層603_aの領域の全てが領域604a_aである構造にしてもよい。

【0109】

また、導電層605b_aは、領域604b_aの一部に重畳するが、必ずしもこれに限定されない。導電層605b_aを領域604b_aの一部に重畳させることにより、導電層605b_a及び領域604b_aの間の抵抗を小さくすることができる。また、導電層605b_aに重畳する半導体層603_aの領域の全てが領域604b_aである構造にしてもよい。

【0110】

絶縁層602_aは、半導体層603_a、導電層605a_a、及び導電層605b_aの上に設けられる。

【0111】

導電層601_aは、絶縁層602_aの一部の上に設けられ、絶縁層602_aを介して半導体層603_aに重畳する。絶縁層602_aを介して導電層601_aと重畳する半導体層603_aの領域がチャネル形成領域になる。

【0112】

また、図7(B)に示すトランジスタは、導電層601_bと、絶縁層602_bと、半導体層603_bと、導電層605a_bと、導電層605b_bと、絶縁層606aと、絶縁層606bと、絶縁層607と、を含む。

【0113】

半導体層603_bは、領域604a_b及び領域604b_bを含む。領域604a_b及び領域604b_bは、互いに離間し、それぞれドーパントが添加された領域である。半導体層603_bは、例えば導電層605a_b、導電層605b_b、及び被素子形成層600_bの上に設けられ、導電層605a_b及び導電層605b_bに電気的に接続される。なお、必ずしも領域604a_b及び領域604b_bを設けなくてもよい。

【0114】

絶縁層602_bは、半導体層603_bの一部の上に設けられる。

【0115】

導電層601_bは、絶縁層602_bの一部の上に設けられ、絶縁層602_bを介して半導体層603_bに重畳する。なお、絶縁層602_bを介して導電層601_bと重畳する半導体層603_bの領域がトランジスタのチャネル形成領域になる。なお、導電層601_bの上に絶縁層が設けられていてもよい。

【0116】

絶縁層606aは、絶縁層602_bの上に設けられ、導電層601_bにおける一対の側面の一方に接する。

【0117】

絶縁層606bは、絶縁層602_bの上に設けられ、導電層601_bにおける一対の側面の他方に接する。

【0118】

なお、絶縁層602_bを介して絶縁層606a及び絶縁層606bに重畳する領域604a_b及び領域604b_bの部分のドーパントの濃度は、絶縁層606a及び絶縁層606bに重畳しない領域604a_b及び領域604b_bの部分のドーパントの濃度より低くてもよい。

【0119】

導電層605a_b及び導電層605b_bは、半導体層603_bの上に設けられる。

【0120】

導電層605a_bは、領域604a_bに電気的に接続される。また、導電層605a_bは、絶縁層606aに接する。

【0121】

導電層605b_bは、領域604b_bに電気的に接続される。また、導電層605b_bは、絶縁層606bに接する。

【0122】

絶縁層607は、導電層601_b、導電層605a_b、導電層605b_b、絶縁層606a、及び絶縁層606bの上に設けられる。

【0123】

さらに、図7(A)及び図7(B)に示す各構成要素について説明する。

【0124】

被素子形成層600_a及び被素子形成層600_bとしては、例えば絶縁層、又は絶縁表面を有する基板などを用いることができる。また、予め素子が形成された層を被素子形成層600_a及び被素子形成層600_bとして用いることもできる。

【0125】

導電層601_a及び導電層601_bのそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタのゲートとしての機能を有する層をゲート電極又はゲート配線ともいう。

【0126】

導電層601_a及び導電層601_bとしては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、導電層601_a及び導電層601_bに適用可能な材料の積層により、導電層601_a及び導電層601_bを構成することもできる。

【0127】

絶縁層602_a及び絶縁層602_bのそれぞれは、トランジスタのゲート絶縁層としての機能を有する。

【0128】

絶縁層602_a及び絶縁層602_bとしては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ハフニウム層、又は酸化ランタン層を用いることができる。また、絶縁層602_a及び絶縁層602_bに適用可能な材料の積層により絶縁層602_a及び絶縁層602_bを構成することもできる。

【0129】

また、絶縁層602_a及び絶縁層602_bとしては、例えば元素周期表における第13族元素及び酸素元素を含む材料の絶縁層を用いることもできる。例えば、半導体層603_a及び半導体層603_bが第13族元素を含む場合に、半導体層603_a及び半導体層603_bに接する絶縁層として第13族元素を含む絶縁層を用いることにより、該絶縁層と酸化物半導体層との界面の状態を良好にすることができる。

【0130】

第13族元素及び酸素元素を含む材料としては、例えば酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどが挙げられる。なお、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多い物質のことをいい、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上の物質のことをいう。例えば、Al2Ox(x=3+α、αは0より大きく1より小さい値)、Ga2Ox(x=3+α、αは0より大きく1より小さい値)、又はGaxAl2−xO3+α(xは0より大きく2より小さい値、αは0より大きく1より小さい値)で表記される材料を用いることもできる。

【0131】

また、絶縁層602_a及び絶縁層602_bに適用可能な材料の層の積層により絶縁層602_a及び絶縁層602_bを構成することもできる。例えば、複数のGa2Oxで表記される酸化ガリウムを含む層の積層により絶縁層602_a及び絶縁層602_bを構成してもよい。また、Ga2Oxで表記される酸化ガリウムを含む絶縁層及びAl2Oxで表記される酸化アルミニウムを含む絶縁層の積層により絶縁層602_a及び絶縁層602_bを構成してもよい。

【0132】

半導体層603_a及び半導体層603_bのそれぞれは、トランジスタのチャネルが形成される層としての機能を有する。半導体層603_a及び半導体層603_bに適用可能な酸化物半導体としては、例えばIn系酸化物(例えば酸化インジウムなど)、Sn系酸化物(例えば酸化スズなど)、又はZn系酸化物(例えば酸化亜鉛など)などを用いることができる。

【0133】

また、上記金属酸化物としては、例えば、四元系金属酸化物、三元系金属酸化物、二元系金属酸化物などの金属酸化物を用いることもできる。なお、上記酸化物半導体として適用可能な金属酸化物は、特性のばらつきを減らすためのスタビライザーとしてガリウム、スズ、ハフニウム、及びアルミニウムの一つまたは複数を含んでいてもよい。また、上記酸化物半導体として適用可能な金属酸化物は、上記スタビライザーとして、ランタノイドである、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムの一つ又は複数を含んでいてもよい。また、上記酸化物半導体として適用可能な金属酸化物は、酸化シリコンを含んでいてもよい。

【0134】

例えば、四元系金属酸化物としては、例えばIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物などを用いることができる。

【0135】

また、三元系金属酸化物としては、例えばIn−Ga−Zn系酸化物(IGZOともいう)、In−Sn−Zn系酸化物、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、又はIn−Lu−Zn系酸化物などを用いることができる。

【0136】

また、二元系金属酸化物としては、例えばIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Sn系酸化物、又はIn−Ga系酸化物などを用いることができる。

【0137】

なお、例えばIn−Ga−Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0138】

また、酸化物半導体としては、InLO3(ZnO)m(mは0より大きい数)で表記される材料を用いることもできる。InLO3(ZnO)mのLは、Ga、Al、Mn、及びCoから選ばれた一つ又は複数の金属元素を示す。

【0139】

例えば、酸化物半導体としては、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)又はIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。また、酸化物半導体としては、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)又はIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いることができる。

【0140】

しかし、これらに限られず、必要とする半導体特性(移動度、閾値電圧、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0141】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0142】

また、半導体層603_a及び半導体層603_bとしては、c軸に配向し、かつab面、表面又は界面の方向から見て三角形状又は六角形状の原子配列を有し、c軸において金属原子が層状又は金属原子と酸素原子とが層状に配列しており、ab面においてa軸又はb軸の向きが異なる(c軸を中心に回転した)結晶を含む酸化物半導体(CAAC−OS:C Axis Aligned Crystalline Oxide Semiconductorともいう)の層を用いることができる。

【0143】

CAACとは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含むものをいう。

【0144】