半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一形態は、酸化物半導体を用いた電界効果型トランジスタを有する半導体装置に

関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置

全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタを構成する技

術が注目されている。薄膜トランジスタに適用可能な半導体薄膜としては、シリコン系半

導体材料が公知であるが、その他の材料として酸化物半導体が注目されている。

【0004】

酸化物半導体の材料としては、酸化亜鉛または酸化亜鉛を含む材料が知られている。そし

て、電子キャリア濃度が1018/cm3未満である非晶質酸化物(酸化物半導体)で形

成された薄膜トランジスタが開示されている(特許文献1乃至3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−165527号公報

【特許文献2】特開2006−165528号公報

【特許文献3】特開2006−165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

一方で、表示装置に近い構成でありながらも、優れた電気特性が要求される固体撮像素子

などでは、SOI基板やバルクの単結晶シリコン基板を用いた電界効果型トランジスタが

一般的に用いられている。

【0007】

しかしながら、単結晶シリコンを用いた電界効果型トランジスタであっても理想的な電気

特性を有しているとは言えず、例えばオフ電流(リーク電流などとも呼ぶ)は、実質的に

ゼロと言えるほど小さいものではない。また、シリコンは温度特性の変化が比較的大きい

材料でもあり、特にオフ電流は変化しやすい。従って、固体撮像素子など電荷保持型の半

導体装置を構成する場合には、周囲の環境に左右されず、十分な電位保持期間の確保が可

能であり、よりオフ電流が低減されたデバイスの開発が望まれている。

【0008】

そこで、開示する本発明の一態様は、安定した電気特性(例えば、オフ電流が極めて低減

されている)を有する薄膜トランジスタを含む固体撮像素子を提供することを目的とする

。

【課題を解決するための手段】

【0009】

本発明の一態様は、シリコン半導体を用いて形成された光電変換素子及び増幅トランジス

タを少なくとも有し、リセットトランジスタ及び転送トランジスタが酸化物半導体で形成

された画素を有する固体撮像素子に関する。

【0010】

また、本発明の一態様における酸化物半導体は、電子供与体(ドナー)となる不純物を除

去することで、真性または実質的に真性な半導体であって、シリコン半導体よりもエネル

ギーギャップが大きい。

【0011】

すなわち、本発明の一態様は、酸化物半導体に含まれる水素の濃度が、二次イオン質量分

析法(SIMS:Secondary Ion Mass Spectroscopy)

における最低値で5×1019/cm3以下、好ましくは5×1018/cm3以下、よ

り好ましくは5×1017/cm3以下、または1×1016/cm3未満として、酸化

物半導体に含まれる水素若しくはOH基を除去し、キャリア濃度を1×1014/cm3

未満、好ましくは1×1012/cm3以下とした酸化物半導体膜でチャネル領域が形成

される薄膜トランジスタを有する固体撮像素子である。

【0012】

酸化物半導体のエネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ま

しくは3eV以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度

を1×1014/cm3以下、好ましくは1×1012/cm3以下となるようにする。

【0013】

この様に高純度化された酸化物半導体は、薄膜トランジスタのチャネル形成領域に用いる

ことで、電気特性がノーマリーオフを呈し、1Vから10Vのドレイン電圧において、そ

のオフ電流は、1×10−13A以下、または100aA/μm(μmは、薄膜トランジ

スタのチャネル幅)以下、好ましくは10aA/μm以下、更に好ましくは1aA/μm

以下となる。

【0014】

本明細書で開示する本発明の一態様は、シリコン半導体基板に埋設された光電変換素子部

と、光電変換素子部と転送トランジスタを介して電気的に接続される信号電荷蓄積部と、

信号電荷蓄積部と電気的に接続されるリセットトランジスタと、信号電荷蓄積部にゲート

電極が電気的に接続される増幅トランジスタと、を有し、転送トランジスタ及びリセット

トランジスタのチャネル形成領域は酸化物半導体で形成されており、増幅トランジスタの

チャネル形成領域はシリコン半導体で形成された画素部を有することを特徴とする半導体

装置である。

【0015】

また、上記増幅トランジスタも酸化物半導体を用いた薄膜トランジスタで形成しても良い

。更に上記画素部には、選択トランジスタが設けられていても良い。また、画素部と接続

される周辺回路部は、シリコン半導体を用いたバルクトランジスタで相補型トランジスタ

の構成とすることが好ましい。

【0016】

本明細書等において「電極」や「配線」という用語は、これらの構成要素を機能的に限定

するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、「

配線」は「電極」の一部として用いられることがある。更に、「電極」や「配線」という

用語は、複数の「電極」や「配線」が一体となって形成されている場合などをも含む。

【0017】

また、「SOI基板」には、シリコンウエハなどの半導体基板に限らず、ガラス基板や石

英基板、サファイア基板、金属基板などの非半導体基板も含まれる。つまり、絶縁体基板

上に半導体材料からなる層を有するものも、広く「SOI基板」に含まれる。さらに、本

明細書等において、「半導体基板」は、半導体材料のみからなる基板を指すに留まらず、

半導体材料を含む基板全般を指すものとする。つまり、本明細書等においては「SOI基

板」も「半導体基板」に含まれる。

【発明の効果】

【0018】

本発明の一形態によれば、オフ電流が極めて小さい酸化物半導体を用いた薄膜トランジス

タをリセットトランジスタ及び転送トランジスタの両方に用いることで信号電荷蓄積部の

電位が一定に保たれ、ダイナミックレンジを向上させることができる。また、周辺回路に

相補型トランジスタが作製可能なシリコン半導体を用いることで動作が高速で、低消費電

力の半導体装置を作製することができる。

【図面の簡単な説明】

【0019】

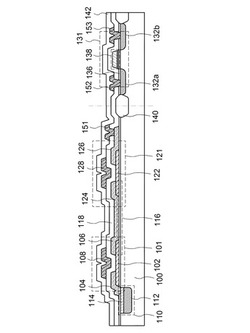

【図1】固体撮像素子の画素の構成について説明する断面図。

【図2】固体撮像素子の画素の構成について説明する断面図。

【図3】固体撮像素子の画素の構成について説明する断面図。

【図4】固体撮像素子の作製方法について説明する断面図。

【図5】固体撮像素子の作製方法について説明する断面図。

【図6】酸化物半導体を用いた薄膜トランジスタのVg−Id特性を示す図。

【図7】酸化物半導体を用いた薄膜トランジスタの写真。

【図8】酸化物半導体を用いた薄膜トランジスタのVg−Id特性(温度特性)示す図。

【図9】酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図。

【図10】図9に示すA−A’断面におけるエネルギーバンド図(模式図)。

【図11】図9に示すB−B’断面におけるエネルギーバンド図(模式図)であって、(A)ゲート(G1)に正の電位(+VG)が印加された状態を示し、(B)ゲート(G1)に負の電位(−VG)が印加された状態を示す図。

【図12】真空準位と金属の仕事関数(φM)、酸化物半導体の電子親和力(χ)の関係を示す図。

【図13】固体撮像素子の画素の構成について説明する図。

【図14】固体撮像素子の画素の動作について説明する図。

【図15】フォトダイオードの動作について説明する図。

【図16】固体撮像素子の画素の構成について説明する図。

【図17】固体撮像素子の画素の動作について説明する図。

【図18】固体撮像素子の画素の構成について説明する図。

【図19】固体撮像素子の画素の動作について説明する図。

【図20】固体撮像素子の画素の構成について説明する図。

【図21】固体撮像素子の画素の動作について説明する図。

【図22】固体撮像素子の画素の構成について説明する図。

【図23】固体撮像素子の画素の動作について説明する図。

【図24】固体撮像素子の構成について説明する図。

【図25】リセット端子駆動回路及び転送端子駆動回路の構成について説明する図。

【図26】垂直出力線駆動回路の構成について説明する図。

【図27】シフトレジスタとバッファ回路の一例を示す図。

【図28】固体撮像素子の画素の構成について説明する断面図。

【発明を実施するための形態】

【0020】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0021】

なお、本明細書で説明する各図において、各構成要素や領域の大きさ、及び層の厚さ等は

、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定され

ない。

【0022】

なお、本明細書にて用いる第1、第2、第3、等の用語は、構成要素の混同を避けるため

に付したものであり、順序などを限定するものではない。そのため、例えば、「第1の」

を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0023】

(実施の形態1)

本発明の一態様は、金属絶縁物半導体素子、所謂MIS(Metal Insulato

r Semiconductor)トランジスタを用いた半導体装置である。本明細書で

は、チャネル形成領域に薄膜の半導体を用いた素子を薄膜トランジスタと称し、チャネル

形成領域にバルクの半導体を用いた素子をバルクトランジスタと称する。ただし、SOI

(Silicon on Insulator)基板に形成されている半導体層は薄膜と

も言えるが、本明細書では該半導体層で形成したトランジスタはバルクトランジスタの一

種とする。

【0024】

本発明の一態様における薄膜トランジスタを含む固体撮像素子の画素を構成する例を以下

に説明する。本実施の形態では、一例として、固体撮像素子における画素が有する薄膜ト

ランジスタと、当該薄膜トランジスタに接続された光電変換素子及びシリコン半導体で形

成されたバルクトランジスタについて説明する。なお画素とは、固体撮像素子に設けられ

た各素子、例えば光電変換素子、トランジスタ、及び配線等からなり、電気的な信号の入

出力で画像を出力させるための素子で構成される素子群のことをいう。

【0025】

なお画素は、図28(A)の断面図に示すように基板表面側に形成したレンズ600、カ

ラーフィルタ602、及び層間絶縁膜606等を通して入射光を光電変換素子608に受

光させる構造とすることができる。ただし、点線枠で囲んだ領域に示すように、矢印で示

す光路の一部が配線層604の一部によって遮光されてしまうことがあり、図28(B)

に示すように基板裏面側にレンズ610及びカラーフィルタ612を形成して入射光を光

電変換素子618に効率良く受光させる構造としても良い。

【0026】

また、AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されてい

る場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、

対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとす

る。

【0027】

本発明の一態様である固体撮像素子の画素部分の一例を図1に断面図で示す。図1は転送

トランジスタ101及びリセットトランジスタ121に酸化物半導体を有する薄膜トラン

ジスタを用いた例で、増幅トランジスタ131は、単結晶シリコン基板100に形成され

たnチャネル型のバルクトランジスタで形成している。光電変換素子110はn型領域1

12と薄いp型領域114を含むフォトダイオードであり、転送トランジスタ101のソ

ース電極104に接続される。また、転送トランジスタ101のドレイン電極下方及びリ

セットトランジスタのソース電極下方には信号電荷蓄積部116(フローティングディフ

ュージョンとも呼ぶ)が形成される。転送トランジスタ101及びリセットトランジスタ

121は、酸化物半導体層がチャネル領域となるトップゲート構造をしており、転送トラ

ンジスタ101のドレイン電極106がリセットトランジスタのソース電極124と電気

的に接続される。増幅トランジスタ131は、n型領域132a、132bとゲート電極

138を含むnチャネル型のバルクトランジスタであり、図示はしていないが、増幅トラ

ンジスタのゲート電極138は、信号電荷蓄積部116と電気的に接続されている。

【0028】

なお、図1の構造において、バルクトランジスタのゲート絶縁層136は、薄膜トランジ

スタである転送トランジスタ101及びリセットトランジスタ121の下地絶縁層を兼ね

ており、信号電荷蓄積部116は、ゲート絶縁層136を誘電体として容量を形成してい

る。また、薄膜トランジスタのゲート絶縁層118は、バルクトランジスタの層間絶縁層

の一部として機能する。

【0029】

酸化物半導体をチャネル形成領域に用いた薄膜トランジスタは、トップゲート型を例とし

て示したが、逆スタガ構造などのボトムゲート型を用いても良い。また、光電変換素子1

10に光を照射する必要があるため、転送トランジスタ101のソース電極の一部を光電

変換素子110の受光部に接続させる例を挙げたが、ソース電極を透光性導電材料で形成

し、光電変換素子110との接続の状態を変えても良い。例えば、図2(A)に示すよう

に、透光性導電材料で形成したソース電極204を有するトランジスタ201を転送トラ

ンジスタとして用いれば、光電変換素子210の受光面の一部または全面に接続すること

ができる。また、図2(B)に示す様に光電変換素子310への光路を確保できるように

、抵抗の低い金属層をソース電極304及びドレイン電極306とし、透光性導電材料層

をバッファ層305、307として積層したトランジスタ301を転送トランジスタとし

て用いても良い。

【0030】

光電変換素子としては、p型単結晶シリコン基板(SOIの場合は、p型単結晶シリコン

層)にn型領域を形成し、その上部に薄いp型領域を形成した所謂埋め込み型フォトダイ

オードを形成する。フォトダイオードの表面にp型領域を形成することで表面で発生する

暗電流、すなわちノイズを低減することができる。

【0031】

また、上記では単結晶半導体基板を用いた例を示したが、SOI構造の基板であっても良

い。また、バルクトランジスタの構造はこれに限らず、ゲート電極端にサイドウォールを

設けたLDD(Lightly Doped Drain)構造やソースドレイン領域の

一部に低抵抗のシリサイド等を形成した構造であっても良い。

【0032】

また、上記画素部には増幅トランジスタ131と電気的に接続される選択トランジスタを

設けても良い。増幅トランジスタ及び選択トランジスタは共にシリコン半導体、酸化物半

導体のどちらを用いても形成することができる。ただし、増幅トランジスタは、より増幅

率の高いシリコン半導体層を用いたバルクトランジスタで形成することが好ましい。

【0033】

また、バルクトランジスタの上部に絶縁層を設け、その上に薄膜トランジスタを設けるこ

ともできる。例えば、薄膜トランジスタで形成する転送トランジスタ、またはリセットト

ランジスタのどちらか一方をバルクトランジスタで形成する増幅トランジスタの上部に設

ければ、一画素につき必要なトランジスタの面積が2/3程度となり、集積度の向上やフ

ォトダイオードの受光面積を増加させることができ、ノイズを低減させることもできる。

図3(A)はその一例である。薄膜トランジスタで形成された転送トランジスタ401と

バルクトランジスタで形成された増幅トランジスタ431が並設されており、その上部に

絶縁層441を介して薄膜トランジスタで形成されたリセットトランジスタ421が設け

られた構造をしている。また、図3(B)は、下層に光電変換素子510とバルクトラン

ジスタで形成された増幅トランジスタ531を形成し、絶縁膜541を介して上層に薄膜

トランジスタで形成された転送トランジスタ501とリセットトランジスタ521を設け

た例であり、光電変換素子及びバルクトランジスタと薄膜トランジスタの作製工程が分離

できるため、工程の制御が容易となる。ただし、信号電荷蓄積部516を形成するための

容量電極540を設けておくことが好ましい。

【0034】

以上の薄膜トランジスタとバルクトランジスタを組み合わせる構成により、信号電荷蓄積

部の電位の保持機能を高め、ダイナミックレンジの広い固体撮像素子の画素部を形成する

ことができる。ただし、この本発明の一態様を実現するには極めてオフ電流の低い薄膜ト

ランジスタを用いることが好ましい。次にその作製方法を説明する。

【0035】

本発明の一態様は、単結晶シリコン半導体を用いたバルクトランジスタと極めて電気特性

の良好な酸化物半導体を用いた薄膜トランジスタを組み合わせることにより固体撮像素子

の画素部を形成するものである。従って、酸化物半導体を用いた薄膜トランジスタの作製

方法を中心に詳細な説明を行う。

【0036】

一例として、図1の構造の作製方法を図4及び図5の断面図を用いて説明する。まず、P

型の単結晶シリコン基板100に絶縁膜140(フィールド酸化膜とも言う)で分離した

素子形成領域を形成する。素子分離領域の形成は、LOCOS法(Local Oxid

ation of Silicon)法)やSTI法(Shallow Trench

Isolation)等を用いることができる。

【0037】

ここで基板は単結晶シリコン基板に限らず、SOI(Silicon on Insul

ator)基板等を用いることもできる。

【0038】

なお、本実施の形態では、埋め込み型のフォトダイオード及びnチャネル型のバルクトラ

ンジスタを用いる構成であるため、p型単結晶シリコン基板を用いるが、pウェルを形成

すればn型単結晶シリコン基板を用いることもできる。

【0039】

次に、素子形成領域を覆うようにゲート絶縁層136を形成する。例えば、熱処理を行い

単結晶シリコン基板100に設けられた素子形成領域の表面を酸化させることにより酸化

シリコン膜を形成することができる。また、熱酸化法により酸化シリコン膜を形成した後

に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シ

リコン膜と酸窒化シリコン膜との積層構造で形成してもよい。

【0040】

他の方法としては、例えば、単結晶シリコン基板100に設けられた素子形成領域の表面

に高密度プラズマ処理により酸化処理または窒化処理を行うことにより、ゲート絶縁層1

36として酸化シリコン膜または窒化シリコン膜で形成することができる。また、高密度

プラズマ処理により素子形成領域の表面に酸化処理を行った後に、再度高密度プラズマ処

理を行うことによって窒化処理を行ってもよい。この場合、素子形成領域の表面に接して

酸化シリコン膜が形成され、当該酸化シリコン膜上に酸窒化シリコン膜が形成され、ゲー

ト絶縁層136は酸化シリコン膜と酸窒化シリコン膜が積層された層となる。

【0041】

次に、ゲート絶縁層136を覆うように導電層を形成する。ここでは、導電層138aと

導電層138bを順に積層して形成する。もちろん、導電層は、単層または2層以上の積

層構造で形成してもよい。

【0042】

導電層138a、138bとしては、タンタル(Ta)、タングステン(W)、チタン(

Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニ

オブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料や化合

物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成するこ

ともできる。他にも、リン等の不純物元素をドーピングした多結晶シリコンに代表される

半導体材料により形成することもできる。

【0043】

ここでは、導電層138aとして窒化タンタルを用いて形成し、その上に導電層138b

としてタングステンを用いて積層構造で設ける。また、他にも、導電層138aとして、

窒化タングステン、窒化モリブデンまたは窒化チタンから選ばれた単層または積層膜を用

い、導電層138bとして、タンタル、モリブデン、チタンから選ばれた単層または積層

膜を用いることができる。

【0044】

次に、積層して設けられた導電層138a、138bを選択的にエッチングして除去する

ことによって、ゲート絶縁層136の上方の一部に導電層138a、138bを残存させ

、ゲート電極138を形成する。

【0045】

次に、素子形成領域以外を覆うようにレジストマスクを選択的に形成し、当該レジストマ

スク及びゲート電極138をマスクとして不純物元素を導入することによってn型領域1

32a及び132bの不純物領域を形成する。ここでは、nチャネル型のバルクトランジ

スタを形成するため、不純物元素としては、n型を付与する不純物元素であるリン(P)

やヒ素(As)等を用いることができる。

【0046】

次に、光電変換素子であるフォトダイオードを作製するためにレジストマスクを選択的に

形成する。まず、n型を付与する不純物元素であるリン(P)やヒ素(As)をp型単結

晶シリコン基板に導入しpn接合を形成した後、p型を付与する不純物元素であるホウ素

(B)をn型領域の表層に導入することで埋め込み型のフォトダイオードを形成すること

ができる。

【0047】

この段階で、図4(A)の右側に示すバルクトランジスタと左側に示すフォトダイオード

の構造が完成する。

【0048】

次に酸化物半導体層をチャネル領域とする薄膜トランジスタの作製方法について説明する

。

【0049】

本実施の形態では、既に単結晶シリコン基板100に設けられているバルクトランジスタ

のゲート絶縁層136上に薄膜トランジスタを形成する。つまり、薄膜トランジスタの下

地膜とバルクトランジスタのゲート絶縁層とを兼ねることができる。ただし、次の方法を

用いて絶縁層を成膜し、下地膜を積層としても良い。

【0050】

酸化物半導体層と接する絶縁層は、酸化シリコン層、酸化窒化シリコン層、酸化アルミニ

ウム層、または酸化窒化アルミニウム層などの酸化物絶縁層を用いると好ましい。絶縁層

の形成方法としては、プラズマCVD法またはスパッタ法等を用いることができるが、絶

縁層中に水素が多量に含まれないようにするためには、スパッタ法で絶縁層を成膜するこ

とが好ましい。

【0051】

絶縁層として、スパッタ法により酸化シリコン層を形成する例を説明する。単結晶シリコ

ン基板100を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタガ

スを導入しシリコンターゲットを用いて、単結晶シリコン基板100に絶縁層として、酸

化シリコン層を成膜する。また単結晶シリコン基板100は室温でもよいし、加熱されて

いてもよい。

【0052】

例えば、石英(好ましくは合成石英)をターゲットとして用い、基板温度108℃、基板

とターゲットの間との距離(T−S間距離)を60mm、圧力0.4Pa、高周波電源1

.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:

1)雰囲気下でRFスパッタ法により酸化シリコン層を成膜する。膜厚は100nmとす

る。なお、石英に代えてシリコンを酸化シリコン層を成膜するためのターゲットとして用

いることができる。このとき、スパッタガスとしては、酸素または、酸素及びアルゴンの

混合ガスを用いて行う。

【0053】

この場合において、処理室内の残留水分を除去しつつ絶縁層を成膜することが好ましい。

絶縁層に水素、水酸基又は水分が含まれないようにするためである。

【0054】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。

例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが

好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであ

ってもよい。クライオポンプを用いて排気した処理室は、例えば、水素原子や、水(H2

O)など水素原子を含む化合物等が排気されるため、当該処理室で成膜し絶縁層に含まれ

る不純物の濃度を低減することができる。

【0055】

絶縁層を成膜する際に用いるスパッタガスは水素、水、水酸基または水素化物などの不純

物がppm程度の濃度またはppb程度の濃度まで除去された高純度ガスを用いることが

好ましい。

【0056】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法、DCスパッタ法、

さらにパルス的にバイアスを与えるパルスDCスパッタ法がある。RFスパッタ法は主に

絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に導電膜を成膜する場合に用いら

れる。

【0057】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ

装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種

類の材料を同時に放電させて成膜することもできる。

【0058】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置

や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ

を用いるスパッタ装置がある。

【0059】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分

とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に

基板にも電圧をかけるバイアススパッタ法もある。

【0060】

また、絶縁層は積層構造でもよく、例えば、基板側から窒化シリコン層、窒化酸化シリコ

ン層、窒化アルミニウム層、または窒化酸化アルミニウム層などの窒化物絶縁層と、上記

酸化物絶縁層との積層構造としてもよい。

【0061】

例えば、酸化シリコン層と基板との間に水素及び水分が除去された高純度窒素を含むスパ

ッタガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜する。この場合にお

いても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成

膜することが好ましい。

【0062】

窒化シリコン層を形成する場合も、成膜時に基板を加熱してもよい。

【0063】

絶縁層として窒化シリコン層と酸化シリコン層とを積層する場合、窒化シリコン層と酸化

シリコン層を同じ処理室において、共通のシリコンターゲットを用いて成膜することがで

きる。先に窒素を含むスパッタガスを導入して、処理室内に装着されたシリコンターゲッ

トを用いて窒化シリコン層を形成し、次にスパッタガスを酸素を含むスパッタガスに切り

替えて同じシリコンターゲットを用いて酸化シリコン層を成膜する。窒化シリコン層と酸

化シリコン層とを大気に曝露せずに連続して形成することができるため、窒化シリコン層

表面に水素や水分などの不純物が吸着することを防止することができる。

【0064】

次いで、絶縁層上(本実施の形態ではゲート絶縁層136上)に、膜厚2nm以上200

nm以下の酸化物半導体膜をスパッタ法で形成する。

【0065】

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、

成膜の前処理として、スパッタ装置の予備加熱室で単結晶シリコン基板100を予備加熱

し、該基板に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、

予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は

省略することもできる。また、この予備加熱は、後に形成する薄膜トランジスタのゲート

絶縁層118の成膜前に行ってもよいし、後に形成するソース電極及びドレイン電極とな

る導電層の成膜前に行っても良い。

【0066】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズ

マを発生させる逆スパッタを行い、絶縁層の表面に付着しているゴミを除去することが好

ましい。逆スパッタとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加し、

イオン化したアルゴンを基板に衝突させて表面を改質する方法である。なお、アルゴンに

代えて窒素、ヘリウム、酸素などを用いてもよい。

【0067】

酸化物半導体膜はスパッタ法により成膜する。酸化物半導体膜としては、四元系金属酸化

物であるIn−Sn−Ga−Zn−O膜や、三元系金属酸化物であるIn−Ga−Zn−

O膜、In−Sn−Zn−O膜、In−Al−Zn−O膜、Sn−Ga−Zn−O膜、A

l−Ga−Zn−O膜、Sn−Al−Zn−O膜や、二元系金属酸化物であるIn−Zn

−O膜、Sn−Zn−O膜、Al−Zn−O膜、Zn−Mg−O膜、Sn−Mg−O膜、

In−Mg−O膜や、In−O膜、Sn−O膜、Zn−O膜などの酸化物半導体膜を用い

ることができる。また、上記酸化物半導体膜にSiO2を含んでもよい。

【0068】

また、酸化物半導体膜は、InMO3(ZnO)m(m>0)で表記される薄膜を用いる

ことができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の

金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及び

Coなどがある。InMO3(ZnO)m(m>0)で表記される構造の酸化物半導体膜

のうち、MとしてGaを含む構造の酸化物半導体を、In−Ga−Zn−O酸化物半導体

とよび、その薄膜をIn−Ga−Zn−O膜ともよぶこととする。

【0069】

本実施の形態では、酸化物半導体膜をIn−Ga−Zn−O系金属酸化物ターゲットを用

いてスパッタ法により成膜する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン

)雰囲気下、酸素雰囲気下、またはそれらの混合雰囲気下においてスパッタ法により形成

することができる。

【0070】

酸化物半導体膜を成膜する際に用いるスパッタガスは水素、水、水酸基または水素化物な

どの不純物がppm程度の濃度またはppb程度の濃度まで除去された高純度ガスを用い

ることが好ましい。

【0071】

酸化物半導体膜をスパッタ法で作製するためのターゲットとしては、酸化亜鉛を主成分と

する金属酸化物のターゲットを用いることができる。例えば、組成比として、In2O3

:Ga2O3:ZnO=1:1:1[mol数比]の金属酸化物ターゲットを用いれば良

い。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の金属酸化物タ

ーゲットを用いてもよい。金属酸化物ターゲットの充填率は90%以上100%以下、好

ましくは95%以上99.9%である。充填率の高い金属酸化物ターゲットを用いること

により、成膜した酸化物半導体膜は緻密な膜となる。

【0072】

酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分

を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲット

として絶縁層上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、

吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、

チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ター

ボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気

した処理室は、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好まし

くは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体

膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱して

もよい。

【0073】

成膜条件の一例としては、基板温度室温、基板とターゲットの間との距離を110mm、

圧力0.4Pa、直流(DC)電源0.5kW、酸素及びアルゴン(酸素流量15scc

m:アルゴン流量30sccm)雰囲気下の条件が適用される。なお、パルス直流(DC

)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減で

き、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30

nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応

じて適宜厚みを選択すればよい。

【0074】

次いで、酸化物半導体膜を第1のフォトリソグラフィ工程及びエッチング工程により島状

の酸化物半導体層102及び122に加工する(図4(B)参照)。ここで、酸化物半導

体層102は第1の薄膜トランジスタのチャネル領域を形成する半導体層であり、酸化物

半導体層122は第2の薄膜トランジスタのチャネル領域を形成する半導体層である。

【0075】

なお、島状の酸化物半導体層を形成するためのレジストマスクはインクジェット法で形成

してもよい。インクジェット法ではフォトマスクを使用しないため、製造コストを低減で

きる。また、ここでの酸化物半導体膜のエッチングは、ドライエッチングでもウェットエ

ッチングでもよく、両方を用いてもよい。

【0076】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例え

ば塩素(Cl2)、塩化硼素(BCl3)、塩化珪素(SiCl4)、四塩化炭素(CC

l4)など)が好ましい。

【0077】

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(S

F6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(H

Br)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガ

スを添加したガス、などを用いることができる。

【0078】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etch

ing)法や、ICP(Inductively Coupled Plasma:誘導

結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングでき

るように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加さ

れる電力量、基板側の電極温度等)を適宜調節する。

【0079】

ウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液、ア

ンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2)な

どを用いることができる。また、ITO−07N(関東化学社製)を用いてもよい。

【0080】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によっ

て除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を

再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等

の材料を回収して再利用することにより、資源を有効活用しコストを低減できる。

【0081】

所望の形状にエッチングできるように、材料に合わせてエッチング条件(エッチング液、

エッチング時間、温度等)を適宜調節する。

【0082】

本実施の形態では、エッチング液として燐酸と酢酸と硝酸を混ぜた溶液を用いたウェット

エッチング法により、酸化物半導体膜を島状の酸化物半導体層102及び122に加工す

る。

【0083】

本実施の形態では、酸化物半導体層102及び122に対して窒素、またはヘリウム、ネ

オン、アルゴン等の希ガス雰囲気下で第1の加熱処理を行う。第1の加熱処理の温度は、

400℃以上750℃以下、好ましくは400℃以上基板の歪み点未満とする。ここでは

、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気

下450℃において1時間の加熱処理を行う。加熱処理温度からの降温時には、雰囲気を

酸素に切り替えても良い。この第1の加熱処理によって酸化物半導体層102及び122

の脱水化または脱水素化を行うことができる。

【0084】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱

輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas

Rapid Thermal Annealing)装置、LRTA(Lamp Ra

pid Thermal Annealing)装置等のRTA(Rapid Ther

mal Annealing)装置を用いることができる。LRTA装置は、ハロゲンラ

ンプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナト

リウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処

理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置で

ある。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理

物と反応しない不活性気体が用いられる。

【0085】

例えば、第1の加熱処理として、650℃以上700℃以下の高温に加熱した不活性ガス

中に基板を入れ、数分間加熱した後に基板不活性ガス中から出すGRTAを行ってもよい

。GRTAを用いると短時間での高温加熱処理が可能となる。

【0086】

なお、第1の加熱処理においては、窒素、ヘリウム、ネオン、またはアルゴン等の雰囲気

ガスに、水、水素などが含まれないことが好ましい。または、該雰囲気ガスの純度を、6

N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純

物濃度を1ppm以下、好ましくは0.1ppm以下)とする。雰囲気ガスとして酸素を

用いる場合も同様の純度であることが好ましい。

【0087】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層

が結晶化し、微結晶層または多結晶層となる場合もある。例えば、結晶化率が90%以上

、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理

の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半

導体層となる場合もある。また、非晶質の酸化物半導体層の中に微結晶部(粒径1nm以

上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる

場合もある。

【0088】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物

半導体膜に行うこともできる。

【0089】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成

膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及び

ドレイン電極上にゲート絶縁層を形成した後、のいずれで行っても良い。

【0090】

次いで、第2のフォトリソグラフィ工程及びエッチング工程によりフォトダイオード上層

のP+層に達する開口部を絶縁層に形成し、絶縁層及び酸化物半導体層102及び122

上に、導電層を形成する。導電層をスパッタ法や真空蒸着法で形成すればよい。導電層の

材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステ

ンから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わ

せた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム

、イットリウムのいずれか一または複数から選択された材料を用いてもよい。また、金属

導電層は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むア

ルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と

、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する

3層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タングステン、

モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み

合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

【0091】

次に、第3のフォトリソグラフィ工程にて導電層上にレジストマスクを形成し、選択的に

エッチングを行って、第1の薄膜トランジスタのソース電極104及びドレイン電極10

6、第2の薄膜トランジスタのソース電極124及びドレイン電極126を形成した後、

レジストマスクを除去する(図4(C)参照)。ここで、第1の薄膜トランジスタのドレ

イン電極106と第2の薄膜トランジスタのソース電極124は電気的に接続された状態

で形成されるが、絶縁された状態でも良く、後に配線を用いて電気的に接続しても良い。

なお、形成されたソース電極、ドレイン電極の端部がテーパであると、上に積層するゲー

ト絶縁層の被覆性が向上するため好ましい。

【0092】

本実施の形態では、ソース電極104及び124、ドレイン電極106及び126として

、スパッタ法により膜厚150nmのチタン膜を形成する。

【0093】

なお、導電層のエッチングの際に、酸化物半導体層102及び122は酸化物半導体層の

一部が除去されて、その下の絶縁層が露出しないようにそれぞれの材料及びエッチング条

件を適宜調節する。

【0094】

本実施の形態では、導電層としてチタン膜を用いて、酸化物半導体層102及び122に

はIn−Ga−Zn−O系酸化物半導体を用いて、エッチャントとしてアンモニア過水(

アンモニア、水、過酸化水素水の混合液)を用いる。

【0095】

なお、第3のフォトリソグラフィ工程及びエッチング工程では、酸化物半導体層102及

び122は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となること

もある。また、ソース電極104及び124、ドレイン電極106及び126を形成する

ためのレジストマスクをインクジェット法で形成してもよい。インクジェット法はフォト

マスクを使用しないため、製造コストを低減することができる。

【0096】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレ

ーザ光やArFレーザ光を用いる。酸化物半導体層102及び122上で隣り合うソース

電極の下端部とドレイン電極の下端部との間隔幅によって後に形成される薄膜トランジス

タのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合に

は、数nm〜数10nmと極めて波長が短い超紫外線(Extreme Ultravi

olet)を用いて第2のフォトリソグラフィ工程でのレジストマスク形成時の露光を行

う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄

膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり

、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も

図ることができる。

【0097】

次いで、絶縁層、酸化物半導体層102及び122、ソース電極104及び124、ドレ

イン電極106及び126上にゲート絶縁層118を形成する(図5(A)参照)。この

とき、バルクトランジスタ上にもゲート絶縁層118は成膜され、層間絶縁膜の一部とな

る。

【0098】

ここで、不純物を除去することによりi型化または実質的にi型化された酸化物半導体(

高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、ゲ

ート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート

絶縁層(GI)は、高品質化が要求される。

【0099】

例えば、マイクロ波(2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐

圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品

質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとす

ることができるからである。もちろん、ゲート絶縁層として良質な絶縁層を形成できるも

のであれば、スパッタ法やプラズマCVD法など他の成膜方法を適用することができる。

また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質さ

れる絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であるこ

とは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるもの

であれば良い。

【0100】

さらに、85℃、2×106V/cm、12時間のゲートバイアス・熱ストレス試験(B

T試験)においては、不純物が酸化物半導体に添加されていると、不純物と酸化物半導体

の主成分との結合が、強電界(B:バイアス)と高温(T:温度)により切断され、生成

された未結合手がしきい値電圧(Vth)のシフトを誘発することとなる。これに対して

、本発明の一態様は、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のよう

にゲート絶縁層との界面特性を良好にすることにより、BT試験を行っても安定な薄膜ト

ランジスタを得ることを可能としている。

【0101】

本実施の形態において、ゲート絶縁層118の形成は、マイクロ波(2.45GHz)を

用いた高密度プラズマCVD装置により行う。ここでは、高密度プラズマCVD装置は、

1×1011/cm3以上のプラズマ密度を達成できる装置を指している。例えば、3k

W以上6kW以下のマイクロ波電力を印加してプラズマを発生させて、絶縁層の成膜を行

う。

【0102】

チャンバーに材料ガスとしてモノシランガス(SiH4)と亜酸化窒素(N2O)と希ガ

スを導入し、10Pa〜30Paの圧力下で高密度プラズマを発生させて基板上に絶縁層

を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素(

N2O)と希ガスとを導入して絶縁層表面にプラズマ処理を行ってもよい。少なくとも亜

酸化窒素(N2O)と希ガスとを導入して絶縁層表面に行われるプラズマ処理は、絶縁層

の成膜より後に行う。上記プロセスを経た絶縁層は、膜厚が薄く、例えば100nm未満

であっても信頼性を確保することができる。

【0103】

ゲート絶縁層118の形成の際、チャンバーに導入するモノシランガス(SiH4)と亜

酸化窒素(N2O)との流量比は、1:10から1:200の範囲とする。また、チャン

バーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用い

ることができるが、中でも安価であるアルゴンを用いることが好ましい。

【0104】

また、高密度プラズマCVD装置により得られる絶縁層は、段差被覆性に優れており、膜

厚を正確に制御することができる。

【0105】

上記プロセスを経た絶縁層は、従来の平行平板型のPECVD装置で得られる絶縁層とは

膜質が大きく異なっており、同じエッチャントを用いたエッチング速度の比較では、平行

平板型のPECVD装置で得られる絶縁層の10%以上または20%以上エッチング速度

が遅く、高密度プラズマCVD装置で得られる絶縁層は緻密な層と言える。

【0106】

本実施の形態では、ゲート絶縁層118として高密度プラズマCVD装置による膜厚10

0nmの酸化窒化珪素層(SiOxNyとも呼ぶ、ただし、x>y>0)を用いる。

【0107】

その他の方法として、プラズマCVD法またはスパッタ法等を用いて、酸化シリコン層、

窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、または酸化アルミニウム層

を単層でまたは積層して形成することもできる。なお、ゲート絶縁層118中に水素が多

量に含まれないようにするためには、スパッタ法でゲート絶縁層118を成膜することも

好ましい。スパッタ法により酸化シリコン層を成膜する場合には、ターゲットとしてシリ

コンまたは石英を用い、スパッタガスとして酸素または、酸素及びアルゴンの混合ガスを

用いて行う。

【0108】

ゲート絶縁層118は、ソース電極104、124、及びドレイン電極106、126側

から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。例えば、第1

のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層(SiOx(x>

0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層としてスパッタ法により膜

厚50nm以上200nm以下の窒化シリコン層(SiNy(y>0))を積層して、膜

厚100nmのゲート絶縁層としてもよい。

【0109】

次いで、第4のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチ

ングを行ってゲート絶縁層118の一部を除去して、薄膜トランジスタのドレイン電極1

26、及びバルクトランジスタのソース領域またはドレイン領域となるn型領域132a

、132bに達する開口部を形成する(図5(B)参照)。

【0110】

次に、開口部が形成されたゲート絶縁層118上に導電層を形成した後、第5のフォトリ

ソグラフィ工程及びエッチング工程によりゲート電極108、128及び配線層151、

152、153を形成する。なお、レジストマスクをインクジェット法で形成してもよい

。インクジェット法はフォトマスクを使用しないため、製造コストを低減することができ

る。

【0111】

また、ゲート電極108、128及び配線層151、152、153は、モリブデン、チ

タン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等

の金属材料又はこれらを主成分とする合金材料を用いて、単層、または積層して形成する

ことができる。

【0112】

例えば、ゲート電極108、128及び配線層151、152、153を2層とする積層

構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、または銅

層上にモリブデン層を積層した2層構造、または銅層上に窒化チタン層若しくは窒化タン

タルを積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造とすること

が好ましい。3層の積層構造としては、タングステン層または窒化タングステン層と、ア

ルミニウムとシリコンの合金またはアルミニウムとチタンの合金と、窒化チタン層または

チタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電層を用いて

ゲート電極を形成することもできる。透光性を有する導電層としては、透光性導電性酸化

物等をその例に挙げることができる。

【0113】

本実施の形態では、ゲート電極108、128及び配線層151、152、153として

膜厚150nmのチタン膜をスパッタ法により形成する。

【0114】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは2

00℃以上400℃以下、例えば250℃以上350℃以下)を行う。本実施の形態では

、窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。また、第2の加熱処理は、

第1の薄膜トランジスタ、第2の薄膜トランジスタ及びバルクトランジスタ上に保護絶縁

層や平坦化絶縁層を形成してから行ってもよい。

【0115】

さらに大気中、100℃以上200℃以下、1時間以上30時間以下で加熱処理を行って

もよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100

℃以上200℃の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえし

て行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよ

い。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

【0116】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層を有

する第1の薄膜トランジスタ及び第2の薄膜トランジスタを形成することができる(図5

(C)参照)。ここで、第1の薄膜トランジスタは転送トランジスタ101として適用す

ることができ、第2の薄膜トランジスタはリセットトランジスタ121として適用するこ

とができ、バルクトランジスタは増幅トランジスタ131として適用することができる。

【0117】

また、薄膜トランジスタ及びバルクトランジスタ上に保護絶縁層142や、平坦化のため

の平坦化絶縁層を設けてもよい。例えば、保護絶縁層142として酸化シリコン層、窒化

シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、または酸化アルミニウム層を単

層、または積層して形成することができる。

【0118】

また、平坦化絶縁層としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド

、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他

に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BP

SG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶

縁膜を複数積層させることで、平坦化絶縁層を形成してもよい。

【0119】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi−O−

Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアル

キル基やアリール基)を用いても良い。また、有機基はフルオロ基を有していても良い。

【0120】

平坦化絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、

スピンコート法、ディップ法、スプレー塗布法、液滴吐出法(インクジェット法、スクリ

ーン印刷法、オフセット印刷法等)などの方法や、ドクターナイフ、ロールコーター、カ

ーテンコーター、ナイフコーター等の器具を用いることができる。

【0121】

上記のように酸化物半導体膜を成膜するに際し、雰囲気中の残留水分を除去することで、

該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化

物半導体膜の安定化を図ることができる。

【0122】

以上のように、酸化物半導体層を用いる薄膜トランジスタを有する半導体装置において、

安定な電気特性を有し信頼性の高い半導体装置を提供することができる。

【0123】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0124】

(実施の形態2)

本発明の一形態は、酸化物半導体中でキャリアの供与体(ドナーまたはアクセプタ)とな

り得る不純物を極めて少ないレベルにまで除去することで、真性または実質的に真性な半

導体であって、当該酸化物半導体を薄膜トランジスタに適用するものである。本実施の形

態では、評価用素子(TEGとも呼ぶ)でのオフ電流の測定値について以下に説明する。

【0125】

図6にL/W=3μm/50μmの薄膜トランジスタを200個並列に接続し、L/W=

3μm/10000μmの薄膜トランジスタの初期特性を示す。また、薄膜トランジスタ

の上面図を図7(A)に示し、その一部を拡大した図を図7(B)に示す。図7(B)の

点線で囲んだ領域がL/W=3μm/50μm、Lov=1.5μmの1段分の薄膜トラ

ンジスタである。薄膜トランジスタの初期特性を測定するため、基板温度を室温とし、ソ

ース−ドレイン間電圧(以下、ドレイン電圧またはVdという)を10Vとし、ソース−

ゲート間電圧(以下、ゲート電圧またはVgという)を−20V〜+20Vまで変化させ

たときのソース−ドレイン電流(以下、ドレイン電流またはIdという)の変化特性、す

なわちVg−Id特性を測定した。なお、図7では、Vgを−20V〜+5Vまでの範囲

で示している。

【0126】

図6に示すようにチャネル幅Wが10000μmの薄膜トランジスタは、Vdが1V及び

10Vにおいてオフ電流は1×10−13[A]以下となっており、測定機(半導体パラ

メータ・アナライザ、Agilent 4156C;Agilent社製)の分解能(1

00fA)以下となっている。

【0127】

すなわち、上記の薄膜トランジスタは、電気特性がノーマリーオフを呈し、1Vから10

Vのドレイン電圧において、チャネル幅1μmあたりのオフ電流は、100aA/μm以

下、好ましくは10aA/μm以下、更に好ましくは1aA/μm以下となるように作用

させることができる。

【0128】

測定した薄膜トランジスタの作製方法について説明する。

【0129】

まず、ガラス基板上に下地層として、CVD法により窒化珪素層を形成し、窒化珪素層上

に酸化窒化珪素層を形成した。酸化窒化珪素層上にゲート電極としてスパッタ法によりタ

ングステン層を形成した。ここで、タングステン層を選択的にエッチングしてゲート電極

を形成した。

【0130】

次に、ゲート電極上にゲート絶縁層としてCVD法により厚さ100nmの酸化窒化珪素

層を形成した。

【0131】

次に、ゲート絶縁層上に、スパッタ法によりIn−Ga−Zn−O系酸化物半導体ターゲ

ット(mol数比で、In2O3:Ga2O3:ZnO=1:1:2)を用いて、厚さ5

0nmの酸化物半導体層を形成した。ここで、酸化物半導体層を選択的にエッチングし、

島状の酸化物半導体層を形成した。

【0132】

次に、酸化物半導体層をクリーンオーブンにて窒素雰囲気下、450℃、1時間の第1の

熱処理を行った。

【0133】

次に、酸化物半導体層上にソース電極及びドレイン電極としてチタン層(厚さ150nm

)をスパッタ法により形成した。ここで、チタン層を選択的にエッチングすることでソー

ス電極及びドレイン電極を形成し、1つの薄膜トランジスタのチャネル長Lが3μm、チ

ャネル幅Wが50μmとし、200個を並列とすることで、L/W=3μm/10000

μmとなるようにした。

【0134】

次に、酸化物半導体層に接するように保護絶縁層としてリアクティブスパッタ法により酸

化珪素層を膜厚300nmで形成した。ここで、保護層である酸化珪素層を選択的にエッ

チングし、ゲート電極、ソース電極及びドレイン電極上に開口部を形成した。その後、窒

素雰囲気下、250℃で1時間、第2の熱処理を行った。

【0135】

そして、Vg−Id特性を測定する前に150℃、10時間の加熱を行った。

【0136】

以上の工程により、ボトムゲート型の薄膜トランジスタを作製した。

【0137】

図6に示すように薄膜トランジスタのオフ電流が、1×10−13[A]程度であるのは

、上記作製工程において酸化物半導体層中における水素濃度を十分に低減できたためであ

る。酸化物半導体層中の水素濃度は、5×1019atoms/cm3以下、好ましくは

5×1018atoms/cm3以下、さらに好ましくは5×1017atoms/cm

3以下、または1×1016/cm3未満とする。なお、酸化物半導体層中の水素濃度測

定は、二次イオン質量分析法(SIMS:Secondary Ion Mass Sp

ectroscopy)で行う。

【0138】

また、In−Ga−Zn−O系酸化物半導体を用いる例を示したが、特に限定されず、他

の酸化物半導体材料、例えば、In−Sn−Zn−O系、Sn−Ga−Zn−O系、Al

−Ga−Zn−O系、Sn−Al−Zn−O系、In−Zn−O系、In−Sn−O系、

Sn−Zn−O系、Al−Zn−O系、In−O系、Sn−O系、Zn−O系などを用い

ることができる。また、酸化物半導体材料として、Alを2.5〜10wt%混入したI

n−Al−Zn−O系や、Siを2.5〜10wt%混入したIn−Zn−O系を用いる

こともできる。

【0139】

また、ホール測定機で測定される酸化物半導体層のキャリア濃度は、5×1014/cm

3未満、好ましくは5×1012/cm3以下、さらに好ましくはシリコンのキャリア濃

度1.45×1010/cm3と同等、もしくはそれ以下である。即ち、酸化物半導体層

のキャリア濃度は、限りなくゼロに近くすることができる。

【0140】

また、薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可

能であり、回路の動作速度を高速化でき、オフ電流値が極めて小さいため、さらに低消費

電力化も図ることができる。

【0141】

また、薄膜トランジスタのオフ状態において、酸化物半導体層は絶縁体とみなせて回路設

計を行うことができる。

【0142】

続いて、本実施の形態で作製した薄膜トランジスタに対してオフ電流の温度特性を評価し

た。温度特性は、薄膜トランジスタが使われる最終製品の耐環境性や、性能の維持などを

考慮する上で重要である。当然ながら、変化量が小さいほど好ましく、製品設計の自由度

が増す。

【0143】

温度特性は、恒温槽を用い、−30℃、0℃、25℃、40℃、60℃、80℃、100

℃、及び120℃のそれぞれの温度で薄膜トランジスタを形成した基板を一定温度とし、

ドレイン電圧を6V、ゲート電圧を−20V〜+20Vまで変化させてVg−Id特性を

取得した。

【0144】

図8(A)に示すのは、上記それぞれの温度で測定したVg−Id特性を重ね書きしたも

のであり、点線で囲むオフ電流の領域を拡大したものを図8(B)に示す。図中の矢印で

示す右端の曲線が−30℃、左端が120℃で取得した曲線で、その他の温度で取得した

曲線は、その間に位置する。オン電流の温度依存性はほとんど見られない。一方、オフ電

流は拡大図の図8(B)においても明らかであるように、ゲート電圧が20V近傍を除い

て、全ての温度で測定機の分解能近傍の1×10−12[A]以下となっており、温度依

存性もない。すなわち、120℃の高温においても、オフ電流が1×10−12[A]以

下を維持しており、チャネル幅Wが10000μmであることを考慮すると、オフ電流が

非常に小さいことがわかる。

【0145】

高純度化された酸化物半導体(purified Oxide Semiconduct

or)を用いた薄膜トランジスタは、オフ電流の温度依存性がほとんど現れない。これは

、図10(A)のバンド図で示すように、酸化物半導体が高純度化されることによって、

導電型が限りなく真性型に近づき、フェルミ準位が禁制帯の中央に位置するため、温度依

存性を示さなくなると言える。また、これは、酸化物半導体のエネルギーが3eV以上で

あり、熱励起キャリアが極めて少ないことにも起因する。また、ソース領域及びドレイン

領域は縮退した状態にあるので温度依存性が現れない要因となっている。薄膜トランジス

タの動作は、縮退したソース領域から酸化物半導体に注入されたキャリアによるものがほ

とんどであり、キャリア密度の温度依存性がないことから上記特性(オフ電流の温度依存

性無し)を説明することができる。また、この極めて低いオフ電流について、以下にバン

ド図を用いて説明する。

【0146】

図9は、酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図である。ゲート

電極(GE1)上にゲート絶縁膜(GI)を介して酸化物半導体層(OS)が設けられ、

その上にソース電極(S)及びドレイン電極(D)が設けられている。

【0147】

図10は、図9に示すA−A’断面におけるエネルギーバンド図(模式図)である。図1

0(A)はソースとドレインの間の電圧を等電位(VD=0V)とした場合を示し、図1

0(B)はドレインに正の電位(VD>0)を加えた場合を示す。

【0148】

図11は、図9におけるB−B’の断面におけるエネルギーバンド図(模式図)である。

図11(A)はゲート(G1)に正の電位(+VG)が印加された状態であり、ソースと

ドレイン間にキャリア(電子)が流れるオン状態を示している。また、図11(B)は、

ゲート(G1)に負の電位(−VG)が印加された状態であり、オフ状態(少数キャリア

は流れない)である場合を示す。

【0149】

図12は、真空準位と金属の仕事関数(φM)、酸化物半導体の電子親和力(χ)の関係

を示す。

【0150】

従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位(EF)は、バンドギ

ャップ中央に位置する真性フェルミ準位(Ei)から離れて、伝導帯寄りに位置している

。なお、酸化物半導体において水素の一部はドナーとなり、n型化する一つの要因である

ことが知られている。

【0151】

これに対して本発明の一態様に係る酸化物半導体は、n型不純物である水素を酸化物半導

体から除去し、酸化物半導体の主成分以外に不純物が極力含まれないように高純度化する

ことにより真性(i型)とし、又は真性型とせんとしたものである。すなわち、不純物を

添加してi型化するのでなく、水素や水等の不純物を極力除去したことにより、高純度化

されたi型(真性)半導体又はそれに近づけることを特徴としている。そうすることによ

り、フェルミ準位(EF)は真性フェルミ準位(Ei)と同じレベルにまですることがで

きる。

【0152】

酸化物半導体のバンドギャップ(Eg)が3.15eVである場合、電子親和力(χ)は

4.3eVと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕

事関数は、酸化物半導体の電子親和力(χ)とほぼ等しい。この場合、金属−酸化物半導

体界面において、電子に対してショットキー型の障壁は形成されない。

【0153】

すなわち、金属の仕事関数(φM)と酸化物半導体の電子親和力(χ)が等しい場合、両

者が接触すると図10(A)で示すようなエネルギーバンド図(模式図)が示される。

【0154】

図10(B)において黒丸(●)は電子を示し、ドレインに正の電位が印加されると、電

子はバリア(h)をこえて酸化物半導体に注入され、ドレインに向かって流れる。この場

合、バリア(h)の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレ

イン電圧が印加された場合には、電圧印加のない図10(A)のバリアの高さすなわちバ

ンドギャップ(Eg)の1/2よりもバリアの高さ(h)は小さい値となる。

【0155】

このとき酸化物半導体に注入された電子は、図11(A)で示すように酸化物半導体中を

流れる。また、図11(B)において、ゲート電極(G1)に負の電位が印加されると、

少数キャリアであるホールは実質的にゼロであるため、電流は限りなく流れなくなる。

【0156】

例えば、薄膜トランジスタのチャネル幅Wが1×104μmでチャネル長Lが3μmの素

子であっても、オフ電流が10−13A以下であり、サブスレッショルドスイング値(S

値)が0.1V/dec.(ゲート絶縁膜厚100nm)の電気特性が得られる。

【0157】

シリコン半導体の真性キャリア密度は1.45×1010/cm3(300K)であり、

室温においてもキャリアが存在している。これは、室温においても、熱励起キャリアが存

在していることを意味している。さらに、シリコン半導体のバンドギャップは1.12e

Vであるので、シリコン半導体を用いたトランジスタは温度に依存してオフ電流が大きく

変動することとなる。

【0158】

従って、単にバンドギャップの広い酸化物半導体をトランジスタに適用するのではなく、

酸化物半導体の主成分以外に不純物が極力含まれないように高純度化することにより、キ

ャリア濃度を1×1014/cm3以下、好ましくは1×1012/cm3以下となるよ

うにすることで、実用的な動作温度で熱的に励起されるキャリアがほとんど無く、ソース

側から注入される電子のみによってトランジスタを動作させることができる。それにより

、オフ電流を1×10−13A以下にまで下げると共に、温度変化によってオフ電流がほ

とんど変化しない極めて安定に動作するトランジスタを得ることができる。

【0159】

本発明の一態様における技術思想は、酸化物半導体中に、不純物を加えることをせずに逆

に不本意に存在する水、水素という不純物を除去することにより、酸化物半導体自体を高

純度化することにある。すなわち、ドナー準位を作る水または水素を除去し、これと同時

に酸素欠乏状態となった酸化物半導体に酸素を補填することにより、酸化物半導体自体を

高純度化することを特徴としている。

【0160】

酸化物半導体は成膜直後ですら1020/cm3のレベルの水素がSIMS(二次イオン

質量分析)で観察される。ドナー準位を作る水または水素を意図的に除去し、更に水また

は水素の除去に伴い同時に減少してしまう酸素を補填することにより、酸化物半導体を高

純度化し、電気的にi型(真性)半導体とすることを技術思想の一つとしている。

【0161】

結果として、水素の量は少なければ少ないほど良く、酸化物半導体中のキャリアも少なけ

れば少ないほど良い。酸化物半導体は、薄膜トランジスタに用いる場合に電流の担い手と

してのキャリアを意図的に有するというよりも、逆に酸化物半導体中のキャリアは無くし

てしまい、ソースから供給されるキャリア(電子)を通過させる通路として機能する、い

わゆる高純度化したi型(真性)半導体である。

【0162】

その結果、酸化物半導体中にキャリアを無くさせる、または極めて少なくさせることによ

り、トランジスタのオフ電流が少なくなるというのが本発明の一態様における技術思想で

ある。すなわち、その指標として水素濃度は5×1019/cm3以下、好ましくは5×

1018/cm3以下、さらに好ましくは5×1017/cm3以下、または1×101

6/cm3未満、またキャリア密度は1×1014/cm3未満、好ましくは1×101

2/cm3以下が求められる。

【0163】

また結果として、酸化物半導体は通路(パス)として機能し、酸化物半導体自体がキャリ

アを供給しない、またはほとんど供給しないように高純度化したi型(真性)とし、キャ

リアはソース、ドレインにより供給される。供給の程度は、酸化物半導体の電子親和力χ

およびフェルミレベル、理想的には真性フェルミレベルと一致したフェルミレベルとソー

ス、ドレインの仕事関数というより、バリアハイト(障壁高さ)で決められる。

【0164】

このため、オフ電流は少なければ少ないほど良く、1〜10Vの間のいずれかのドレイン

電圧を印加した場合のトランジスタ特性において、100aA/μm(チャネル幅W=1

μm当たりの電流)以下、好ましくは10aA/μm以下、さらに好ましくは1aA/μ

m以下であることを特徴としている。

【0165】

このようにオフ電流が極めて小さい薄膜トランジスタを用いて、記憶回路(記憶素子)な

どを作製した場合、オフ電流が小さくほとんどリークがないため、電位保持時間が長く、

記憶データを長時間保持することが可能となる。

【0166】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0167】

(実施の形態3)

本発明の一態様における薄膜トランジスタを含む固体撮像素子の動作について説明する。

【0168】

CMOS(Complementary Metal Oxide Semicondu

ctor)イメージセンサは、信号電荷蓄積部に電位を保持し、その電位を増幅トランジ

スタを介して垂直出力線に出力する固体撮像素子である。CMOSイメージセンサに含ま

れるリセットトランジスタ及び/または転送トランジスタにリーク電流があると、そのリ

ーク電流によって充電または放電が起こり、信号電荷蓄積部の電位が変化する。信号電荷

蓄積部の電位が変わると増幅トランジスタの電位も変わってしまい、本来の電位からずれ

た値となり、撮像された映像が劣化してしまう。

【0169】

本実施の形態では、実施の形態1及び2で示した薄膜トランジスタをCMOSイメージセ

ンサのリセットトランジスタ及び転送トランジスタに適用した場合の動作の効果を説明す

る。なお、増幅トランジスタは薄膜トランジスタまたはバルクトランジスタのどちらを適

用しても良い。

【0170】

図13は、CMOSイメージセンサの画素構成の一例を示す図である。画素は光電変換素

子であるフォトダイオード1002、転送トランジスタ1004、リセットトランジスタ

1006、増幅トランジスタ1008及び各種配線で構成されており、マトリクス状に複

数が配置されてセンサを構成している。また、増幅トランジスタ1008と電気的に接続

される選択トランジスタを設けても良い。なお、トランジスタ記号に記してある「OS」

は酸化物半導体(Oxide Semiconductor)を示し、「Si」はシリコ

ンを示しており、それぞれのトランジスタに適用すると好ましい材料を表している。以降

の図面についても同様である。

【0171】

ここで、フォトダイオード1002は、転送トランジスタ1004のソース側に接続され

ており、転送トランジスタ1004のドレイン側には信号電荷蓄積部1010(FD:フ

ローティングディフュージョンとも呼ぶ)が形成される。信号電荷蓄積部1010にはリ

セットトランジスタ1006のソース及び増幅トランジスタ1008のゲートが接続され

ている。別の構成として、リセット電源線1110を削除することもできる。例えば、リ

セットトランジスタ1006のドレインをリセット電源線1110ではなく、電源線11

00または垂直出力線1120につなぐ方法がある。

【0172】

次に図14のタイミングチャートを用いて動作を説明する。まず、電源端子に電源電圧が

供給される。続いて、リセットトランジスタ1006のゲートにリセットパルスが入力さ

れ、リセットトランジスタ1006がオンする。信号電荷蓄積部1010はリセット電源

の電位に充電される。その後、リセットトランジスタ1006はオフになり信号電荷蓄積

部1010はリセット電源の電位に保持される(期間T1)。ここで、リセットトランジ

スタ1006及び転送トランジスタ1004にリーク電流がほとんど流れなければ、次の

トランジスタの動作まで電位は保持される。次に、転送トランジスタ1004がオンする

と信号電荷蓄積部1010から電流がフォトダイオードに流れて、信号電荷蓄積部101

0の電位は低下する(期間T2)。転送トランジスタ1004がオフすると、オフした時

点での電位が信号電荷蓄積部1010に保持される(期間T3)。リセットトランジスタ

1006及び転送トランジスタ1004にリーク電流がほとんど流れなければ、次のトラ

ンジスタの動作まで電位は保持される。そして、増幅トランジスタ1008を介して垂直

出力線1120に出力される。その後、電源端子への電源電圧の供給が遮断される。この

ような順序で信号が出力される。

【0173】

つまり、リセットトランジスタ1006及び転送トランジスタ1004に実施の形態1及

び2に示した極めてオフ電流の低い酸化物半導体の薄膜トランジスタを適用することによ

って、信号電荷蓄積部1010から薄膜トランジスタを介したリーク電流をほとんど無く

すことができ、上記期間T1及びT3の保持期間中に極めて高い電位保持機能を作用させ

ることができる。

【0174】

次にフォトダイオード1002の動作について図15を用いて説明する。フォトダイオー

ドは光が照射されないときは通常のダイオードと同じ電圧電流特性を示す(図15に示す

Aの曲線)。光が照射されると、特に逆バイアス印加時において、光照射なしに比較して

大きな電流が流れる(図15に示すBの曲線)。フォトダイオード動作点を図13の画素

の動作に合わせて説明する。転送トランジスタ1004がオフの状態では、フォトダイオ

ード1002に電流経路がないため、光が照射されるとフォトダイオードのカソードは図

15のc点に位置する。リセットトランジスタ1006がオンし信号電荷蓄積部1010

がリセット電源電位に保持されたあと、転送トランジスタ1004がオンするとフォトダ

イオード1002のカソード電位はリセット電源電位となり、図15ではd点に移動する

。そして、信号電荷蓄積部1010から転送トランジスタ1004を介して、放電電流が

フォトダイオード1002に流れ、信号電荷蓄積部1010の電位は低下する。転送トラ

ンジスタ1004がオフしたところで、放電は止まり、そのときの図15での動作点をe

とすると動作点dと動作点e間の電位差がフォトダイオード1002の放電によって得ら

れる信号の電位差となる。

【0175】

次に、リセットトランジスタ、増幅トランジスタ、各信号線を複数の画素で兼用する場合

の動作について説明する。図16は、リセットトランジスタ、転送トランジスタ、増幅ト

ランジスタ、フォトダイオードが各画素に一つずつあり、かつリセット線、転送スイッチ

線、垂直出力線が画素に接続された基本形である。

【0176】

基本形の動作を図17のタイミングチャートに従って説明する。1ライン目の駆動につい

ては、まず第1のリセット線1240の電位(RST1)が高電位になると、第1のリセ

ットトランジスタ1216をオンさせる。これで第1の信号電荷蓄積部1210の電位(

FD1)が電源電位(以下、VDD)まで持ち上がる。第1のリセット線1240の電位

(RST1)が低電位になり、第1のリセットトランジスタ1216がオフしても、電流

パスがなければ第1の信号電荷蓄積部1210の電位はVDDに保持される。次に、第1

の転送スイッチ線1250の電位(TRF1)が高電位になると、第1の転送トランジス

タ1214がオンし、第1のフォトダイオード1212に照射されている光に応じた電流

が第1のフォトダイオード1212と第1の転送トランジスタ1214に流れ、第1の信

号電荷蓄積部1210の電位(FD1)が放電により低下する。第1の転送スイッチ線1

250の電位(TRF1)が低電位になると、第1の転送トランジスタ1214がオフし

、再び電流パスがなくなるため第1の信号電荷蓄積部1210の電位(FD1)は保持さ

れる。この電位を第1の増幅トランジスタ1218を介して垂直出力線1220に出力す

る。次に第2のリセット線1340及び第2の転送スイッチ線1350を有する2ライン

目の駆動が行われる。この様にして順次駆動される。なお、図17のRST2、TRF2

及びFD2は、2ライン目の駆動におけるタイミングチャートを示している。

【0177】

図18は上記の基本形とは異なり、縦4個の画素について、リセットトランジスタ、増幅

トランジスタ、リセット線を兼用する垂直4画素共有型の構成を示している。トランジス

タ及び配線の数を削減することで画素面積の縮小による微細化や、フォトダイオードの受

光面積拡大によってノイズを低減することができる。縦4個の各画素の転送トランジスタ

のドレイン側が電気的に接続され、信号電荷蓄積部1410が形成されており、信号電荷

蓄積部1410にはリセットトランジスタ1406のソース及び増幅トランジスタ140

8のゲートが接続されている。

【0178】

垂直4画素共有型の動作を図19のタイミングチャートに従って説明する。1ライン目の

駆動は、まず第1のリセット線1461の電位(RST1)が高電位になり、第1のリセ

ットトランジスタ1406がオンする。これで、信号電荷蓄積部1410の電位(FD)

がVDDまで持ち上がる。第1のリセット線1461の電位(RST1)が低電位になり

、第1のリセットトランジスタ1406がオフしても電流パスがなければ信号電荷蓄積部

1410の電位(FD)はVDDに保持される。次に、第1の転送スイッチ線1451の

電位(TRF1)が高電位になり、第1の転送トランジスタ1414がオンし、第1のフ

ォトダイオード1412に照射されている光に応じた電流が第1のフォトダイオード14

12と第1の転送トランジスタ1414に流れ、信号電荷蓄積部1410の電位(FD)

が放電により低下する。第1の転送スイッチ線1451電位(TRF1)が低電位になる

と第1の転送トランジスタ1414がオフし、再び電流パスがなくなるため信号電荷蓄積

部1410の電位(FD)は保持される。この電位を第1の増幅トランジスタ1408を

介して垂直出力線1470に出力する。

【0179】

2ライン目の駆動は、再び第1のリセット線1461の電位(RST1)が高電位になり

、第1のリセットトランジスタ1406がオンする。これで、信号電荷蓄積部1410の

電位(FD)がVDDまで持ち上がる。第1のリセット線1461の電位(RST1)が

低電位になり、第1のリセットトランジスタ1406がオフしても電流パスがなければ信

号電荷蓄積部1410の電位(FD)はVDDに保持される。次に、第2の転送スイッチ

線1452の電位(TRF2)が高電位になり、第2の転送トランジスタ1424がオン

し、第2のフォトダイオード1422に照射されている光に応じた電流が第2のフォトダ

イオード1422と第2の転送トランジスタ1424に流れ、信号電荷蓄積部1410の

電位(FD)が放電により低下する。第2の転送スイッチ線1452の電位(TRF2)

が低電位になると第2の転送トランジスタ1424がオフし、再び電流パスがなくなるた

め信号電荷蓄積部1410の電位(FD)は保持される。この電位を第1の増幅トランジ

スタ1408を介して垂直出力線1470に出力する。

【0180】

3ライン目の駆動は、再び第1のリセット線1461の電位(RST1)が高電位になり

、第1のリセットトランジスタ1406がオンする。これで、信号電荷蓄積部1410の

電位(FD)がVDDまで持ち上がる。第1のリセット線1461の電位(RST1)が

低電位になり、第1のリセットトランジスタ1406がオフしても電流パスがなければ信

号電荷蓄積部1410の電位(FD)はVDDに保持される。次に、第3の転送スイッチ

線1453の電位(TRF3)が高電位になり、第3の転送トランジスタ1434がオン

し、第3のフォトダイオード1432に照射されている光に応じた電流が第3のフォトダ

イオード1432と第3の転送トランジスタ1434に流れ、信号電荷蓄積部1410の

電位(FD)が放電により低下する。第3の転送スイッチ線1453の電位(TRF3)

が低電位になると第3の転送トランジスタ1434がオフし、再び電流パスがなくなるた

め信号電荷蓄積部1410の電位は保持される。この電位を第1の増幅トランジスタ14

08を介して垂直出力線1470に出力する。

【0181】

4ライン目の駆動は、再び第1のリセット線1461の電位(RST1)が高電位になり

、第1のリセットトランジスタ1406がオンする。これで、信号電荷蓄積部1410の

電位(FD)がVDDまで持ち上がる。第1のリセット線1461の電位(RST1)が

低電位になり、第1のリセットトランジスタ1406がオフしても電流パスがなければ信

号電荷蓄積部1410の電位(FD)はVDDに保持される。次に、第4の転送スイッチ

線の1454の電位(TRF4)が高電位になり、第4の転送トランジスタ1444がオ

ンし、第4のフォトダイオード1442に照射されている光に応じた電流が第4のフォト

ダイオード1442と第4の転送トランジスタ1444に流れ、信号電荷蓄積部1410

の電位(FD)が放電により低下する。第4の転送スイッチ線1454の電位(TRF4

)が低電位になると第4の転送トランジスタ1444がオフし、再び電流パスがなくなる

ため信号電荷蓄積部1410の電位(FD)は保持される。この電位を第1の増幅トラン

ジスタ1408を介して垂直出力線1470に出力する。5ライン目から8ライン目まで

の駆動については、第2のリセット線の電位(RST2)を制御することで、1ライン目

から4ライン目までと同様に順次駆動される。

【0182】

図20は図18とは異なる画素共有構成で、垂直、水平それぞれ2個ずつの画素について

、リセット線、リセットトランジスタ、増幅トランジスタを兼用する垂直水平4画素共有

型である。垂直4画素共有型と同じく、トランジスタ及び配線の数を削減することで画素

面積の縮小による微細化や、フォトダイオードの受光面積拡大によってノイズを低減する

ことができる。縦横に隣り合う4個の画素について、各画素の転送トランジスタのドレイ

ン側が電気的に接続され、信号電荷蓄積部1510が形成されており、信号電荷蓄積部1

510にはリセットトランジスタ1506のソース及び増幅トランジスタ1508のゲー

トが接続されている。

【0183】

垂直水平4画素共有型の動作を図21のタイミングチャートに従って説明する。1ライン

目の駆動は、まず第1のリセット線1561の電位(RST1)が高電位になり、第1の

リセットトランジスタ1506がオンする。これで信号電荷蓄積部1510の電位(FD

)がVDDまで持ち上がる。第1のリセット線1561の電位(RST1)が低電位にな

り、第1のリセットトランジスタ1506がオフする。第1のリセットトランジスタ15

06がオフしても電流パスが無ければ信号電荷蓄積部1510の電位(FD)はVDDに

保持される。次に、第1の転送スイッチ線1551の電位(TRF1)が高電位になり、

第1の転送トランジスタ1514がオンし、第1のフォトダイオード1512に照射され

ている光に応じた電流が、第1のフォトダイオード1512と第1の転送トランジスタ1

514に流れ、信号電荷蓄積部1510の電位(FD)が放電により低下する。第1の転

送スイッチ線1551の電位(TRF1)が低電位になると、第1の転送トランジスタ1

514がオフし、再び電流パスがなくなるため信号電荷蓄積部1510の電位(FD)は

保持される。この電位を第1の増幅トランジスタ1508を介して垂直出力線1570に

出力する。

【0184】

次に、再度第1のリセット線1561の電位(RST1)が高電位になり、第1のリセッ

トトランジスタ1506がオンする。これで信号電荷蓄積部1510の電位(FD)がV

DDまで持ち上がる。第1のリセット線1561の電位(RST1)が低電位になり、第

1のリセットトランジスタ1506がオフする。第1のリセットトランジスタ1506が

オフしても電流パスが無ければ信号電荷蓄積部1510の電位(FD)はVDDに保持さ

れる。次に、第2の転送スイッチ線1552の電位(TRF2)が高電位になり、第2の

転送トランジスタ1524がオンし、第2のフォトダイオード1522に照射されている

光に応じた電流が、第2のフォトダイオード1522と第2の転送トランジスタ1524

に流れ、信号電荷蓄積部1510の電位(FD)が放電により低下する。第2の転送スイ

ッチ線1552の電位(TRF2)が低電位になると、第2の転送トランジスタ1524

がオフし、再び電流パスがなくなるため信号電荷蓄積部1510の電位(FD)は保持さ

れる。この電位を第1の増幅トランジスタ1508を介して垂直出力線1570に出力す

る。この2つの動作で1ライン目の画素の出力が順に垂直出力線1570に出力される。

【0185】

2ライン目の駆動は、再び第1のリセット線1561の電位(RST1)が高電位になり

、第1のリセットトランジスタ1506がオンする。これで信号電荷蓄積部1510の電

位(FD)がVDDまで持ち上がる。第1のリセット線1561の電位(RST1)が低

電位になり、第1のリセットトランジスタ1506がオフする。第1のリセットトランジ

スタ1506がオフしても電流パスが無ければ信号電荷蓄積部1510の電位(FD)は

VDDに保持される。次に、第3の転送スイッチ線1553の電位(TRF3)が高電位

になり、第3の転送トランジスタ1534がオンし、第3のフォトダイオード1532に

照射されている光に応じた電流が、第3のフォトダイオード1532と第3の転送トラン

ジスタ1534に流れ、信号電荷蓄積部1510の電位(FD)が放電により低下する。

第3の転送スイッチ線1553の電位(TRF3)が低電位になると、第3の転送トラン

ジスタ1534がオフし、再び電流パスがなくなるため信号電荷蓄積部1510の電位は

保持される。この電位を第1の増幅トランジスタ1508を介して垂直出力線1570に

出力する。

【0186】

次に、再度第1のリセット線1561の電位(RST1)が高電位になり、第1のリセッ

トトランジスタ1506がオンする。これで信号電荷蓄積部1510の電位(FD)がV

DDまで持ち上がる。第1のリセット線1561の電位(RST1)が低電位になり、第

1のリセットトランジスタ1506がオフする。第1のリセットトランジスタ1506が

オフしても電流パスが無ければ信号電荷蓄積部1510の電位(FD)はVDDに保持さ

れる。次に、第4の転送スイッチ線1554の電位(TRF4)が高電位になり、第4の

転送トランジスタ1544がオンし、第4のフォトダイオード1542に照射されている

光に応じた電流が、第4のフォトダイオード1542と第4の転送トランジスタ1544

に流れ、信号電荷蓄積部1510の電位(FD)が放電により低下する。第4の転送スイ

ッチ線1554の電位(TRF4)が低電位になると、第4の転送トランジスタ1544

がオフし、再び電流パスがなくなるため信号電荷蓄積部1510の電位(FD)は保持さ

れる。この電位を第1の増幅トランジスタ1508を介して垂直出力線1570に出力す

る。次に、第2のリセット線1562の電位(RST2)を制御することで、1ライン目

及び2ライン目と同様に3ライン目及び4ライン目の駆動を順次行う。

【0187】

図22は、垂直、水平それぞれ2個ずつの画素について、リセット線、転送スイッチ線、

リセットトランジスタ、増幅トランジスタを兼用する転送スイッチ線共有型である。前述

した画素共有型に更に転送スイッチ線を共有させたもので、トランジスタ及び配線の数を

削減することで画素面積の縮小による微細化や、フォトダイオードの受光面積拡大によっ

てノイズを低減することができる。縦横に隣り合う4個の画素について、各画素の転送ト

ランジスタのドレイン側が電気的に接続され、信号電荷蓄積部が形成されており、信号電

荷蓄積部にはリセットトランジスタのソース及び増幅トランジスタのゲートが接続されて

いる。また、この構成は、垂直方向の位置する2つの転送トランジスタが転送スイッチ線

を共有していることで、水平方向だけでなく、垂直方向にも同時に動くトランジスタがあ

ることを特徴としている。

【0188】

転送スイッチ線共有型の動作を図23のタイミングチャートに従って説明する。1ライン

目、2ライン目の駆動は、まず第1のリセット線1665の電位(RST1)及び第2の

リセット線1666の電位(RST2)が高電位になり、第1のリセットトランジスタ1

616及び第2のリセットトランジスタ1626がオンする。これで第1の信号電荷蓄積

部1610の電位(FD1)及び第2の信号電荷蓄積部1620の電位(FD2)がVD

Dまで持ち上がる。第1のリセット線1665の電位(RST1)及び第2のリセット線

1666の電位(RST2)が低電位となり、第1のリセットトランジスタ1616及び

第2のリセットトランジスタ1626がオフする。第1のリセットトランジスタ1616

及び第2のリセットトランジスタ1626がオフしても電流パスがなければ第1の信号電

荷蓄積部1610の電位(FD1)及び第2の信号電荷蓄積部1620の電位(FD2)

はVDDに保持される。

【0189】

次に第1の転送スイッチ線1751の電位(TRF1)が高電位になり、第1の転送トラ

ンジスタ1614及び第3の転送トランジスタ1634がオンし、第1のフォトダイオー

ド1612及び第3のフォトダイオード1632に照射されている光に応じた電流が第1

のフォトダイオード1612及び第3のフォトダイオード1632と第1の転送トランジ

スタ1614及び第3の転送トランジスタ1634に流れ、第1の信号電荷蓄積部161

0の電位(FD1)及び第2の信号電荷蓄積部1620の電位(FD2)が放電により低

下する。第1の転送スイッチ線1751の電位(RST1)が低電位になると第1の転送

トランジスタ1614及び第3の転送トランジスタ1634がオフし、再び電流パスがな

くなるため第1の信号電荷蓄積部1610の電位(FD1)及び第2の信号電荷蓄積部1

620の電位(FD2)は保持される。これらの電位を第1の増幅トランジスタ1618

を介して第1の垂直出力線1675に出力し、第2の増幅トランジスタ1628を介して

第2の垂直出力線1676に出力する。

【0190】

次に、再度第1のリセット線1665の電位(RST1)及び第2のリセット線1666

の電位(RST2)が高電位になり、第1のリセットトランジスタ1616及び第2のリ

セットトランジスタ1626がオンする。これで第1の信号電荷蓄積部1610の電位(

FD1)及び第2の信号電荷蓄積部1620の電位(FD2)がVDDまで持ち上がる。

第1のリセット線1665の電位(RST1)及び第2のリセット線1666の電位(R

ST2)が低電位になり、第1のリセットトランジスタ1616及び第2のリセットトラ

ンジスタ1626がオフする。第1のリセットトランジスタ1616及び第2のリセット

トランジスタ1626がオフしても電流パスがなければ第1の信号電荷蓄積部1610の

電位(FD1)及び第2の信号電荷蓄積部1620の電位(FD2)はVDDに保持され

る。

【0191】

次に、第2の転送スイッチ線1752の電位(TRF2)の電位が高電位になり、第2の

転送トランジスタ1624及び第4の転送トランジスタ1644がオンし、第2のフォト

ダイオード1622及び第4のフォトダイオード1642に照射されている光に応じた電

流が第2のフォトダイオード1622及び第4のフォトダイオード1642と第2の転送

トランジスタ1624及び第4の転送トランジスタ1644に流れ、第1の信号電荷蓄積

部1610の電位(FD1)及び第2の信号電荷蓄積部1620の電位(FD2)が放電

により低下する。第2の転送スイッチ線1752の電位(TRF2)が低電位になると第

2の転送トランジスタ1624及び第4の転送トランジスタ1644がオフし、再び電流

パスがなくなるため第1の信号電荷蓄積部1610の電位(FD1)及び第2の信号電荷

蓄積部1620の電位(FD2)は保持される。これらの電位を第1の増幅トランジスタ

1618を介して第1の垂直出力線1675に出力し、第2の増幅トランジスタ1628

を介して第2の垂直出力線1676に出力する。これらの動作で1ライン目及び2ライン

目の画素の出力が順に第1の垂直出力線1675及び第2の垂直出力線1676に出力さ

れる。

【0192】

次に3ライン目、4ライン目の駆動について説明する。まず第2のリセット線1666の

電位(RST2)及び第3のリセット線1667の電位(RST3)が高電位となり、第

2のリセットトランジスタ1626及び第3のリセットトランジスタ1636がオンする

。これで第2の信号電荷蓄積部1620の電位(FD2)及び第3の信号電荷蓄積部16

30の電位(FD3)がVDDまで持ち上がる。第2のリセット線1666の電位(RS

T2)及び第3のリセット線1667の電位(RST3)が低電位になり、第2のリセッ

トトランジスタ1626及び第3のリセットトランジスタ1636がオフする。第2のリ

セットトランジスタ1626及び第3のリセットトランジスタ1636がオフしても電流

パスがなければ第2の信号電荷蓄積部1620の電位(FD1)及び第3の信号電荷蓄積

部1630の電位(FD2)はVDDに保持される。

【0193】

次に、第3の転送スイッチ線1753の電位(TRF3)の電位が高電位になり、第5の

転送トランジスタ1654及び第7の転送トランジスタ1674がオンし、第5のフォト

ダイオード1652及び第7のフォトダイオード1672に照射されている光に応じた電

流が第5のフォトダイオード1652及び第7のフォトダイオード1672と第5の転送

トランジスタ1654及び第7の転送トランジスタ1674に流れ、第2の信号電荷蓄積

部1620の電位(FD2)及び第3の信号電荷蓄積部1630の電位(FD3)が放電

により低下する。第3の転送スイッチ線1753の電位(TRF3)が低電位になると第

5の転送トランジスタ1654及び第7の転送トランジスタ1674がオフし、再び電流

パスがなくなるため第2の信号電荷蓄積部1620の電位(FD2)及び第3の信号電荷

蓄積部1630の電位(FD3)は保持される。これらの電位を第2の増幅トランジスタ

1628を介して第2の垂直出力線1676に出力し、第3の増幅トランジスタ1638

を介して第1の垂直出力線1675に出力する。

【0194】

次に、第2のリセット線1666の電位(RST2)及び第3のリセット線1667の電

位(RST3)が高電位となり、第2のリセットトランジスタ1626及び第3のリセッ

トトランジスタ1636がオンする。これで第2の信号電荷蓄積部1620の電位(FD

2)及び第3の信号電荷蓄積部1630の電位(FD3)がVDDまで持ち上がる。第2

のリセット線1666の電位(RST2)及び第3のリセット線1667の電位(RST

3)が低電位となり、第2の第2のリセットトランジスタ1626及び第3のリセットト

ランジスタ1636がオフする。第2のリセットトランジスタ1626及び第3のリセッ

トトランジスタ1636がオフしても電流パスがなければ第2の信号電荷蓄積部1620

の電位(FD2)及び第3の信号電荷蓄積部1630の電位(FD3)はVDDに保持さ

れる。

【0195】

次に、第4の転送スイッチ線1754の電位(TRF4)の電位が高電位となり、第6の

転送トランジスタ1664及び第8の転送トランジスタ1684がオンし、第6のフォト

ダイオード1662及び第8のフォトダイオード1682に照射されている光に応じた電

流が第6のフォトダイオード1662及び第8のフォトダイオード1682と第6の転送

トランジスタ1664及び第8の転送トランジスタ1684に流れ、第2の信号電荷蓄積

部1620の電位(FD2)及び第3の信号電荷蓄積部1630電位(FD3)が放電に

より低下する。第4の転送スイッチ線1754の電位(TRF4)が低電位になると第6

の転送トランジスタ1664及び第8の転送トランジスタ1684がオフし、再び電流パ

スがなくなるため第2の信号電荷蓄積部1620の電位(FD2)及び第3の信号電荷蓄

積部1630の電位(FD3)は保持される。これらの電位を第2の増幅トランジスタ1

628を介して第2の垂直出力線1676に出力し、第3の増幅トランジスタ1638を

介して第1の垂直出力線1675に出力する。これらの動作で3ライン目、4ライン目の

画素の出力が順に第2の垂直出力線1676及び第1の垂直出力線1675に出力される

。次に第3のリセット線1667の電位(RST3)及び第4のリセット線の電位(RS

T4)を制御することで、3ライン目及び4ライン目と同様に5ライン目及び6ライン目

の駆動を順次行う。

【0196】

図24はCMOSイメージセンサ全体の図である。画素部2000を有する画素マトリク

ス2100の両側にリセット端子駆動回路2020、転送端子駆動回路2040が配置さ

れる。図24では画素マトリクス2100の両側に該駆動回路を配置しているが、片側に

該駆動回路を配置しても良い。また、該駆動回路からの信号を出力する配線に対して、垂

直方向に垂直出力線駆動回路2060が配置される。リセット端子駆動回路2020及び

転送端子駆動回路2040は、ロウ(低電位)及びハイ(高電位)の2値出力の駆動回路

であるので、図25で示す様にシフトレジスタ2200とバッファ回路2300の組み合

わせで駆動することができる。これらの駆動回路はバルクトランジスタ、または薄膜トラ

ンジスタで構成することができるが、相補型(CMOS)トランジスタの形成が可能なシ

リコン半導体を用いたバルクトランジスタを用いることが好ましい。

【0197】

垂直出力線駆動回路2060は、図26に示すようにシフトレジスタ2210とバッファ

回路2310とアナログスイッチ2400によって構成することができる。各垂直出力線

2120をアナログスイッチ2400によって選択し、映像出力線2500に映像信号を

出力する。アナログスイッチ2400はシフトレジスタ2210とバッファ回路2310

で順次選択していくものとする。垂直出力線駆動回路2060はバルクトランジスタ、ま

たは薄膜トランジスタで構成することができるが、相補型トランジスタの形成が可能なシ

リコン半導体を用いたバルクトランジスタを用いることが好ましい。

【0198】

図27にシフトレジスタとバッファ回路の例を示す。図27に示すのはクロックドインバ

ーターによって構成されたシフトレジスタ2220とインバータによって構成されたバッ

ファ回路2320の例である。シフトレジスタ、バッファ回路はこの回路に限定されるも

のではなく、リセット端子駆動回路2020、転送端子駆動回路2040、垂直出力線駆

動回路2060も上記構成に限定されるものではない。

【0199】

上記実施の形態に係る固体撮像素子は、さまざまな電子機器(遊技機も含む)に適用する

ことができる。例えば、デジタルカメラ、デジタルビデオカメラ、携帯電話、携帯型ゲー

ム機、携帯情報端末など、画像情報を取得する手段を有する電子機器に用いることができ

る。

【0200】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【符号の説明】

【0201】

100 単結晶シリコン基板

101 転送トランジスタ

102 酸化物半導体層

104 ソース電極

106 ドレイン電極

108 ゲート電極

110 光電変換素子

114 p型領域

116 信号電荷蓄積部

118 ゲート絶縁層

121 リセットトランジスタ

122 酸化物半導体層

124 ソース電極

126 ドレイン電極

128 ゲート電極

131 増幅トランジスタ

136 ゲート絶縁層

138 ゲート電極

140 絶縁膜

142 保護絶縁層

151 配線層

132a n型領域

132b n型領域

138a 導電層

138b 導電層

201 トランジスタ

204 ソース電極

210 光電変換素子

301 トランジスタ

304 ソース電極

305 バッファ層

306 ドレイン電極

310 光電変換素子

112 n型領域

401 転送トランジスタ

421 リセットトランジスタ

431 増幅トランジスタ

441 絶縁層

450 窒素雰囲気下

501 転送トランジスタ

510 光電変換素子

516 信号電荷蓄積部

521 リセットトランジスタ

531 増幅トランジスタ

540 容量電極

541 絶縁膜

600 レンズ

602 カラーフィルタ

604 配線層

606 層間絶縁膜

608 光電変換素子

610 レンズ

612 カラーフィルタ

618 光電変換素子

1002 フォトダイオード

1004 転送トランジスタ

1006 リセットトランジスタ

1008 増幅トランジスタ

1010 信号電荷蓄積部

1100 電源線

1110 リセット電源線

1120 垂直出力線

1210 信号電荷蓄積部

1212 フォトダイオード

1214 転送トランジスタ

1216 リセットトランジスタ

1218 増幅トランジスタ

1220 垂直出力線

1240 リセット線

1250 転送スイッチ線

1340 リセット線

1350 転送スイッチ線

1406 リセットトランジスタ

1408 増幅トランジスタ

1410 信号電荷蓄積部

1412 フォトダイオード

1414 転送トランジスタ

1422 フォトダイオード

1424 転送トランジスタ

1432 フォトダイオード

1434 転送トランジスタ

1442 フォトダイオード

1444 転送トランジスタ

1451 転送スイッチ線

1452 転送スイッチ線

1453 転送スイッチ線

1454 転送スイッチ線

1461 リセット線

1470 垂直出力線

1506 リセットトランジスタ

1508 増幅トランジスタ

1510 信号電荷蓄積部

1512 フォトダイオード

1514 転送トランジスタ

1522 フォトダイオード

1524 転送トランジスタ

1532 フォトダイオード

1534 転送トランジスタ

1542 フォトダイオード

1544 転送トランジスタ

1551 転送スイッチ線

1552 転送スイッチ線

1553 転送スイッチ線

1554 転送スイッチ線

1561 リセット線

1562 リセット線

1570 垂直出力線

1610 信号電荷蓄積部

1612 フォトダイオード

1614 転送トランジスタ

1616 リセットトランジスタ

1618 増幅トランジスタ

1620 信号電荷蓄積部

1622 フォトダイオード

1624 転送トランジスタ

1626 リセットトランジスタ

1628 増幅トランジスタ

1630 信号電荷蓄積部

1632 フォトダイオード

1634 転送トランジスタ

1636 リセットトランジスタ

1638 増幅トランジスタ

1642 フォトダイオード

1644 転送トランジスタ

1652 フォトダイオード

1654 転送トランジスタ

1662 フォトダイオード

1664 転送トランジスタ

1665 リセット線

1666 リセット線

1667 リセット線

1672 フォトダイオード

1674 転送トランジスタ

1675 垂直出力線

1676 垂直出力線

1682 フォトダイオード

1684 転送トランジスタ

1751 転送スイッチ線

1752 転送スイッチ線

1753 転送スイッチ線

1754 転送スイッチ線

2000 画素部

2020 リセット端子駆動回路

2040 転送端子駆動回路

2060 垂直出力線駆動回路

2100 画素マトリクス

2120 各垂直出力線

2200 シフトレジスタ

2210 シフトレジスタ

2220 シフトレジスタ

2300 バッファ回路

2310 バッファ回路

2320 バッファ回路

2400 アナログスイッチ

2500 映像出力線

【技術分野】

【0001】

本発明の一形態は、酸化物半導体を用いた電界効果型トランジスタを有する半導体装置に

関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置

全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタを構成する技

術が注目されている。薄膜トランジスタに適用可能な半導体薄膜としては、シリコン系半

導体材料が公知であるが、その他の材料として酸化物半導体が注目されている。

【0004】

酸化物半導体の材料としては、酸化亜鉛または酸化亜鉛を含む材料が知られている。そし

て、電子キャリア濃度が1018/cm3未満である非晶質酸化物(酸化物半導体)で形

成された薄膜トランジスタが開示されている(特許文献1乃至3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−165527号公報

【特許文献2】特開2006−165528号公報

【特許文献3】特開2006−165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

一方で、表示装置に近い構成でありながらも、優れた電気特性が要求される固体撮像素子

などでは、SOI基板やバルクの単結晶シリコン基板を用いた電界効果型トランジスタが

一般的に用いられている。

【0007】

しかしながら、単結晶シリコンを用いた電界効果型トランジスタであっても理想的な電気

特性を有しているとは言えず、例えばオフ電流(リーク電流などとも呼ぶ)は、実質的に

ゼロと言えるほど小さいものではない。また、シリコンは温度特性の変化が比較的大きい

材料でもあり、特にオフ電流は変化しやすい。従って、固体撮像素子など電荷保持型の半

導体装置を構成する場合には、周囲の環境に左右されず、十分な電位保持期間の確保が可

能であり、よりオフ電流が低減されたデバイスの開発が望まれている。

【0008】

そこで、開示する本発明の一態様は、安定した電気特性(例えば、オフ電流が極めて低減

されている)を有する薄膜トランジスタを含む固体撮像素子を提供することを目的とする

。

【課題を解決するための手段】

【0009】

本発明の一態様は、シリコン半導体を用いて形成された光電変換素子及び増幅トランジス

タを少なくとも有し、リセットトランジスタ及び転送トランジスタが酸化物半導体で形成

された画素を有する固体撮像素子に関する。

【0010】

また、本発明の一態様における酸化物半導体は、電子供与体(ドナー)となる不純物を除

去することで、真性または実質的に真性な半導体であって、シリコン半導体よりもエネル

ギーギャップが大きい。

【0011】

すなわち、本発明の一態様は、酸化物半導体に含まれる水素の濃度が、二次イオン質量分

析法(SIMS:Secondary Ion Mass Spectroscopy)

における最低値で5×1019/cm3以下、好ましくは5×1018/cm3以下、よ

り好ましくは5×1017/cm3以下、または1×1016/cm3未満として、酸化

物半導体に含まれる水素若しくはOH基を除去し、キャリア濃度を1×1014/cm3

未満、好ましくは1×1012/cm3以下とした酸化物半導体膜でチャネル領域が形成

される薄膜トランジスタを有する固体撮像素子である。

【0012】

酸化物半導体のエネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ま

しくは3eV以上として、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度

を1×1014/cm3以下、好ましくは1×1012/cm3以下となるようにする。

【0013】

この様に高純度化された酸化物半導体は、薄膜トランジスタのチャネル形成領域に用いる

ことで、電気特性がノーマリーオフを呈し、1Vから10Vのドレイン電圧において、そ

のオフ電流は、1×10−13A以下、または100aA/μm(μmは、薄膜トランジ

スタのチャネル幅)以下、好ましくは10aA/μm以下、更に好ましくは1aA/μm

以下となる。

【0014】

本明細書で開示する本発明の一態様は、シリコン半導体基板に埋設された光電変換素子部

と、光電変換素子部と転送トランジスタを介して電気的に接続される信号電荷蓄積部と、

信号電荷蓄積部と電気的に接続されるリセットトランジスタと、信号電荷蓄積部にゲート

電極が電気的に接続される増幅トランジスタと、を有し、転送トランジスタ及びリセット

トランジスタのチャネル形成領域は酸化物半導体で形成されており、増幅トランジスタの

チャネル形成領域はシリコン半導体で形成された画素部を有することを特徴とする半導体

装置である。

【0015】

また、上記増幅トランジスタも酸化物半導体を用いた薄膜トランジスタで形成しても良い

。更に上記画素部には、選択トランジスタが設けられていても良い。また、画素部と接続

される周辺回路部は、シリコン半導体を用いたバルクトランジスタで相補型トランジスタ

の構成とすることが好ましい。

【0016】

本明細書等において「電極」や「配線」という用語は、これらの構成要素を機能的に限定

するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、「

配線」は「電極」の一部として用いられることがある。更に、「電極」や「配線」という

用語は、複数の「電極」や「配線」が一体となって形成されている場合などをも含む。

【0017】

また、「SOI基板」には、シリコンウエハなどの半導体基板に限らず、ガラス基板や石

英基板、サファイア基板、金属基板などの非半導体基板も含まれる。つまり、絶縁体基板

上に半導体材料からなる層を有するものも、広く「SOI基板」に含まれる。さらに、本

明細書等において、「半導体基板」は、半導体材料のみからなる基板を指すに留まらず、

半導体材料を含む基板全般を指すものとする。つまり、本明細書等においては「SOI基

板」も「半導体基板」に含まれる。

【発明の効果】

【0018】

本発明の一形態によれば、オフ電流が極めて小さい酸化物半導体を用いた薄膜トランジス

タをリセットトランジスタ及び転送トランジスタの両方に用いることで信号電荷蓄積部の

電位が一定に保たれ、ダイナミックレンジを向上させることができる。また、周辺回路に

相補型トランジスタが作製可能なシリコン半導体を用いることで動作が高速で、低消費電

力の半導体装置を作製することができる。

【図面の簡単な説明】

【0019】

【図1】固体撮像素子の画素の構成について説明する断面図。

【図2】固体撮像素子の画素の構成について説明する断面図。

【図3】固体撮像素子の画素の構成について説明する断面図。

【図4】固体撮像素子の作製方法について説明する断面図。

【図5】固体撮像素子の作製方法について説明する断面図。

【図6】酸化物半導体を用いた薄膜トランジスタのVg−Id特性を示す図。

【図7】酸化物半導体を用いた薄膜トランジスタの写真。

【図8】酸化物半導体を用いた薄膜トランジスタのVg−Id特性(温度特性)示す図。

【図9】酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図。

【図10】図9に示すA−A’断面におけるエネルギーバンド図(模式図)。

【図11】図9に示すB−B’断面におけるエネルギーバンド図(模式図)であって、(A)ゲート(G1)に正の電位(+VG)が印加された状態を示し、(B)ゲート(G1)に負の電位(−VG)が印加された状態を示す図。

【図12】真空準位と金属の仕事関数(φM)、酸化物半導体の電子親和力(χ)の関係を示す図。

【図13】固体撮像素子の画素の構成について説明する図。

【図14】固体撮像素子の画素の動作について説明する図。

【図15】フォトダイオードの動作について説明する図。

【図16】固体撮像素子の画素の構成について説明する図。

【図17】固体撮像素子の画素の動作について説明する図。

【図18】固体撮像素子の画素の構成について説明する図。

【図19】固体撮像素子の画素の動作について説明する図。

【図20】固体撮像素子の画素の構成について説明する図。

【図21】固体撮像素子の画素の動作について説明する図。

【図22】固体撮像素子の画素の構成について説明する図。

【図23】固体撮像素子の画素の動作について説明する図。

【図24】固体撮像素子の構成について説明する図。

【図25】リセット端子駆動回路及び転送端子駆動回路の構成について説明する図。

【図26】垂直出力線駆動回路の構成について説明する図。

【図27】シフトレジスタとバッファ回路の一例を示す図。

【図28】固体撮像素子の画素の構成について説明する断面図。

【発明を実施するための形態】

【0020】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0021】

なお、本明細書で説明する各図において、各構成要素や領域の大きさ、及び層の厚さ等は

、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定され

ない。

【0022】

なお、本明細書にて用いる第1、第2、第3、等の用語は、構成要素の混同を避けるため

に付したものであり、順序などを限定するものではない。そのため、例えば、「第1の」

を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0023】

(実施の形態1)

本発明の一態様は、金属絶縁物半導体素子、所謂MIS(Metal Insulato

r Semiconductor)トランジスタを用いた半導体装置である。本明細書で

は、チャネル形成領域に薄膜の半導体を用いた素子を薄膜トランジスタと称し、チャネル

形成領域にバルクの半導体を用いた素子をバルクトランジスタと称する。ただし、SOI

(Silicon on Insulator)基板に形成されている半導体層は薄膜と

も言えるが、本明細書では該半導体層で形成したトランジスタはバルクトランジスタの一

種とする。

【0024】

本発明の一態様における薄膜トランジスタを含む固体撮像素子の画素を構成する例を以下

に説明する。本実施の形態では、一例として、固体撮像素子における画素が有する薄膜ト

ランジスタと、当該薄膜トランジスタに接続された光電変換素子及びシリコン半導体で形

成されたバルクトランジスタについて説明する。なお画素とは、固体撮像素子に設けられ

た各素子、例えば光電変換素子、トランジスタ、及び配線等からなり、電気的な信号の入

出力で画像を出力させるための素子で構成される素子群のことをいう。

【0025】

なお画素は、図28(A)の断面図に示すように基板表面側に形成したレンズ600、カ

ラーフィルタ602、及び層間絶縁膜606等を通して入射光を光電変換素子608に受

光させる構造とすることができる。ただし、点線枠で囲んだ領域に示すように、矢印で示

す光路の一部が配線層604の一部によって遮光されてしまうことがあり、図28(B)

に示すように基板裏面側にレンズ610及びカラーフィルタ612を形成して入射光を光

電変換素子618に効率良く受光させる構造としても良い。

【0026】

また、AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されてい

る場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、

対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとす

る。

【0027】

本発明の一態様である固体撮像素子の画素部分の一例を図1に断面図で示す。図1は転送

トランジスタ101及びリセットトランジスタ121に酸化物半導体を有する薄膜トラン

ジスタを用いた例で、増幅トランジスタ131は、単結晶シリコン基板100に形成され

たnチャネル型のバルクトランジスタで形成している。光電変換素子110はn型領域1

12と薄いp型領域114を含むフォトダイオードであり、転送トランジスタ101のソ

ース電極104に接続される。また、転送トランジスタ101のドレイン電極下方及びリ

セットトランジスタのソース電極下方には信号電荷蓄積部116(フローティングディフ

ュージョンとも呼ぶ)が形成される。転送トランジスタ101及びリセットトランジスタ

121は、酸化物半導体層がチャネル領域となるトップゲート構造をしており、転送トラ

ンジスタ101のドレイン電極106がリセットトランジスタのソース電極124と電気

的に接続される。増幅トランジスタ131は、n型領域132a、132bとゲート電極

138を含むnチャネル型のバルクトランジスタであり、図示はしていないが、増幅トラ

ンジスタのゲート電極138は、信号電荷蓄積部116と電気的に接続されている。

【0028】

なお、図1の構造において、バルクトランジスタのゲート絶縁層136は、薄膜トランジ

スタである転送トランジスタ101及びリセットトランジスタ121の下地絶縁層を兼ね

ており、信号電荷蓄積部116は、ゲート絶縁層136を誘電体として容量を形成してい

る。また、薄膜トランジスタのゲート絶縁層118は、バルクトランジスタの層間絶縁層

の一部として機能する。

【0029】

酸化物半導体をチャネル形成領域に用いた薄膜トランジスタは、トップゲート型を例とし

て示したが、逆スタガ構造などのボトムゲート型を用いても良い。また、光電変換素子1

10に光を照射する必要があるため、転送トランジスタ101のソース電極の一部を光電

変換素子110の受光部に接続させる例を挙げたが、ソース電極を透光性導電材料で形成

し、光電変換素子110との接続の状態を変えても良い。例えば、図2(A)に示すよう

に、透光性導電材料で形成したソース電極204を有するトランジスタ201を転送トラ

ンジスタとして用いれば、光電変換素子210の受光面の一部または全面に接続すること

ができる。また、図2(B)に示す様に光電変換素子310への光路を確保できるように

、抵抗の低い金属層をソース電極304及びドレイン電極306とし、透光性導電材料層

をバッファ層305、307として積層したトランジスタ301を転送トランジスタとし

て用いても良い。

【0030】

光電変換素子としては、p型単結晶シリコン基板(SOIの場合は、p型単結晶シリコン

層)にn型領域を形成し、その上部に薄いp型領域を形成した所謂埋め込み型フォトダイ

オードを形成する。フォトダイオードの表面にp型領域を形成することで表面で発生する

暗電流、すなわちノイズを低減することができる。

【0031】

また、上記では単結晶半導体基板を用いた例を示したが、SOI構造の基板であっても良

い。また、バルクトランジスタの構造はこれに限らず、ゲート電極端にサイドウォールを

設けたLDD(Lightly Doped Drain)構造やソースドレイン領域の

一部に低抵抗のシリサイド等を形成した構造であっても良い。

【0032】

また、上記画素部には増幅トランジスタ131と電気的に接続される選択トランジスタを

設けても良い。増幅トランジスタ及び選択トランジスタは共にシリコン半導体、酸化物半

導体のどちらを用いても形成することができる。ただし、増幅トランジスタは、より増幅

率の高いシリコン半導体層を用いたバルクトランジスタで形成することが好ましい。

【0033】

また、バルクトランジスタの上部に絶縁層を設け、その上に薄膜トランジスタを設けるこ

ともできる。例えば、薄膜トランジスタで形成する転送トランジスタ、またはリセットト

ランジスタのどちらか一方をバルクトランジスタで形成する増幅トランジスタの上部に設

ければ、一画素につき必要なトランジスタの面積が2/3程度となり、集積度の向上やフ

ォトダイオードの受光面積を増加させることができ、ノイズを低減させることもできる。

図3(A)はその一例である。薄膜トランジスタで形成された転送トランジスタ401と

バルクトランジスタで形成された増幅トランジスタ431が並設されており、その上部に

絶縁層441を介して薄膜トランジスタで形成されたリセットトランジスタ421が設け

られた構造をしている。また、図3(B)は、下層に光電変換素子510とバルクトラン

ジスタで形成された増幅トランジスタ531を形成し、絶縁膜541を介して上層に薄膜

トランジスタで形成された転送トランジスタ501とリセットトランジスタ521を設け

た例であり、光電変換素子及びバルクトランジスタと薄膜トランジスタの作製工程が分離

できるため、工程の制御が容易となる。ただし、信号電荷蓄積部516を形成するための

容量電極540を設けておくことが好ましい。

【0034】

以上の薄膜トランジスタとバルクトランジスタを組み合わせる構成により、信号電荷蓄積

部の電位の保持機能を高め、ダイナミックレンジの広い固体撮像素子の画素部を形成する

ことができる。ただし、この本発明の一態様を実現するには極めてオフ電流の低い薄膜ト

ランジスタを用いることが好ましい。次にその作製方法を説明する。

【0035】

本発明の一態様は、単結晶シリコン半導体を用いたバルクトランジスタと極めて電気特性

の良好な酸化物半導体を用いた薄膜トランジスタを組み合わせることにより固体撮像素子

の画素部を形成するものである。従って、酸化物半導体を用いた薄膜トランジスタの作製

方法を中心に詳細な説明を行う。

【0036】

一例として、図1の構造の作製方法を図4及び図5の断面図を用いて説明する。まず、P

型の単結晶シリコン基板100に絶縁膜140(フィールド酸化膜とも言う)で分離した

素子形成領域を形成する。素子分離領域の形成は、LOCOS法(Local Oxid

ation of Silicon)法)やSTI法(Shallow Trench

Isolation)等を用いることができる。

【0037】

ここで基板は単結晶シリコン基板に限らず、SOI(Silicon on Insul

ator)基板等を用いることもできる。

【0038】

なお、本実施の形態では、埋め込み型のフォトダイオード及びnチャネル型のバルクトラ

ンジスタを用いる構成であるため、p型単結晶シリコン基板を用いるが、pウェルを形成

すればn型単結晶シリコン基板を用いることもできる。

【0039】

次に、素子形成領域を覆うようにゲート絶縁層136を形成する。例えば、熱処理を行い

単結晶シリコン基板100に設けられた素子形成領域の表面を酸化させることにより酸化

シリコン膜を形成することができる。また、熱酸化法により酸化シリコン膜を形成した後

に、窒化処理を行うことによって酸化シリコン膜の表面を窒化させることにより、酸化シ

リコン膜と酸窒化シリコン膜との積層構造で形成してもよい。

【0040】

他の方法としては、例えば、単結晶シリコン基板100に設けられた素子形成領域の表面

に高密度プラズマ処理により酸化処理または窒化処理を行うことにより、ゲート絶縁層1

36として酸化シリコン膜または窒化シリコン膜で形成することができる。また、高密度

プラズマ処理により素子形成領域の表面に酸化処理を行った後に、再度高密度プラズマ処

理を行うことによって窒化処理を行ってもよい。この場合、素子形成領域の表面に接して

酸化シリコン膜が形成され、当該酸化シリコン膜上に酸窒化シリコン膜が形成され、ゲー

ト絶縁層136は酸化シリコン膜と酸窒化シリコン膜が積層された層となる。

【0041】

次に、ゲート絶縁層136を覆うように導電層を形成する。ここでは、導電層138aと

導電層138bを順に積層して形成する。もちろん、導電層は、単層または2層以上の積

層構造で形成してもよい。

【0042】

導電層138a、138bとしては、タンタル(Ta)、タングステン(W)、チタン(

Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニ

オブ(Nb)等から選択された元素、またはこれらの元素を主成分とする合金材料や化合

物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成するこ

ともできる。他にも、リン等の不純物元素をドーピングした多結晶シリコンに代表される

半導体材料により形成することもできる。

【0043】

ここでは、導電層138aとして窒化タンタルを用いて形成し、その上に導電層138b

としてタングステンを用いて積層構造で設ける。また、他にも、導電層138aとして、

窒化タングステン、窒化モリブデンまたは窒化チタンから選ばれた単層または積層膜を用

い、導電層138bとして、タンタル、モリブデン、チタンから選ばれた単層または積層

膜を用いることができる。

【0044】

次に、積層して設けられた導電層138a、138bを選択的にエッチングして除去する

ことによって、ゲート絶縁層136の上方の一部に導電層138a、138bを残存させ

、ゲート電極138を形成する。

【0045】

次に、素子形成領域以外を覆うようにレジストマスクを選択的に形成し、当該レジストマ

スク及びゲート電極138をマスクとして不純物元素を導入することによってn型領域1

32a及び132bの不純物領域を形成する。ここでは、nチャネル型のバルクトランジ

スタを形成するため、不純物元素としては、n型を付与する不純物元素であるリン(P)

やヒ素(As)等を用いることができる。

【0046】

次に、光電変換素子であるフォトダイオードを作製するためにレジストマスクを選択的に

形成する。まず、n型を付与する不純物元素であるリン(P)やヒ素(As)をp型単結

晶シリコン基板に導入しpn接合を形成した後、p型を付与する不純物元素であるホウ素

(B)をn型領域の表層に導入することで埋め込み型のフォトダイオードを形成すること

ができる。

【0047】

この段階で、図4(A)の右側に示すバルクトランジスタと左側に示すフォトダイオード

の構造が完成する。

【0048】

次に酸化物半導体層をチャネル領域とする薄膜トランジスタの作製方法について説明する

。

【0049】

本実施の形態では、既に単結晶シリコン基板100に設けられているバルクトランジスタ

のゲート絶縁層136上に薄膜トランジスタを形成する。つまり、薄膜トランジスタの下

地膜とバルクトランジスタのゲート絶縁層とを兼ねることができる。ただし、次の方法を

用いて絶縁層を成膜し、下地膜を積層としても良い。

【0050】

酸化物半導体層と接する絶縁層は、酸化シリコン層、酸化窒化シリコン層、酸化アルミニ

ウム層、または酸化窒化アルミニウム層などの酸化物絶縁層を用いると好ましい。絶縁層

の形成方法としては、プラズマCVD法またはスパッタ法等を用いることができるが、絶

縁層中に水素が多量に含まれないようにするためには、スパッタ法で絶縁層を成膜するこ

とが好ましい。

【0051】

絶縁層として、スパッタ法により酸化シリコン層を形成する例を説明する。単結晶シリコ

ン基板100を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタガ

スを導入しシリコンターゲットを用いて、単結晶シリコン基板100に絶縁層として、酸

化シリコン層を成膜する。また単結晶シリコン基板100は室温でもよいし、加熱されて

いてもよい。

【0052】

例えば、石英(好ましくは合成石英)をターゲットとして用い、基板温度108℃、基板

とターゲットの間との距離(T−S間距離)を60mm、圧力0.4Pa、高周波電源1

.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:

1)雰囲気下でRFスパッタ法により酸化シリコン層を成膜する。膜厚は100nmとす

る。なお、石英に代えてシリコンを酸化シリコン層を成膜するためのターゲットとして用

いることができる。このとき、スパッタガスとしては、酸素または、酸素及びアルゴンの

混合ガスを用いて行う。

【0053】

この場合において、処理室内の残留水分を除去しつつ絶縁層を成膜することが好ましい。

絶縁層に水素、水酸基又は水分が含まれないようにするためである。

【0054】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。

例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが

好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであ

ってもよい。クライオポンプを用いて排気した処理室は、例えば、水素原子や、水(H2

O)など水素原子を含む化合物等が排気されるため、当該処理室で成膜し絶縁層に含まれ

る不純物の濃度を低減することができる。

【0055】

絶縁層を成膜する際に用いるスパッタガスは水素、水、水酸基または水素化物などの不純

物がppm程度の濃度またはppb程度の濃度まで除去された高純度ガスを用いることが

好ましい。

【0056】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法、DCスパッタ法、

さらにパルス的にバイアスを与えるパルスDCスパッタ法がある。RFスパッタ法は主に

絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に導電膜を成膜する場合に用いら

れる。

【0057】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ

装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種

類の材料を同時に放電させて成膜することもできる。

【0058】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置

や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ

を用いるスパッタ装置がある。

【0059】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分

とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に

基板にも電圧をかけるバイアススパッタ法もある。

【0060】

また、絶縁層は積層構造でもよく、例えば、基板側から窒化シリコン層、窒化酸化シリコ

ン層、窒化アルミニウム層、または窒化酸化アルミニウム層などの窒化物絶縁層と、上記

酸化物絶縁層との積層構造としてもよい。

【0061】

例えば、酸化シリコン層と基板との間に水素及び水分が除去された高純度窒素を含むスパ

ッタガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜する。この場合にお

いても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成

膜することが好ましい。

【0062】

窒化シリコン層を形成する場合も、成膜時に基板を加熱してもよい。

【0063】

絶縁層として窒化シリコン層と酸化シリコン層とを積層する場合、窒化シリコン層と酸化

シリコン層を同じ処理室において、共通のシリコンターゲットを用いて成膜することがで

きる。先に窒素を含むスパッタガスを導入して、処理室内に装着されたシリコンターゲッ

トを用いて窒化シリコン層を形成し、次にスパッタガスを酸素を含むスパッタガスに切り

替えて同じシリコンターゲットを用いて酸化シリコン層を成膜する。窒化シリコン層と酸

化シリコン層とを大気に曝露せずに連続して形成することができるため、窒化シリコン層

表面に水素や水分などの不純物が吸着することを防止することができる。

【0064】

次いで、絶縁層上(本実施の形態ではゲート絶縁層136上)に、膜厚2nm以上200

nm以下の酸化物半導体膜をスパッタ法で形成する。

【0065】

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、

成膜の前処理として、スパッタ装置の予備加熱室で単結晶シリコン基板100を予備加熱

し、該基板に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、

予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は

省略することもできる。また、この予備加熱は、後に形成する薄膜トランジスタのゲート

絶縁層118の成膜前に行ってもよいし、後に形成するソース電極及びドレイン電極とな

る導電層の成膜前に行っても良い。

【0066】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズ

マを発生させる逆スパッタを行い、絶縁層の表面に付着しているゴミを除去することが好

ましい。逆スパッタとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加し、

イオン化したアルゴンを基板に衝突させて表面を改質する方法である。なお、アルゴンに

代えて窒素、ヘリウム、酸素などを用いてもよい。

【0067】

酸化物半導体膜はスパッタ法により成膜する。酸化物半導体膜としては、四元系金属酸化

物であるIn−Sn−Ga−Zn−O膜や、三元系金属酸化物であるIn−Ga−Zn−

O膜、In−Sn−Zn−O膜、In−Al−Zn−O膜、Sn−Ga−Zn−O膜、A

l−Ga−Zn−O膜、Sn−Al−Zn−O膜や、二元系金属酸化物であるIn−Zn

−O膜、Sn−Zn−O膜、Al−Zn−O膜、Zn−Mg−O膜、Sn−Mg−O膜、

In−Mg−O膜や、In−O膜、Sn−O膜、Zn−O膜などの酸化物半導体膜を用い

ることができる。また、上記酸化物半導体膜にSiO2を含んでもよい。

【0068】

また、酸化物半導体膜は、InMO3(ZnO)m(m>0)で表記される薄膜を用いる

ことができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の

金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及び

Coなどがある。InMO3(ZnO)m(m>0)で表記される構造の酸化物半導体膜

のうち、MとしてGaを含む構造の酸化物半導体を、In−Ga−Zn−O酸化物半導体

とよび、その薄膜をIn−Ga−Zn−O膜ともよぶこととする。

【0069】

本実施の形態では、酸化物半導体膜をIn−Ga−Zn−O系金属酸化物ターゲットを用

いてスパッタ法により成膜する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン

)雰囲気下、酸素雰囲気下、またはそれらの混合雰囲気下においてスパッタ法により形成

することができる。

【0070】

酸化物半導体膜を成膜する際に用いるスパッタガスは水素、水、水酸基または水素化物な

どの不純物がppm程度の濃度またはppb程度の濃度まで除去された高純度ガスを用い

ることが好ましい。

【0071】

酸化物半導体膜をスパッタ法で作製するためのターゲットとしては、酸化亜鉛を主成分と

する金属酸化物のターゲットを用いることができる。例えば、組成比として、In2O3

:Ga2O3:ZnO=1:1:1[mol数比]の金属酸化物ターゲットを用いれば良

い。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の金属酸化物タ

ーゲットを用いてもよい。金属酸化物ターゲットの充填率は90%以上100%以下、好

ましくは95%以上99.9%である。充填率の高い金属酸化物ターゲットを用いること

により、成膜した酸化物半導体膜は緻密な膜となる。

【0072】

酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分

を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲット

として絶縁層上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、

吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、

チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ター

ボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気

した処理室は、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好まし

くは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体

膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱して

もよい。

【0073】

成膜条件の一例としては、基板温度室温、基板とターゲットの間との距離を110mm、

圧力0.4Pa、直流(DC)電源0.5kW、酸素及びアルゴン(酸素流量15scc

m:アルゴン流量30sccm)雰囲気下の条件が適用される。なお、パルス直流(DC

)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減で

き、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30

nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応

じて適宜厚みを選択すればよい。

【0074】

次いで、酸化物半導体膜を第1のフォトリソグラフィ工程及びエッチング工程により島状

の酸化物半導体層102及び122に加工する(図4(B)参照)。ここで、酸化物半導

体層102は第1の薄膜トランジスタのチャネル領域を形成する半導体層であり、酸化物

半導体層122は第2の薄膜トランジスタのチャネル領域を形成する半導体層である。

【0075】

なお、島状の酸化物半導体層を形成するためのレジストマスクはインクジェット法で形成

してもよい。インクジェット法ではフォトマスクを使用しないため、製造コストを低減で

きる。また、ここでの酸化物半導体膜のエッチングは、ドライエッチングでもウェットエ

ッチングでもよく、両方を用いてもよい。

【0076】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例え

ば塩素(Cl2)、塩化硼素(BCl3)、塩化珪素(SiCl4)、四塩化炭素(CC

l4)など)が好ましい。

【0077】

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(S

F6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(H

Br)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガ

スを添加したガス、などを用いることができる。

【0078】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etch

ing)法や、ICP(Inductively Coupled Plasma:誘導

結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングでき

るように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加さ

れる電力量、基板側の電極温度等)を適宜調節する。

【0079】

ウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液、ア

ンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2)な

どを用いることができる。また、ITO−07N(関東化学社製)を用いてもよい。

【0080】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によっ

て除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を

再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等

の材料を回収して再利用することにより、資源を有効活用しコストを低減できる。

【0081】

所望の形状にエッチングできるように、材料に合わせてエッチング条件(エッチング液、

エッチング時間、温度等)を適宜調節する。

【0082】

本実施の形態では、エッチング液として燐酸と酢酸と硝酸を混ぜた溶液を用いたウェット

エッチング法により、酸化物半導体膜を島状の酸化物半導体層102及び122に加工す

る。

【0083】

本実施の形態では、酸化物半導体層102及び122に対して窒素、またはヘリウム、ネ

オン、アルゴン等の希ガス雰囲気下で第1の加熱処理を行う。第1の加熱処理の温度は、

400℃以上750℃以下、好ましくは400℃以上基板の歪み点未満とする。ここでは

、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気

下450℃において1時間の加熱処理を行う。加熱処理温度からの降温時には、雰囲気を

酸素に切り替えても良い。この第1の加熱処理によって酸化物半導体層102及び122

の脱水化または脱水素化を行うことができる。

【0084】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱

輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas

Rapid Thermal Annealing)装置、LRTA(Lamp Ra

pid Thermal Annealing)装置等のRTA(Rapid Ther

mal Annealing)装置を用いることができる。LRTA装置は、ハロゲンラ

ンプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナト

リウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処

理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置で

ある。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理

物と反応しない不活性気体が用いられる。

【0085】

例えば、第1の加熱処理として、650℃以上700℃以下の高温に加熱した不活性ガス

中に基板を入れ、数分間加熱した後に基板不活性ガス中から出すGRTAを行ってもよい

。GRTAを用いると短時間での高温加熱処理が可能となる。

【0086】

なお、第1の加熱処理においては、窒素、ヘリウム、ネオン、またはアルゴン等の雰囲気

ガスに、水、水素などが含まれないことが好ましい。または、該雰囲気ガスの純度を、6

N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純

物濃度を1ppm以下、好ましくは0.1ppm以下)とする。雰囲気ガスとして酸素を

用いる場合も同様の純度であることが好ましい。

【0087】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層

が結晶化し、微結晶層または多結晶層となる場合もある。例えば、結晶化率が90%以上

、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理

の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半

導体層となる場合もある。また、非晶質の酸化物半導体層の中に微結晶部(粒径1nm以

上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる

場合もある。

【0088】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物

半導体膜に行うこともできる。

【0089】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成

膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及び

ドレイン電極上にゲート絶縁層を形成した後、のいずれで行っても良い。

【0090】

次いで、第2のフォトリソグラフィ工程及びエッチング工程によりフォトダイオード上層

のP+層に達する開口部を絶縁層に形成し、絶縁層及び酸化物半導体層102及び122

上に、導電層を形成する。導電層をスパッタ法や真空蒸着法で形成すればよい。導電層の

材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステ

ンから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わ

せた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム

、イットリウムのいずれか一または複数から選択された材料を用いてもよい。また、金属

導電層は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むア

ルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と

、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する

3層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タングステン、

モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み

合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

【0091】

次に、第3のフォトリソグラフィ工程にて導電層上にレジストマスクを形成し、選択的に

エッチングを行って、第1の薄膜トランジスタのソース電極104及びドレイン電極10

6、第2の薄膜トランジスタのソース電極124及びドレイン電極126を形成した後、

レジストマスクを除去する(図4(C)参照)。ここで、第1の薄膜トランジスタのドレ

イン電極106と第2の薄膜トランジスタのソース電極124は電気的に接続された状態

で形成されるが、絶縁された状態でも良く、後に配線を用いて電気的に接続しても良い。

なお、形成されたソース電極、ドレイン電極の端部がテーパであると、上に積層するゲー

ト絶縁層の被覆性が向上するため好ましい。

【0092】

本実施の形態では、ソース電極104及び124、ドレイン電極106及び126として

、スパッタ法により膜厚150nmのチタン膜を形成する。

【0093】

なお、導電層のエッチングの際に、酸化物半導体層102及び122は酸化物半導体層の

一部が除去されて、その下の絶縁層が露出しないようにそれぞれの材料及びエッチング条

件を適宜調節する。

【0094】

本実施の形態では、導電層としてチタン膜を用いて、酸化物半導体層102及び122に

はIn−Ga−Zn−O系酸化物半導体を用いて、エッチャントとしてアンモニア過水(

アンモニア、水、過酸化水素水の混合液)を用いる。

【0095】

なお、第3のフォトリソグラフィ工程及びエッチング工程では、酸化物半導体層102及

び122は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となること

もある。また、ソース電極104及び124、ドレイン電極106及び126を形成する

ためのレジストマスクをインクジェット法で形成してもよい。インクジェット法はフォト

マスクを使用しないため、製造コストを低減することができる。

【0096】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレ

ーザ光やArFレーザ光を用いる。酸化物半導体層102及び122上で隣り合うソース

電極の下端部とドレイン電極の下端部との間隔幅によって後に形成される薄膜トランジス

タのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合に

は、数nm〜数10nmと極めて波長が短い超紫外線(Extreme Ultravi

olet)を用いて第2のフォトリソグラフィ工程でのレジストマスク形成時の露光を行

う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄

膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり

、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も

図ることができる。

【0097】

次いで、絶縁層、酸化物半導体層102及び122、ソース電極104及び124、ドレ

イン電極106及び126上にゲート絶縁層118を形成する(図5(A)参照)。この

とき、バルクトランジスタ上にもゲート絶縁層118は成膜され、層間絶縁膜の一部とな

る。

【0098】

ここで、不純物を除去することによりi型化または実質的にi型化された酸化物半導体(

高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、ゲ

ート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート

絶縁層(GI)は、高品質化が要求される。

【0099】

例えば、マイクロ波(2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐

圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品

質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとす

ることができるからである。もちろん、ゲート絶縁層として良質な絶縁層を形成できるも

のであれば、スパッタ法やプラズマCVD法など他の成膜方法を適用することができる。

また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質さ

れる絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であるこ

とは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるもの

であれば良い。

【0100】

さらに、85℃、2×106V/cm、12時間のゲートバイアス・熱ストレス試験(B

T試験)においては、不純物が酸化物半導体に添加されていると、不純物と酸化物半導体

の主成分との結合が、強電界(B:バイアス)と高温(T:温度)により切断され、生成

された未結合手がしきい値電圧(Vth)のシフトを誘発することとなる。これに対して

、本発明の一態様は、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のよう

にゲート絶縁層との界面特性を良好にすることにより、BT試験を行っても安定な薄膜ト

ランジスタを得ることを可能としている。

【0101】

本実施の形態において、ゲート絶縁層118の形成は、マイクロ波(2.45GHz)を

用いた高密度プラズマCVD装置により行う。ここでは、高密度プラズマCVD装置は、

1×1011/cm3以上のプラズマ密度を達成できる装置を指している。例えば、3k

W以上6kW以下のマイクロ波電力を印加してプラズマを発生させて、絶縁層の成膜を行

う。

【0102】

チャンバーに材料ガスとしてモノシランガス(SiH4)と亜酸化窒素(N2O)と希ガ

スを導入し、10Pa〜30Paの圧力下で高密度プラズマを発生させて基板上に絶縁層

を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素(

N2O)と希ガスとを導入して絶縁層表面にプラズマ処理を行ってもよい。少なくとも亜

酸化窒素(N2O)と希ガスとを導入して絶縁層表面に行われるプラズマ処理は、絶縁層

の成膜より後に行う。上記プロセスを経た絶縁層は、膜厚が薄く、例えば100nm未満

であっても信頼性を確保することができる。

【0103】

ゲート絶縁層118の形成の際、チャンバーに導入するモノシランガス(SiH4)と亜

酸化窒素(N2O)との流量比は、1:10から1:200の範囲とする。また、チャン

バーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用い

ることができるが、中でも安価であるアルゴンを用いることが好ましい。

【0104】

また、高密度プラズマCVD装置により得られる絶縁層は、段差被覆性に優れており、膜

厚を正確に制御することができる。

【0105】

上記プロセスを経た絶縁層は、従来の平行平板型のPECVD装置で得られる絶縁層とは

膜質が大きく異なっており、同じエッチャントを用いたエッチング速度の比較では、平行

平板型のPECVD装置で得られる絶縁層の10%以上または20%以上エッチング速度

が遅く、高密度プラズマCVD装置で得られる絶縁層は緻密な層と言える。

【0106】

本実施の形態では、ゲート絶縁層118として高密度プラズマCVD装置による膜厚10

0nmの酸化窒化珪素層(SiOxNyとも呼ぶ、ただし、x>y>0)を用いる。

【0107】

その他の方法として、プラズマCVD法またはスパッタ法等を用いて、酸化シリコン層、

窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、または酸化アルミニウム層

を単層でまたは積層して形成することもできる。なお、ゲート絶縁層118中に水素が多

量に含まれないようにするためには、スパッタ法でゲート絶縁層118を成膜することも

好ましい。スパッタ法により酸化シリコン層を成膜する場合には、ターゲットとしてシリ