半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に窒化物半導体を用いた電界効果トランジスタに適用して有効な技術に関する。

【背景技術】

【0002】

窒化ガリウム(GaN)に代表されるIII族窒化物半導体はシリコン半導体と比べて禁制帯幅が大きく、絶縁破壊電界は1桁程度大きいという特徴を持つため、次世代パワーデバイスとして有望視されている。特にIII族窒化物半導体で構成されたヘテロ接合では、分極効果によりヘテロ界面に高濃度の電荷(2次元電子ガス)を発生させることができる。この発生した2次元電子ガスは、イオン化不純物散乱の影響が少なく高い移動度を有する。したがって、III族窒化物半導体は、電力変換の損失に直結するオン抵抗を大幅に低減することが可能となる。一方で、素子が扱える電圧を大きくすると、電界効果トランジスタのオン時にキャリアが走行する距離も長くなるため、耐圧とオン抵抗はトレードオフの関係となる。

【0003】

本技術分野の背景技術として、特開2007−134607号公報(特許文献1)がある。この公報には、分極により発生する正及び負の電荷を利用し、オン抵抗と耐圧のトレードオフを改善した整流ダイオードについて記載されている。また、特開2010−135640号公報(特許文献2)には、分極接合を2つ積層し、2つのチャネルによってオン抵抗を低減した電界効果トランジスタについて記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−134607号公報

【特許文献2】特開2010−135640号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記従来技術では、窒化物半導体によるヘテロ接合体、すなわちヘテロ界面に生成されるチャネルを複数積層した電界効果トランジスタにおいて、表面のゲート電極から遠い側のチャネルをバイアス印加により制御することが困難である。したがって、ゲートに十分なオフバイアスを印加しないと、遠い側のチャネルのキャリアをカットすることができない。すなわち、この電界効果トランジスタは、ゲートにバイアスを印加しないときはオン状態でありノーマリオンとなる。

【0006】

パワーデバイスにおいては、安全のため、ゲートにバイアスを印加しないときにはオフとなるノーマリオフが強く望まれる。上記特許文献2には、表面をリセスしてゲートを埋め込んだ構造が記載されている。この場合、上部のチャネルをリセスゲートが遮断してしまい、上部チャネルのキャリアは伝導に寄与しない。すなわち、オン抵抗が低減できなくなるという課題を有する。

【0007】

そこで、本発明の目的は、複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供することである。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明の半導体装置の主要な構成は、次の通りとなる。

【0009】

第1の窒化物半導体層と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体を備え、窒化物半導体積層体に設けられたドレイン電極と、ソース電極と、ドレイン電極とソース電極の両者に対向して設けられたゲート電極とを有し、ドレイン電極とソース電極は、窒化物半導体積層体の表面または側面に配置され、ゲート電極は、窒化物半導体積層体の深さ方向に設けられた第1ゲート電極と、該第1ゲート電極と窒化物半導体積層体の深さ方向の配置深さが異なる第2ゲート電極とを有することを特徴とする。

【0010】

この構成によれば、配置が深い第1ゲート電極によって第2積層体中の複数のチャネルをすべて遮断することができ、ノーマリオフを達成できる。一方、ゲートに正バイアスを印加して電界効果トランジスタをオンさせる時には、第2ゲート電極によって窒化物半導体積層体中の複数のチャネルを接続させ、複数チャネル中のキャリアも伝導に寄与できる。したがって、オン抵抗の低減が可能となる。

【発明の効果】

【0011】

本発明によれば、複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現できる。

【図面の簡単な説明】

【0012】

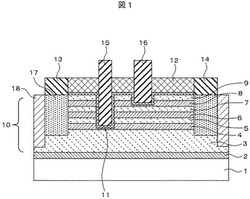

【図1】本発明の実施例1における半導体装置の断面構造を示す説明図である。

【図2】本発明の実施例1における半導体装置の平面構造を示す説明図である。

【図3】本発明の実施例1における半導体装置の第1ゲート電極15下のバンドダイヤグラムを示す説明図である。

【図4】本発明の実施例1における半導体装置の第2ゲート電極16下のバンドダイヤグラムを示す説明図である。

【図5】本発明の実施例2における半導体装置の断面構造を示す説明図である。

【図6】本発明の実施例3における半導体装置の断面構造を示す説明図である。

【図7】本発明の実施例3における半導体装置の製造工程を示す断面構造図である。

【図8】本発明の実施例3における半導体装置の製造工程を示す断面構造図である。

【発明を実施するための形態】

【0013】

以下、実施例を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【実施例1】

【0014】

図1および図2はそれぞれ、本発明の実施例1における半導体装置の断面および平面構造を示す説明図である。なお、図1と図2は対応するが、素子絶縁分離領域18は、図2には図示していない。

【0015】

本実施例1による半導体装置は、半導体基板1上に形成されたバッファ層2および窒化物半導体の積層体10と、窒化物半導体積層体10中に形成された第1導電型の不純物(n+)が導入された領域17と、その上部に形成されたソース電極13と、同じくn+領域17上に形成されたドレイン電極14と、窒化物半導体積層体10の一部あるいは上部に絶縁膜11を介して形成されたゲート電極15および16とを備えている電界効果トランジスタである。素子間絶縁が必要な領域には、素子分離領域18が形成され、素子表面は保護絶縁膜12で覆われている。

【0016】

前記電界効果トランジスタにおいて、半導体基板1は、例えばSi、サファイア、SiC、GaNなどからなる。

【0017】

バッファ層2は、例えば厚さ数十nm以下の(Al)GaNとAlNが積層された超格子層から構成される。

【0018】

バッファ層2上に形成された窒化物半導体積層体10は、例えば窒化物半導体3から9が積層されて構成されている。窒化物半導体3は、例えば不純物が意図的に導入されていないアンドープで厚さ数μmのGaNからなり、窒化物半導体4は、例えば厚さ25nm程度の窒化物半導体3より禁制帯幅が大きいAlxGa1−xN(0<x≦1)からなる。ここでAl組成比xは格子歪の影響を少なくするため、0.25程度以下が好ましい。このヘテロ接合体の接合界面には、分極によって1x1013/cm2程度の電荷が生じている。

【0019】

また、窒化物半導体4としては、InyAl1−yN(0<y≦1)でも良い。In組成比が0.18程度のときGaNと格子整合するため、結晶成長が容易になる。本構成においても、ヘテロ界面に分極によって高濃度の電荷が生じる。

【0020】

窒化物半導体5と6、および、7と8も同様にヘテロ接合体を形成しており、窒化物半導体5および7が禁制帯幅の小さい、例えば厚さ25nm程度のGaNから構成され、窒化物半導体6および8は、それぞれ窒化物半導体5および7より禁制帯幅の大きい、例えば厚さ25nm程度のAlGaN(Al組成0.25程度)からなる。ここでは、3組の窒化物半導体ヘテロ接合体を積層した例を示したが、ヘテロ接合体は少なくとも2組以上あればよい。上記へテロ接合体が多く積層されるほど、電界効果トランジスタのキャリアとして寄与する電荷の総量が多くなり、オン抵抗がより低減できる。

【0021】

窒化物半導体積層体10の表面には、キャリアへの表面準位の影響を少なくするため、例えば厚さ5nm程度のGaNからなる窒化物半導体9が形成されていることが望ましい。

【0022】

以下、図1を参照しながら、製造工程を順次説明する。

はじめに、半導体基板1上に、エピタキシャル成長でバッファ層2と窒化物半導体積層体10を形成する。

続いて、図示しないSiO2膜を堆積し、フォトリソグラフィおよびドライエッチングによりSiO2膜を加工してパターニングする。さらに、これをハードマスクとして、塩素プラズマを用いたドライエッチングにより、窒化物半導体積層体10を窒化物半導体3に到達するまで加工する。この加工された領域18は、ヘテロ界面がなくなるためキャリアが存在せず、絶縁された素子分離領域18となる。

【0023】

また別の手法として、フォトリソグラフィによりパターンを形成した後、イオン注入によってBあるいはFeなどを窒化物半導体積層体10の表面から窒化物半導体3に到達するように注入する。この注入領域は、前記の手法と同様に絶縁された素子分離領域18となる。

【0024】

続いて、フォトリソグラフィによりパターンを形成した後、イオン注入によってSiなどを窒化物半導体積層体10の表面から窒化物半導体3に到達するように注入する。この高濃度(例えば、1x1018/cm3以上)に注入された領域は、注入された不純物によって第1導電型(n+)の低抵抗な領域17となる。

【0025】

さらには、スパッタ法あるいは蒸着法およびリフトオフ法を用いて、n+領域17上にオーミック電極(Ti/Al等)を形成する。これにより、ソース電極13およびドレイン電極14が形成される。

【0026】

次に、フォトリソグラフィとドライエッチングにより、窒化物半導体積層体10のゲート領域を各々加工する。ここで、第1のゲート領域においては、窒化物半導体積層体10の表面から窒化物半導体4に到達するまで、第2のゲート領域においては、窒化物半導体積層体10の表面から窒化物半導体8に到達するまで加工する。このとき、第1ゲート領域下には、1組のヘテロ接合体が残っており、第2ゲート領域下には、3組のヘテロ接合体が残っている。ただし、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

【0027】

続いて、スパッタ法あるいはCVD(Chemical Vapor Deposition)法あるいはALD(Atomic Layer Deposition)法などを用いてゲート絶縁膜11を堆積する。このゲート絶縁膜11は、例えばSiO2膜、SiN膜、Al2O3膜、HfO2膜など、あるいはこれらの積層膜から構成され、厚さは数nmから数十nmで形成される。

【0028】

さらには、フォトリソグラフィおよびリフトオフ法などによって、ゲート電極15および16を形成する。ゲート電極は、例えばAl、Ti/Pt/Au、Ti/Al、TiN/Al、ドープドPoly−Si、TiN/ドープドPoly−Si、などから構成される。このMIS(Metal Insulator Semiconductor)構造では、ゲートにバイアスを印加してもゲート電流がほとんど流れず、ゲートに高いバイアスを印加することができる。また、ゲート絶縁膜の構成によって、電界効果トランジスタのしきい電圧を調整することも可能である。

【0029】

ここでは、ゲート絶縁膜11を介してゲート電極15および16を形成した例を示したが、ゲート絶縁膜11を介さずゲート電極を形成してもよい。この場合、ゲートは窒化物半導体積層体10とショットキー接触し、ゲート電極は、例えばNi/Au、Pt/Au、Pd/Auなどから構成される。このショットキーゲートの場合、ゲートにバイアスを印加するとゲート電流が流れるためゲートに高いバイアスを印加することはできないが、製造工程が簡易となる。

【0030】

最後にスパッタ法あるいはCVD法を用いて絶縁保護膜12を厚さ数百nmから数μm程度堆積し、図示していないがそれぞれの電極に外部からバイアスを印加するパッド領域を開口して、本実施例の半導体装置が完成する。

【0031】

平面構造としては、図2に示すように、素子絶縁分離領域18に囲まれた窒化物半導体積層体10(ここで窒化物半導体積層体10上の絶縁保護膜12などは図示していない)において、窒化物半導体積層体10上にソース電極13とドレイン電極14が対向して配置されており、その間に第1ゲート電極15および第2ゲート電極16が素子絶縁分離領域18上に架かるまで配置されている。

【0032】

本実施例の構成による、第1ゲート電極15および第1ゲート電極15下の窒化物半導体積層体10のバンドダイヤグラムを図3に示す。第1ゲート電極15にバイアスを印可していないとき(0V)、第1ゲート電極15とゲート絶縁膜11の静電ポテンシャルにより、系のフェルミエネルギー(EF)は窒化物半導体3と4からなるヘテロ接合体の伝導帯(EC)より低くなっており、ヘテロ界面のキャリアがなくなっている。したがって、電界効果トランジスタはオフ状態であり、ノーマリオフ動作を実現できる。

【0033】

一方、第1ゲート電極15に正バイアスを(例えば、+15V)印加すると、系のEFは窒化物半導体3と4からなるヘテロ接合体の伝導帯(EC)より高くなり、ヘテロ界面に高濃度の2次元電子ガスが生成される。したがって、電界効果トランジスタはオン状態となる。このとき、第2ゲート電極16にも正バイアス(例えば、+10V)印加する。第2ゲート電極16および第2ゲート電極16下の窒化物半導体積層体10のバンドダイヤグラムを図4に示す。第2ゲート電極16に印加された正バイアスにより、窒化物半導体積層体10のゲート側のECはEFより低く下がっており、それぞれ窒化物半導体3と4、5と6、7と8からなる3組のヘテロ接合体のヘテロ界面には、2次元電子ガスが生成されている。

【0034】

さらには、各2次元電子ガスに対して障壁となっている窒化物半導体4および6の障壁高さもEF対して低くなっており、電子はトンネル効果によって障壁を乗り越えることができる。したがって、図1で示す電界効果トランジスタのオン状態時において、キャリアはソース電極13から第1ゲート電極15下を介し、第2ゲート電極16下で複数(図1では3組)のチャネルが接続され、その3組のチャネルを通ってドレイン電極14へ到達する。すなわち、ヘテロ接合体の積層数が多ければ多いほど、生成される2次元電子ガスの量は多くなり、電界効果トランジスタのオン抵抗が低減できる。

【0035】

この電界効果トランジスタのオフ耐圧に関しては、上記特許文献1に記載されているように、分極効果によってヘテロ接合体の積層数にかかわらず、一定を維持できる。また、正バイアスが印加されたドレイン電極14からの電気力線は、第1ゲート電極15と第2ゲート電極16両者に終端するため、第1ゲート電極15に対して、第2ゲート電極16は電界緩和効果をもつ。すなわち、本実施例によって、オフ耐圧の向上も可能となる。

【実施例2】

【0036】

実施例1においては、ゲート電極が2つあるため、それぞれのゲート電極ごとに独立してバイアスを印加し制御できるというメリットがあるが、配線のレイアウトや電界効果トランジスタの駆動方法が複雑になる。そこで、本実施例では、製造工程、レイアウト、駆動方法が簡易な半導体装置の例を説明する。

【0037】

図5は、実施例2における半導体装置の断面構造を示す説明図である。実施例1で既に説明した同一の符号を付された構成と、同一の機能を有する部分については、説明を省略する。

【0038】

本実施例は、実施例1と異なり、ゲート電極15とゲート電極16が窒化物半導体積層体10の表面上で一体となって形成されていることを特徴とする。以下、製造工程を順次追いながら説明する。

【0039】

実施例1と同様、半導体基板1上に、バッファ層2および窒化物半導体積層体10を形成し、素子分離領域18、n型領域17、ソース電極13、ドレイン電極14を形成する。

【0040】

次に、CVD法あるいはスパッタ法などにより、絶縁保護膜12を堆積する。ここで、絶縁保護膜12は、例えば厚さ300nm程度でSiO2膜あるいはSiN膜、またはこれらの積層膜などから構成される。

【0041】

続いて、フォトリソグラフィにより第1ゲート領域15と第2ゲート領域16をパターニングし、ドライエッチングにより該領域の前記絶縁保護膜12を加工する。

【0042】

さらには、フォトリソグラフィにより第1ゲート領域15のみをパターニングし、ドライエッチングにより該領域の窒化物半導体積層体10を加工する。この際、実施例1と同様に、窒化物半導体積層体10の表面から窒化物半導体4に到達するまで加工することが望ましい。

【0043】

この後、CVD法あるいはALD法などにより、実施例1記載のゲート絶縁膜11を堆積する。続いて、フォトリソグラフィおよびリフトオフ法などにより、実施例1記載の第1ゲート電極15および第2ゲート電極16を形成する。図5では、第2ゲート電極16は窒化物半導体積層体10の表面上に形成した例を図示しているが、図1で示すように窒化物半導体積層体10の内部に形成しても良い。ただし、実施例1で述べたように、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

最後に、図示していないがそれぞれの電極に外部からバイアスを印加するパッド領域を開口して、本実施例の半導体装置が完成する。

【0044】

本実施例では、第1ゲート電極15と第2ゲート電極16を同時に形成できるので、製造工程を簡略化できる。さらには、第1ゲート電極15と第2ゲート電極16が一体化されているため、配線レイアウトや電界効果トランジスタの駆動方法も簡易となる。

【0045】

本構成においても、実施例1同様、ノーマリオフ動作およびオン抵抗の低減を実現できる。

【実施例3】

【0046】

実施例2においては、第1および第2ゲート電極領域15、16の絶縁保護膜12をパターニング後、第1ゲート電極領域15をフォトグラフィでパターニングし、加工する必要があった。

【0047】

本実施例では、製造工程がより簡易な半導体装置の例を説明する。

図6は、実施例3における半導体装置の断面構造を示す説明図である。実施例1および2で既に説明した同一の符号を付された構成と、同一の機能を有する部分については、説明を省略する。

【0048】

本実施例は、実施例2と異なり、窒化物半導体積層体10中において、ゲート電極15とゲート電極16が一体となって形成されていることを特徴とする。以下、製造工程を順次追いながら説明する。

【0049】

実施例2と同様、半導体基板1上に、バッファ層2および窒化物半導体積層体10を形成し、素子分離領域18、n型領域17、ソース電極13、ドレイン電極14を形成する。

【0050】

次に、CVD法あるいはスパッタ法などにより、絶縁保護膜12を堆積する。ここで、絶縁保護膜12は、例えば厚さ300nm程度のSiN膜などから構成される。

【0051】

続いて、フォトリソグラフィにより、第2ゲート領域16に相当する領域をパターニングし、ドライエッチングにより該領域の前記絶縁保護膜12を加工する。さらには、パターニングされた絶縁保護膜12をハードマスクにして、窒化物半導体積層体10をドライエッチングにより加工する。図7では、窒化物半導体積層体10の表面から窒化物半導体8まで加工した例を示したが、加工領域下に2組以上のヘテロ接合体が残っていればよい。

【0052】

次に、CVD法あるいはスパッタ法などにより、例えば厚さ300nm程度のSiO2膜などを堆積する。その後、ドライエッチングにより、前記SiO2膜をエッチバックすることで、保護絶縁膜12の開口部側壁に前記SiO2膜からなるサイドウォール19を形成する。続いて、前記保護絶縁膜12およびサイドウォール19をハードマスクに、ドライエッチングにより窒化物半導体積層体10を加工する(図8)。

【0053】

さらには、例えばフッ酸などを用いて選択的にウエットエッチングすることにより、前記サイドウォール19のみを除去でき、ゲート領域を段差形状に加工した窒化物半導体積層体10が得られる。

【0054】

この後、実施例2同様、ゲート絶縁膜11を堆積し、ゲート電極形成等を経て、本実施例の半導体装置が完成する。ただし、実施例1で述べたように、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

【0055】

本実施例では、実施例2と異なり、フォトリソグラフィを追加せず第1ゲート電極領域を加工でき、製造工程を簡略化できる。さらに、本実施例の電界効果トランジスタのオン状態においては、キャリアが第1ゲート電極15下を通過後ただちに、第2ゲート電極16によって複数のヘテロ接合体中のキャリアを結合させることができ、よりオン抵抗が低減できる。

【0056】

また、電界効果トランジスタのオフ状態においては、図6に示されているように、ゲート電極をドレイン電極14側に庇状に形成することで、第1および第2ゲート電極15、16に対するドレイン電極14からの電界を緩和させることができ、オフ耐圧の向上も可能となる。

【0057】

本構成においても、実施例1および2同様、ノーマリオフ動作およびオン抵抗の低減を実現できる。

【符号の説明】

【0058】

1…半導体基板、

2…バッファ層

3,4,5,6,7,8,9…窒化物半導体、

10…窒化物半導体積層体、

11…ゲート絶縁膜、

12…絶縁保護膜、

13…ソース電極、

14…ドレイン電極

15…第1ゲート電極、

16…第2ゲート電極、

17…n型領域、

18…素子絶縁分離領域、

19…サイドウォール。

【技術分野】

【0001】

本発明は、半導体装置に関し、特に窒化物半導体を用いた電界効果トランジスタに適用して有効な技術に関する。

【背景技術】

【0002】

窒化ガリウム(GaN)に代表されるIII族窒化物半導体はシリコン半導体と比べて禁制帯幅が大きく、絶縁破壊電界は1桁程度大きいという特徴を持つため、次世代パワーデバイスとして有望視されている。特にIII族窒化物半導体で構成されたヘテロ接合では、分極効果によりヘテロ界面に高濃度の電荷(2次元電子ガス)を発生させることができる。この発生した2次元電子ガスは、イオン化不純物散乱の影響が少なく高い移動度を有する。したがって、III族窒化物半導体は、電力変換の損失に直結するオン抵抗を大幅に低減することが可能となる。一方で、素子が扱える電圧を大きくすると、電界効果トランジスタのオン時にキャリアが走行する距離も長くなるため、耐圧とオン抵抗はトレードオフの関係となる。

【0003】

本技術分野の背景技術として、特開2007−134607号公報(特許文献1)がある。この公報には、分極により発生する正及び負の電荷を利用し、オン抵抗と耐圧のトレードオフを改善した整流ダイオードについて記載されている。また、特開2010−135640号公報(特許文献2)には、分極接合を2つ積層し、2つのチャネルによってオン抵抗を低減した電界効果トランジスタについて記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−134607号公報

【特許文献2】特開2010−135640号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記従来技術では、窒化物半導体によるヘテロ接合体、すなわちヘテロ界面に生成されるチャネルを複数積層した電界効果トランジスタにおいて、表面のゲート電極から遠い側のチャネルをバイアス印加により制御することが困難である。したがって、ゲートに十分なオフバイアスを印加しないと、遠い側のチャネルのキャリアをカットすることができない。すなわち、この電界効果トランジスタは、ゲートにバイアスを印加しないときはオン状態でありノーマリオンとなる。

【0006】

パワーデバイスにおいては、安全のため、ゲートにバイアスを印加しないときにはオフとなるノーマリオフが強く望まれる。上記特許文献2には、表面をリセスしてゲートを埋め込んだ構造が記載されている。この場合、上部のチャネルをリセスゲートが遮断してしまい、上部チャネルのキャリアは伝導に寄与しない。すなわち、オン抵抗が低減できなくなるという課題を有する。

【0007】

そこで、本発明の目的は、複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供することである。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明の半導体装置の主要な構成は、次の通りとなる。

【0009】

第1の窒化物半導体層と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体を備え、窒化物半導体積層体に設けられたドレイン電極と、ソース電極と、ドレイン電極とソース電極の両者に対向して設けられたゲート電極とを有し、ドレイン電極とソース電極は、窒化物半導体積層体の表面または側面に配置され、ゲート電極は、窒化物半導体積層体の深さ方向に設けられた第1ゲート電極と、該第1ゲート電極と窒化物半導体積層体の深さ方向の配置深さが異なる第2ゲート電極とを有することを特徴とする。

【0010】

この構成によれば、配置が深い第1ゲート電極によって第2積層体中の複数のチャネルをすべて遮断することができ、ノーマリオフを達成できる。一方、ゲートに正バイアスを印加して電界効果トランジスタをオンさせる時には、第2ゲート電極によって窒化物半導体積層体中の複数のチャネルを接続させ、複数チャネル中のキャリアも伝導に寄与できる。したがって、オン抵抗の低減が可能となる。

【発明の効果】

【0011】

本発明によれば、複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現できる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施例1における半導体装置の断面構造を示す説明図である。

【図2】本発明の実施例1における半導体装置の平面構造を示す説明図である。

【図3】本発明の実施例1における半導体装置の第1ゲート電極15下のバンドダイヤグラムを示す説明図である。

【図4】本発明の実施例1における半導体装置の第2ゲート電極16下のバンドダイヤグラムを示す説明図である。

【図5】本発明の実施例2における半導体装置の断面構造を示す説明図である。

【図6】本発明の実施例3における半導体装置の断面構造を示す説明図である。

【図7】本発明の実施例3における半導体装置の製造工程を示す断面構造図である。

【図8】本発明の実施例3における半導体装置の製造工程を示す断面構造図である。

【発明を実施するための形態】

【0013】

以下、実施例を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【実施例1】

【0014】

図1および図2はそれぞれ、本発明の実施例1における半導体装置の断面および平面構造を示す説明図である。なお、図1と図2は対応するが、素子絶縁分離領域18は、図2には図示していない。

【0015】

本実施例1による半導体装置は、半導体基板1上に形成されたバッファ層2および窒化物半導体の積層体10と、窒化物半導体積層体10中に形成された第1導電型の不純物(n+)が導入された領域17と、その上部に形成されたソース電極13と、同じくn+領域17上に形成されたドレイン電極14と、窒化物半導体積層体10の一部あるいは上部に絶縁膜11を介して形成されたゲート電極15および16とを備えている電界効果トランジスタである。素子間絶縁が必要な領域には、素子分離領域18が形成され、素子表面は保護絶縁膜12で覆われている。

【0016】

前記電界効果トランジスタにおいて、半導体基板1は、例えばSi、サファイア、SiC、GaNなどからなる。

【0017】

バッファ層2は、例えば厚さ数十nm以下の(Al)GaNとAlNが積層された超格子層から構成される。

【0018】

バッファ層2上に形成された窒化物半導体積層体10は、例えば窒化物半導体3から9が積層されて構成されている。窒化物半導体3は、例えば不純物が意図的に導入されていないアンドープで厚さ数μmのGaNからなり、窒化物半導体4は、例えば厚さ25nm程度の窒化物半導体3より禁制帯幅が大きいAlxGa1−xN(0<x≦1)からなる。ここでAl組成比xは格子歪の影響を少なくするため、0.25程度以下が好ましい。このヘテロ接合体の接合界面には、分極によって1x1013/cm2程度の電荷が生じている。

【0019】

また、窒化物半導体4としては、InyAl1−yN(0<y≦1)でも良い。In組成比が0.18程度のときGaNと格子整合するため、結晶成長が容易になる。本構成においても、ヘテロ界面に分極によって高濃度の電荷が生じる。

【0020】

窒化物半導体5と6、および、7と8も同様にヘテロ接合体を形成しており、窒化物半導体5および7が禁制帯幅の小さい、例えば厚さ25nm程度のGaNから構成され、窒化物半導体6および8は、それぞれ窒化物半導体5および7より禁制帯幅の大きい、例えば厚さ25nm程度のAlGaN(Al組成0.25程度)からなる。ここでは、3組の窒化物半導体ヘテロ接合体を積層した例を示したが、ヘテロ接合体は少なくとも2組以上あればよい。上記へテロ接合体が多く積層されるほど、電界効果トランジスタのキャリアとして寄与する電荷の総量が多くなり、オン抵抗がより低減できる。

【0021】

窒化物半導体積層体10の表面には、キャリアへの表面準位の影響を少なくするため、例えば厚さ5nm程度のGaNからなる窒化物半導体9が形成されていることが望ましい。

【0022】

以下、図1を参照しながら、製造工程を順次説明する。

はじめに、半導体基板1上に、エピタキシャル成長でバッファ層2と窒化物半導体積層体10を形成する。

続いて、図示しないSiO2膜を堆積し、フォトリソグラフィおよびドライエッチングによりSiO2膜を加工してパターニングする。さらに、これをハードマスクとして、塩素プラズマを用いたドライエッチングにより、窒化物半導体積層体10を窒化物半導体3に到達するまで加工する。この加工された領域18は、ヘテロ界面がなくなるためキャリアが存在せず、絶縁された素子分離領域18となる。

【0023】

また別の手法として、フォトリソグラフィによりパターンを形成した後、イオン注入によってBあるいはFeなどを窒化物半導体積層体10の表面から窒化物半導体3に到達するように注入する。この注入領域は、前記の手法と同様に絶縁された素子分離領域18となる。

【0024】

続いて、フォトリソグラフィによりパターンを形成した後、イオン注入によってSiなどを窒化物半導体積層体10の表面から窒化物半導体3に到達するように注入する。この高濃度(例えば、1x1018/cm3以上)に注入された領域は、注入された不純物によって第1導電型(n+)の低抵抗な領域17となる。

【0025】

さらには、スパッタ法あるいは蒸着法およびリフトオフ法を用いて、n+領域17上にオーミック電極(Ti/Al等)を形成する。これにより、ソース電極13およびドレイン電極14が形成される。

【0026】

次に、フォトリソグラフィとドライエッチングにより、窒化物半導体積層体10のゲート領域を各々加工する。ここで、第1のゲート領域においては、窒化物半導体積層体10の表面から窒化物半導体4に到達するまで、第2のゲート領域においては、窒化物半導体積層体10の表面から窒化物半導体8に到達するまで加工する。このとき、第1ゲート領域下には、1組のヘテロ接合体が残っており、第2ゲート領域下には、3組のヘテロ接合体が残っている。ただし、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

【0027】

続いて、スパッタ法あるいはCVD(Chemical Vapor Deposition)法あるいはALD(Atomic Layer Deposition)法などを用いてゲート絶縁膜11を堆積する。このゲート絶縁膜11は、例えばSiO2膜、SiN膜、Al2O3膜、HfO2膜など、あるいはこれらの積層膜から構成され、厚さは数nmから数十nmで形成される。

【0028】

さらには、フォトリソグラフィおよびリフトオフ法などによって、ゲート電極15および16を形成する。ゲート電極は、例えばAl、Ti/Pt/Au、Ti/Al、TiN/Al、ドープドPoly−Si、TiN/ドープドPoly−Si、などから構成される。このMIS(Metal Insulator Semiconductor)構造では、ゲートにバイアスを印加してもゲート電流がほとんど流れず、ゲートに高いバイアスを印加することができる。また、ゲート絶縁膜の構成によって、電界効果トランジスタのしきい電圧を調整することも可能である。

【0029】

ここでは、ゲート絶縁膜11を介してゲート電極15および16を形成した例を示したが、ゲート絶縁膜11を介さずゲート電極を形成してもよい。この場合、ゲートは窒化物半導体積層体10とショットキー接触し、ゲート電極は、例えばNi/Au、Pt/Au、Pd/Auなどから構成される。このショットキーゲートの場合、ゲートにバイアスを印加するとゲート電流が流れるためゲートに高いバイアスを印加することはできないが、製造工程が簡易となる。

【0030】

最後にスパッタ法あるいはCVD法を用いて絶縁保護膜12を厚さ数百nmから数μm程度堆積し、図示していないがそれぞれの電極に外部からバイアスを印加するパッド領域を開口して、本実施例の半導体装置が完成する。

【0031】

平面構造としては、図2に示すように、素子絶縁分離領域18に囲まれた窒化物半導体積層体10(ここで窒化物半導体積層体10上の絶縁保護膜12などは図示していない)において、窒化物半導体積層体10上にソース電極13とドレイン電極14が対向して配置されており、その間に第1ゲート電極15および第2ゲート電極16が素子絶縁分離領域18上に架かるまで配置されている。

【0032】

本実施例の構成による、第1ゲート電極15および第1ゲート電極15下の窒化物半導体積層体10のバンドダイヤグラムを図3に示す。第1ゲート電極15にバイアスを印可していないとき(0V)、第1ゲート電極15とゲート絶縁膜11の静電ポテンシャルにより、系のフェルミエネルギー(EF)は窒化物半導体3と4からなるヘテロ接合体の伝導帯(EC)より低くなっており、ヘテロ界面のキャリアがなくなっている。したがって、電界効果トランジスタはオフ状態であり、ノーマリオフ動作を実現できる。

【0033】

一方、第1ゲート電極15に正バイアスを(例えば、+15V)印加すると、系のEFは窒化物半導体3と4からなるヘテロ接合体の伝導帯(EC)より高くなり、ヘテロ界面に高濃度の2次元電子ガスが生成される。したがって、電界効果トランジスタはオン状態となる。このとき、第2ゲート電極16にも正バイアス(例えば、+10V)印加する。第2ゲート電極16および第2ゲート電極16下の窒化物半導体積層体10のバンドダイヤグラムを図4に示す。第2ゲート電極16に印加された正バイアスにより、窒化物半導体積層体10のゲート側のECはEFより低く下がっており、それぞれ窒化物半導体3と4、5と6、7と8からなる3組のヘテロ接合体のヘテロ界面には、2次元電子ガスが生成されている。

【0034】

さらには、各2次元電子ガスに対して障壁となっている窒化物半導体4および6の障壁高さもEF対して低くなっており、電子はトンネル効果によって障壁を乗り越えることができる。したがって、図1で示す電界効果トランジスタのオン状態時において、キャリアはソース電極13から第1ゲート電極15下を介し、第2ゲート電極16下で複数(図1では3組)のチャネルが接続され、その3組のチャネルを通ってドレイン電極14へ到達する。すなわち、ヘテロ接合体の積層数が多ければ多いほど、生成される2次元電子ガスの量は多くなり、電界効果トランジスタのオン抵抗が低減できる。

【0035】

この電界効果トランジスタのオフ耐圧に関しては、上記特許文献1に記載されているように、分極効果によってヘテロ接合体の積層数にかかわらず、一定を維持できる。また、正バイアスが印加されたドレイン電極14からの電気力線は、第1ゲート電極15と第2ゲート電極16両者に終端するため、第1ゲート電極15に対して、第2ゲート電極16は電界緩和効果をもつ。すなわち、本実施例によって、オフ耐圧の向上も可能となる。

【実施例2】

【0036】

実施例1においては、ゲート電極が2つあるため、それぞれのゲート電極ごとに独立してバイアスを印加し制御できるというメリットがあるが、配線のレイアウトや電界効果トランジスタの駆動方法が複雑になる。そこで、本実施例では、製造工程、レイアウト、駆動方法が簡易な半導体装置の例を説明する。

【0037】

図5は、実施例2における半導体装置の断面構造を示す説明図である。実施例1で既に説明した同一の符号を付された構成と、同一の機能を有する部分については、説明を省略する。

【0038】

本実施例は、実施例1と異なり、ゲート電極15とゲート電極16が窒化物半導体積層体10の表面上で一体となって形成されていることを特徴とする。以下、製造工程を順次追いながら説明する。

【0039】

実施例1と同様、半導体基板1上に、バッファ層2および窒化物半導体積層体10を形成し、素子分離領域18、n型領域17、ソース電極13、ドレイン電極14を形成する。

【0040】

次に、CVD法あるいはスパッタ法などにより、絶縁保護膜12を堆積する。ここで、絶縁保護膜12は、例えば厚さ300nm程度でSiO2膜あるいはSiN膜、またはこれらの積層膜などから構成される。

【0041】

続いて、フォトリソグラフィにより第1ゲート領域15と第2ゲート領域16をパターニングし、ドライエッチングにより該領域の前記絶縁保護膜12を加工する。

【0042】

さらには、フォトリソグラフィにより第1ゲート領域15のみをパターニングし、ドライエッチングにより該領域の窒化物半導体積層体10を加工する。この際、実施例1と同様に、窒化物半導体積層体10の表面から窒化物半導体4に到達するまで加工することが望ましい。

【0043】

この後、CVD法あるいはALD法などにより、実施例1記載のゲート絶縁膜11を堆積する。続いて、フォトリソグラフィおよびリフトオフ法などにより、実施例1記載の第1ゲート電極15および第2ゲート電極16を形成する。図5では、第2ゲート電極16は窒化物半導体積層体10の表面上に形成した例を図示しているが、図1で示すように窒化物半導体積層体10の内部に形成しても良い。ただし、実施例1で述べたように、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

最後に、図示していないがそれぞれの電極に外部からバイアスを印加するパッド領域を開口して、本実施例の半導体装置が完成する。

【0044】

本実施例では、第1ゲート電極15と第2ゲート電極16を同時に形成できるので、製造工程を簡略化できる。さらには、第1ゲート電極15と第2ゲート電極16が一体化されているため、配線レイアウトや電界効果トランジスタの駆動方法も簡易となる。

【0045】

本構成においても、実施例1同様、ノーマリオフ動作およびオン抵抗の低減を実現できる。

【実施例3】

【0046】

実施例2においては、第1および第2ゲート電極領域15、16の絶縁保護膜12をパターニング後、第1ゲート電極領域15をフォトグラフィでパターニングし、加工する必要があった。

【0047】

本実施例では、製造工程がより簡易な半導体装置の例を説明する。

図6は、実施例3における半導体装置の断面構造を示す説明図である。実施例1および2で既に説明した同一の符号を付された構成と、同一の機能を有する部分については、説明を省略する。

【0048】

本実施例は、実施例2と異なり、窒化物半導体積層体10中において、ゲート電極15とゲート電極16が一体となって形成されていることを特徴とする。以下、製造工程を順次追いながら説明する。

【0049】

実施例2と同様、半導体基板1上に、バッファ層2および窒化物半導体積層体10を形成し、素子分離領域18、n型領域17、ソース電極13、ドレイン電極14を形成する。

【0050】

次に、CVD法あるいはスパッタ法などにより、絶縁保護膜12を堆積する。ここで、絶縁保護膜12は、例えば厚さ300nm程度のSiN膜などから構成される。

【0051】

続いて、フォトリソグラフィにより、第2ゲート領域16に相当する領域をパターニングし、ドライエッチングにより該領域の前記絶縁保護膜12を加工する。さらには、パターニングされた絶縁保護膜12をハードマスクにして、窒化物半導体積層体10をドライエッチングにより加工する。図7では、窒化物半導体積層体10の表面から窒化物半導体8まで加工した例を示したが、加工領域下に2組以上のヘテロ接合体が残っていればよい。

【0052】

次に、CVD法あるいはスパッタ法などにより、例えば厚さ300nm程度のSiO2膜などを堆積する。その後、ドライエッチングにより、前記SiO2膜をエッチバックすることで、保護絶縁膜12の開口部側壁に前記SiO2膜からなるサイドウォール19を形成する。続いて、前記保護絶縁膜12およびサイドウォール19をハードマスクに、ドライエッチングにより窒化物半導体積層体10を加工する(図8)。

【0053】

さらには、例えばフッ酸などを用いて選択的にウエットエッチングすることにより、前記サイドウォール19のみを除去でき、ゲート領域を段差形状に加工した窒化物半導体積層体10が得られる。

【0054】

この後、実施例2同様、ゲート絶縁膜11を堆積し、ゲート電極形成等を経て、本実施例の半導体装置が完成する。ただし、実施例1で述べたように、第1ゲート領域下にはヘテロ接合体が残っていなくともよく、第2ゲート領域下には、2組以上のヘテロ接合体が残っていることが望ましい。

【0055】

本実施例では、実施例2と異なり、フォトリソグラフィを追加せず第1ゲート電極領域を加工でき、製造工程を簡略化できる。さらに、本実施例の電界効果トランジスタのオン状態においては、キャリアが第1ゲート電極15下を通過後ただちに、第2ゲート電極16によって複数のヘテロ接合体中のキャリアを結合させることができ、よりオン抵抗が低減できる。

【0056】

また、電界効果トランジスタのオフ状態においては、図6に示されているように、ゲート電極をドレイン電極14側に庇状に形成することで、第1および第2ゲート電極15、16に対するドレイン電極14からの電界を緩和させることができ、オフ耐圧の向上も可能となる。

【0057】

本構成においても、実施例1および2同様、ノーマリオフ動作およびオン抵抗の低減を実現できる。

【符号の説明】

【0058】

1…半導体基板、

2…バッファ層

3,4,5,6,7,8,9…窒化物半導体、

10…窒化物半導体積層体、

11…ゲート絶縁膜、

12…絶縁保護膜、

13…ソース電極、

14…ドレイン電極

15…第1ゲート電極、

16…第2ゲート電極、

17…n型領域、

18…素子絶縁分離領域、

19…サイドウォール。

【特許請求の範囲】

【請求項1】

第1の窒化物半導体層と、前記第1の窒化物半導体層の禁制帯幅よりも大きい禁制帯幅を有する第2の窒化物半導体層とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体を備え、

前記窒化物半導体積層体に設けられたドレイン電極及びソース電極と、並びに前記ドレイン電極と前記ソース電極に挟まれる位置にあってそれぞれに対向するように設けられたゲート電極とを有し、

前記ドレイン電極と前記ソース電極は、前記窒化物半導体積層体の表面または側面に配置され、

前記ゲート電極は、前記窒化物半導体積層体の深さ方向に設けられた第1ゲート電極と、該第1ゲート電極と前記窒化物半導体積層体の深さ方向の配置深さが異なる第2ゲート電極とを有することを特徴とする半導体装置。

【請求項2】

前記第1ゲート電極は、前記窒化物半導体積層体の内部に配置され、かつ、前記第1ゲート電極下部には、前記へテロ接合体が1組以下配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1ゲート電極は、少なくとも1組以上の前記ヘテロ接合体を貫通していることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記第2ゲート電極は、前記窒化物半導体積層体の内部あるいは表面に配置され、かつ、前記第2ゲート電極下部には、前記へテロ接合体が2組以上配置されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

前記第1ゲート電極および第2ゲート電極は、前記窒化物半導体積層体の表面上、又は前記窒化物半導体積層体の内部に設けられた溝部に設けられたゲート絶縁膜を介して配置された導電性材料で構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記第1ゲート電極と前記第2ゲート電極それぞれの長手方向の両端は、前記窒化物半導体積層体の内部および表面上部において前記窒化物半導体積層体の側面に沿って設けられた素子絶縁分離領域に架かるように配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記第1ゲート電極と前記第2ゲート電極は、前記窒化物半導体積層体の内部にそれぞれ所定の間隔を保持して設けられ、前記窒化物半導体積層体の表面においては一体化され電気的に接続されていることを特徴とする請求項6に記載の半導体装置。

【請求項8】

前記第1ゲート電極と前記第2ゲート電極は、前記窒化物半導体積層体の内部および表面で一体化され電気的に接続されていることを特徴とする請求項6に記載の半導体装置。

【請求項9】

前記ヘテロ接合体は、GaNとAlxGa1−xN(0<x≦1)からなることを特徴とする請求項1に記載の半導体装置。

【請求項10】

前記ヘテロ接合体は、GaNとInyAl1−yN(0<y≦1)からなることを特徴とする請求項1に記載の半導体装置。

【請求項1】

第1の窒化物半導体層と、前記第1の窒化物半導体層の禁制帯幅よりも大きい禁制帯幅を有する第2の窒化物半導体層とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体を備え、

前記窒化物半導体積層体に設けられたドレイン電極及びソース電極と、並びに前記ドレイン電極と前記ソース電極に挟まれる位置にあってそれぞれに対向するように設けられたゲート電極とを有し、

前記ドレイン電極と前記ソース電極は、前記窒化物半導体積層体の表面または側面に配置され、

前記ゲート電極は、前記窒化物半導体積層体の深さ方向に設けられた第1ゲート電極と、該第1ゲート電極と前記窒化物半導体積層体の深さ方向の配置深さが異なる第2ゲート電極とを有することを特徴とする半導体装置。

【請求項2】

前記第1ゲート電極は、前記窒化物半導体積層体の内部に配置され、かつ、前記第1ゲート電極下部には、前記へテロ接合体が1組以下配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1ゲート電極は、少なくとも1組以上の前記ヘテロ接合体を貫通していることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記第2ゲート電極は、前記窒化物半導体積層体の内部あるいは表面に配置され、かつ、前記第2ゲート電極下部には、前記へテロ接合体が2組以上配置されていることを特徴とする請求項1または2に記載の半導体装置。

【請求項5】

前記第1ゲート電極および第2ゲート電極は、前記窒化物半導体積層体の表面上、又は前記窒化物半導体積層体の内部に設けられた溝部に設けられたゲート絶縁膜を介して配置された導電性材料で構成されていることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記第1ゲート電極と前記第2ゲート電極それぞれの長手方向の両端は、前記窒化物半導体積層体の内部および表面上部において前記窒化物半導体積層体の側面に沿って設けられた素子絶縁分離領域に架かるように配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記第1ゲート電極と前記第2ゲート電極は、前記窒化物半導体積層体の内部にそれぞれ所定の間隔を保持して設けられ、前記窒化物半導体積層体の表面においては一体化され電気的に接続されていることを特徴とする請求項6に記載の半導体装置。

【請求項8】

前記第1ゲート電極と前記第2ゲート電極は、前記窒化物半導体積層体の内部および表面で一体化され電気的に接続されていることを特徴とする請求項6に記載の半導体装置。

【請求項9】

前記ヘテロ接合体は、GaNとAlxGa1−xN(0<x≦1)からなることを特徴とする請求項1に記載の半導体装置。

【請求項10】

前記ヘテロ接合体は、GaNとInyAl1−yN(0<y≦1)からなることを特徴とする請求項1に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−98284(P2013−98284A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−238406(P2011−238406)

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]