半導体装置

【課題】良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、ガリウム砒素からなる半導体基板10と、半導体基板10上に設けられた能動層15と、能動層15と対向する半導体基板10の下面に設けられた第1Ni層12と、第1Ni層の下面に設けられたCu層14と、Cu層14の下面に設けられた第2Ni層16と、を具備する半導体装置である。本発明によれば、良好な放熱性を確保し、かつ反りを抑制することが可能な半導体装置を提供することできる。

【解決手段】本発明は、ガリウム砒素からなる半導体基板10と、半導体基板10上に設けられた能動層15と、能動層15と対向する半導体基板10の下面に設けられた第1Ni層12と、第1Ni層の下面に設けられたCu層14と、Cu層14の下面に設けられた第2Ni層16と、を具備する半導体装置である。本発明によれば、良好な放熱性を確保し、かつ反りを抑制することが可能な半導体装置を提供することできる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関する。

【背景技術】

【0002】

ガリウム砒素(GaAs)を含む半導体装置は、高周波数増幅用のパワーデバイスとして用いられている。GaAsからなる基板には、例えばFET(Field Effect Transistor:電界効果トランジスタ)等の能動素子、さらには受動素子が形成される。能動素子はその動作により発熱するため、これを放出することが求められる。半導体チップの放熱性を高めるため、GaAsからなる基板を薄くすることがある。しかし、GaAs基板はもろいため、例えば製造工程中のハンドリング等において破損することがある。そこでPHS(Plated Heat Sink:プレーテッドヒートシンク)により、基板を補強し、かつ放熱性を高めることがある。PHSには金(Au)が用いられる。特許文献1には、半導体基板の下面にAuからなるPHSを設ける技術が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平5−166849号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

良好な放熱性を確保するためにはGaAs基板を薄くし、強度を高めるためにはPHSを厚くすることが好ましい。しかし、PHSが厚いと、半導体チップを実装する際に大きな反りが発生することがある。特にPHSに用いられるAu等の熱膨張係数が大きいため、反りが大きくなる。本願発明は、上記課題に鑑み、良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、ガリウム砒素からなる基板と、前記基板上に設けられた能動層と、前記能動層と対向する基板の下面に設けられた第1ニッケルメッキ層と、前記第1ニッケル層の下面に設けられた銅メッキ層と、前記銅メッキ層の下面に設けられた第2ニッケルメッキ層と、を具備する半導体装置である。

【0006】

上記構成において、前記基板の厚さは20μm以上、40μm以下である構成とすることができる。

【0007】

上記構成において、前記第1ニッケルメッキ層の厚さ、及び前記第2ニッケルメッキ層の厚さは、それぞれ0.5μm以上、3μm以下である構成とすることができる。

【0008】

上記構成において、前記基板の表面積が1mm2未満の場合、前記銅メッキ層の厚さは5μm以上8μm未満であり、前記基板の表面積が1mm2以上9mm2未満の場合、前記銅メッキ層の厚さは8μm以上10μm以下であり、前記基板の表面積が9mm2以上の場合、前記銅メッキ層の厚さは16μm以上25μm以下である構成とすることができる。

【0009】

上記構成において、前記第2ニッケルメッキ層の下面に設けられた金層を具備する構成とすることができる。

【0010】

上記構成において、前記金層は前記第1ニッケルメッキ層の側面、前記銅メッキ層の側面、及び前記第2ニッケルメッキ層の側面を覆っている構成とすることができる。

【0011】

上記構成において、前記第2ニッケルメッキ層は前記第1ニッケルメッキ層の側面及び前記銅メッキ層の側面を覆い、前記金層は前記第2ニッケルメッキ層の側面を覆っている構成とすることができる。

【0012】

上記構成において、前記半導体装置は、金錫を含む接着部材により、実装基板に固定される構成とすることができる。

【0013】

上記構成において、前記第2ニッケルメッキ層は、前記銅メッキ層の側面を覆ってなる構成とすることができる。

【発明の効果】

【0014】

本発明によれば、良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0015】

【図1】図1(a)から図1(c)は半導体チップの反りを模式的に例示する断面図である。

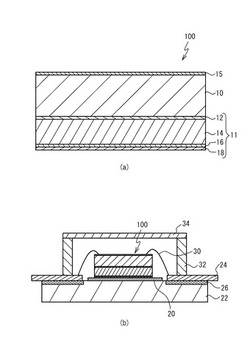

【図2】図2(a)は実施例1に係る半導体チップを例示する断面図である。図2(b)は半導体チップの実装例を示す断面図である。

【図3】図3(a)から図3(c)は実施例1に係る半導体チップの製造方法を例示する断面図である。

【図4】図4(a)から図4(c)は実施例1に係る半導体チップの製造方法を例示する断面図である。

【図5】図5は比較例に係る半導体チップを例示する断面図である。

【図6】図6は実験結果を示すグラフである。

【図7】図7は実施例2に係る半導体チップを例示する断面図である。

【図8】図8(a)から図8(d)は実施例2に係る半導体チップの製造方法を例示する断面図である。

【図9】図9(a)は実施例3に係る半導体チップを例示する断面図である。図9(b)は実施例3の変形例に係る半導体チップを例示する断面図である。

【図10】図10(a)から図10(d)は実施例3に係る半導体チップの製造方法を例示する断面図である。

【発明を実施するための形態】

【0016】

まず半導体チップにおいて発生する反りについて説明する。図1(a)から図1(c)は半導体チップ100aの反りを模式的に例示する断面図である。半導体チップ100aは簡略化している。

【0017】

図1(a)において、半導体基板10に反りは発生していない。図1(b)に示すように、例えば半導体基板10の下面に、例えばAu又はCu等からなるPHS11を設け半導体チップ100aを形成する。PHS11の内部応力により、半導体チップ100aの中央部が浮き上がるような、凸方向の反りが発生する。図1(c)に示すように、半導体チップ100aは、例えば金錫(AuSn)等からなるロウ材20により、Cu等からなる実装基板に実装される。このとき、ロウ材20が軟化する280℃以上まで加熱する。GaAsとPHS11との熱膨張係数の差が大きいため半導体チップ100aに端部が浮き上がるような、凹方向反りが発生する。反り量が大きい場合、半導体チップ100aが実装基板から剥離した状態でロウ材20が硬化し、半導体チップ100aが固定される。その結果、半導体チップ100aにクラックが生じる。次に、実施例1について説明する。

【実施例1】

【0018】

実施例1は、ニッケル(Ni)/Cu/NiからなるPHSを用いることにより実装前の凸方向の反りを大きくすることで、実装後の凹方向の反りを低減する例である。図2(a)は実施例1に係る半導体チップ100を例示する断面図である。図2(a)及び図2(b)において、PHS11は簡略化し、シードメタルは省略している。

【0019】

図2(a)に示すように、GaAsからなる半導体基板10の上面には、GaAsからなりFET等の素子として機能する能動層15が設けられている。能動層15と対向する半導体基板10の下面には、第1Ni層12(第1ニッケルメッキ層)が設けられている。第1Ni層12の下面にCu層14(銅メッキ層)が設けられている。Cu層14の下面に第2Ni層16(第2ニッケルメッキ層)が設けられている。第2Ni層16の下面にAu層18が設けられている。第1Ni層12、Cu層14、第2Ni層16及びAu層18は、半導体基板10に形成された素子において発生した熱を放熱するPHS11として機能する。第1Ni層12は半導体基板10の下面のAuからなるシードメタルに接触し、Cu層14は第1Ni層12の下面に接触している。第2Ni層16はCu層14の下面に接触し、Au層18は第2Ni層16の下面に接触している。

【0020】

半導体基板10の厚さは例えば20〜30μmである。Cu層14の厚さは例えば5〜30μmである。第1Ni層12及び第2Ni層16それぞれの厚さは例えば0.5〜3μmである。Au層18の厚さは例えば0.8〜3μmである。

【0021】

図2(b)は半導体チップ100の実装例を示す断面図である。図2(b)に示すように、半導体チップ100は、PHS11の下面に設けられたロウ材20(接着部材)により実装基板22の上面に搭載されている。実装基板22の絶縁領域26上にはリードフレーム24が設けられている。半導体チップ100とリードフレーム24とは、ボンディングワイヤ30により電気的に接続されている。半導体チップ100は、例えばセラミック等の絶縁体からなる側壁32及びキャップ34により封止されている。ロウ材20は例えばAuSnを含む。実装基板22及びリードフレーム24は例えばCu等の金属を含む。ボンディングワイヤ30は例えばアルミニウム(Al)又はAu等の金属からなる。半導体チップ100において発生した熱は、PHS11及び実装基板22を介して放出される。

【0022】

次に半導体チップ100の製造方法について説明する。図3(a)から図4(c)は実施例1に係る半導体チップ100の製造方法を例示する断面図である。能動層15の図示は省略する。

【0023】

図3(a)に示すように、不図示のワックス等により、例えばガラスからなる支持体40の下面に、GaAsを含むウェハ41を貼り付ける。素子が形成された上面が支持体40の下面に接着する。図3(b)に示すように、ウェハ41を研磨し、ウェハ41を薄くする。図3(c)に示すように、例えばエッチング等により、スクライブラインに沿ってウェハ41の一部を除去し、個片化された半導体基板10を形成する。

【0024】

図4(a)に示すように、支持体40の下面、半導体基板10の下面及び側面に例えばAuからなるシードメタル13を設ける。さらに複数の半導体基板10の間にレジスト42を設ける。図4(b)に示すように、電解メッキ法により第1Ni層12、Cu層14、第2Ni層16、及びAu層18を設ける。シードメタル13は給電線として機能する。第1Ni層12及び第2Ni層16の形成には、例えば55℃の温度において、スルミファン酸Niメッキ浴を用いる。Cu層14の形成には、例えば25℃の温度、2A/dm2の電流密度において、硫酸Cuメッキ浴を用いる。Au層18は、まず薄いAu層(フラッシュメッキ層)を設けた後、厚いAu層を設けることで形成する。Au層18の形成には、例えば55℃の温度、0.1〜0.5A/dm2の電流密度において、亜硫酸Auメッキ浴を用いる。図4(c)に示すように、レジスト42及びシードメタル13を除去する。これにより、半導体チップ100が形成される。

【0025】

電解メッキにより形成されたNiは圧縮応力を有する。PHS11において、Cu層14はNi層に挟まれている。従って半導体チップ100は、図1(b)に示した凸方向に大きく反る。反り量H1は例えば20〜25μmである。半導体チップ100はロウ材20により、実装基板22に実装される。熱膨張係数の差により半導体チップ100は図1(c)に示したように凹方向に反る。凸方向の反り量が大きいため、凹方向の反りは打ち消される。凹方向の反り量H2は例えば30〜50μmである。

【0026】

反り量を検証した実験について説明する。実験では、実施例1と比較例とにおいて、PHSの厚さを変更し、実装前後における反り量を測定した。比較例について説明する。

【0027】

図5は比較例に係る半導体チップ100Rを例示する断面図である。図5に示すように、半導体チップ100Rは半導体基板110、能動層115及びPHS111を備える。半導体基板110はGaAsからなり、PHS111はAuからなる。

【0028】

実施例1及び比較例共に、半導体チップのチップサイズは9.3mm2、半導体基板の厚さは28μmである。チップサイズとは半導体基板の上面の面積(表面積)である。PHS11中の第1Ni層12及び第2Ni層16それぞれの厚さは1μmである。Cu層14の厚さは5、10及び20μmと変化させた。次に実験結果について説明する。

【0029】

図6は実験結果を示すグラフである。横軸はPHS11を構成するCu層14の厚さ、又はPHS111の厚さを示す。縦軸は反り量を示す。図1(b)に示した方向の反り量H1を負の値、図1(c)に示した方向の反り量H2を正の値としている。黒塗りの印は実施例1における反り量、白抜きの印は比較例における反り量を表す。丸は実装前の反り量、四角は実装後の反り量を表す。三角は実装前後における反りの変化を表す。

【0030】

図6に示すように、比較例においては、実装前における反り量は−10〜−5μm程度である。実装後における反り量は80〜90μm程度である。反りの変化量は85〜100μm程度である。図1(a)〜図1(c)において述べたように、実装後の反り量が大きいため、半導体チップの破損、実装の不良が生じる。特にAuの強度が小さいため、PHS111を厚くすることが求められる。PHS111が厚いほど、反り量は大きくなる。

【0031】

これに対し、実施例1においては、実装前における反り量は−30〜−20μm程度である。実装後における反り量は30〜60μm程度である。変化量は60〜80μmである。このように、実施例1によれば、Niにより実装前の反り量が大きくなる。このため実装時の凹方向の反りが低減される。またNi及びCuはAuに比べて強度が大きいため、実施例1におけるPHS11は比較例におけるPHS111より薄くすることができる。従って、反りはより小さくなる。この結果、半導体チップの破損が抑制され、かつ半導体チップの実装が良好に行われる。

【0032】

Cu層14は良好な熱伝導性を有する。従って、半導体基板10からの放熱は効率的に行われる。Cu層14の厚さが5〜20μm、第1Ni層12及び第2Ni層16の厚さが1〜3μmの場合の、PHS11の熱抵抗は4.04〜4.51℃/Wである。比較例におけるPHS111の厚さが28〜40μmの場合、熱抵抗は4.42〜4.61℃/Wである。実施例1によれば、比較例と同程度の放熱性を得ることができる。

【0033】

既述したように、Cu及びNiの強度はAuよりも大きいため、PHS11は薄くすることができる。このため反りの低減、及びコストダウンが可能である。反りを低減するためには、Cu層14は薄い方が好ましい。しかしCu層14が薄いと、強度が低下しハンドリングによる破損が発生することがある。チップサイズが大きいほどクラックが発生しやすい。また図1(c)に示したような半導体チップの剥離も生じやすい。このため、チップサイズが大きい場合、Cu層14を厚くすることが好ましい。

【0034】

反りを低減し、かつ十分な強度が得られるCu層14の厚さを検証するための実験を行った。サンプルとして図2(a)の構成の半導体チップ100を用いた。チップサイズS及びCu層14の厚さTを変更し、反り量及び強度を調べ、適切な厚さを検証した。実験の結果を表1に示す。

【表1】

表1に示すように、チップサイズSが1mm2未満の場合、Cu層14の厚さTは5μm以上8μm未満が好ましい。チップサイズSが1mm2以上9mm2未満の場合、厚さTは8μm以上10μm以下が好ましい。チップサイズSが9mm2以上の場合、厚さTは16μm以上25μm以下が好ましい。なお、チップサイズSが1mm2以上9mm2未満の場合であっても、厚さTを16μm以上25μm以下とすることも可能である。

【0035】

第1Ni層12は、Cuの半導体基板10への拡散を抑制する拡散防止層としても機能する。第2Ni層16は、CuのAu層18への拡散を抑制する拡散防止層としても機能する。第1Ni層12及び第2Ni層16が薄すぎるとCuの拡散の抑制、及び反りの低減が困難になり、また半導体チップ100の強度が小さくなる。厚すぎると熱抵抗が大きくなる。従って、第1Ni層12の厚さは0.5〜3μmが好ましく、0.6〜2.9μm、0.7〜2.8μmとしてもよい。反りを低減し、かつ強度を高めるためには厚さが0.5μm以上であることが好ましい。厚さ1μm以上であれば、反り量は大きく変わらない。その一方、厚さ3μm以上では、熱抵抗が大きくなる。従って、第1Ni層12の厚さは0.5〜3μm、特に1〜3μmが好ましい。第2Ni層16の厚さも同様の範囲が好ましい。また第1Ni層12と第2Ni層16とは異なる厚さを有してもよい。

【0036】

Au層18は、Niの酸化を抑制する酸化防止層、及びCuのロウ材20への拡散を抑制する拡散防止層として機能する。またAuはロウ材20を形成するAuSnとの濡れ性が高いため、実装信頼性が向上する。Cuの拡散を抑制し、高い濡れ性を確保するためにはAu層18は厚いことが好ましい。しかし、厚すぎると反りが大きくなる。従って、Au層18の厚さは0.8〜3μmが好ましく、0.9〜2.9μm、1.0〜2.8μmとしてもよい。

【実施例2】

【0037】

実施例2はAu層18の構成を変えた例である。図7は実施例2に係る半導体チップ200を例示する断面図である。図7に示すように、半導体チップ200におけるAu層18は、第1Ni層12の側面、Cu層14の側面及び第2Ni層16の側面を覆っている。Au層18に保護されるため、第1Ni層12、Cu層14及び第2Ni層16の酸化が抑制される。

【0038】

半導体チップ200の製造方法について説明する。図8(a)から図8(d)は実施例2に係る半導体チップ200の製造方法を例示する断面図である。図3(a)から図4(a)までの工程は実施例2にも共通である。

【0039】

図8(a)に示すように、電解メッキ法により第1Ni層12、Cu層14及び第2Ni層16を設ける。図8(b)に示すように、レジスト42を除去した後、半導体基板10間にレジスト44を設ける。図8(c)に示すように、電解メッキ法により、Au層18を設ける。図8(d)に示すように、レジスト44及びシードメタル13を除去する。これにより半導体チップ200が形成される。

【実施例3】

【0040】

実施例3は第2Ni層16及びAu層18の構成を変更した例である。図9(a)は実施例3に係る半導体チップ300を例示する断面図である。図9(a)に示すように、半導体チップ300における第2Ni層16は第1Ni層12の側面及びCu層14の側面を覆っている。Au層18は第2Ni層16の側面を覆っている。第2Ni層16及びAu層18に保護されるため、第1Ni層12及びCu層14の酸化は抑制される。Au層18に保護されるため、第2Ni層16の酸化も抑制される。図9(b)は実施例3の変形例に係る半導体チップ310を例示する断面図である。図9(b)に示すように、Au層18を設けない場合でも、第2Ni層16がCu層14の側面及び下面を覆ってもよい。

【0041】

図10(a)から図10(d)は実施例3に係る半導体チップ300の製造方法を例示する断面図である。図3(a)から図4(a)までの工程は実施例2にも共通である。

【0042】

図10(a)に示すように、電解メッキ法により、第1Ni層12及びCu層14を設ける。図10(b)に示すように、レジスト42を除去した後、レジスト44を設ける。図10(c)に示すように、電解メッキ法により第2Ni層16及びAu層18を設ける。図10(d)に示すように、レジスト44及びシードメタル13を除去する。これにより半導体チップ300が形成される。半導体チップ310の製造方法の説明は省略する。

【0043】

実施例1〜3は、FET以外に、例えばIGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)、サイリスタ等のパワーデバイスを含む半導体装置に適用することができる。

【0044】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0045】

10 半導体基板

11 PHS

12 第1Ni層

14 Cu層

15 能動層

16 第2Ni層

18 Au層

20 ロウ材

22 実装基板

100、200、300、310 半導体チップ

【技術分野】

【0001】

本発明は半導体装置に関する。

【背景技術】

【0002】

ガリウム砒素(GaAs)を含む半導体装置は、高周波数増幅用のパワーデバイスとして用いられている。GaAsからなる基板には、例えばFET(Field Effect Transistor:電界効果トランジスタ)等の能動素子、さらには受動素子が形成される。能動素子はその動作により発熱するため、これを放出することが求められる。半導体チップの放熱性を高めるため、GaAsからなる基板を薄くすることがある。しかし、GaAs基板はもろいため、例えば製造工程中のハンドリング等において破損することがある。そこでPHS(Plated Heat Sink:プレーテッドヒートシンク)により、基板を補強し、かつ放熱性を高めることがある。PHSには金(Au)が用いられる。特許文献1には、半導体基板の下面にAuからなるPHSを設ける技術が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平5−166849号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

良好な放熱性を確保するためにはGaAs基板を薄くし、強度を高めるためにはPHSを厚くすることが好ましい。しかし、PHSが厚いと、半導体チップを実装する際に大きな反りが発生することがある。特にPHSに用いられるAu等の熱膨張係数が大きいため、反りが大きくなる。本願発明は、上記課題に鑑み、良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、ガリウム砒素からなる基板と、前記基板上に設けられた能動層と、前記能動層と対向する基板の下面に設けられた第1ニッケルメッキ層と、前記第1ニッケル層の下面に設けられた銅メッキ層と、前記銅メッキ層の下面に設けられた第2ニッケルメッキ層と、を具備する半導体装置である。

【0006】

上記構成において、前記基板の厚さは20μm以上、40μm以下である構成とすることができる。

【0007】

上記構成において、前記第1ニッケルメッキ層の厚さ、及び前記第2ニッケルメッキ層の厚さは、それぞれ0.5μm以上、3μm以下である構成とすることができる。

【0008】

上記構成において、前記基板の表面積が1mm2未満の場合、前記銅メッキ層の厚さは5μm以上8μm未満であり、前記基板の表面積が1mm2以上9mm2未満の場合、前記銅メッキ層の厚さは8μm以上10μm以下であり、前記基板の表面積が9mm2以上の場合、前記銅メッキ層の厚さは16μm以上25μm以下である構成とすることができる。

【0009】

上記構成において、前記第2ニッケルメッキ層の下面に設けられた金層を具備する構成とすることができる。

【0010】

上記構成において、前記金層は前記第1ニッケルメッキ層の側面、前記銅メッキ層の側面、及び前記第2ニッケルメッキ層の側面を覆っている構成とすることができる。

【0011】

上記構成において、前記第2ニッケルメッキ層は前記第1ニッケルメッキ層の側面及び前記銅メッキ層の側面を覆い、前記金層は前記第2ニッケルメッキ層の側面を覆っている構成とすることができる。

【0012】

上記構成において、前記半導体装置は、金錫を含む接着部材により、実装基板に固定される構成とすることができる。

【0013】

上記構成において、前記第2ニッケルメッキ層は、前記銅メッキ層の側面を覆ってなる構成とすることができる。

【発明の効果】

【0014】

本発明によれば、良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0015】

【図1】図1(a)から図1(c)は半導体チップの反りを模式的に例示する断面図である。

【図2】図2(a)は実施例1に係る半導体チップを例示する断面図である。図2(b)は半導体チップの実装例を示す断面図である。

【図3】図3(a)から図3(c)は実施例1に係る半導体チップの製造方法を例示する断面図である。

【図4】図4(a)から図4(c)は実施例1に係る半導体チップの製造方法を例示する断面図である。

【図5】図5は比較例に係る半導体チップを例示する断面図である。

【図6】図6は実験結果を示すグラフである。

【図7】図7は実施例2に係る半導体チップを例示する断面図である。

【図8】図8(a)から図8(d)は実施例2に係る半導体チップの製造方法を例示する断面図である。

【図9】図9(a)は実施例3に係る半導体チップを例示する断面図である。図9(b)は実施例3の変形例に係る半導体チップを例示する断面図である。

【図10】図10(a)から図10(d)は実施例3に係る半導体チップの製造方法を例示する断面図である。

【発明を実施するための形態】

【0016】

まず半導体チップにおいて発生する反りについて説明する。図1(a)から図1(c)は半導体チップ100aの反りを模式的に例示する断面図である。半導体チップ100aは簡略化している。

【0017】

図1(a)において、半導体基板10に反りは発生していない。図1(b)に示すように、例えば半導体基板10の下面に、例えばAu又はCu等からなるPHS11を設け半導体チップ100aを形成する。PHS11の内部応力により、半導体チップ100aの中央部が浮き上がるような、凸方向の反りが発生する。図1(c)に示すように、半導体チップ100aは、例えば金錫(AuSn)等からなるロウ材20により、Cu等からなる実装基板に実装される。このとき、ロウ材20が軟化する280℃以上まで加熱する。GaAsとPHS11との熱膨張係数の差が大きいため半導体チップ100aに端部が浮き上がるような、凹方向反りが発生する。反り量が大きい場合、半導体チップ100aが実装基板から剥離した状態でロウ材20が硬化し、半導体チップ100aが固定される。その結果、半導体チップ100aにクラックが生じる。次に、実施例1について説明する。

【実施例1】

【0018】

実施例1は、ニッケル(Ni)/Cu/NiからなるPHSを用いることにより実装前の凸方向の反りを大きくすることで、実装後の凹方向の反りを低減する例である。図2(a)は実施例1に係る半導体チップ100を例示する断面図である。図2(a)及び図2(b)において、PHS11は簡略化し、シードメタルは省略している。

【0019】

図2(a)に示すように、GaAsからなる半導体基板10の上面には、GaAsからなりFET等の素子として機能する能動層15が設けられている。能動層15と対向する半導体基板10の下面には、第1Ni層12(第1ニッケルメッキ層)が設けられている。第1Ni層12の下面にCu層14(銅メッキ層)が設けられている。Cu層14の下面に第2Ni層16(第2ニッケルメッキ層)が設けられている。第2Ni層16の下面にAu層18が設けられている。第1Ni層12、Cu層14、第2Ni層16及びAu層18は、半導体基板10に形成された素子において発生した熱を放熱するPHS11として機能する。第1Ni層12は半導体基板10の下面のAuからなるシードメタルに接触し、Cu層14は第1Ni層12の下面に接触している。第2Ni層16はCu層14の下面に接触し、Au層18は第2Ni層16の下面に接触している。

【0020】

半導体基板10の厚さは例えば20〜30μmである。Cu層14の厚さは例えば5〜30μmである。第1Ni層12及び第2Ni層16それぞれの厚さは例えば0.5〜3μmである。Au層18の厚さは例えば0.8〜3μmである。

【0021】

図2(b)は半導体チップ100の実装例を示す断面図である。図2(b)に示すように、半導体チップ100は、PHS11の下面に設けられたロウ材20(接着部材)により実装基板22の上面に搭載されている。実装基板22の絶縁領域26上にはリードフレーム24が設けられている。半導体チップ100とリードフレーム24とは、ボンディングワイヤ30により電気的に接続されている。半導体チップ100は、例えばセラミック等の絶縁体からなる側壁32及びキャップ34により封止されている。ロウ材20は例えばAuSnを含む。実装基板22及びリードフレーム24は例えばCu等の金属を含む。ボンディングワイヤ30は例えばアルミニウム(Al)又はAu等の金属からなる。半導体チップ100において発生した熱は、PHS11及び実装基板22を介して放出される。

【0022】

次に半導体チップ100の製造方法について説明する。図3(a)から図4(c)は実施例1に係る半導体チップ100の製造方法を例示する断面図である。能動層15の図示は省略する。

【0023】

図3(a)に示すように、不図示のワックス等により、例えばガラスからなる支持体40の下面に、GaAsを含むウェハ41を貼り付ける。素子が形成された上面が支持体40の下面に接着する。図3(b)に示すように、ウェハ41を研磨し、ウェハ41を薄くする。図3(c)に示すように、例えばエッチング等により、スクライブラインに沿ってウェハ41の一部を除去し、個片化された半導体基板10を形成する。

【0024】

図4(a)に示すように、支持体40の下面、半導体基板10の下面及び側面に例えばAuからなるシードメタル13を設ける。さらに複数の半導体基板10の間にレジスト42を設ける。図4(b)に示すように、電解メッキ法により第1Ni層12、Cu層14、第2Ni層16、及びAu層18を設ける。シードメタル13は給電線として機能する。第1Ni層12及び第2Ni層16の形成には、例えば55℃の温度において、スルミファン酸Niメッキ浴を用いる。Cu層14の形成には、例えば25℃の温度、2A/dm2の電流密度において、硫酸Cuメッキ浴を用いる。Au層18は、まず薄いAu層(フラッシュメッキ層)を設けた後、厚いAu層を設けることで形成する。Au層18の形成には、例えば55℃の温度、0.1〜0.5A/dm2の電流密度において、亜硫酸Auメッキ浴を用いる。図4(c)に示すように、レジスト42及びシードメタル13を除去する。これにより、半導体チップ100が形成される。

【0025】

電解メッキにより形成されたNiは圧縮応力を有する。PHS11において、Cu層14はNi層に挟まれている。従って半導体チップ100は、図1(b)に示した凸方向に大きく反る。反り量H1は例えば20〜25μmである。半導体チップ100はロウ材20により、実装基板22に実装される。熱膨張係数の差により半導体チップ100は図1(c)に示したように凹方向に反る。凸方向の反り量が大きいため、凹方向の反りは打ち消される。凹方向の反り量H2は例えば30〜50μmである。

【0026】

反り量を検証した実験について説明する。実験では、実施例1と比較例とにおいて、PHSの厚さを変更し、実装前後における反り量を測定した。比較例について説明する。

【0027】

図5は比較例に係る半導体チップ100Rを例示する断面図である。図5に示すように、半導体チップ100Rは半導体基板110、能動層115及びPHS111を備える。半導体基板110はGaAsからなり、PHS111はAuからなる。

【0028】

実施例1及び比較例共に、半導体チップのチップサイズは9.3mm2、半導体基板の厚さは28μmである。チップサイズとは半導体基板の上面の面積(表面積)である。PHS11中の第1Ni層12及び第2Ni層16それぞれの厚さは1μmである。Cu層14の厚さは5、10及び20μmと変化させた。次に実験結果について説明する。

【0029】

図6は実験結果を示すグラフである。横軸はPHS11を構成するCu層14の厚さ、又はPHS111の厚さを示す。縦軸は反り量を示す。図1(b)に示した方向の反り量H1を負の値、図1(c)に示した方向の反り量H2を正の値としている。黒塗りの印は実施例1における反り量、白抜きの印は比較例における反り量を表す。丸は実装前の反り量、四角は実装後の反り量を表す。三角は実装前後における反りの変化を表す。

【0030】

図6に示すように、比較例においては、実装前における反り量は−10〜−5μm程度である。実装後における反り量は80〜90μm程度である。反りの変化量は85〜100μm程度である。図1(a)〜図1(c)において述べたように、実装後の反り量が大きいため、半導体チップの破損、実装の不良が生じる。特にAuの強度が小さいため、PHS111を厚くすることが求められる。PHS111が厚いほど、反り量は大きくなる。

【0031】

これに対し、実施例1においては、実装前における反り量は−30〜−20μm程度である。実装後における反り量は30〜60μm程度である。変化量は60〜80μmである。このように、実施例1によれば、Niにより実装前の反り量が大きくなる。このため実装時の凹方向の反りが低減される。またNi及びCuはAuに比べて強度が大きいため、実施例1におけるPHS11は比較例におけるPHS111より薄くすることができる。従って、反りはより小さくなる。この結果、半導体チップの破損が抑制され、かつ半導体チップの実装が良好に行われる。

【0032】

Cu層14は良好な熱伝導性を有する。従って、半導体基板10からの放熱は効率的に行われる。Cu層14の厚さが5〜20μm、第1Ni層12及び第2Ni層16の厚さが1〜3μmの場合の、PHS11の熱抵抗は4.04〜4.51℃/Wである。比較例におけるPHS111の厚さが28〜40μmの場合、熱抵抗は4.42〜4.61℃/Wである。実施例1によれば、比較例と同程度の放熱性を得ることができる。

【0033】

既述したように、Cu及びNiの強度はAuよりも大きいため、PHS11は薄くすることができる。このため反りの低減、及びコストダウンが可能である。反りを低減するためには、Cu層14は薄い方が好ましい。しかしCu層14が薄いと、強度が低下しハンドリングによる破損が発生することがある。チップサイズが大きいほどクラックが発生しやすい。また図1(c)に示したような半導体チップの剥離も生じやすい。このため、チップサイズが大きい場合、Cu層14を厚くすることが好ましい。

【0034】

反りを低減し、かつ十分な強度が得られるCu層14の厚さを検証するための実験を行った。サンプルとして図2(a)の構成の半導体チップ100を用いた。チップサイズS及びCu層14の厚さTを変更し、反り量及び強度を調べ、適切な厚さを検証した。実験の結果を表1に示す。

【表1】

表1に示すように、チップサイズSが1mm2未満の場合、Cu層14の厚さTは5μm以上8μm未満が好ましい。チップサイズSが1mm2以上9mm2未満の場合、厚さTは8μm以上10μm以下が好ましい。チップサイズSが9mm2以上の場合、厚さTは16μm以上25μm以下が好ましい。なお、チップサイズSが1mm2以上9mm2未満の場合であっても、厚さTを16μm以上25μm以下とすることも可能である。

【0035】

第1Ni層12は、Cuの半導体基板10への拡散を抑制する拡散防止層としても機能する。第2Ni層16は、CuのAu層18への拡散を抑制する拡散防止層としても機能する。第1Ni層12及び第2Ni層16が薄すぎるとCuの拡散の抑制、及び反りの低減が困難になり、また半導体チップ100の強度が小さくなる。厚すぎると熱抵抗が大きくなる。従って、第1Ni層12の厚さは0.5〜3μmが好ましく、0.6〜2.9μm、0.7〜2.8μmとしてもよい。反りを低減し、かつ強度を高めるためには厚さが0.5μm以上であることが好ましい。厚さ1μm以上であれば、反り量は大きく変わらない。その一方、厚さ3μm以上では、熱抵抗が大きくなる。従って、第1Ni層12の厚さは0.5〜3μm、特に1〜3μmが好ましい。第2Ni層16の厚さも同様の範囲が好ましい。また第1Ni層12と第2Ni層16とは異なる厚さを有してもよい。

【0036】

Au層18は、Niの酸化を抑制する酸化防止層、及びCuのロウ材20への拡散を抑制する拡散防止層として機能する。またAuはロウ材20を形成するAuSnとの濡れ性が高いため、実装信頼性が向上する。Cuの拡散を抑制し、高い濡れ性を確保するためにはAu層18は厚いことが好ましい。しかし、厚すぎると反りが大きくなる。従って、Au層18の厚さは0.8〜3μmが好ましく、0.9〜2.9μm、1.0〜2.8μmとしてもよい。

【実施例2】

【0037】

実施例2はAu層18の構成を変えた例である。図7は実施例2に係る半導体チップ200を例示する断面図である。図7に示すように、半導体チップ200におけるAu層18は、第1Ni層12の側面、Cu層14の側面及び第2Ni層16の側面を覆っている。Au層18に保護されるため、第1Ni層12、Cu層14及び第2Ni層16の酸化が抑制される。

【0038】

半導体チップ200の製造方法について説明する。図8(a)から図8(d)は実施例2に係る半導体チップ200の製造方法を例示する断面図である。図3(a)から図4(a)までの工程は実施例2にも共通である。

【0039】

図8(a)に示すように、電解メッキ法により第1Ni層12、Cu層14及び第2Ni層16を設ける。図8(b)に示すように、レジスト42を除去した後、半導体基板10間にレジスト44を設ける。図8(c)に示すように、電解メッキ法により、Au層18を設ける。図8(d)に示すように、レジスト44及びシードメタル13を除去する。これにより半導体チップ200が形成される。

【実施例3】

【0040】

実施例3は第2Ni層16及びAu層18の構成を変更した例である。図9(a)は実施例3に係る半導体チップ300を例示する断面図である。図9(a)に示すように、半導体チップ300における第2Ni層16は第1Ni層12の側面及びCu層14の側面を覆っている。Au層18は第2Ni層16の側面を覆っている。第2Ni層16及びAu層18に保護されるため、第1Ni層12及びCu層14の酸化は抑制される。Au層18に保護されるため、第2Ni層16の酸化も抑制される。図9(b)は実施例3の変形例に係る半導体チップ310を例示する断面図である。図9(b)に示すように、Au層18を設けない場合でも、第2Ni層16がCu層14の側面及び下面を覆ってもよい。

【0041】

図10(a)から図10(d)は実施例3に係る半導体チップ300の製造方法を例示する断面図である。図3(a)から図4(a)までの工程は実施例2にも共通である。

【0042】

図10(a)に示すように、電解メッキ法により、第1Ni層12及びCu層14を設ける。図10(b)に示すように、レジスト42を除去した後、レジスト44を設ける。図10(c)に示すように、電解メッキ法により第2Ni層16及びAu層18を設ける。図10(d)に示すように、レジスト44及びシードメタル13を除去する。これにより半導体チップ300が形成される。半導体チップ310の製造方法の説明は省略する。

【0043】

実施例1〜3は、FET以外に、例えばIGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)、サイリスタ等のパワーデバイスを含む半導体装置に適用することができる。

【0044】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0045】

10 半導体基板

11 PHS

12 第1Ni層

14 Cu層

15 能動層

16 第2Ni層

18 Au層

20 ロウ材

22 実装基板

100、200、300、310 半導体チップ

【特許請求の範囲】

【請求項1】

ガリウム砒素からなる基板と、

前記基板上に設けられた能動層と、

前記能動層と対向する基板の下面に設けられた第1ニッケルメッキ層と、

前記第1ニッケル層の下面に設けられた銅メッキ層と、

前記銅メッキ層の下面に設けられた第2ニッケルメッキ層と、を具備することを特徴とする半導体装置。

【請求項2】

前記基板の厚さは20μm以上、40μm以下であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第1ニッケルメッキ層の厚さ、及び前記第2ニッケルメッキ層の厚さは、それぞれ0.5μm以上、3μm以下であることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記基板の表面積が1mm2未満の場合、前記銅メッキ層の厚さは5μm以上8μm未満であり、前記基板の表面積が1mm2以上9mm2未満の場合、前記銅メッキ層の厚さは8μm以上10μm以下であり、前記基板の表面積が9mm2以上の場合、前記銅メッキ層の厚さは16μm以上25μm以下であることを特徴とする請求項1から3いずれか一項記載の半導体装置。

【請求項5】

前記第2ニッケルメッキ層の下面に設けられた金層を具備することを特徴とする請求項1から4いずれか一項記載の半導体装置。

【請求項6】

前記金層は前記第1ニッケルメッキ層の側面、前記銅メッキ層の側面、及び前記第2ニッケルメッキ層の側面を覆っていることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記第2ニッケルメッキ層は前記第1ニッケルメッキ層の側面及び前記銅メッキ層の側面を覆い、

前記金層は前記第2ニッケルメッキ層の側面を覆っていることを特徴とする請求項5記載の半導体装置。

【請求項8】

前記半導体装置は、金錫を含む接着部材により、実装基板に固定されることを特徴とする請求項1から7いずれか一項記載の半導体装置。

【請求項9】

前記第2ニッケルメッキ層は、前記銅メッキ層の側面を覆ってなることを特徴とする請求項1から4いずれか一項記載の半導体装置。

【請求項1】

ガリウム砒素からなる基板と、

前記基板上に設けられた能動層と、

前記能動層と対向する基板の下面に設けられた第1ニッケルメッキ層と、

前記第1ニッケル層の下面に設けられた銅メッキ層と、

前記銅メッキ層の下面に設けられた第2ニッケルメッキ層と、を具備することを特徴とする半導体装置。

【請求項2】

前記基板の厚さは20μm以上、40μm以下であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第1ニッケルメッキ層の厚さ、及び前記第2ニッケルメッキ層の厚さは、それぞれ0.5μm以上、3μm以下であることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記基板の表面積が1mm2未満の場合、前記銅メッキ層の厚さは5μm以上8μm未満であり、前記基板の表面積が1mm2以上9mm2未満の場合、前記銅メッキ層の厚さは8μm以上10μm以下であり、前記基板の表面積が9mm2以上の場合、前記銅メッキ層の厚さは16μm以上25μm以下であることを特徴とする請求項1から3いずれか一項記載の半導体装置。

【請求項5】

前記第2ニッケルメッキ層の下面に設けられた金層を具備することを特徴とする請求項1から4いずれか一項記載の半導体装置。

【請求項6】

前記金層は前記第1ニッケルメッキ層の側面、前記銅メッキ層の側面、及び前記第2ニッケルメッキ層の側面を覆っていることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記第2ニッケルメッキ層は前記第1ニッケルメッキ層の側面及び前記銅メッキ層の側面を覆い、

前記金層は前記第2ニッケルメッキ層の側面を覆っていることを特徴とする請求項5記載の半導体装置。

【請求項8】

前記半導体装置は、金錫を含む接着部材により、実装基板に固定されることを特徴とする請求項1から7いずれか一項記載の半導体装置。

【請求項9】

前記第2ニッケルメッキ層は、前記銅メッキ層の側面を覆ってなることを特徴とする請求項1から4いずれか一項記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−98481(P2013−98481A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−242437(P2011−242437)

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000154325)住友電工デバイス・イノベーション株式会社 (291)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000154325)住友電工デバイス・イノベーション株式会社 (291)

【Fターム(参考)】

[ Back to top ]