半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタなどの半導体素子を含む回路を有する半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性のものと、電力の供給がなくなっても記憶内容は保持される不揮発性のものとに大別される。

【0003】

揮発性の半導体記憶装置の代表的な例としては、DRAM(Dynamic Random Access Memory)がある。DRAMは、トランジスタを選択し、該トランジスタと接続するキャパシタに電荷を蓄積することで、情報を記憶する。

【0004】

DRAMでは、情報を読み出すと同時にキャパシタに蓄積された電荷が失われるため、情報の読み出しの度に再度の書き込みが必要となる。また、DRAMを構成するトランジスタがオフ状態のときでも、ソースおよびドレイン間のリーク電流(オフ電流)などによって電荷が失われるため、データの保持期間が短い。このため、所定の周期で書き込み動作(リフレッシュ動作)が必要となり、消費電力が増大してしまう。また、電力の供給がなくなるとデータが失われるため、電力の供給を止めた状態で長期間に渡ってデータを保持するためには、磁性材料や光学材料を利用した別の記憶装置が必要となる。

【0005】

揮発性の半導体記憶装置の別の例としてはSRAM(Static Random Access Memory)がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においてはDRAMより有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりのコストが高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと同様である。

【0006】

不揮発性の半導体記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く、DRAMで必要なリフレッシュ動作が不要であるという利点を有している(特許文献1参照。)。

【0007】

しかし、書き込みの際に生じるトンネル電流によってフラッシュメモリを構成するゲート絶縁膜が劣化するため、所定回数の書き込みによって半導体記憶装置として機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各メモリセルへの書き込み回数を均一化する手法が採られるが、これを実現するためには複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。したがって、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きである。

【0008】

また、フラッシュメモリは、フローティングゲートに電荷を注入するため、またはその電荷を除去するために高い電圧が必要となる。また、そのための回路も必要である。さらに、電荷の注入または除去のためには比較的長い時間を要し、書き込み、消去の高速化が容易ではないという問題もある。

【0009】

上述した半導体記憶装置を構成するトランジスタは、主にシリコン系半導体が用いられる。ところで、近年になり、酸化物半導体を用いたトランジスタが注目されている。酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタよりも電界効果移動度が高い。そのため、酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタに置き換わる技術として期待されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開昭57−105889号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

従来のDRAMのように頻繁にリフレッシュ動作を繰り返さなくてもデータの保持が可能であり、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供することを目的の一つとする。

【0012】

さらに、上述の新たな構造の半導体記憶装置の集積度を高め、単位面積あたりの記憶容量を増加させることを目的の一つとする。

【課題を解決するための手段】

【0013】

本発明の一態様である半導体記憶装置は、一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を第1のトランジスタの該一対の電極の一方と共有するキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

【0014】

なお、「上面の高さ」とは、特に断りがない限り基板表面を基準としたときの高さをいう。

【0015】

また、本発明の一態様である半導体記憶装置を構成するメモリセルは、前述のキャパシタに保持される電位の高低によってデータが区別される。

【0016】

または、本発明の一態様であるメモリセルは、第1のトランジスタの一対の電極の一方およびキャパシタとゲートが接続される第2のトランジスタを有し、キャパシタに保持される電位に応じて、第2のトランジスタのオン、オフが切り替わることを利用してデータが区別される。

【0017】

なお、第1のトランジスタを構成する一対の電極間距離は、最小加工寸法(Fとも表記する。)となるように設けられる。

【0018】

第1のゲート電極は、間隔がFであるソース電極およびドレイン電極(一対の電極)の少なくとも側壁と接して設けられた絶縁膜を介してソース電極およびドレイン電極間に設けられる。そのため、第1のゲート電極は、Fよりも絶縁膜の厚さの2倍分だけ幅が小さくなる。

【0019】

なお、第1のゲート電極は、絶縁膜上に、ソース電極およびドレイン電極間を埋めるように導電膜を成膜した後、化学機械研磨(CMP:Chemical Mechanical Polishing)処理によって、導電膜のソース電極およびドレイン電極上の部分を取り除くことで形成できる。このようにして設けられた第1のゲート電極は、自己整合的に形成されるため、幅をF未満とすることができる。そのため、個々のメモリセルのサイズの小さくでき、集積度の高い半導体記憶装置を得ることができる。

【0020】

第1のゲート電極および第1のゲート絶縁膜について、形成方法を以下に簡単に示す。第1のゲート電極の上面の高さが、一対の電極の上面の高さよりも低くなるように設け、第1のゲート電極および一対の電極上に第1のゲート絶縁膜となる絶縁膜を成膜する。次に、CMP処理により第1のゲート絶縁膜となる絶縁膜の一部を除去する。これを、一対の電極が露出するまで行うと、第1のゲート絶縁膜が得られる。このようにして形成した第1のゲート絶縁膜は、絶縁膜を介して一対の電極間にあり、かつ第1のゲート電極上に設けられる。

【0021】

なお、シリコン系半導体を用いたトランジスタは、しきい値電圧などの電気的特性を制御する技術が確立されているのに対し、酸化物半導体を用いたトランジスタは、当該技術は確立されていない。具体的には、シリコン系半導体材料を用いたトランジスタは、不純物ドーピングなどによって、しきい値電圧の制御が可能であるのに対し、酸化物半導体材料を用いたトランジスタは、不純物ドーピングなどによって、しきい値電圧を制御することが困難である。

【0022】

上記構造の第1のトランジスタは、第1のゲート電極に電位を印加することでしきい値電圧を制御することができる。なお、電源電位の供給が止まっても第1のゲート電極に電位が固定できるようにするために、第1のゲート電極と接続するキャパシタおよびスイッチを設けてもよい。

【0023】

なお、第1のゲート電極は、メモリセルを取り囲むように設けられる。そのため、第1のゲート電極がガードリングの機能を有し、半導体記憶装置の静電破壊を防止でき、歩留まりが高く、信頼性の高い半導体記憶装置を得ることができる。

【0024】

酸化物半導体膜として、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を選択すればよい。バンドギャップを前述の数値以上とすることによって、トランジスタのオフ電流を小さくすることができる。なお、バンドギャップが前述の数値以上であり、かつ半導体特性を示す酸化物半導体ではない材料に置き換えても構わない。

【0025】

また、酸化物半導体膜は、間接的または直接的にキャリアを生成する不純物(水素、アルカリ金属、アルカリ土類金属、希ガス、窒素、リンおよびホウ素など)の濃度が低くなるよう高純度化されていると好ましい。さらに、酸素欠損を極力低減することが好ましい。酸化物半導体膜中の不純物および酸素欠損を低減することによって、酸化物半導体膜中において意図しないキャリアの生成が低減され、トランジスタのオフ電流を小さくすることができる。

【0026】

このように、第1のトランジスタのオフ電流を小さくすることで、第1のトランジスタをオフ状態としたときにキャパシタの電荷を長期間に渡って保持することができる。したがって、長期間に渡ってデータを保持することのできる半導体記憶装置が得られる。

【発明の効果】

【0027】

しきい値電圧が制御され、かつオフ電流の極めて小さいトランジスタを用いることで、リフレッシュ動作の頻度が低く、消費電力の小さい半導体記憶装置を提供することができる。

【0028】

また、個々のメモリセルの面積の小さい、集積度の高い半導体記憶装置を提供することができる。

【0029】

また、個々のメモリセルを囲むように等電位の導電膜が設けられるため、ガードリングの機能を有し、静電破壊が起こりにくい半導体記憶装置を提供することができる。

【図面の簡単な説明】

【0030】

【図1】半導体記憶装置を構成するメモリセルの例を示す上面図および断面図。

【図2】図1に示すメモリセルをマトリクス状に組み合わせたメモリセルアレイの例を示す回路図。

【図3】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図4】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図5】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図6】半導体記憶装置を構成するメモリセルの例を示す上面図および断面図。

【図7】図6に示すメモリセルをマトリクス状に組み合わせたメモリセルアレイの例を示す回路図。

【図8】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図9】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図10】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図11】本発明の一態様であるトランジスタを用いたCPUの具体例を示すブロック図およびその一部の回路図。

【図12】本発明の一態様である電子機器の例を示す斜視図。

【図13】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図14】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図15】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図16】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図17】計算によって得られた電界効果移動度のVgs依存性を説明する図。

【図18】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図19】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図20】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図21】計算に用いたトランジスタの構造を示す断面図。

【図22】トランジスタの構造を示す断面図および上面図。

【図23】試料1および試料2であるトランジスタのVgs−Ids特性および電界効果移動度を示す図。

【図24】試料1であるトランジスタのBT試験前後のVgs−Ids特性を示す図。

【図25】試料2であるトランジスタのBT試験前後のVgs−Ids特性を示す図。

【図26】試料2であるトランジスタのしきい値電圧および電界効果移動度と基板温度の関係を示す図。

【図27】酸化物半導体膜を用いたトランジスタのオフ電流を示す図。

【図28】酸化物半導体膜のXRDスペクトルを示す図。

【発明を実施するための形態】

【0031】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更しうることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0032】

以下、本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0033】

また、電圧は、ある電位と基準の電位(例えばソース電位、接地電位)との電位差のことを示す場合が多い。よって、電圧を電位に置き換えることができる。また、電位VH、電位VDD、電位GNDなどのように電位を表記したとしても、厳密に電位VH、電位VDD、電位GNDとなっていないことがある。よって、電位VH、電位VDD、電位GNDは、電位VH近傍、電位VDD近傍、電位GND近傍と置き換えることができる。なお、「接地する」と「GNDに接続する」は同義である。

【0034】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

【0035】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0036】

なお、本明細書では、マトリクスにおいて特定の行や列、位置を扱う場合には、符号に座標を示す記号をつけて、例えば、「メモリセルMC_n_m」、「ビット線BL_m」というように表記するが、特に、行や列、位置を特定しない場合や集合的に扱う場合、またはどの位置にあるか明らかである場合には、「メモリセルMC」、「ビット線BL」、または、単に「メモリセル」、「ビット線」というように表記することもある。

【0037】

(実施の形態1)

本実施の形態では、本発明の一態様を適用した半導体記憶装置について図1乃至図5を用いて説明する。

【0038】

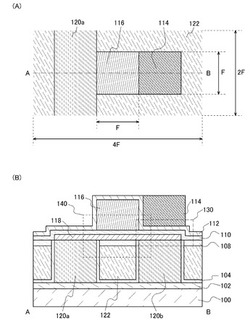

図1は、半導体記憶装置であるDRAMの一つのメモリセルを示す上面図(図1(A)参照。)および断面図(図1(B)参照。)である。

【0039】

図1(A)より、メモリセルのサイズは8F2(縦2F×横4F)である。

【0040】

図1(B)より、メモリセルは、酸化物半導体膜を用いたトランジスタ140と、キャパシタ130と、を有する。

【0041】

なお、メモリセルは、基板100上の下地絶縁膜102上に設けられる。なお、基板100の表面状態によっては、下地絶縁膜102を設けない構造としても構わない。

【0042】

トランジスタ140は、導電膜120aおよび導電膜120bと、導電膜120aおよび導電膜120bの側面と接して設けられた第1の絶縁膜104と、第1の絶縁膜104を介して導電膜120aおよび導電膜120b間に設けられ、導電膜120aおよび導電膜120bの上面の高さよりも上面の高さの低い第1のゲート電極122と、第1のゲート電極122上に設けられた第1のゲート絶縁膜108と、第1のゲート絶縁膜108、導電膜120aおよび導電膜120bと接して設けられた酸化物半導体膜118と、酸化物半導体膜118上に設けられた第2のゲート絶縁膜110と、第2のゲート絶縁膜110を介して酸化物半導体膜118上に設けられた第2のゲート電極116と、を有する。なお、トランジスタ140を覆って第2の絶縁膜112を設けても構わない。

【0043】

キャパシタ130は、導電膜120b、第2のゲート絶縁膜110および電極114を有する。電極114は第2の絶縁膜112の側面と接するように図示されているが、これに限定されるものではない。例えば、第2のゲート電極116と一部が重畳しても構わないし、第1のゲート電極122と同一層である導電膜と一部が重畳しても構わない。なお、電極114の代わりに第1のゲート電極122と同一層の導電膜を用いても構わない。第1のゲート電極122と同一層の導電膜をキャパシタに用いると、導電膜120bの側面に沿ってキャパシタ130を作製することができる。そのため、キャパシタ130の誘電体層が同じと仮定したときで導電膜120bの厚さがFの3分の1より厚いとき、電極114を用いた場合よりも容量を大きくすることができる。なお、ここでは便宜上Fを用いて厚さを記載するが、Fは上面形状における最小加工寸法であるため、当然ながら導電膜120bの厚さをFよりも小さくすることが可能である。

【0044】

なお、キャパシタ130に電極114を用いた場合、キャパシタ130の誘電体層は第2のゲート絶縁膜110および第2の絶縁膜112となる。また、キャパシタ130に第1のゲート電極122と同一層の導電膜を用いた場合、キャパシタ130の誘電体層は第1の絶縁膜104となる。

【0045】

ここで、導電膜120aはトランジスタ140のソース電極として機能する。また、導電膜120bはトランジスタ140のドレイン電極およびキャパシタ130の一対の電極の一方として機能する。

【0046】

ここで、第1のゲート電極122は、トランジスタ140のしきい値電圧を制御するためのバックゲート電極としての機能を有する。また、第1のゲート電極122と同一層である導電膜がメモリセルを囲むように設けられており、該導電膜はガードリングとしての機能を有し、メモリセルの静電破壊を防止することができる。

【0047】

トランジスタ140の導電膜120aは、ビット線と接続する。ここでは、導電膜120aが延在しビット線を形成している場合について記載する。

【0048】

また、図示しないが、トランジスタ140の第2のゲート電極116は、ワード線と接続する。

【0049】

酸化物半導体膜118は、厚さを1nm以上50nm以下とする。好ましくは、厚さを3nm以上20nm以下とする。特に、チャネル長が30nm以下のトランジスタでは、酸化物半導体膜118の厚さを5nm程度とすることで、しきい値電圧の変動を抑制でき、安定な電気的特性を有する。

【0050】

酸化物半導体膜118は、少なくともInおよびZnを含むことが好ましい。また、酸化物半導体膜118は、InおよびZnに加え、トランジスタの電気的特性のばらつきを低減するためにGa、Sn、HfまたはAlを有すると好ましい。

【0051】

または、酸化物半導体膜118は、InおよびZnに加え、トランジスタの電気的特性のばらつきを低減するためにランタノイドであるLa、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、YbおよびLuから選ばれた一種以上を有してもよい。

【0052】

酸化物半導体膜118として、例えば、二元系金属の酸化物であるIn−Zn−O系材料、Sn−Zn−O系材料、Al−Zn−O系材料、Zn−Mg−O系材料、Sn−Mg−O系材料、In−Mg−O系材料、In−Ga−O系材料、三元系金属の酸化物であるIn−Ga−Zn−O系材料、In−Al−Zn−O系材料、In−Sn−Zn−O系材料、Sn−Ga−Zn−O系材料、Al−Ga−Zn−O系材料、Sn−Al−Zn−O系材料、In−Hf−Zn−O系材料、In−La−Zn−O系材料、In−Ce−Zn−O系材料、In−Pr−Zn−O系材料、In−Nd−Zn−O系材料、In−Sm−Zn−O系材料、In−Eu−Zn−O系材料、In−Gd−Zn−O系材料、In−Tb−Zn−O系材料、In−Dy−Zn−O系材料、In−Ho−Zn−O系材料、In−Er−Zn−O系材料、In−Tm−Zn−O系材料、In−Yb−Zn−O系材料、In−Lu−Zn−O系材料、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系材料、In−Hf−Ga−Zn−O系材料、In−Al−Ga−Zn−O系材料、In−Sn−Al−Zn−O系材料、In−Sn−Hf−Zn−O系材料、In−Hf−Al−Zn−O系材料を用いることができる。

【0053】

例えば、In−Ga−Zn−O系材料とは、In、GaおよびZnを主成分として有する酸化物という意味であり、In、GaおよびZnの比率は問わない。

【0054】

例えば、In−Sn−Zn−O系材料を用いたトランジスタでは比較的容易に高い電界効果移動度が得られる。具体的には、トランジスタの電界効果移動度を31cm2/Vs以上、40cm2/Vs以上、60cm2/Vs以上、80cm2/Vs以上または100cm2/Vs以上とすることができる。なお、In−Sn−Zn−O系材料以外(例えばIn−Ga−Zn−O系材料)でも、欠陥密度を低減することにより電界効果移動度を高めることができる。

【0055】

酸化物半導体膜118としてIn−Zn−O系材料を用いる場合、原子数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さらに好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

【0056】

酸化物半導体膜118として、化学式InMO3(ZnO)m(m>0)で表記される材料を用いてもよい。ここで、Mは、Zn、Ga、Al、Mn、Sn、HfおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

【0057】

酸化物半導体膜118は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を選択する。ただし、酸化物半導体膜118に代えて、バンドギャップが前述の数値以上である半導体性を示す材料を用いても構わない。

【0058】

なお、酸化物半導体膜118は、特に水素、アルカリ金属およびアルカリ土類金属などが低減され、極めて不純物濃度の低い酸化物半導体膜118であると好ましい。酸化物半導体膜118が前述の不純物を有すると、不純物の形成する準位によりバンドギャップ内の再結合が起こり、トランジスタはオフ電流が増大してしまう。そのほかに、酸化物半導体膜中で間接的または直接的にキャリアを生成する不純物として、希ガス、窒素、リンおよびホウ素などがあり、これらも低減されていることが好ましい。

【0059】

酸化物半導体膜118中の水素濃度は、二次イオン質量分析(SIMS:Secondary Ion Mass Spectrometry)において、5×1019cm−3未満、好ましくは5×1018cm−3以下、より好ましくは1×1018cm−3以下、さらに好ましくは5×1017cm−3以下とする。

【0060】

また、酸化物半導体膜118中のアルカリ金属濃度は、SIMSにおいて、ナトリウム濃度が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下とする。同様に、リチウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。同様に、カリウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。

【0061】

以上に示した酸化物半導体膜118を用いることでトランジスタのオフ電流を小さくできる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流を1×10−18A以下、1×10−21A以下、または1×10−24A以下とすることができる。そのため、データの保持特性に優れ、消費電力の小さい半導体記憶装置を作製することができる。

【0062】

酸化物半導体膜118は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0063】

好ましくは、酸化物半導体膜118は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0064】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0065】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0066】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0067】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0068】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0069】

CAAC−OS膜に含まれる結晶構造の一例について図13乃至図15を用いて詳細に説明する。なお、特に断りがない限り、図13乃至図15は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図13において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0070】

図13(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図13(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図13(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図13(A)に示す小グループは電荷が0である。

【0071】

図13(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図13(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図13(B)に示す構造をとりうる。図13(B)に示す小グループは電荷が0である。

【0072】

図13(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図13(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。図13(C)に示す小グループは電荷が0である。

【0073】

図13(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図13(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図13(D)に示す小グループは電荷が+1となる。

【0074】

図13(E)に、2個のZnを含む小グループを示す。図13(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図13(E)に示す小グループは電荷が−1となる。

【0075】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0076】

ここで、これらの小グループ同士が結合する規則について説明する。Inの上半分の3個のOは下方向に3個の近接Inを有し、下半分の3個のOは上方向に3個の近接Inを有する。Gaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。Znの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向に3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。その理由を以下に示す。例えば、6配位の金属原子(InまたはSn)が上半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)の上半分の4配位のO、5配位の金属原子(GaまたはIn)の下半分の4配位のOまたは4配位の金属原子(Zn)の上半分の4配位のOのいずれかと結合することになる。

【0077】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0078】

図14(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図14(B)に、3つの中グループで構成される大グループを示す。なお、図14(C)は、図14(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0079】

図14(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図14(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図14(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0080】

図14(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0081】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図13(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0082】

具体的には、図14(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0083】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系材料や、三元系金属の酸化物であるIn−Ga−Zn−O系材料(IGZOとも表記する。)、In−Al−Zn−O系材料、Sn−Ga−Zn−O系材料、Al−Ga−Zn−O系材料、Sn−Al−Zn−O系材料や、In−Hf−Zn−O系材料、In−La−Zn−O系材料、In−Ce−Zn−O系材料、In−Pr−Zn−O系材料、In−Nd−Zn−O系材料、In−Sm−Zn−O系材料、In−Eu−Zn−O系材料、In−Gd−Zn−O系材料、In−Tb−Zn−O系材料、In−Dy−Zn−O系材料、In−Ho−Zn−O系材料、In−Er−Zn−O系材料、In−Tm−Zn−O系材料、In−Yb−Zn−O系材料、In−Lu−Zn−O系材料や、二元系金属の酸化物であるIn−Zn−O系材料、Sn−Zn−O系材料、Al−Zn−O系材料、Zn−Mg−O系材料、Sn−Mg−O系材料、In−Mg−O系材料や、In−Ga−O系の材料、一元系金属の酸化物であるIn−O系材料、Sn−O系材料、Zn−O系材料などを用いた場合も同様である。

【0084】

例えば、図15(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0085】

図15(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0086】

図15(B)に3つの中グループで構成される大グループを示す。なお、図15(C)は、図15(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0087】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0088】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図15(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0089】

具体的には、図15(B)に示した大グループが繰り返されることで、In−Ga−Zn−O系の結晶を得ることができる。なお、得られるIn−Ga−Zn−O系の層構造は、InGaO3(ZnO)n(nは自然数。)とする組成式で表すことができる。

【0090】

n=1(InGaZnO4)の場合は、例えば、図16(A)に示す結晶構造を取りうる。なお、図16(A)に示す結晶構造において、図13(B)で説明したように、GaおよびInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0091】

また、n=2(InGaZn2O5)の場合は、例えば、図16(B)に示す結晶構造を取りうる。なお、図16(B)に示す結晶構造において、図13(B)で説明したように、GaおよびInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0092】

以下に、本発明の一態様である半導体記憶装置に適用可能なトランジスタに用いる酸化物半導体膜の結晶状態について説明する。

【0093】

結晶状態を評価するに当たり、酸化物半導体膜のX線回折(XRD:X−Ray Diffraction)分析を行った。XRD分析には、Bruker AXS社製X線回折装置D8 ADVANCEを用い、Out−of−Plane法で測定した。

【0094】

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

【0095】

まず、脱水素化処理済みの石英基板を準備した。

【0096】

次に、石英基板上にIn−Sn−Zn−O膜を100nmの厚さで成膜した。

【0097】

In−Sn−Zn−O膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いた。なお、成膜時の基板加熱温度は室温または200℃とした。このようにして作製した試料を試料Aとした。

【0098】

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650℃の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を保持したまま酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

【0099】

図28に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2θが35deg近傍および37deg〜38degに結晶由来のピークが観測された。

【0100】

即ち、試料に対し加熱処理を650℃の温度で行うことで結晶性を有する酸化物半導体膜が得られることがわかる。

【0101】

CAAC−OS膜は、下地となる膜が平坦であると形成されやすい。具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、さらに好ましくは0.1nm以下となるように下地となる膜を設ける。なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、数式1にて定義される。

【0102】

【数1】

【0103】

なお、数式1において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)の4点で表される四角形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0104】

基板100に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon On Insulator)基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いると好ましい。

【0105】

また、基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接的にトランジスタを作製する。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

【0106】

下地絶縁膜102は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。

【0107】

酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0原子%以上10原子%以下の範囲で含まれるものをいう。また、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものをいう。但し、上記範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward scattering Spectrometry)を用いて測定した場合のものである。また、構成元素の組成は、その合計が100原子%を超えない値をとる。

【0108】

導電膜120aおよび導電膜120bとなる導電膜は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層でまたは積層で用いればよい。

【0109】

第1の絶縁膜104、第1のゲート絶縁膜108、第2のゲート絶縁膜110および第2の絶縁膜112となる絶縁膜は、下地絶縁膜102と同様の方法および同様の材料を用いて成膜すればよい。

【0110】

第1のゲート絶縁膜108および第2のゲート絶縁膜110は、加熱処理により酸素を放出する絶縁膜を用いると好ましい。

【0111】

また、第1のゲート絶縁膜108は、酸化物半導体膜118が結晶成長しやすいように、十分な平坦性を有することが好ましい。

【0112】

「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018cm−3以上、または1.0×1020cm−3以上であることをいう。

【0113】

ここで、TDS分析にて、酸素の放出量の測定方法について、以下に説明する。

【0114】

TDS分析したときの気体の放出量は、イオン強度の積分値に比例する。このため、測定したイオン強度の積分値と、標準試料との比により、気体の放出量を計算することができる。標準試料の基準値とは、所定の密度の原子を含む試料において、当該原子に相当するイオン強度の積分値に対する当該原子の密度の割合である。

【0115】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式2で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0116】

【数2】

【0117】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値である。αは、TDS分析におけるイオン強度に影響する係数である。数式2の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

【0118】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量について見積もることができる。

【0119】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0120】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0121】

第1のゲート絶縁膜108および第2のゲート絶縁膜110から酸化物半導体膜118に酸素が供給されることで、酸化物半導体膜118と第1のゲート絶縁膜108および第2のゲート絶縁膜110との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜118と第1のゲート絶縁膜108および第2のゲート絶縁膜110との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少ないトランジスタを得ることができる。

【0122】

さらに、酸化物半導体膜118の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜118の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そこで、第1のゲート絶縁膜108および第2のゲート絶縁膜110から酸化物半導体膜118に酸素が十分に供給され、好ましくは酸化物半導体膜118に酸素が過剰に含まれていることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜118の酸素欠損を低減することができる。

【0123】

なお、第2の絶縁膜112は、250℃以上450℃以下の範囲における酸素の拡散係数が、第1のゲート絶縁膜108および第2のゲート絶縁膜110よりも小さい材料を用いる。例えば、第1のゲート絶縁膜108および第2のゲート絶縁膜110が加熱処理により酸素を放出する酸化シリコン膜である場合、第2の絶縁膜112に酸化アルミニウム膜を用いればよい。このような性質を有する第2の絶縁膜112を設けることで、トランジスタ140から酸素が外方拡散していくことを防止できる。

【0124】

第1のゲート電極122、第2のゲート電極116および電極114となる導電膜は、導電膜120aおよび導電膜120bとなる導電膜と同様の方法および同様の材料を用いて成膜すればよい。または、少なくともInおよびZnを含む酸化物または酸窒化物を用いても構わない。例えば、In−Ga−Zn−O−N系材料などを用いればよい。

【0125】

以下にトランジスタの電界効果移動度について図17乃至図20を用いて説明する。なお、わかりやすさのため、説明に用いるトランジスタの構造は、本発明の一態様に係るトランジスタの構造とは異なるものを採用した。

【0126】

酸化物半導体に限らず、トランジスタの電界効果移動度は、様々な理由によって本来の得られるはずの電界効果移動度よりも低く測定される。電界効果移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面における欠陥がある。ここでは、Levinsonモデルを用い、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出す。

【0127】

本来のトランジスタの電界効果移動度をμ0とし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定したときに測定される電界効果移動度μは数式3で表される。

【0128】

【数3】

【0129】

ここで、Eはポテンシャル障壁の高さであり、kはボルツマン定数、Tは絶対温度である。なお、Levinsonモデルでは、ポテンシャル障壁の高さEが欠陥に由来すると仮定し、数式4で表される。

【0130】

【数4】

【0131】

ここで、eは電気素量、Nはチャネル内の単位面積あたりの平均欠陥密度、εは半導体の誘電率、nはチャネルの単位面積あたりのキャリア密度、Coxは単位面積当たりのゲート絶縁膜容量、Vgsはゲート電圧、tはチャネルの厚さである。なお、厚さが30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

【0132】

線形領域におけるドレイン電流Idsは、数式5で表される。

【0133】

【数5】

【0134】

ここで、Lはチャネル長、Wはチャネル幅であり、ここでは、LおよびWは10μmとする。また、Vdsはドレイン電圧である。

【0135】

数式5の両辺の対数を取ると、数式6で表される。

【0136】

【数6】

【0137】

数式6の右辺はVgsの関数であるため、縦軸をln(Ids/Vgs)、横軸を1/Vgsとする直線の傾きから欠陥密度Nが求められる。即ち、トランジスタのVgs−Ids特性から半導体中の欠陥密度Nが得られる。

【0138】

半導体中の欠陥密度Nは半導体の成膜時の基板温度に依存する。半導体として、In、SnおよびZnの比率が、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いて成膜した酸化物半導体を用いた場合、酸化物半導体中の欠陥密度Nは1×1012/cm2程度となる。

【0139】

上述した酸化物半導体中の欠陥密度Nをもとに、数式3および数式4を用いて計算すると、本来のトランジスタの電界効果移動度μ0は120cm2/Vsとなる。したがって、酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥がない、理想的なトランジスタの電界効果移動度μ0は120cm2/Vsとわかる。ところが、欠陥の多い酸化物半導体では、トランジスタの電界効果移動度μは30cm2/Vs程度である。

【0140】

また、半導体内部に欠陥がなくても、チャネルとゲート絶縁膜との界面散乱によってトランジスタの輸送特性は影響を受ける。ゲート絶縁膜界面からxだけ離れた場所における電界効果移動度μ1は、数式7で表される。

【0141】

【数7】

【0142】

ここで、Dはゲート電極による電界強度、Bは定数、lは界面散乱の影響が生じる深さである。Bおよびlは、トランジスタの電気的特性の実測より求めることができ、上記酸化物半導体を用いたトランジスタの電気的特性の実測からは、B=4.75×107cm/s、l=10nmが得られる。Dが増加すると、即ちVgsが高くなると、数式7の第2項が増加するため、電界効果移動度μ1は低下することがわかる。

【0143】

酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥のない、理想的なトランジスタの電界効果移動度μ2を計算した結果を図17に示す。なお、計算にはシノプシス社製Sentaurus Deviceを使用し、酸化物半導体のバンドギャップを2.8eV、電子親和力を4.7eV、比誘電率を15、厚さを15nmとした。さらに、ゲートの仕事関数を5.5eV、ソースおよびドレインの仕事関数を4.6eVとした。また、ゲート絶縁膜の厚さは100nm、比誘電率を4.1とした。また、チャネル長およびチャネル幅はともに10μm、Vdsは0.1Vとした。

【0144】

図17で示されるように、Vgsが1V近傍で電界効果移動度μ2は100cm2/Vs以上のピークを有するが、Vgsがさらに高くなると、界面散乱の影響が大きくなり、電界効果移動度μ2が低下することがわかる。

【0145】

このような理想的なトランジスタを微細化した場合について、計算した結果を図18乃至図20に示す。なお、計算には図21に示した構造のトランジスタを仮定している。

【0146】

図21(A)に示すトランジスタは、基板2100と、基板2100上に設けられた下地絶縁膜2102と、下地絶縁膜2102の周辺に設けられた保護絶縁膜2104と、下地絶縁膜2102および保護絶縁膜2104上に設けられた高抵抗領域2106aおよび低抵抗領域2106bを有する酸化物半導体膜2106と、酸化物半導体膜2106上に設けられたゲート絶縁膜2108と、ゲート絶縁膜2108を介して酸化物半導体膜2106と重畳して設けられたゲート電極2110と、ゲート電極2110の側面と接して設けられた側壁絶縁膜2112と、少なくとも酸化物半導体膜2106と接して設けられた一対の電極2114と、を有する。

【0147】

ここで、低抵抗領域2106bの抵抗率を2×10−3Ωcm、ゲート電極2110の幅を33nm、側壁絶縁膜2112の幅を5nm、チャネル幅を40nmとする。なお、チャネル領域を便宜上高抵抗領域2106aという名称で記載しているが、ここではチャネル領域を真性半導体と仮定している。

【0148】

計算にはシノプシス社製Sentaurus Deviceを使用した。図18は、図21(A)に示される構造のトランジスタのIds(実線)および電界効果移動度μ(点線)のVgs依存性である。なお、IdsはVdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図18(A)に、10nmとした場合を図18(B)に、5nmとした場合を図18(C)にそれぞれ示す。

【0149】

図18より、ゲート絶縁膜が薄くなるほど、オフ状態(ここではVgsが−3Vから0Vの範囲を指す。)でのドレイン電流Idsが低下する。一方、電界効果移動度μのピーク値やオン状態(ここではVgsが0Vから3Vの範囲を指す。)でのドレイン電流Idsには目立った変化がない。図18より、Vgsが1V近傍でIdsは半導体装置であるメモリなどに必要とされる10μAを超えることがわかる。

【0150】

同様に、図21(B)で示されるトランジスタについて計算を行っている。図21(B)で示されるトランジスタは、高抵抗領域2107aおよび低抵抗領域2107bを有する酸化物半導体膜2107を有する点で、図21(A)で示されるトランジスタとは異なる。具体的には、図21(B)で示されるトランジスタは、側壁絶縁膜2112と重畳する酸化物半導体膜2107の領域が高抵抗領域2107aに含まれる。即ち、該トランジスタは側壁絶縁膜2112の幅だけオフセット領域を有するトランジスタである。なお、オフセット領域の幅をオフセット長(Loff)ともいう。

【0151】

図21(B)で示されるトランジスタにおいて、Loffを5nmとし、ドレイン電流Ids(実線)および電界効果移動度μ(点線)のVgs依存性を図19に示す。なお、Idsは、Vdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図19(A)に、10nmとした場合を図19(B)に、5nmとした場合を図19(C)にそれぞれ示す。

【0152】

また、図20は、図21(B)に示されるトランジスタの構造から、Loffを15nmとしたもののドレイン電流Ids(実線)および電界効果移動度μ(点線)のVgs依存性である。なお、Idsは、Vdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図20(A)に、10nmとした場合を図20(B)に、5nmとした場合を図20(C)にそれぞれ示す。

【0153】

図19および図20に示した計算結果より、図18と同様に、いずれもゲート絶縁膜が薄くなるほどオフ状態(ここではVgsが−3Vから0Vの範囲を指す。)でのドレイン電流Idsが低下する。一方、電界効果移動度μのピーク値やオン状態(ここではVgsが0Vから3Vの範囲を指す。)でのドレイン電流Idsには目立った変化がないとわかる。

【0154】

なお、電界効果移動度μのピークは、図18では80cm2/Vs程度であるが、図19では60cm2/Vs程度、図20では40cm2/Vs程度、Loffが増加するほど低下することがわかる。また、オフ状態でのIdsも同様の傾向となることがわかる。一方、オン状態のIdsはオフセット長Loffの増加に伴って減少するが、オフ状態のIdsの低下に比べるとはるかに緩やかである。また、いずれの計算結果からもVgsが1V近傍で、Idsはメモリなどに必要とされる10μAを超えることがわかる。

【0155】

次に、図1で説明したメモリセルをマトリクス状に配置したメモリセルアレイについて回路図である図2を用いて説明する。

【0156】

メモリセルアレイは、ワード線WLと、ビット線BLと、バックゲート線BGLと、メモリセルMCと、を有する。

【0157】

メモリセルMCにおいて、トランジスタ140のゲートはワード線WLと接続し、トランジスタ140のソースはビット線BLと接続し、トランジスタ140のバックゲートはバックゲート線BGLと接続する。また、キャパシタ130の一対の電極の一方はトランジスタ140のドレインと接続し、キャパシタ130の一対の電極の他方は接地される。ただし、キャパシタ130の一対の電極の他方は必ずしも接地されているわけではなく、バックゲート線BGLと接続されていてもよい。

【0158】

ここで、トランジスタ140のゲートは第2のゲート電極116に、トランジスタ140のソースは導電膜120aに、トランジスタ140のドレインは導電膜120bに、トランジスタ140のバックゲートは第1のゲート電極122に、それぞれ対応する。

【0159】

なお、バックゲート線BGLは、スイッチング素子およびキャパシタと接続されていても構わない。その場合、バックゲート線BGLには、スイッチング素子を介して電位が印加される。また、スイッチング素子をオフ状態にすると、キャパシタに電位が保持される。スイッチング素子は、ノーマリーオフであることが好ましい。そうすることで、スイッチング素子への電源供給を止めた場合にもキャパシタには電位が保持されることになる。例えば、スイッチング素子として、トランジスタ140と同様のトランジスタを用いても構わない。

【0160】

ここで、ノーマリーオフとは、電源による電位の印加がないときにオフ状態であることをいう。

【0161】

このように、バックゲート線BGLを設けることによって、トランジスタ140のしきい値電圧を制御することができる。例えば、バックゲート線BGLに負電圧(トランジスタ140のソース電位よりも低い電位)を印加し、トランジスタ140のしきい値電圧を正方向に変動させることで、ゲート電圧が0Vのとき(電源供給なしのとき)にトランジスタ140を確実にオフ状態にすることができる。そのため、電源供給なしでも、長期間に渡ってメモリセルMCのデータを保持することが可能となる。

【0162】

ここで、図2に示すメモリセルアレイにデータを書き込む方法および読み出す方法を説明する。

【0163】

メモリセルアレイへのデータの書き込みは、メモリセルMCごとまたは行ごとに行う。

【0164】

まずは、メモリセルMCごとにデータを書き込む方法を説明する。例えば、1行1列にあるメモリセルMCにデータ1を書き込む場合、1行目のワード線WLに電位VHを印加した後、1列目のビット線BLの電位をVDDにすればよい。または、1行1列にあるメモリセルMCにデータ0を書き込む場合、1行目のワード線WLに電位VHを印加した後、1列目のビット線BLの電位をGNDにすればよい。次に、ワード線WLの電位をGND(またはGND以下)にすることで、キャパシタ130にデータが保持される。この動作を全てのメモリセルMCに行えば、メモリセルアレイにデータを書き込むことができる。なお、メモリセルMCごとにデータを書き込んだ後、同じ行にある別のメモリセルMCにデータを書き込むことでデータが失われてしまう。それを防ぐため、一度書き込んだデータを保持する回路を設け、同じ行の全てのメモリセルMCへのデータの書き込みが終了するまで、個々のメモリセルMCにデータを書き込むたびに、すでに書き込み済みの個々のメモリセルMCに対しても繰り返しデータの書き込みを行う。

【0165】

または、データの書き込みは行ごとに行う。例えば、1行目のメモリセルMCにデータを書き込む場合、1行目のワード線WLに電位VHを印加した後、データ1を書き込みたいメモリセルのある列のビット線の電位をVDDとし、データ0を書き込みたいメモリセルのある列のビット線の電位をGNDとする。次に、ワード線WLの電位をGND(またはGND以下)にすることで、キャパシタ130にデータが保持される。この動作を行ごとに行えば、全てのメモリセルに対してデータを書き込むことができる。

【0166】

次に、データの読み出し方法について説明する。

【0167】

まずは、メモリセルMCごとにデータを読み出す方法を説明する。例えば、1行1列にあるメモリセルMCのデータを読み出す場合、1列目のビット線BLを所定の電位(定電位)とする。次に、1行目のワード線WLの電位をVHとすると、1列目のビット線BLの電位がメモリセルMCに保持されたデータに応じて変動する。このときのビット線BLの電位をセンスアンプ(図示せず)にて読み出すことができる。この動作をメモリセルMCごとに行うことで、全てのメモリセルのデータを読み出すことができる。なお、メモリセルMCごとにデータを読み出す場合、データを読み出すたびに同じ行にある別のメモリセルMCのデータが失われてしまう。それを防ぐため、一度書き込んだデータを保持する回路を設け、同じ行の全てのメモリセルMCへのデータの読み出しが終了するまで、個々のメモリセルMCにデータを読み出すたびに、読み出しが済んでいない個々のメモリセルMCに対して繰り返しデータの書き込みを行う。

【0168】

または、データの読み出しは行ごとに行う。例えば、1行目のメモリセルMCのデータを読み出す場合、全ビット線BLを所定の電位(定電位)とする。次に、1行目のワード線WLの電位をVHとすると、各ビット線BLの電位がデータに応じて変動する。この動作を行ごとに行うことで、全てのメモリセルのデータを読み出すことができる。

【0169】

以上がメモリセルアレイへのデータの書き込みおよび読み出し方法である。

【0170】

図1に示すメモリセルの作製方法を図3乃至図5を用いて説明する。

【0171】

まず、基板100上にスパッタリング法、蒸着法、プラズマ化学気相成長法(PCVD法)、パルスレーザー堆積法(PLD法)、原子層堆積法(ALD法)または分子線エピタキシー法(MBE法)などを用いて下地絶縁膜102を成膜する(図3(A)参照。)。

【0172】

次に、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて導電膜を成膜する。次に、該導電膜をフォトリソグラフィ工程によって加工し、導電膜120aおよび導電膜120bを形成する(図3(B)参照。)。

【0173】

次に、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて第1の絶縁膜105を成膜する(図3(C)参照。)。

【0174】

次に、導電膜120aおよび導電膜120bが形成する段差を埋めるような形状の導電膜123を形成する(図3(D)参照。)。導電膜123は、例えば、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて導電膜を成膜し、該導電膜をCMP処理などによって平坦化して形成しても構わないし、公知のリフロー技術や平坦化膜成膜技術(バイアススパッタリング法など)を用いて形成しても構わない。

【0175】

次に、導電膜123を選択的にエッチングすることで導電膜120aおよび導電膜120bの上面よりも高さが低くなるように加工し、第1のゲート電極122を形成する(図4(A)参照。)。

【0176】

次に、導電膜120aおよび導電膜120bが形成する段差を埋めるような形状の絶縁膜109を形成する(図4(B)参照。)。絶縁膜109は、例えば、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて絶縁膜を成膜し、該絶縁膜をCMP処理などによって平坦化して形成しても構わないし、公知の平坦化膜成膜技術を用いて形成しても構わない。

【0177】

次に、絶縁膜109をCMP処理により加工し、第1のゲート絶縁膜108を形成する(図4(C)参照。)。ただし、絶縁膜109を、CMP処理に代えてドライエッチング法を用いて加工し、第1のゲート絶縁膜108を形成しても構わない。また、図4(C)では、第1のゲート絶縁膜108と導電膜120aおよび導電膜120bの上面の高さが一致しているが、この形状に限定されない。例えば、どちらかの膜面が高くなっていても構わない。

【0178】

次に、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて酸化物半導体膜を成膜する。

【0179】

酸化物半導体膜は、好ましくはスパッタリング法により、基板加熱温度を100℃以上600℃以下、好ましくは150℃以上550℃以下、さらに好ましくは200℃以上500℃以下とし、酸素ガス雰囲気で成膜する。酸化物半導体膜の厚さは、1nm以上50nm以下、好ましくは3nm以上20nm以下とする。成膜時の基板加熱温度が高いほど、得られる酸化物半導体膜の不純物濃度は低くなる。また、酸化物半導体膜中の原子配列が整い、高密度化され、多結晶膜またはCAAC−OS膜が形成されやすくなる。さらに、酸素ガス雰囲気で成膜することでも、希ガスなどの余分な原子が膜中に含まれないため、CAAC−OS膜が形成されやすくなる。ただし、酸素ガスと希ガスの混合雰囲気としてもよく、その場合は酸素ガスの割合は30体積%以上、好ましくは50体積%以上、さらに好ましくは80体積%以上とする。なお、酸化物半導体膜は薄いほど、トランジスタの短チャネル効果が低減される。ただし、薄くしすぎると界面散乱の影響が強くなり、電界効果移動度の低下が起こることがある。

【0180】

酸化物半導体膜としてIn−Sn−Zn−O系材料をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Sn:Zn=2:1:3、In:Sn:Zn=1:2:2、In:Sn:Zn=1:1:1またはIn:Sn:Zn=20:45:35で示されるIn−Sn−Zn−Oターゲットを用いる。前述の組成比を有するIn−Sn−Zn−Oターゲットを用いて酸化物半導体膜を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0181】

次に、第1の加熱処理を行う。第1の加熱処理は、減圧雰囲気、不活性雰囲気または酸化性雰囲気で行う。第1の加熱処理により、酸化物半導体膜中の不純物濃度を低減することができる。

【0182】

第1の加熱処理は、減圧雰囲気または不活性雰囲気で加熱処理を行った後、温度を保持しつつ酸化性雰囲気に切り替えてさらに加熱処理を行うと好ましい。これは、減圧雰囲気または不活性雰囲気にて加熱処理を行うと、酸化物半導体膜中の不純物濃度を効果的に低減することができるが、同時に酸素欠損も生じてしまうためであり、このとき生じた酸素欠損を、酸化性雰囲気での加熱処理により低減することができる。

【0183】

酸化物半導体膜は、成膜時の基板加熱に加え、第1の加熱処理を行うことで、膜中の不純物準位を極めて小さくすることが可能となる。その結果、トランジスタの電界効果移動度を後述する理想的な電界効果移動度近くまで高めることが可能となる。

【0184】

なお、酸化物半導体膜に酸素イオンを注入し、加熱処理により酸化物半導体膜に含まれる水素などの不純物を放出させ、該加熱処理と同時に、またはその後の加熱処理(第1の加熱処理など)により酸化物半導体膜を結晶化させてもよい。

【0185】

次に、酸化物半導体膜をフォトリソグラフィ工程によって加工し、酸化物半導体膜118を形成する(図5(A)参照。)。

【0186】

次に、第2のゲート絶縁膜110を成膜する(図5(B)参照。)。第2のゲート絶縁膜110は、第1の絶縁膜104または第1のゲート絶縁膜108の形成方法を参照して成膜すればよい。

【0187】

次に、第2のゲート電極116を形成する(図5(C)参照。)。第2のゲート電極116は、導電膜120aおよび導電膜120b、または第1のゲート電極122の形成方法を参照して形成すればよい。

【0188】

ここで、第2の加熱処理を行ってもよい。第2の加熱処理は、第1の加熱処理と同様の方法で行えばよい。第2の加熱処理を行うことで、第1のゲート絶縁膜108、第2のゲート絶縁膜110などから酸素が放出され、酸化物半導体膜118中の酸素欠損、酸化物半導体膜118と第1のゲート絶縁膜108および第2のゲート絶縁膜110との界面準位密度を低減することができる。そのため、得られるメモリセルの信頼性を高めることができる。

【0189】

次に、第2の絶縁膜112を成膜し、その後電極114を形成すれば図1(B)に示すメモリセルを作製することができる。

【0190】

以下に、本発明の一態様である半導体記憶装置に適用することのできる酸化物半導体を用いたトランジスタの電気的特性について説明する。

【0191】

図22は、作製したトランジスタ(試料1および試料2)の構造を示す上面図および断面図である。図22(A)はトランジスタの上面図である。また、図22(B)は図22(A)の一点鎖線A−Bに対応する断面図である。

【0192】

図22(B)に示すトランジスタは、基板600と、基板600上に設けられた下地絶縁膜602と、下地絶縁膜602上に設けられた酸化物半導体膜606と、酸化物半導体膜606と接する一対の電極614と、酸化物半導体膜606および一対の電極614上に設けられたゲート絶縁膜608と、ゲート絶縁膜608を介して酸化物半導体膜606と重畳して設けられたゲート電極610と、ゲート絶縁膜608およびゲート電極610を覆って設けられた層間絶縁膜616と、ゲート絶縁膜608および層間絶縁膜616に設けられた開口部を介して一対の電極614と接続する配線618と、層間絶縁膜616および配線618を覆って設けられた保護膜620と、を有する。

【0193】

基板600としてはガラス基板を、下地絶縁膜602としては酸化シリコン膜を、酸化物半導体膜606としてはIn−Sn−Zn−O膜を、一対の電極614としてはタングステン膜を、ゲート絶縁膜608としては酸化シリコン膜を、ゲート電極610としては窒化タンタル膜とタングステン膜との積層構造を、層間絶縁膜616としては酸化窒化シリコン膜とポリイミド膜との積層構造を、配線618としてはチタン膜、アルミニウム膜、チタン膜がこの順で形成された積層構造を、保護膜620としてはポリイミド膜を、それぞれ用いた。

【0194】

なお、図22(A)に示す構造のトランジスタにおいて、ゲート電極610と一対の電極614との重畳する幅をLovと呼ぶ。同様に、酸化物半導体膜606に対する一対の電極614のはみ出しをdWと呼ぶ。

【0195】

図22(B)に示す構造のトランジスタ(試料1および試料2)の作製方法を以下に説明する。

【0196】

まず、基板600の表面に対し、アルゴン雰囲気でプラズマ処理を行った。プラズマ処理は、スパッタリング装置を用い、基板600側にバイアス電力を200W(RF)印加して3分間行った。

【0197】

続けて、真空状態を保ったまま、下地絶縁膜602である酸化シリコン膜を300nmの厚さで成膜した。

【0198】

酸化シリコン膜は、スパッタリング装置を用い、酸素雰囲気で電力を1500W(RF)として成膜した。ターゲットは、石英ターゲットを用いた。なお、成膜時の基板加熱温度は100℃とした。

【0199】

次に、下地絶縁膜602の表面をCMP処理し、Ra=0.2nm程度まで平坦化した。

【0200】

次に、酸化物半導体膜であるIn−Sn−Zn−O膜を15nmの厚さで成膜した。

【0201】

In−Sn−Zn−O膜は、スパッタリング装置を用い、アルゴン:酸素=2:3[体積比]の混合雰囲気で電力を100W(DC)として成膜した。ターゲットは、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いた。なお、成膜時の基板加熱温度は200℃とした。

【0202】

次に、試料2のみ加熱処理を650℃の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を保持したままさらに酸素雰囲気で1時間の加熱処理を行った。

【0203】

次に、フォトリソグラフィ工程によって酸化物半導体膜を加工して、酸化物半導体膜606を形成した。

【0204】

次に、タングステン膜を50nmの厚さで成膜した。

【0205】

タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を1000W(DC)として成膜した。なお、成膜時の基板加熱温度は200℃とした。

【0206】

次に、フォトリソグラフィ工程によってタングステン膜を加工して、一対の電極614を形成した。

【0207】

次に、ゲート絶縁膜608である酸化シリコン膜を100nmの厚さで成膜した。なお、酸化シリコン膜の比誘電率は3.8とした。

【0208】

ゲート絶縁膜608である酸化シリコン膜は、下地絶縁膜602と同様の方法で成膜した。

【0209】

次に、窒化タンタル膜およびタングステン膜を、この順番でそれぞれ15nmおよび135nmの厚さで成膜した。

【0210】

窒化タンタル膜は、スパッタリング装置を用い、アルゴン:窒素=5:1の混合雰囲気で電力を1000W(DC)として成膜した。なお、成膜時に基板加熱は行っていない。

【0211】

タングステン膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を4000W(DC)として成膜した。なお、成膜時の基板加熱温度は200℃とした。

【0212】

次に、フォトリソグラフィ工程によって窒化タンタル膜およびタングステン膜を加工して、ゲート電極610を形成した。

【0213】

次に、層間絶縁膜616となる酸化窒化シリコン膜を300nmの厚さで成膜した。

【0214】

層間絶縁膜616となる酸化窒化シリコン膜は、PCVD装置を用い、モノシラン:亜酸化窒素=1:200の混合雰囲気で電力を35W(RF)として成膜した。なお、成膜時の基板加熱温度は325℃とした。

【0215】

次に、フォトリソグラフィ工程によって層間絶縁膜616となる酸化窒化シリコン膜を加工した。

【0216】

次に、層間絶縁膜616となる感光性ポリイミドを1500nmの厚さで成膜した。

【0217】

次に、層間絶縁膜616となる酸化窒化シリコン膜のフォトリソグラフィ工程で用いたフォトマスクを用いて層間絶縁膜616となる感光性ポリイミドを露光し、その後現像し、次に感光性ポリイミド膜を硬化させるために加熱処理を行い、硬化した感光性ポリイミドおよび酸化窒化シリコン膜とを有する層間絶縁膜616を形成した。加熱処理は、窒素雰囲気において、300℃の温度で行った。

【0218】

次に、チタン膜、アルミニウム膜およびチタン膜を、この順番でそれぞれ50nm、100nmおよび5nmの厚さで成膜した。

【0219】

チタン膜は、二層ともにスパッタリング装置を用い、アルゴン雰囲気で電力を1000W(DC)として成膜した。なお、成膜時に基板加熱は行っていない。

【0220】

アルミニウム膜は、スパッタリング装置を用い、アルゴン雰囲気で電力を1000W(DC)として成膜した。なお、成膜時に基板加熱は行っていない。

【0221】

次に、フォトリソグラフィ工程によってチタン膜、アルミニウム膜およびチタン膜を加工して、配線618を形成した。

【0222】

次に、保護膜620である感光性ポリイミド膜を1500nmの厚さで成膜した。

【0223】

次に、配線618のフォトリソグラフィ工程で用いたフォトマスクを用いて感光性ポリイミドを露光し、その後現像して、保護膜620に配線618を露出する開口部を形成した。

【0224】

次に、感光性ポリイミド膜を硬化させるために加熱処理を行った。加熱処理は、層間絶縁膜616で用いた感光性ポリイミド膜に対する加熱処理と同様の方法で行った。

【0225】

以上の工程で、図22(B)に示す構造のトランジスタを作製した。

【0226】

次に、図22(B)に示す構造のトランジスタの電気的特性を評価した。

【0227】

図22(B)に示す構造のトランジスタにおけるVgs−Ids特性を測定し、試料1の結果を図23(A)に、試料2の結果を図23(B)にそれぞれ示す。なお、測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、Lovが片側3μm(合計6μm)、dWが片側3μm(合計6μm)である。また、Vdsは10Vとした。

【0228】

また、試料1と試料2とを比較すると、酸化物半導体膜の成膜後に加熱処理を行うことでトランジスタの電界効果移動度が高くなることがわかる。発明者等は、これが加熱処理により酸化物半導体膜中の不純物濃度が低減されたためである、と考えた。したがって、酸化物半導体膜の成膜後に行う加熱処理によって酸化物半導体膜中の不純物濃度を低減し、その結果、トランジスタの電界効果移動度を理想的な電界効果移動度に近づけることができたとわかる。

【0229】

このように、酸化物半導体膜の成膜後に加熱処理を行うことで、酸化物半導体膜中の不純物濃度が低減され、その結果トランジスタの電界効果移動度が高まることがわかる。

【0230】

次に、試料1および試料2に対しBT試験を行った。BT試験について以下に説明する。

【0231】

まず基板温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids特性の測定を行った。次に、基板温度を150℃とし、Vdsを0.1Vとした。次に、ゲート絶縁膜608に印加される電界強度が2MV/cmとなるようにVgsに20Vを印加し、そのまま1時間保持した。次に、Vgsを0Vとした。次に、基板温度25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids測定を行った。これをプラスBT試験と呼ぶ。

【0232】

同様に、まず基板温度を25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids特性の測定を行った。次に、基板温度を150℃とし、Vdsを0.1Vとした。次に、ゲート絶縁膜608に印加される電界強度が−2MV/cmとなるようにVgsに−20Vを印加し、そのまま1時間保持した。次に、Vgsを0Vとした。次に、基板温度25℃とし、Vdsを10Vとし、トランジスタのVgs−Ids測定を行った。これをマイナスBT試験と呼ぶ。

【0233】

試料1のプラスBT試験の結果を図24(A)に、マイナスBT試験の結果を図24(B)に示す。また、試料2のプラスBT試験の結果を図25(A)に、マイナスBT試験の結果を図25(B)に示す。なお、図には、BT試験前後のVgs−Ids特性の変動をわかりやすくするため、矢印を付している。

【0234】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび−0.42Vであった。また、試料2のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。

【0235】

試料1および試料2は、BT試験前後におけるしきい値電圧の変動が小さく、信頼性の高いトランジスタであることがわかる。

【0236】

次に、試料2のトランジスタにおいて、基板温度と電気的特性の関係について評価した。

【0237】

測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、Lovが片側3μm(合計6μm)、dWが0μmとした。なお、Vdsは10Vとした。なお、基板温度は−40℃、−25℃、25℃、75℃、125℃および150℃で行った。

【0238】

図26(A)に基板温度としきい値電圧の関係を、図26(B)に基板温度と電界効果移動度の関係を示す。

【0239】

図26(A)より、基板温度が高いほどしきい値電圧は低くなることがわかる。なお、その範囲は−40℃(0.38V)〜150℃(−1.08V)であった。

【0240】

また、図26(B)より、基板温度が高いほど電界効果移動度が低くなることがわかる。なお、その範囲は−40℃(37.4cm2/Vs)〜150℃(33.4cm2/Vs)であった。

【0241】

このように、試料2は、上述の温度範囲において電気的特性の変動が小さいことがわかる。

【0242】

以上に示したトランジスタは、高い電界効果移動度を有し、信頼性が高いことがわかる。

【0243】

同様に、本発明の一態様である半導体記憶装置に適用可能なトランジスタの、チャネル幅が1μm当たりのオフ電流を評価した。

【0244】

試料2と同様の方法で試料を作製した。なお、測定に用いたトランジスタは、Lを3μm、Wを10cm、Lovを2μm、dWを0μmとしている。

【0245】

図27に、トランジスタのオフ電流と測定時の基板温度(絶対温度)の逆数との関係を示す。ここでは、簡単のため測定時の基板温度の逆数に1000を掛けた数値(1000/T)を横軸としている。

【0246】

以下にトランジスタのオフ電流の測定方法を簡単に説明する。ここでは便宜上測定対象となるトランジスタを第1のトランジスタと呼ぶ。

【0247】

第1のトランジスタのドレインはフローティングゲートFGと接続され、フローティングゲートFGは第2のトランジスタのゲートと接続される。

【0248】

まず、第1のトランジスタをオフ状態とし、次に、フローティングゲートFGに電荷を与える。なお、第2のトランジスタには一定のドレイン電圧が印加されている。

【0249】

このとき、フローティングゲートFGの電荷が第1のトランジスタを通じて徐々にリークする。フローティングゲートFGの電荷が抜けると、第2のトランジスタのソース電位が変化する。このソース電位の時間に対する変化量から第1のトランジスタからリークする電荷量が見積もられ、オフ電流を測定することができる。

【0250】

図27より、作製したトランジスタは、測定時の基板温度が85℃のときオフ電流は1×10−21A/μm(1zA/μm)であった。

【0251】

このように、作製したトランジスタのオフ電流は極めて小さいことがわかる。

【0252】

以上に示すように、信頼性が高く、オフ電流の小さいトランジスタで構成された、信頼性が高く、リフレッシュ動作の頻度の低いメモリセルを得ることができる。

【0253】

通常バックゲートを設ける場合、バックゲート電極をソース電極およびドレイン電極から分離するためにトランジスタのサイズを大きくする必要があるが、第1のゲート電極122をバックゲート電極として用いることで、バックゲート電極を有する微細なトランジスタを作製することができる。そのため、図1に示したメモリセルで構成される半導体記憶装置の集積度を高めることができる。

【0254】

本実施の形態に示したメモリセルは、トランジスタのしきい値電圧が制御され、かつトランジスタのオフ電流が極めて小さいため、リフレッシュ動作の頻度を低減することができる。そのため、消費電力の小さい半導体記憶装置を提供することができる。

【0255】

また、トランジスタにバックゲート電極を設けてもメモリセルの面積を大きくする必要がないため、集積度の高い半導体記憶装置を提供することができる。

【0256】

また、第1のゲート電極と同一層である導電膜がメモリセルを囲むように設けられるため、該導電膜がガードリングとしての機能を有し、メモリセルの静電破壊が起こりにくい半導体記憶装置を提供することができる。

【0257】

本実施の形態は、適宜他の実施の形態と組み合わせて用いても構わない。

【0258】

(実施の形態2)

本実施の形態では、実施の形態1に示した半導体記憶装置と構成の異なる半導体記憶装置について図6乃至図10を用いて説明する。

【0259】

図6は、メモリセルを示す上面図(図6(A)参照。)および断面図(図6(B)参照。)である。

【0260】

図6(A)より、一つのメモリセルのサイズは8F2(縦2F×横4F)である。

【0261】

図6(B)より、メモリセルは、第1のトランジスタ250と、第2のトランジスタ240と、キャパシタ230と、を有する。

【0262】

なお、メモリセルは、基板200と、基板200上の下地絶縁膜202上に設けられる。なお、基板200の表面状態によっては、下地絶縁膜202を設けない構造としても構わない。

【0263】

第1のトランジスタ250は、高抵抗領域226a、低抵抗領域226bおよび低抵抗領域226cを有する半導体膜226と、半導体膜226上に設けられたゲート絶縁膜228と、ゲート絶縁膜228を介して高抵抗領域226aと重畳して設けられた導電膜220bと、を有する。

【0264】

第2のトランジスタ240は、導電膜220bと、ゲート絶縁膜228に設けられた開口部を介して低抵抗領域226bと接続する、導電膜220bと同一層かつ同一材料である導電膜220aと、ゲート絶縁膜228の上面、導電膜220aおよび導電膜220bの側面と接して設けられた第1の絶縁膜204と、第1の絶縁膜204を介して導電膜220aおよび導電膜220b間に設けられ、導電膜220aおよび導電膜220bの上面の高さよりも上面の高さの低い第1のゲート電極222と、第1のゲート電極222上に設けられた第1のゲート絶縁膜208と、第1のゲート絶縁膜208、導電膜220aおよび導電膜220bと接して設けられた酸化物半導体膜218と、酸化物半導体膜218上に設けられた第2のゲート絶縁膜210と、第2のゲート絶縁膜210を介して酸化物半導体膜218に重畳して設けられた第2のゲート電極216と、を有する。なお、第2のトランジスタ240を覆って第2の絶縁膜212を設けても構わない。

【0265】

キャパシタ230は、導電膜220b、第2のゲート絶縁膜210および電極214を有する。

【0266】

なお、基板200、下地絶縁膜202、導電膜220b、導電膜220a、第1の絶縁膜204、第1のゲート電極222、第1のゲート絶縁膜208、酸化物半導体膜218、第2のゲート絶縁膜210、第2のゲート電極216、第2の絶縁膜212および電極214は、それぞれ基板100、下地絶縁膜102、導電膜120b、導電膜120a、第1の絶縁膜104、第1のゲート電極122、第1のゲート絶縁膜108、酸化物半導体膜118、第2のゲート絶縁膜110、第2のゲート電極116、第2の絶縁膜112および電極114と同様の方法および同様の材料を用いて形成すればよい。

【0267】

半導体膜226は、多結晶シリコン、単結晶シリコン、多結晶ゲルマニウム、単結晶ゲルマニウム、ガリウムヒ素などに代表される公知の半導体材料を用いればよい。

【0268】

ここで、導電膜220aは第1のトランジスタ250のソース電極および第2のトランジスタ240のソース電極として機能する。また、導電膜220bは、第1のトランジスタ250のゲート電極、第2のトランジスタ240のドレイン電極およびキャパシタ230の一対の電極の一方として機能する。また、高抵抗領域226a、低抵抗領域226bおよび低抵抗領域226cは、それぞれ第1のトランジスタ250のチャネル領域、ソース領域およびドレイン領域として機能する。

【0269】

ここで、第1のゲート電極222は、第2のトランジスタ240のしきい値電圧を制御するためのバックゲート電極としての機能を有する。また、第1のゲート電極222と同一層である導電膜がメモリセルを囲むように設けられるため、該導電膜がガードリングとしての機能を有し、メモリセルの静電破壊を防止することができる。

【0270】

導電膜220aは、ビット線と接続する。ここでは、導電膜220aが延在しビット線を形成している場合について記載する。

【0271】

また、図示しないが、第2のゲート電極216はワード線と接続し、低抵抗領域226cはソース線と接続する。

【0272】

次に、図6で説明したメモリセルをマトリクス状に配置したメモリセルアレイについて回路図である図7を用いて説明する。

【0273】

メモリセルアレイは、ワード線WLと、ビット線BLと、ソース線SLと、バックゲート線BGLと、メモリセルMCと、を有する。

【0274】

メモリセルMCにおいて、第1のトランジスタ250のソースおよび第2のトランジスタ240のソースはビット線BLと接続し、第1のトランジスタ250のドレインはソース線SLと接続し、第2のトランジスタ240のゲートはワード線WLと接続し、第1のトランジスタ250のゲートは第2のトランジスタ240のドレインおよびキャパシタ230の一対の電極の一方と接続し、第2のトランジスタ240のバックゲートはバックゲート線BGLと接続し、キャパシタ230の一対の電極の他方は接地する。

【0275】

メモリセルMC_1_1およびメモリセルMC_2_1は、ビット線BL_1を共有しており、メモリセルMC_1_1およびメモリセルMC_1_2は、ワード線WL_1およびソース線SL_1を共有している。即ち、各列でビット線BLを、各行でワード線WLおよびソース線SLを共有している。

【0276】

ここで、第1のトランジスタ250のゲートは導電膜220bに、第1のトランジスタ250のソースは低抵抗領域226bに、第1のトランジスタ250のドレインは低抵抗領域226cに、第2のトランジスタ240のゲートは第2のゲート電極216に、第2のトランジスタ240のソースは導電膜220aに、第2のトランジスタ240のドレインは導電膜220bに、第2のトランジスタ240のバックゲートは第1のゲート電極222に、それぞれ対応する。

【0277】

なお、バックゲート線BGLは、スイッチング素子およびキャパシタと接続されていても構わない。その場合、バックゲート線BGLには、スイッチング素子を介して電位が印加される。また、スイッチング素子をオフ状態にすると、キャパシタに電位が保持される。スイッチング素子は、ノーマリーオフであることが好ましい。そうすることで、スイッチング素子への電源供給を止めた場合にもキャパシタには電位が保持されることになる。例えば、スイッチング素子として、第2のトランジスタ240と同様のトランジスタを用いても構わない。

【0278】

このように、バックゲート線BGLを設けることによって、第2のトランジスタ240のしきい値電圧を制御することができる。例えば、バックゲート線BGLに負電圧(第2のトランジスタ240のソース電位よりも低い電位)を印加し、第2のトランジスタ240のしきい値電圧を正方向に変動させることで、ゲート電圧が0Vのとき(電源供給なしのとき)に第2のトランジスタ240を確実にオフ状態にすることができる。そのため、電源供給なしでも、長期間に渡ってメモリセルMCのデータを保持することが可能となる。

【0279】

ここで、図7に示すメモリセルアレイにデータを書き込む方法および読み出す方法を説明する。

【0280】

まずは、メモリセルアレイへのデータの書き込み方法を示す。

【0281】

データの書き込みは行ごとに行う。ここでは、メモリセルMC_1_1およびメモリセルMC_1_2からデータを書き込む。

【0282】

まず、ワード線WL_1を電位VH(VDDよりも第2のトランジスタ240のしきい値電圧(Vth)以上高い電位)とし、ワード線WL_2、ソース線SL_1およびソース線SL_2を電位GNDとする。次に、データ1を書き込むメモリセルMCがある列に対応するビット線BLを電位VDDとし、データ0を書き込むメモリセルMCがある列に対応するビット線BLを電位GNDとする。このようにすることで、データ1を書き込むメモリセルMCのキャパシタ230の電位はVDDとなり、データ0を書き込むメモリセルMCのキャパシタ230の電位はGNDとなる。

【0283】

次に、行を移動して、同様の方法でメモリセルMC_2_1およびメモリセルMC_2_2にデータを書き込む。

【0284】

以上のような方法で、メモリセルアレイにデータを書き込むことができる。

【0285】

次に、メモリセルアレイに書き込んだデータの保持方法を示す。

【0286】

書き込んだデータの保持は、ワード線WL_1、ワード線WL_2、ビット線BL_1、ビット線BL_2、ソース線SL_1およびソース線SL_2を浮遊電位(フロートともいう。)とする。または、ワード線WL_1、ワード線WL_2、ビット線BL_1、ビット線BL_2、ソース線SL_1およびソース線SL_2をGND(またはGND以下)とする。

【0287】

以上のような方法で、メモリセルアレイに書き込んだデータを保持することができる。

【0288】

次に、メモリセルアレイに保持されたデータを読み出す方法を示す。

【0289】

保持されたデータの読み出しは行ごとに行う。ここでは、メモリセルMC_1_1およびメモリセルMC_1_2からデータを読み出す。

【0290】

まず、ソース線SL_1を電位VDDとし、ソース線SL_2、ワード線WL_1およびワード線WL_2を電位GNDとする。なお、図示しないが、ビット線BL_1およびビット線BL_2は、プルダウン回路と接続する。プルダウン回路と接続することによって、ビット線BLにプルダウン回路以外何も接続していないとき、ビット線BLを電位GNDに固定することができる。即ち、メモリセルMCがデータ1を保持しているとき、第1のトランジスタ250がオンし、ビット線BLが電位VDDとなる。または、メモリセルMCがデータ0を保持しているとき、第1のトランジスタ250がオフしているため、ビット線BLは電位GNDとなる。こうしてビット線BLの電位によってデータを読み出すことができる。

【0291】

次に、行を移動して、同様の方法でメモリセルMC_2_1およびメモリセルMC_2_2からデータを読み出す。

【0292】

以上のような方法で、メモリセルアレイに保持されたデータを読み出すことができる。

【0293】

以上がメモリセルアレイへのデータの書き込みおよび読み出し方法である。

【0294】

図6に示すメモリセルの作製方法を図8乃至図10を用いて説明する。

【0295】

まず、基板200上に下地絶縁膜202を成膜する。次に、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて半導体膜276を成膜する(図8(A)参照。)。

【0296】

なお、基板200、下地絶縁膜202および半導体膜276を有するSOI基板などの半導体基板を用いても構わない。

【0297】

次に、半導体膜276に対し、フォトリソグラフィ工程によって選択的に不純物を添加することで、高抵抗領域226a、低抵抗領域226bおよび低抵抗領域226cを形成する(図8(B)参照。)。

【0298】

次に、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて絶縁膜を成膜し、フォトリソグラフィ工程によって加工してゲート絶縁膜228を形成する(図8(C)参照。)。

【0299】

次に、導電膜220aおよび導電膜220bを形成する(図8(D)参照。)。

【0300】

次に、第1の絶縁膜205を成膜する(図9(A)参照。)。

【0301】

次に、第1のゲート電極222を形成する(図9(B)参照。)。

【0302】

次に、第1のゲート絶縁膜208を形成する(図9(C)参照。)。

【0303】

次に、酸化物半導体膜を成膜する。

【0304】

次に、第1の加熱処理を行う。第1の加熱処理は、実施の形態1に示した第1の加熱処理を参酌する。

【0305】

なお、酸化物半導体膜に酸素イオンを注入し、加熱処理により酸化物半導体膜に含まれる水素などの不純物を放出させ、該加熱処理と同時に、またはその後の加熱処理(第1の加熱処理など)により酸化物半導体膜を結晶化させてもよい。

【0306】

次に、酸化物半導体膜を加工して、酸化物半導体膜218を形成する(図10(A)参照。)。

【0307】

次に、第2のゲート絶縁膜210を成膜する(図10(B)参照。)。

【0308】

次に、第2のゲート電極216を形成する(図10(C)参照。)。

【0309】

ここで、第2の加熱処理を行ってもよい。第2の加熱処理は、実施の形態1に示した第2の加熱処理を参酌する。

【0310】

次に、第2の絶縁膜212を成膜し、その後電極214を形成すれば図6(B)に示すメモリセルを作製することができる。

【0311】

通常バックゲートを設ける場合、バックゲート電極をソース電極およびドレイン電極から分離するためにトランジスタのサイズを大きくする必要があるが、第1のゲート電極222をバックゲート電極として用いることで、バックゲート電極を有する微細なトランジスタを作製することができる。そのため、図6に示したメモリセルで構成される半導体記憶装置の集積度を高めることができる。

【0312】

本実施の形態に示したメモリセルは、トランジスタのしきい値電圧が制御され、かつトランジスタのオフ電流が極めて小さいため、メモリセルに書き込んだデータを長期間に渡って保持することができる。そのため、消費電力の小さい半導体記憶装置を提供することができる。

【0313】

また、トランジスタにバックゲート電極を設けてもメモリセルの面積を大きくする必要がないため、集積度の高い半導体記憶装置を提供することができる。

【0314】

また、第1のゲート電極と同一層である導電膜がメモリセルを囲むように設けられるため、該導電膜がガードリングとしての機能を有し、メモリセルの静電破壊が起こりにくい半導体記憶装置を提供することができる。

【0315】

本実施の形態は、適宜他の実施の形態と組み合わせて用いても構わない。

【0316】

(実施の形態3)

実施の形態1または実施の形態2で示した半導体記憶装置を少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

【0317】

図11(A)は、CPUの具体的な構成を示すブロック図である。図11(A)に示すCPUは、基板1190上に、演算回路(ALU:Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図11(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0318】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0319】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行う。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行う。

【0320】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

【0321】

図11(A)に示すCPUでは、レジスタ1196に、実施の形態1または実施の形態2で示した半導体記憶装置が設けられている。

【0322】

図11(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有する半導体記憶装置において、論理(値)を反転させる論理素子によるデータの保持を行うか、キャパシタによるデータの保持を行うかを、選択する。論理(値)を反転させる論理素子によるデータの保持を行う場合、レジスタ1196内の半導体記憶装置への電源電圧の供給が行われる。キャパシタによるデータの保持を行う場合、キャパシタへのデータの書き換えが行われ、レジスタ1196内の半導体記憶装置への電源電圧の供給を停止することができる。

【0323】

電源停止に関しては、図11(B)または図11(C)に示すように、半導体記憶装置群と、電源電位VDDまたは電源電位VSSの与えられているノードとのに、スイッチング素子を設けることにより行うことができる。以下に図11(B)および図11(C)の回路の説明を行う。

【0324】

図11(B)および図11(C)では、半導体記憶装置への電源電位の供給を制御するスイッチング素子に、酸化物半導体を用いたトランジスタを含む記憶回路の構成の一例を示す。

【0325】

図11(B)に示す記憶装置は、スイッチング素子1141と、半導体記憶装置1142を複数有する半導体記憶装置群1143とを有している。具体的に、各半導体記憶装置1142には、実施の形態1または実施の形態2に示す半導体記憶装置を用いることができる。半導体記憶装置群1143が有する各半導体記憶装置1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが与えられている。さらに、半導体記憶装置群1143が有する各半導体記憶装置1142には、信号INの電位と、ローレベルの電源電位VSSが与えられている。

【0326】

図11(B)では、スイッチング素子1141として、酸化物半導体などのバンドギャップの大きい半導体を有するトランジスタを用いており、該トランジスタは、そのゲートに与えられる信号SigAによりスイッチングが制御される。

【0327】

なお、図11(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

【0328】

また、図11(C)には、半導体記憶装置群1143が有する各半導体記憶装置1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、半導体記憶装置群1143が有する各半導体記憶装置1142への、ローレベルの電源電位VSSの供給を制御することができる。

【0329】

半導体記憶装置群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

【0330】

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)などのLSIにも応用可能である。

【0331】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0332】

(実施の形態4)

本実施の形態では、実施の形態1乃至実施の形態3の少なくともいずれかを適用した電子機器の例について説明する。

【0333】

図12(A)は携帯型情報端末である。筐体9300と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。本発明の一態様は、電子機器の内部にあるCPUおよびメモリモジュールに適用することができる。

【0334】

図12(B)は、デジタルスチルカメラである。筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323と、を具備する。本発明の一態様は、電子機器の内部にあるメモリモジュールに適用することができる。

【0335】

本発明の一態様を用いることで、電子機器の品質を高めることができる。また消費電力を低減し、信頼性を高めることができる。

【0336】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【符号の説明】

【0337】

100 基板

102 下地絶縁膜

104 第1の絶縁膜

105 第1の絶縁膜

108 第1のゲート絶縁膜

109 絶縁膜

110 第2のゲート絶縁膜

112 第2の絶縁膜

114 電極

116 第2のゲート電極

118 酸化物半導体膜

120a 導電膜

120b 導電膜

122 第1のゲート電極

123 導電膜

130 キャパシタ

140 トランジスタ

200 基板

202 下地絶縁膜

204 第1の絶縁膜

205 第1の絶縁膜

208 第1のゲート絶縁膜

210 第2のゲート絶縁膜

212 第2の絶縁膜

214 電極

216 第2のゲート電極

218 酸化物半導体膜

220a 導電膜

220b 導電膜

222 第1のゲート電極

226 半導体膜

226a 高抵抗領域

226b 低抵抗領域

226c 低抵抗領域

228 ゲート絶縁膜

230 キャパシタ

240 第2のトランジスタ

250 第1のトランジスタ

276 半導体膜

600 基板

602 下地絶縁膜

606 酸化物半導体膜

608 ゲート絶縁膜

610 ゲート電極

614 一対の電極

616 層間絶縁膜

618 配線

620 保護膜

1141 スイッチング素子

1142 半導体記憶装置

1143 半導体記憶装置群

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

2100 基板

2102 下地絶縁膜

2104 保護絶縁膜

2106 酸化物半導体膜

2106a 高抵抗領域

2106b 低抵抗領域

2107 酸化物半導体膜

2107a 高抵抗領域

2107b 低抵抗領域

2108 ゲート絶縁膜

2110 ゲート電極

2112 側壁絶縁膜

2114 一対の電極

9300 筐体

9301 ボタン

9302 マイクロフォン

9303 表示部

9304 スピーカ

9305 カメラ

9320 筐体

9321 ボタン

9322 マイクロフォン

9323 表示部

【技術分野】

【0001】

本発明は、トランジスタなどの半導体素子を含む回路を有する半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性のものと、電力の供給がなくなっても記憶内容は保持される不揮発性のものとに大別される。

【0003】

揮発性の半導体記憶装置の代表的な例としては、DRAM(Dynamic Random Access Memory)がある。DRAMは、トランジスタを選択し、該トランジスタと接続するキャパシタに電荷を蓄積することで、情報を記憶する。

【0004】

DRAMでは、情報を読み出すと同時にキャパシタに蓄積された電荷が失われるため、情報の読み出しの度に再度の書き込みが必要となる。また、DRAMを構成するトランジスタがオフ状態のときでも、ソースおよびドレイン間のリーク電流(オフ電流)などによって電荷が失われるため、データの保持期間が短い。このため、所定の周期で書き込み動作(リフレッシュ動作)が必要となり、消費電力が増大してしまう。また、電力の供給がなくなるとデータが失われるため、電力の供給を止めた状態で長期間に渡ってデータを保持するためには、磁性材料や光学材料を利用した別の記憶装置が必要となる。

【0005】

揮発性の半導体記憶装置の別の例としてはSRAM(Static Random Access Memory)がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においてはDRAMより有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりのコストが高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと同様である。

【0006】

不揮発性の半導体記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く、DRAMで必要なリフレッシュ動作が不要であるという利点を有している(特許文献1参照。)。

【0007】

しかし、書き込みの際に生じるトンネル電流によってフラッシュメモリを構成するゲート絶縁膜が劣化するため、所定回数の書き込みによって半導体記憶装置として機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各メモリセルへの書き込み回数を均一化する手法が採られるが、これを実現するためには複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。したがって、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きである。

【0008】

また、フラッシュメモリは、フローティングゲートに電荷を注入するため、またはその電荷を除去するために高い電圧が必要となる。また、そのための回路も必要である。さらに、電荷の注入または除去のためには比較的長い時間を要し、書き込み、消去の高速化が容易ではないという問題もある。

【0009】

上述した半導体記憶装置を構成するトランジスタは、主にシリコン系半導体が用いられる。ところで、近年になり、酸化物半導体を用いたトランジスタが注目されている。酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタよりも電界効果移動度が高い。そのため、酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタに置き換わる技術として期待されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開昭57−105889号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

従来のDRAMのように頻繁にリフレッシュ動作を繰り返さなくてもデータの保持が可能であり、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供することを目的の一つとする。

【0012】

さらに、上述の新たな構造の半導体記憶装置の集積度を高め、単位面積あたりの記憶容量を増加させることを目的の一つとする。

【課題を解決するための手段】

【0013】

本発明の一態様である半導体記憶装置は、一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を第1のトランジスタの該一対の電極の一方と共有するキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

【0014】

なお、「上面の高さ」とは、特に断りがない限り基板表面を基準としたときの高さをいう。

【0015】

また、本発明の一態様である半導体記憶装置を構成するメモリセルは、前述のキャパシタに保持される電位の高低によってデータが区別される。

【0016】

または、本発明の一態様であるメモリセルは、第1のトランジスタの一対の電極の一方およびキャパシタとゲートが接続される第2のトランジスタを有し、キャパシタに保持される電位に応じて、第2のトランジスタのオン、オフが切り替わることを利用してデータが区別される。

【0017】

なお、第1のトランジスタを構成する一対の電極間距離は、最小加工寸法(Fとも表記する。)となるように設けられる。

【0018】

第1のゲート電極は、間隔がFであるソース電極およびドレイン電極(一対の電極)の少なくとも側壁と接して設けられた絶縁膜を介してソース電極およびドレイン電極間に設けられる。そのため、第1のゲート電極は、Fよりも絶縁膜の厚さの2倍分だけ幅が小さくなる。

【0019】

なお、第1のゲート電極は、絶縁膜上に、ソース電極およびドレイン電極間を埋めるように導電膜を成膜した後、化学機械研磨(CMP:Chemical Mechanical Polishing)処理によって、導電膜のソース電極およびドレイン電極上の部分を取り除くことで形成できる。このようにして設けられた第1のゲート電極は、自己整合的に形成されるため、幅をF未満とすることができる。そのため、個々のメモリセルのサイズの小さくでき、集積度の高い半導体記憶装置を得ることができる。

【0020】

第1のゲート電極および第1のゲート絶縁膜について、形成方法を以下に簡単に示す。第1のゲート電極の上面の高さが、一対の電極の上面の高さよりも低くなるように設け、第1のゲート電極および一対の電極上に第1のゲート絶縁膜となる絶縁膜を成膜する。次に、CMP処理により第1のゲート絶縁膜となる絶縁膜の一部を除去する。これを、一対の電極が露出するまで行うと、第1のゲート絶縁膜が得られる。このようにして形成した第1のゲート絶縁膜は、絶縁膜を介して一対の電極間にあり、かつ第1のゲート電極上に設けられる。

【0021】

なお、シリコン系半導体を用いたトランジスタは、しきい値電圧などの電気的特性を制御する技術が確立されているのに対し、酸化物半導体を用いたトランジスタは、当該技術は確立されていない。具体的には、シリコン系半導体材料を用いたトランジスタは、不純物ドーピングなどによって、しきい値電圧の制御が可能であるのに対し、酸化物半導体材料を用いたトランジスタは、不純物ドーピングなどによって、しきい値電圧を制御することが困難である。

【0022】

上記構造の第1のトランジスタは、第1のゲート電極に電位を印加することでしきい値電圧を制御することができる。なお、電源電位の供給が止まっても第1のゲート電極に電位が固定できるようにするために、第1のゲート電極と接続するキャパシタおよびスイッチを設けてもよい。

【0023】

なお、第1のゲート電極は、メモリセルを取り囲むように設けられる。そのため、第1のゲート電極がガードリングの機能を有し、半導体記憶装置の静電破壊を防止でき、歩留まりが高く、信頼性の高い半導体記憶装置を得ることができる。

【0024】

酸化物半導体膜として、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を選択すればよい。バンドギャップを前述の数値以上とすることによって、トランジスタのオフ電流を小さくすることができる。なお、バンドギャップが前述の数値以上であり、かつ半導体特性を示す酸化物半導体ではない材料に置き換えても構わない。

【0025】

また、酸化物半導体膜は、間接的または直接的にキャリアを生成する不純物(水素、アルカリ金属、アルカリ土類金属、希ガス、窒素、リンおよびホウ素など)の濃度が低くなるよう高純度化されていると好ましい。さらに、酸素欠損を極力低減することが好ましい。酸化物半導体膜中の不純物および酸素欠損を低減することによって、酸化物半導体膜中において意図しないキャリアの生成が低減され、トランジスタのオフ電流を小さくすることができる。

【0026】

このように、第1のトランジスタのオフ電流を小さくすることで、第1のトランジスタをオフ状態としたときにキャパシタの電荷を長期間に渡って保持することができる。したがって、長期間に渡ってデータを保持することのできる半導体記憶装置が得られる。

【発明の効果】

【0027】

しきい値電圧が制御され、かつオフ電流の極めて小さいトランジスタを用いることで、リフレッシュ動作の頻度が低く、消費電力の小さい半導体記憶装置を提供することができる。

【0028】

また、個々のメモリセルの面積の小さい、集積度の高い半導体記憶装置を提供することができる。

【0029】

また、個々のメモリセルを囲むように等電位の導電膜が設けられるため、ガードリングの機能を有し、静電破壊が起こりにくい半導体記憶装置を提供することができる。

【図面の簡単な説明】

【0030】

【図1】半導体記憶装置を構成するメモリセルの例を示す上面図および断面図。

【図2】図1に示すメモリセルをマトリクス状に組み合わせたメモリセルアレイの例を示す回路図。

【図3】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図4】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図5】図1に示す半導体記憶装置の作製方法を説明する断面図。

【図6】半導体記憶装置を構成するメモリセルの例を示す上面図および断面図。

【図7】図6に示すメモリセルをマトリクス状に組み合わせたメモリセルアレイの例を示す回路図。

【図8】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図9】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図10】図6に示す半導体記憶装置の作製方法を説明する断面図。

【図11】本発明の一態様であるトランジスタを用いたCPUの具体例を示すブロック図およびその一部の回路図。

【図12】本発明の一態様である電子機器の例を示す斜視図。

【図13】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図14】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図15】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図16】本発明の一態様に係る酸化物半導体の結晶構造を説明する図。

【図17】計算によって得られた電界効果移動度のVgs依存性を説明する図。

【図18】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図19】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図20】計算によって得られたIdsおよび電界効果移動度のVgs依存性を説明する図。

【図21】計算に用いたトランジスタの構造を示す断面図。

【図22】トランジスタの構造を示す断面図および上面図。

【図23】試料1および試料2であるトランジスタのVgs−Ids特性および電界効果移動度を示す図。

【図24】試料1であるトランジスタのBT試験前後のVgs−Ids特性を示す図。

【図25】試料2であるトランジスタのBT試験前後のVgs−Ids特性を示す図。

【図26】試料2であるトランジスタのしきい値電圧および電界効果移動度と基板温度の関係を示す図。

【図27】酸化物半導体膜を用いたトランジスタのオフ電流を示す図。

【図28】酸化物半導体膜のXRDスペクトルを示す図。

【発明を実施するための形態】

【0031】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更しうることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0032】

以下、本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0033】

また、電圧は、ある電位と基準の電位(例えばソース電位、接地電位)との電位差のことを示す場合が多い。よって、電圧を電位に置き換えることができる。また、電位VH、電位VDD、電位GNDなどのように電位を表記したとしても、厳密に電位VH、電位VDD、電位GNDとなっていないことがある。よって、電位VH、電位VDD、電位GNDは、電位VH近傍、電位VDD近傍、電位GND近傍と置き換えることができる。なお、「接地する」と「GNDに接続する」は同義である。

【0034】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

【0035】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0036】

なお、本明細書では、マトリクスにおいて特定の行や列、位置を扱う場合には、符号に座標を示す記号をつけて、例えば、「メモリセルMC_n_m」、「ビット線BL_m」というように表記するが、特に、行や列、位置を特定しない場合や集合的に扱う場合、またはどの位置にあるか明らかである場合には、「メモリセルMC」、「ビット線BL」、または、単に「メモリセル」、「ビット線」というように表記することもある。

【0037】

(実施の形態1)

本実施の形態では、本発明の一態様を適用した半導体記憶装置について図1乃至図5を用いて説明する。

【0038】

図1は、半導体記憶装置であるDRAMの一つのメモリセルを示す上面図(図1(A)参照。)および断面図(図1(B)参照。)である。

【0039】

図1(A)より、メモリセルのサイズは8F2(縦2F×横4F)である。

【0040】

図1(B)より、メモリセルは、酸化物半導体膜を用いたトランジスタ140と、キャパシタ130と、を有する。

【0041】

なお、メモリセルは、基板100上の下地絶縁膜102上に設けられる。なお、基板100の表面状態によっては、下地絶縁膜102を設けない構造としても構わない。

【0042】

トランジスタ140は、導電膜120aおよび導電膜120bと、導電膜120aおよび導電膜120bの側面と接して設けられた第1の絶縁膜104と、第1の絶縁膜104を介して導電膜120aおよび導電膜120b間に設けられ、導電膜120aおよび導電膜120bの上面の高さよりも上面の高さの低い第1のゲート電極122と、第1のゲート電極122上に設けられた第1のゲート絶縁膜108と、第1のゲート絶縁膜108、導電膜120aおよび導電膜120bと接して設けられた酸化物半導体膜118と、酸化物半導体膜118上に設けられた第2のゲート絶縁膜110と、第2のゲート絶縁膜110を介して酸化物半導体膜118上に設けられた第2のゲート電極116と、を有する。なお、トランジスタ140を覆って第2の絶縁膜112を設けても構わない。

【0043】

キャパシタ130は、導電膜120b、第2のゲート絶縁膜110および電極114を有する。電極114は第2の絶縁膜112の側面と接するように図示されているが、これに限定されるものではない。例えば、第2のゲート電極116と一部が重畳しても構わないし、第1のゲート電極122と同一層である導電膜と一部が重畳しても構わない。なお、電極114の代わりに第1のゲート電極122と同一層の導電膜を用いても構わない。第1のゲート電極122と同一層の導電膜をキャパシタに用いると、導電膜120bの側面に沿ってキャパシタ130を作製することができる。そのため、キャパシタ130の誘電体層が同じと仮定したときで導電膜120bの厚さがFの3分の1より厚いとき、電極114を用いた場合よりも容量を大きくすることができる。なお、ここでは便宜上Fを用いて厚さを記載するが、Fは上面形状における最小加工寸法であるため、当然ながら導電膜120bの厚さをFよりも小さくすることが可能である。

【0044】

なお、キャパシタ130に電極114を用いた場合、キャパシタ130の誘電体層は第2のゲート絶縁膜110および第2の絶縁膜112となる。また、キャパシタ130に第1のゲート電極122と同一層の導電膜を用いた場合、キャパシタ130の誘電体層は第1の絶縁膜104となる。

【0045】

ここで、導電膜120aはトランジスタ140のソース電極として機能する。また、導電膜120bはトランジスタ140のドレイン電極およびキャパシタ130の一対の電極の一方として機能する。

【0046】

ここで、第1のゲート電極122は、トランジスタ140のしきい値電圧を制御するためのバックゲート電極としての機能を有する。また、第1のゲート電極122と同一層である導電膜がメモリセルを囲むように設けられており、該導電膜はガードリングとしての機能を有し、メモリセルの静電破壊を防止することができる。

【0047】

トランジスタ140の導電膜120aは、ビット線と接続する。ここでは、導電膜120aが延在しビット線を形成している場合について記載する。

【0048】

また、図示しないが、トランジスタ140の第2のゲート電極116は、ワード線と接続する。

【0049】

酸化物半導体膜118は、厚さを1nm以上50nm以下とする。好ましくは、厚さを3nm以上20nm以下とする。特に、チャネル長が30nm以下のトランジスタでは、酸化物半導体膜118の厚さを5nm程度とすることで、しきい値電圧の変動を抑制でき、安定な電気的特性を有する。

【0050】

酸化物半導体膜118は、少なくともInおよびZnを含むことが好ましい。また、酸化物半導体膜118は、InおよびZnに加え、トランジスタの電気的特性のばらつきを低減するためにGa、Sn、HfまたはAlを有すると好ましい。

【0051】

または、酸化物半導体膜118は、InおよびZnに加え、トランジスタの電気的特性のばらつきを低減するためにランタノイドであるLa、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、YbおよびLuから選ばれた一種以上を有してもよい。

【0052】

酸化物半導体膜118として、例えば、二元系金属の酸化物であるIn−Zn−O系材料、Sn−Zn−O系材料、Al−Zn−O系材料、Zn−Mg−O系材料、Sn−Mg−O系材料、In−Mg−O系材料、In−Ga−O系材料、三元系金属の酸化物であるIn−Ga−Zn−O系材料、In−Al−Zn−O系材料、In−Sn−Zn−O系材料、Sn−Ga−Zn−O系材料、Al−Ga−Zn−O系材料、Sn−Al−Zn−O系材料、In−Hf−Zn−O系材料、In−La−Zn−O系材料、In−Ce−Zn−O系材料、In−Pr−Zn−O系材料、In−Nd−Zn−O系材料、In−Sm−Zn−O系材料、In−Eu−Zn−O系材料、In−Gd−Zn−O系材料、In−Tb−Zn−O系材料、In−Dy−Zn−O系材料、In−Ho−Zn−O系材料、In−Er−Zn−O系材料、In−Tm−Zn−O系材料、In−Yb−Zn−O系材料、In−Lu−Zn−O系材料、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系材料、In−Hf−Ga−Zn−O系材料、In−Al−Ga−Zn−O系材料、In−Sn−Al−Zn−O系材料、In−Sn−Hf−Zn−O系材料、In−Hf−Al−Zn−O系材料を用いることができる。

【0053】

例えば、In−Ga−Zn−O系材料とは、In、GaおよびZnを主成分として有する酸化物という意味であり、In、GaおよびZnの比率は問わない。

【0054】

例えば、In−Sn−Zn−O系材料を用いたトランジスタでは比較的容易に高い電界効果移動度が得られる。具体的には、トランジスタの電界効果移動度を31cm2/Vs以上、40cm2/Vs以上、60cm2/Vs以上、80cm2/Vs以上または100cm2/Vs以上とすることができる。なお、In−Sn−Zn−O系材料以外(例えばIn−Ga−Zn−O系材料)でも、欠陥密度を低減することにより電界効果移動度を高めることができる。

【0055】

酸化物半導体膜118としてIn−Zn−O系材料を用いる場合、原子数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さらに好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

【0056】

酸化物半導体膜118として、化学式InMO3(ZnO)m(m>0)で表記される材料を用いてもよい。ここで、Mは、Zn、Ga、Al、Mn、Sn、HfおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

【0057】

酸化物半導体膜118は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を選択する。ただし、酸化物半導体膜118に代えて、バンドギャップが前述の数値以上である半導体性を示す材料を用いても構わない。

【0058】

なお、酸化物半導体膜118は、特に水素、アルカリ金属およびアルカリ土類金属などが低減され、極めて不純物濃度の低い酸化物半導体膜118であると好ましい。酸化物半導体膜118が前述の不純物を有すると、不純物の形成する準位によりバンドギャップ内の再結合が起こり、トランジスタはオフ電流が増大してしまう。そのほかに、酸化物半導体膜中で間接的または直接的にキャリアを生成する不純物として、希ガス、窒素、リンおよびホウ素などがあり、これらも低減されていることが好ましい。

【0059】

酸化物半導体膜118中の水素濃度は、二次イオン質量分析(SIMS:Secondary Ion Mass Spectrometry)において、5×1019cm−3未満、好ましくは5×1018cm−3以下、より好ましくは1×1018cm−3以下、さらに好ましくは5×1017cm−3以下とする。

【0060】

また、酸化物半導体膜118中のアルカリ金属濃度は、SIMSにおいて、ナトリウム濃度が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下とする。同様に、リチウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。同様に、カリウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。

【0061】

以上に示した酸化物半導体膜118を用いることでトランジスタのオフ電流を小さくできる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流を1×10−18A以下、1×10−21A以下、または1×10−24A以下とすることができる。そのため、データの保持特性に優れ、消費電力の小さい半導体記憶装置を作製することができる。

【0062】

酸化物半導体膜118は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0063】

好ましくは、酸化物半導体膜118は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0064】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0065】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0066】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0067】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0068】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0069】

CAAC−OS膜に含まれる結晶構造の一例について図13乃至図15を用いて詳細に説明する。なお、特に断りがない限り、図13乃至図15は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図13において、丸で囲まれたOは4配位のOを示し、二重丸で囲まれたOは3配位のOを示す。

【0070】

図13(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図13(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図13(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図13(A)に示す小グループは電荷が0である。

【0071】

図13(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図13(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図13(B)に示す構造をとりうる。図13(B)に示す小グループは電荷が0である。

【0072】

図13(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図13(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。図13(C)に示す小グループは電荷が0である。

【0073】

図13(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図13(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図13(D)に示す小グループは電荷が+1となる。

【0074】

図13(E)に、2個のZnを含む小グループを示す。図13(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図13(E)に示す小グループは電荷が−1となる。

【0075】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0076】

ここで、これらの小グループ同士が結合する規則について説明する。Inの上半分の3個のOは下方向に3個の近接Inを有し、下半分の3個のOは上方向に3個の近接Inを有する。Gaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。Znの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向に3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。その理由を以下に示す。例えば、6配位の金属原子(InまたはSn)が上半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)の上半分の4配位のO、5配位の金属原子(GaまたはIn)の下半分の4配位のOまたは4配位の金属原子(Zn)の上半分の4配位のOのいずれかと結合することになる。

【0077】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0078】

図14(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図14(B)に、3つの中グループで構成される大グループを示す。なお、図14(C)は、図14(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0079】

図14(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図14(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図14(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0080】

図14(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0081】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図13(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0082】

具体的には、図14(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0083】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系材料や、三元系金属の酸化物であるIn−Ga−Zn−O系材料(IGZOとも表記する。)、In−Al−Zn−O系材料、Sn−Ga−Zn−O系材料、Al−Ga−Zn−O系材料、Sn−Al−Zn−O系材料や、In−Hf−Zn−O系材料、In−La−Zn−O系材料、In−Ce−Zn−O系材料、In−Pr−Zn−O系材料、In−Nd−Zn−O系材料、In−Sm−Zn−O系材料、In−Eu−Zn−O系材料、In−Gd−Zn−O系材料、In−Tb−Zn−O系材料、In−Dy−Zn−O系材料、In−Ho−Zn−O系材料、In−Er−Zn−O系材料、In−Tm−Zn−O系材料、In−Yb−Zn−O系材料、In−Lu−Zn−O系材料や、二元系金属の酸化物であるIn−Zn−O系材料、Sn−Zn−O系材料、Al−Zn−O系材料、Zn−Mg−O系材料、Sn−Mg−O系材料、In−Mg−O系材料や、In−Ga−O系の材料、一元系金属の酸化物であるIn−O系材料、Sn−O系材料、Zn−O系材料などを用いた場合も同様である。

【0084】

例えば、図15(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0085】

図15(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0086】

図15(B)に3つの中グループで構成される大グループを示す。なお、図15(C)は、図15(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0087】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0088】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図15(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0089】

具体的には、図15(B)に示した大グループが繰り返されることで、In−Ga−Zn−O系の結晶を得ることができる。なお、得られるIn−Ga−Zn−O系の層構造は、InGaO3(ZnO)n(nは自然数。)とする組成式で表すことができる。

【0090】

n=1(InGaZnO4)の場合は、例えば、図16(A)に示す結晶構造を取りうる。なお、図16(A)に示す結晶構造において、図13(B)で説明したように、GaおよびInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0091】

また、n=2(InGaZn2O5)の場合は、例えば、図16(B)に示す結晶構造を取りうる。なお、図16(B)に示す結晶構造において、図13(B)で説明したように、GaおよびInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0092】

以下に、本発明の一態様である半導体記憶装置に適用可能なトランジスタに用いる酸化物半導体膜の結晶状態について説明する。

【0093】

結晶状態を評価するに当たり、酸化物半導体膜のX線回折(XRD:X−Ray Diffraction)分析を行った。XRD分析には、Bruker AXS社製X線回折装置D8 ADVANCEを用い、Out−of−Plane法で測定した。

【0094】

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

【0095】

まず、脱水素化処理済みの石英基板を準備した。

【0096】

次に、石英基板上にIn−Sn−Zn−O膜を100nmの厚さで成膜した。

【0097】

In−Sn−Zn−O膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いた。なお、成膜時の基板加熱温度は室温または200℃とした。このようにして作製した試料を試料Aとした。

【0098】

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650℃の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を保持したまま酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

【0099】

図28に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2θが35deg近傍および37deg〜38degに結晶由来のピークが観測された。

【0100】

即ち、試料に対し加熱処理を650℃の温度で行うことで結晶性を有する酸化物半導体膜が得られることがわかる。

【0101】

CAAC−OS膜は、下地となる膜が平坦であると形成されやすい。具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、さらに好ましくは0.1nm以下となるように下地となる膜を設ける。なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、数式1にて定義される。

【0102】

【数1】

【0103】

なお、数式1において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)の4点で表される四角形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0104】

基板100に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI(Silicon On Insulator)基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いると好ましい。

【0105】

また、基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接的にトランジスタを作製する。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

【0106】

下地絶縁膜102は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。

【0107】

酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0原子%以上10原子%以下の範囲で含まれるものをいう。また、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものをいう。但し、上記範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward scattering Spectrometry)を用いて測定した場合のものである。また、構成元素の組成は、その合計が100原子%を超えない値をとる。

【0108】

導電膜120aおよび導電膜120bとなる導電膜は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層でまたは積層で用いればよい。

【0109】

第1の絶縁膜104、第1のゲート絶縁膜108、第2のゲート絶縁膜110および第2の絶縁膜112となる絶縁膜は、下地絶縁膜102と同様の方法および同様の材料を用いて成膜すればよい。

【0110】

第1のゲート絶縁膜108および第2のゲート絶縁膜110は、加熱処理により酸素を放出する絶縁膜を用いると好ましい。

【0111】

また、第1のゲート絶縁膜108は、酸化物半導体膜118が結晶成長しやすいように、十分な平坦性を有することが好ましい。

【0112】

「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018cm−3以上、または1.0×1020cm−3以上であることをいう。

【0113】

ここで、TDS分析にて、酸素の放出量の測定方法について、以下に説明する。

【0114】

TDS分析したときの気体の放出量は、イオン強度の積分値に比例する。このため、測定したイオン強度の積分値と、標準試料との比により、気体の放出量を計算することができる。標準試料の基準値とは、所定の密度の原子を含む試料において、当該原子に相当するイオン強度の積分値に対する当該原子の密度の割合である。

【0115】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式2で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0116】

【数2】

【0117】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値である。αは、TDS分析におけるイオン強度に影響する係数である。数式2の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

【0118】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量について見積もることができる。

【0119】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0120】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0121】

第1のゲート絶縁膜108および第2のゲート絶縁膜110から酸化物半導体膜118に酸素が供給されることで、酸化物半導体膜118と第1のゲート絶縁膜108および第2のゲート絶縁膜110との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜118と第1のゲート絶縁膜108および第2のゲート絶縁膜110との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少ないトランジスタを得ることができる。

【0122】

さらに、酸化物半導体膜118の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜118の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そこで、第1のゲート絶縁膜108および第2のゲート絶縁膜110から酸化物半導体膜118に酸素が十分に供給され、好ましくは酸化物半導体膜118に酸素が過剰に含まれていることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜118の酸素欠損を低減することができる。

【0123】

なお、第2の絶縁膜112は、250℃以上450℃以下の範囲における酸素の拡散係数が、第1のゲート絶縁膜108および第2のゲート絶縁膜110よりも小さい材料を用いる。例えば、第1のゲート絶縁膜108および第2のゲート絶縁膜110が加熱処理により酸素を放出する酸化シリコン膜である場合、第2の絶縁膜112に酸化アルミニウム膜を用いればよい。このような性質を有する第2の絶縁膜112を設けることで、トランジスタ140から酸素が外方拡散していくことを防止できる。

【0124】

第1のゲート電極122、第2のゲート電極116および電極114となる導電膜は、導電膜120aおよび導電膜120bとなる導電膜と同様の方法および同様の材料を用いて成膜すればよい。または、少なくともInおよびZnを含む酸化物または酸窒化物を用いても構わない。例えば、In−Ga−Zn−O−N系材料などを用いればよい。

【0125】

以下にトランジスタの電界効果移動度について図17乃至図20を用いて説明する。なお、わかりやすさのため、説明に用いるトランジスタの構造は、本発明の一態様に係るトランジスタの構造とは異なるものを採用した。

【0126】

酸化物半導体に限らず、トランジスタの電界効果移動度は、様々な理由によって本来の得られるはずの電界効果移動度よりも低く測定される。電界効果移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面における欠陥がある。ここでは、Levinsonモデルを用い、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出す。

【0127】

本来のトランジスタの電界効果移動度をμ0とし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定したときに測定される電界効果移動度μは数式3で表される。

【0128】

【数3】

【0129】

ここで、Eはポテンシャル障壁の高さであり、kはボルツマン定数、Tは絶対温度である。なお、Levinsonモデルでは、ポテンシャル障壁の高さEが欠陥に由来すると仮定し、数式4で表される。

【0130】

【数4】

【0131】

ここで、eは電気素量、Nはチャネル内の単位面積あたりの平均欠陥密度、εは半導体の誘電率、nはチャネルの単位面積あたりのキャリア密度、Coxは単位面積当たりのゲート絶縁膜容量、Vgsはゲート電圧、tはチャネルの厚さである。なお、厚さが30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

【0132】

線形領域におけるドレイン電流Idsは、数式5で表される。

【0133】

【数5】

【0134】

ここで、Lはチャネル長、Wはチャネル幅であり、ここでは、LおよびWは10μmとする。また、Vdsはドレイン電圧である。

【0135】

数式5の両辺の対数を取ると、数式6で表される。

【0136】

【数6】

【0137】

数式6の右辺はVgsの関数であるため、縦軸をln(Ids/Vgs)、横軸を1/Vgsとする直線の傾きから欠陥密度Nが求められる。即ち、トランジスタのVgs−Ids特性から半導体中の欠陥密度Nが得られる。

【0138】

半導体中の欠陥密度Nは半導体の成膜時の基板温度に依存する。半導体として、In、SnおよびZnの比率が、In:Sn:Zn=1:1:1[原子数比]のIn−Sn−Zn−Oターゲットを用いて成膜した酸化物半導体を用いた場合、酸化物半導体中の欠陥密度Nは1×1012/cm2程度となる。

【0139】

上述した酸化物半導体中の欠陥密度Nをもとに、数式3および数式4を用いて計算すると、本来のトランジスタの電界効果移動度μ0は120cm2/Vsとなる。したがって、酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥がない、理想的なトランジスタの電界効果移動度μ0は120cm2/Vsとわかる。ところが、欠陥の多い酸化物半導体では、トランジスタの電界効果移動度μは30cm2/Vs程度である。

【0140】

また、半導体内部に欠陥がなくても、チャネルとゲート絶縁膜との界面散乱によってトランジスタの輸送特性は影響を受ける。ゲート絶縁膜界面からxだけ離れた場所における電界効果移動度μ1は、数式7で表される。

【0141】

【数7】

【0142】

ここで、Dはゲート電極による電界強度、Bは定数、lは界面散乱の影響が生じる深さである。Bおよびlは、トランジスタの電気的特性の実測より求めることができ、上記酸化物半導体を用いたトランジスタの電気的特性の実測からは、B=4.75×107cm/s、l=10nmが得られる。Dが増加すると、即ちVgsが高くなると、数式7の第2項が増加するため、電界効果移動度μ1は低下することがわかる。

【0143】

酸化物半導体中および酸化物半導体と接するゲート絶縁膜との界面に欠陥のない、理想的なトランジスタの電界効果移動度μ2を計算した結果を図17に示す。なお、計算にはシノプシス社製Sentaurus Deviceを使用し、酸化物半導体のバンドギャップを2.8eV、電子親和力を4.7eV、比誘電率を15、厚さを15nmとした。さらに、ゲートの仕事関数を5.5eV、ソースおよびドレインの仕事関数を4.6eVとした。また、ゲート絶縁膜の厚さは100nm、比誘電率を4.1とした。また、チャネル長およびチャネル幅はともに10μm、Vdsは0.1Vとした。

【0144】

図17で示されるように、Vgsが1V近傍で電界効果移動度μ2は100cm2/Vs以上のピークを有するが、Vgsがさらに高くなると、界面散乱の影響が大きくなり、電界効果移動度μ2が低下することがわかる。

【0145】

このような理想的なトランジスタを微細化した場合について、計算した結果を図18乃至図20に示す。なお、計算には図21に示した構造のトランジスタを仮定している。

【0146】

図21(A)に示すトランジスタは、基板2100と、基板2100上に設けられた下地絶縁膜2102と、下地絶縁膜2102の周辺に設けられた保護絶縁膜2104と、下地絶縁膜2102および保護絶縁膜2104上に設けられた高抵抗領域2106aおよび低抵抗領域2106bを有する酸化物半導体膜2106と、酸化物半導体膜2106上に設けられたゲート絶縁膜2108と、ゲート絶縁膜2108を介して酸化物半導体膜2106と重畳して設けられたゲート電極2110と、ゲート電極2110の側面と接して設けられた側壁絶縁膜2112と、少なくとも酸化物半導体膜2106と接して設けられた一対の電極2114と、を有する。

【0147】

ここで、低抵抗領域2106bの抵抗率を2×10−3Ωcm、ゲート電極2110の幅を33nm、側壁絶縁膜2112の幅を5nm、チャネル幅を40nmとする。なお、チャネル領域を便宜上高抵抗領域2106aという名称で記載しているが、ここではチャネル領域を真性半導体と仮定している。

【0148】

計算にはシノプシス社製Sentaurus Deviceを使用した。図18は、図21(A)に示される構造のトランジスタのIds(実線)および電界効果移動度μ(点線)のVgs依存性である。なお、IdsはVdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図18(A)に、10nmとした場合を図18(B)に、5nmとした場合を図18(C)にそれぞれ示す。

【0149】

図18より、ゲート絶縁膜が薄くなるほど、オフ状態(ここではVgsが−3Vから0Vの範囲を指す。)でのドレイン電流Idsが低下する。一方、電界効果移動度μのピーク値やオン状態(ここではVgsが0Vから3Vの範囲を指す。)でのドレイン電流Idsには目立った変化がない。図18より、Vgsが1V近傍でIdsは半導体装置であるメモリなどに必要とされる10μAを超えることがわかる。

【0150】

同様に、図21(B)で示されるトランジスタについて計算を行っている。図21(B)で示されるトランジスタは、高抵抗領域2107aおよび低抵抗領域2107bを有する酸化物半導体膜2107を有する点で、図21(A)で示されるトランジスタとは異なる。具体的には、図21(B)で示されるトランジスタは、側壁絶縁膜2112と重畳する酸化物半導体膜2107の領域が高抵抗領域2107aに含まれる。即ち、該トランジスタは側壁絶縁膜2112の幅だけオフセット領域を有するトランジスタである。なお、オフセット領域の幅をオフセット長(Loff)ともいう。

【0151】

図21(B)で示されるトランジスタにおいて、Loffを5nmとし、ドレイン電流Ids(実線)および電界効果移動度μ(点線)のVgs依存性を図19に示す。なお、Idsは、Vdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図19(A)に、10nmとした場合を図19(B)に、5nmとした場合を図19(C)にそれぞれ示す。

【0152】

また、図20は、図21(B)に示されるトランジスタの構造から、Loffを15nmとしたもののドレイン電流Ids(実線)および電界効果移動度μ(点線)のVgs依存性である。なお、Idsは、Vdsを1Vとし、電界効果移動度μはVdsを0.1Vとして計算している。ここで、ゲート絶縁膜の厚さが15nmとした場合を図20(A)に、10nmとした場合を図20(B)に、5nmとした場合を図20(C)にそれぞれ示す。

【0153】

図19および図20に示した計算結果より、図18と同様に、いずれもゲート絶縁膜が薄くなるほどオフ状態(ここではVgsが−3Vから0Vの範囲を指す。)でのドレイン電流Idsが低下する。一方、電界効果移動度μのピーク値やオン状態(ここではVgsが0Vから3Vの範囲を指す。)でのドレイン電流Idsには目立った変化がないとわかる。

【0154】

なお、電界効果移動度μのピークは、図18では80cm2/Vs程度であるが、図19では60cm2/Vs程度、図20では40cm2/Vs程度、Loffが増加するほど低下することがわかる。また、オフ状態でのIdsも同様の傾向となることがわかる。一方、オン状態のIdsはオフセット長Loffの増加に伴って減少するが、オフ状態のIdsの低下に比べるとはるかに緩やかである。また、いずれの計算結果からもVgsが1V近傍で、Idsはメモリなどに必要とされる10μAを超えることがわかる。

【0155】

次に、図1で説明したメモリセルをマトリクス状に配置したメモリセルアレイについて回路図である図2を用いて説明する。

【0156】

メモリセルアレイは、ワード線WLと、ビット線BLと、バックゲート線BGLと、メモリセルMCと、を有する。

【0157】

メモリセルMCにおいて、トランジスタ140のゲートはワード線WLと接続し、トランジスタ140のソースはビット線BLと接続し、トランジスタ140のバックゲートはバックゲート線BGLと接続する。また、キャパシタ130の一対の電極の一方はトランジスタ140のドレインと接続し、キャパシタ130の一対の電極の他方は接地される。ただし、キャパシタ130の一対の電極の他方は必ずしも接地されているわけではなく、バックゲート線BGLと接続されていてもよい。

【0158】

ここで、トランジスタ140のゲートは第2のゲート電極116に、トランジスタ140のソースは導電膜120aに、トランジスタ140のドレインは導電膜120bに、トランジスタ140のバックゲートは第1のゲート電極122に、それぞれ対応する。

【0159】

なお、バックゲート線BGLは、スイッチング素子およびキャパシタと接続されていても構わない。その場合、バックゲート線BGLには、スイッチング素子を介して電位が印加される。また、スイッチング素子をオフ状態にすると、キャパシタに電位が保持される。スイッチング素子は、ノーマリーオフであることが好ましい。そうすることで、スイッチング素子への電源供給を止めた場合にもキャパシタには電位が保持されることになる。例えば、スイッチング素子として、トランジスタ140と同様のトランジスタを用いても構わない。

【0160】

ここで、ノーマリーオフとは、電源による電位の印加がないときにオフ状態であることをいう。

【0161】