半導体記憶装置およびその制御方法

【課題】プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段3と、エラー訂正後のデータを保持するデータ保持手段6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。

【解決手段】本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段3と、エラー訂正後のデータを保持するデータ保持手段6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体記憶装置およびその制御方法に関し、特に誤り訂正回路を含む半導体記憶装置およびその制御方法に関する。

【背景技術】

【0002】

一般的に、DRAM(Dynamic Random Access Memory)等の半導体メモリを含む回路では、α線や中性子線が原因で発生するソフトエラーの影響を受ける。このソフトエラーの影響を少なくするために、1ビットエラー訂正、2ビットエラー検出の機能を有するECC(Error Checking & Correction)回路が設けられている。さらに、メモリからデータを読み出す際に1ビットエラーが発生するとECC回路によりそのデータを訂正し、その訂正後のデータを同じアドレスに書き込む動作(再書き込み動作)を行うことにより、メモリから読み出されるデータの信頼性を高めることができる。このような再書き込み動作はパトロール方式とも呼ばれ、特許文献1乃至3にその技術が開示されている。

【0003】

また、SRAM(Static Random Access Memory)においても、半導体素子構造の微細化および記憶容量の増加に伴い、ソフトエラーによる影響が無視できないものとなってきている。特許文献4には、このソフトエラーによる影響を少なくするための技術が開示されている。特許文献4に開示されている半導体メモリでは、メモリセルからのデータを読み出し、エラー訂正、メモリセルへの書き戻し、といった一連の動作を1クロックサイクルで実現している。また、特許文献5には強誘電体メモリのソフトエラーによりシステムへの大きなダメージが引き起こされる確率を低減する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭59−53949号公報

【特許文献2】特開平2−103652号公報

【特許文献3】特開平4−23295号公報

【特許文献4】特開2006−114141号公報

【特許文献5】特開2004−199713号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

背景技術で説明したように、パトロール方式を用いた半導体記憶装置(例えば、DRAM)では、1ビットエラーや2ビットエラー等が発生する割合を小さくすることができるため、半導体記憶装置の信頼性を向上させることができる。しかしながら、パトロール方式を用いた半導体記憶装置では、パトロール処理を実行している間、プログラムを処理するためのメモリアクセスは待たされるため、プログラム処理性能を損なうという問題があった。

【0006】

上記課題に鑑み本発明の目的は、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することである。

【課題を解決するための手段】

【0007】

本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、前記エラー訂正後のデータを保持するデータ保持手段と、を備え、前記メモリセルは、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、前記データ保持手段は、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する。

【0008】

本発明にかかる、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、前記エラー訂正後のデータを保持するデータ保持手段と、を備える半導体記憶装置の制御方法は、前記メモリセルが、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、前記データ保持手段が、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する。

【発明の効果】

【0009】

本発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【図面の簡単な説明】

【0010】

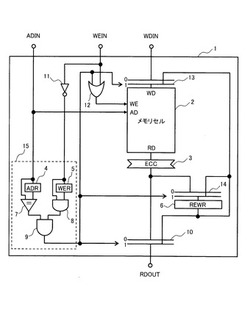

【図1】実施の形態1にかかる半導体記憶装置を示す図である。

【図2】実施の形態1にかかる半導体記憶装置の動作を説明するためのタイミングチャートである。

【図3】実施の形態2にかかる半導体記憶装置を示す図である。

【図4】実施の形態2にかかる半導体記憶装置の動作を説明するためのタイミングチャートである。

【発明を実施するための形態】

【0011】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。

図1は、本発明の実施の形態1にかかる半導体記憶装置を示す図である。

本実施の形態にかかる半導体記憶装置1は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段(ECC回路)3と、エラー訂正後のデータを保持するデータ保持手段(レジスタ(REWR))6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。また、データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。以下、本実施の形態にかかる半導体記憶装置について詳細に説明する。

【0012】

図1に示す半導体記憶装置は、1ポートRAMと呼ばれ(1RW RAMとも呼ばれる)、1サイクルに読み出し又は書き込みのどちらか一方しか実行できないタイプのRAMである。図1に示す半導体記憶装置では、2サイクル以上読み出しアドレスに変化がなかった際に、読み出したデータをECC回路にて訂正後、メモリセル2への再書き込みを実施することが可能である。

【0013】

図1に示す半導体記憶装置1は、メモリセル2、ECC回路3、レジスタ4〜6、比較器7、ANDゲート8、9、セレクタ10、13、14、インバータ11、およびORゲート12を有する。ここで、レジスタ4、5、比較器7、およびANDゲート8、9は検出手段15を構成する。半導体記憶装置1にはアドレス信号(ADIN)、ライトイネーブル信号(WEIN)、および書き込みデータ(WDIN)が入力される。また、半導体記憶装置1はアドレス信号(ADIN)に対応する読み出しデータ(RDOUT)を出力する。なお、ライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうか、また"0"の時に書き込みを行なうかについては任意に設定することができるが、本実施の形態ではライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうものとする。

【0014】

レジスタ(ADR)4は、端子ADINから供給されたアドレス信号(ADIN)を保持するレジスタである。比較器7は、一方の入力に端子ADINから供給されたアドレス信号(ADIN)が供給され、他方の入力にレジスタ4の出力が供給され、これらの比較結果をANDゲート9に出力する。すなわち、比較器7は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ4に保持された1サイクル前のアドレス信号とを比較し、2サイクル以上アドレス信号に変化がないか否かをチェックする。比較器7は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ4に保持された1サイクル前のアドレス信号とが同一である場合、ハイレベルの信号("1")を出力する。

【0015】

レジスタ(WER)5は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号を保持するレジスタである。ANDゲート(第1のANDゲート)8は、一方の入力に端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号が供給され、他方の入力にレジスタ5の出力が供給され、これらの論理積をANDゲート9に出力する。すなわち、ANDゲート8は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号と、レジスタ5に保持された1サイクル前の反転されたライトイネーブル信号(WEIN)とを比較し、2サイクル以上書き込みがないこと(つまり、2サイクル以上ライトイネーブル信号(WEIN)が"0"であること)をチェックする。

【0016】

ANDゲート(第2のANDゲート)9は、一方の入力に比較器7の出力が供給され、他方の入力にANDゲート8の出力が供給され、これらの論理積を出力する。つまり、ANDゲート9は、2サイクル以上同じアドレスで読み出しを行なっていることを検出する。半導体記憶装置1が2サイクル以上同じアドレスで読み出しを行なっている場合、ANDゲート9はハイレベルの信号("1")を出力する。

【0017】

ORゲート12は、端子WEINから供給されたライトイネーブル信号(WEIN)とANDゲート9の出力とを入力し、論理和を出力する。ここで、ANDゲート9の出力はメモリセル2への再書き込み時のライトイネーブル信号となる。よって、ORゲート12はメモリセル2のライトイネーブル(WE)に、メモリセル2への再書き込みを意味するライトイネーブル信号(ANDゲート9の出力)、またはメモリセル2への書き込みを意味するライトイネーブル信号(WEIN)を出力する。

【0018】

メモリセル2は、ライトイネーブル(WE)がハイレベルの時にアドレス(AD)に対応した書き込みデータ(WD)を保持する。また、ライトイネーブル(WE)がロウレベルの時にアドレス(AD)に対応した読み出しデータ(RD)を出力する。

【0019】

ECC回路3は、メモリセル2の読み出しデータ(RD)を入力し、当該データにエラーがある場合は当該データを訂正する。レジスタ(REWR)6は、ECC回路3で訂正されたデータをメモリセル2に書き戻すために、当該訂正されたデータを保持する。

【0020】

セレクタ14は、ANDゲート9の出力に応じて、ECC回路3で訂正されたデータまたはレジスタ6に保持されているデータを選択し、レジスタ6に出力する。つまり、セレクタ14は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、ECC回路3で訂正されたデータを選択する。また、セレクタ14は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6のデータをホールドする。

【0021】

セレクタ(第1のセレクタ)13は、ANDゲート9の出力に応じて、書き込みデータ(WDIN)またはレジスタ6に保持されているデータを選択し、メモリセル2へ出力する。つまり、セレクタ13は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合またはメモリセル2への書き込みを指示するライトイネーブル信号(WEIN)が供給された場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、書き込みデータ(WDIN)を選択する。また、セレクタ13は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6に保持されているデータを選択する。

【0022】

セレクタ10は、ANDゲート9の出力に応じて、ECC回路3で訂正されたデータまたはレジスタ6に保持されているデータを選択し、半導体記憶装置1の読み出しデータ(RDOUT)として出力する。つまり、セレクタ10は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、ECC回路3で訂正されたデータを選択する。また、セレクタ10は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6に保持されているデータを選択する。

【0023】

次に、本実施の形態にかかる半導体記憶装置の動作について、図2に示すタイミングチャートを用いて説明する。図2に示すタイミングチャートでは、端子ADINから供給されたアドレス信号(ADIN)が"2"の時に2サイクル間同一アドレスの読み出しが実施される。また、アドレス信号(ADIN)が"5"の時に3サイクル間同一アドレスが続くが、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベルとなる)が実施される。また、アドレス信号(ADIN)が"6"の時に3サイクル間同一アドレスの読み出しが実施される。なお、図2のタイミングチャートに示すように、本実施の形態にかかる半導体記憶装置ではアドレス信号(ADIN)が入力された後、1サイクル遅れて各アドレス信号(ADIN)に対応した各レジスタへのデータの保持や読み出しデータ(RDOUT)の出力等が行なわれる。

【0024】

まず、半導体記憶装置1にアドレス信号(ADIN)として"0"が供給されると、レジスタ(ADR)4はADR="0"を保持する。このとき、ライトイネーブル信号(WEIN)はロウレベル("0")であるので、レジスタ(WER)5はWER="1"を保持する。ANDゲート9の出力はロウレベルとなる。ライトイネーブル信号(WEIN)およびANDゲート9の出力が共にロウレベルであるので、メモリセル2のライトイネーブル(WE)はロウレベルとなる。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"0"が供給される。このとき、メモリセル2は、AD="0"に対応した読み出しデータ(RD="D0")をECC回路3に出力する。セレクタ14は、ANDゲート9の出力がロウレベルであるので、ECC回路3の出力を選択する。レジスタ(REWR)6はECC回路3の出力"D0"を保持する。セレクタ10は、ANDゲート9の出力がロウレベルであるので、ECC回路3の出力を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D0"が出力される。以降、アドレス信号(ADIN)が"1"、1つ目の"2"の場合も同様の動作となる。

【0025】

半導体記憶装置1にアドレス信号(ADIN)として2つ目の"2"が供給されると、比較器7は、供給されたアドレス信号(ADIN)とレジスタ(ADR)4に保持されている値が共に"2"であるので、ANDゲート9にハイレベルの信号を出力する。また、ANDゲート8は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)5に保持されている値が共にハイレベルであるので、ANDゲート9にハイレベルの信号を出力する。よって、ANDゲート9の出力はハイレベルとなる。

【0026】

ANDゲート9の出力がハイレベルであるので、ORゲート12はメモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"2"が供給される。セレクタ14は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値をホールドする。セレクタ13は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値であるREWR="D2"をメモリセル2の書き込みデータ(WD)として供給する。このとき、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="2")に対応した書き込みデータWD="D2"がメモリセル2に再書き込みされる。一方、セレクタ10はANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6に保持されているデータ"D2"を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D2"が出力される。

【0027】

アドレス信号(ADIN)として"3"、"4"が供給された場合の動作についても、上記で説明したアドレス信号(ADIN)として"0"が供給された場合の動作と同様である。

【0028】

次に、アドレス信号(ADIN)として3サイクル間"5"が供給される場合について説明する。この場合、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベル)が実施される。アドレス信号(ADIN)として最初のアドレス信号ADIN="5"が供給されると、比較器7は、レジスタ4に保持されているADR="4"と、供給されたアドレス信号ADIN="5"とが異なるのでANDゲート9にロウレベルの信号を出力する。よって、ANDゲート9の出力はロウレベルとなる。

【0029】

また、端子WEINからハイレベルのライトイネーブル信号(WEIN)が供給されると、ORゲート12は、メモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。このとき、セレクタ13は、ANDゲート9の出力がロウレベルであるので、端子WDINから供給された書き込みデータWDIN="D5"をメモリセル2の書き込みデータ(WD)として出力する。そして、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル2に書き込まれる。

【0030】

なお、この場合はANDゲート9の出力がロウレベルであるので、セレクタ10、14はECC回路3の出力を選択する。しかし、メモリセル2からは読み出しデータ(RD)が出力されないので、半導体記憶装置1のデータ出力(RDOUT)とレジスタ(REWR)6の値は"不定"となる。

【0031】

次に、アドレス信号(ADIN)として、2つ目のADIN="5"と3つ目のADIN="5"が順次供給される。このときの動作は、上記で説明した1つ目のADIN="2"と2つ目のADIN="2"が供給された場合の動作と同様であるので重複した説明は省略する。

【0032】

次に、アドレス信号(ADIN)として、3サイクル間ADIN="6"が供給される。アドレス信号(ADIN)として、1つ目のADIN="6"と2つ目のADIN="6"が供給された場合の動作は、上記で説明した1つ目のADIN="2"と2つ目のADIN="2"が供給された場合の動作と同様であるので重複した説明は省略する。

【0033】

2つ目のADIN="6"が供給された後、アドレス信号(ADIN)として3つ目のADIN="6"が供給される。このとき、比較器7は、供給されたアドレス信号(ADIN)とレジスタ(ADR)4に保持されている値が共に"6"であるので、ANDゲート9にハイレベルの信号を出力する。また、AND8は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)5に保持されている値が共にハイレベルであるので、ANDゲート9にハイレベルの信号を出力する。よって、ANDゲート9の出力はハイレベルとなる。

【0034】

ANDゲート9の出力がハイレベルであるので、ORゲート12はメモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"6"が供給される。セレクタ14は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値をホールドする。セレクタ13は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値であるREWR="D6"をメモリセル2の書き込みデータ(WD)として供給する。このとき、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="6")に対応した書き込みデータ(WD="D6")がメモリセル2に再書き込みされる。一方、セレクタ10はANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6に保持されているECC回路3でエラー訂正済みのデータ"D6"を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D6"が出力される。

【0035】

本実施の形態にかかる半導体記憶装置の動作についてまとめると次のようになる。

(1)同一アドレスn(nは任意の整数)が入力される1サイクル目に対応するタイミング。

ANDゲート9の出力はロウレベルとなる。メモリセル2は、アドレスnに対応した読み出しデータ(RD)を出力する。レジスタ(REWR)6はアドレスnに応じたエラー訂正後のデータを保持する。また、セレクタ10は、ECC回路3から出力されたアドレスnに対応したエラー訂正後のデータを半導体記憶装置の出力(RDOUT)として出力する。

【0036】

(2)同一アドレスnが入力される2サイクル目に対応するタイミング。

ANDゲート9の出力はハイレベルとなる。メモリセル2はアドレスnに対応づけてレジスタ(REWR)6に保持されているデータを書き込む(再書き込み)。レジスタ(REWR)6は、アドレスnに対応した読み出しデータとしてレジスタ(REWR)6に保持されているデータを半導体記憶装置1のデータ出力(RDOUT)として出力する。

【0037】

背景技術で説明したように、パトロール方式を用いた半導体記憶装置(例えば、DRAM)では、パトロール処理を実行している間、プログラムを処理するためのメモリアクセスは待たされるため、プログラム処理性能を損なうという問題があった。すなわち、パトロール実行中のメモリアドレスやバンクが、プログラムを処理する通常命令によるメモリアクセスと重なった場合、通常のメモリアクセスはパトロール処理を実行しているアドレスが異なるアドレスに遷移するまで待たされるという問題があった。

【0038】

また、キャッシュメモリなどに使われる半導体記憶装置(例えば、SRAM)に於いては、高速でプログラムを処理する情報処理装置のクロック周波数が高いため、特許文献4に開示されているような技術では遅延制約を満たすことが困難であるという問題があった。

【0039】

これに対して本実施の形態にかかる半導体記憶装置1では、2サイクル以上同じアドレスで読み出しを行なっている場合、レジスタ(REWR)6に保持されている1つ前のサイクルのデータをメモリセル2へ再書き込みすると同時に、当該保持されているデータを半導体記憶装置1の出力(RDOUT)として出力している。よって、メモリセル2が1サイクルに読み出し又は書き込みのどちらか一方しか実行できない場合であっても、メモリセル2へのデータの再書き込みと、半導体記憶装置1からのデータの出力(データの読み出し)とを1サイクルで同時に実施することができる。したがって、メモリアクセスタイミングを変更する必要がなくなり、クロック周波数が高い場合であっても遅延制約を満たすことができる。

【0040】

よって、本実施の形態にかかる発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【0041】

実施の形態2

次に、本発明の実施の形態2について説明する。図3は、実施の形態2にかかる半導体記憶装置を示す図である。本実施の形態にかかる半導体記憶装置では、再書き込み動作ついて巡回機能を追加している。これ以外の構成は、基本的には実施の形態1で説明した半導体記憶装置と同様である。ここで巡回機能とは、1ポートRAMにおいて4サイクル以上読み出しアドレスに変化がない場合に、その変化しなくなったアドレスを開始アドレスとして2サイクルに1回の割合でアドレスをインクリメントし、1サイクル目に読み出したデータをECC回路にて訂正後、2サイクル目に書き戻すことを順次繰り返す機能である。

【0042】

図3に示す半導体記憶装置20は、メモリセル21、ECC回路22、レジスタ23〜28、比較器29、ANDゲート30、31、セレクタ32、34〜37、40、インバータ33、38、およびORゲート39を有する。ここで、レジスタ23、24、比較器29、およびANDゲート30、31は検出手段45を構成する。また、レジスタ28、セレクタ32、およびインバータ33は、メモリセル21からのデータの読み出しまたはメモリセル21へのデータの書き込みをサイクル毎に交互に切り替える切り替え手段46を構成する。また、レジスタ25およびセレクタ34、35は、2サイクルに1回アドレスをインクリメントするアドレス生成手段47を構成する。また、本実施の形態ではデータ保持手段48は、エラー訂正後のデータを保持する第1のデータ保持手段(レジスタ(REWR))27と、エラー訂正後のデータを保持すると共に当該データを検出手段45の検出結果に応じてホールド可能な第2のデータ保持手段(レジスタ(HLDR))26と、を備える。

【0043】

半導体記憶装置20にはアドレス信号(ADIN)、ライトイネーブル信号(WEIN)、および書き込みデータ(WDIN)が入力される。また、半導体記憶装置20はアドレス信号(ADIN)に対応する読み出しデータ(RDOUT)を出力する。なお、ライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうか、また"0"の時に書き込みを行なうのかについては任意に設定することができるが、本実施の形態ではライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうものとする。

【0044】

レジスタ(ADR)23は、端子ADINから供給されたアドレス信号(ADIN)を保持するレジスタである。比較器29は、端子ADINから供給されたアドレス信号(ADIN)とレジスタ23の出力とを入力し、これらの比較結果をANDゲート31に出力する。すなわち、比較器29は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ23に保持された1サイクル前のアドレス信号とを比較し、2サイクル以上アドレス信号に変化がないか否かをチェックする。比較器29は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ23に保持された1サイクル前のアドレス信号とが同一である場合、ハイレベルの信号を出力する。

【0045】

レジスタ(WER)24は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号を保持するレジスタである。ANDゲート30は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号とレジスタ24の出力とを入力し、これらの論理積をANDゲート31に出力する。すなわち、ANDゲート30は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号と、レジスタ24に保持された1サイクル前の反転されたライトイネーブル信号(WEIN)とを比較し、2サイクル以上書き込みがないこと(つまり、2サイクル以上ライトイネーブル信号(WEIN)が"0"であること)をチェックする。

【0046】

ANDゲート31は、比較器29の出力およびANDゲート30の出力を入力し、これらの論理積を出力する。つまり、ANDゲート31は、2サイクル以上同じアドレスで読み出しを行なっていることを検出する。半導体記憶装置20が2サイクル以上同じアドレスで読み出しを行なっている場合、ANDゲート31はハイレベルの信号("1")を出力する。なお、本実施の形態では、半導体記憶装置20が2サイクル以上同じアドレスで読み出しを行なっている状態、つまりANDゲート31がハイレベルの信号を出力している状態を便宜上"RAMの巡回中"と表現する。

【0047】

セレクタ32は、ANDゲート31がハイレベルの信号を出力している場合には、レジスタ(TMGR)28に保持されている値をインバータ33で反転させた信号を選択し、ANDゲート31がロウレベルの信号を出力している場合には"0"を選択する。レジスタ(TMGR)28は、セレクタ32の出力を保持する。つまり、ANDゲート31がハイレベルの信号を2サイクル以上出力し続けている間、セレクタ32はサイクル毎に"0"と"1"を交互に出力する。

【0048】

セレクタ34は、ANDゲート31がロウレベルの信号を出力している場合、端子ADINから供給されたアドレス信号(ADIN)を選択する("0X")。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合で、かつセレクタ32の出力がロウレベルである場合、レジスタ(パトロールレジスタ:PATR)25に保持されている値を選択する("10")。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合で、かつセレクタ32の出力がハイレベルである場合、レジスタ25に保持されている値をインクリメントした値を選択する("11")。レジスタ(PATR)25はセレクタ34の出力を保持する。

【0049】

つまり、セレクタ34は、ANDゲート31がハイレベルの信号を出力し続けている場合、2サイクルに1回カウントアップした値をアドレスとして出力する。これにより、RAMの巡回中に読み出し動作と再書き込み動作を交互に繰り返すことができる。

【0050】

セレクタ35は、ANDゲート31がロウレベルの信号を出力している場合、端子ADINから供給されたアドレス信号(ADIN)を選択する。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合、レジスタ(PATR)25に保持されている値を選択する。セレクタ35の出力は、メモリセル21に対するアドレス(AD)となる。

【0051】

ORゲート39は、端子WEINから供給されたライトイネーブル信号(WEIN)とセレクタ32の出力とを入力し、論理和を出力する。ここで、セレクタ32の出力はメモリセル21への再書き込み時のライトイネーブル信号となる。よって、ORゲート39はメモリセル21のライトイネーブル(WE)に、メモリセル21への再書き込みを意味するライトイネーブル信号(セレクタ32の出力)、またはメモリセル21への書き込みを意味するライトイネーブル信号(WEIN)を出力する。

【0052】

メモリセル21は、ライトイネーブル(WE)がハイレベルの時にアドレス(AD)に対応した書き込みデータ(WD)を保持する。また、ライトイネーブル(WE)がロウレベルの時にアドレス(AD)に対応した読み出しデータ(RD)を出力する。すなわち、メモリセル21は、切り替え手段46からの信号に応じて、アドレス生成手段47で生成されたアドレスに応じたデータの読み出し、または当該アドレスに対応づけたレジスタ27に保持されているデータの書き込みを実施する。

【0053】

ECC回路22は、メモリセル21の読み出しデータ(RD)を入力し、当該データにエラーがある場合は当該データを訂正する。レジスタ(REWR:第1のレジスタ)27は、ECC回路22で訂正されたデータをメモリセル21に書き戻すために、当該訂正されたデータを保持する。

【0054】

セレクタ(第2のセレクタ)40は、ANDゲート31の出力に応じて、書き込みデータ(WDIN)またはレジスタ27に保持されているデータを選択し、メモリセル21へ出力する。つまり、セレクタ40は、ANDゲート31の出力がハイレベルである場合にはレジスタ(REWR)27に保持されているデータを、ANDゲート31の出力がロウレベルである場合には端子WDINに供給される書き込みデータ(WDIN)を、メモリセル21にそれぞれ供給する。

【0055】

セレクタ36は、ANDゲート31の出力に応じて、ECC回路22で訂正されたデータまたはレジスタ(HLDR:第2のレジスタ)26に保持されているデータを選択し、レジスタ26に出力する。つまり、セレクタ36は、ANDゲート31の出力がロウレベルである場合にはECC回路22で訂正されたデータを選択する。また、セレクタ36は、ANDゲート31の出力がハイレベルである場合にはレジスタ26のデータをホールドする。

【0056】

セレクタ37は、ANDゲート31の出力に応じて、ECC回路22で訂正されたデータまたはレジスタ26に保持されているデータを選択し、半導体記憶装置20の読み出しデータ(RDOUT)として出力する。つまり、セレクタ37は、ANDゲート31の出力がロウレベルである場合にはECC回路22で訂正されたデータを選択する。また、セレクタ37は、ANDゲート31の出力がハイレベルである場合にはレジスタ26に保持されているデータを選択する。

【0057】

次に、本実施の形態にかかる半導体記憶装置の動作について、図4に示すタイミングチャートを用いて説明する。図4に示すタイミングチャートでは、端子ADINから供給されたアドレス信号(ADIN)が"2"の時に2サイクル間同一アドレスの読み出しが実施される。また、アドレス信号(ADIN)が"5"以降において同一アドレスが続くが、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベルとなる)が実施される。なお、図4のタイミングチャートに示すように、本実施の形態にかかる半導体記憶装置ではアドレス信号(ADIN)が入力された後、1サイクル遅れて各アドレス信号(ADIN)に対応した各レジスタへのデータの保持や読み出しデータ(RDOUT)の出力等が行なわれる。

【0058】

まず、半導体記憶装置20にアドレス信号(ADIN)として"0"が供給されると、レジスタ(ADR)23はADR="0"を保持する。このとき、ライトイネーブル信号(WEIN)はロウレベル("0")であるので、レジスタ(WER)24はWER="1"を保持する。また、ANDゲート31の出力はロウレベルであるので、セレクタ32は"0"を出力する。ライトイネーブル信号(WEIN)およびセレクタ32の出力は共にロウレベルであるので、メモリセル21のライトイネーブル(WE)はロウレベルとなる。

【0059】

また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"0"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"0"が供給される。このとき、メモリセル21は、AD="0"に対応した読み出しデータ(RD="D0")をECC回路22に出力する。セレクタ36は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。レジスタ(HLDR)26はECC回路22の出力"D0"を保持する。また、レジスタ(REWR)27もECC回路22の出力"D0"を保持する。セレクタ37は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D0"が出力される。以降、アドレス信号(ADIN)が"1"、最初の"2"の場合も同様の動作となる。

【0060】

半導体記憶装置20にアドレス信号(ADIN)として2つ目の"2"が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"2"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値が共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0061】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28の初期値はロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"2"に1を加えた"3"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"3"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"2")を選択する。

【0062】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"2"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D2"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="2")に対応した書き込みデータ(WD="D2")がメモリセル21に再書き込みされる。

【0063】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D2"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D2"が出力される。

【0064】

アドレス信号(ADIN)として"3"、"4"が供給された場合についても、上記で説明したアドレス信号(ADIN)として"0"が供給された場合と同様である。

【0065】

次に、アドレス"5"への書き込み(つまり、WEIN="1")が実施される場合(符号50で示す)について説明する。アドレス信号(ADIN)としてADIN="5"が供給されると、比較器29は、レジスタ23に保持されているADR="4"と、供給されたアドレス信号ADIN="5"とが異なるのでANDゲート31にロウレベルの信号を出力する。よって、ANDゲート31の出力はロウレベルとなる。このとき、セレクタ32の出力はロウレベルとなる。

【0066】

一方、端子WEINからはハイレベルのライトイネーブル信号(WEIN)が供給されるので、ORゲート39は、メモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。このとき、セレクタ40は、ANDゲート31の出力がロウレベルであるので、端子WDINから供給された書き込みデータ(WDIN="D5")をメモリセル21の書き込みデータ(WD)として出力する。また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"5"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"5"が供給される。そして、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル21に書き込まれる。

【0067】

なお、この場合はANDゲート31の出力がロウレベルであるので、セレクタ36、37はECC回路22の出力を選択する。しかし、メモリセル21からは読み出しデータ(RD)が出力されないので、半導体記憶装置20のデータ出力(RDOUT)、レジスタ(HLDR)26、およびレジスタ(REWR)27の値は"不定"となる。

【0068】

次に、アドレス信号(ADIN)として4サイクル以上同じアドレス"5"が供給され、かつ読み出しを行なっている場合(符号51〜54で示す)について説明する。

半導体記憶装置20にアドレス信号(ADIN)として1つ目の"5"(符号51で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。一方、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号(ハイレベル)とレジスタ(WER)24に保持されている値(ロウレベル)とが異なるので、ANDゲート31にロウレベルの信号を出力する。よって、ANDゲート31の出力はロウレベルとなる。

【0069】

ANDゲート31の出力がロウレベルであるので、セレクタ32は"0"を出力する。ORゲート39は、ライトイネーブル信号(WEIN)およびセレクタ32の出力が共にロウレベルであるので、メモリセル21のライトイネーブル(WE)にロウレベルの信号を出力する。

【0070】

ANDゲート31の出力がロウレベルであるので、セレクタ34はアドレス信号(ADIN)である"5"をレジスタ(PATR)25に保持する。また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"5"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"5"が供給される。このとき、メモリセル21は、AD="5"に対応した読み出しデータ(RD="D5")をECC回路22に出力する。セレクタ36は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。レジスタ(HLDR)26はECC回路22の出力"D5"を保持する。また、レジスタ(REWR)27もECC回路22の出力"D5"を保持する。セレクタ37は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0071】

次に、半導体記憶装置20にアドレス信号(ADIN)として2つ目の"5"(符号52で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0072】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"5"に1を加えた"6"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"6"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"5")を選択する。

【0073】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"5"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D5"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル21に再書き込みされる。

【0074】

なお、このときメモリセル21は再書き込み動作を実施しているため、メモリセル21から読み出しデータ(RD)は出力されない。よって、レジスタ(REWR)27に保持されるデータは"不定"となる。しかし、この"不定"のデータはメモリセル21への再書き込み用データとして使用されないため、半導体記憶装置20の動作には影響しない。

【0075】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0076】

次に、半導体記憶装置20にアドレス信号(ADIN)として3つ目の"5"(符号53で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0077】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がハイレベル("1")であるので、セレクタ32からはロウレベルの信号が出力される。セレクタ34は、ANDゲート31の出力がハイレベル、セレクタ32の出力がロウレベルであるので、レジスタ(PATR)25に保持されている値"6"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"6"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値"6"を選択する。

【0078】

ORゲート39は、セレクタ32の出力および供給されたライトイネーブル信号(WEIN)が共にロウレベルであるので、メモリセル21のライトイネーブル(WE)にロウレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"6"が供給される。このとき、メモリセル21は、AD="6"に対応した読み出しデータ(RD="D6")をECC回路22に出力する。レジスタ(REWR)27はECC回路22の出力"D6"を保持する。セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値"D5"をホールドする。セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0079】

次に、半導体記憶装置20にアドレス信号(ADIN)として4つ目の"5"(符号54で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0080】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"6"に1を加えた"7"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"7"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"6")を選択する。

【0081】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"6"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D6"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="6")に対応した書き込みデータ(WD="D6")がメモリセル21に再書き込みされる。

【0082】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値"D5"をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0083】

以降、半導体記憶装置20にアドレス信号(ADIN)として"5"が供給され続ける限り、上記で説明した動作と同様の動作を繰り返す。

以上で説明した本実施の形態にかかる半導体記憶装置の動作をまとめると次のようになる。

【0084】

(1)同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミング。

ANDゲート31の出力はロウレベル、セレクタ32出力はロウレベルとなる。アドレス生成手段47は、入力アドレス(ADIN)nをアドレスとして出力する。メモリセル21は、アドレスnに対応した読み出しデータ(RD=Dn)を出力する。レジスタ(HLDR)26およびレジスタ(REWR)27はアドレスnに応じたエラー訂正後のデータDnを保持する。また、セレクタ37は、ECC回路22から出力されたアドレスnに対応したエラー訂正後のデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0085】

(2)同一アドレスnが入力される2サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はハイレベルとなる。アドレス生成手段47はアドレスをインクリメントし、このアドレスn+1をレジスタ(PATR)25に保持する(このアドレスn+1は、次回のサイクルで用いられる)。このとき、アドレス生成手段47はアドレスnを出力する。メモリセル21はアドレスnに対応づけてレジスタ(REWR)27に保持されているデータDnを書き込む(再書き込み)。レジスタ(HLDR)26は、アドレスnに対応した読み出しデータとしてレジスタ(HLDR)26に保持されているデータDnを出力する。セレクタ37は、レジスタ(HLDR)26に保持されているデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0086】

(3)同一アドレスnが入力される3サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はロウレベルとなる。アドレス生成手段47はレジスタ(PATR)25に保持されているアドレスn+1をホールドする。このとき、アドレス生成手段47はアドレスn+1を出力する。メモリセル21は、アドレスn+1に対応した読み出しデータ(RD=Dn+1)を出力する。レジスタ(REWR)27はアドレスn+1に対応したエラー訂正後のデータDn+1を保持する。また、セレクタ37は、レジスタ(HLDR)26に保持されているアドレスnに対応したデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0087】

(4)同一アドレスnが入力される4サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はハイレベルとなる。アドレス生成手段47はアドレスをインクリメントし、このアドレスn+2をレジスタ(PATR)25に保持する(このアドレスn+2は、次回のサイクルで用いられる)。このとき、アドレス生成手段47はアドレスn+1を出力する。メモリセル21はアドレスn+1に対応づけてレジスタ(REWR)27に保持されているデータDn+1を書き込む(再書き込み)。レジスタ(HLDR)26は、アドレスnに対応した読み出しデータとしてレジスタ(HLDR)26に保持されているデータDnを出力する。セレクタ37は、レジスタ(HLDR)26に保持されているデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0088】

以上で説明したように、本実施の形態にかかる半導体記憶装置20では、4サイクル以上同じアドレスで読み出しを行なっている場合、再書き込みを実施した読み出しアドレスから2サイクルに1回の割合でアドレスをインクリメントし、インクリメント後のアドレスを用いてメモリセル21からデータを読み出し、当該データをECC回路22で訂正後、この訂正後のデータを同一アドレス(インクリメント後のアドレス)を用いて再書き込みしている。このとき、半導体記憶装置20は出力(RDOUT)としてレジスタ(HLDR)26に保持されているデータを出力しているので、入力アドレス(ADIN)に対応したデータを出力していることになる。

【0089】

このように、本実施の形態にかかる半導体記憶装置20では、メモリセル21からの読み出しとメモリセル21への書き込みを交互に繰り返す巡回機能を実装しているので、半導体記憶装置の信頼性を向上させることができる。よって、本実施の形態にかかる発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【0090】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。上記の実施の形態では1サイクルに読み出し又は書き込みのどちらかしかできない1ポートRAMについて説明したが、本発明はこれに限定されるものではない。例えば、2ポートRAM(1R1Wとも呼ばれる)や4ポートRAM(2R2Wとも呼ばれる)等の多ポートRAMに本発明を適用してもよい。

【0091】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0092】

1、20 半導体記憶装置

2、21 メモリセル

3、22 ECC回路

4、23 レジスタ(ADR)

5、24 レジスタ(WER)

6、27 レジスタ(REWR)

7、29 比較器

8、30 ANDゲート(第1のANDゲート)

9、31 ANDゲート(第2のANDゲート)

10、13、14、32、34、35、36、37、40 セレクタ

11、33、38 インバータ

12、39 ORゲート

15、45 検出手段

25 レジスタ(PATR)

26 レジスタ(HLDR)

28 レジスタ(TMGR)

46 切り替え手段

47 アドレス生成手段

48 データ保持手段

【技術分野】

【0001】

本発明は半導体記憶装置およびその制御方法に関し、特に誤り訂正回路を含む半導体記憶装置およびその制御方法に関する。

【背景技術】

【0002】

一般的に、DRAM(Dynamic Random Access Memory)等の半導体メモリを含む回路では、α線や中性子線が原因で発生するソフトエラーの影響を受ける。このソフトエラーの影響を少なくするために、1ビットエラー訂正、2ビットエラー検出の機能を有するECC(Error Checking & Correction)回路が設けられている。さらに、メモリからデータを読み出す際に1ビットエラーが発生するとECC回路によりそのデータを訂正し、その訂正後のデータを同じアドレスに書き込む動作(再書き込み動作)を行うことにより、メモリから読み出されるデータの信頼性を高めることができる。このような再書き込み動作はパトロール方式とも呼ばれ、特許文献1乃至3にその技術が開示されている。

【0003】

また、SRAM(Static Random Access Memory)においても、半導体素子構造の微細化および記憶容量の増加に伴い、ソフトエラーによる影響が無視できないものとなってきている。特許文献4には、このソフトエラーによる影響を少なくするための技術が開示されている。特許文献4に開示されている半導体メモリでは、メモリセルからのデータを読み出し、エラー訂正、メモリセルへの書き戻し、といった一連の動作を1クロックサイクルで実現している。また、特許文献5には強誘電体メモリのソフトエラーによりシステムへの大きなダメージが引き起こされる確率を低減する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭59−53949号公報

【特許文献2】特開平2−103652号公報

【特許文献3】特開平4−23295号公報

【特許文献4】特開2006−114141号公報

【特許文献5】特開2004−199713号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

背景技術で説明したように、パトロール方式を用いた半導体記憶装置(例えば、DRAM)では、1ビットエラーや2ビットエラー等が発生する割合を小さくすることができるため、半導体記憶装置の信頼性を向上させることができる。しかしながら、パトロール方式を用いた半導体記憶装置では、パトロール処理を実行している間、プログラムを処理するためのメモリアクセスは待たされるため、プログラム処理性能を損なうという問題があった。

【0006】

上記課題に鑑み本発明の目的は、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することである。

【課題を解決するための手段】

【0007】

本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、前記エラー訂正後のデータを保持するデータ保持手段と、を備え、前記メモリセルは、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、前記データ保持手段は、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する。

【0008】

本発明にかかる、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、前記エラー訂正後のデータを保持するデータ保持手段と、を備える半導体記憶装置の制御方法は、前記メモリセルが、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、前記データ保持手段が、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する。

【発明の効果】

【0009】

本発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1にかかる半導体記憶装置を示す図である。

【図2】実施の形態1にかかる半導体記憶装置の動作を説明するためのタイミングチャートである。

【図3】実施の形態2にかかる半導体記憶装置を示す図である。

【図4】実施の形態2にかかる半導体記憶装置の動作を説明するためのタイミングチャートである。

【発明を実施するための形態】

【0011】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。

図1は、本発明の実施の形態1にかかる半導体記憶装置を示す図である。

本実施の形態にかかる半導体記憶装置1は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段(ECC回路)3と、エラー訂正後のデータを保持するデータ保持手段(レジスタ(REWR))6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。また、データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。以下、本実施の形態にかかる半導体記憶装置について詳細に説明する。

【0012】

図1に示す半導体記憶装置は、1ポートRAMと呼ばれ(1RW RAMとも呼ばれる)、1サイクルに読み出し又は書き込みのどちらか一方しか実行できないタイプのRAMである。図1に示す半導体記憶装置では、2サイクル以上読み出しアドレスに変化がなかった際に、読み出したデータをECC回路にて訂正後、メモリセル2への再書き込みを実施することが可能である。

【0013】

図1に示す半導体記憶装置1は、メモリセル2、ECC回路3、レジスタ4〜6、比較器7、ANDゲート8、9、セレクタ10、13、14、インバータ11、およびORゲート12を有する。ここで、レジスタ4、5、比較器7、およびANDゲート8、9は検出手段15を構成する。半導体記憶装置1にはアドレス信号(ADIN)、ライトイネーブル信号(WEIN)、および書き込みデータ(WDIN)が入力される。また、半導体記憶装置1はアドレス信号(ADIN)に対応する読み出しデータ(RDOUT)を出力する。なお、ライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうか、また"0"の時に書き込みを行なうかについては任意に設定することができるが、本実施の形態ではライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうものとする。

【0014】

レジスタ(ADR)4は、端子ADINから供給されたアドレス信号(ADIN)を保持するレジスタである。比較器7は、一方の入力に端子ADINから供給されたアドレス信号(ADIN)が供給され、他方の入力にレジスタ4の出力が供給され、これらの比較結果をANDゲート9に出力する。すなわち、比較器7は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ4に保持された1サイクル前のアドレス信号とを比較し、2サイクル以上アドレス信号に変化がないか否かをチェックする。比較器7は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ4に保持された1サイクル前のアドレス信号とが同一である場合、ハイレベルの信号("1")を出力する。

【0015】

レジスタ(WER)5は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号を保持するレジスタである。ANDゲート(第1のANDゲート)8は、一方の入力に端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号が供給され、他方の入力にレジスタ5の出力が供給され、これらの論理積をANDゲート9に出力する。すなわち、ANDゲート8は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ11で反転させた信号と、レジスタ5に保持された1サイクル前の反転されたライトイネーブル信号(WEIN)とを比較し、2サイクル以上書き込みがないこと(つまり、2サイクル以上ライトイネーブル信号(WEIN)が"0"であること)をチェックする。

【0016】

ANDゲート(第2のANDゲート)9は、一方の入力に比較器7の出力が供給され、他方の入力にANDゲート8の出力が供給され、これらの論理積を出力する。つまり、ANDゲート9は、2サイクル以上同じアドレスで読み出しを行なっていることを検出する。半導体記憶装置1が2サイクル以上同じアドレスで読み出しを行なっている場合、ANDゲート9はハイレベルの信号("1")を出力する。

【0017】

ORゲート12は、端子WEINから供給されたライトイネーブル信号(WEIN)とANDゲート9の出力とを入力し、論理和を出力する。ここで、ANDゲート9の出力はメモリセル2への再書き込み時のライトイネーブル信号となる。よって、ORゲート12はメモリセル2のライトイネーブル(WE)に、メモリセル2への再書き込みを意味するライトイネーブル信号(ANDゲート9の出力)、またはメモリセル2への書き込みを意味するライトイネーブル信号(WEIN)を出力する。

【0018】

メモリセル2は、ライトイネーブル(WE)がハイレベルの時にアドレス(AD)に対応した書き込みデータ(WD)を保持する。また、ライトイネーブル(WE)がロウレベルの時にアドレス(AD)に対応した読み出しデータ(RD)を出力する。

【0019】

ECC回路3は、メモリセル2の読み出しデータ(RD)を入力し、当該データにエラーがある場合は当該データを訂正する。レジスタ(REWR)6は、ECC回路3で訂正されたデータをメモリセル2に書き戻すために、当該訂正されたデータを保持する。

【0020】

セレクタ14は、ANDゲート9の出力に応じて、ECC回路3で訂正されたデータまたはレジスタ6に保持されているデータを選択し、レジスタ6に出力する。つまり、セレクタ14は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、ECC回路3で訂正されたデータを選択する。また、セレクタ14は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6のデータをホールドする。

【0021】

セレクタ(第1のセレクタ)13は、ANDゲート9の出力に応じて、書き込みデータ(WDIN)またはレジスタ6に保持されているデータを選択し、メモリセル2へ出力する。つまり、セレクタ13は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合またはメモリセル2への書き込みを指示するライトイネーブル信号(WEIN)が供給された場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、書き込みデータ(WDIN)を選択する。また、セレクタ13は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6に保持されているデータを選択する。

【0022】

セレクタ10は、ANDゲート9の出力に応じて、ECC回路3で訂正されたデータまたはレジスタ6に保持されているデータを選択し、半導体記憶装置1の読み出しデータ(RDOUT)として出力する。つまり、セレクタ10は、端子ADINから供給されたアドレス信号(ADIN)が毎サイクル異なる場合(この場合はANDゲート9がロウレベルであり、メモリセル2への再書き込みが実施されない)、ECC回路3で訂正されたデータを選択する。また、セレクタ10は、端子ADINから供給されたアドレス信号(ADIN)が2サイクル以上同一でかつ読み出しを行なっている場合(この場合はANDゲート9がハイレベルであり、メモリセル2への再書き込みが実施される)、レジスタ6に保持されているデータを選択する。

【0023】

次に、本実施の形態にかかる半導体記憶装置の動作について、図2に示すタイミングチャートを用いて説明する。図2に示すタイミングチャートでは、端子ADINから供給されたアドレス信号(ADIN)が"2"の時に2サイクル間同一アドレスの読み出しが実施される。また、アドレス信号(ADIN)が"5"の時に3サイクル間同一アドレスが続くが、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベルとなる)が実施される。また、アドレス信号(ADIN)が"6"の時に3サイクル間同一アドレスの読み出しが実施される。なお、図2のタイミングチャートに示すように、本実施の形態にかかる半導体記憶装置ではアドレス信号(ADIN)が入力された後、1サイクル遅れて各アドレス信号(ADIN)に対応した各レジスタへのデータの保持や読み出しデータ(RDOUT)の出力等が行なわれる。

【0024】

まず、半導体記憶装置1にアドレス信号(ADIN)として"0"が供給されると、レジスタ(ADR)4はADR="0"を保持する。このとき、ライトイネーブル信号(WEIN)はロウレベル("0")であるので、レジスタ(WER)5はWER="1"を保持する。ANDゲート9の出力はロウレベルとなる。ライトイネーブル信号(WEIN)およびANDゲート9の出力が共にロウレベルであるので、メモリセル2のライトイネーブル(WE)はロウレベルとなる。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"0"が供給される。このとき、メモリセル2は、AD="0"に対応した読み出しデータ(RD="D0")をECC回路3に出力する。セレクタ14は、ANDゲート9の出力がロウレベルであるので、ECC回路3の出力を選択する。レジスタ(REWR)6はECC回路3の出力"D0"を保持する。セレクタ10は、ANDゲート9の出力がロウレベルであるので、ECC回路3の出力を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D0"が出力される。以降、アドレス信号(ADIN)が"1"、1つ目の"2"の場合も同様の動作となる。

【0025】

半導体記憶装置1にアドレス信号(ADIN)として2つ目の"2"が供給されると、比較器7は、供給されたアドレス信号(ADIN)とレジスタ(ADR)4に保持されている値が共に"2"であるので、ANDゲート9にハイレベルの信号を出力する。また、ANDゲート8は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)5に保持されている値が共にハイレベルであるので、ANDゲート9にハイレベルの信号を出力する。よって、ANDゲート9の出力はハイレベルとなる。

【0026】

ANDゲート9の出力がハイレベルであるので、ORゲート12はメモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"2"が供給される。セレクタ14は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値をホールドする。セレクタ13は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値であるREWR="D2"をメモリセル2の書き込みデータ(WD)として供給する。このとき、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="2")に対応した書き込みデータWD="D2"がメモリセル2に再書き込みされる。一方、セレクタ10はANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6に保持されているデータ"D2"を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D2"が出力される。

【0027】

アドレス信号(ADIN)として"3"、"4"が供給された場合の動作についても、上記で説明したアドレス信号(ADIN)として"0"が供給された場合の動作と同様である。

【0028】

次に、アドレス信号(ADIN)として3サイクル間"5"が供給される場合について説明する。この場合、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベル)が実施される。アドレス信号(ADIN)として最初のアドレス信号ADIN="5"が供給されると、比較器7は、レジスタ4に保持されているADR="4"と、供給されたアドレス信号ADIN="5"とが異なるのでANDゲート9にロウレベルの信号を出力する。よって、ANDゲート9の出力はロウレベルとなる。

【0029】

また、端子WEINからハイレベルのライトイネーブル信号(WEIN)が供給されると、ORゲート12は、メモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。このとき、セレクタ13は、ANDゲート9の出力がロウレベルであるので、端子WDINから供給された書き込みデータWDIN="D5"をメモリセル2の書き込みデータ(WD)として出力する。そして、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル2に書き込まれる。

【0030】

なお、この場合はANDゲート9の出力がロウレベルであるので、セレクタ10、14はECC回路3の出力を選択する。しかし、メモリセル2からは読み出しデータ(RD)が出力されないので、半導体記憶装置1のデータ出力(RDOUT)とレジスタ(REWR)6の値は"不定"となる。

【0031】

次に、アドレス信号(ADIN)として、2つ目のADIN="5"と3つ目のADIN="5"が順次供給される。このときの動作は、上記で説明した1つ目のADIN="2"と2つ目のADIN="2"が供給された場合の動作と同様であるので重複した説明は省略する。

【0032】

次に、アドレス信号(ADIN)として、3サイクル間ADIN="6"が供給される。アドレス信号(ADIN)として、1つ目のADIN="6"と2つ目のADIN="6"が供給された場合の動作は、上記で説明した1つ目のADIN="2"と2つ目のADIN="2"が供給された場合の動作と同様であるので重複した説明は省略する。

【0033】

2つ目のADIN="6"が供給された後、アドレス信号(ADIN)として3つ目のADIN="6"が供給される。このとき、比較器7は、供給されたアドレス信号(ADIN)とレジスタ(ADR)4に保持されている値が共に"6"であるので、ANDゲート9にハイレベルの信号を出力する。また、AND8は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)5に保持されている値が共にハイレベルであるので、ANDゲート9にハイレベルの信号を出力する。よって、ANDゲート9の出力はハイレベルとなる。

【0034】

ANDゲート9の出力がハイレベルであるので、ORゲート12はメモリセル2のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル2のアドレス(AD)には、アドレス信号(ADIN)である"6"が供給される。セレクタ14は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値をホールドする。セレクタ13は、ANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6の値であるREWR="D6"をメモリセル2の書き込みデータ(WD)として供給する。このとき、メモリセル2のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="6")に対応した書き込みデータ(WD="D6")がメモリセル2に再書き込みされる。一方、セレクタ10はANDゲート9の出力がハイレベルであるので、レジスタ(REWR)6に保持されているECC回路3でエラー訂正済みのデータ"D6"を選択する。よって、半導体記憶装置1の出力(RDOUT)として"D6"が出力される。

【0035】

本実施の形態にかかる半導体記憶装置の動作についてまとめると次のようになる。

(1)同一アドレスn(nは任意の整数)が入力される1サイクル目に対応するタイミング。

ANDゲート9の出力はロウレベルとなる。メモリセル2は、アドレスnに対応した読み出しデータ(RD)を出力する。レジスタ(REWR)6はアドレスnに応じたエラー訂正後のデータを保持する。また、セレクタ10は、ECC回路3から出力されたアドレスnに対応したエラー訂正後のデータを半導体記憶装置の出力(RDOUT)として出力する。

【0036】

(2)同一アドレスnが入力される2サイクル目に対応するタイミング。

ANDゲート9の出力はハイレベルとなる。メモリセル2はアドレスnに対応づけてレジスタ(REWR)6に保持されているデータを書き込む(再書き込み)。レジスタ(REWR)6は、アドレスnに対応した読み出しデータとしてレジスタ(REWR)6に保持されているデータを半導体記憶装置1のデータ出力(RDOUT)として出力する。

【0037】

背景技術で説明したように、パトロール方式を用いた半導体記憶装置(例えば、DRAM)では、パトロール処理を実行している間、プログラムを処理するためのメモリアクセスは待たされるため、プログラム処理性能を損なうという問題があった。すなわち、パトロール実行中のメモリアドレスやバンクが、プログラムを処理する通常命令によるメモリアクセスと重なった場合、通常のメモリアクセスはパトロール処理を実行しているアドレスが異なるアドレスに遷移するまで待たされるという問題があった。

【0038】

また、キャッシュメモリなどに使われる半導体記憶装置(例えば、SRAM)に於いては、高速でプログラムを処理する情報処理装置のクロック周波数が高いため、特許文献4に開示されているような技術では遅延制約を満たすことが困難であるという問題があった。

【0039】

これに対して本実施の形態にかかる半導体記憶装置1では、2サイクル以上同じアドレスで読み出しを行なっている場合、レジスタ(REWR)6に保持されている1つ前のサイクルのデータをメモリセル2へ再書き込みすると同時に、当該保持されているデータを半導体記憶装置1の出力(RDOUT)として出力している。よって、メモリセル2が1サイクルに読み出し又は書き込みのどちらか一方しか実行できない場合であっても、メモリセル2へのデータの再書き込みと、半導体記憶装置1からのデータの出力(データの読み出し)とを1サイクルで同時に実施することができる。したがって、メモリアクセスタイミングを変更する必要がなくなり、クロック周波数が高い場合であっても遅延制約を満たすことができる。

【0040】

よって、本実施の形態にかかる発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【0041】

実施の形態2

次に、本発明の実施の形態2について説明する。図3は、実施の形態2にかかる半導体記憶装置を示す図である。本実施の形態にかかる半導体記憶装置では、再書き込み動作ついて巡回機能を追加している。これ以外の構成は、基本的には実施の形態1で説明した半導体記憶装置と同様である。ここで巡回機能とは、1ポートRAMにおいて4サイクル以上読み出しアドレスに変化がない場合に、その変化しなくなったアドレスを開始アドレスとして2サイクルに1回の割合でアドレスをインクリメントし、1サイクル目に読み出したデータをECC回路にて訂正後、2サイクル目に書き戻すことを順次繰り返す機能である。

【0042】

図3に示す半導体記憶装置20は、メモリセル21、ECC回路22、レジスタ23〜28、比較器29、ANDゲート30、31、セレクタ32、34〜37、40、インバータ33、38、およびORゲート39を有する。ここで、レジスタ23、24、比較器29、およびANDゲート30、31は検出手段45を構成する。また、レジスタ28、セレクタ32、およびインバータ33は、メモリセル21からのデータの読み出しまたはメモリセル21へのデータの書き込みをサイクル毎に交互に切り替える切り替え手段46を構成する。また、レジスタ25およびセレクタ34、35は、2サイクルに1回アドレスをインクリメントするアドレス生成手段47を構成する。また、本実施の形態ではデータ保持手段48は、エラー訂正後のデータを保持する第1のデータ保持手段(レジスタ(REWR))27と、エラー訂正後のデータを保持すると共に当該データを検出手段45の検出結果に応じてホールド可能な第2のデータ保持手段(レジスタ(HLDR))26と、を備える。

【0043】

半導体記憶装置20にはアドレス信号(ADIN)、ライトイネーブル信号(WEIN)、および書き込みデータ(WDIN)が入力される。また、半導体記憶装置20はアドレス信号(ADIN)に対応する読み出しデータ(RDOUT)を出力する。なお、ライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうか、また"0"の時に書き込みを行なうのかについては任意に設定することができるが、本実施の形態ではライトイネーブル信号(WEIN)が"1"の時に書き込みを行なうものとする。

【0044】

レジスタ(ADR)23は、端子ADINから供給されたアドレス信号(ADIN)を保持するレジスタである。比較器29は、端子ADINから供給されたアドレス信号(ADIN)とレジスタ23の出力とを入力し、これらの比較結果をANDゲート31に出力する。すなわち、比較器29は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ23に保持された1サイクル前のアドレス信号とを比較し、2サイクル以上アドレス信号に変化がないか否かをチェックする。比較器29は、端子ADINから供給されたアドレス信号(ADIN)と、レジスタ23に保持された1サイクル前のアドレス信号とが同一である場合、ハイレベルの信号を出力する。

【0045】

レジスタ(WER)24は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号を保持するレジスタである。ANDゲート30は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号とレジスタ24の出力とを入力し、これらの論理積をANDゲート31に出力する。すなわち、ANDゲート30は、端子WEINから供給されたライトイネーブル信号(WEIN)をインバータ38で反転させた信号と、レジスタ24に保持された1サイクル前の反転されたライトイネーブル信号(WEIN)とを比較し、2サイクル以上書き込みがないこと(つまり、2サイクル以上ライトイネーブル信号(WEIN)が"0"であること)をチェックする。

【0046】

ANDゲート31は、比較器29の出力およびANDゲート30の出力を入力し、これらの論理積を出力する。つまり、ANDゲート31は、2サイクル以上同じアドレスで読み出しを行なっていることを検出する。半導体記憶装置20が2サイクル以上同じアドレスで読み出しを行なっている場合、ANDゲート31はハイレベルの信号("1")を出力する。なお、本実施の形態では、半導体記憶装置20が2サイクル以上同じアドレスで読み出しを行なっている状態、つまりANDゲート31がハイレベルの信号を出力している状態を便宜上"RAMの巡回中"と表現する。

【0047】

セレクタ32は、ANDゲート31がハイレベルの信号を出力している場合には、レジスタ(TMGR)28に保持されている値をインバータ33で反転させた信号を選択し、ANDゲート31がロウレベルの信号を出力している場合には"0"を選択する。レジスタ(TMGR)28は、セレクタ32の出力を保持する。つまり、ANDゲート31がハイレベルの信号を2サイクル以上出力し続けている間、セレクタ32はサイクル毎に"0"と"1"を交互に出力する。

【0048】

セレクタ34は、ANDゲート31がロウレベルの信号を出力している場合、端子ADINから供給されたアドレス信号(ADIN)を選択する("0X")。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合で、かつセレクタ32の出力がロウレベルである場合、レジスタ(パトロールレジスタ:PATR)25に保持されている値を選択する("10")。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合で、かつセレクタ32の出力がハイレベルである場合、レジスタ25に保持されている値をインクリメントした値を選択する("11")。レジスタ(PATR)25はセレクタ34の出力を保持する。

【0049】

つまり、セレクタ34は、ANDゲート31がハイレベルの信号を出力し続けている場合、2サイクルに1回カウントアップした値をアドレスとして出力する。これにより、RAMの巡回中に読み出し動作と再書き込み動作を交互に繰り返すことができる。

【0050】

セレクタ35は、ANDゲート31がロウレベルの信号を出力している場合、端子ADINから供給されたアドレス信号(ADIN)を選択する。また、セレクタ34は、ANDゲート31がハイレベルの信号を出力している場合、レジスタ(PATR)25に保持されている値を選択する。セレクタ35の出力は、メモリセル21に対するアドレス(AD)となる。

【0051】

ORゲート39は、端子WEINから供給されたライトイネーブル信号(WEIN)とセレクタ32の出力とを入力し、論理和を出力する。ここで、セレクタ32の出力はメモリセル21への再書き込み時のライトイネーブル信号となる。よって、ORゲート39はメモリセル21のライトイネーブル(WE)に、メモリセル21への再書き込みを意味するライトイネーブル信号(セレクタ32の出力)、またはメモリセル21への書き込みを意味するライトイネーブル信号(WEIN)を出力する。

【0052】

メモリセル21は、ライトイネーブル(WE)がハイレベルの時にアドレス(AD)に対応した書き込みデータ(WD)を保持する。また、ライトイネーブル(WE)がロウレベルの時にアドレス(AD)に対応した読み出しデータ(RD)を出力する。すなわち、メモリセル21は、切り替え手段46からの信号に応じて、アドレス生成手段47で生成されたアドレスに応じたデータの読み出し、または当該アドレスに対応づけたレジスタ27に保持されているデータの書き込みを実施する。

【0053】

ECC回路22は、メモリセル21の読み出しデータ(RD)を入力し、当該データにエラーがある場合は当該データを訂正する。レジスタ(REWR:第1のレジスタ)27は、ECC回路22で訂正されたデータをメモリセル21に書き戻すために、当該訂正されたデータを保持する。

【0054】

セレクタ(第2のセレクタ)40は、ANDゲート31の出力に応じて、書き込みデータ(WDIN)またはレジスタ27に保持されているデータを選択し、メモリセル21へ出力する。つまり、セレクタ40は、ANDゲート31の出力がハイレベルである場合にはレジスタ(REWR)27に保持されているデータを、ANDゲート31の出力がロウレベルである場合には端子WDINに供給される書き込みデータ(WDIN)を、メモリセル21にそれぞれ供給する。

【0055】

セレクタ36は、ANDゲート31の出力に応じて、ECC回路22で訂正されたデータまたはレジスタ(HLDR:第2のレジスタ)26に保持されているデータを選択し、レジスタ26に出力する。つまり、セレクタ36は、ANDゲート31の出力がロウレベルである場合にはECC回路22で訂正されたデータを選択する。また、セレクタ36は、ANDゲート31の出力がハイレベルである場合にはレジスタ26のデータをホールドする。

【0056】

セレクタ37は、ANDゲート31の出力に応じて、ECC回路22で訂正されたデータまたはレジスタ26に保持されているデータを選択し、半導体記憶装置20の読み出しデータ(RDOUT)として出力する。つまり、セレクタ37は、ANDゲート31の出力がロウレベルである場合にはECC回路22で訂正されたデータを選択する。また、セレクタ37は、ANDゲート31の出力がハイレベルである場合にはレジスタ26に保持されているデータを選択する。

【0057】

次に、本実施の形態にかかる半導体記憶装置の動作について、図4に示すタイミングチャートを用いて説明する。図4に示すタイミングチャートでは、端子ADINから供給されたアドレス信号(ADIN)が"2"の時に2サイクル間同一アドレスの読み出しが実施される。また、アドレス信号(ADIN)が"5"以降において同一アドレスが続くが、最初の1サイクルはアドレス"5"への書き込み(つまり、WEINがハイレベルとなる)が実施される。なお、図4のタイミングチャートに示すように、本実施の形態にかかる半導体記憶装置ではアドレス信号(ADIN)が入力された後、1サイクル遅れて各アドレス信号(ADIN)に対応した各レジスタへのデータの保持や読み出しデータ(RDOUT)の出力等が行なわれる。

【0058】

まず、半導体記憶装置20にアドレス信号(ADIN)として"0"が供給されると、レジスタ(ADR)23はADR="0"を保持する。このとき、ライトイネーブル信号(WEIN)はロウレベル("0")であるので、レジスタ(WER)24はWER="1"を保持する。また、ANDゲート31の出力はロウレベルであるので、セレクタ32は"0"を出力する。ライトイネーブル信号(WEIN)およびセレクタ32の出力は共にロウレベルであるので、メモリセル21のライトイネーブル(WE)はロウレベルとなる。

【0059】

また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"0"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"0"が供給される。このとき、メモリセル21は、AD="0"に対応した読み出しデータ(RD="D0")をECC回路22に出力する。セレクタ36は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。レジスタ(HLDR)26はECC回路22の出力"D0"を保持する。また、レジスタ(REWR)27もECC回路22の出力"D0"を保持する。セレクタ37は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D0"が出力される。以降、アドレス信号(ADIN)が"1"、最初の"2"の場合も同様の動作となる。

【0060】

半導体記憶装置20にアドレス信号(ADIN)として2つ目の"2"が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"2"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値が共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0061】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28の初期値はロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"2"に1を加えた"3"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"3"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"2")を選択する。

【0062】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"2"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D2"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="2")に対応した書き込みデータ(WD="D2")がメモリセル21に再書き込みされる。

【0063】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D2"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D2"が出力される。

【0064】

アドレス信号(ADIN)として"3"、"4"が供給された場合についても、上記で説明したアドレス信号(ADIN)として"0"が供給された場合と同様である。

【0065】

次に、アドレス"5"への書き込み(つまり、WEIN="1")が実施される場合(符号50で示す)について説明する。アドレス信号(ADIN)としてADIN="5"が供給されると、比較器29は、レジスタ23に保持されているADR="4"と、供給されたアドレス信号ADIN="5"とが異なるのでANDゲート31にロウレベルの信号を出力する。よって、ANDゲート31の出力はロウレベルとなる。このとき、セレクタ32の出力はロウレベルとなる。

【0066】

一方、端子WEINからはハイレベルのライトイネーブル信号(WEIN)が供給されるので、ORゲート39は、メモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。このとき、セレクタ40は、ANDゲート31の出力がロウレベルであるので、端子WDINから供給された書き込みデータ(WDIN="D5")をメモリセル21の書き込みデータ(WD)として出力する。また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"5"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"5"が供給される。そして、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル21に書き込まれる。

【0067】

なお、この場合はANDゲート31の出力がロウレベルであるので、セレクタ36、37はECC回路22の出力を選択する。しかし、メモリセル21からは読み出しデータ(RD)が出力されないので、半導体記憶装置20のデータ出力(RDOUT)、レジスタ(HLDR)26、およびレジスタ(REWR)27の値は"不定"となる。

【0068】

次に、アドレス信号(ADIN)として4サイクル以上同じアドレス"5"が供給され、かつ読み出しを行なっている場合(符号51〜54で示す)について説明する。

半導体記憶装置20にアドレス信号(ADIN)として1つ目の"5"(符号51で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。一方、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号(ハイレベル)とレジスタ(WER)24に保持されている値(ロウレベル)とが異なるので、ANDゲート31にロウレベルの信号を出力する。よって、ANDゲート31の出力はロウレベルとなる。

【0069】

ANDゲート31の出力がロウレベルであるので、セレクタ32は"0"を出力する。ORゲート39は、ライトイネーブル信号(WEIN)およびセレクタ32の出力が共にロウレベルであるので、メモリセル21のライトイネーブル(WE)にロウレベルの信号を出力する。

【0070】

ANDゲート31の出力がロウレベルであるので、セレクタ34はアドレス信号(ADIN)である"5"をレジスタ(PATR)25に保持する。また、ANDゲート31の出力はロウレベルであるので、セレクタ35はアドレス信号(ADIN)である"5"を出力する。よって、メモリセル21のアドレス(AD)には、アドレス信号(ADIN)である"5"が供給される。このとき、メモリセル21は、AD="5"に対応した読み出しデータ(RD="D5")をECC回路22に出力する。セレクタ36は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。レジスタ(HLDR)26はECC回路22の出力"D5"を保持する。また、レジスタ(REWR)27もECC回路22の出力"D5"を保持する。セレクタ37は、ANDゲート31の出力がロウレベルであるので、ECC回路22の出力を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0071】

次に、半導体記憶装置20にアドレス信号(ADIN)として2つ目の"5"(符号52で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0072】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"5"に1を加えた"6"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"6"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"5")を選択する。

【0073】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"5"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D5"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="5")に対応した書き込みデータ(WD="D5")がメモリセル21に再書き込みされる。

【0074】

なお、このときメモリセル21は再書き込み動作を実施しているため、メモリセル21から読み出しデータ(RD)は出力されない。よって、レジスタ(REWR)27に保持されるデータは"不定"となる。しかし、この"不定"のデータはメモリセル21への再書き込み用データとして使用されないため、半導体記憶装置20の動作には影響しない。

【0075】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0076】

次に、半導体記憶装置20にアドレス信号(ADIN)として3つ目の"5"(符号53で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0077】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がハイレベル("1")であるので、セレクタ32からはロウレベルの信号が出力される。セレクタ34は、ANDゲート31の出力がハイレベル、セレクタ32の出力がロウレベルであるので、レジスタ(PATR)25に保持されている値"6"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"6"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値"6"を選択する。

【0078】

ORゲート39は、セレクタ32の出力および供給されたライトイネーブル信号(WEIN)が共にロウレベルであるので、メモリセル21のライトイネーブル(WE)にロウレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"6"が供給される。このとき、メモリセル21は、AD="6"に対応した読み出しデータ(RD="D6")をECC回路22に出力する。レジスタ(REWR)27はECC回路22の出力"D6"を保持する。セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値"D5"をホールドする。セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0079】

次に、半導体記憶装置20にアドレス信号(ADIN)として4つ目の"5"(符号54で示す)が供給されると、比較器29は、供給されたアドレス信号(ADIN)とレジスタ(ADR)23に保持されている値が共に"5"であるので、ANDゲート31にハイレベルの信号を出力する。また、ANDゲート30は、供給されたライトイネーブル信号(WEIN)を反転した信号とレジスタ(WER)24に保持されている値とが共にハイレベルであるので、ANDゲート31にハイレベルの信号を出力する。よって、ANDゲート31の出力はハイレベルとなる。

【0080】

セレクタ32は、ANDゲート31の出力がハイレベルであるので、インバータ33の出力を選択する。ここで、レジスタ(TMGR)28に保持されている値がロウレベル("0")であるので、セレクタ32からはハイレベルの信号が出力される。セレクタ34は、ANDゲート31の出力およびセレクタ32の出力が共にハイレベルであるので、レジスタ(PATR)25に保持されている値"6"に1を加えた"7"を出力する。レジスタ(PATR)25は、セレクタ34の出力値"7"を保持する。一方、セレクタ35は、ANDゲート31の出力がハイレベルであるので、レジスタ(PATR)25に既に保持されている値(つまり、セレクタ34で選択される前の値"6")を選択する。

【0081】

セレクタ32の出力がハイレベルであるので、ORゲート39はメモリセル21のライトイネーブル(WE)にハイレベルの信号を出力する。メモリセル21のアドレス(AD)には、セレクタ35の出力値である"6"が供給される。セレクタ40は、ANDゲート31の出力がハイレベルであるので、レジスタ(REWR)27の値であるREWR="D6"をメモリセル21の書き込みデータ(WD)として供給する。このとき、メモリセル21のライトイネーブル(WE)がハイレベルであるので、アドレス(AD="6")に対応した書き込みデータ(WD="D6")がメモリセル21に再書き込みされる。

【0082】

セレクタ36は、ANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26の値"D5"をホールドする。一方、セレクタ37はANDゲート31の出力がハイレベルであるので、レジスタ(HLDR)26に保持されているECC回路22でエラー訂正済みのデータ"D5"を選択する。よって、半導体記憶装置20の出力(RDOUT)として"D5"が出力される。

【0083】

以降、半導体記憶装置20にアドレス信号(ADIN)として"5"が供給され続ける限り、上記で説明した動作と同様の動作を繰り返す。

以上で説明した本実施の形態にかかる半導体記憶装置の動作をまとめると次のようになる。

【0084】

(1)同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミング。

ANDゲート31の出力はロウレベル、セレクタ32出力はロウレベルとなる。アドレス生成手段47は、入力アドレス(ADIN)nをアドレスとして出力する。メモリセル21は、アドレスnに対応した読み出しデータ(RD=Dn)を出力する。レジスタ(HLDR)26およびレジスタ(REWR)27はアドレスnに応じたエラー訂正後のデータDnを保持する。また、セレクタ37は、ECC回路22から出力されたアドレスnに対応したエラー訂正後のデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0085】

(2)同一アドレスnが入力される2サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はハイレベルとなる。アドレス生成手段47はアドレスをインクリメントし、このアドレスn+1をレジスタ(PATR)25に保持する(このアドレスn+1は、次回のサイクルで用いられる)。このとき、アドレス生成手段47はアドレスnを出力する。メモリセル21はアドレスnに対応づけてレジスタ(REWR)27に保持されているデータDnを書き込む(再書き込み)。レジスタ(HLDR)26は、アドレスnに対応した読み出しデータとしてレジスタ(HLDR)26に保持されているデータDnを出力する。セレクタ37は、レジスタ(HLDR)26に保持されているデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0086】

(3)同一アドレスnが入力される3サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はロウレベルとなる。アドレス生成手段47はレジスタ(PATR)25に保持されているアドレスn+1をホールドする。このとき、アドレス生成手段47はアドレスn+1を出力する。メモリセル21は、アドレスn+1に対応した読み出しデータ(RD=Dn+1)を出力する。レジスタ(REWR)27はアドレスn+1に対応したエラー訂正後のデータDn+1を保持する。また、セレクタ37は、レジスタ(HLDR)26に保持されているアドレスnに対応したデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0087】

(4)同一アドレスnが入力される4サイクル目に対応するタイミング。

ANDゲート31の出力はハイレベル、セレクタ32出力はハイレベルとなる。アドレス生成手段47はアドレスをインクリメントし、このアドレスn+2をレジスタ(PATR)25に保持する(このアドレスn+2は、次回のサイクルで用いられる)。このとき、アドレス生成手段47はアドレスn+1を出力する。メモリセル21はアドレスn+1に対応づけてレジスタ(REWR)27に保持されているデータDn+1を書き込む(再書き込み)。レジスタ(HLDR)26は、アドレスnに対応した読み出しデータとしてレジスタ(HLDR)26に保持されているデータDnを出力する。セレクタ37は、レジスタ(HLDR)26に保持されているデータDnを半導体記憶装置の出力(RDOUT)として出力する。

【0088】

以上で説明したように、本実施の形態にかかる半導体記憶装置20では、4サイクル以上同じアドレスで読み出しを行なっている場合、再書き込みを実施した読み出しアドレスから2サイクルに1回の割合でアドレスをインクリメントし、インクリメント後のアドレスを用いてメモリセル21からデータを読み出し、当該データをECC回路22で訂正後、この訂正後のデータを同一アドレス(インクリメント後のアドレス)を用いて再書き込みしている。このとき、半導体記憶装置20は出力(RDOUT)としてレジスタ(HLDR)26に保持されているデータを出力しているので、入力アドレス(ADIN)に対応したデータを出力していることになる。

【0089】

このように、本実施の形態にかかる半導体記憶装置20では、メモリセル21からの読み出しとメモリセル21への書き込みを交互に繰り返す巡回機能を実装しているので、半導体記憶装置の信頼性を向上させることができる。よって、本実施の形態にかかる発明により、プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置およびその制御方法を提供することができる。

【0090】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。上記の実施の形態では1サイクルに読み出し又は書き込みのどちらかしかできない1ポートRAMについて説明したが、本発明はこれに限定されるものではない。例えば、2ポートRAM(1R1Wとも呼ばれる)や4ポートRAM(2R2Wとも呼ばれる)等の多ポートRAMに本発明を適用してもよい。

【0091】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0092】

1、20 半導体記憶装置

2、21 メモリセル

3、22 ECC回路

4、23 レジスタ(ADR)

5、24 レジスタ(WER)

6、27 レジスタ(REWR)

7、29 比較器

8、30 ANDゲート(第1のANDゲート)

9、31 ANDゲート(第2のANDゲート)

10、13、14、32、34、35、36、37、40 セレクタ

11、33、38 インバータ

12、39 ORゲート

15、45 検出手段

25 レジスタ(PATR)

26 レジスタ(HLDR)

28 レジスタ(TMGR)

46 切り替え手段

47 アドレス生成手段

48 データ保持手段

【特許請求の範囲】

【請求項1】

アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、

前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、

前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、

前記エラー訂正後のデータを保持するデータ保持手段と、を備え、

前記メモリセルは、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、

前記データ保持手段は、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

半導体記憶装置。

【請求項2】

前記同一アドレスが入力される1サイクル目に対応するタイミングにおいて、前記データ保持手段は前記アドレスに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスに対応づけて前記データ保持手段に保持されている前記データを書き込み、前記データ保持手段は、前記アドレスに対応した読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

請求項1に記載の半導体記憶装置。

【請求項3】

2サイクルに1回アドレスをインクリメントするアドレス生成手段と、

前記メモリセルからのデータの読み出しまたは前記メモリセルへのデータの書き込みをサイクル毎に交互に切り替える切り替え手段と、を更に備え、

前記メモリセルは、前記切り替え手段からの信号に応じて、前記アドレス生成手段で生成されたアドレスに応じたデータの読み出し、または当該アドレスに対応づけた前記データ保持手段に保持されている前記データの書き込みを実施する、

請求項1または2に記載の半導体記憶装置。

【請求項4】

前記データ保持手段は、前記エラー訂正後のデータを保持する第1のデータ保持手段と、前記エラー訂正後のデータを保持すると共に当該データを前記検出手段の検出結果に応じてホールド可能な第2のデータ保持手段と、を備え、

前記同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミングにおいて、前記第1および第2のデータ保持手段はアドレスnに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスnに対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段は、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力し、

前記同一アドレスnが入力される3サイクル目に対応するタイミングにおいて、前記第1のデータ保持手段は前記アドレス生成手段で生成されたアドレスn+1に対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される4サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスn+1に対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段は、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力する、

請求項3に記載の半導体記憶装置。

【請求項5】

前記半導体記憶装置に供給される書き込みデータと、前記データ保持手段に保持されている前記データと、を選択的に出力する第1のセレクタを更に備え、

前記メモリセルへの書き込みを指示するライトイネーブル信号が前記半導体記憶装置に供給された場合、前記第1のセレクタは前記書き込みデータを前記メモリセルに供給し、

前記検出手段が前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出した場合、前記第1のセレクタは前記データ保持手段に保持されている前記データを前記メモリセルに供給する、

請求項1または2に記載の半導体記憶装置。

【請求項6】

前記半導体記憶装置に供給される書き込みデータと、前記第1のデータ保持手段に保持されている前記データと、を選択的に出力する第2のセレクタを更に備え、

前記メモリセルへの書き込みを指示するライトイネーブル信号が前記半導体記憶装置に供給された場合、前記第2のセレクタは前記書き込みデータを前記メモリセルに供給し、

前記切り替え手段が前記メモリセルへのデータの書き込みを指示する信号を出力した場合、前記第2のセレクタは前記第1のデータ保持手段に保持されている前記データを前記メモリセルに供給する、

請求項4に記載の半導体記憶装置。

【請求項7】

前記検出手段は、

一方の入力に前記半導体記憶装置に供給される前記アドレスが供給され、他方の入力に第1のレジスタを介して前記アドレスが供給される比較器と、

一方の入力に前記半導体記憶装置に供給されるライトイネーブル信号が反転された信号が供給され、他方の入力に第2のレジスタを介して前記ライトイネーブル信号が反転された信号が供給される第1のANDゲートと、

一方の入力に前記比較器の出力が供給され、他方の入力に前記第1のANDゲートの出力が供給される第2のANDゲートと、を備える

請求項1乃至6のいずれか一項に記載の半導体記憶装置。

【請求項8】

半導体記憶装置の制御方法であって、

前記半導体記憶装置は、

アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、

前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、

前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、

前記エラー訂正後のデータを保持するデータ保持手段と、を備え、

前記メモリセルが、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、

前記データ保持手段が、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

半導体記憶装置の制御方法。

【請求項9】

前記同一アドレスが入力される1サイクル目に対応するタイミングにおいて、前記データ保持手段が前記アドレスに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスに対応づけて前記データ保持手段に保持されている前記データを書き込み、前記データ保持手段が、前記アドレスに対応した読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

請求項8に記載の半導体記憶装置の制御方法。

【請求項10】

前記半導体記憶装置は、

2サイクルに1回アドレスをインクリメントするアドレス生成手段と、

前記メモリセルからのデータの読み出しまたは前記メモリセルへのデータの書き込みをサイクル毎に交互に切り替える切り替え手段と、

前記データ保持手段として、前記エラー訂正後のデータを保持する第1のデータ保持手段と、前記エラー訂正後のデータを保持すると共に当該データを前記検出手段の検出結果に応じてホールド可能な第2のデータ保持手段と、を更に備え、

前記同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミングにおいて、前記第1および第2のデータ保持手段がアドレスnに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスnに対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段が、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力し、

前記同一アドレスnが入力される3サイクル目に対応するタイミングにおいて、前記第1のデータ保持手段が前記アドレス生成手段で生成されたアドレスn+1に対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される4サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスn+1に対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段が、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力する、

請求項8に記載の半導体記憶装置の制御方法。

【請求項1】

アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、

前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、

前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、

前記エラー訂正後のデータを保持するデータ保持手段と、を備え、

前記メモリセルは、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、

前記データ保持手段は、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

半導体記憶装置。

【請求項2】

前記同一アドレスが入力される1サイクル目に対応するタイミングにおいて、前記データ保持手段は前記アドレスに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスに対応づけて前記データ保持手段に保持されている前記データを書き込み、前記データ保持手段は、前記アドレスに対応した読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

請求項1に記載の半導体記憶装置。

【請求項3】

2サイクルに1回アドレスをインクリメントするアドレス生成手段と、

前記メモリセルからのデータの読み出しまたは前記メモリセルへのデータの書き込みをサイクル毎に交互に切り替える切り替え手段と、を更に備え、

前記メモリセルは、前記切り替え手段からの信号に応じて、前記アドレス生成手段で生成されたアドレスに応じたデータの読み出し、または当該アドレスに対応づけた前記データ保持手段に保持されている前記データの書き込みを実施する、

請求項1または2に記載の半導体記憶装置。

【請求項4】

前記データ保持手段は、前記エラー訂正後のデータを保持する第1のデータ保持手段と、前記エラー訂正後のデータを保持すると共に当該データを前記検出手段の検出結果に応じてホールド可能な第2のデータ保持手段と、を備え、

前記同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミングにおいて、前記第1および第2のデータ保持手段はアドレスnに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスnに対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段は、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力し、

前記同一アドレスnが入力される3サイクル目に対応するタイミングにおいて、前記第1のデータ保持手段は前記アドレス生成手段で生成されたアドレスn+1に対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される4サイクル目に対応するタイミングにおいて、前記メモリセルは前記アドレスn+1に対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段は、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力する、

請求項3に記載の半導体記憶装置。

【請求項5】

前記半導体記憶装置に供給される書き込みデータと、前記データ保持手段に保持されている前記データと、を選択的に出力する第1のセレクタを更に備え、

前記メモリセルへの書き込みを指示するライトイネーブル信号が前記半導体記憶装置に供給された場合、前記第1のセレクタは前記書き込みデータを前記メモリセルに供給し、

前記検出手段が前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出した場合、前記第1のセレクタは前記データ保持手段に保持されている前記データを前記メモリセルに供給する、

請求項1または2に記載の半導体記憶装置。

【請求項6】

前記半導体記憶装置に供給される書き込みデータと、前記第1のデータ保持手段に保持されている前記データと、を選択的に出力する第2のセレクタを更に備え、

前記メモリセルへの書き込みを指示するライトイネーブル信号が前記半導体記憶装置に供給された場合、前記第2のセレクタは前記書き込みデータを前記メモリセルに供給し、

前記切り替え手段が前記メモリセルへのデータの書き込みを指示する信号を出力した場合、前記第2のセレクタは前記第1のデータ保持手段に保持されている前記データを前記メモリセルに供給する、

請求項4に記載の半導体記憶装置。

【請求項7】

前記検出手段は、

一方の入力に前記半導体記憶装置に供給される前記アドレスが供給され、他方の入力に第1のレジスタを介して前記アドレスが供給される比較器と、

一方の入力に前記半導体記憶装置に供給されるライトイネーブル信号が反転された信号が供給され、他方の入力に第2のレジスタを介して前記ライトイネーブル信号が反転された信号が供給される第1のANDゲートと、

一方の入力に前記比較器の出力が供給され、他方の入力に前記第1のANDゲートの出力が供給される第2のANDゲートと、を備える

請求項1乃至6のいずれか一項に記載の半導体記憶装置。

【請求項8】

半導体記憶装置の制御方法であって、

前記半導体記憶装置は、

アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセルと、

前記メモリセルに対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段と、

前記メモリセルから読み出されたデータのエラーを訂正するエラー訂正手段と、

前記エラー訂正後のデータを保持するデータ保持手段と、を備え、

前記メモリセルが、前記検出手段の検出結果に応じて、前記データ保持手段に保持されている前記データを前記アドレスに対応づけて書き込み、

前記データ保持手段が、前記アドレスに応じた読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

半導体記憶装置の制御方法。

【請求項9】

前記同一アドレスが入力される1サイクル目に対応するタイミングにおいて、前記データ保持手段が前記アドレスに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスに対応づけて前記データ保持手段に保持されている前記データを書き込み、前記データ保持手段が、前記アドレスに対応した読み出しデータとして前記データ保持手段に保持されている前記データを出力する、

請求項8に記載の半導体記憶装置の制御方法。

【請求項10】

前記半導体記憶装置は、

2サイクルに1回アドレスをインクリメントするアドレス生成手段と、

前記メモリセルからのデータの読み出しまたは前記メモリセルへのデータの書き込みをサイクル毎に交互に切り替える切り替え手段と、

前記データ保持手段として、前記エラー訂正後のデータを保持する第1のデータ保持手段と、前記エラー訂正後のデータを保持すると共に当該データを前記検出手段の検出結果に応じてホールド可能な第2のデータ保持手段と、を更に備え、

前記同一アドレスn(nは任意の整数とする)が入力される1サイクル目に対応するタイミングにおいて、前記第1および第2のデータ保持手段がアドレスnに対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される2サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスnに対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段が、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力し、

前記同一アドレスnが入力される3サイクル目に対応するタイミングにおいて、前記第1のデータ保持手段が前記アドレス生成手段で生成されたアドレスn+1に対応した前記エラー訂正後のデータを保持し、

前記同一アドレスnが入力される4サイクル目に対応するタイミングにおいて、前記メモリセルが前記アドレスn+1に対応づけて前記第1のデータ保持手段に保持されている前記データを書き込み、前記第2のデータ保持手段が、前記アドレスnに対応した読み出しデータとして前記第2のデータ保持手段に保持されている前記データを出力する、

請求項8に記載の半導体記憶装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−128902(P2012−128902A)

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願番号】特願2010−278836(P2010−278836)

【出願日】平成22年12月15日(2010.12.15)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願日】平成22年12月15日(2010.12.15)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]