半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は半導体記憶装置およびその製造方法に関する。

【背景技術】

【0002】

電気的に書き換え可能で且つ高集積化が可能な不揮発性半導体記憶装置として、NAND型フラッシュEEPROMが知られている。NAND型フラッシュEEPROMのメモリセルトランジスタは、電荷を蓄積するフローティングゲートとフローティングゲートの電圧を制御するコントロールゲートとを含むスタックゲート構造を有している。

【0003】

近年、メモリセルの高集積化に伴い、メモリセルアレイのパターンが微細化されている。メモリセルアレイの微細化が進むと、リソグラフィ技術によるライン・スペースによってもメモリセルアレイのフローティングゲートやSTI(Shallow Trench Isolation)を加工することが困難になる。そこで、メモリセルアレイのフローティングゲートやSTIのトレンチを加工する際には、側壁をマスクとして利用した側壁転写プロセスが用いられる。側壁転写プロセスは、芯材の側面に側壁膜を形成し、芯材を除去した後、その側壁膜をマスクとして用いて材料を加工する技術である。

【0004】

このような側壁転写プロセスを用いてメモリを製造するとき、メモリセルアレイと周辺回路とを別個に加工する。メモリセルアレイと周辺回路とを個別に加工する場合、メモリセルアレイの微細なパターンを描画するために、メモリセルアレイと周辺回路との間に比較的太いラインパターン(アレイ端パターンともいう)を設ける。このアレイ端パターンは、メモリセルアレイ端に近いメモリセルのパターンを充分に露光するために、隣接するメモリセル間の間隔と同程度の間隔を空けてメモリセルアレイに隣接するように配置される。メモリセルアレイの微細化に伴い、メモリセルアレイとアレイ端パターンとの間隔もメモリセル間の間隔と同様に狭くなる。

【0005】

従来、側壁転写プロセスの側壁マスクをメモリセルアレイ領域に形成する際に、周辺回路を被覆するフォトレジストの境界は、メモリセルアレイとアレイ端パターンとの間に位置していた。このフォトレジストをマスクとして用いてメモリセルアレイ側にある芯材をウェットエッチングで除去し、側壁マスクを形成していた。

【0006】

しかし、素子の微細化によってメモリセルアレイとアレイ端パターンとの間隔が狭くなると、フォトレジストの境界をメモリセルアレイとアレイ端パターンとの間に位置づけることは技術的に困難になる。

【0007】

また、ウェットエッチングの溶剤がアレイ端パターンに染み込み易くなり、アレイ端パターンにある芯材の一部がエッチングされ、この芯材が変形するおそれがある。この場合、芯材の形状がフローティングゲートおよび半導体基板に転写され、アレイ端パターンにあるSTIについて、所望の形状が得られない可能性がある。これは、メモリの信頼性を低下させてしまう。

【0008】

さらに、アレイ端パターンにおいては、周辺領域と同様に芯材を残置させたまま、フローティングゲートおよびSTIのトレンチが加工される。従って、アレイ端パターンにおいては、フローティングゲートは、その上面でコントロールゲートと面するため、フローティングゲートとコントロールゲートとチャネルとの間のカップリング容量比が小さくなる。これは、アレイ端パターンにおいて、フローティングゲートとコントロールゲートとの間の耐圧、あるいは、フローティングゲートと基板との間の耐圧を低下させる原因となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2008−27978号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

微細化されても、メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させ、従来よりも容易に製造可能な半導体記憶装置を提供する。

【課題を解決するための手段】

【0011】

本実施形態による半導体記憶装置は、半導体基板を備える。第1の絶縁膜が半導体基板上に設けられている。電荷蓄積層は、第1の絶縁膜上に設けられ電荷を蓄積可能である。ゲート間絶縁膜は、電荷蓄積層上に設けられている。コントロールゲートは、ゲート間絶縁膜上に設けられ電荷蓄積層の電圧を制御する。複数のメモリセルは、第1の絶縁膜と、電荷蓄積層と、ゲート間絶縁膜と、コントロールゲートとを含む。メモリセルアレイは、複数のメモリセルを有する。周辺回路は、メモリセルアレイの周辺に設けられている。第1のダミーセルは、第1の絶縁膜と、電荷蓄積層と、ゲート間絶縁膜と、コントロールゲートとを含み、メモリセルアレイの端に設けられている。第2のダミーセルは、半導体基板上に設けられ第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられている。第1のダミーセルにおいて、ゲート間絶縁膜およびコントロールゲートは電荷蓄積層の上面および2つの側面に設けられている。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に従ったメモリの構成を示す平面図。

【図2】第1の実施形態に従ったメモリセルアレイMCAの構成図。

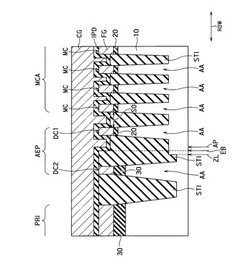

【図3】図1の3−3線に沿った断面図。

【図4】第1の実施形態によるメモリの製造方法を示す断面図。

【図5】図4に続く、メモリの製造方法を示す断面図。

【図6】図5に続く、メモリの製造方法を示す断面図。

【図7】図6に続く、メモリの製造方法を示す断面図。

【図8】図7に続く、メモリの製造方法を示す断面図。

【図9】図8に続く、メモリの製造方法を示す断面図。

【図10】図9に続く、メモリの製造方法を示す断面図。

【図11】図10に続く、メモリの製造方法を示す断面図。

【図12】第2の実施形態に従ったメモリの構成を示す断面図。

【図13】第2の実施形態によるメモリの製造方法を示す断面図。

【図14】図13に続く、メモリの製造方法を示す断面図。

【図15】第3の実施形態に従ったメモリの構成を示す断面図。

【図16】第3の実施形態によるメモリの製造方法を示す断面図。

【図17】図16に続く、メモリの製造方法を示す断面図。

【発明を実施するための形態】

【0013】

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

【0014】

(第1の実施形態)

図1は、第1の実施形態に従ったNANDフラッシュEEPROM(以下、単にメモリともいう)の構成を示す平面図である。メモリは、メモリセルアレイMCAと、周辺回路PRIと、第1のダミーセルDC1と、第2のダミーセルDC2とを備えている。

【0015】

メモリセルアレイMCAは、アクティブエリアAA上に形成された複数のメモリセルMCを有する。メモリセルアレイMCAの詳細な構成は、図2に示す。周辺回路は、メモリセルアレイMCAの周辺に形成され、メモリセルアレイMCAを制御するために設けられた複数の半導体素子(図示せず)を有する。

【0016】

第1および第2のダミーセルDC1、DC2は、アレイ端パターンAEPの領域に形成されている。アレイ端パターンAEPは、メモリセルアレイMCAの微細なパターンを描画するために、メモリセルアレイMCAと周辺回路PRIとの間に設けられたラインパターンである。本実施形態では、第1のダミーセルDC1が、メモリセルアレイMCA端に近いメモリセルMCのパターンを充分に露光するために、隣接するメモリセルMC間の間隔と同程度の間隔S0を空けてメモリセルアレイに隣接するように配置されている。

【0017】

アレイ端パターンAEPの領域上に示す第1の境界としての境界ZLは、ゲート絶縁膜の厚い高耐圧トランジスタとゲート絶縁膜の薄い低耐圧トランジスタとの境界を示す。境界ZLを境として周辺回路PRI側に高耐圧用のゲート絶縁膜が設けられ、メモリセルアレイMCA側に低耐圧用のゲート絶縁膜(トンネルゲート絶縁膜)が設けられている。従って、メモリセルMCのトンネルゲート絶縁膜は、低耐圧トランジスタ用の薄いゲート絶縁膜である。周辺回路PRIのトランジスタのゲート絶縁膜は、高耐圧トランジスタ用の厚いゲート絶縁膜である。

【0018】

本実施形態において、境界ZLは、第1のダミーセルDC1と第2のダミーセルDC2との間に位置する。従って、第1のダミーセルDC1は、低耐圧用のゲート絶縁膜(図3の参照番号20)を有する。第2のダミーセルDC2は、高耐圧用のゲート絶縁膜を有する(図3の参照番号30)。

【0019】

第2の境界としての境界APは、側壁転写プロセスを用いてメモリセルアレイMCAに側壁マスクを形成する際に、周辺回路PRIを被覆するフォトレジストの境界である。素子の微細化により、メモリセルアレイMCAとアレイ端パターンAEPとの間(間隔S0)に境界APを位置づけることは、リソグラフィ技術では困難である。これに対し、本実施形態では、間隔S0よりも広いアレイ端パターンAEPの領域(第1のダミーセルDC1と第2のダミーセルDC2との間)に境界APを位置づけている。従って、リソグラフィ技術で簡単にフォトレジストの境界APを位置づけることができる。アレイ端パターンAEPの領域に境界APがある場合、アレイ端パターンAEPにある芯材は変形したまま残存せず、除去される(図7参照)。このため、アレイ端パターンAEPにあるダミーセルDC1、DC2は、メモリセルMCとほぼ同じサイズに形成される。

【0020】

第3の境界としての境界EBは、素子分離STIをエッチングバックするときに周辺回路PRIを被覆するフォトレジストの境界である。メモリセルアレイMCAの領域では素子分離STIの形成時に、素子分離STIをエッチングバックしてフローティングゲートFG(電荷蓄積層)の側面を露出させ、フローティングゲートFGの側面にIPD(Inter-Poly Dielectric)膜およびコントロールゲートCGを設ける。素子分離STIのエッチングバックの際、周辺回路PRをフォトレジストで保護する。境界EBは、第1のダミーセルDC1と第2のダミーセルDC2との間に位置する。従って、第1のダミーセルDC1のフローティングゲートFGの両側側面には、IPD膜およびコントロールゲートCGが設けられる。一方、第2のダミーセルDC1のフローティングゲートFGの両側側面には、IPD膜およびコントロールゲートCGはほとんど設けられず、素子分離STIが残置される。尚、メモリセルMC、第1および第2のダミーセルDC1、DC2のより詳細な構成および製造方法は、後述する。

【0021】

図2は、第1の実施形態に従ったメモリセルアレイMCAの構成図である。メモリセルアレイは、複数のメモリブロックBLOCKを含む。図2には、或るブロックBLOCKi(iは整数)の構成を示す。ブロックBLOCKiは、データ消去の単位であり、各カラムのビット線BLに接続される複数のNANDストリングNS0〜NS5を含む。NANDストリングNS0〜NS5は、直列に接続された複数のメモリセルMCと、これらのメモリセルMCの両端に接続された選択ゲートトランジスタSGS、SGDとを有する。NANDストリングNSは、図1に示すようにストライプ状に形成されたアクティブエリアAA上に設けられている。この例では、各NANDストリングNSにおいて5つのメモリセルMCが直列に接続されているが、通常、32個または64個のメモリセルMCが直列に接続されている。NANDストリングNS0〜NS5の一端は、対応するビット線BL0〜BL5に接続され、その他端は共通ソース線SLに接続されている。

【0022】

メモリセルMCのコントロールゲートCGは、そのメモリセルMCが属するページに対応するワード線WL0〜WL4に接続されている。例えば、ページj(j=0〜4)に属するメモリセルMCのコントロールゲートは、ワード線WLjに接続されている。選択ゲートトランジスタSGD、SGSのゲートは、選択ゲート線SGL1またはSGL2に接続されている。ページは、データ読出しまたはデータ書込みの単位である。

【0023】

複数のワード線WLは、ロウ方向に延伸しており、複数のビット線BLは、ロウ方向にほぼ直交するようにカラム方向に延伸している。

【0024】

図2に示すように、メモリセルMCは、ワード線WLとビット線BLとによって構成される格子形状の交点に対応して設けられている。例えば、ワード線WL0〜WL4とビット線BL0〜BL5とによって構成される格子形状の交点は、5×6のマトリクス状に位置する。メモリセルMCは、これらの交点に対応するように5×6のマトリクス状に二次元配置されている。尚、本実施形態のブロックは、5×6(30個)のメモリセルMCを有するが、1ブロック内のメモリセルMCの個数は、これに限定されない。

【0025】

メモリセルMCは、フローティングゲートFGおよびコントロールゲートCGを有するn型FET(Field-Effect Transistor)で構成されている。ワード線WLによってコントロールゲートCGに電圧を与えることで、フローティングゲートFGに電荷(電子)を注入し、あるいは、フローティングゲートFGから電荷(電子)を放出させる。これにより、メモリセルMCにデータを書き込み、あるいは、メモリセルMCのデータを消去する。メモリセルMCは、フローティングゲートFGに蓄積された電荷の量(電子の数)に応じた閾値電圧を有する。メモリセルMCは、閾値電圧の違いとして、二値データ(1ビット)あるいは多値データ(2ビット以上)を電気的に記憶することができる。

【0026】

図3は、図1の3−3線に沿った断面図である。図3は、メモリセルアレイMCA、アレイ端パターンAEPおよび周辺回路PRIの構成を示す。

【0027】

本実施形態によるメモリは、半導体基板10を備えている。メモリセルMCは、トンネルゲート絶縁膜20と、フローティングゲートFGと、ゲート間絶縁膜IPDと、コントロールゲートCGとを含む。

【0028】

第1の絶縁膜としてのトンネルゲート絶縁膜20は、半導体基板10上に設けられている。トンネルゲート絶縁膜20は、低耐圧用のゲート絶縁膜であり、例えば、シリコン酸化膜を用いて形成されている。フローティングゲートFGは、トンネルゲート絶縁膜20上に設けられ、電荷(電子)を蓄積し、あるいは、放出することによってデータを格納することができる。フローティングゲートFGは、例えば、ポリシリコンを用いて形成されている。ゲート間絶縁膜IPDは、フローティングゲートFG上に設けられている。ゲート間絶縁膜IPDは、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜よりも誘電率の高いHigh−k膜を用いて形成されている。コントロールゲートCGは、ゲート間絶縁膜IPD上に設けられており、フローティングゲートFGの電圧を制御する。コントロールゲートCGは、例えば、ポリシリコンを用いて形成されている。

【0029】

コントロールゲートCGおよびゲート間絶縁膜IPDは、互いに隣接する複数のメモリセルMC間において素子分離STI(半導体基板10)へ向かって落とし込まれており、フローティングゲートFGのロウ方向に向く2つの側面に面している。これにより、コントロールゲートCGとフローティングゲートFGとの間の対向面積が大きくなるので、コントロールゲートCGとフローティングゲートFGとチャネルとの間のカップリング容量比Crが大きくなる。これにより、コントロールゲートCGによって、フローティングゲートFGの電圧を制御しやすくなる。

【0030】

メモリセルアレイMCAと周辺回路PRIとの間のアレイ端パターンAEPには、第1および第2のダミーセルDC1、DC2が設けられている。第1および第2のダミーセルDC1、DC2の平面レイアウトにおける大きさは、メモリセルMCとほぼ同じ大きさである。

【0031】

第1のダミーセルDC1は、メモリセルMCと同様の構成を有する。即ち、第1のダミーセルDC1は、トンネルゲート絶縁膜20と、フローティングゲートFGと、ゲート間絶縁膜IPDと、コントロールゲートCGとを含む。第1のダミーセルDC1は、メモリセルアレイMCAから間隔S0だけ離れた位置に、メモリセルアレイMCAの端に隣接して設けられている。間隔S0は、メモリセルアレイMCAを微細加工することができるように設定され、メモリセルMC間の間隔と同程度かそれより大きくてもよい。

【0032】

境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間にあるので、第1のダミーセルDC1においては、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面だけでなく、ロウ方向に向く2つの側面にも設けられている。換言すると、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGのロウ方向の両側において素子分離STI(半導体基板10)に向かって落とし込まれている。これにより、コントロールゲートCGは、フローティングゲートFGの上面だけでなく、2つの側面にも面しているので、カップリング容量比Crが大きくなる。その結果、データ書込みまたはデータ消去において、コントロールゲートCG(ワード線WL)に電圧が印加された場合であっても、第1のダミーセルDC1において、ゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊され難くなる。

【0033】

第2のダミーセルDC2は、第1のダミーセルDC1と周辺回路PRIとの間に設けられており、トンネルゲート絶縁膜20よりも厚い第2の絶縁膜としてのゲート絶縁膜30を備える。これは、境界ZLが第1のダミーセルDC1と第2のダミーセルDC2との間にあるからである。さらに、第2のダミーセルDC2は、ゲート絶縁膜30上に形成されたフローティングゲートFGと、フローティングゲートFG上に設けられたゲート間絶縁膜IPDと、ゲート間絶縁膜IPD上に設けられたコントロールゲートCGとを備えている。

【0034】

第2のダミーセルDC2において、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面に設けられているものの、フローティングゲートFGの両側において素子分離STI(半導体基板10)に向かって落とし込まれていない。フローティングゲートFGのロウ方向に向かう2つの側面は、素子分離STIに面している。これは、境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間に位置するからである。しかし、第2のダミーセルDC2は、高耐圧用のゲート絶縁膜30を備えているため、第2のダミーセルDC2の耐圧は問題とならない。

【0035】

本実施形態によれば、第1のダミーセルDC1において、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面だけでなく、ロウ方向に向く2つの側面にも設けられている。コントロールゲートCGは、フローティングゲートFGの上面だけでなく、2つの側面にも面しているので、カップリング容量比Crが大きくなる。その結果、データ書込みまたはデータ消去において、コントロールゲートCG(ワード線WL)に電圧が印加された場合であっても、第1のダミーセルDC1において、ゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊され難くなる。即ち、アレイ端パターンAEPにおける第1および第2のダミーセルDC1、DC2の耐圧を上昇させることができる。

【0036】

図4〜図11は、第1の実施形態によるメモリの製造方法を示す断面図である。まず、図4に示すように、第1の絶縁膜としてのトンネルゲート絶縁膜20および第2の絶縁膜としてのゲート絶縁膜30を半導体基板10上に形成する。第1の境界としての境界ZLを境としてメモリセルアレイMCA側にトンネルゲート絶縁膜20を形成し、周辺回路PRI側にゲート絶縁膜30を形成する。トンネルゲート絶縁膜20は、例えば、数nmであり、ゲート絶縁膜30は、トンネルゲート絶縁膜20よりも厚く、例えば、約30nmである。

【0037】

トンネルゲート絶縁膜20およびゲート絶縁膜30は、例えば、半導体基板10を熱酸化して形成されたシリコン酸化膜を用いて形成されている。尚、トンネルゲート絶縁膜20の表面およびゲート絶縁膜30の表面が同一面になるように、周辺回路PRI側の半導体基板10の表面は、予めエッチングされている。

【0038】

ここで、境界ZLは、後に形成される第1のダミーセルDC1と第2のダミーセルDC2との間に位置し、メモリセルMCと第1のダミーセルDC1との間には位置していない。即ち、境界ZLは、メモリセルMCと第1のダミーセルDC1との間隔S0よりも広いアレイ端パターンAEPに重複するように設定されている。メモリセルMCと第1のダミーセルDC1との間の間隔S0は、例えば、約50〜150nmであり、第1のダミーセルDC1と第2のダミーセルDC2との間の間隔(アレイ端パターンAEPの間隔)は、例えば、約500nmである。従って、本実施形態によれば、半導体基板10のエッチングおよびゲート絶縁膜20、30の形成のためのリソグラフィ工程において、アライメントが比較的容易である。

【0039】

次に、図5に示すように、トンネルゲート絶縁膜20およびゲート絶縁膜30上にフローティングゲートFGの材料を堆積する。フローティングゲートFGは、例えば、ポリシリコンを用いて形成されている。

【0040】

次に、第1のマスク材41の材料、第2のマスク材42の材料および芯材50の材料をフローティングゲートFGの材料上に堆積する。第1のマスク材41は、例えばシリコン酸化膜等の絶縁膜を用いて形成される。第2のマスク材41は、例えば第1のマスク材および芯材50とは異なる絶縁膜、例えばアモスファスシリコン膜やシリコン窒化膜を用いて形成される。芯材50は、例えば、シリコン酸化膜等の絶縁膜を用いて形成されている。次に、リソグラフィ技術およびRIE(Reactive Ion Etching)法を用いて、芯材50の材料を加工する。このとき、図6に示すように、アレイ端パターンAEPの芯材50は境界ZLに重複する。続いて、側壁マスク60の材料を芯材50の上面および側面、並びに、第2のマスク材42の材料上に堆積する。側壁マスク60の材料は、芯材50とは異なる絶縁膜、例えば、シリコン窒化膜またはアモルファスシリコンを用いて形成されている。側壁マスク60の材料は、側壁マスク60の材料を芯材50の上面および側面を被覆するように形成される。次に、RIE法を用いて側壁マスク60の材料を異方的にエッチングする。これにより、図6に示すように、側壁マスク60が芯材50の側面に残置される。

【0041】

次に、リソグラフィ技術を用いて、第2の境界としての境界APを境として、周辺回路PRI側の領域をフォトレジストPRで被覆する。境界APは、境界ZLと同様に、第1のダミーセルDC1と第2のダミーセルDC2との間に位置し、アレイ端パターンAEPに重複するように設定されている。

【0042】

次に、フォトレジストPRをマスクとして用いて、側壁マスク60を残置させたまま、露出された芯材50を選択的にエッチングする。このとき、ウェットエッチング、CDE(Chemical Dry Etching)等の等方性エッチングを用いて、芯材50を除去する。境界APは、アレイ端パターンAEPに重複しており、アレイ端パターンAEPにおける芯材50の上面の一部は露出されている。従って、アレイ端パターンAEPの芯材50も同時に除去される。フォトレジストPRで被覆された周辺回路PRI側の芯材50は残置される。これにより、図7に示す構造が得られる。

【0043】

境界AP(アレイ端パターンAEP)より周辺回路PRI側においては、芯材50が残置されているので、周辺回路PRIでは、芯材50および側壁マスク60が素子の電極パターン(ゲート電極またはキャパシタ電極等)に形成される。一方、境界APよりメモリセルアレイMCA側では、芯材50は除去されるので、側壁マスク60がフローティングゲートFGのパターンに形成される。また、アレイ端パターンAEPのうち境界APより周辺回路PRI側でも、芯材50は除去されるので、側壁マスク60がフローティングゲートFGのパターンに形成される。

【0044】

次に、フォトレジストPRの除去後、側壁マスク60または芯材50をマスクとして用いて、第2のマスク材42をRIE法で加工する。第2のマスク材42をマスクとして用いて、第1のマスク材41をRIE法で加工する。第1のマスク材41をマスクとして、フローティングゲートFGの材料、トンネルゲート絶縁膜20、ゲート絶縁膜30および半導体基板10をRIE法で加工する。これにより、図8に示すように、フローティングゲートFGを形成するとともに、素子分離STIに用いられるトレンチ70を形成する。

【0045】

尚、境界ZLを境として、膜厚の異なるトンネルゲート絶縁膜20およびゲート絶縁膜30が隣接している。絶縁膜20、30(例えば、シリコン酸化膜)をエッチングする際、絶縁膜20、30のエッチング選択比は、半導体基板10(例えば、シリコン単結晶)に比べて高い。絶縁膜20、30のエッチングを終了し半導体基板10のエッチングを開始する時点では、ZL境界部における半導体基板10の段差は残った状態となっている。半導体基板10のエッチング速度はメモリセルMCA、アレイ端パターンAEPおよび周辺回路PRIのいずれにおいても変わらない。このため、アレイ端パターンAEPにおけるトレンチ70の底部には、境界ZLを境として段差STが形成される。

【0046】

次に、トレンチ70内に素子分離絶縁膜80を充填する。続いて、フローティングゲートFGの上面が露出されるまで、素子分離絶縁膜80を平坦化処理する。これにより、図9に示す構造が得られる。

【0047】

次に、図10に示すように、リソグラフィ技術を用いて、第3の境界としての境界EBを境として周辺回路PRI側の領域をフォトレジストPR2で被覆し、メモリセルアレイMCA側の領域を露出させる。次に、図10に示すように、メモリセルアレイMCAにある素子分離絶縁膜80をエッチングバックすることによって、フローティングゲートFGの側面の上部を露出させる。境界EBは、第1のダミーセルDC1と周辺回路PRIとの間にあり、本実施形態では、境界EBは、アレイ端パターンAEPに重複している。従って、第1のダミーセルDC1のフローティングゲートFGの側面も露出される。

【0048】

一方、本実施形態では、第2のダミーセルDC2は、フォトレジストPR2で被覆されているため、第2のダミーセルDC2の側面は、素子分離絶縁膜80で被覆されたままである。

【0049】

フォトレジストPR2の除去後、図11に示す構ように、ゲート間絶縁膜IPDをメモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの上面および側面に堆積する。即ち、ゲート間絶縁膜IPDは、隣接するメモリセルMC間にある素子分離STI(半導体基板10)に向かって落とし込まれている。また、ゲート間絶縁膜IPDは、第1のダミーセルDC1の上面および側面も被覆するように形成され、第1のダミーセルDC1の両側においても素子分離STI(半導体基板10)に向かって落とし込まれている。さらに、第2のダミーセルDC2の側面は素子分離絶縁膜80で被覆されたままであるので、ゲート間絶縁膜IPDは、第2のダミーセルDC2の上面上に堆積されるが、その側面には堆積されない。

【0050】

ゲート間絶縁膜IPDの膜厚は、ゲート間絶縁膜IPDが互いに隣接するメモリセルMC間を埋め込まないように、メモリセルMC間の間隔の2分の1未満とする。

【0051】

次に、周辺回路PRIにおいて、フローティングゲートFGとコントロールゲートCGとを電気的に接続させるために、ゲート間絶縁膜IPDの一部を除去する。また、必要に応じてメモリセルアレイMCAにおいても、図示しない選択ゲートトランジスタ部分のゲート間絶縁膜IPDの一部を除去する。

【0052】

次に、コントロールゲートCGの材料をゲート間絶縁膜IPD上に堆積する。コントロールゲートCGは、例えば、ポリシリコンや金属シリサイドを用いて形成される。コントロールゲートCGは、メモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの上面および側面にゲート間絶縁膜IPDを介して形成される。換言すると、コントロールゲートCGは、ゲート間絶縁膜IPDと同様に、メモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの両側において素子分離STI(半導体基板10)に向かって落とし込まれている。コントロールゲートCGを加工した後、層間絶縁膜、ビット線BL等を形成することによって、図3に示すメモリが完成する。

【0053】

本実施形態によれば、境界ZLがアレイ端パターンAEPの第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。通常、第1のダミーセルDC1と第2のダミーセルDC2との間の間隔は、メモリセルアレイMCAと第1のダミーセルDC1との間の間隔S0に比べて大きい。従って、本実施形態では、高耐圧用のゲート絶縁膜30と低耐圧用のトンネルゲート絶縁膜20とを形成する際の、リソグラフィ工程のアライメントが容易である。境界APおよびEBについても、境界ZLと同様のことが言える。

【0054】

本実施形態によれば、境界ZLがアレイ端パターンAEPの第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。これにより、第2のダミーセルDC2は、トンネルゲート絶縁膜20よりも厚いゲート絶縁膜30を備える。従って、第2のダミーセルDC2は、メモリセルMCよりも耐圧の高い高耐圧トランジスタとなる。

【0055】

一方、第1のダミーセルDC1は、トンネルゲート絶縁膜20を備える。しかし、境界APおよび境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。従って、アレイ端パターンAEPにある芯材50を除去し、第1のダミーセルDC1と第2のダミーセルDC2との間に素子分離STIを形成することができ、かつ、第1のダミーセルDC1のフローティングゲートFGの両側にある素子分離絶縁膜80をエッチングバックすることができる。これにより、コントロールゲートCGは、第1のダミーセルDC1のフローティングゲートFGの両側面にゲート間絶縁膜IPDを介して面する。その結果、カップリング容量比Crが大きくなり、データ書込みまたはデータ消去において、第1のダミーセルDC1のゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊されることを抑制することができる。即ち、アレイ端パターンAEPにおける第1および第2のダミーセルDC1、DC2の耐圧を上昇させることができる。

【0056】

(第2の実施形態)

図12は、第2の実施形態に従ったメモリの構成を示す断面図である。第2の実施形態では、境界EBが第2のダミーセルDC2に重複するように設定されている点で第1の実施形態と異なる。これにより、第2のダミーセルDC2のフローティングゲートFGの片側側面F1にはゲート間絶縁膜IPDおよびコントロールゲートCGが設けられており、他方の側面F2には素子分離絶縁膜80が設けられている。これにより、第2のダミーセルDC2の耐圧が第1の実施形態と比べさらに高くなる。第2の実施形態のその他の構成は、対応する第1の実施形態の構成と同様でよい。従って、第2の実施形態は、第1の実施形態と同様の効果を有する。

【0057】

第2の実施形態の製造方法は、図4から図9に示す工程を得た後、図13および図14に示す工程を含む。

【0058】

第2の実施形態では、境界EBが第2のダミーセルDC2に重複するので、素子分離絶縁膜80をエッチングバックする際に、図13に示すように、第2のダミーセルDC2のフローティングゲートFGの片側の側面F1が露出される。

【0059】

これに伴い、図14に示すように、ゲート間絶縁膜IPDは、第2のダミーセルDC2のフローティングゲートFGの上面および片側の側面F1にも形成される。第2のダミーセルDC2のフローティングゲートFGの他方の側面F2は、素子分離STIで被覆されたままである。コントロールゲートCGは、第2のダミーセルDC2のフローティングゲートFGの上面および片側の側面F1にゲート間絶縁膜IPDを介して形成される。その後、第1の実施形態と同様に層間絶縁膜およびビット線等を形成することによって、第2の実施形態によるメモリが完成する。

【0060】

(第3の実施形態)

図15は、第3の実施形態に従ったメモリの構成を示す断面図である。第3の実施形態では、境界EBが第2のダミーセルDC2と周辺回路PRIとの間にある素子分離STIにおいて重複するように設定されている点で第1の実施形態と異なる。これにより、第2のダミーセルDC2のフローティングゲートFGの両側側面F1、F2にはゲート間絶縁膜IPDおよびコントロールゲートCGが設けられている。これにより、第2のダミーセルDC2の耐圧が第2の実施形態と比べさらに高くなる。第3の実施形態のその他の構成は、対応する第1の実施形態の構成と同様でよい。従って、第3の実施形態は、第1の実施形態と同様の効果を有する。

【0061】

第3の実施形態の製造方法は、図4から図9に示す工程を得た後、図16および図17に示す工程を含む。

【0062】

第3の実施形態では、境界EBが第2のダミーセルDC2と周辺回路PRIとの間の素子分離STIに重複するので、素子分離絶縁膜80をエッチングバックする際に、図16に示すように、第2のダミーセルDC2のフローティングゲートFGの両側側面F1、F2が露出される。

【0063】

これに伴い、図17に示すように、ゲート間絶縁膜IPDは、第2のダミーセルDC2のフローティングゲートFGの上面および両側側面F1、F2にも形成される。コントロールゲートCGは、第2のダミーセルDC2のフローティングゲートFGの上面および両側側面F1、F2にゲート間絶縁膜IPDを介して形成される。その後、第1の実施形態と同様に層間絶縁膜およびビット線等を形成することによって、第3の実施形態によるメモリが完成する。

【0064】

尚、第1から第3の実施形態により、境界EBは、第1のダミーセルDC1と周辺回路PRIとの間の任意の位置、言い換えると境界ZLを基準としてメモリセルアレイMCA側のもっとも近くに設けられた側壁60と周辺回路PRIとの間に設定されればよいことになる。

【0065】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0066】

MCA・・・メモリセルアレイ、PRI・・・周辺回路、MC・・・メモリセル、DC1・・・第1のダミーセル、DC2・・・第2のダミーセル、AEP・・・アレイ端パターン、STI・・・素子分離、AA・・・アクティブエリア、FG・・・フローティングゲート、CG・・・コントロールゲート、IPD・・・IPD膜、10・・・半導体基板、20・・・トンネルゲート絶縁膜、30・・・ゲート絶縁膜

【技術分野】

【0001】

本発明の実施形態は半導体記憶装置およびその製造方法に関する。

【背景技術】

【0002】

電気的に書き換え可能で且つ高集積化が可能な不揮発性半導体記憶装置として、NAND型フラッシュEEPROMが知られている。NAND型フラッシュEEPROMのメモリセルトランジスタは、電荷を蓄積するフローティングゲートとフローティングゲートの電圧を制御するコントロールゲートとを含むスタックゲート構造を有している。

【0003】

近年、メモリセルの高集積化に伴い、メモリセルアレイのパターンが微細化されている。メモリセルアレイの微細化が進むと、リソグラフィ技術によるライン・スペースによってもメモリセルアレイのフローティングゲートやSTI(Shallow Trench Isolation)を加工することが困難になる。そこで、メモリセルアレイのフローティングゲートやSTIのトレンチを加工する際には、側壁をマスクとして利用した側壁転写プロセスが用いられる。側壁転写プロセスは、芯材の側面に側壁膜を形成し、芯材を除去した後、その側壁膜をマスクとして用いて材料を加工する技術である。

【0004】

このような側壁転写プロセスを用いてメモリを製造するとき、メモリセルアレイと周辺回路とを別個に加工する。メモリセルアレイと周辺回路とを個別に加工する場合、メモリセルアレイの微細なパターンを描画するために、メモリセルアレイと周辺回路との間に比較的太いラインパターン(アレイ端パターンともいう)を設ける。このアレイ端パターンは、メモリセルアレイ端に近いメモリセルのパターンを充分に露光するために、隣接するメモリセル間の間隔と同程度の間隔を空けてメモリセルアレイに隣接するように配置される。メモリセルアレイの微細化に伴い、メモリセルアレイとアレイ端パターンとの間隔もメモリセル間の間隔と同様に狭くなる。

【0005】

従来、側壁転写プロセスの側壁マスクをメモリセルアレイ領域に形成する際に、周辺回路を被覆するフォトレジストの境界は、メモリセルアレイとアレイ端パターンとの間に位置していた。このフォトレジストをマスクとして用いてメモリセルアレイ側にある芯材をウェットエッチングで除去し、側壁マスクを形成していた。

【0006】

しかし、素子の微細化によってメモリセルアレイとアレイ端パターンとの間隔が狭くなると、フォトレジストの境界をメモリセルアレイとアレイ端パターンとの間に位置づけることは技術的に困難になる。

【0007】

また、ウェットエッチングの溶剤がアレイ端パターンに染み込み易くなり、アレイ端パターンにある芯材の一部がエッチングされ、この芯材が変形するおそれがある。この場合、芯材の形状がフローティングゲートおよび半導体基板に転写され、アレイ端パターンにあるSTIについて、所望の形状が得られない可能性がある。これは、メモリの信頼性を低下させてしまう。

【0008】

さらに、アレイ端パターンにおいては、周辺領域と同様に芯材を残置させたまま、フローティングゲートおよびSTIのトレンチが加工される。従って、アレイ端パターンにおいては、フローティングゲートは、その上面でコントロールゲートと面するため、フローティングゲートとコントロールゲートとチャネルとの間のカップリング容量比が小さくなる。これは、アレイ端パターンにおいて、フローティングゲートとコントロールゲートとの間の耐圧、あるいは、フローティングゲートと基板との間の耐圧を低下させる原因となる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2008−27978号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

微細化されても、メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させ、従来よりも容易に製造可能な半導体記憶装置を提供する。

【課題を解決するための手段】

【0011】

本実施形態による半導体記憶装置は、半導体基板を備える。第1の絶縁膜が半導体基板上に設けられている。電荷蓄積層は、第1の絶縁膜上に設けられ電荷を蓄積可能である。ゲート間絶縁膜は、電荷蓄積層上に設けられている。コントロールゲートは、ゲート間絶縁膜上に設けられ電荷蓄積層の電圧を制御する。複数のメモリセルは、第1の絶縁膜と、電荷蓄積層と、ゲート間絶縁膜と、コントロールゲートとを含む。メモリセルアレイは、複数のメモリセルを有する。周辺回路は、メモリセルアレイの周辺に設けられている。第1のダミーセルは、第1の絶縁膜と、電荷蓄積層と、ゲート間絶縁膜と、コントロールゲートとを含み、メモリセルアレイの端に設けられている。第2のダミーセルは、半導体基板上に設けられ第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられている。第1のダミーセルにおいて、ゲート間絶縁膜およびコントロールゲートは電荷蓄積層の上面および2つの側面に設けられている。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に従ったメモリの構成を示す平面図。

【図2】第1の実施形態に従ったメモリセルアレイMCAの構成図。

【図3】図1の3−3線に沿った断面図。

【図4】第1の実施形態によるメモリの製造方法を示す断面図。

【図5】図4に続く、メモリの製造方法を示す断面図。

【図6】図5に続く、メモリの製造方法を示す断面図。

【図7】図6に続く、メモリの製造方法を示す断面図。

【図8】図7に続く、メモリの製造方法を示す断面図。

【図9】図8に続く、メモリの製造方法を示す断面図。

【図10】図9に続く、メモリの製造方法を示す断面図。

【図11】図10に続く、メモリの製造方法を示す断面図。

【図12】第2の実施形態に従ったメモリの構成を示す断面図。

【図13】第2の実施形態によるメモリの製造方法を示す断面図。

【図14】図13に続く、メモリの製造方法を示す断面図。

【図15】第3の実施形態に従ったメモリの構成を示す断面図。

【図16】第3の実施形態によるメモリの製造方法を示す断面図。

【図17】図16に続く、メモリの製造方法を示す断面図。

【発明を実施するための形態】

【0013】

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

【0014】

(第1の実施形態)

図1は、第1の実施形態に従ったNANDフラッシュEEPROM(以下、単にメモリともいう)の構成を示す平面図である。メモリは、メモリセルアレイMCAと、周辺回路PRIと、第1のダミーセルDC1と、第2のダミーセルDC2とを備えている。

【0015】

メモリセルアレイMCAは、アクティブエリアAA上に形成された複数のメモリセルMCを有する。メモリセルアレイMCAの詳細な構成は、図2に示す。周辺回路は、メモリセルアレイMCAの周辺に形成され、メモリセルアレイMCAを制御するために設けられた複数の半導体素子(図示せず)を有する。

【0016】

第1および第2のダミーセルDC1、DC2は、アレイ端パターンAEPの領域に形成されている。アレイ端パターンAEPは、メモリセルアレイMCAの微細なパターンを描画するために、メモリセルアレイMCAと周辺回路PRIとの間に設けられたラインパターンである。本実施形態では、第1のダミーセルDC1が、メモリセルアレイMCA端に近いメモリセルMCのパターンを充分に露光するために、隣接するメモリセルMC間の間隔と同程度の間隔S0を空けてメモリセルアレイに隣接するように配置されている。

【0017】

アレイ端パターンAEPの領域上に示す第1の境界としての境界ZLは、ゲート絶縁膜の厚い高耐圧トランジスタとゲート絶縁膜の薄い低耐圧トランジスタとの境界を示す。境界ZLを境として周辺回路PRI側に高耐圧用のゲート絶縁膜が設けられ、メモリセルアレイMCA側に低耐圧用のゲート絶縁膜(トンネルゲート絶縁膜)が設けられている。従って、メモリセルMCのトンネルゲート絶縁膜は、低耐圧トランジスタ用の薄いゲート絶縁膜である。周辺回路PRIのトランジスタのゲート絶縁膜は、高耐圧トランジスタ用の厚いゲート絶縁膜である。

【0018】

本実施形態において、境界ZLは、第1のダミーセルDC1と第2のダミーセルDC2との間に位置する。従って、第1のダミーセルDC1は、低耐圧用のゲート絶縁膜(図3の参照番号20)を有する。第2のダミーセルDC2は、高耐圧用のゲート絶縁膜を有する(図3の参照番号30)。

【0019】

第2の境界としての境界APは、側壁転写プロセスを用いてメモリセルアレイMCAに側壁マスクを形成する際に、周辺回路PRIを被覆するフォトレジストの境界である。素子の微細化により、メモリセルアレイMCAとアレイ端パターンAEPとの間(間隔S0)に境界APを位置づけることは、リソグラフィ技術では困難である。これに対し、本実施形態では、間隔S0よりも広いアレイ端パターンAEPの領域(第1のダミーセルDC1と第2のダミーセルDC2との間)に境界APを位置づけている。従って、リソグラフィ技術で簡単にフォトレジストの境界APを位置づけることができる。アレイ端パターンAEPの領域に境界APがある場合、アレイ端パターンAEPにある芯材は変形したまま残存せず、除去される(図7参照)。このため、アレイ端パターンAEPにあるダミーセルDC1、DC2は、メモリセルMCとほぼ同じサイズに形成される。

【0020】

第3の境界としての境界EBは、素子分離STIをエッチングバックするときに周辺回路PRIを被覆するフォトレジストの境界である。メモリセルアレイMCAの領域では素子分離STIの形成時に、素子分離STIをエッチングバックしてフローティングゲートFG(電荷蓄積層)の側面を露出させ、フローティングゲートFGの側面にIPD(Inter-Poly Dielectric)膜およびコントロールゲートCGを設ける。素子分離STIのエッチングバックの際、周辺回路PRをフォトレジストで保護する。境界EBは、第1のダミーセルDC1と第2のダミーセルDC2との間に位置する。従って、第1のダミーセルDC1のフローティングゲートFGの両側側面には、IPD膜およびコントロールゲートCGが設けられる。一方、第2のダミーセルDC1のフローティングゲートFGの両側側面には、IPD膜およびコントロールゲートCGはほとんど設けられず、素子分離STIが残置される。尚、メモリセルMC、第1および第2のダミーセルDC1、DC2のより詳細な構成および製造方法は、後述する。

【0021】

図2は、第1の実施形態に従ったメモリセルアレイMCAの構成図である。メモリセルアレイは、複数のメモリブロックBLOCKを含む。図2には、或るブロックBLOCKi(iは整数)の構成を示す。ブロックBLOCKiは、データ消去の単位であり、各カラムのビット線BLに接続される複数のNANDストリングNS0〜NS5を含む。NANDストリングNS0〜NS5は、直列に接続された複数のメモリセルMCと、これらのメモリセルMCの両端に接続された選択ゲートトランジスタSGS、SGDとを有する。NANDストリングNSは、図1に示すようにストライプ状に形成されたアクティブエリアAA上に設けられている。この例では、各NANDストリングNSにおいて5つのメモリセルMCが直列に接続されているが、通常、32個または64個のメモリセルMCが直列に接続されている。NANDストリングNS0〜NS5の一端は、対応するビット線BL0〜BL5に接続され、その他端は共通ソース線SLに接続されている。

【0022】

メモリセルMCのコントロールゲートCGは、そのメモリセルMCが属するページに対応するワード線WL0〜WL4に接続されている。例えば、ページj(j=0〜4)に属するメモリセルMCのコントロールゲートは、ワード線WLjに接続されている。選択ゲートトランジスタSGD、SGSのゲートは、選択ゲート線SGL1またはSGL2に接続されている。ページは、データ読出しまたはデータ書込みの単位である。

【0023】

複数のワード線WLは、ロウ方向に延伸しており、複数のビット線BLは、ロウ方向にほぼ直交するようにカラム方向に延伸している。

【0024】

図2に示すように、メモリセルMCは、ワード線WLとビット線BLとによって構成される格子形状の交点に対応して設けられている。例えば、ワード線WL0〜WL4とビット線BL0〜BL5とによって構成される格子形状の交点は、5×6のマトリクス状に位置する。メモリセルMCは、これらの交点に対応するように5×6のマトリクス状に二次元配置されている。尚、本実施形態のブロックは、5×6(30個)のメモリセルMCを有するが、1ブロック内のメモリセルMCの個数は、これに限定されない。

【0025】

メモリセルMCは、フローティングゲートFGおよびコントロールゲートCGを有するn型FET(Field-Effect Transistor)で構成されている。ワード線WLによってコントロールゲートCGに電圧を与えることで、フローティングゲートFGに電荷(電子)を注入し、あるいは、フローティングゲートFGから電荷(電子)を放出させる。これにより、メモリセルMCにデータを書き込み、あるいは、メモリセルMCのデータを消去する。メモリセルMCは、フローティングゲートFGに蓄積された電荷の量(電子の数)に応じた閾値電圧を有する。メモリセルMCは、閾値電圧の違いとして、二値データ(1ビット)あるいは多値データ(2ビット以上)を電気的に記憶することができる。

【0026】

図3は、図1の3−3線に沿った断面図である。図3は、メモリセルアレイMCA、アレイ端パターンAEPおよび周辺回路PRIの構成を示す。

【0027】

本実施形態によるメモリは、半導体基板10を備えている。メモリセルMCは、トンネルゲート絶縁膜20と、フローティングゲートFGと、ゲート間絶縁膜IPDと、コントロールゲートCGとを含む。

【0028】

第1の絶縁膜としてのトンネルゲート絶縁膜20は、半導体基板10上に設けられている。トンネルゲート絶縁膜20は、低耐圧用のゲート絶縁膜であり、例えば、シリコン酸化膜を用いて形成されている。フローティングゲートFGは、トンネルゲート絶縁膜20上に設けられ、電荷(電子)を蓄積し、あるいは、放出することによってデータを格納することができる。フローティングゲートFGは、例えば、ポリシリコンを用いて形成されている。ゲート間絶縁膜IPDは、フローティングゲートFG上に設けられている。ゲート間絶縁膜IPDは、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸化膜よりも誘電率の高いHigh−k膜を用いて形成されている。コントロールゲートCGは、ゲート間絶縁膜IPD上に設けられており、フローティングゲートFGの電圧を制御する。コントロールゲートCGは、例えば、ポリシリコンを用いて形成されている。

【0029】

コントロールゲートCGおよびゲート間絶縁膜IPDは、互いに隣接する複数のメモリセルMC間において素子分離STI(半導体基板10)へ向かって落とし込まれており、フローティングゲートFGのロウ方向に向く2つの側面に面している。これにより、コントロールゲートCGとフローティングゲートFGとの間の対向面積が大きくなるので、コントロールゲートCGとフローティングゲートFGとチャネルとの間のカップリング容量比Crが大きくなる。これにより、コントロールゲートCGによって、フローティングゲートFGの電圧を制御しやすくなる。

【0030】

メモリセルアレイMCAと周辺回路PRIとの間のアレイ端パターンAEPには、第1および第2のダミーセルDC1、DC2が設けられている。第1および第2のダミーセルDC1、DC2の平面レイアウトにおける大きさは、メモリセルMCとほぼ同じ大きさである。

【0031】

第1のダミーセルDC1は、メモリセルMCと同様の構成を有する。即ち、第1のダミーセルDC1は、トンネルゲート絶縁膜20と、フローティングゲートFGと、ゲート間絶縁膜IPDと、コントロールゲートCGとを含む。第1のダミーセルDC1は、メモリセルアレイMCAから間隔S0だけ離れた位置に、メモリセルアレイMCAの端に隣接して設けられている。間隔S0は、メモリセルアレイMCAを微細加工することができるように設定され、メモリセルMC間の間隔と同程度かそれより大きくてもよい。

【0032】

境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間にあるので、第1のダミーセルDC1においては、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面だけでなく、ロウ方向に向く2つの側面にも設けられている。換言すると、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGのロウ方向の両側において素子分離STI(半導体基板10)に向かって落とし込まれている。これにより、コントロールゲートCGは、フローティングゲートFGの上面だけでなく、2つの側面にも面しているので、カップリング容量比Crが大きくなる。その結果、データ書込みまたはデータ消去において、コントロールゲートCG(ワード線WL)に電圧が印加された場合であっても、第1のダミーセルDC1において、ゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊され難くなる。

【0033】

第2のダミーセルDC2は、第1のダミーセルDC1と周辺回路PRIとの間に設けられており、トンネルゲート絶縁膜20よりも厚い第2の絶縁膜としてのゲート絶縁膜30を備える。これは、境界ZLが第1のダミーセルDC1と第2のダミーセルDC2との間にあるからである。さらに、第2のダミーセルDC2は、ゲート絶縁膜30上に形成されたフローティングゲートFGと、フローティングゲートFG上に設けられたゲート間絶縁膜IPDと、ゲート間絶縁膜IPD上に設けられたコントロールゲートCGとを備えている。

【0034】

第2のダミーセルDC2において、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面に設けられているものの、フローティングゲートFGの両側において素子分離STI(半導体基板10)に向かって落とし込まれていない。フローティングゲートFGのロウ方向に向かう2つの側面は、素子分離STIに面している。これは、境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間に位置するからである。しかし、第2のダミーセルDC2は、高耐圧用のゲート絶縁膜30を備えているため、第2のダミーセルDC2の耐圧は問題とならない。

【0035】

本実施形態によれば、第1のダミーセルDC1において、コントロールゲートCGおよびゲート間絶縁膜IPDは、フローティングゲートFGの上面だけでなく、ロウ方向に向く2つの側面にも設けられている。コントロールゲートCGは、フローティングゲートFGの上面だけでなく、2つの側面にも面しているので、カップリング容量比Crが大きくなる。その結果、データ書込みまたはデータ消去において、コントロールゲートCG(ワード線WL)に電圧が印加された場合であっても、第1のダミーセルDC1において、ゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊され難くなる。即ち、アレイ端パターンAEPにおける第1および第2のダミーセルDC1、DC2の耐圧を上昇させることができる。

【0036】

図4〜図11は、第1の実施形態によるメモリの製造方法を示す断面図である。まず、図4に示すように、第1の絶縁膜としてのトンネルゲート絶縁膜20および第2の絶縁膜としてのゲート絶縁膜30を半導体基板10上に形成する。第1の境界としての境界ZLを境としてメモリセルアレイMCA側にトンネルゲート絶縁膜20を形成し、周辺回路PRI側にゲート絶縁膜30を形成する。トンネルゲート絶縁膜20は、例えば、数nmであり、ゲート絶縁膜30は、トンネルゲート絶縁膜20よりも厚く、例えば、約30nmである。

【0037】

トンネルゲート絶縁膜20およびゲート絶縁膜30は、例えば、半導体基板10を熱酸化して形成されたシリコン酸化膜を用いて形成されている。尚、トンネルゲート絶縁膜20の表面およびゲート絶縁膜30の表面が同一面になるように、周辺回路PRI側の半導体基板10の表面は、予めエッチングされている。

【0038】

ここで、境界ZLは、後に形成される第1のダミーセルDC1と第2のダミーセルDC2との間に位置し、メモリセルMCと第1のダミーセルDC1との間には位置していない。即ち、境界ZLは、メモリセルMCと第1のダミーセルDC1との間隔S0よりも広いアレイ端パターンAEPに重複するように設定されている。メモリセルMCと第1のダミーセルDC1との間の間隔S0は、例えば、約50〜150nmであり、第1のダミーセルDC1と第2のダミーセルDC2との間の間隔(アレイ端パターンAEPの間隔)は、例えば、約500nmである。従って、本実施形態によれば、半導体基板10のエッチングおよびゲート絶縁膜20、30の形成のためのリソグラフィ工程において、アライメントが比較的容易である。

【0039】

次に、図5に示すように、トンネルゲート絶縁膜20およびゲート絶縁膜30上にフローティングゲートFGの材料を堆積する。フローティングゲートFGは、例えば、ポリシリコンを用いて形成されている。

【0040】

次に、第1のマスク材41の材料、第2のマスク材42の材料および芯材50の材料をフローティングゲートFGの材料上に堆積する。第1のマスク材41は、例えばシリコン酸化膜等の絶縁膜を用いて形成される。第2のマスク材41は、例えば第1のマスク材および芯材50とは異なる絶縁膜、例えばアモスファスシリコン膜やシリコン窒化膜を用いて形成される。芯材50は、例えば、シリコン酸化膜等の絶縁膜を用いて形成されている。次に、リソグラフィ技術およびRIE(Reactive Ion Etching)法を用いて、芯材50の材料を加工する。このとき、図6に示すように、アレイ端パターンAEPの芯材50は境界ZLに重複する。続いて、側壁マスク60の材料を芯材50の上面および側面、並びに、第2のマスク材42の材料上に堆積する。側壁マスク60の材料は、芯材50とは異なる絶縁膜、例えば、シリコン窒化膜またはアモルファスシリコンを用いて形成されている。側壁マスク60の材料は、側壁マスク60の材料を芯材50の上面および側面を被覆するように形成される。次に、RIE法を用いて側壁マスク60の材料を異方的にエッチングする。これにより、図6に示すように、側壁マスク60が芯材50の側面に残置される。

【0041】

次に、リソグラフィ技術を用いて、第2の境界としての境界APを境として、周辺回路PRI側の領域をフォトレジストPRで被覆する。境界APは、境界ZLと同様に、第1のダミーセルDC1と第2のダミーセルDC2との間に位置し、アレイ端パターンAEPに重複するように設定されている。

【0042】

次に、フォトレジストPRをマスクとして用いて、側壁マスク60を残置させたまま、露出された芯材50を選択的にエッチングする。このとき、ウェットエッチング、CDE(Chemical Dry Etching)等の等方性エッチングを用いて、芯材50を除去する。境界APは、アレイ端パターンAEPに重複しており、アレイ端パターンAEPにおける芯材50の上面の一部は露出されている。従って、アレイ端パターンAEPの芯材50も同時に除去される。フォトレジストPRで被覆された周辺回路PRI側の芯材50は残置される。これにより、図7に示す構造が得られる。

【0043】

境界AP(アレイ端パターンAEP)より周辺回路PRI側においては、芯材50が残置されているので、周辺回路PRIでは、芯材50および側壁マスク60が素子の電極パターン(ゲート電極またはキャパシタ電極等)に形成される。一方、境界APよりメモリセルアレイMCA側では、芯材50は除去されるので、側壁マスク60がフローティングゲートFGのパターンに形成される。また、アレイ端パターンAEPのうち境界APより周辺回路PRI側でも、芯材50は除去されるので、側壁マスク60がフローティングゲートFGのパターンに形成される。

【0044】

次に、フォトレジストPRの除去後、側壁マスク60または芯材50をマスクとして用いて、第2のマスク材42をRIE法で加工する。第2のマスク材42をマスクとして用いて、第1のマスク材41をRIE法で加工する。第1のマスク材41をマスクとして、フローティングゲートFGの材料、トンネルゲート絶縁膜20、ゲート絶縁膜30および半導体基板10をRIE法で加工する。これにより、図8に示すように、フローティングゲートFGを形成するとともに、素子分離STIに用いられるトレンチ70を形成する。

【0045】

尚、境界ZLを境として、膜厚の異なるトンネルゲート絶縁膜20およびゲート絶縁膜30が隣接している。絶縁膜20、30(例えば、シリコン酸化膜)をエッチングする際、絶縁膜20、30のエッチング選択比は、半導体基板10(例えば、シリコン単結晶)に比べて高い。絶縁膜20、30のエッチングを終了し半導体基板10のエッチングを開始する時点では、ZL境界部における半導体基板10の段差は残った状態となっている。半導体基板10のエッチング速度はメモリセルMCA、アレイ端パターンAEPおよび周辺回路PRIのいずれにおいても変わらない。このため、アレイ端パターンAEPにおけるトレンチ70の底部には、境界ZLを境として段差STが形成される。

【0046】

次に、トレンチ70内に素子分離絶縁膜80を充填する。続いて、フローティングゲートFGの上面が露出されるまで、素子分離絶縁膜80を平坦化処理する。これにより、図9に示す構造が得られる。

【0047】

次に、図10に示すように、リソグラフィ技術を用いて、第3の境界としての境界EBを境として周辺回路PRI側の領域をフォトレジストPR2で被覆し、メモリセルアレイMCA側の領域を露出させる。次に、図10に示すように、メモリセルアレイMCAにある素子分離絶縁膜80をエッチングバックすることによって、フローティングゲートFGの側面の上部を露出させる。境界EBは、第1のダミーセルDC1と周辺回路PRIとの間にあり、本実施形態では、境界EBは、アレイ端パターンAEPに重複している。従って、第1のダミーセルDC1のフローティングゲートFGの側面も露出される。

【0048】

一方、本実施形態では、第2のダミーセルDC2は、フォトレジストPR2で被覆されているため、第2のダミーセルDC2の側面は、素子分離絶縁膜80で被覆されたままである。

【0049】

フォトレジストPR2の除去後、図11に示す構ように、ゲート間絶縁膜IPDをメモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの上面および側面に堆積する。即ち、ゲート間絶縁膜IPDは、隣接するメモリセルMC間にある素子分離STI(半導体基板10)に向かって落とし込まれている。また、ゲート間絶縁膜IPDは、第1のダミーセルDC1の上面および側面も被覆するように形成され、第1のダミーセルDC1の両側においても素子分離STI(半導体基板10)に向かって落とし込まれている。さらに、第2のダミーセルDC2の側面は素子分離絶縁膜80で被覆されたままであるので、ゲート間絶縁膜IPDは、第2のダミーセルDC2の上面上に堆積されるが、その側面には堆積されない。

【0050】

ゲート間絶縁膜IPDの膜厚は、ゲート間絶縁膜IPDが互いに隣接するメモリセルMC間を埋め込まないように、メモリセルMC間の間隔の2分の1未満とする。

【0051】

次に、周辺回路PRIにおいて、フローティングゲートFGとコントロールゲートCGとを電気的に接続させるために、ゲート間絶縁膜IPDの一部を除去する。また、必要に応じてメモリセルアレイMCAにおいても、図示しない選択ゲートトランジスタ部分のゲート間絶縁膜IPDの一部を除去する。

【0052】

次に、コントロールゲートCGの材料をゲート間絶縁膜IPD上に堆積する。コントロールゲートCGは、例えば、ポリシリコンや金属シリサイドを用いて形成される。コントロールゲートCGは、メモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの上面および側面にゲート間絶縁膜IPDを介して形成される。換言すると、コントロールゲートCGは、ゲート間絶縁膜IPDと同様に、メモリセルMCおよび第1のダミーセルDC1のそれぞれのフローティングゲートFGの両側において素子分離STI(半導体基板10)に向かって落とし込まれている。コントロールゲートCGを加工した後、層間絶縁膜、ビット線BL等を形成することによって、図3に示すメモリが完成する。

【0053】

本実施形態によれば、境界ZLがアレイ端パターンAEPの第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。通常、第1のダミーセルDC1と第2のダミーセルDC2との間の間隔は、メモリセルアレイMCAと第1のダミーセルDC1との間の間隔S0に比べて大きい。従って、本実施形態では、高耐圧用のゲート絶縁膜30と低耐圧用のトンネルゲート絶縁膜20とを形成する際の、リソグラフィ工程のアライメントが容易である。境界APおよびEBについても、境界ZLと同様のことが言える。

【0054】

本実施形態によれば、境界ZLがアレイ端パターンAEPの第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。これにより、第2のダミーセルDC2は、トンネルゲート絶縁膜20よりも厚いゲート絶縁膜30を備える。従って、第2のダミーセルDC2は、メモリセルMCよりも耐圧の高い高耐圧トランジスタとなる。

【0055】

一方、第1のダミーセルDC1は、トンネルゲート絶縁膜20を備える。しかし、境界APおよび境界EBが第1のダミーセルDC1と第2のダミーセルDC2との間に設定されている。従って、アレイ端パターンAEPにある芯材50を除去し、第1のダミーセルDC1と第2のダミーセルDC2との間に素子分離STIを形成することができ、かつ、第1のダミーセルDC1のフローティングゲートFGの両側にある素子分離絶縁膜80をエッチングバックすることができる。これにより、コントロールゲートCGは、第1のダミーセルDC1のフローティングゲートFGの両側面にゲート間絶縁膜IPDを介して面する。その結果、カップリング容量比Crが大きくなり、データ書込みまたはデータ消去において、第1のダミーセルDC1のゲート間絶縁膜IPDまたはトンネルゲート絶縁膜20が破壊されることを抑制することができる。即ち、アレイ端パターンAEPにおける第1および第2のダミーセルDC1、DC2の耐圧を上昇させることができる。

【0056】

(第2の実施形態)

図12は、第2の実施形態に従ったメモリの構成を示す断面図である。第2の実施形態では、境界EBが第2のダミーセルDC2に重複するように設定されている点で第1の実施形態と異なる。これにより、第2のダミーセルDC2のフローティングゲートFGの片側側面F1にはゲート間絶縁膜IPDおよびコントロールゲートCGが設けられており、他方の側面F2には素子分離絶縁膜80が設けられている。これにより、第2のダミーセルDC2の耐圧が第1の実施形態と比べさらに高くなる。第2の実施形態のその他の構成は、対応する第1の実施形態の構成と同様でよい。従って、第2の実施形態は、第1の実施形態と同様の効果を有する。

【0057】

第2の実施形態の製造方法は、図4から図9に示す工程を得た後、図13および図14に示す工程を含む。

【0058】

第2の実施形態では、境界EBが第2のダミーセルDC2に重複するので、素子分離絶縁膜80をエッチングバックする際に、図13に示すように、第2のダミーセルDC2のフローティングゲートFGの片側の側面F1が露出される。

【0059】

これに伴い、図14に示すように、ゲート間絶縁膜IPDは、第2のダミーセルDC2のフローティングゲートFGの上面および片側の側面F1にも形成される。第2のダミーセルDC2のフローティングゲートFGの他方の側面F2は、素子分離STIで被覆されたままである。コントロールゲートCGは、第2のダミーセルDC2のフローティングゲートFGの上面および片側の側面F1にゲート間絶縁膜IPDを介して形成される。その後、第1の実施形態と同様に層間絶縁膜およびビット線等を形成することによって、第2の実施形態によるメモリが完成する。

【0060】

(第3の実施形態)

図15は、第3の実施形態に従ったメモリの構成を示す断面図である。第3の実施形態では、境界EBが第2のダミーセルDC2と周辺回路PRIとの間にある素子分離STIにおいて重複するように設定されている点で第1の実施形態と異なる。これにより、第2のダミーセルDC2のフローティングゲートFGの両側側面F1、F2にはゲート間絶縁膜IPDおよびコントロールゲートCGが設けられている。これにより、第2のダミーセルDC2の耐圧が第2の実施形態と比べさらに高くなる。第3の実施形態のその他の構成は、対応する第1の実施形態の構成と同様でよい。従って、第3の実施形態は、第1の実施形態と同様の効果を有する。

【0061】

第3の実施形態の製造方法は、図4から図9に示す工程を得た後、図16および図17に示す工程を含む。

【0062】

第3の実施形態では、境界EBが第2のダミーセルDC2と周辺回路PRIとの間の素子分離STIに重複するので、素子分離絶縁膜80をエッチングバックする際に、図16に示すように、第2のダミーセルDC2のフローティングゲートFGの両側側面F1、F2が露出される。

【0063】

これに伴い、図17に示すように、ゲート間絶縁膜IPDは、第2のダミーセルDC2のフローティングゲートFGの上面および両側側面F1、F2にも形成される。コントロールゲートCGは、第2のダミーセルDC2のフローティングゲートFGの上面および両側側面F1、F2にゲート間絶縁膜IPDを介して形成される。その後、第1の実施形態と同様に層間絶縁膜およびビット線等を形成することによって、第3の実施形態によるメモリが完成する。

【0064】

尚、第1から第3の実施形態により、境界EBは、第1のダミーセルDC1と周辺回路PRIとの間の任意の位置、言い換えると境界ZLを基準としてメモリセルアレイMCA側のもっとも近くに設けられた側壁60と周辺回路PRIとの間に設定されればよいことになる。

【0065】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0066】

MCA・・・メモリセルアレイ、PRI・・・周辺回路、MC・・・メモリセル、DC1・・・第1のダミーセル、DC2・・・第2のダミーセル、AEP・・・アレイ端パターン、STI・・・素子分離、AA・・・アクティブエリア、FG・・・フローティングゲート、CG・・・コントロールゲート、IPD・・・IPD膜、10・・・半導体基板、20・・・トンネルゲート絶縁膜、30・・・ゲート絶縁膜

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられ電荷を蓄積可能な電荷蓄積層と、前記電荷蓄積層上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられ前記電荷蓄積層の電圧を制御するコントロールゲートとを含む複数のメモリセルを有するメモリセルアレイと、

前記メモリセルアレイの周辺に設けられた周辺回路と、

前記第1の絶縁膜と、前記電荷蓄積層と、前記ゲート間絶縁膜と、前記コントロールゲートとを含み、前記メモリセルアレイの端に設けられた第1のダミーセルと、

前記半導体基板上に設けられ前記第1の絶縁膜よりも厚い第2の絶縁膜を含み、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備え、

前記第1のダミーセルにおいて、前記ゲート間絶縁膜および前記コントロールゲートは前記電荷蓄積層の上面および2つの側面に設けられ、

前記第1のダミーセルの前記ゲート間絶縁膜および前記コントロールゲートは、前記電荷蓄積層の両側において前記半導体基板に向かって落とし込まれており、

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に素子分離絶縁膜が設けられていることを特徴とする半導体記憶装置。

【請求項2】

半導体基板と、

前記半導体基板上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられ電荷を蓄積可能な電荷蓄積層と、前記電荷蓄積層上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられ前記電荷蓄積層の電圧を制御するコントロールゲートとを含む複数のメモリセルを有するメモリセルアレイと、

前記メモリセルアレイの周辺に設けられた周辺回路と、

前記第1の絶縁膜と、前記電荷蓄積層と、前記ゲート間絶縁膜と、前記コントロールゲートとを含み、前記メモリセルアレイの端に設けられた第1のダミーセルと、

前記半導体基板上に設けられ前記第1の絶縁膜よりも厚い第2の絶縁膜を含み、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備え、

前記第1のダミーセルにおいて、前記ゲート間絶縁膜および前記コントロールゲートは前記電荷蓄積層の上面および2つの側面に設けられていることを特徴とする半導体記憶装置。

【請求項3】

前記第1のダミーセルの前記ゲート間絶縁膜および前記コントロールゲートは、前記電荷蓄積層の両側において前記半導体基板に向かって落とし込まれていることを特徴とする請求項2に記載の半導体記憶装置。

【請求項4】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に素子分離絶縁膜が設けられていることを特徴とする請求項2に記載の半導体記憶装置。

【請求項5】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の片側側面に前記ゲート間絶縁膜および前記コントロールゲートが設けられ、

前記第2のダミーセルの前記電荷蓄積層の他方の側面に素子分離絶縁膜が設けられていることを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項6】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に前記ゲート間絶縁膜および前記コントロールゲートが設けられていることを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項7】

前記第1および前記第2のダミーセルは、前記メモリセルとほぼ同じ大きさを有することを特徴とする請求項1から請求項5のいずれかに記載の半導体記憶装置。

【請求項8】

複数のメモリセルを含むメモリセルアレイと、前記メモリセルアレイの周辺に設けられた周辺回路と、前記メモリセルアレイの端に設けられた第1のダミーセルと、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備えた半導体記憶装置の製造方法であって、

前記第1のダミーセルと前記第2のダミーセルとの間の第1の境界を境として前記メモリセルアレイ側の半導体基板上に第1の絶縁膜を形成し、前記第1の境界を境として前記周辺回路側の前記半導体基板上に前記第1の絶縁膜よりも厚い第2の絶縁膜を形成し、

前記第1および前記第2の絶縁膜上に電荷蓄積層の材料を形成し、

前記電荷蓄積層の材料上にマスク材と芯材とを形成し、

前記芯材の側面に側壁マスクを形成し、

前記第1のダミーセルと前記第2のダミーセルとの間の第2の境界を境として、前記周辺回路側の前記芯材を残置させつつ、前記メモリセルアレイ側の前記芯材を除去し、

前記芯材および前記側壁マスクをマスクとして用いて、前記電荷蓄積層を加工するとともに、素子分離用のトレンチを形成し、

前記素子分離用のトレンチ内に素子分離絶縁膜を充填し、

前記第1のダミーセルと前記周辺回路との間の第3の境界を境として、前記メモリセルアレイ側にある前記素子分離絶縁膜をエッチングして、前記メモリセルおよび少なくとも前記第1のダミーセルのそれぞれの前記電荷蓄積層の側面の少なくとも一部を露出させ、

前記メモリセルおよび前記第1のダミーセルのそれぞれの前記電荷蓄積層の上面および側面にゲート間絶縁膜を形成し、

前記メモリセルおよび前記第1のダミーセルのそれぞれの前記電荷蓄積層の上面および側面に前記ゲート間絶縁膜を介してコントロールゲートを形成することを具備した半導体記憶装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられ電荷を蓄積可能な電荷蓄積層と、前記電荷蓄積層上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられ前記電荷蓄積層の電圧を制御するコントロールゲートとを含む複数のメモリセルを有するメモリセルアレイと、

前記メモリセルアレイの周辺に設けられた周辺回路と、

前記第1の絶縁膜と、前記電荷蓄積層と、前記ゲート間絶縁膜と、前記コントロールゲートとを含み、前記メモリセルアレイの端に設けられた第1のダミーセルと、

前記半導体基板上に設けられ前記第1の絶縁膜よりも厚い第2の絶縁膜を含み、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備え、

前記第1のダミーセルにおいて、前記ゲート間絶縁膜および前記コントロールゲートは前記電荷蓄積層の上面および2つの側面に設けられ、

前記第1のダミーセルの前記ゲート間絶縁膜および前記コントロールゲートは、前記電荷蓄積層の両側において前記半導体基板に向かって落とし込まれており、

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に素子分離絶縁膜が設けられていることを特徴とする半導体記憶装置。

【請求項2】

半導体基板と、

前記半導体基板上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられ電荷を蓄積可能な電荷蓄積層と、前記電荷蓄積層上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられ前記電荷蓄積層の電圧を制御するコントロールゲートとを含む複数のメモリセルを有するメモリセルアレイと、

前記メモリセルアレイの周辺に設けられた周辺回路と、

前記第1の絶縁膜と、前記電荷蓄積層と、前記ゲート間絶縁膜と、前記コントロールゲートとを含み、前記メモリセルアレイの端に設けられた第1のダミーセルと、

前記半導体基板上に設けられ前記第1の絶縁膜よりも厚い第2の絶縁膜を含み、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備え、

前記第1のダミーセルにおいて、前記ゲート間絶縁膜および前記コントロールゲートは前記電荷蓄積層の上面および2つの側面に設けられていることを特徴とする半導体記憶装置。

【請求項3】

前記第1のダミーセルの前記ゲート間絶縁膜および前記コントロールゲートは、前記電荷蓄積層の両側において前記半導体基板に向かって落とし込まれていることを特徴とする請求項2に記載の半導体記憶装置。

【請求項4】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に素子分離絶縁膜が設けられていることを特徴とする請求項2に記載の半導体記憶装置。

【請求項5】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の片側側面に前記ゲート間絶縁膜および前記コントロールゲートが設けられ、

前記第2のダミーセルの前記電荷蓄積層の他方の側面に素子分離絶縁膜が設けられていることを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項6】

前記第2のダミーセルにおいて、前記電荷蓄積層は前記第2の絶縁膜上に設けられ、前記ゲート間絶縁膜は前記電荷蓄積層上に設けられ、前記コントロールゲートは前記ゲート間絶縁膜上に設けられ、

前記第2のダミーセルの前記電荷蓄積層の両側側面に前記ゲート間絶縁膜および前記コントロールゲートが設けられていることを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項7】

前記第1および前記第2のダミーセルは、前記メモリセルとほぼ同じ大きさを有することを特徴とする請求項1から請求項5のいずれかに記載の半導体記憶装置。

【請求項8】

複数のメモリセルを含むメモリセルアレイと、前記メモリセルアレイの周辺に設けられた周辺回路と、前記メモリセルアレイの端に設けられた第1のダミーセルと、前記第1のダミーセルと前記周辺回路との間に設けられた第2のダミーセルとを備えた半導体記憶装置の製造方法であって、

前記第1のダミーセルと前記第2のダミーセルとの間の第1の境界を境として前記メモリセルアレイ側の半導体基板上に第1の絶縁膜を形成し、前記第1の境界を境として前記周辺回路側の前記半導体基板上に前記第1の絶縁膜よりも厚い第2の絶縁膜を形成し、

前記第1および前記第2の絶縁膜上に電荷蓄積層の材料を形成し、

前記電荷蓄積層の材料上にマスク材と芯材とを形成し、

前記芯材の側面に側壁マスクを形成し、

前記第1のダミーセルと前記第2のダミーセルとの間の第2の境界を境として、前記周辺回路側の前記芯材を残置させつつ、前記メモリセルアレイ側の前記芯材を除去し、

前記芯材および前記側壁マスクをマスクとして用いて、前記電荷蓄積層を加工するとともに、素子分離用のトレンチを形成し、

前記素子分離用のトレンチ内に素子分離絶縁膜を充填し、

前記第1のダミーセルと前記周辺回路との間の第3の境界を境として、前記メモリセルアレイ側にある前記素子分離絶縁膜をエッチングして、前記メモリセルおよび少なくとも前記第1のダミーセルのそれぞれの前記電荷蓄積層の側面の少なくとも一部を露出させ、

前記メモリセルおよび前記第1のダミーセルのそれぞれの前記電荷蓄積層の上面および側面にゲート間絶縁膜を形成し、

前記メモリセルおよび前記第1のダミーセルのそれぞれの前記電荷蓄積層の上面および側面に前記ゲート間絶縁膜を介してコントロールゲートを形成することを具備した半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−62415(P2013−62415A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−200531(P2011−200531)

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]