半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置およびその製造方法に関する。

【背景技術】

【0002】

半導体記憶装置は、ビット当たりの面積を縮小することを通じて製造コストの減少および大容量化が主に図られている。半導体記憶装置として、可変抵抗膜を用いた半導体記憶装置が知られている。可変抵抗膜は、抵抗値の相違する2つ以上の定常状態を有する。この複数の状態を保持データと関連付けることによってデータが不揮発に記憶される。このような記憶装置として、MRAM(magnetoresistive random access memory)およびReRAM(resistive random access memory)がある。MRAMおよびReRAMを含め、記憶装置のビット当たりの面積の縮小による発展が困難になってきている。その理由は、面積の縮小には物理的限界が存在すること、微細加工のための装置が高額であること等が挙げられる。このことは、ビット当たりの単価の低減が困難なことを意味する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−10688号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ビット当たりの単価を低減できる半導体記憶装置およびその製造方法を提供しようとするものである。

【課題を解決するための手段】

【0005】

一実施形態による半導体記憶装置は、第1方向に沿う第1部分と第2方向に沿いかつ第1部分と接続された第2部分とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線を含む。可変抵抗膜は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

【図面の簡単な説明】

【0006】

【図1】第1実施形態に係る半導体記憶装置の全体的な構造を示す図。

【図2】第1実施形態に係る半導体記憶装置の一部の斜視図。

【図3】第1実施形態に係る半導体記憶装置の平面図。

【図4】第1実施形態に係る半導体記憶装置の等価回路図。

【図5】第1実施形態に係る半導体記憶装置の製造方法の一ステップを示す斜視図。

【図6】図5に続くステップを示す斜視図。

【図7】図6に続くステップを示す斜視図。

【図8】図7に続くステップを示す斜視図。

【図9】図8に続くステップを示す斜視図。

【図10】第2実施形態に係る半導体記憶装置の一部の斜視図。

【図11】第2実施形態に係る半導体記憶装置の一部の斜視図。

【図12】第2実施形態に係る半導体記憶装置の平面図。

【図13】第2実施形態に係る半導体記憶装置の等価回路図。

【図14】第3実施形態に係る半導体記憶装置の一部の斜視図。

【図15】第3実施形態に係る半導体記憶装置の一部の斜視図。

【図16】第3実施形態に係る半導体記憶装置の平面図。

【図17】第2実施形態に係る半導体記憶装置の等価回路図。

【図18】第3実施形態の変形例に係る半導体記憶装置の一部の斜視図。

【発明を実施するための形態】

【0007】

以下に実施形態について図面を参照して説明する。なお、以下の説明において、略同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断されるべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0008】

また、以下に示す各実施形態は、この実施形態の技術的思想を具体化するための装置や方法を例示するものであって、実施形態の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。実施形態の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0009】

(第1実施形態)

図1は、第1実施形態に係る半導体記憶装置の全体的な構造を概略的に示している。図1に示されるように、半導体基板1の表面の上方に、メモリブロック2が設けられている。メモリブロック2は、z軸に沿って間隔をもって重ねられた複数の層3a〜3nを含んでいる。層3a〜3nは、同じ構成を有し、このため、層3a〜3nを個別に特定する必要がない場合、1つの層を代表して、または包括的に層3と称する。層3は、xy平面に沿って行列状に配置された複数のメモリセル4を含んでいる。各メモリセル4は、少なくとも抵抗変化型素子およびトランジスタを含んでいる。

【0010】

メモリブロック2は、複数の第1配線11を含んでいる。各第1配線11は、各層3中に位置し、xy平面に沿って後述の特定の形状を有し、特定の複数のメモリセル4の各々の一端に接続されている。メモリブロック2は、複数の第2配線12を含んでいる。各第2配線12は、複数の層3をz軸に沿って貫き、特定の複数のメモリセル4の各々の他端に接続されている。メモリブロック2はまた、制御線13を有する。制御線13は、トランジスタを制御するためのものであり、複数の層3をz軸に沿って貫き、複数のトランジスタのゲートとして機能する。

【0011】

第1配線11、第2配線12、制御線13は、基板1上の周辺回路14と電気的に接続されている。第1配線11は、メモリブロック2の端から導電性のプラグおよび配線を介して周辺回路14に接続されている。第2配線および制御線13は、メモリブロック2の内部を通過し、基板1の上方の導電性の配線およびプラグ配線を介して周辺回路14と接続されている。

【0012】

例えば、周辺回路14は、例えばデコーダ、センスアンプ、コントローラ、電流ドライバ、電流シンク等を含んでいる。周辺回路14は、コントローラを介してデコーダを制御して特定のメモリセルにデータを書き込んだり、特定のメモリセルからデータを読み出したりするように第1配線11、第2配線12、制御線13を制御する。アクセス対象のメモリセルは、半導体記憶装置の外部からのアドレス信号によって特定され、コントローラおよびデコーダによって使用される。センスアンプは、読み出されたデータを増幅し、半導体記憶装置の外部に出力する。

【0013】

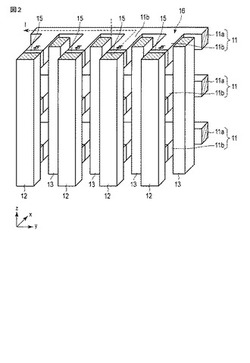

図2は、第1実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図2は、図1の構造のうちの3つの層のみを示している。図2に示されるように、複数の第1配線11を含んでいる。各第1配線11は、図1の1つの層3内に形成される。第1配線11は、導電性の材料からなり、例えば不純物を含んだシリコンからなる。第1配線11同士は、z軸に沿って相互に距離を有する。各第1配線11は同じ平面形状(xy平面に沿う形状)を有する。第1配線11は、第1部分11aと複数の第2部分11bとを有する。第1配線11の第1部分11aは、y軸に沿って延びる。第1配線の第2部分11bは、x軸に沿って延び、y軸に沿って相互に距離を有する。各第2部分11bは、一端において第1部分11aと接続さている。以上のような第1部分11aおよび第2部分11bによって、第1配線11は櫛状の平面形状を有する。

【0014】

第1配線の第2部分11bの各々の他端は、可変抵抗膜15の一端と接続されている。可変抵抗膜15は、yz平面に沿って広がり、x軸に沿って対向する2つの面の一方(第1面)が、上記のように第2部分11bの端と接続されている。可変抵抗膜15のx軸に沿って対向する2つの面の他方(第2面)は、第2配線12と接続されている。第2配線12は、z軸に沿って複数の層3を貫いて延び、z軸に沿って並ぶ複数の可変抵抗膜15の第2面に共通に接続されている。第2配線12は、導電材料からなる。

【0015】

制御線13は、導電材料からなり、z軸に沿って複数の層3を貫いて延びる。制御線13は、xy面に沿って広がりを有し、z軸に沿って並ぶ複数の第2部分11bにy軸に沿って並ぶ。制御線13は、第1配線11の第1部分11aとも第2部分11bとも距離を有しており、これらの間には絶縁材料(図示せず)が位置している。制御線13は、例えば第1配線11の第2部分11bのx軸に沿った中間近傍に位置する。第1配線11の第2部分11bのうちの制御線13に並ぶ部分は、非導電性の半導体材料、例えばシリコンからなる。この非導電性部分、第1配線11の第2部分11bのうちの非導電性部分を挟む2つの導電体部分、および制御線13はトランジスタ16を構成する。非導電性部分はチャネルとして機能し、所望の閾値に応じた適切な量および種類の不純物を含んでいる。第1配線11の第2部分11bのうちの非導電性部分を挟む2つの導電性部分はソース/ドレイン領域として機能する。制御線13は、トランジスタ16のゲート電極として機能する。制御線13と、第1配線11の第2部分11bとの間の絶縁材料はゲート絶縁膜として機能する。トランジスタ16は、制御線13を適切な電位にすることによってオンする。可変抵抗膜15とトランジスタ16は、メモリセル4を構成する。可変抵抗膜15と第1配線11の第2部分11bとによって、これらの境界においてダイオード17が実現されている。ダイオード17は、可変抵抗膜側においてアノードを有し、第1配線11の第2部分側においてカソードを有する。

【0016】

図2に示される各要素同士の間の領域、具体的には、例えば第1配線11同士の間の領域は絶縁膜により埋め込まれている。

【0017】

可変抵抗膜15として、抵抗値の相違する2つ以上の定常状態を有し、2つの端子を通過する電流または2つの端子に印加される電圧に応じて1つの定常状態を取るあらゆる素子を用いることができる。より具体的には、ReRAMまたはMRAMのメモリセルにおいて使用されるものを用いることができる。ReRAMにおいて用いられるタイプの可変抵抗膜は、素子への印加電圧/電流によって内部の物理状態が変化する物質、より具体的には強相関系材料を含んでいる。また、MRAMにおいて用いられるタイプの可変抵抗膜は、少なくとも、積層された、強磁性材料からなる固定層、非磁性材料からなる中間層、強磁性材料からなる自由層(記録層)を含む。このタイプの素子は、スピン偏極した電子の流れを、2つの端子を通過する電流の向きに応じて低抵抗状態または高抵抗状態を取るように構成される。

【0018】

可変抵抗膜15の種類に応じて、メモリセル4にデータを記憶させるためのメモリセル4への電流または電圧の印加の仕方は相違する。また、本実施形態に適用された可変抵抗膜の種類に応じて、周辺回路14の構成も相違する。電流または電圧の大きさや方向、さらに非選択のメモリセルへの電流または電圧の印加を含め、選択されたメモリセル4にデータを記憶させるためのあらゆる詳細事項は、実施形態に依存せず、従って実施形態を限定しない。このような詳細事項は、当業者にとって知られている。概略的には、選択メモリセル4の可変抵抗膜15には、これと接続された第1配線11および第2配線12によって適切な電流または電圧が印加され、これを通じて、選択メモリセル4にデータが記憶される。また、選択メモリセル4に適切な電流または電圧を印加することを通じて選択メモリセル4のデータが読み出される。

【0019】

図2の構造は、x軸に沿って繰り返し設けられている。図3は、第1実施形態に係る半導体記憶装置の平面図を概略的に示している。また、図3は、1層のみを示している。図3に示されるように、x軸に沿って第1配線11、複数の第2配線12、制御線13、複数の可変抵抗膜15から各々がなる2つの単位構造が並んでいる。図3では、図の簡略化のために、2つの単位構造のみを例示している。単位構造同士は独立している。図3に示されるように、2つの単位構造は、y軸に関して線対称の関係を有する。ある第1配線11の各第2部分11bのy軸上の座標は、別の第1配線11の各第2部分11bのy軸上の座標と一致している。すなわち、相違する第1配線11の相互に対応する各第2部分11bは、同じx軸上の仮想線上にある。しかしながら、このことは必須ではない。例えば、複数の単位構造同士が、y軸上の位置に関して相違していてもよい。さらに、複数の単位構造が、同じ向きを有していてもよい。

【0020】

図4は、第1実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図4はまた、図2の構造を模式的に表現している。以下に、最上層の左から3番目のメモリセル4が選択されている場合のデータ書き込みについて、図4および図2を参照して説明する。以下の説明は、ReRAMに適用された実施形態の例に関する。以下の説明における第1、第2配線11、12、および制御線13の電位は、周辺回路14によって制御される。周辺回路14は、外部からのアドレス信号により特定されるメモリセル4にアクセスするための動作を行なう。図2および図4に示されるように、選択されたメモリセル(選択セル)4と接続された第2配線(選択第2配線)12は、例えば0Vにされる。また、選択セル4と接続された第1配線(選択第1配線)11、すなわち本例では最上層の第1配線11は、選択第2配線12より低い電位、例えば−3Vにされる。一方、選択第1配線11以外の第1配線11はみな、選択第2配線12より高い電位、例えば+2Vにされる。また、選択第2配線12以外の第2配線12の電位は任意である。第1配線11および第2配線12の電位の設定の順序は本例に限られない。

【0021】

第1配線11および第2配線12の電位の設定後、選択セル4と接続された制御線13が活性化される。この活性化により、この制御線13と接続された、選択セル4および選択セル4にz軸に沿って並ぶ非選択のメモリセル4の各々のトランジスタ16がオンする。別の制御線13と接続されたメモリセル4の各トランジスタ16はオフを維持する。このようなトランジスタ16のオンまたはオフの結果、選択セル4のみを図2および図4のように電流が流れる。すなわち、第2配線12から選択セル4の可変抵抗膜15およびトランジスタ16を介して第1配線11へと電流Iが流れる。電流Iは、選択セル4のダイオード17を順方向に流れる。一方、ダイオード17による遮断により、非選択の第1配線11から選択第2配線12へは電流は流れない。すなわち、活性化された制御線13および非選択第1配線11の両方に接続された非選択セル4を介した電流は流れない。

【0022】

ReRAMでは、データの書き込みは、可変抵抗膜15を低抵抗状態から高抵抗状態に変化させる操作と、高抗状態から低抵抗状態に変化させる操作を含む。これらの操作の違いは、可変抵抗膜15に印加される電流または電圧の大きさである。上記の電位の値は例示であり、可変抵抗膜15のいずれの抵抗状態への移行を目指すかに応じて、適切な任意の電位が用いられ得る。

【0023】

次に、図5〜図9は、第1実施形態に係る半導体記憶装置の製造方法のステップを順次示している。図5では、図3のように2つの隣接する単位構造が描かれている。まず、図5に示されるように、半導体基板1(図示せず)の上方に、複数の半導体膜21および複数の絶縁膜22が交互に形成される。半導体膜21は第1配線11へとパターニングされる膜である。半導体膜21のうちの第1配線11へとパターニングされる部分には、不純物が導入され、導電性にされる。一方、半導体膜21のうちのトランジスタ16のチャネルとして機能する部分には、閾値制御のための不純物が導入される。

【0024】

次に、半導体膜21および絶縁膜22の積層構造上に、マスク(図示せず)が形成される。マスクは、y軸に沿って延びる開口を有する。開口は、図3等の各単位構造相互間の領域に対応する。次に、例えば、マスクを介した異方性エッチングによって、積層構造が分断される。分断された各部分は、図3等の1つの単位構造に対応する。次に、各分断された単位構造の側面全体に膜23が形成される。膜23は、可変抵抗膜15へとパターニングされる膜であり、可変抵抗膜15のx軸に沿った長さに対応する厚さを有する。膜23は、図5では、対向する2つの分断された単位構造の対向する各側面上に形成される。次に、膜23上の全面に膜24が形成される。膜24は、第2配線12へとパターニングされる膜であり、第2配線12のx軸に沿った長さに対応する厚さを有する。

【0025】

次に、半導体膜21、絶縁膜22、膜23、および膜24からなる構造上に、マスク(図示せず)が形成される。マスクは、第1配線11、可変抵抗膜15、第2配線12が形成される領域を覆い、その他の領域において開口を有する。すなわち、パターニングされたマスクは、図3のような、第1配線11、可変抵抗膜15、第2配線12のxy平面に沿った形状に対応する。

【0026】

次に、図6に示されるように、例えば、マスクを介した異方性エッチングによって、絶縁膜22、膜23、および膜24がパターニングされる。パターニングされた構造は、xy平面に沿って櫛型の形状のz軸に沿った立体構造を有する。パターニングの結果、第1配線11および第2配線12が形成され、膜23は、y軸に沿って複数の部分へと分断される。なお、図6およびこれ以降の図7〜図9は、簡略化のため、図5の2つの単位構造の原形のうちの奥側のもののみを示している。

【0027】

次に、図7に示されるように、各絶縁膜22の膜23に接する先端がx軸に沿って後退させられる。この後退させる処理は、膜23を第2配線12と反対の面において露出させるためのものである。後退処理には、例えば、ウェットエッチングが用いられる。後退処理の結果、膜23と絶縁膜22との間でかつ第1配線11同士の間に間隔(空間)31が形成される。次に、例えば等方性エッチングにより、間隔31から膜23がエッチングされる。このエッチングの際、間隔31の上下の第1配線11がマスクとして機能する。エッチングの結果、膜23のうちの間隔31に対して露出していた部分が除去されて、膜23が相互に分断されて、図8に示されるように可変抵抗膜15が形成される。

【0028】

次に、図9に示されるように、ここまで得られた構造中の要素同士の間の空間が絶縁膜32により埋め込まれる。絶縁膜32として、埋め込み性能の高い材料、例えばTEOS(tetraethoxysilane)を用いることができる。この絶縁膜32のうちの後述の制御線13と第1配線11の第2部分11bとの間の部分は、トランジスタ16のゲート絶縁膜として機能する。または、絶縁膜32の形成に先立ち、ゲート絶縁膜が別途形成されてもよい。次に、絶縁膜32上にマスク(図示せず)が形成される。マスクは、制御線13が形成される予定の領域の上方において開口を有する。次に、開口が導電材料により埋め込まれる。導電材料は、例えば、不純物の導入により導電体化されたポリシリコンからなる。埋め込みの結果、制御線13が形成される。

【0029】

以上述べたように、第1実施形態によれば、より具体的には、xy平面に沿って延びかつz軸に沿って並ぶ複数の第1配線11にyz面に沿って可変抵抗膜15の第1面が接続され、z軸に沿って並ぶ複数の可変抵抗膜15の各第2面に共通にz軸に沿って延びる第2配線12が接続されている。これにより、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。3次元構造によって、セル当たりの面積の縮小に頼らずに、半導体記憶装置の高集積化を実現できる。すなわち、ビット当たりの単価の低減を実現できる。

【0030】

(第2実施形態)

第2実施形態は、半導体記憶装置の構造のバリエーションに関する。

【0031】

図10および図11は、第2実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図10および図11は、図12に示すようにz軸に沿って隣接している。図12は、第2実施形態に係る半導体記憶装置の概略的な平面図である。図10〜図12に示されるように、可変抵抗膜15は、xz面に沿って広がる第1面および第2面を有する。また、可変抵抗膜15は、第1面において、第1配線11の第2部分11bのxz面に沿う2つの面のうちの、例えば、制御線13と反対の側の面に接続されている。図10〜図12から分かるように、図10の構造と図11の構造は、y軸に関して線対称の関係を有する。各要素同士の間の領域は、第1実施形態と同様に、絶縁膜22および各要素間の空間を埋め込む絶縁膜32(合わせて層間絶縁膜と称する)によって埋め込まれている。ただし、図10および図11では、層間絶縁膜32は、図の簡略化のために省略されている。

【0032】

図13は、第2実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図13はまた、図10および図11の構造を模式的に表現している。第2実施形態に係る半導体記憶装置は、第1実施形態と、可変抵抗膜15と第1配線11とが接続する面が異なる。回路構成については、第1実施形態と同じである。したがって、第2実施形態の半導体記憶装置は、メモリセル4へのアクセスの際の電流の流れ方の点では、第1実施形態と同じである。

【0033】

第2実施形態に関して説明した点以外の全ての点について、第1実施形態についての記述が当てはまる。

【0034】

以上述べたように、第2実施形態によれば、可変抵抗膜15と第1配線11とが接続する面が異なることを含む点を除き、第1実施形態と同じく、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。このため、第1実施形態と同じ利点を得られる。

【0035】

(第3実施形態)

第3実施形態も、半導体記憶装置の構造のバリエーションに関する。

【0036】

図14および図15は、第3実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図14および図15は、同一の構造を、相違する部分を省略した形で示している。より具体的には、図14は当該構造のx軸に沿って奥側の構造を中心に示し、図15は、手前側の構造を中心に示している。図16は、第3実施形態に係る半導体記憶装置の概略的な平面図である。

【0037】

図14〜図16に示されるように、第1配線11は、第1実施形態(図2)および第2実施形態(図10)と同じ構造を有する。図15では、図の簡略化のために、最上の第1配線のみが示されている。可変抵抗膜11は、第2実施形態と同じ形で第1配線11と接続されている。すなわち、可変抵抗膜15は、xz面に沿って広がる第1面および第2面のうち第1面において第1配線11の第2部分11bの側面(xz面に沿う面)と接続されている。可変抵抗膜15は、第1配線11の第2部分11bのxz面に沿う2つの面のうち、例えば、制御線13と反対の面に接続されている。

【0038】

第2配線12は、xy面に沿って延びている。すなわち、各第2配線12は、図14および図15の1つの層3内に形成され、対応する第1配線11と同じ層内に形成される。図14では、最下の第2配線12のみが示されている。各第2配線12は同じ平面形状(xy面に沿う形状)を有する。第2配線12は、第1部分12a、複数の第2部分12b、および複数の第3部分12cを有する。第2配線12の第2部分12aは、y軸に沿って延びる。第2配線12の第2部分12bは、x軸に沿って延び、y軸に沿って相互に距離を有する。第2配線12の第1部分12aおよび第2部分12bからなる構造は、第1配線11とy軸に関して線対称の関係を有する。第2配線12の第3部分12cは、L字に類似の平面形状(xy面に沿う形状)を有する。第2配線12の第3部分12cの突起部分のxz面に沿う面は、第2配線12の第2部分12bのxz面に沿う面と接続されている。第2配線12の第3部分12cの突起部分は、典型的には、可変抵抗膜15のy軸に沿う厚さと同じ厚さを有する。また、第2配線12の第3部分12cは、突起部分と異なりかつxz面に沿う面において、可変抵抗膜15の第2面(第1配線11と反対でかつxz面に沿う面)と接続されている。第3実施形態では、第2配線は、例えば図1に示されるように、メモリブロック2の端から導電性のプラグおよび配線を介して周辺回路14に接続されている。

【0039】

制御線13は、第1制御線13aおよび第2制御線13bを含んでいる。第1制御線13aは、第1、第2実施形態の制御線13と同一である。第2制御線13bは、第1制御線13aとy軸に関して線対称の位置に位置する。すなわち、第2制御線13bは、導電材料からなり、z軸に沿って複数の層3を貫いて延び、xy面に沿って広がりを有し、z軸に沿って並ぶ複数の第2配線12の第2部分12bにy軸に沿って並ぶ。第2制御線13bは、第2配線12の第1部分12aとも第2部分12bとも距離を有しており、これらの間には絶縁材料(図示せず)が位置している。第2制御線13bは、例えば第2配線12の第2部分12bのx軸に沿った中間近傍に位置する。第2配線12の第2部分12bのうちの第2制御線13bに並ぶ部分は、非導電性の半導体材料、例えばシリコンからなる。この非導電性部分、第2配線12の第2部分12bのうちの非導電性部分を挟む2つの導電性部分、および第2制御線13bは第2トランジスタ16bを構成する。非導電性部分はチャネルとして機能し、所望の閾値に応じた適切な量および種類の不純物を含んでいる。第2配線12の第2部分12bのうちの非導電性部分を挟む2つの部分はソース/ドレイン領域として機能する。第2制御線13bは、ゲート電極として機能する。第2制御線13bと、第2配線12の第2部分12bとの間の絶縁材料はゲート絶縁膜として機能する。第2トランジスタ16bは、制御線13bを適切な電位にすることによってオンする。可変抵抗膜15および第1、第2トランジスタ16、16bは、メモリセル4を構成する。図14では、第2制御線13bは、図の簡略化のために省略されている。第2制御線13bの電位も、周辺回路14によって行われる。第2制御線13bは、図1に示されるように、メモリブロック2の内部を通過し、基板1の上方の導電性の配線およびプラグを介して周辺回路14と接続されている。

【0040】

各要素間の領域は、第1、第2実施形態と同様に、層間絶縁膜(絶縁膜22、32)によって埋め込まれている。ただし、図14および図15では、層間絶縁膜は、図の簡略化のために省略されている。

【0041】

図17は、第3実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図17はまた、図14および図15の構造を模式的に表現している。図17は、図の簡略化のために1層のみを示している。図17は、左から3番目のメモリセル4が選択されている場合を示している。

【0042】

図17に示されるように、選択セル4の第1制御線13aおよび第2制御線13bが論理的に有効にされて、選択セル4のトランジスタ16および第2トランジスタ16bがオンする。この結果、第1配線11、選択セル4、および第2配線12を結ぶ電流経路が形成される。なお、第1制御線13aおよび第2制御線13bのオンによって、これら第1、第2制御線13a、13bに接続された、別の層中の非選択メモリセル4のトランジスタ16aおよび第2トランジスタ16bもオンする。次に、選択メモリセル4が含まれる層中においてのみ第1、第2配線11、12を流れる電流が供給される。第1配線11に接続された電流ドライバと第2配線12に接続された電流シンクを用いれば、電流は、選択セル4を図14および図17の上から下に向かって流れる。または、第2配線12に接続された電流ドライバと第1配線11に接続された電流シンクを用いれば、電流は、選択セル4を図14および図17の下から上に向かって流れる。このように、メモリセル4(可変抵抗膜15)を貫く2方向の電流を選択的に流すことが可能である。なお、図14〜図16では、電流が第1または第2配線11、12を図の左から右へ向かう例を示しているが、逆向きであってもよい。さらに、第1、第2配線11、12の一方のある側から流出した電流が他方の同じ側に流入してもよい。

【0043】

図18は、第3実施形態の変形例に係る半導体記憶装置の一部を概略的に示す斜視図である。図18に示されるように、第1、第2配線11、12が、図14および図15のものよりも広い幅を有していてもよい。このような構造は、例えば、図14および図15に示す幅の形成済みの第1、第2配線11、12の側面に金属材料を付加することによって形成することができる。この形成は、例えば細い幅の第1、第2配線11、12の側面に金属材料を付加し、エッチングにより成形することを通じて可能である。第1、第2配線11、12の幅を広くすることによって、第1、第2配線11、12の抵抗値を下げることができる。さらに、付加される部分を金属材料とすれば、抵抗値の減少効果は高い。

【0044】

第3実施形態に関して説明した点以外の全ての点について、第1実施形態についての記述が当てはまる。

【0045】

以上述べたように、第3実施形態によれば、第1実施形態と同じく、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。このため、第1実施形態と同じ利点を得られる。さらに、第3実施形態によれば、1つのメモリセル4は、第1配線11と第2配線12との間に直列接続された、可変抵抗膜15とこれを挟む2つのトランジスタ16a、16bを含んでいる。このため、非選択の第1、第2配線11、12の電位を制御することなく、選択セル4のみに電流を流すことができる。なぜなら、選択第1、第2配線11、12の間では選択セル4を含んだ電流経路しか形成されず、また、選択された制御線13a、13bと接続された非選択セル4は選択第1、第2配線11、12とは接続されないからである。このため、選択セル4のみに電流または電圧の印加の制御が簡単な半導体記憶装置を実現できる。さらに、選択セル4のみを通過する電流を流すことが可能であるので、メモリセル4(可変抵抗膜15)を貫く2方向の電流を選択的に流すことが可能である。このため、電流の方向に基づいて相違するデータを記憶するタイプの半導体記憶装置(例えばMRAM)においても3次元構造を実現できる。

【0046】

いずれの実施形態も、上記のものに限定されず、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の実施形態が抽出され得る。例えば、上記各実施形態に示される全構成要件から幾つかの構成要件が削除されても、この構成要件が削除された構成が実施形態として抽出され得る。

【符号の説明】

【0047】

1…半導体基板、2…メモリブロック、3…層、4…メモリセル、11…第1配線、12…第2配線、13…制御線、14…周辺回路、15…可変抵抗膜、16…トランジスタ、17…ダイオード。

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置およびその製造方法に関する。

【背景技術】

【0002】

半導体記憶装置は、ビット当たりの面積を縮小することを通じて製造コストの減少および大容量化が主に図られている。半導体記憶装置として、可変抵抗膜を用いた半導体記憶装置が知られている。可変抵抗膜は、抵抗値の相違する2つ以上の定常状態を有する。この複数の状態を保持データと関連付けることによってデータが不揮発に記憶される。このような記憶装置として、MRAM(magnetoresistive random access memory)およびReRAM(resistive random access memory)がある。MRAMおよびReRAMを含め、記憶装置のビット当たりの面積の縮小による発展が困難になってきている。その理由は、面積の縮小には物理的限界が存在すること、微細加工のための装置が高額であること等が挙げられる。このことは、ビット当たりの単価の低減が困難なことを意味する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−10688号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ビット当たりの単価を低減できる半導体記憶装置およびその製造方法を提供しようとするものである。

【課題を解決するための手段】

【0005】

一実施形態による半導体記憶装置は、第1方向に沿う第1部分と第2方向に沿いかつ第1部分と接続された第2部分とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線を含む。可変抵抗膜は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

【図面の簡単な説明】

【0006】

【図1】第1実施形態に係る半導体記憶装置の全体的な構造を示す図。

【図2】第1実施形態に係る半導体記憶装置の一部の斜視図。

【図3】第1実施形態に係る半導体記憶装置の平面図。

【図4】第1実施形態に係る半導体記憶装置の等価回路図。

【図5】第1実施形態に係る半導体記憶装置の製造方法の一ステップを示す斜視図。

【図6】図5に続くステップを示す斜視図。

【図7】図6に続くステップを示す斜視図。

【図8】図7に続くステップを示す斜視図。

【図9】図8に続くステップを示す斜視図。

【図10】第2実施形態に係る半導体記憶装置の一部の斜視図。

【図11】第2実施形態に係る半導体記憶装置の一部の斜視図。

【図12】第2実施形態に係る半導体記憶装置の平面図。

【図13】第2実施形態に係る半導体記憶装置の等価回路図。

【図14】第3実施形態に係る半導体記憶装置の一部の斜視図。

【図15】第3実施形態に係る半導体記憶装置の一部の斜視図。

【図16】第3実施形態に係る半導体記憶装置の平面図。

【図17】第2実施形態に係る半導体記憶装置の等価回路図。

【図18】第3実施形態の変形例に係る半導体記憶装置の一部の斜視図。

【発明を実施するための形態】

【0007】

以下に実施形態について図面を参照して説明する。なお、以下の説明において、略同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断されるべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0008】

また、以下に示す各実施形態は、この実施形態の技術的思想を具体化するための装置や方法を例示するものであって、実施形態の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。実施形態の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

【0009】

(第1実施形態)

図1は、第1実施形態に係る半導体記憶装置の全体的な構造を概略的に示している。図1に示されるように、半導体基板1の表面の上方に、メモリブロック2が設けられている。メモリブロック2は、z軸に沿って間隔をもって重ねられた複数の層3a〜3nを含んでいる。層3a〜3nは、同じ構成を有し、このため、層3a〜3nを個別に特定する必要がない場合、1つの層を代表して、または包括的に層3と称する。層3は、xy平面に沿って行列状に配置された複数のメモリセル4を含んでいる。各メモリセル4は、少なくとも抵抗変化型素子およびトランジスタを含んでいる。

【0010】

メモリブロック2は、複数の第1配線11を含んでいる。各第1配線11は、各層3中に位置し、xy平面に沿って後述の特定の形状を有し、特定の複数のメモリセル4の各々の一端に接続されている。メモリブロック2は、複数の第2配線12を含んでいる。各第2配線12は、複数の層3をz軸に沿って貫き、特定の複数のメモリセル4の各々の他端に接続されている。メモリブロック2はまた、制御線13を有する。制御線13は、トランジスタを制御するためのものであり、複数の層3をz軸に沿って貫き、複数のトランジスタのゲートとして機能する。

【0011】

第1配線11、第2配線12、制御線13は、基板1上の周辺回路14と電気的に接続されている。第1配線11は、メモリブロック2の端から導電性のプラグおよび配線を介して周辺回路14に接続されている。第2配線および制御線13は、メモリブロック2の内部を通過し、基板1の上方の導電性の配線およびプラグ配線を介して周辺回路14と接続されている。

【0012】

例えば、周辺回路14は、例えばデコーダ、センスアンプ、コントローラ、電流ドライバ、電流シンク等を含んでいる。周辺回路14は、コントローラを介してデコーダを制御して特定のメモリセルにデータを書き込んだり、特定のメモリセルからデータを読み出したりするように第1配線11、第2配線12、制御線13を制御する。アクセス対象のメモリセルは、半導体記憶装置の外部からのアドレス信号によって特定され、コントローラおよびデコーダによって使用される。センスアンプは、読み出されたデータを増幅し、半導体記憶装置の外部に出力する。

【0013】

図2は、第1実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図2は、図1の構造のうちの3つの層のみを示している。図2に示されるように、複数の第1配線11を含んでいる。各第1配線11は、図1の1つの層3内に形成される。第1配線11は、導電性の材料からなり、例えば不純物を含んだシリコンからなる。第1配線11同士は、z軸に沿って相互に距離を有する。各第1配線11は同じ平面形状(xy平面に沿う形状)を有する。第1配線11は、第1部分11aと複数の第2部分11bとを有する。第1配線11の第1部分11aは、y軸に沿って延びる。第1配線の第2部分11bは、x軸に沿って延び、y軸に沿って相互に距離を有する。各第2部分11bは、一端において第1部分11aと接続さている。以上のような第1部分11aおよび第2部分11bによって、第1配線11は櫛状の平面形状を有する。

【0014】

第1配線の第2部分11bの各々の他端は、可変抵抗膜15の一端と接続されている。可変抵抗膜15は、yz平面に沿って広がり、x軸に沿って対向する2つの面の一方(第1面)が、上記のように第2部分11bの端と接続されている。可変抵抗膜15のx軸に沿って対向する2つの面の他方(第2面)は、第2配線12と接続されている。第2配線12は、z軸に沿って複数の層3を貫いて延び、z軸に沿って並ぶ複数の可変抵抗膜15の第2面に共通に接続されている。第2配線12は、導電材料からなる。

【0015】

制御線13は、導電材料からなり、z軸に沿って複数の層3を貫いて延びる。制御線13は、xy面に沿って広がりを有し、z軸に沿って並ぶ複数の第2部分11bにy軸に沿って並ぶ。制御線13は、第1配線11の第1部分11aとも第2部分11bとも距離を有しており、これらの間には絶縁材料(図示せず)が位置している。制御線13は、例えば第1配線11の第2部分11bのx軸に沿った中間近傍に位置する。第1配線11の第2部分11bのうちの制御線13に並ぶ部分は、非導電性の半導体材料、例えばシリコンからなる。この非導電性部分、第1配線11の第2部分11bのうちの非導電性部分を挟む2つの導電体部分、および制御線13はトランジスタ16を構成する。非導電性部分はチャネルとして機能し、所望の閾値に応じた適切な量および種類の不純物を含んでいる。第1配線11の第2部分11bのうちの非導電性部分を挟む2つの導電性部分はソース/ドレイン領域として機能する。制御線13は、トランジスタ16のゲート電極として機能する。制御線13と、第1配線11の第2部分11bとの間の絶縁材料はゲート絶縁膜として機能する。トランジスタ16は、制御線13を適切な電位にすることによってオンする。可変抵抗膜15とトランジスタ16は、メモリセル4を構成する。可変抵抗膜15と第1配線11の第2部分11bとによって、これらの境界においてダイオード17が実現されている。ダイオード17は、可変抵抗膜側においてアノードを有し、第1配線11の第2部分側においてカソードを有する。

【0016】

図2に示される各要素同士の間の領域、具体的には、例えば第1配線11同士の間の領域は絶縁膜により埋め込まれている。

【0017】

可変抵抗膜15として、抵抗値の相違する2つ以上の定常状態を有し、2つの端子を通過する電流または2つの端子に印加される電圧に応じて1つの定常状態を取るあらゆる素子を用いることができる。より具体的には、ReRAMまたはMRAMのメモリセルにおいて使用されるものを用いることができる。ReRAMにおいて用いられるタイプの可変抵抗膜は、素子への印加電圧/電流によって内部の物理状態が変化する物質、より具体的には強相関系材料を含んでいる。また、MRAMにおいて用いられるタイプの可変抵抗膜は、少なくとも、積層された、強磁性材料からなる固定層、非磁性材料からなる中間層、強磁性材料からなる自由層(記録層)を含む。このタイプの素子は、スピン偏極した電子の流れを、2つの端子を通過する電流の向きに応じて低抵抗状態または高抵抗状態を取るように構成される。

【0018】

可変抵抗膜15の種類に応じて、メモリセル4にデータを記憶させるためのメモリセル4への電流または電圧の印加の仕方は相違する。また、本実施形態に適用された可変抵抗膜の種類に応じて、周辺回路14の構成も相違する。電流または電圧の大きさや方向、さらに非選択のメモリセルへの電流または電圧の印加を含め、選択されたメモリセル4にデータを記憶させるためのあらゆる詳細事項は、実施形態に依存せず、従って実施形態を限定しない。このような詳細事項は、当業者にとって知られている。概略的には、選択メモリセル4の可変抵抗膜15には、これと接続された第1配線11および第2配線12によって適切な電流または電圧が印加され、これを通じて、選択メモリセル4にデータが記憶される。また、選択メモリセル4に適切な電流または電圧を印加することを通じて選択メモリセル4のデータが読み出される。

【0019】

図2の構造は、x軸に沿って繰り返し設けられている。図3は、第1実施形態に係る半導体記憶装置の平面図を概略的に示している。また、図3は、1層のみを示している。図3に示されるように、x軸に沿って第1配線11、複数の第2配線12、制御線13、複数の可変抵抗膜15から各々がなる2つの単位構造が並んでいる。図3では、図の簡略化のために、2つの単位構造のみを例示している。単位構造同士は独立している。図3に示されるように、2つの単位構造は、y軸に関して線対称の関係を有する。ある第1配線11の各第2部分11bのy軸上の座標は、別の第1配線11の各第2部分11bのy軸上の座標と一致している。すなわち、相違する第1配線11の相互に対応する各第2部分11bは、同じx軸上の仮想線上にある。しかしながら、このことは必須ではない。例えば、複数の単位構造同士が、y軸上の位置に関して相違していてもよい。さらに、複数の単位構造が、同じ向きを有していてもよい。

【0020】

図4は、第1実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図4はまた、図2の構造を模式的に表現している。以下に、最上層の左から3番目のメモリセル4が選択されている場合のデータ書き込みについて、図4および図2を参照して説明する。以下の説明は、ReRAMに適用された実施形態の例に関する。以下の説明における第1、第2配線11、12、および制御線13の電位は、周辺回路14によって制御される。周辺回路14は、外部からのアドレス信号により特定されるメモリセル4にアクセスするための動作を行なう。図2および図4に示されるように、選択されたメモリセル(選択セル)4と接続された第2配線(選択第2配線)12は、例えば0Vにされる。また、選択セル4と接続された第1配線(選択第1配線)11、すなわち本例では最上層の第1配線11は、選択第2配線12より低い電位、例えば−3Vにされる。一方、選択第1配線11以外の第1配線11はみな、選択第2配線12より高い電位、例えば+2Vにされる。また、選択第2配線12以外の第2配線12の電位は任意である。第1配線11および第2配線12の電位の設定の順序は本例に限られない。

【0021】

第1配線11および第2配線12の電位の設定後、選択セル4と接続された制御線13が活性化される。この活性化により、この制御線13と接続された、選択セル4および選択セル4にz軸に沿って並ぶ非選択のメモリセル4の各々のトランジスタ16がオンする。別の制御線13と接続されたメモリセル4の各トランジスタ16はオフを維持する。このようなトランジスタ16のオンまたはオフの結果、選択セル4のみを図2および図4のように電流が流れる。すなわち、第2配線12から選択セル4の可変抵抗膜15およびトランジスタ16を介して第1配線11へと電流Iが流れる。電流Iは、選択セル4のダイオード17を順方向に流れる。一方、ダイオード17による遮断により、非選択の第1配線11から選択第2配線12へは電流は流れない。すなわち、活性化された制御線13および非選択第1配線11の両方に接続された非選択セル4を介した電流は流れない。

【0022】

ReRAMでは、データの書き込みは、可変抵抗膜15を低抵抗状態から高抵抗状態に変化させる操作と、高抗状態から低抵抗状態に変化させる操作を含む。これらの操作の違いは、可変抵抗膜15に印加される電流または電圧の大きさである。上記の電位の値は例示であり、可変抵抗膜15のいずれの抵抗状態への移行を目指すかに応じて、適切な任意の電位が用いられ得る。

【0023】

次に、図5〜図9は、第1実施形態に係る半導体記憶装置の製造方法のステップを順次示している。図5では、図3のように2つの隣接する単位構造が描かれている。まず、図5に示されるように、半導体基板1(図示せず)の上方に、複数の半導体膜21および複数の絶縁膜22が交互に形成される。半導体膜21は第1配線11へとパターニングされる膜である。半導体膜21のうちの第1配線11へとパターニングされる部分には、不純物が導入され、導電性にされる。一方、半導体膜21のうちのトランジスタ16のチャネルとして機能する部分には、閾値制御のための不純物が導入される。

【0024】

次に、半導体膜21および絶縁膜22の積層構造上に、マスク(図示せず)が形成される。マスクは、y軸に沿って延びる開口を有する。開口は、図3等の各単位構造相互間の領域に対応する。次に、例えば、マスクを介した異方性エッチングによって、積層構造が分断される。分断された各部分は、図3等の1つの単位構造に対応する。次に、各分断された単位構造の側面全体に膜23が形成される。膜23は、可変抵抗膜15へとパターニングされる膜であり、可変抵抗膜15のx軸に沿った長さに対応する厚さを有する。膜23は、図5では、対向する2つの分断された単位構造の対向する各側面上に形成される。次に、膜23上の全面に膜24が形成される。膜24は、第2配線12へとパターニングされる膜であり、第2配線12のx軸に沿った長さに対応する厚さを有する。

【0025】

次に、半導体膜21、絶縁膜22、膜23、および膜24からなる構造上に、マスク(図示せず)が形成される。マスクは、第1配線11、可変抵抗膜15、第2配線12が形成される領域を覆い、その他の領域において開口を有する。すなわち、パターニングされたマスクは、図3のような、第1配線11、可変抵抗膜15、第2配線12のxy平面に沿った形状に対応する。

【0026】

次に、図6に示されるように、例えば、マスクを介した異方性エッチングによって、絶縁膜22、膜23、および膜24がパターニングされる。パターニングされた構造は、xy平面に沿って櫛型の形状のz軸に沿った立体構造を有する。パターニングの結果、第1配線11および第2配線12が形成され、膜23は、y軸に沿って複数の部分へと分断される。なお、図6およびこれ以降の図7〜図9は、簡略化のため、図5の2つの単位構造の原形のうちの奥側のもののみを示している。

【0027】

次に、図7に示されるように、各絶縁膜22の膜23に接する先端がx軸に沿って後退させられる。この後退させる処理は、膜23を第2配線12と反対の面において露出させるためのものである。後退処理には、例えば、ウェットエッチングが用いられる。後退処理の結果、膜23と絶縁膜22との間でかつ第1配線11同士の間に間隔(空間)31が形成される。次に、例えば等方性エッチングにより、間隔31から膜23がエッチングされる。このエッチングの際、間隔31の上下の第1配線11がマスクとして機能する。エッチングの結果、膜23のうちの間隔31に対して露出していた部分が除去されて、膜23が相互に分断されて、図8に示されるように可変抵抗膜15が形成される。

【0028】

次に、図9に示されるように、ここまで得られた構造中の要素同士の間の空間が絶縁膜32により埋め込まれる。絶縁膜32として、埋め込み性能の高い材料、例えばTEOS(tetraethoxysilane)を用いることができる。この絶縁膜32のうちの後述の制御線13と第1配線11の第2部分11bとの間の部分は、トランジスタ16のゲート絶縁膜として機能する。または、絶縁膜32の形成に先立ち、ゲート絶縁膜が別途形成されてもよい。次に、絶縁膜32上にマスク(図示せず)が形成される。マスクは、制御線13が形成される予定の領域の上方において開口を有する。次に、開口が導電材料により埋め込まれる。導電材料は、例えば、不純物の導入により導電体化されたポリシリコンからなる。埋め込みの結果、制御線13が形成される。

【0029】

以上述べたように、第1実施形態によれば、より具体的には、xy平面に沿って延びかつz軸に沿って並ぶ複数の第1配線11にyz面に沿って可変抵抗膜15の第1面が接続され、z軸に沿って並ぶ複数の可変抵抗膜15の各第2面に共通にz軸に沿って延びる第2配線12が接続されている。これにより、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。3次元構造によって、セル当たりの面積の縮小に頼らずに、半導体記憶装置の高集積化を実現できる。すなわち、ビット当たりの単価の低減を実現できる。

【0030】

(第2実施形態)

第2実施形態は、半導体記憶装置の構造のバリエーションに関する。

【0031】

図10および図11は、第2実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図10および図11は、図12に示すようにz軸に沿って隣接している。図12は、第2実施形態に係る半導体記憶装置の概略的な平面図である。図10〜図12に示されるように、可変抵抗膜15は、xz面に沿って広がる第1面および第2面を有する。また、可変抵抗膜15は、第1面において、第1配線11の第2部分11bのxz面に沿う2つの面のうちの、例えば、制御線13と反対の側の面に接続されている。図10〜図12から分かるように、図10の構造と図11の構造は、y軸に関して線対称の関係を有する。各要素同士の間の領域は、第1実施形態と同様に、絶縁膜22および各要素間の空間を埋め込む絶縁膜32(合わせて層間絶縁膜と称する)によって埋め込まれている。ただし、図10および図11では、層間絶縁膜32は、図の簡略化のために省略されている。

【0032】

図13は、第2実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図13はまた、図10および図11の構造を模式的に表現している。第2実施形態に係る半導体記憶装置は、第1実施形態と、可変抵抗膜15と第1配線11とが接続する面が異なる。回路構成については、第1実施形態と同じである。したがって、第2実施形態の半導体記憶装置は、メモリセル4へのアクセスの際の電流の流れ方の点では、第1実施形態と同じである。

【0033】

第2実施形態に関して説明した点以外の全ての点について、第1実施形態についての記述が当てはまる。

【0034】

以上述べたように、第2実施形態によれば、可変抵抗膜15と第1配線11とが接続する面が異なることを含む点を除き、第1実施形態と同じく、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。このため、第1実施形態と同じ利点を得られる。

【0035】

(第3実施形態)

第3実施形態も、半導体記憶装置の構造のバリエーションに関する。

【0036】

図14および図15は、第3実施形態に係る半導体記憶装置の一部を概略的に示す斜視図である。図14および図15は、同一の構造を、相違する部分を省略した形で示している。より具体的には、図14は当該構造のx軸に沿って奥側の構造を中心に示し、図15は、手前側の構造を中心に示している。図16は、第3実施形態に係る半導体記憶装置の概略的な平面図である。

【0037】

図14〜図16に示されるように、第1配線11は、第1実施形態(図2)および第2実施形態(図10)と同じ構造を有する。図15では、図の簡略化のために、最上の第1配線のみが示されている。可変抵抗膜11は、第2実施形態と同じ形で第1配線11と接続されている。すなわち、可変抵抗膜15は、xz面に沿って広がる第1面および第2面のうち第1面において第1配線11の第2部分11bの側面(xz面に沿う面)と接続されている。可変抵抗膜15は、第1配線11の第2部分11bのxz面に沿う2つの面のうち、例えば、制御線13と反対の面に接続されている。

【0038】

第2配線12は、xy面に沿って延びている。すなわち、各第2配線12は、図14および図15の1つの層3内に形成され、対応する第1配線11と同じ層内に形成される。図14では、最下の第2配線12のみが示されている。各第2配線12は同じ平面形状(xy面に沿う形状)を有する。第2配線12は、第1部分12a、複数の第2部分12b、および複数の第3部分12cを有する。第2配線12の第2部分12aは、y軸に沿って延びる。第2配線12の第2部分12bは、x軸に沿って延び、y軸に沿って相互に距離を有する。第2配線12の第1部分12aおよび第2部分12bからなる構造は、第1配線11とy軸に関して線対称の関係を有する。第2配線12の第3部分12cは、L字に類似の平面形状(xy面に沿う形状)を有する。第2配線12の第3部分12cの突起部分のxz面に沿う面は、第2配線12の第2部分12bのxz面に沿う面と接続されている。第2配線12の第3部分12cの突起部分は、典型的には、可変抵抗膜15のy軸に沿う厚さと同じ厚さを有する。また、第2配線12の第3部分12cは、突起部分と異なりかつxz面に沿う面において、可変抵抗膜15の第2面(第1配線11と反対でかつxz面に沿う面)と接続されている。第3実施形態では、第2配線は、例えば図1に示されるように、メモリブロック2の端から導電性のプラグおよび配線を介して周辺回路14に接続されている。

【0039】

制御線13は、第1制御線13aおよび第2制御線13bを含んでいる。第1制御線13aは、第1、第2実施形態の制御線13と同一である。第2制御線13bは、第1制御線13aとy軸に関して線対称の位置に位置する。すなわち、第2制御線13bは、導電材料からなり、z軸に沿って複数の層3を貫いて延び、xy面に沿って広がりを有し、z軸に沿って並ぶ複数の第2配線12の第2部分12bにy軸に沿って並ぶ。第2制御線13bは、第2配線12の第1部分12aとも第2部分12bとも距離を有しており、これらの間には絶縁材料(図示せず)が位置している。第2制御線13bは、例えば第2配線12の第2部分12bのx軸に沿った中間近傍に位置する。第2配線12の第2部分12bのうちの第2制御線13bに並ぶ部分は、非導電性の半導体材料、例えばシリコンからなる。この非導電性部分、第2配線12の第2部分12bのうちの非導電性部分を挟む2つの導電性部分、および第2制御線13bは第2トランジスタ16bを構成する。非導電性部分はチャネルとして機能し、所望の閾値に応じた適切な量および種類の不純物を含んでいる。第2配線12の第2部分12bのうちの非導電性部分を挟む2つの部分はソース/ドレイン領域として機能する。第2制御線13bは、ゲート電極として機能する。第2制御線13bと、第2配線12の第2部分12bとの間の絶縁材料はゲート絶縁膜として機能する。第2トランジスタ16bは、制御線13bを適切な電位にすることによってオンする。可変抵抗膜15および第1、第2トランジスタ16、16bは、メモリセル4を構成する。図14では、第2制御線13bは、図の簡略化のために省略されている。第2制御線13bの電位も、周辺回路14によって行われる。第2制御線13bは、図1に示されるように、メモリブロック2の内部を通過し、基板1の上方の導電性の配線およびプラグを介して周辺回路14と接続されている。

【0040】

各要素間の領域は、第1、第2実施形態と同様に、層間絶縁膜(絶縁膜22、32)によって埋め込まれている。ただし、図14および図15では、層間絶縁膜は、図の簡略化のために省略されている。

【0041】

図17は、第3実施形態に係る半導体記憶装置での電流の流れを概略的に示す等価回路図である。図17はまた、図14および図15の構造を模式的に表現している。図17は、図の簡略化のために1層のみを示している。図17は、左から3番目のメモリセル4が選択されている場合を示している。

【0042】

図17に示されるように、選択セル4の第1制御線13aおよび第2制御線13bが論理的に有効にされて、選択セル4のトランジスタ16および第2トランジスタ16bがオンする。この結果、第1配線11、選択セル4、および第2配線12を結ぶ電流経路が形成される。なお、第1制御線13aおよび第2制御線13bのオンによって、これら第1、第2制御線13a、13bに接続された、別の層中の非選択メモリセル4のトランジスタ16aおよび第2トランジスタ16bもオンする。次に、選択メモリセル4が含まれる層中においてのみ第1、第2配線11、12を流れる電流が供給される。第1配線11に接続された電流ドライバと第2配線12に接続された電流シンクを用いれば、電流は、選択セル4を図14および図17の上から下に向かって流れる。または、第2配線12に接続された電流ドライバと第1配線11に接続された電流シンクを用いれば、電流は、選択セル4を図14および図17の下から上に向かって流れる。このように、メモリセル4(可変抵抗膜15)を貫く2方向の電流を選択的に流すことが可能である。なお、図14〜図16では、電流が第1または第2配線11、12を図の左から右へ向かう例を示しているが、逆向きであってもよい。さらに、第1、第2配線11、12の一方のある側から流出した電流が他方の同じ側に流入してもよい。

【0043】

図18は、第3実施形態の変形例に係る半導体記憶装置の一部を概略的に示す斜視図である。図18に示されるように、第1、第2配線11、12が、図14および図15のものよりも広い幅を有していてもよい。このような構造は、例えば、図14および図15に示す幅の形成済みの第1、第2配線11、12の側面に金属材料を付加することによって形成することができる。この形成は、例えば細い幅の第1、第2配線11、12の側面に金属材料を付加し、エッチングにより成形することを通じて可能である。第1、第2配線11、12の幅を広くすることによって、第1、第2配線11、12の抵抗値を下げることができる。さらに、付加される部分を金属材料とすれば、抵抗値の減少効果は高い。

【0044】

第3実施形態に関して説明した点以外の全ての点について、第1実施形態についての記述が当てはまる。

【0045】

以上述べたように、第3実施形態によれば、第1実施形態と同じく、可変抵抗膜をメモリセルに用いる半導体記憶装置の3次元構造が実現される。このため、第1実施形態と同じ利点を得られる。さらに、第3実施形態によれば、1つのメモリセル4は、第1配線11と第2配線12との間に直列接続された、可変抵抗膜15とこれを挟む2つのトランジスタ16a、16bを含んでいる。このため、非選択の第1、第2配線11、12の電位を制御することなく、選択セル4のみに電流を流すことができる。なぜなら、選択第1、第2配線11、12の間では選択セル4を含んだ電流経路しか形成されず、また、選択された制御線13a、13bと接続された非選択セル4は選択第1、第2配線11、12とは接続されないからである。このため、選択セル4のみに電流または電圧の印加の制御が簡単な半導体記憶装置を実現できる。さらに、選択セル4のみを通過する電流を流すことが可能であるので、メモリセル4(可変抵抗膜15)を貫く2方向の電流を選択的に流すことが可能である。このため、電流の方向に基づいて相違するデータを記憶するタイプの半導体記憶装置(例えばMRAM)においても3次元構造を実現できる。

【0046】

いずれの実施形態も、上記のものに限定されず、実施段階ではその要旨を逸脱しない範囲で、種々に変形することが可能である。さらに、上記実施形態には種々の段階が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の実施形態が抽出され得る。例えば、上記各実施形態に示される全構成要件から幾つかの構成要件が削除されても、この構成要件が削除された構成が実施形態として抽出され得る。

【符号の説明】

【0047】

1…半導体基板、2…メモリブロック、3…層、4…メモリセル、11…第1配線、12…第2配線、13…制御線、14…周辺回路、15…可変抵抗膜、16…トランジスタ、17…ダイオード。

【特許請求の範囲】

【請求項1】

第1方向に沿う第1部分と第2方向に沿いかつ前記第1部分と接続された第2部分とを有し、前記第2部分において半導体材料を含み、前記第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線と、

前記第1配線の前記第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る可変抵抗膜と、

前記可変抵抗膜の前記第1面と対向する第2面と接続された第2配線と、

前記第1平面と交わる方向に沿い、前記少なくとも2つの第1配線の前記第2部分の前記半導体材料を含む部分と絶縁膜を介して接し、前記第1配線の前記第2部分の前記半導体材料を含む部分および前記絶縁膜とともにトランジスタを構成する制御線と、

を具備することを特徴とする半導体記憶装置。

【請求項2】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1部分と反対の端に接続され、

前記第2配線が、前記第1平面と交わる方向に沿う、

ことを特徴とする請求項1の半導体記憶装置。

【請求項3】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1方向が貫く面に接続され、

前記第2配線が、前記第1平面と交わる方向に沿う、

ことを特徴とする請求項1の半導体記憶装置。

【請求項4】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1方向が貫く面に接続され、

前記第2配線が、前記第1方向に沿う第1部分と前記第2方向に沿いかつ前記第2配線の前記第1部分および前記可変抵抗膜の前記第2面に接続された第2部分とを有する、

ことを特徴とする請求項1の半導体記憶装置。

【請求項5】

第1導電膜と、前記第1導電膜上の絶縁膜と、前記絶縁膜上の第2導電膜とを含む積層膜を形成することと、

前記第1導電膜から前記第2導電膜にわたる前記積層膜の側面に、相違する抵抗値を示す複数の状態を取り得る可変抵抗膜を形成することと、

前記可変抵抗膜の前記積層膜に面する面と対向する面上に第3導電膜を形成することと、

前記絶縁膜の前記可変抵抗膜に面する面を後退させて前記可変抵抗膜の前記第1導電膜と前記第2導電膜との間の部分を露出させることと、

前記可変抵抗膜の前記露出した部分から前記可変抵抗膜を除去して、前記可変抵抗膜を前記第1導電膜の側面と接続された第1部分と前記第2導電膜の側面と接続された第2部分とに分割することと、

前記第1導電膜および前記第2導電膜と間隔をおいて並ぶ導電性の柱を形成することと、

を具備する、半導体記憶装置の製造方法。

【請求項1】

第1方向に沿う第1部分と第2方向に沿いかつ前記第1部分と接続された第2部分とを有し、前記第2部分において半導体材料を含み、前記第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線と、

前記第1配線の前記第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る可変抵抗膜と、

前記可変抵抗膜の前記第1面と対向する第2面と接続された第2配線と、

前記第1平面と交わる方向に沿い、前記少なくとも2つの第1配線の前記第2部分の前記半導体材料を含む部分と絶縁膜を介して接し、前記第1配線の前記第2部分の前記半導体材料を含む部分および前記絶縁膜とともにトランジスタを構成する制御線と、

を具備することを特徴とする半導体記憶装置。

【請求項2】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1部分と反対の端に接続され、

前記第2配線が、前記第1平面と交わる方向に沿う、

ことを特徴とする請求項1の半導体記憶装置。

【請求項3】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1方向が貫く面に接続され、

前記第2配線が、前記第1平面と交わる方向に沿う、

ことを特徴とする請求項1の半導体記憶装置。

【請求項4】

前記可変抵抗膜の前記第1面が、前記第1配線の前記第2部分の前記第1方向が貫く面に接続され、

前記第2配線が、前記第1方向に沿う第1部分と前記第2方向に沿いかつ前記第2配線の前記第1部分および前記可変抵抗膜の前記第2面に接続された第2部分とを有する、

ことを特徴とする請求項1の半導体記憶装置。

【請求項5】

第1導電膜と、前記第1導電膜上の絶縁膜と、前記絶縁膜上の第2導電膜とを含む積層膜を形成することと、

前記第1導電膜から前記第2導電膜にわたる前記積層膜の側面に、相違する抵抗値を示す複数の状態を取り得る可変抵抗膜を形成することと、

前記可変抵抗膜の前記積層膜に面する面と対向する面上に第3導電膜を形成することと、

前記絶縁膜の前記可変抵抗膜に面する面を後退させて前記可変抵抗膜の前記第1導電膜と前記第2導電膜との間の部分を露出させることと、

前記可変抵抗膜の前記露出した部分から前記可変抵抗膜を除去して、前記可変抵抗膜を前記第1導電膜の側面と接続された第1部分と前記第2導電膜の側面と接続された第2部分とに分割することと、

前記第1導電膜および前記第2導電膜と間隔をおいて並ぶ導電性の柱を形成することと、

を具備する、半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−69753(P2013−69753A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−205776(P2011−205776)

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]