半導体記憶装置およびROMデータパターンの発生方法

【課題】 メモリセル拡散マスクパターンの形状容易化により、メモリセル拡散マスクパターン形成の安定化及び歩留向上を図る。

【解決手段】 隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターン5で構成し、拡散マスクパターン5がメモリセルアレイ1上に配列され、拡散マスクパターン5で形成されるメモリセルのソースコモン配線8をメタル配線にした。このように、メモリセル拡散マスクパターンを2ビット矩形拡散マスクパターンとし、ソースコモン配線を拡散層からメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化し、さらに実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持し、実メモリセルの拡散マスクパターンのパターン形成精度を向上させ、歩留向上を図る。

【解決手段】 隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターン5で構成し、拡散マスクパターン5がメモリセルアレイ1上に配列され、拡散マスクパターン5で形成されるメモリセルのソースコモン配線8をメタル配線にした。このように、メモリセル拡散マスクパターンを2ビット矩形拡散マスクパターンとし、ソースコモン配線を拡散層からメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化し、さらに実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持し、実メモリセルの拡散マスクパターンのパターン形成精度を向上させ、歩留向上を図る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はマスクROM(Read Only Memory)などの半導体記憶装置に関し、特に、メモリセルの拡散マスクパターンの形成容易化を実現するレイアウト技術についての半導体記憶装置およびROMデータパターンの発生方法に関する。

【背景技術】

【0002】

図7で示すような構成が、従来の半導体記憶装置の例として示されるマスクROMの構成を示すブロック図である。

【0003】

この半導体記憶装置は、メモリセル拡散マスクパターン21が櫛形の形状のN型MOSトランジスタで構成されるメモリセルアレイ部20、外部からのアドレス信号やチップイネーブル信号を制御する制御部3、制御部3で制御されたロウアドレス信号からワード線を選択するロウデコーダ部2、制御部3で制御されたカラムアドレス信号からビット線を選択するカラムデコーダ部4で構成される。

【0004】

ワード線22は、メモリセルトランジスタのゲート部に接続され、ビット線23は、メモリセルトランジスタのドレイン部にドレインノードコンタクト24によって接続されている。またメモリセルトランジスタのソース部は、メモリセル拡散マスクパターン21によってメモリセルアレイ部20内をロウ方向に接続されており、ロウデコーダ部2で接地電位に接続されている。このメモリセル拡散マスクパターン21の形状を示した図が、図8である。

【0005】

図8に示すように、従来のメモリセル拡散マスクパターンはロウ方向に櫛形の構成をしており、メモリセルアレイ部20内をカラム方向に繰り返し配置されている。このような構成で2ビットのメモリセルトランジスタを1つの拡散マスクパターンで構成し、ドレインノードコンタクト24の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成をとっている。

【0006】

さらに、図9は、図7のメモリセルアレイ部20の一部を取り出して示した図であり、2ビット櫛形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン21とメモリセルトランジスタのゲートに接続されたワード線(n)22a、ワード線(n−1)22bと前記メモリセル拡散マスクパターン21で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト24により接続されたビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23c、により構成されている。

【0007】

例えば制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)22aが選択された場合、全てのメモリセルトランジスタのソースは櫛形メモリセル拡散パターンにより拡散層で接続されており、ソース電位である接地電位となっており、ワード線(n)22aの選択により、櫛形メモリセル拡散マスクパターン21の上部のメモリセルトランジスタがONし、あらかじめドレインノードコンタクト24が配置されているメモリセルのビット線(m)23bがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m)23bの選択に応じて読み出され、あらかじめドレインノードコンタクト24が配置されていないメモリセルのビット線(m−1)23aやビット線(m+1)23cは、メモリセルトランジスタはONするが、ドレインノードコンタクト24が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(m−1)23aやビット線(m+1)23cが選択された場合に読み出す。

【0008】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)22bが選択された場合も同様に全てのメモリセルトランジスタのソースは櫛形メモリセル拡散パターンにより拡散層で接続されており、ソース電位である接地電位となっており、ワード線(n−1)22bの選択により、櫛形メモリセル拡散マスクパターン21の下部のメモリセルトランジスタがONし、あらかじめドレインノードコンタクト24が配置されているメモリセルのビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23cがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23cの選択に応じて読み出される。

【0009】

以上のようにメモリセル拡散マスクパターンは拡散層でロウ方向にソースノードを共通化する2ビット櫛形パターンで構成されている。

【特許文献1】特開2004−342261号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上記従来の半導体記憶装置において、メモリセル拡散マスクパターンはメモリセルのソースが共通であることから、拡散層で配線する2ビット櫛形拡散マスクパターンで構成されている。

【0011】

しかしながら、このような構成である限りは、近年の微細化に伴い、櫛形パターン形成が困難になってきており、メモリセル形状のアンバランスや形状不良といった歩留低下の原因となってきている。

【0012】

したがって、本発明の目的は、メモリセル拡散マスクパターンの形状容易化により、メモリセル拡散マスクパターン形成の安定化及び歩留向上を図る半導体記憶装置およびROMデータパターンの発生方法を提供することである。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明の請求項1記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターンで構成し、前記拡散マスクパターンがメモリセルアレイ上に配列され、前記拡散マスクパターンで形成されるメモリセルのソースコモン配線をメタル配線にした。

【0014】

すなわち、従来の2ビット櫛形メモリセル拡散マスクパターンを2ビット矩形拡散マスクパターンとし、メモリセルのソースコモン配線を拡散層からメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化するものとする。

【0015】

請求項2記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルアレイ上の最外周の拡散マスクパターンは、実メモリセルではなくダミーパターンとして形成した。

【0016】

請求項3記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタのソース電位である電源線に接続されている。

【0017】

請求項4記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線に接続されている。

【0018】

請求項5記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタのソース電位である電源線は最下層である第1メタル配線層で構成されている。

【0019】

請求項6記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記電源線は最下層である第1メタル配線層で構成されている。

【0020】

請求項7記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線は最下層である第1メタル配線層で構成されている。

【0021】

請求項8記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記内部ドライブ信号線は最下層である第1メタル配線層で構成されている。

【0022】

請求項9記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0023】

請求項10記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0024】

請求項11記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0025】

請求項12記載の半導体記憶装置は、請求項9記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0026】

請求項13記載の半導体記憶装置は、請求項10記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0027】

請求項14記載の半導体記憶装置は、請求項11記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0028】

請求項15記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0029】

請求項16記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0030】

請求項17記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0031】

請求項18記載の半導体記憶装置は、請求項15記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0032】

請求項19記載の半導体記憶装置は、請求項16記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0033】

請求項20記載の半導体記憶装置は、請求項17記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0034】

請求項21記載のROMデータパターンの発生方法は、請求項18記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してROMデータパターンとして生成する。

【0035】

請求項22記載のROMデータパターンの発生方法は、請求項19記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成する。

【0036】

請求項23記載のROMデータパターンの発生方法は、請求項20記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成する。

【発明の効果】

【0037】

本発明の請求項1記載の半導体記憶装置によれば、2ビットのメモリセルトランジスタを、1つの拡散マスクパターンで構成し、拡散マスクパターンがメモリセルアレイ上に配列され、ソースコモン配線をメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化し、パターン形成を容易化する効果を得ることができる。またパターン形成の容易化により、歩留を向上する効果を得ることができる。

【0038】

請求項2記載の半導体記憶装置によれば、メモリセルアレイ部のメモリセル拡散マスクパターンの最外周の2ビット拡散マスクパターンをROMの実メモリセルとして使用せず、ダミーパターンとすることにより、実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持する。パターン連続性の維持により、実メモリセルの拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0039】

請求項3記載の半導体記憶装置によれば、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、電源線に共通接続するため1つのコンタクトマスクパターンを用いることでレイアウト面積増大を防ぐ効果が得られる。

【0040】

請求項4記載の半導体記憶装置によれば、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、ソース電位を制御する内部ドライブ信号線に共通接続するため1つのコンタクトマスクパターンを用いることでレイアウト面積増大を防ぐ効果が得られる。

【0041】

請求項5及び請求項6記載の半導体記憶装置によれば、メモリセルトランジスタのソース電位である電源線をメタル配線層の最下層である第1メタル配線層で構成することにより接地電源を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作の効果が得られる。

【0042】

請求項7及び請求項8記載の半導体記憶装置によれば、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線をメタル配線層の最下層である第1メタル配線層で構成することにより任意のソース電位を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作の効果が得られる。

【0043】

請求項9及び請求項10及び請求項11記載の半導体記憶装置によれば、メモリセルトランジスタのソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターンを下層部に構成することによって、メモリセル拡散マスクパターンの連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0044】

請求項12記載の半導体記憶装置によれば、請求項9記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0045】

請求項13記載の半導体記憶装置によれば、請求項10記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0046】

請求項14記載の半導体記憶装置によれば、請求項11記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0047】

請求項15の半導体記憶装置によれば、請求項1記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0048】

請求項16の半導体記憶装置によれば、請求項3記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0049】

請求項17の半導体記憶装置によれば、請求項4記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0050】

請求項18及び請求項21記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項15に記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【0051】

請求項19及び請求項22記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項16に記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【0052】

請求項20及び請求項23記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項17記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【発明を実施するための最良の形態】

【0053】

以下、本発明の実施の形態を図面を参照しながら説明する。

【0054】

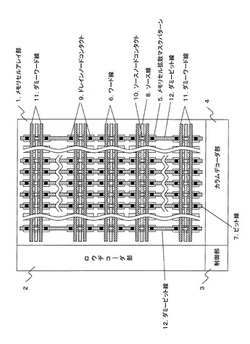

本発明の第1の実施形態を図1〜図3に基づいて説明する。図1は本発明の第1の実施の形態に係る半導体記憶装置の構成を示すレイアウト図、図2は図1のメモリセルアレイ部におけるメモリセル拡散マスクパターン形状を示すレイアウト図である。

【0055】

本発明の第1の実施の形態に係る半導体記憶装置は、図1で示すように、メモリセル拡散マスクパターン5が矩形の形状で構成されるメモリセルアレイ部1、外部からのアドレス信号やチップイネーブル信号を制御する制御部3、制御部3で制御されたロウアドレス信号からワード線を選択するロウデコーダ部2、制御部3で制御されたカラムアドレス信号からビット線を選択するカラムデコーダ部4で構成される。ワード線6は、メモリセルトランジスタのゲート部に接続され、ビット線7は、メモリセルトランジスタのドレイン部にドレインノードコンタクト9によって接続されている。またメモリセルトランジスタのソース部は、ソース線8によってメモリセルアレイ部1内をロウ方向に接続されており、ロウデコーダ部2で接地電位に接続されている。このメモリセル拡散マスクパターン5の形状を示した図が、図2である。

【0056】

図2に示すように、メモリセル拡散マスクパターンは矩形の構成をしており、メモリセルアレイ部1内をロウ方向、カラム方向の両方向に繰り返し配置されている。このような構成で2ビットのメモリセルトランジスタを1つの拡散マスクパターンで構成し、ドレインノードコンタクト9の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成をとっている。

【0057】

さらに、図3は、図1のメモリセルアレイ部1の一部を取り出して示したレイアウト図であり、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8と、メモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7c、により構成されている。

【0058】

例えば制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)6aが選択された場合、3つの矩形メモリセル拡散マスクパターン5で2ビットの隣り合うメモリセルトランジスタが3組形成されており、全てのメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、3つの矩形メモリセル拡散マスクパターン5の上部のメモリセルトランジスタがワード線(n)6aの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(m)7bがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m)7bの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(m−1)7aやビット線(m+1)7cは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(m−1)7aやビット線(m+1)7cが選択された場合に読み出す。

【0059】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)6bが選択された場合も同様に全てのメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、3つの矩形メモリセル拡散マスクパターン5の下部のメモリセルトランジスタがワード線(n−1)6bの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cの選択に応じて読み出される。

【0060】

このように動作的には従来の半導体記憶装置と同様の動作が実現できる。

【0061】

ここで、メモリセル拡散マスクパターンの形状を比較してみると、従来の2ビット櫛形拡散マスクパターンに比べ、本実施形態の2ビット矩形拡散パターンは形状が容易化され、メモリセル拡散マスクパターン生成時の形状のアンバランスや形状不具合を起こし難いパターンとなっており、歩留向上を図ることが可能である。

【0062】

また、図1において、メモリセルアレイ部1の最外周の2ビット矩形拡散マスクパターンで生成されるメモリセルトランジスタをROMの実メモリセルとして使用せず、ソースに接地電位に接続されたダミーワード線11あるいはドレインに接地電位に接続されたダミービット線12に接続、あるいはその両方に接続することによってダミーセルとすることで最外周の2ビット矩形拡散マスクパターンをダミーパターンとする。こうすることにより、実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持し、実メモリセルの拡散マスクパターンのパターン形成精度を向上させることが可能である。

【0063】

また、図3において、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、電源線に共通接続するため、隣り合う2ビットのメモリセルトランジスタのソースに1つのコンタクトマスクパターンを用いることでソースコモン配線を接続できるため、レイアウト面積増大を防ぐ効果が得られる。

【0064】

さらに、図3において、メモリセルトランジスタのソースに接続されたソース線8の電源線をメタル配線層の最下層である第1メタル配線層で構成することにより接地電源を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作が可能である。このとき読み出しデータ線であるビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cは第2メタル配線層か、あるいは更に上層の配線層で構成されている。

【0065】

また、本発明の実施の形態において、メモリセルトランジスタのソース電位を接地電位として説明したが、これに言及するものではなく、任意の電位に設定するために内部ドライブ信号線に接続した場合にも同様の構成及び効果を得ることができる。

【0066】

本発明の第2の実施形態を図4および図5に基づいて説明する。

【0067】

本発明の第2の実施の形態に係る半導体記憶装置は、本発明の第1の実施の形態に係る半導体装置において、図4に示すように、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8と、メモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線7と、読み出しデータ線であるビット線7の間にソース電位裏打ち用配線13とを配置した構成をとるものである。このソース電位裏打ち用配線13は複数の読み出しデータ線単位毎に配置されるものとする。このような構成をとることでメモリ容量が増加し、ロウ方向のソース線8の配線長が長くなることによる配線抵抗の増大を防ぎ、ソース電位の変動を低減し安定したソース電位を供給することができる。

【0068】

このソース電位裏打ち用配線領域においても図4に示すように、メモリセル拡散マスクパターン5を下層部に配置しており、メモリセルトランジスタを生成する構成になっているが、ソースノードコンタクト10及びドレインノードコンタクト9の配置により、ソース、ドレインともソース電位裏打ち用配線13と同電位に接続されるためダミーセルとして扱うことができる。こうすることによって、ソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5の連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0069】

また、図5は図4と同様にメモリ容量が増加し、ロウ方向のソース線8の配線長が長くなることによる配線抵抗の増大を防ぎ、ソース電位の変動を低減し安定したソース電位を供給するために、読み出しデータ線であるビット線7の間にソース電位裏打ち用配線13を配置し、このソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5を下層部に配置する構成である。ソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5の連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果に加え、図5で示すレイアウト構成においては、生成されるメモリセルトランジスタのソース及びドレインをソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0070】

本発明の第3の実施形態を図6に基づいて説明する。

【0071】

本発明の第3の実施の形態に係る半導体記憶装置は、本発明の第1の実施の形態に係る半導体装置においてメモリセルアレイ部1の一部を取り出して示したレイアウト図6で示すように、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8とメモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線(s−1)7d、ビット線(s)7e、ビット線(s+1)7fにより構成されている。ROMデータの“0”、“1”の区分をドレインノードコンタクト9の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成であるため、隣り合う2ビットのメモリセルトランジスタのうちどちらか一方あるいは両方に“0”のROMデータが設定されている場合はメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8と接続するため、ソースノードコンタクト10を配置し、ビット線に“0”データを読み出すためにドレインノードコンタクト9を配置する必要がある。しかし、隣り合う2ビットのメモリセルトランジスタの両方とも“1”のROMデータが設定されている場合はソース電位をビット線に読み出す必要がなくプリチャージ電位のままであることから、ドレインノードコンタクト9だけでなくソースノードコンタクト10も配置する必要がない。

【0072】

例えば図6において、ドレインノードコンタクト9の有無により、ビット線(s−1)7dの下層に生成された2ビットのメモリセルトランジスタのうちワード線(n)6aがゲートに接続されている上側のメモリセルトランジスタは“1”データ、ワード線(n−1)6bがゲートに接続されている下側のメモリセルトランジスタは“0”データに設定されている。同様にビット線(s)7eの下層に生成された2ビットのメモリセルトランジスタは上下両方とも“1”データに設定され、ビット線(s+1)7fの下層に生成された2ビットのメモリセルトランジスタのうちワード線(n)6aがゲートに接続されている上側のメモリセルトランジスタは“0”データ、ワード線(n−1)6bがゲートに接続されている下側のメモリセルトランジスタは“1”データに設定されている。

【0073】

制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)6aが選択された場合、3つの矩形メモリセル拡散マスクパターン5で2ビットの隣り合うメモリセルトランジスタが3組形成されており、左右2組のメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、真ん中のメモリセルトランジスタのソースはソースノードコンタクト10が配置されておらず、ソース線8と接続されていない。

【0074】

3つの矩形メモリセル拡散マスクパターン5の上部のメモリセルトランジスタがワード線(n)6aの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(s+1)7fがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(s+1)7fの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(s−1)7dやビット線(s)7eは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(s−1)7dやビット線(s)7eが選択された場合に読み出す。

【0075】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)6bが選択された場合も同様に左右2組のメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、真ん中のメモリセルトランジスタのソースはソースノードコンタクト10が配置されておらず、ソース線8と接続されていない。

【0076】

3つの矩形メモリセル拡散マスクパターン5の下部のメモリセルトランジスタがワード線(n−1)6bの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(s−1)7dがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(s−1)7dの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(s)7eやビット線(s+1)7fは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(s)7eやビット線(s+1)7fが選択された場合に読み出す。

【0077】

以上のように隣り合う2ビットのメモリセルトランジスタの両方とも“1”のROMデータが設定されているビット線(s)7eも設定値どおり読み出すことが可能であるので、このような場合、ソースノードコンタクト10を配置する必要がない。こうすることによりソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【産業上の利用可能性】

【0078】

本発明に係る半導体記憶装置は、メモリセルアレイ上のメモリセル拡散マスクパターンの容易化及びパターンの連続性の維持により、微細化するメモリセル拡散マスクパターン形成の容易化を実現する半導体記憶装置等として有用である。

【図面の簡単な説明】

【0079】

【図1】本発明の第1の実施の形態に係る半導体記憶装置の構成を示すレイアウト図である。

【図2】図1のメモリセルアレイ部のメモリセル拡散マスクパターン形状を示すレイアウト図である。

【図3】図1のメモリセルアレイ部の一部を示すレイアウト図である。

【図4】本発明の第2の実施の形態に係る半導体記憶装置の構成でメモリセルアレイ部の一部を示すレイアウト図である。

【図5】図4の構成で隣り合う2ビットのメモリセルトランジスタにドレインノードコンタクトが無い場合のレイアウト図である。

【図6】本発明の第3の実施の形態に係る半導体記憶装置の構成でメモリセルアレイ部の一部を示すレイアウト図である。

【図7】従来の半導体記憶装置の構成を示すレイアウト図である。

【図8】図7のメモリセルアレイ部のメモリセル拡散マスクパターン形状を示すレイアウト図である。

【図9】図7のメモリセルアレイ部の一部を示すレイアウト図である。

【符号の説明】

【0080】

1 メモリセルアレイ部

2 ロウデコーダ部

3 制御部

4 カラムデコーダ部

5 メモリセル拡散マスクパターン

6 ワード線

6a ワード線(n)

6b ワード線(n−1)

7 ビット線

7a ビット線(m−1)

7b ビット線(m)

7c ビット線(m+1)

7d ビット線(s−1)

7e ビット線(s)

7f ビット線(s+1)

8 ソース線

9 ドレインノードコンタク

10 ソースノードコンタクト

11 ダミーワード線

12 ダミービット線

13 ソース電位裏打ち用配線

20 メモリセルアレイ部

21 メモリセル拡散マスクパターン

22 ワード線

22a ワード線(n)

22b ワード線(n−1)

23 ビット線

23a ビット線(m−1)

23b ビット線(m)

23c ビット線(m+1)

24 ドレインノードコンタクト

【技術分野】

【0001】

本発明はマスクROM(Read Only Memory)などの半導体記憶装置に関し、特に、メモリセルの拡散マスクパターンの形成容易化を実現するレイアウト技術についての半導体記憶装置およびROMデータパターンの発生方法に関する。

【背景技術】

【0002】

図7で示すような構成が、従来の半導体記憶装置の例として示されるマスクROMの構成を示すブロック図である。

【0003】

この半導体記憶装置は、メモリセル拡散マスクパターン21が櫛形の形状のN型MOSトランジスタで構成されるメモリセルアレイ部20、外部からのアドレス信号やチップイネーブル信号を制御する制御部3、制御部3で制御されたロウアドレス信号からワード線を選択するロウデコーダ部2、制御部3で制御されたカラムアドレス信号からビット線を選択するカラムデコーダ部4で構成される。

【0004】

ワード線22は、メモリセルトランジスタのゲート部に接続され、ビット線23は、メモリセルトランジスタのドレイン部にドレインノードコンタクト24によって接続されている。またメモリセルトランジスタのソース部は、メモリセル拡散マスクパターン21によってメモリセルアレイ部20内をロウ方向に接続されており、ロウデコーダ部2で接地電位に接続されている。このメモリセル拡散マスクパターン21の形状を示した図が、図8である。

【0005】

図8に示すように、従来のメモリセル拡散マスクパターンはロウ方向に櫛形の構成をしており、メモリセルアレイ部20内をカラム方向に繰り返し配置されている。このような構成で2ビットのメモリセルトランジスタを1つの拡散マスクパターンで構成し、ドレインノードコンタクト24の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成をとっている。

【0006】

さらに、図9は、図7のメモリセルアレイ部20の一部を取り出して示した図であり、2ビット櫛形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン21とメモリセルトランジスタのゲートに接続されたワード線(n)22a、ワード線(n−1)22bと前記メモリセル拡散マスクパターン21で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト24により接続されたビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23c、により構成されている。

【0007】

例えば制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)22aが選択された場合、全てのメモリセルトランジスタのソースは櫛形メモリセル拡散パターンにより拡散層で接続されており、ソース電位である接地電位となっており、ワード線(n)22aの選択により、櫛形メモリセル拡散マスクパターン21の上部のメモリセルトランジスタがONし、あらかじめドレインノードコンタクト24が配置されているメモリセルのビット線(m)23bがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m)23bの選択に応じて読み出され、あらかじめドレインノードコンタクト24が配置されていないメモリセルのビット線(m−1)23aやビット線(m+1)23cは、メモリセルトランジスタはONするが、ドレインノードコンタクト24が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(m−1)23aやビット線(m+1)23cが選択された場合に読み出す。

【0008】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)22bが選択された場合も同様に全てのメモリセルトランジスタのソースは櫛形メモリセル拡散パターンにより拡散層で接続されており、ソース電位である接地電位となっており、ワード線(n−1)22bの選択により、櫛形メモリセル拡散マスクパターン21の下部のメモリセルトランジスタがONし、あらかじめドレインノードコンタクト24が配置されているメモリセルのビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23cがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m−1)23a、ビット線(m)23b、ビット線(m+1)23cの選択に応じて読み出される。

【0009】

以上のようにメモリセル拡散マスクパターンは拡散層でロウ方向にソースノードを共通化する2ビット櫛形パターンで構成されている。

【特許文献1】特開2004−342261号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上記従来の半導体記憶装置において、メモリセル拡散マスクパターンはメモリセルのソースが共通であることから、拡散層で配線する2ビット櫛形拡散マスクパターンで構成されている。

【0011】

しかしながら、このような構成である限りは、近年の微細化に伴い、櫛形パターン形成が困難になってきており、メモリセル形状のアンバランスや形状不良といった歩留低下の原因となってきている。

【0012】

したがって、本発明の目的は、メモリセル拡散マスクパターンの形状容易化により、メモリセル拡散マスクパターン形成の安定化及び歩留向上を図る半導体記憶装置およびROMデータパターンの発生方法を提供することである。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明の請求項1記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターンで構成し、前記拡散マスクパターンがメモリセルアレイ上に配列され、前記拡散マスクパターンで形成されるメモリセルのソースコモン配線をメタル配線にした。

【0014】

すなわち、従来の2ビット櫛形メモリセル拡散マスクパターンを2ビット矩形拡散マスクパターンとし、メモリセルのソースコモン配線を拡散層からメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化するものとする。

【0015】

請求項2記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルアレイ上の最外周の拡散マスクパターンは、実メモリセルではなくダミーパターンとして形成した。

【0016】

請求項3記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタのソース電位である電源線に接続されている。

【0017】

請求項4記載の半導体記憶装置は、隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線に接続されている。

【0018】

請求項5記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタのソース電位である電源線は最下層である第1メタル配線層で構成されている。

【0019】

請求項6記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記電源線は最下層である第1メタル配線層で構成されている。

【0020】

請求項7記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線は最下層である第1メタル配線層で構成されている。

【0021】

請求項8記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記内部ドライブ信号線は最下層である第1メタル配線層で構成されている。

【0022】

請求項9記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0023】

請求項10記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0024】

請求項11記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている。

【0025】

請求項12記載の半導体記憶装置は、請求項9記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0026】

請求項13記載の半導体記憶装置は、請求項10記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0027】

請求項14記載の半導体記憶装置は、請求項11記載の半導体記憶装置において、前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い。

【0028】

請求項15記載の半導体記憶装置は、請求項1記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0029】

請求項16記載の半導体記憶装置は、請求項3記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0030】

請求項17記載の半導体記憶装置は、請求項4記載の半導体記憶装置において、ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する。

【0031】

請求項18記載の半導体記憶装置は、請求項15記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0032】

請求項19記載の半導体記憶装置は、請求項16記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0033】

請求項20記載の半導体記憶装置は、請求項17記載の半導体記憶装置において、前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした。

【0034】

請求項21記載のROMデータパターンの発生方法は、請求項18記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してROMデータパターンとして生成する。

【0035】

請求項22記載のROMデータパターンの発生方法は、請求項19記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成する。

【0036】

請求項23記載のROMデータパターンの発生方法は、請求項20記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成する。

【発明の効果】

【0037】

本発明の請求項1記載の半導体記憶装置によれば、2ビットのメモリセルトランジスタを、1つの拡散マスクパターンで構成し、拡散マスクパターンがメモリセルアレイ上に配列され、ソースコモン配線をメタル配線にすることにより、メモリセル拡散マスクパターンの形状を容易化し、パターン形成を容易化する効果を得ることができる。またパターン形成の容易化により、歩留を向上する効果を得ることができる。

【0038】

請求項2記載の半導体記憶装置によれば、メモリセルアレイ部のメモリセル拡散マスクパターンの最外周の2ビット拡散マスクパターンをROMの実メモリセルとして使用せず、ダミーパターンとすることにより、実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持する。パターン連続性の維持により、実メモリセルの拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0039】

請求項3記載の半導体記憶装置によれば、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、電源線に共通接続するため1つのコンタクトマスクパターンを用いることでレイアウト面積増大を防ぐ効果が得られる。

【0040】

請求項4記載の半導体記憶装置によれば、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、ソース電位を制御する内部ドライブ信号線に共通接続するため1つのコンタクトマスクパターンを用いることでレイアウト面積増大を防ぐ効果が得られる。

【0041】

請求項5及び請求項6記載の半導体記憶装置によれば、メモリセルトランジスタのソース電位である電源線をメタル配線層の最下層である第1メタル配線層で構成することにより接地電源を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作の効果が得られる。

【0042】

請求項7及び請求項8記載の半導体記憶装置によれば、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線をメタル配線層の最下層である第1メタル配線層で構成することにより任意のソース電位を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作の効果が得られる。

【0043】

請求項9及び請求項10及び請求項11記載の半導体記憶装置によれば、メモリセルトランジスタのソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターンを下層部に構成することによって、メモリセル拡散マスクパターンの連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0044】

請求項12記載の半導体記憶装置によれば、請求項9記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0045】

請求項13記載の半導体記憶装置によれば、請求項10記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0046】

請求項14記載の半導体記憶装置によれば、請求項11記載の半導体記憶装置のソース電位裏打ち用配線領域の下層部に形成されるトランジスタのソース及びドレインはソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0047】

請求項15の半導体記憶装置によれば、請求項1記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0048】

請求項16の半導体記憶装置によれば、請求項3記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0049】

請求項17の半導体記憶装置によれば、請求項4記載の半導体装置で、メモリセルトランジスタのドレインコンタクトパターンの有無でROMデータの“1”、“0”の区分を行うことで容易にROMデータパターンを生成する効果を得ることができる。

【0050】

請求項18及び請求項21記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項15に記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【0051】

請求項19及び請求項22記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項16に記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【0052】

請求項20及び請求項23記載の半導体記憶装置及びROMデータパターンの発生方法によれば、請求項17記載の半導体記憶装置で隣り合う2ビットのメモリセルトランジスタのドレインノードコンタクトが2ビット共存在しない場合に共通ソースノードコンタクトパターンを配置せず、ソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【発明を実施するための最良の形態】

【0053】

以下、本発明の実施の形態を図面を参照しながら説明する。

【0054】

本発明の第1の実施形態を図1〜図3に基づいて説明する。図1は本発明の第1の実施の形態に係る半導体記憶装置の構成を示すレイアウト図、図2は図1のメモリセルアレイ部におけるメモリセル拡散マスクパターン形状を示すレイアウト図である。

【0055】

本発明の第1の実施の形態に係る半導体記憶装置は、図1で示すように、メモリセル拡散マスクパターン5が矩形の形状で構成されるメモリセルアレイ部1、外部からのアドレス信号やチップイネーブル信号を制御する制御部3、制御部3で制御されたロウアドレス信号からワード線を選択するロウデコーダ部2、制御部3で制御されたカラムアドレス信号からビット線を選択するカラムデコーダ部4で構成される。ワード線6は、メモリセルトランジスタのゲート部に接続され、ビット線7は、メモリセルトランジスタのドレイン部にドレインノードコンタクト9によって接続されている。またメモリセルトランジスタのソース部は、ソース線8によってメモリセルアレイ部1内をロウ方向に接続されており、ロウデコーダ部2で接地電位に接続されている。このメモリセル拡散マスクパターン5の形状を示した図が、図2である。

【0056】

図2に示すように、メモリセル拡散マスクパターンは矩形の構成をしており、メモリセルアレイ部1内をロウ方向、カラム方向の両方向に繰り返し配置されている。このような構成で2ビットのメモリセルトランジスタを1つの拡散マスクパターンで構成し、ドレインノードコンタクト9の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成をとっている。

【0057】

さらに、図3は、図1のメモリセルアレイ部1の一部を取り出して示したレイアウト図であり、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8と、メモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7c、により構成されている。

【0058】

例えば制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)6aが選択された場合、3つの矩形メモリセル拡散マスクパターン5で2ビットの隣り合うメモリセルトランジスタが3組形成されており、全てのメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、3つの矩形メモリセル拡散マスクパターン5の上部のメモリセルトランジスタがワード線(n)6aの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(m)7bがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m)7bの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(m−1)7aやビット線(m+1)7cは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(m−1)7aやビット線(m+1)7cが選択された場合に読み出す。

【0059】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)6bが選択された場合も同様に全てのメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、3つの矩形メモリセル拡散マスクパターン5の下部のメモリセルトランジスタがワード線(n−1)6bの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cの選択に応じて読み出される。

【0060】

このように動作的には従来の半導体記憶装置と同様の動作が実現できる。

【0061】

ここで、メモリセル拡散マスクパターンの形状を比較してみると、従来の2ビット櫛形拡散マスクパターンに比べ、本実施形態の2ビット矩形拡散パターンは形状が容易化され、メモリセル拡散マスクパターン生成時の形状のアンバランスや形状不具合を起こし難いパターンとなっており、歩留向上を図ることが可能である。

【0062】

また、図1において、メモリセルアレイ部1の最外周の2ビット矩形拡散マスクパターンで生成されるメモリセルトランジスタをROMの実メモリセルとして使用せず、ソースに接地電位に接続されたダミーワード線11あるいはドレインに接地電位に接続されたダミービット線12に接続、あるいはその両方に接続することによってダミーセルとすることで最外周の2ビット矩形拡散マスクパターンをダミーパターンとする。こうすることにより、実メモリセルとして使用するメモリセル拡散マスクパターンのパターン連続性を維持し、実メモリセルの拡散マスクパターンのパターン形成精度を向上させることが可能である。

【0063】

また、図3において、ロウ方向のメモリセルトランジスタのソースコモン配線をメタル配線とし、電源線に共通接続するため、隣り合う2ビットのメモリセルトランジスタのソースに1つのコンタクトマスクパターンを用いることでソースコモン配線を接続できるため、レイアウト面積増大を防ぐ効果が得られる。

【0064】

さらに、図3において、メモリセルトランジスタのソースに接続されたソース線8の電源線をメタル配線層の最下層である第1メタル配線層で構成することにより接地電源を低抵抗でメモリセルトランジスタのソースに供給することが可能となり、安定したソース電位の供給が行われ、安定したメモリセルトランジスタ動作が可能である。このとき読み出しデータ線であるビット線(m−1)7a、ビット線(m)7b、ビット線(m+1)7cは第2メタル配線層か、あるいは更に上層の配線層で構成されている。

【0065】

また、本発明の実施の形態において、メモリセルトランジスタのソース電位を接地電位として説明したが、これに言及するものではなく、任意の電位に設定するために内部ドライブ信号線に接続した場合にも同様の構成及び効果を得ることができる。

【0066】

本発明の第2の実施形態を図4および図5に基づいて説明する。

【0067】

本発明の第2の実施の形態に係る半導体記憶装置は、本発明の第1の実施の形態に係る半導体装置において、図4に示すように、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8と、メモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと、前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線7と、読み出しデータ線であるビット線7の間にソース電位裏打ち用配線13とを配置した構成をとるものである。このソース電位裏打ち用配線13は複数の読み出しデータ線単位毎に配置されるものとする。このような構成をとることでメモリ容量が増加し、ロウ方向のソース線8の配線長が長くなることによる配線抵抗の増大を防ぎ、ソース電位の変動を低減し安定したソース電位を供給することができる。

【0068】

このソース電位裏打ち用配線領域においても図4に示すように、メモリセル拡散マスクパターン5を下層部に配置しており、メモリセルトランジスタを生成する構成になっているが、ソースノードコンタクト10及びドレインノードコンタクト9の配置により、ソース、ドレインともソース電位裏打ち用配線13と同電位に接続されるためダミーセルとして扱うことができる。こうすることによって、ソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5の連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果が得られる。

【0069】

また、図5は図4と同様にメモリ容量が増加し、ロウ方向のソース線8の配線長が長くなることによる配線抵抗の増大を防ぎ、ソース電位の変動を低減し安定したソース電位を供給するために、読み出しデータ線であるビット線7の間にソース電位裏打ち用配線13を配置し、このソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5を下層部に配置する構成である。ソース電位裏打ち用配線領域においてもメモリセル拡散マスクパターン5の連続性を維持し、拡散マスクパターンのパターン形成精度を向上させる効果に加え、図5で示すレイアウト構成においては、生成されるメモリセルトランジスタのソース及びドレインをソース電位裏打ち用配線とのコンタクトパターンを配置せず、接続しないことにより余分なワード線容量を削減する効果が得られる。

【0070】

本発明の第3の実施形態を図6に基づいて説明する。

【0071】

本発明の第3の実施の形態に係る半導体記憶装置は、本発明の第1の実施の形態に係る半導体装置においてメモリセルアレイ部1の一部を取り出して示したレイアウト図6で示すように、2ビット矩形拡散マスクパターンの形状を示すメモリセル拡散マスクパターン5と前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのソースにソースノードコンタクト10により接続されたソース線8とメモリセルトランジスタのゲートに接続されたワード線(n)6a、ワード線(n−1)6bと前記メモリセル拡散マスクパターン5で生成されるメモリセルトランジスタのドレインにドレインノードコンタクト9により接続されたビット線(s−1)7d、ビット線(s)7e、ビット線(s+1)7fにより構成されている。ROMデータの“0”、“1”の区分をドレインノードコンタクト9の有無で記憶データの“0”、“1”に対応させるコンタクト方式のマスクROMの構成であるため、隣り合う2ビットのメモリセルトランジスタのうちどちらか一方あるいは両方に“0”のROMデータが設定されている場合はメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8と接続するため、ソースノードコンタクト10を配置し、ビット線に“0”データを読み出すためにドレインノードコンタクト9を配置する必要がある。しかし、隣り合う2ビットのメモリセルトランジスタの両方とも“1”のROMデータが設定されている場合はソース電位をビット線に読み出す必要がなくプリチャージ電位のままであることから、ドレインノードコンタクト9だけでなくソースノードコンタクト10も配置する必要がない。

【0072】

例えば図6において、ドレインノードコンタクト9の有無により、ビット線(s−1)7dの下層に生成された2ビットのメモリセルトランジスタのうちワード線(n)6aがゲートに接続されている上側のメモリセルトランジスタは“1”データ、ワード線(n−1)6bがゲートに接続されている下側のメモリセルトランジスタは“0”データに設定されている。同様にビット線(s)7eの下層に生成された2ビットのメモリセルトランジスタは上下両方とも“1”データに設定され、ビット線(s+1)7fの下層に生成された2ビットのメモリセルトランジスタのうちワード線(n)6aがゲートに接続されている上側のメモリセルトランジスタは“0”データ、ワード線(n−1)6bがゲートに接続されている下側のメモリセルトランジスタは“1”データに設定されている。

【0073】

制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n)6aが選択された場合、3つの矩形メモリセル拡散マスクパターン5で2ビットの隣り合うメモリセルトランジスタが3組形成されており、左右2組のメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、真ん中のメモリセルトランジスタのソースはソースノードコンタクト10が配置されておらず、ソース線8と接続されていない。

【0074】

3つの矩形メモリセル拡散マスクパターン5の上部のメモリセルトランジスタがワード線(n)6aの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(s+1)7fがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(s+1)7fの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(s−1)7dやビット線(s)7eは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(s−1)7dやビット線(s)7eが選択された場合に読み出す。

【0075】

また制御部3で制御されたロウアドレス信号によってロウデコーダ部2でワード線(n−1)6bが選択された場合も同様に左右2組のメモリセルトランジスタのソースはロウデコーダ部で接地電位に接続されたソース線8とソースノードコンタクト10により接地電位に設定され、真ん中のメモリセルトランジスタのソースはソースノードコンタクト10が配置されておらず、ソース線8と接続されていない。

【0076】

3つの矩形メモリセル拡散マスクパターン5の下部のメモリセルトランジスタがワード線(n−1)6bの選択によりONし、あらかじめドレインノードコンタクト9が配置されているメモリセルのビット線(s−1)7dがソース電位である接地電位になり“0”データが制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でのビット線(s−1)7dの選択に応じて読み出され、あらかじめドレインノードコンタクト9が配置されていないメモリセルのビット線(s)7eやビット線(s+1)7fは、メモリセルトランジスタはONするが、ドレインノードコンタクト9が配置されていないため、ソース電位がビット線に伝わらず、プリチャージ電位のままであり、“1”データを制御部3で制御されたカラムアドレス信号によってカラムデコーダ部4でビット線(s)7eやビット線(s+1)7fが選択された場合に読み出す。

【0077】

以上のように隣り合う2ビットのメモリセルトランジスタの両方とも“1”のROMデータが設定されているビット線(s)7eも設定値どおり読み出すことが可能であるので、このような場合、ソースノードコンタクト10を配置する必要がない。こうすることによりソースノードコンタクト数を削減することでコンタクトの密集を防ぎ、コンタクトパターン形成を容易化して歩留向上の効果を得ることができる。

【産業上の利用可能性】

【0078】

本発明に係る半導体記憶装置は、メモリセルアレイ上のメモリセル拡散マスクパターンの容易化及びパターンの連続性の維持により、微細化するメモリセル拡散マスクパターン形成の容易化を実現する半導体記憶装置等として有用である。

【図面の簡単な説明】

【0079】

【図1】本発明の第1の実施の形態に係る半導体記憶装置の構成を示すレイアウト図である。

【図2】図1のメモリセルアレイ部のメモリセル拡散マスクパターン形状を示すレイアウト図である。

【図3】図1のメモリセルアレイ部の一部を示すレイアウト図である。

【図4】本発明の第2の実施の形態に係る半導体記憶装置の構成でメモリセルアレイ部の一部を示すレイアウト図である。

【図5】図4の構成で隣り合う2ビットのメモリセルトランジスタにドレインノードコンタクトが無い場合のレイアウト図である。

【図6】本発明の第3の実施の形態に係る半導体記憶装置の構成でメモリセルアレイ部の一部を示すレイアウト図である。

【図7】従来の半導体記憶装置の構成を示すレイアウト図である。

【図8】図7のメモリセルアレイ部のメモリセル拡散マスクパターン形状を示すレイアウト図である。

【図9】図7のメモリセルアレイ部の一部を示すレイアウト図である。

【符号の説明】

【0080】

1 メモリセルアレイ部

2 ロウデコーダ部

3 制御部

4 カラムデコーダ部

5 メモリセル拡散マスクパターン

6 ワード線

6a ワード線(n)

6b ワード線(n−1)

7 ビット線

7a ビット線(m−1)

7b ビット線(m)

7c ビット線(m+1)

7d ビット線(s−1)

7e ビット線(s)

7f ビット線(s+1)

8 ソース線

9 ドレインノードコンタク

10 ソースノードコンタクト

11 ダミーワード線

12 ダミービット線

13 ソース電位裏打ち用配線

20 メモリセルアレイ部

21 メモリセル拡散マスクパターン

22 ワード線

22a ワード線(n)

22b ワード線(n−1)

23 ビット線

23a ビット線(m−1)

23b ビット線(m)

23c ビット線(m+1)

24 ドレインノードコンタクト

【特許請求の範囲】

【請求項1】

隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターンで構成し、前記拡散マスクパターンがメモリセルアレイ上に配列され、前記拡散マスクパターンで形成されるメモリセルのソースコモン配線をメタル配線にしたことを特徴とする半導体記憶装置。

【請求項2】

メモリセルアレイ上の最外周の拡散マスクパターンは、実メモリセルではなくダミーパターンとして形成した請求項1記載の半導体記憶装置。

【請求項3】

隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタのソース電位である電源線に接続されていることを特徴とする半導体記憶装置。

【請求項4】

隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線に接続されていることを特徴とする半導体記憶装置。

【請求項5】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタのソース電位である電源線は最下層である第1メタル配線層で構成されている請求項1記載の半導体記憶装置。

【請求項6】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記電源線は最下層である第1メタル配線層で構成されている請求項3記載の半導体記憶装置。

【請求項7】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線は最下層である第1メタル配線層で構成されている請求項1記載の半導体記憶装置。

【請求項8】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記内部ドライブ信号線は最下層である第1メタル配線層で構成されている請求項4記載の半導体記憶装置。

【請求項9】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項1記載の半導体記憶装置。

【請求項10】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項3記載の半導体記憶装置。

【請求項11】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項4記載の半導体記憶装置。

【請求項12】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項9記載の半導体記憶装置。

【請求項13】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項10記載の半導体記憶装置。

【請求項14】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項11記載の半導体記憶装置。

【請求項15】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項1記載の半導体記憶装置。

【請求項16】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項3記載の半導体記憶装置。

【請求項17】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項4記載の半導体記憶装置。

【請求項18】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項15記載の半導体記憶装置。

【請求項19】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項16記載の半導体記憶装置。

【請求項20】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項17記載の半導体記憶装置。

【請求項21】

請求項18記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してROMデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【請求項22】

請求項19記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【請求項23】

請求項20記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【請求項1】

隣り合う2ビットのメモリセルトランジスタを、一つの拡散マスクパターンで構成し、前記拡散マスクパターンがメモリセルアレイ上に配列され、前記拡散マスクパターンで形成されるメモリセルのソースコモン配線をメタル配線にしたことを特徴とする半導体記憶装置。

【請求項2】

メモリセルアレイ上の最外周の拡散マスクパターンは、実メモリセルではなくダミーパターンとして形成した請求項1記載の半導体記憶装置。

【請求項3】

隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタのソース電位である電源線に接続されていることを特徴とする半導体記憶装置。

【請求項4】

隣り合う2ビットのメモリセルトランジスタのソースが共通接続され、ソースコモン配線をメタル配線とし、前記ソースコモン配線に接続される一つのコンタクトマスクパターンを用いて、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線に接続されていることを特徴とする半導体記憶装置。

【請求項5】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタのソース電位である電源線は最下層である第1メタル配線層で構成されている請求項1記載の半導体記憶装置。

【請求項6】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記電源線は最下層である第1メタル配線層で構成されている請求項3記載の半導体記憶装置。

【請求項7】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、メモリセルトランジスタの任意のソース電位を供給する内部ドライブ信号線は最下層である第1メタル配線層で構成されている請求項1記載の半導体記憶装置。

【請求項8】

メモリセルの読み出しデータ線は第2メタル配線層か、あるいは更に上層の配線層で構成し、前記内部ドライブ信号線は最下層である第1メタル配線層で構成されている請求項4記載の半導体記憶装置。

【請求項9】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項1記載の半導体記憶装置。

【請求項10】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項3記載の半導体記憶装置。

【請求項11】

複数の読み出しデータ線単位にソース電位の配線抵抗を低減し安定供給するためのソース電位裏打ち用配線である電源線を配列し、前記電源線領域においても前記拡散マスクパターンがアレイ上に配置されている請求項4記載の半導体記憶装置。

【請求項12】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項9記載の半導体記憶装置。

【請求項13】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項10記載の半導体記憶装置。

【請求項14】

前記電源線領域で生成されるメモリセルトランジスタと同一のトランジスタのソース及びドレインは配線層とのコンタクトパターンが無い請求項11記載の半導体記憶装置。

【請求項15】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項1記載の半導体記憶装置。

【請求項16】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項3記載の半導体記憶装置。

【請求項17】

ROMデータの1,0の区分を、前記メモリセルトランジスタのドレインコンタクトパターンの有無で構成する請求項4記載の半導体記憶装置。

【請求項18】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項15記載の半導体記憶装置。

【請求項19】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項16記載の半導体記憶装置。

【請求項20】

前記隣り合う2ビットのメモリセルトランジスタのドレインコンタクトが2ビットとも無いとき、共通ソースコンタクトパターンを無くした請求項17記載の半導体記憶装置。

【請求項21】

請求項18記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してROMデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【請求項22】

請求項19記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【請求項23】

請求項20記載の半導体記憶装置において、前記ソースコンタクトパターンの生成は、前記ROMデータのドレインコンタクトパターン生成時、演算してデータパターンとして生成することを特徴とするROMデータパターンの発生方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2007−27634(P2007−27634A)

【公開日】平成19年2月1日(2007.2.1)

【国際特許分類】

【出願番号】特願2005−211345(P2005−211345)

【出願日】平成17年7月21日(2005.7.21)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

【公開日】平成19年2月1日(2007.2.1)

【国際特許分類】

【出願日】平成17年7月21日(2005.7.21)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]