半導体記憶装置の製造方法

【課題】記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにする。

【解決手段】半導体記憶装置の製造方法は、記憶部300及び論理部301を有する基板101の上に、記憶部ゲート絶縁膜102及び第1の導電膜141を形成する工程よりも後に、第1の導電膜141及び記憶部ゲート絶縁膜102における論理部301の上に形成された部分を除去する。論理部ゲート絶縁膜111及び第2の導電膜147を形成する工程よりも後に記憶部300において第1の導電膜141を露出する。

【解決手段】半導体記憶装置の製造方法は、記憶部300及び論理部301を有する基板101の上に、記憶部ゲート絶縁膜102及び第1の導電膜141を形成する工程よりも後に、第1の導電膜141及び記憶部ゲート絶縁膜102における論理部301の上に形成された部分を除去する。論理部ゲート絶縁膜111及び第2の導電膜147を形成する工程よりも後に記憶部300において第1の導電膜141を露出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体記憶装置の製造方法に関し、特に半導体基板上に記憶部と論理部とを有する半導体記憶装置の製造方法に関する。

【背景技術】

【0002】

半導体基板上に、シリコン酸化膜とシリコン窒化膜との積層膜(ONO膜)を用いたメモリトランジスタが形成された記憶部と、相補型金属酸化膜半導体(CMOS)が形成された論理部とが混載された半導体記憶装置は、高密度、高信頼性のデバイスとして注目されている(例えば、特許文献1を参照。)。ONO膜を用いたメモリトランジスタは、ONO膜中の窒化シリコン膜に電荷をトラップする。窒化シリコン膜中にトラップした電荷はシリコン基板及びゲート電極に放出されないようにでき、メモリトランジスタの電荷保持特性を向上することができる。また、ソース側及びドレイン側の両方に電荷がトラップされるようにできるため、1素子に複数の情報を記憶でき、記憶装置を高密度化することが可能となる。

【0003】

ONO膜を用いたメモリトランジスタとCMOSとが混載された半導体記憶装置を形成する場合には、ONO膜を選択的に除去する必要がある。例えば、まず基板上の全面にONO膜を形成した後、論理部においてONO膜を選択的に除去し、ONO膜を除去した論理部の上にCMOSのゲート絶縁膜を形成する。論理部においてONO膜を除去しゲート絶縁膜を形成する際には、記憶部において窒化膜を含む保護膜によりONO膜を覆う。これにより、論理部においてONO膜を選択的に除去でき、CMOSのゲート絶縁膜を形成する際に記憶においてONO膜が酸化されることを防ぐことができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−77220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、前記従来の半導体記憶装置の製造方法には以下のような問題がある。ONO膜の上に形成された窒化膜を含む保護膜は、熱燐酸により除去する。熱燐酸をエッチャントとして用いることにより、窒化膜と酸化膜との選択比を10程度にまですることができるため、保護膜を選択的に除去することが期待される。しかし、熱燐酸の酸化膜に対するエッチングレートは、熱燐酸中に含まれるシリコンの濃度によって変動し、熱燐酸中に含まれるシリコンの濃度が低いほどエッチングレートが高くなる。従って、交換直後の新しいエッチャントと、累積エッチング時間が長く、酸化膜が溶け込みシリコンの濃度が高くなったエッチャントでは、酸化膜のエッチングレートが異なる。

【0006】

保護膜を除去することにより、ONO膜の上層の酸化膜が露出する。また、一般的に論理部には膜厚が異なる複数のゲート絶縁膜を形成するため、保護膜の除去はゲート絶縁膜が露出した状態で行われる。このため、保護膜を除去する際には、ONO膜及びゲート絶縁膜のエッチングも生じてしまう。さらに、エッチャントの状態により酸化膜のエッチングレートが変動するため、ONO膜の膜厚及びゲート絶縁膜の膜厚にばらつきが生じる。その結果、記憶部及び論理部においてトランジスタの閾値及び駆動電流が変動する等の、電気的特性のばらつき及び信頼性の低下が生じる。

【0007】

本発明は、前記の問題を解決し、記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにすることを目的とする。

【課題を解決するための手段】

【0008】

前記の目的を達成するため、本発明は半導体記憶装置の製造方法を、記憶部の保護膜をコントロールゲート電極となる導電膜の上に形成し、記憶部の保護膜を除去する前に論理部のゲート電極となる導電膜を形成する構成とする。

【0009】

本発明に係る半導体記憶装置の製造方法は、記憶部及び論理部を有する基板の上に、記憶部ゲート絶縁膜を形成する工程(a)と、工程(a)よりも後に、基板の上に第1の導電膜を形成する工程(b)と、第1の導電膜及び記憶部ゲート絶縁膜における論理部の上に形成された部分を除去する工程(c)と、工程(c)よりも後に、基板の上に論理部ゲート絶縁膜を形成する工程(d)と、工程(d)よりも後に、基板の上に第2の導電膜を形成する工程(e)と、工程(e)よりも後に、記憶部において第1の導電膜を露出する工程(f)と、工程(f)よりも後に、第1の導電膜を選択的に除去して記憶部においてワード線を形成する工程(g)と、工程(f)よりも後に、第2の導電膜を選択的に除去して論理部において論理部ゲート電極を形成する工程(h)とを備えている。

【0010】

本発明の半導体記憶装置の製造方法は、第1の導電膜を形成する工程よりも後に論理部の上に形成された記憶部ゲート絶縁膜を除去する。このため、ウェットエッチングを用いる工程において、記憶部ゲート絶縁膜は第1の導電膜に覆われている。従って、記憶部ゲート絶縁膜の膜厚がウェットエッチングにより変動することはない。また、第2の導電膜を形成する工程よりも後に記憶部において第1の導電膜を露出する。このため、ウェットエッチングを用いる工程において論理部ゲート絶縁膜は第2の導電膜に覆われている。従って、論理部ゲート絶縁膜の膜厚がウェットエッチングにより変動することはない。その結果、記憶部及び論理部においてトランジスタの閾値及び駆動電流が変動する等の、電気的特性のばらつき及び信頼性の低下を抑えることができる。また、記憶部ゲート絶縁膜及び論理部ゲート絶縁膜に化学気相堆積法により堆積した酸化シリコン膜を用いることが可能となるので、微細化にも有用である。

【0011】

本発明の半導体記憶装置の製造方法において、論理部ゲート絶縁膜は、第1のゲート絶縁膜及び第2のゲート絶縁膜を含み、論理部は、第1領域と第2領域とを含み、論理部ゲート電極は、第1のゲート電極及び第2のゲート電極を含み、工程(d)は、基板の上に第1のゲート絶縁膜を形成する工程(d1)と、第1のゲート絶縁膜における第1領域の上に形成された部分を残存させ、第2領域の上に形成された部分を選択的に除去する工程(d2)と、工程(d2)よりも後に、第2領域の上に第2のゲート絶縁膜を形成する工程(d3)とを含み、工程(h)において、第1領域の上に第1のゲート電極を形成し、第2領域の上に第2のゲート電極を形成してもよい。

【0012】

本発明の半導体記憶装置の製造方法は、工程(b)よりも前に、記憶部においてワード線と交差する方向に延びるビット線拡散層を形成する工程(i)をさらに備えていてもよい。

【0013】

本発明の半導体記憶装置の製造方法は、工程(i)よりも後に且つ工程(b)よりも前に、ビット線拡散層の上にビット線絶縁膜を形成する工程(j)をさらに備えていてもよい。

【0014】

本発明の半導体記憶装置の製造方法は、工程(h)よりも後に、論理部において論理部ゲート電極をマスクとして不純物注入を行い、論理部ゲート電極の両側方にソース拡散層及びドレイン拡散層を形成する工程(k)をさらに備えていてもよい。

【0015】

本発明の半導体記憶装置の製造方法において、ワード線及び論理部ゲート電極は、多結晶シリコン膜からなり、ワード線は、結晶粒塊のサイズが論理部ゲート電極よりも大きい状態であってもよい。

【0016】

本発明の半導体記憶装置の製造方法において、記憶部ゲート絶縁膜は、ONO膜とすればよい。

【発明の効果】

【0017】

本発明に係る半導体記憶装置の製造方法によれば、記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できる。

【図面の簡単な説明】

【0018】

【図1】一実施形態に係る半導体記憶装置を示す平面図である。

【図2】一実施形態に係る半導体記憶装置を示す断面図である。

【図3】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図4】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図5】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図6】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図7】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図8】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

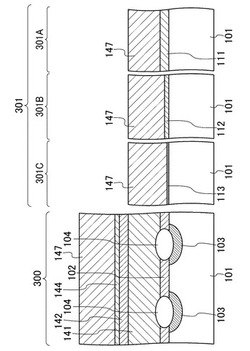

【図9】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図10】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図11】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図12】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図13】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図14】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【発明を実施するための形態】

【0019】

本実施形態の半導体記憶装置は、図1及び2に示すように、記憶部300と論理部301とを有している。記憶部300には、メモリ素子が形成されている。具体的には、シリコン等からなる半導体基板101の上部に、不純物拡散層であるビット線拡散層103が第1の方向に延びるように形成されている。半導体基板101の上には酸化シリコン(例えば、SiO2)膜、窒化シリコン(例えば、Si3N4)膜及び酸化シリコン膜が順次積層されたONO膜102が形成されている。ONO膜102の上には、コントロールゲート電極を含むワード線105が形成されている。ワード線105は、第1の方向と交差する第2の方向に延びる。ビット線拡散層103とワード線105とは、ビット線拡散層103の上に形成されたビット線絶縁膜104により絶縁されている。ONO膜102は、電荷をトラップする記憶部ゲート絶縁膜である。

【0020】

論理部301には、金属酸化膜半導体電界効果トランジスタ(MOSFET)が形成されている。論理部301の第1領域301Aには、動作電圧が12V程度であり、フラッシュメモリを動作させる昇圧回路等を構成する高耐圧MOSFETが形成されている。第2領域301Bには、動作電圧が5V程度であり、主に入出力(I/O)回路等を構成する中耐圧MOSFETが形成されている。第3領域301Cには、動作電圧が2V程度であり、中央制御ユニット(CPU)等を構成する低耐圧MOSFETが形成されている。

【0021】

高耐圧MOSFETは、半導体基板101の上に、第1のゲート絶縁膜111を介在させて形成された第1のゲート電極121と、半導体基板101における第1のゲート電極121の側方に形成された第1のソースドレイン拡散層131とを有している。

【0022】

中耐圧MOSFETは、半導体基板101の上に、第2のゲート絶縁膜112を介在させて形成された第2のゲート電極122と、半導体基板101における第2のゲート電極122の側方に形成された第2のソースドレイン拡散層132とを有している。

【0023】

低耐圧MOSFETは、半導体基板101の上に、第3のゲート絶縁膜113を介在させて形成された第3のゲート電極123と、半導体基板101における第3のゲート電極123の側方に形成された第3のソースドレイン拡散層133とを有している。

【0024】

以下に、本実施形態の半導体記憶装置の製造方法について図面を参照して説明する。まず、図3に示すように、シリコン基板等からなる半導体基板101上の全面に記憶部ゲート絶縁膜となるONO膜102を形成する。ONO膜102の形成はまず、熱酸化法により膜厚が約4nmの第1の酸化シリコン膜を形成した後、第1の酸化シリコン膜の上に化学気相堆積(CVD)法により膜厚が約20nmの窒化シリコン膜を形成する。続いて、窒化シリコン膜の上に熱酸化法により膜厚が約20nmの第2の酸化シリコン膜を形成すればよい。第2の酸化シリコン膜を形成した後の窒化シリコン膜の膜厚は5nm程度となる。なお、第2の酸化シリコン膜は、熱酸化法による酸化シリコン膜とCVD法による酸化シリコン膜との積層構造としてもよい。続いて、記憶部300において、ビット線拡散層を形成する領域の上に形成されたONO膜102をドライエッチングにより除去する。この後、加速電圧が20keVでドーズ量が2.0×1015/cm2である注入条件により、記憶部300におけるONO膜102を除去した領域に砒素(As)イオンを注入して、ビット線拡散層103を形成する。続いて、熱酸化法によりビット線拡散層103の上面を酸化して膜厚が約35nmのビット線絶縁膜104を形成する

次に、図4に示すように記憶部300及び論理部301の上に、CVD法により膜厚が約200nmの多結晶シリコン膜からなる第1の導電膜141を堆積する。

【0025】

次に、図5に示すように第1の導電膜141の上に、CVD法により膜厚が約20nmの窒化シリコンからなる保護膜142を堆積する。続いて、フォトリソグラフィ法により、論理部301が開口するマスクパターン143を形成する。形成したマスクパターン143を用いて、論理部301において保護膜142及び第1の導電膜141を順次ドライエッチングにより除去する。

【0026】

次に、図6に示すように、マスクパターン143を除去した後、記憶部300における保護膜142をマスクとして、論理部301においてONO膜102の第2の酸化シリコン膜をウェットエッチングにより除去する。続いて、膜厚が約5nmの窒化シリコン膜を熱燐酸によるウェットエッチングにより除去する。このとき、オーバーエッチング量を調整し、記憶部300において保護膜142を残存させる。続いて、露出した第1の酸化シリコン膜をウェットエッチングにより除去する。

【0027】

次に、図7に示すように、論理部301において露出した半導体基板101上に膜厚が約17nm〜23nmの第1のゲート絶縁膜111を熱酸化法により形成する。なお、第1のゲート絶縁膜111は、CVD法により酸化シリコン膜を堆積した後、堆積した酸化シリコン膜の下側の半導体基板101に熱酸化膜を形成して積層構造としてもよい。また、熱酸化膜を形成した後、熱酸化膜の上にCVD法により酸化シリコン膜を堆積して積層構造としてもよい。第1のゲート絶縁膜111を形成する際に、記憶部300において保護膜142の上部に第3の酸化シリコン膜144が形成される。

【0028】

次に、図8に示すように、フォトリソグラフィ法により、論理部301の第2領域301Bが開口するマスクパターン145を形成し、形成したマスクパターン145を用いて、第2領域301Bにおいて第1のゲート絶縁膜111をウェットエッチングにより除去する。

【0029】

次に、図9に示すように、マスクパターン145を除去した後、第2領域301Bの上に膜厚が約13nm〜17nmの第2のゲート絶縁膜112を熱酸化法により形成する。なお、第2のゲート絶縁膜112は、CVD法により酸化シリコン膜を堆積した後、酸化シリコン膜の下側の半導体基板101に熱酸化膜を形成して積層構造としてもよい。また、熱酸化膜を形成した後、熱酸化膜の上にCVD法により酸化シリコンを堆積して積層構造としてもよい。CVD法により酸化シリコン膜を堆積する場合には、記憶部300及び第1領域301A及び第3領域301Cの上にも酸化シリコン膜が堆積する。

【0030】

次に、図10に示すように、フォトリソグラフィ法により、第3領域301Cが開口するマスクパターン146を形成し、形成したマスクパターン146を用いて、第3領域301Cの上に形成された第1のゲート絶縁膜111をウェットエッチングにより除去する。なお、第2のゲート絶縁膜112を形成する際に、CVD法により酸化シリコン膜を堆積した場合には、第3領域301Cにおいて第1のゲート絶縁膜111の上に酸化シリコン膜が堆積している。このため、第1のゲート絶縁膜111と共に堆積した酸化シリコン膜も同時に除去する。

【0031】

次に、図11に示すように、マスクパターン146を除去した後、第3領域301Cの上に膜厚が約2nm〜5nmの第3のゲート絶縁膜113を熱酸化法により形成する。続いて、半導体基板101上の全面に、CVD法により膜厚が約200nmの多結晶シリコン膜からなる第2の導電膜147を堆積する。

【0032】

次に、図12に示すように、フォトリソグラフィ法により、記憶部300が開口するマスクパターン148を形成し、形成したマスクパターン148を用いて、記憶部300において第2の導電膜147をドライエッチングにより除去する。

【0033】

次に、図13に示すように、マスクパターン148を除去した後、記憶部300において第3の酸化シリコン膜144をウェットエッチングにより除去する。続いて、保護膜142を熱燐酸によるウェットエッチングにより除去する。

【0034】

次に、図14に示すように、第1の導電膜141及び第2の導電膜147を選択的にエッチング除去することにより、メモリ素子のワード線105、高耐圧MOSFET用の第1のゲート電極121、中耐圧MOSFET用の第2のゲート電極122及び低耐圧MOSFET用の第3のゲート電極123を形成する。高耐圧MOSFETのゲート長は約0.8μm、低耐圧MOSFETのゲート長は約0.2μm、中耐圧MOSFETのゲート長は約0.6μmとなるように形成する。続いて、イオン注入を行い、高耐圧MOSFET用の第1のソースドレイン拡散層131、中耐圧MOSFET用の第2のソースドレイン拡散層132及び低耐圧MOSFET用の第3のソースドレイン拡散層133を形成する。

【0035】

この後、シリサイド層、金属配線、保護膜及びボンディングパッド等を形成することにより半導体記憶装置が完成する。

【0036】

なお、記憶部300に形成された第1の導電膜141には第1のゲート絶縁膜111、第2のゲート絶縁膜112及び第3のゲート絶縁膜113を形成する際に850℃〜1000℃程度の熱が加わる。このため、ワード線105である多結晶シリコン膜の結晶粒塊(グレイン)の大きさは、第1のゲート電極121〜第3のゲート電極123である多結晶シリコン膜よりも大きい。

【0037】

本実施形態の半導体記憶装置の製造方法は、ONO膜102、第1のゲート絶縁膜111及び第2のゲート絶縁膜112が露出した状態で、熱燐酸によるウェットエッチング処理を行わない。このため、ONO膜102、第1のゲート絶縁膜111及び第2のゲート絶縁膜112の膜厚のばらつきを0.5nm〜1.5nm(3%〜10%)程度低減することができる。その結果、メモリ素子及びMOSFETの閾値電圧及び駆動電流等の変動並びに各種膜における信頼性の変動を低減することができる。

【0038】

素子の微細化に伴いシリコン基板中の応力が大きくなると結晶欠陥に起因したリークが誘発される。シリコン基板中の応力を低減するためには、ゲート絶縁膜をCVD法により堆積した酸化シリコン膜とすることが非常に有効である。しかし、CVD法により堆積した酸化シリコン膜は熱酸化法により形成した酸化シリコン膜と比べて熱燐酸による膜減りが大きい。このため、従来はゲート絶縁膜材料として積極的に使用することができなかった。しかし、本実施形態の半導体記憶装置の製造方法は、ゲート絶縁膜が露出した状態で熱燐酸によるエッチングを行わない。このため、CVD法により形成した酸化シリコン膜をゲート絶縁膜に用いても、膜減りの問題が発生しない。従って、本実施形態の半導体記憶装置の製造方法は、半導体記憶装置の微細化にも有用である。

【0039】

なお、本実施形態では、論理部にゲート絶縁膜の膜厚が異なる3種類のMOSFETが形成されている例について説明した。しかし、MOSFETの種類は1種類であっても、2種類以上であっても、同様の効果が得られる。

【産業上の利用可能性】

【0040】

本発明に係る半導体記憶装置の製造方法は、半導体記憶装置の電気的特性のばらつき及び信頼性の低下を回避でき、特に半導体基板上に記憶部と論理部とを有する不揮発性半導体記憶装置の製造方法等として有用である。

【符号の説明】

【0041】

101 半導体基板

102 ONO膜

103 ビット線拡散層

104 ビット線絶縁膜

105 ワード線

111 第1のゲート絶縁膜

112 第2のゲート絶縁膜

113 第3のゲート絶縁膜

121 第1のゲート電極

122 第2のゲート電極

123 第3のゲート電極

131 第1のソースドレイン拡散層

132 第2のソースドレイン拡散層

133 第3のソースドレイン拡散層

141 第1の導電膜

142 保護膜

143 マスクパターン

144 酸化シリコン膜

145 マスクパターン

146 マスクパターン

147 第2の導電膜

148 マスクパターン

300 記憶部

301 論理部

301A 第1領域

301B 第2領域

301C 第3領域

【技術分野】

【0001】

本発明は、半導体記憶装置の製造方法に関し、特に半導体基板上に記憶部と論理部とを有する半導体記憶装置の製造方法に関する。

【背景技術】

【0002】

半導体基板上に、シリコン酸化膜とシリコン窒化膜との積層膜(ONO膜)を用いたメモリトランジスタが形成された記憶部と、相補型金属酸化膜半導体(CMOS)が形成された論理部とが混載された半導体記憶装置は、高密度、高信頼性のデバイスとして注目されている(例えば、特許文献1を参照。)。ONO膜を用いたメモリトランジスタは、ONO膜中の窒化シリコン膜に電荷をトラップする。窒化シリコン膜中にトラップした電荷はシリコン基板及びゲート電極に放出されないようにでき、メモリトランジスタの電荷保持特性を向上することができる。また、ソース側及びドレイン側の両方に電荷がトラップされるようにできるため、1素子に複数の情報を記憶でき、記憶装置を高密度化することが可能となる。

【0003】

ONO膜を用いたメモリトランジスタとCMOSとが混載された半導体記憶装置を形成する場合には、ONO膜を選択的に除去する必要がある。例えば、まず基板上の全面にONO膜を形成した後、論理部においてONO膜を選択的に除去し、ONO膜を除去した論理部の上にCMOSのゲート絶縁膜を形成する。論理部においてONO膜を除去しゲート絶縁膜を形成する際には、記憶部において窒化膜を含む保護膜によりONO膜を覆う。これにより、論理部においてONO膜を選択的に除去でき、CMOSのゲート絶縁膜を形成する際に記憶においてONO膜が酸化されることを防ぐことができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−77220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、前記従来の半導体記憶装置の製造方法には以下のような問題がある。ONO膜の上に形成された窒化膜を含む保護膜は、熱燐酸により除去する。熱燐酸をエッチャントとして用いることにより、窒化膜と酸化膜との選択比を10程度にまですることができるため、保護膜を選択的に除去することが期待される。しかし、熱燐酸の酸化膜に対するエッチングレートは、熱燐酸中に含まれるシリコンの濃度によって変動し、熱燐酸中に含まれるシリコンの濃度が低いほどエッチングレートが高くなる。従って、交換直後の新しいエッチャントと、累積エッチング時間が長く、酸化膜が溶け込みシリコンの濃度が高くなったエッチャントでは、酸化膜のエッチングレートが異なる。

【0006】

保護膜を除去することにより、ONO膜の上層の酸化膜が露出する。また、一般的に論理部には膜厚が異なる複数のゲート絶縁膜を形成するため、保護膜の除去はゲート絶縁膜が露出した状態で行われる。このため、保護膜を除去する際には、ONO膜及びゲート絶縁膜のエッチングも生じてしまう。さらに、エッチャントの状態により酸化膜のエッチングレートが変動するため、ONO膜の膜厚及びゲート絶縁膜の膜厚にばらつきが生じる。その結果、記憶部及び論理部においてトランジスタの閾値及び駆動電流が変動する等の、電気的特性のばらつき及び信頼性の低下が生じる。

【0007】

本発明は、前記の問題を解決し、記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにすることを目的とする。

【課題を解決するための手段】

【0008】

前記の目的を達成するため、本発明は半導体記憶装置の製造方法を、記憶部の保護膜をコントロールゲート電極となる導電膜の上に形成し、記憶部の保護膜を除去する前に論理部のゲート電極となる導電膜を形成する構成とする。

【0009】

本発明に係る半導体記憶装置の製造方法は、記憶部及び論理部を有する基板の上に、記憶部ゲート絶縁膜を形成する工程(a)と、工程(a)よりも後に、基板の上に第1の導電膜を形成する工程(b)と、第1の導電膜及び記憶部ゲート絶縁膜における論理部の上に形成された部分を除去する工程(c)と、工程(c)よりも後に、基板の上に論理部ゲート絶縁膜を形成する工程(d)と、工程(d)よりも後に、基板の上に第2の導電膜を形成する工程(e)と、工程(e)よりも後に、記憶部において第1の導電膜を露出する工程(f)と、工程(f)よりも後に、第1の導電膜を選択的に除去して記憶部においてワード線を形成する工程(g)と、工程(f)よりも後に、第2の導電膜を選択的に除去して論理部において論理部ゲート電極を形成する工程(h)とを備えている。

【0010】

本発明の半導体記憶装置の製造方法は、第1の導電膜を形成する工程よりも後に論理部の上に形成された記憶部ゲート絶縁膜を除去する。このため、ウェットエッチングを用いる工程において、記憶部ゲート絶縁膜は第1の導電膜に覆われている。従って、記憶部ゲート絶縁膜の膜厚がウェットエッチングにより変動することはない。また、第2の導電膜を形成する工程よりも後に記憶部において第1の導電膜を露出する。このため、ウェットエッチングを用いる工程において論理部ゲート絶縁膜は第2の導電膜に覆われている。従って、論理部ゲート絶縁膜の膜厚がウェットエッチングにより変動することはない。その結果、記憶部及び論理部においてトランジスタの閾値及び駆動電流が変動する等の、電気的特性のばらつき及び信頼性の低下を抑えることができる。また、記憶部ゲート絶縁膜及び論理部ゲート絶縁膜に化学気相堆積法により堆積した酸化シリコン膜を用いることが可能となるので、微細化にも有用である。

【0011】

本発明の半導体記憶装置の製造方法において、論理部ゲート絶縁膜は、第1のゲート絶縁膜及び第2のゲート絶縁膜を含み、論理部は、第1領域と第2領域とを含み、論理部ゲート電極は、第1のゲート電極及び第2のゲート電極を含み、工程(d)は、基板の上に第1のゲート絶縁膜を形成する工程(d1)と、第1のゲート絶縁膜における第1領域の上に形成された部分を残存させ、第2領域の上に形成された部分を選択的に除去する工程(d2)と、工程(d2)よりも後に、第2領域の上に第2のゲート絶縁膜を形成する工程(d3)とを含み、工程(h)において、第1領域の上に第1のゲート電極を形成し、第2領域の上に第2のゲート電極を形成してもよい。

【0012】

本発明の半導体記憶装置の製造方法は、工程(b)よりも前に、記憶部においてワード線と交差する方向に延びるビット線拡散層を形成する工程(i)をさらに備えていてもよい。

【0013】

本発明の半導体記憶装置の製造方法は、工程(i)よりも後に且つ工程(b)よりも前に、ビット線拡散層の上にビット線絶縁膜を形成する工程(j)をさらに備えていてもよい。

【0014】

本発明の半導体記憶装置の製造方法は、工程(h)よりも後に、論理部において論理部ゲート電極をマスクとして不純物注入を行い、論理部ゲート電極の両側方にソース拡散層及びドレイン拡散層を形成する工程(k)をさらに備えていてもよい。

【0015】

本発明の半導体記憶装置の製造方法において、ワード線及び論理部ゲート電極は、多結晶シリコン膜からなり、ワード線は、結晶粒塊のサイズが論理部ゲート電極よりも大きい状態であってもよい。

【0016】

本発明の半導体記憶装置の製造方法において、記憶部ゲート絶縁膜は、ONO膜とすればよい。

【発明の効果】

【0017】

本発明に係る半導体記憶装置の製造方法によれば、記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できる。

【図面の簡単な説明】

【0018】

【図1】一実施形態に係る半導体記憶装置を示す平面図である。

【図2】一実施形態に係る半導体記憶装置を示す断面図である。

【図3】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図4】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図5】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図6】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図7】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図8】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図9】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図10】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図11】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図12】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図13】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【図14】一実施形態に係る半導体記憶装置の製造方法の一工程を示す断面図である。

【発明を実施するための形態】

【0019】

本実施形態の半導体記憶装置は、図1及び2に示すように、記憶部300と論理部301とを有している。記憶部300には、メモリ素子が形成されている。具体的には、シリコン等からなる半導体基板101の上部に、不純物拡散層であるビット線拡散層103が第1の方向に延びるように形成されている。半導体基板101の上には酸化シリコン(例えば、SiO2)膜、窒化シリコン(例えば、Si3N4)膜及び酸化シリコン膜が順次積層されたONO膜102が形成されている。ONO膜102の上には、コントロールゲート電極を含むワード線105が形成されている。ワード線105は、第1の方向と交差する第2の方向に延びる。ビット線拡散層103とワード線105とは、ビット線拡散層103の上に形成されたビット線絶縁膜104により絶縁されている。ONO膜102は、電荷をトラップする記憶部ゲート絶縁膜である。

【0020】

論理部301には、金属酸化膜半導体電界効果トランジスタ(MOSFET)が形成されている。論理部301の第1領域301Aには、動作電圧が12V程度であり、フラッシュメモリを動作させる昇圧回路等を構成する高耐圧MOSFETが形成されている。第2領域301Bには、動作電圧が5V程度であり、主に入出力(I/O)回路等を構成する中耐圧MOSFETが形成されている。第3領域301Cには、動作電圧が2V程度であり、中央制御ユニット(CPU)等を構成する低耐圧MOSFETが形成されている。

【0021】

高耐圧MOSFETは、半導体基板101の上に、第1のゲート絶縁膜111を介在させて形成された第1のゲート電極121と、半導体基板101における第1のゲート電極121の側方に形成された第1のソースドレイン拡散層131とを有している。

【0022】

中耐圧MOSFETは、半導体基板101の上に、第2のゲート絶縁膜112を介在させて形成された第2のゲート電極122と、半導体基板101における第2のゲート電極122の側方に形成された第2のソースドレイン拡散層132とを有している。

【0023】

低耐圧MOSFETは、半導体基板101の上に、第3のゲート絶縁膜113を介在させて形成された第3のゲート電極123と、半導体基板101における第3のゲート電極123の側方に形成された第3のソースドレイン拡散層133とを有している。

【0024】

以下に、本実施形態の半導体記憶装置の製造方法について図面を参照して説明する。まず、図3に示すように、シリコン基板等からなる半導体基板101上の全面に記憶部ゲート絶縁膜となるONO膜102を形成する。ONO膜102の形成はまず、熱酸化法により膜厚が約4nmの第1の酸化シリコン膜を形成した後、第1の酸化シリコン膜の上に化学気相堆積(CVD)法により膜厚が約20nmの窒化シリコン膜を形成する。続いて、窒化シリコン膜の上に熱酸化法により膜厚が約20nmの第2の酸化シリコン膜を形成すればよい。第2の酸化シリコン膜を形成した後の窒化シリコン膜の膜厚は5nm程度となる。なお、第2の酸化シリコン膜は、熱酸化法による酸化シリコン膜とCVD法による酸化シリコン膜との積層構造としてもよい。続いて、記憶部300において、ビット線拡散層を形成する領域の上に形成されたONO膜102をドライエッチングにより除去する。この後、加速電圧が20keVでドーズ量が2.0×1015/cm2である注入条件により、記憶部300におけるONO膜102を除去した領域に砒素(As)イオンを注入して、ビット線拡散層103を形成する。続いて、熱酸化法によりビット線拡散層103の上面を酸化して膜厚が約35nmのビット線絶縁膜104を形成する

次に、図4に示すように記憶部300及び論理部301の上に、CVD法により膜厚が約200nmの多結晶シリコン膜からなる第1の導電膜141を堆積する。

【0025】

次に、図5に示すように第1の導電膜141の上に、CVD法により膜厚が約20nmの窒化シリコンからなる保護膜142を堆積する。続いて、フォトリソグラフィ法により、論理部301が開口するマスクパターン143を形成する。形成したマスクパターン143を用いて、論理部301において保護膜142及び第1の導電膜141を順次ドライエッチングにより除去する。

【0026】

次に、図6に示すように、マスクパターン143を除去した後、記憶部300における保護膜142をマスクとして、論理部301においてONO膜102の第2の酸化シリコン膜をウェットエッチングにより除去する。続いて、膜厚が約5nmの窒化シリコン膜を熱燐酸によるウェットエッチングにより除去する。このとき、オーバーエッチング量を調整し、記憶部300において保護膜142を残存させる。続いて、露出した第1の酸化シリコン膜をウェットエッチングにより除去する。

【0027】

次に、図7に示すように、論理部301において露出した半導体基板101上に膜厚が約17nm〜23nmの第1のゲート絶縁膜111を熱酸化法により形成する。なお、第1のゲート絶縁膜111は、CVD法により酸化シリコン膜を堆積した後、堆積した酸化シリコン膜の下側の半導体基板101に熱酸化膜を形成して積層構造としてもよい。また、熱酸化膜を形成した後、熱酸化膜の上にCVD法により酸化シリコン膜を堆積して積層構造としてもよい。第1のゲート絶縁膜111を形成する際に、記憶部300において保護膜142の上部に第3の酸化シリコン膜144が形成される。

【0028】

次に、図8に示すように、フォトリソグラフィ法により、論理部301の第2領域301Bが開口するマスクパターン145を形成し、形成したマスクパターン145を用いて、第2領域301Bにおいて第1のゲート絶縁膜111をウェットエッチングにより除去する。

【0029】

次に、図9に示すように、マスクパターン145を除去した後、第2領域301Bの上に膜厚が約13nm〜17nmの第2のゲート絶縁膜112を熱酸化法により形成する。なお、第2のゲート絶縁膜112は、CVD法により酸化シリコン膜を堆積した後、酸化シリコン膜の下側の半導体基板101に熱酸化膜を形成して積層構造としてもよい。また、熱酸化膜を形成した後、熱酸化膜の上にCVD法により酸化シリコンを堆積して積層構造としてもよい。CVD法により酸化シリコン膜を堆積する場合には、記憶部300及び第1領域301A及び第3領域301Cの上にも酸化シリコン膜が堆積する。

【0030】

次に、図10に示すように、フォトリソグラフィ法により、第3領域301Cが開口するマスクパターン146を形成し、形成したマスクパターン146を用いて、第3領域301Cの上に形成された第1のゲート絶縁膜111をウェットエッチングにより除去する。なお、第2のゲート絶縁膜112を形成する際に、CVD法により酸化シリコン膜を堆積した場合には、第3領域301Cにおいて第1のゲート絶縁膜111の上に酸化シリコン膜が堆積している。このため、第1のゲート絶縁膜111と共に堆積した酸化シリコン膜も同時に除去する。

【0031】

次に、図11に示すように、マスクパターン146を除去した後、第3領域301Cの上に膜厚が約2nm〜5nmの第3のゲート絶縁膜113を熱酸化法により形成する。続いて、半導体基板101上の全面に、CVD法により膜厚が約200nmの多結晶シリコン膜からなる第2の導電膜147を堆積する。

【0032】

次に、図12に示すように、フォトリソグラフィ法により、記憶部300が開口するマスクパターン148を形成し、形成したマスクパターン148を用いて、記憶部300において第2の導電膜147をドライエッチングにより除去する。

【0033】

次に、図13に示すように、マスクパターン148を除去した後、記憶部300において第3の酸化シリコン膜144をウェットエッチングにより除去する。続いて、保護膜142を熱燐酸によるウェットエッチングにより除去する。

【0034】

次に、図14に示すように、第1の導電膜141及び第2の導電膜147を選択的にエッチング除去することにより、メモリ素子のワード線105、高耐圧MOSFET用の第1のゲート電極121、中耐圧MOSFET用の第2のゲート電極122及び低耐圧MOSFET用の第3のゲート電極123を形成する。高耐圧MOSFETのゲート長は約0.8μm、低耐圧MOSFETのゲート長は約0.2μm、中耐圧MOSFETのゲート長は約0.6μmとなるように形成する。続いて、イオン注入を行い、高耐圧MOSFET用の第1のソースドレイン拡散層131、中耐圧MOSFET用の第2のソースドレイン拡散層132及び低耐圧MOSFET用の第3のソースドレイン拡散層133を形成する。

【0035】

この後、シリサイド層、金属配線、保護膜及びボンディングパッド等を形成することにより半導体記憶装置が完成する。

【0036】

なお、記憶部300に形成された第1の導電膜141には第1のゲート絶縁膜111、第2のゲート絶縁膜112及び第3のゲート絶縁膜113を形成する際に850℃〜1000℃程度の熱が加わる。このため、ワード線105である多結晶シリコン膜の結晶粒塊(グレイン)の大きさは、第1のゲート電極121〜第3のゲート電極123である多結晶シリコン膜よりも大きい。

【0037】

本実施形態の半導体記憶装置の製造方法は、ONO膜102、第1のゲート絶縁膜111及び第2のゲート絶縁膜112が露出した状態で、熱燐酸によるウェットエッチング処理を行わない。このため、ONO膜102、第1のゲート絶縁膜111及び第2のゲート絶縁膜112の膜厚のばらつきを0.5nm〜1.5nm(3%〜10%)程度低減することができる。その結果、メモリ素子及びMOSFETの閾値電圧及び駆動電流等の変動並びに各種膜における信頼性の変動を低減することができる。

【0038】

素子の微細化に伴いシリコン基板中の応力が大きくなると結晶欠陥に起因したリークが誘発される。シリコン基板中の応力を低減するためには、ゲート絶縁膜をCVD法により堆積した酸化シリコン膜とすることが非常に有効である。しかし、CVD法により堆積した酸化シリコン膜は熱酸化法により形成した酸化シリコン膜と比べて熱燐酸による膜減りが大きい。このため、従来はゲート絶縁膜材料として積極的に使用することができなかった。しかし、本実施形態の半導体記憶装置の製造方法は、ゲート絶縁膜が露出した状態で熱燐酸によるエッチングを行わない。このため、CVD法により形成した酸化シリコン膜をゲート絶縁膜に用いても、膜減りの問題が発生しない。従って、本実施形態の半導体記憶装置の製造方法は、半導体記憶装置の微細化にも有用である。

【0039】

なお、本実施形態では、論理部にゲート絶縁膜の膜厚が異なる3種類のMOSFETが形成されている例について説明した。しかし、MOSFETの種類は1種類であっても、2種類以上であっても、同様の効果が得られる。

【産業上の利用可能性】

【0040】

本発明に係る半導体記憶装置の製造方法は、半導体記憶装置の電気的特性のばらつき及び信頼性の低下を回避でき、特に半導体基板上に記憶部と論理部とを有する不揮発性半導体記憶装置の製造方法等として有用である。

【符号の説明】

【0041】

101 半導体基板

102 ONO膜

103 ビット線拡散層

104 ビット線絶縁膜

105 ワード線

111 第1のゲート絶縁膜

112 第2のゲート絶縁膜

113 第3のゲート絶縁膜

121 第1のゲート電極

122 第2のゲート電極

123 第3のゲート電極

131 第1のソースドレイン拡散層

132 第2のソースドレイン拡散層

133 第3のソースドレイン拡散層

141 第1の導電膜

142 保護膜

143 マスクパターン

144 酸化シリコン膜

145 マスクパターン

146 マスクパターン

147 第2の導電膜

148 マスクパターン

300 記憶部

301 論理部

301A 第1領域

301B 第2領域

301C 第3領域

【特許請求の範囲】

【請求項1】

記憶部及び論理部を有する基板の上に、記憶部ゲート絶縁膜を形成する工程(a)と、

前記工程(a)よりも後に、前記基板の上に第1の導電膜を形成する工程(b)と、

前記第1の導電膜及び記憶部ゲート絶縁膜における前記論理部の上に形成された部分を除去する工程(c)と、

前記工程(c)よりも後に、前記基板の上に論理部ゲート絶縁膜を形成する工程(d)と、

前記工程(d)よりも後に、前記基板の上に第2の導電膜を形成する工程(e)と、

前記工程(e)よりも後に、前記記憶部において前記第1の導電膜を露出する工程(f)と、

前記工程(f)よりも後に、前記第1の導電膜を選択的に除去して前記記憶部においてワード線を形成する工程(g)と、

前記工程(f)よりも後に、前記第2の導電膜を選択的に除去して前記論理部において論理部ゲート電極を形成する工程(h)とを備えていることを特徴とする半導体記憶装置の製造方法。

【請求項2】

前記論理部ゲート絶縁膜は、第1のゲート絶縁膜及び第2のゲート絶縁膜を含み、

前記論理部は、第1領域と第2領域とを含み、

前記論理部ゲート電極は、第1のゲート電極及び第2のゲート電極を含み、

前記工程(d)は、

前記基板の上に第1のゲート絶縁膜を形成する工程(d1)と、

前記第1のゲート絶縁膜における前記第1領域の上に形成された部分を残存させ、前記第2領域の上に形成された部分を選択的に除去する工程(d2)と、

前記工程(d2)よりも後に、前記第2領域の上に第2のゲート絶縁膜を形成する工程(d3)とを含み、

前記工程(h)において、前記第1領域の上に第1のゲート電極を形成し、前記第2領域の上に第2のゲート電極を形成することを特徴とする請求項1に記載の半導体記憶装置の製造方法。

【請求項3】

前記工程(b)よりも前に、前記記憶部において前記ワード線と交差する方向に延びるビット線拡散層を形成する工程(i)をさらに備えていることを特徴とする請求項1又は2に記載の半導体記憶装置の製造方法。

【請求項4】

前記工程(i)よりも後に且つ前記工程(b)よりも前に、前記ビット線拡散層の上にビット線絶縁膜を形成する工程(j)をさらに備えていることを特徴とする請求項3に記載の半導体記憶装置の製造方法。

【請求項5】

前記工程(h)よりも後に、前記論理部において前記論理部ゲート電極をマスクとして不純物注入を行い、前記論理部ゲート電極の両側方にソース拡散層及びドレイン拡散層を形成する工程(k)をさらに備えていることを特徴とする請求項1〜4のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項6】

前記ワード線及び論理部ゲート電極は、多結晶シリコン膜からなり、

前記ワード線は、結晶粒塊のサイズが前記論理部ゲート電極よりも大きいことを特徴とする請求項1〜5のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項7】

前記記憶部ゲート絶縁膜は、ONO膜からなることを特徴とする請求項1〜6のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項1】

記憶部及び論理部を有する基板の上に、記憶部ゲート絶縁膜を形成する工程(a)と、

前記工程(a)よりも後に、前記基板の上に第1の導電膜を形成する工程(b)と、

前記第1の導電膜及び記憶部ゲート絶縁膜における前記論理部の上に形成された部分を除去する工程(c)と、

前記工程(c)よりも後に、前記基板の上に論理部ゲート絶縁膜を形成する工程(d)と、

前記工程(d)よりも後に、前記基板の上に第2の導電膜を形成する工程(e)と、

前記工程(e)よりも後に、前記記憶部において前記第1の導電膜を露出する工程(f)と、

前記工程(f)よりも後に、前記第1の導電膜を選択的に除去して前記記憶部においてワード線を形成する工程(g)と、

前記工程(f)よりも後に、前記第2の導電膜を選択的に除去して前記論理部において論理部ゲート電極を形成する工程(h)とを備えていることを特徴とする半導体記憶装置の製造方法。

【請求項2】

前記論理部ゲート絶縁膜は、第1のゲート絶縁膜及び第2のゲート絶縁膜を含み、

前記論理部は、第1領域と第2領域とを含み、

前記論理部ゲート電極は、第1のゲート電極及び第2のゲート電極を含み、

前記工程(d)は、

前記基板の上に第1のゲート絶縁膜を形成する工程(d1)と、

前記第1のゲート絶縁膜における前記第1領域の上に形成された部分を残存させ、前記第2領域の上に形成された部分を選択的に除去する工程(d2)と、

前記工程(d2)よりも後に、前記第2領域の上に第2のゲート絶縁膜を形成する工程(d3)とを含み、

前記工程(h)において、前記第1領域の上に第1のゲート電極を形成し、前記第2領域の上に第2のゲート電極を形成することを特徴とする請求項1に記載の半導体記憶装置の製造方法。

【請求項3】

前記工程(b)よりも前に、前記記憶部において前記ワード線と交差する方向に延びるビット線拡散層を形成する工程(i)をさらに備えていることを特徴とする請求項1又は2に記載の半導体記憶装置の製造方法。

【請求項4】

前記工程(i)よりも後に且つ前記工程(b)よりも前に、前記ビット線拡散層の上にビット線絶縁膜を形成する工程(j)をさらに備えていることを特徴とする請求項3に記載の半導体記憶装置の製造方法。

【請求項5】

前記工程(h)よりも後に、前記論理部において前記論理部ゲート電極をマスクとして不純物注入を行い、前記論理部ゲート電極の両側方にソース拡散層及びドレイン拡散層を形成する工程(k)をさらに備えていることを特徴とする請求項1〜4のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項6】

前記ワード線及び論理部ゲート電極は、多結晶シリコン膜からなり、

前記ワード線は、結晶粒塊のサイズが前記論理部ゲート電極よりも大きいことを特徴とする請求項1〜5のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項7】

前記記憶部ゲート絶縁膜は、ONO膜からなることを特徴とする請求項1〜6のいずれか1項に記載の半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−4764(P2013−4764A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−134896(P2011−134896)

【出願日】平成23年6月17日(2011.6.17)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月17日(2011.6.17)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]