半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるコンタクト抵抗を低減すること。

【解決手段】本発明に係る半導体記憶装置は、基板1上に形成されたメモリセルと、基板1上に形成された周辺トランジスタとを備える。メモリセルは、基板1上に形成された選択トランジスタと、その選択トランジスタに接続されたキャパシタとを備える。周辺トランジスタの拡散層5は第1コンタクトC1を介して上層配線に接続される。ゲート電極3は第2コンタクトC2を介してワード線や上層配線に接続される。選択トランジスタの拡散層4は第3コンタクトC3を介してビット線あるいはキャパシタに接続される。第1〜第3コンタクトC1〜C3のうち、第1コンタクトC1の底部にのみシリサイド21が選択的に形成される。

【解決手段】本発明に係る半導体記憶装置は、基板1上に形成されたメモリセルと、基板1上に形成された周辺トランジスタとを備える。メモリセルは、基板1上に形成された選択トランジスタと、その選択トランジスタに接続されたキャパシタとを備える。周辺トランジスタの拡散層5は第1コンタクトC1を介して上層配線に接続される。ゲート電極3は第2コンタクトC2を介してワード線や上層配線に接続される。選択トランジスタの拡散層4は第3コンタクトC3を介してビット線あるいはキャパシタに接続される。第1〜第3コンタクトC1〜C3のうち、第1コンタクトC1の底部にのみシリサイド21が選択的に形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体記憶装置に関する。特に、本発明は、サリサイド(salicide)技術が適用された半導体記憶装置に関する。

【背景技術】

【0002】

シリコンと金属を高温で反応させると抵抗率が低く、耐熱性及び耐酸化性に優れたシリサイドが形成される。DRAMやDRAM内蔵マイコンにおいて、コンタクト抵抗の抑制を目的として、そのようなシリサイドを金属配線のコンタクトホールの底部に形成するサリサイド(salicide)技術がしばしば用いられる(例えば特許文献1参照)。図1〜図4を参照して、サリサイド構造を有する従来のDRAMの製造工程を説明する。

【0003】

図1を参照して、基板101にSTI(Shallow Trench Isolation)等の素子分離構造102が形成された後、基板101上にゲート絶縁膜を介してゲート電極103が形成される。このゲート電極103は、DRAMセルに含まれる選択トランジスタのゲート電極や、ロジック回路に含まれる周辺トランジスタのゲート電極である。また、ゲート電極103は、ポリシリコンとWSi(タングステンシリサイド)からなるポリサイドゲート構造を有する。その後、ゲート電極103をマスクとして用いることによって、基板101中に、選択トランジスタのソース/ドレイン拡散層104や周辺トランジスタのソース/ドレイン拡散層105が形成される。

【0004】

次に、全面に層間絶縁膜107が堆積される。そして、選択トランジスタ(メモリセル)内のソース/ドレイン拡散層104上に、セルコンタクトプラグ106が形成される。このセルコンタクトプラグ106は、ドープトポリシリコンあるいはドープトアモルファスシリコンで形成される。セルコンタクトプラグ106は、メモリセルのキャパシタとソース/ドレイン拡散層104との間、あるいは、ビット線とソース/ドレイン拡散層104との間を接続するためのプラグの一部である。

【0005】

次に、セルコンタクトプラグ106を覆うように、更に全面に層間絶縁膜107が堆積される。その後、フォトリソグラフィー技術により、第1〜第3コンタクトホールC1〜C3が形成される。具体的には、所定のパターンを有するレジストマスクが層間絶縁膜107上に形成された後、所定の領域の層間絶縁膜107がドライエッチングにより除去される。これにより、周辺トランジスタが形成される領域において、ソース/ドレイン拡散層105に届く第1コンタクトホールC1が形成される。また、ゲート電極103に届く第2コンタクトホールC2が形成される。更に、DRAMセルが形成される領域において、セルコンタクトプラグ106に届く第3コンタクトホールC3が形成される。

【0006】

次に、コンタクト抵抗を低減するために、第1〜第3コンタクトホールC1〜C3の底部に、CoSi(コバルトシリサイド)が形成される。具体的には、図2に示されるように、Co膜110がスパッタ法により全面に堆積される。また、Co膜110の酸化防止のため、Ti膜111がキャップ膜として全面に堆積される。次に、400℃程度の熱処理が実施され、シリサイド反応が発生する。余剰なCo膜110とキャップ膜であるTi膜111が混酸等により除去されると、図3に示される構造が得られる。図3において、コンタクトホールC1〜C3のそれぞれの底部に、CoSi121、122、及び123が形成される。但し、ゲート電極132として、ポリサイドゲートの代わりにポリメタルゲート(W/WN/poly,W/TiN/poly等)が用いられた場合、ゲート電極132上にCoSi122は形成されない。

【0007】

次に、図4に示されるように、周辺トランジスタ領域のコンタクトホールC1内に、配線と接続される第1コンタクトプラグ131が埋め込まれる。また、ゲート電極103上のコンタクトホールC2内に、第2コンタクトプラグ132が埋め込まれる。また、選択トランジスタのセルコンタクトプラグ106上のコンタクトホールC3内に、ビット線やメモリセルのキャパシタに接続される第3コンタクトプラグ133が形成される。これら第1〜第3コンタクトプラグ131〜133は、W/TiN/Tiの積層構造を有している。

【0008】

【特許文献1】特開2003−289131号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本願発明者は、次の点に着目した。図2及び図3を参照して、セルコンタクトプラグ106上のコンタクトホールC3の深さは、他のコンタクトホールC1,C2よりも浅い。そのため、コンタクトホールC3におけるCo膜110の成膜量が、他と比べて多くなる傾向がある。その結果、コンタクトホールC3の底部におけるシリサイド反応においては、“凝集”が容易に起こりやすくなる。“凝集”とは、熱処理によってシリサイドが島状に成長し、不均一・不連続が形成される現象である。凝集が発生すると、配線幅の減少に伴って配線抵抗が急激に上昇することが知られている(細線効果)。つまり、コンタクト抵抗を低減するために形成されたCoSi123が、逆にコンタクト抵抗を上昇させる原因となる可能性がある。

【0010】

更に、従来技術によれば、ゲート電極103としてポリサイドゲート(ポリシリコン,WSi)が用いられる場合、コンタクトホールC2の底部にはCoSi122が形成される。そして、図4に示されるように、第2コンタクトプラグ132が形成されると、ゲート電極領域には、「W/TiN/TiSi/CoSi/WSi」の積層構造が形成されることになる。このような積層構造によれば、CoSi122が無い場合と比較して界面の数が増加し、界面の数の増加はコンタクト抵抗の増加を招く。

【0011】

このように、コンタクトホールの底にCoSiを形成するプロセスは、周辺トランジスタのコンタクト抵抗を低減できる反面、選択トランジスタのコンタクト抵抗を増加させてしまう可能性がある。全体としてコンタクト抵抗を低減することができる技術が望まれている。

【0012】

本発明の目的は、コンタクト抵抗を低減することができる半導体記憶装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0013】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0014】

本発明の第1の観点において、半導体記憶装置が提供される。その半導体記憶装置は、基板(1)上に形成されたメモリセルと、基板(1)上に形成された周辺トランジスタ(3,5)とを備える。メモリセルは、基板(1)上に形成された選択トランジスタ(3,4)と、その選択トランジスタ(3,4)に接続されたキャパシタとを備える。周辺トランジスタ(3,5)の拡散層(5)は第1コンタクト(C1)を介して上層配線に接続される。周辺トランジスタ(3,5)や選択トランジスタ(3,4)のゲート(3)は第2コンタクト(C2)を介して上層配線に接続される。選択トランジスタ(3,4)の拡散層(4)は第3コンタクト(C3)を介してビット線あるいはキャパシタに接続される。本発明によれば、第1〜第3コンタクト(C1〜C3)のうち、第1コンタクト(C1)中にのみシリサイド(21)が選択的に形成される。

【0015】

上記シリサイド(21)は、第1コンタクト(C1)の底部に形成される。シリサイド(21)は、例えばコバルトシリサイド(CoSi)である。

【0016】

上記第3コンタクト(C3)は、選択トランジスタ(3,4)の拡散層(4)上に形成された第1プラグ(6)と、その第1プラグ(6)上にシリサイドを介さずに形成された第2プラグ(33)とを含む。第1コンタクト(C1)の底部は、第2プラグ(33)の底部よりも深い場所に位置する。

【0017】

本発明の第2の観点において、半導体記憶装置の製造方法が提供される。その製造方法は、(A)基板(1)上にメモリセルの選択トランジスタ(3,4)及び周辺トランジスタ(3,5)を形成する工程と、(B)選択トランジスタ(3,4)の拡散層(4)上に第1プラグ(6)を形成する工程と、(C)全面に層間絶縁膜(7)を形成する工程と、(D)層間絶縁膜(7)をエッチングすることによって、周辺トランジスタ(3,5)の拡散層(5)、選択トランジスタ(3,4)のゲート(3)、及び第1プラグ(6)のそれぞれに届く第1、第2、第3コンタクトホール(C1,C2,C3)を形成する工程と、(E)第1〜第3コンタクトホール(C1〜C3)のうち、第1コンタクトホール(C1)の底部にのみシリサイド(21)を選択的に形成する工程とを有する。シリサイド(21)は、例えばコバルトシリサイド(CoSi)である。

【0018】

上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)第1コンタクトホール(C1)上にレジストマスク(12)を選択的に形成する工程と、(c)そのレジストマスク(12)を用いたエッチングにより金属膜(10)を選択的に除去する工程と、(d)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。

【0019】

また、上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)全面にポジ型のレジストを塗布する工程と、(c)第1〜第3コンタクトホール(C1〜C3)のうち第2及び第3コンタクトホール(C2,C3)の穴底にのみ光が届くように露光処理を行う工程と、(d)光が照射されたレジストを除去することによって、第1コンタクトホール(C1)内にのみレジストマスク(40)を選択的に形成する工程と、(e)そのレジストマスク(40)を用いたエッチングにより金属膜(10)を選択的に除去する工程と、(f)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。

【0020】

また、第1〜第3コンタクトホール(C1〜C3)の穴径はそれぞれ、r1,r2,r3で表され、第1〜第3コンタクトホール(C1〜C3)の深さはそれぞれ、t1,t2,t3で表される。このとき、上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)ウエハを水平面から角度θだけ傾けてスパッタエッチングを実施することによって、金属膜(10)の一部を除去する工程と、(c)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。ここで、角度θは、次の関係式:r1/t1<tanθ≦r2/t2≦r3/t3を満たす。

【0021】

本発明に係る製造方法は、更に、(F)シリサイド(21)と上層配線を接続するプラグ(31)を、第1コンタクトホール(C1)内に埋め込む工程と、(G)ゲート(3)と上層配線とを接続するプラグ(32)を、第2コンタクトホール(C2)内に埋め込む工程と、(H)第1プラグ(6)とメモリセルのキャパシタとを接続する第2プラグ(33)を、第3コンタクトホール(C3)内に埋め込む工程とを有する。

【0022】

以上に説明されたように、本発明によれば、第1〜第3コンタクトホール(C1〜C3)のうち、第1コンタクトホール(C1)中にのみシリサイド(21)が選択的に形成される。これにより、周辺トランジスタの拡散層(5)につながるコンタクトのコンタクト抵抗が低減される。また、ゲート(3)につながる第2コンタクトホール(C2)の底部にはシリサイドは形成されない。従って、界面数の増加のせいでコンタクト抵抗が上昇することが防止される。更に、第3コンタクトホール(C3)の底部にはシリサイドは形成されない。従って、凝集によるコンタクト抵抗の増加が抑制される。このように、本発明によれば、全体としてコンタクト抵抗を低減することが可能となる。

【発明の効果】

【0023】

本発明に係る半導体記憶装置及びその製造方法によれば、全体としてコンタクト抵抗を低減することが可能となる。

【発明を実施するための最良の形態】

【0024】

添付図面を参照して、本発明に係る半導体記憶装置及びその製造方法を説明する。半導体記憶装置としては、キャパシタを含むメモリセルを有するDRAMが例示される。このDRAMの製造方法においては、サリサイド技術が適用される。以下の説明において、シリサイドとしてCoSi(コバルトシリサイド)が形成される例が示される。但し、用いられるシリサイドはCoSiに限られず、NiSi(ニッケルシリサイド)等の他のシリサイドが用いられてもよい。

【0025】

1.第1の実施の形態

図5〜図9は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。図5を参照して、基板1にSTI等の素子分離構造2が形成された後、基板1上にゲート絶縁膜を介してゲート電極3が形成される。このゲート電極3は、DRAMセルに含まれる選択トランジスタのゲート電極や、ロジック回路に含まれる周辺トランジスタのゲート電極である。また、ゲート電極3は、ポリシリコンとWSi(タングステンシリサイド)からなるポリサイドゲート構造を有する。その後、ゲート電極3をマスクとして用いることによって、基板1中に、選択トランジスタのソース/ドレイン拡散層4や周辺トランジスタのソース/ドレイン拡散層5が形成される。このように、基板1上に、DRAMセルの選択トランジスタや、ロジック回路に含まれる周辺トランジスタが形成される。

【0026】

次に、全面に層間絶縁膜7が堆積される。そして、選択トランジスタ(メモリセル)内のソース/ドレイン拡散層4上に、セルコンタクトプラグ6が形成される。このセルコンタクトプラグ6は、ドープトポリシリコンあるいはドープトアモルファスシリコンで形成される。セルコンタクトプラグ6は、メモリセルのキャパシタとソース/ドレイン拡散層4との間、あるいは、ビット線とソース/ドレイン拡散層4との間を接続するためのプラグの一部である。

【0027】

次に、セルコンタクトプラグ6を覆うように、更に全面に層間絶縁膜7が堆積される。その後、フォトリソグラフィー技術により、第1〜第3コンタクトホールC1〜C3が形成される。具体的には、所定のパターンを有するレジストマスクが層間絶縁膜7上に形成された後、所定の領域の層間絶縁膜7がドライエッチングにより除去される。これにより、周辺トランジスタが形成される領域において、ソース/ドレイン拡散層5に届く第1コンタクトホールC1が形成される。また、周辺トランジスタ及び選択トランジスタのゲート電極3に届く第2コンタクトホールC2が形成される。更に、DRAMセルが形成される領域において、セルコンタクトプラグ6に届く第3コンタクトホールC3が形成される。

【0028】

尚、基板1上にセルコンタクトプラグ6が形成されているため、第3コンタクトホールC3の底部は、第1コンタクトホールC1の底部よりも浅い場所に位置している。また、以下の説明において、第2コンタクトホールC2は選択トランジスタのゲート電極3につながるコンタクトホールであるとする。周辺トランジスタのゲート電極3の場合も同様である。

【0029】

次に、図6に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。更に、フォトリソグラフィー技術によって、所定のパターンを有するレジストマスク12がTi膜11上に形成される。ここで、レジストマスク12は、第1コンタクトホールC1を覆うように、すなわち、周辺トランジスタが形成された領域上に選択的に形成される。第2、第3コンタクトホールC2、C3上にはレジストマスク12は形成されない。

【0030】

次に、上記レジストマスク12を用いたドライエッチングあるいはウェットエッチングにより、Ti膜11及びCo膜10が選択的に除去される。レジストマスク12は第1コンタクトホールC1を覆うように形成されているので、第1コンタクトホールC1上のTi膜11及びCo膜10は除去されない。一方、ゲート電極3及びセルコンタクトプラグ6上のTi膜11及びCo膜10が除去される。レジストマスク12が除去されると、図7に示された構造が得られる。

【0031】

次に、400℃程度の熱処理が実施され、シリサイド反応が発生する。余剰なCo膜10とキャップ膜であるTi膜11が混酸等により除去されると、図8に示される構造が得られる。図8において、周辺トランジスタが形成される領域における第1コンタクトホールC1の底部にCoSi21が形成されている。一方、第2及び第3コンタクトホールC2、C3の底部にはシリサイドは形成されていない。つまり、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成されている。

【0032】

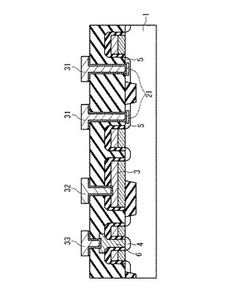

次に、図9に示されるように、周辺トランジスタ領域のコンタクトホールC1内に、CoSi21と接続される第1コンタクトプラグ31が埋め込まれる。第1コンタクトプラグ31とCoSi21は、周辺トランジスタのソース/ドレイン拡散層5と上層配線との間を接続するコンタクトとしての役割を果たす。また、選択トランジスタのゲート電極3上のコンタクトホールC2内に、ワード線(上層配線)と接続される第2コンタクトプラグ32が埋め込まれる。第2コンタクトプラグ32は、ゲート電極3とワード線との間を接続するコンタクトとしての役割を果たす。また、選択トランジスタのセルコンタクトプラグ6上のコンタクトホールC3内に、第3コンタクトプラグ33が埋め込まれる。セルコンタクトプラグ6と第3コンタクトプラグ33との間にはシリサイドは形成されていない。これら第3コンタクトプラグ33と上記セルコンタクトプラグ6は、選択トランジスタの拡散層4とビット線あるいはメモリセルのキャパシタとの間を接続するコンタクトとしての役割を果たす。これら第1〜第3コンタクトプラグ31〜33は、W/TiN/Tiの積層構造を有している。

【0033】

その後、第3コンタクトプラグ33につながるようにメモリセルのキャパシタが形成される。また、所定のパターンを有するワード線、ビット線及び上層配線が形成される。

【0034】

以上に説明されたように、本実施の形態によれば、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1中にのみCoSi21が選択的に形成される。これにより、周辺トランジスタのソース/ドレイン拡散層5につながるコンタクトのコンタクト抵抗が低減される。また、第2コンタクトホールC2の底部にはシリサイドは形成されない。従って、界面数の増加のせいでコンタクト抵抗が上昇することが防止される。更に、第3コンタクトホールC3の底部にはシリサイドは形成されない。従って、凝集によるコンタクト抵抗の増加が抑制される。このように、本実施の形態によれば、全体としてコンタクト抵抗を低減することが可能となる。

【0035】

2.第2の実施の形態

図10〜図12は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。第2の実施の形態において、図5に示された状態までは第1の実施の形態と同様の工程によって製造される。

【0036】

次に、図10に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。

【0037】

次に、光が照射されると可溶性になるポジ型レジストが全面に塗布される。次に、レティクルを用いることなしに全面露光処理が行われる。ここで、上述の通り、基板1上にセルコンタクトプラグ6が形成されているため、第1コンタクトホールC1の底部は、第2及び第3コンタクトホールC2,C3の底部よりも深い場所に位置している。従って、第1〜第3コンタクトホールC1〜C3のうち第2及び第3コンタクトホールC2,C3の穴底にのみ光が届くように露光量を調節することが可能である。つまり、第1コンタクトホールC1底部のポジ型レジストの性質を変えないように露光処理を実施することが可能である。ポジ型レジストの除去工程においては、メモリセルの選択トランジスタ領域、すなわち光が照射された領域のレジストだけが除去される。その結果、図11に示されるように、第1コンタクトホールC1内にのみレジストマスク40が選択的に形成される。

【0038】

次に、上記レジストマスク40を用いたドライエッチングあるいはウェットエッチングにより、Ti膜11及びCo膜10が選択的に除去される。レジストマスク40は第1コンタクトホールC1の穴底に形成されているので、第1コンタクトホールC1底部のTi膜11及びCo膜10は除去されない。一方、ゲート電極3及びセルコンタクトプラグ6上のTi膜11及びCo膜10は除去される。レジストマスク40が除去されると、図12に示された構造が得られる。

【0039】

その後、第1の実施の形態と同様に、400℃程度の熱処理が実施される。これにより、既出の図8で示されたように、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成される。続いて、既出の図9に示されたように、第1〜第3コンタクトプラグ31〜33が第1〜第3コンタクトホールC1〜C3のそれぞれに埋め込まれる。

【0040】

以上に説明された第2の実施の形態によれば、第1の実施の形態と同じ効果が得られる。更に、レティクルを使用することなくフォトレジストをパターニングできるため、微細加工が容易になるという追加的な効果が得られる。

【0041】

3.第3の実施の形態

第3の実施の形態において、図5に示された状態までは第1の実施の形態と同様の工程によって製造される。ここで、図13に示されるように、第1〜第3コンタクトホールC1〜C3の穴径(直径)は、それぞれr1,r2,r3であるとする。また、第1〜第3コンタクトホールC1〜C3の深さは、それぞれt1,t2,t3であるとする。

【0042】

次に、既出の図10に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。

【0043】

次に、図14に示されるように、ウエハが水平面から角度θだけ傾けられる。ここで、角度θは、次の関係式(1)を満たすように設定される:

r1/t1<tanθ≦r2/t2≦r3/t3 ・・・(1)

この状態でスパッタエッチングが実施されると、Co膜10とTi膜11は部分的にスパッタエッチングされることになる。具体的には、第2コンタクトホールC2及び第3コンタクトホールC3からはCo膜10とTi膜11が除去されるが、第1コンタクトホールC1の底部からはCo膜10とTi膜11は除去されない。すなわち、第1コンタクトホールC1の底部にのみ金属膜を残すことが可能である(図12参照)。

【0044】

その後、第1の実施の形態と同様に、400℃程度の熱処理が実施される。これにより、既出の図8に示されたように、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成される。続いて、既出の図9に示されたように、第1〜第3コンタクトプラグ31〜33が第1〜第3コンタクトホールC1〜C3のそれぞれに埋め込まれる。

【0045】

以上に説明された第3の実施の形態によれば、第1の実施の形態と同じ効果が得られる。更に、第1コンタクトホールC1の底部だけにシリサイドを選択的に形成するために、フォトリソグラフィー技術を行う必要がない。従って、製造プロセスが単純化されるという追加的な効果が得られる。

【図面の簡単な説明】

【0046】

【図1】図1は、従来の半導体記憶装置の製造工程を示す断面図である。

【図2】図2は、従来の半導体記憶装置の製造工程を示す断面図である。

【図3】図3は、従来の半導体記憶装置の製造工程を示す断面図である。

【図4】図4は、従来の半導体記憶装置の製造工程を示す断面図である。

【図5】図5は、本発明の第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図6】図6は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図7】図7は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図8】図8は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図9】図9は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図10】図10は、本発明の第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図11】図11は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図12】図12は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図13】図13は、本発明の第3の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図14】図14は、第3の実施の形態に係る半導体記憶装置の製造方法を示す概念図である。

【符号の説明】

【0047】

1 基板

2 素子分離構造

3 ゲート電極(ポリサイドゲート)

4 ソース/ドレイン拡散層

5 ソース/ドレイン拡散層

6 セルコンタクトプラグ

7 層間絶縁膜

10 Co膜

11 Ti膜

12 レジストマスク

21 コバルトシリサイド

31 第1コンタクトプラグ

32 第2コンタクトプラグ

33 第3コンタクトプラグ

40 レジストマスク

C1 第1コンタクトホール(周辺トランジスタのソース/ドレイン上)

C2 第2コンタクトホール(選択トランジスタのゲート上)

C3 第3コンタクトホール(選択トランジスタのソース/ドレイン上)

【技術分野】

【0001】

本発明は、半導体記憶装置に関する。特に、本発明は、サリサイド(salicide)技術が適用された半導体記憶装置に関する。

【背景技術】

【0002】

シリコンと金属を高温で反応させると抵抗率が低く、耐熱性及び耐酸化性に優れたシリサイドが形成される。DRAMやDRAM内蔵マイコンにおいて、コンタクト抵抗の抑制を目的として、そのようなシリサイドを金属配線のコンタクトホールの底部に形成するサリサイド(salicide)技術がしばしば用いられる(例えば特許文献1参照)。図1〜図4を参照して、サリサイド構造を有する従来のDRAMの製造工程を説明する。

【0003】

図1を参照して、基板101にSTI(Shallow Trench Isolation)等の素子分離構造102が形成された後、基板101上にゲート絶縁膜を介してゲート電極103が形成される。このゲート電極103は、DRAMセルに含まれる選択トランジスタのゲート電極や、ロジック回路に含まれる周辺トランジスタのゲート電極である。また、ゲート電極103は、ポリシリコンとWSi(タングステンシリサイド)からなるポリサイドゲート構造を有する。その後、ゲート電極103をマスクとして用いることによって、基板101中に、選択トランジスタのソース/ドレイン拡散層104や周辺トランジスタのソース/ドレイン拡散層105が形成される。

【0004】

次に、全面に層間絶縁膜107が堆積される。そして、選択トランジスタ(メモリセル)内のソース/ドレイン拡散層104上に、セルコンタクトプラグ106が形成される。このセルコンタクトプラグ106は、ドープトポリシリコンあるいはドープトアモルファスシリコンで形成される。セルコンタクトプラグ106は、メモリセルのキャパシタとソース/ドレイン拡散層104との間、あるいは、ビット線とソース/ドレイン拡散層104との間を接続するためのプラグの一部である。

【0005】

次に、セルコンタクトプラグ106を覆うように、更に全面に層間絶縁膜107が堆積される。その後、フォトリソグラフィー技術により、第1〜第3コンタクトホールC1〜C3が形成される。具体的には、所定のパターンを有するレジストマスクが層間絶縁膜107上に形成された後、所定の領域の層間絶縁膜107がドライエッチングにより除去される。これにより、周辺トランジスタが形成される領域において、ソース/ドレイン拡散層105に届く第1コンタクトホールC1が形成される。また、ゲート電極103に届く第2コンタクトホールC2が形成される。更に、DRAMセルが形成される領域において、セルコンタクトプラグ106に届く第3コンタクトホールC3が形成される。

【0006】

次に、コンタクト抵抗を低減するために、第1〜第3コンタクトホールC1〜C3の底部に、CoSi(コバルトシリサイド)が形成される。具体的には、図2に示されるように、Co膜110がスパッタ法により全面に堆積される。また、Co膜110の酸化防止のため、Ti膜111がキャップ膜として全面に堆積される。次に、400℃程度の熱処理が実施され、シリサイド反応が発生する。余剰なCo膜110とキャップ膜であるTi膜111が混酸等により除去されると、図3に示される構造が得られる。図3において、コンタクトホールC1〜C3のそれぞれの底部に、CoSi121、122、及び123が形成される。但し、ゲート電極132として、ポリサイドゲートの代わりにポリメタルゲート(W/WN/poly,W/TiN/poly等)が用いられた場合、ゲート電極132上にCoSi122は形成されない。

【0007】

次に、図4に示されるように、周辺トランジスタ領域のコンタクトホールC1内に、配線と接続される第1コンタクトプラグ131が埋め込まれる。また、ゲート電極103上のコンタクトホールC2内に、第2コンタクトプラグ132が埋め込まれる。また、選択トランジスタのセルコンタクトプラグ106上のコンタクトホールC3内に、ビット線やメモリセルのキャパシタに接続される第3コンタクトプラグ133が形成される。これら第1〜第3コンタクトプラグ131〜133は、W/TiN/Tiの積層構造を有している。

【0008】

【特許文献1】特開2003−289131号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本願発明者は、次の点に着目した。図2及び図3を参照して、セルコンタクトプラグ106上のコンタクトホールC3の深さは、他のコンタクトホールC1,C2よりも浅い。そのため、コンタクトホールC3におけるCo膜110の成膜量が、他と比べて多くなる傾向がある。その結果、コンタクトホールC3の底部におけるシリサイド反応においては、“凝集”が容易に起こりやすくなる。“凝集”とは、熱処理によってシリサイドが島状に成長し、不均一・不連続が形成される現象である。凝集が発生すると、配線幅の減少に伴って配線抵抗が急激に上昇することが知られている(細線効果)。つまり、コンタクト抵抗を低減するために形成されたCoSi123が、逆にコンタクト抵抗を上昇させる原因となる可能性がある。

【0010】

更に、従来技術によれば、ゲート電極103としてポリサイドゲート(ポリシリコン,WSi)が用いられる場合、コンタクトホールC2の底部にはCoSi122が形成される。そして、図4に示されるように、第2コンタクトプラグ132が形成されると、ゲート電極領域には、「W/TiN/TiSi/CoSi/WSi」の積層構造が形成されることになる。このような積層構造によれば、CoSi122が無い場合と比較して界面の数が増加し、界面の数の増加はコンタクト抵抗の増加を招く。

【0011】

このように、コンタクトホールの底にCoSiを形成するプロセスは、周辺トランジスタのコンタクト抵抗を低減できる反面、選択トランジスタのコンタクト抵抗を増加させてしまう可能性がある。全体としてコンタクト抵抗を低減することができる技術が望まれている。

【0012】

本発明の目的は、コンタクト抵抗を低減することができる半導体記憶装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0013】

以下に、[発明を実施するための最良の形態]で使用される番号・符号を用いて、[課題を解決するための手段]を説明する。これらの番号・符号は、[特許請求の範囲]の記載と[発明を実施するための最良の形態]との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0014】

本発明の第1の観点において、半導体記憶装置が提供される。その半導体記憶装置は、基板(1)上に形成されたメモリセルと、基板(1)上に形成された周辺トランジスタ(3,5)とを備える。メモリセルは、基板(1)上に形成された選択トランジスタ(3,4)と、その選択トランジスタ(3,4)に接続されたキャパシタとを備える。周辺トランジスタ(3,5)の拡散層(5)は第1コンタクト(C1)を介して上層配線に接続される。周辺トランジスタ(3,5)や選択トランジスタ(3,4)のゲート(3)は第2コンタクト(C2)を介して上層配線に接続される。選択トランジスタ(3,4)の拡散層(4)は第3コンタクト(C3)を介してビット線あるいはキャパシタに接続される。本発明によれば、第1〜第3コンタクト(C1〜C3)のうち、第1コンタクト(C1)中にのみシリサイド(21)が選択的に形成される。

【0015】

上記シリサイド(21)は、第1コンタクト(C1)の底部に形成される。シリサイド(21)は、例えばコバルトシリサイド(CoSi)である。

【0016】

上記第3コンタクト(C3)は、選択トランジスタ(3,4)の拡散層(4)上に形成された第1プラグ(6)と、その第1プラグ(6)上にシリサイドを介さずに形成された第2プラグ(33)とを含む。第1コンタクト(C1)の底部は、第2プラグ(33)の底部よりも深い場所に位置する。

【0017】

本発明の第2の観点において、半導体記憶装置の製造方法が提供される。その製造方法は、(A)基板(1)上にメモリセルの選択トランジスタ(3,4)及び周辺トランジスタ(3,5)を形成する工程と、(B)選択トランジスタ(3,4)の拡散層(4)上に第1プラグ(6)を形成する工程と、(C)全面に層間絶縁膜(7)を形成する工程と、(D)層間絶縁膜(7)をエッチングすることによって、周辺トランジスタ(3,5)の拡散層(5)、選択トランジスタ(3,4)のゲート(3)、及び第1プラグ(6)のそれぞれに届く第1、第2、第3コンタクトホール(C1,C2,C3)を形成する工程と、(E)第1〜第3コンタクトホール(C1〜C3)のうち、第1コンタクトホール(C1)の底部にのみシリサイド(21)を選択的に形成する工程とを有する。シリサイド(21)は、例えばコバルトシリサイド(CoSi)である。

【0018】

上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)第1コンタクトホール(C1)上にレジストマスク(12)を選択的に形成する工程と、(c)そのレジストマスク(12)を用いたエッチングにより金属膜(10)を選択的に除去する工程と、(d)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。

【0019】

また、上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)全面にポジ型のレジストを塗布する工程と、(c)第1〜第3コンタクトホール(C1〜C3)のうち第2及び第3コンタクトホール(C2,C3)の穴底にのみ光が届くように露光処理を行う工程と、(d)光が照射されたレジストを除去することによって、第1コンタクトホール(C1)内にのみレジストマスク(40)を選択的に形成する工程と、(e)そのレジストマスク(40)を用いたエッチングにより金属膜(10)を選択的に除去する工程と、(f)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。

【0020】

また、第1〜第3コンタクトホール(C1〜C3)の穴径はそれぞれ、r1,r2,r3で表され、第1〜第3コンタクトホール(C1〜C3)の深さはそれぞれ、t1,t2,t3で表される。このとき、上記(E)工程は、(a)全面にシリサイド(21)の材料となる金属膜(10)を堆積する工程と、(b)ウエハを水平面から角度θだけ傾けてスパッタエッチングを実施することによって、金属膜(10)の一部を除去する工程と、(c)熱処理によって第1コンタクトホール(C1)の底部にシリサイド(21)を形成する工程とを含んでもよい。ここで、角度θは、次の関係式:r1/t1<tanθ≦r2/t2≦r3/t3を満たす。

【0021】

本発明に係る製造方法は、更に、(F)シリサイド(21)と上層配線を接続するプラグ(31)を、第1コンタクトホール(C1)内に埋め込む工程と、(G)ゲート(3)と上層配線とを接続するプラグ(32)を、第2コンタクトホール(C2)内に埋め込む工程と、(H)第1プラグ(6)とメモリセルのキャパシタとを接続する第2プラグ(33)を、第3コンタクトホール(C3)内に埋め込む工程とを有する。

【0022】

以上に説明されたように、本発明によれば、第1〜第3コンタクトホール(C1〜C3)のうち、第1コンタクトホール(C1)中にのみシリサイド(21)が選択的に形成される。これにより、周辺トランジスタの拡散層(5)につながるコンタクトのコンタクト抵抗が低減される。また、ゲート(3)につながる第2コンタクトホール(C2)の底部にはシリサイドは形成されない。従って、界面数の増加のせいでコンタクト抵抗が上昇することが防止される。更に、第3コンタクトホール(C3)の底部にはシリサイドは形成されない。従って、凝集によるコンタクト抵抗の増加が抑制される。このように、本発明によれば、全体としてコンタクト抵抗を低減することが可能となる。

【発明の効果】

【0023】

本発明に係る半導体記憶装置及びその製造方法によれば、全体としてコンタクト抵抗を低減することが可能となる。

【発明を実施するための最良の形態】

【0024】

添付図面を参照して、本発明に係る半導体記憶装置及びその製造方法を説明する。半導体記憶装置としては、キャパシタを含むメモリセルを有するDRAMが例示される。このDRAMの製造方法においては、サリサイド技術が適用される。以下の説明において、シリサイドとしてCoSi(コバルトシリサイド)が形成される例が示される。但し、用いられるシリサイドはCoSiに限られず、NiSi(ニッケルシリサイド)等の他のシリサイドが用いられてもよい。

【0025】

1.第1の実施の形態

図5〜図9は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。図5を参照して、基板1にSTI等の素子分離構造2が形成された後、基板1上にゲート絶縁膜を介してゲート電極3が形成される。このゲート電極3は、DRAMセルに含まれる選択トランジスタのゲート電極や、ロジック回路に含まれる周辺トランジスタのゲート電極である。また、ゲート電極3は、ポリシリコンとWSi(タングステンシリサイド)からなるポリサイドゲート構造を有する。その後、ゲート電極3をマスクとして用いることによって、基板1中に、選択トランジスタのソース/ドレイン拡散層4や周辺トランジスタのソース/ドレイン拡散層5が形成される。このように、基板1上に、DRAMセルの選択トランジスタや、ロジック回路に含まれる周辺トランジスタが形成される。

【0026】

次に、全面に層間絶縁膜7が堆積される。そして、選択トランジスタ(メモリセル)内のソース/ドレイン拡散層4上に、セルコンタクトプラグ6が形成される。このセルコンタクトプラグ6は、ドープトポリシリコンあるいはドープトアモルファスシリコンで形成される。セルコンタクトプラグ6は、メモリセルのキャパシタとソース/ドレイン拡散層4との間、あるいは、ビット線とソース/ドレイン拡散層4との間を接続するためのプラグの一部である。

【0027】

次に、セルコンタクトプラグ6を覆うように、更に全面に層間絶縁膜7が堆積される。その後、フォトリソグラフィー技術により、第1〜第3コンタクトホールC1〜C3が形成される。具体的には、所定のパターンを有するレジストマスクが層間絶縁膜7上に形成された後、所定の領域の層間絶縁膜7がドライエッチングにより除去される。これにより、周辺トランジスタが形成される領域において、ソース/ドレイン拡散層5に届く第1コンタクトホールC1が形成される。また、周辺トランジスタ及び選択トランジスタのゲート電極3に届く第2コンタクトホールC2が形成される。更に、DRAMセルが形成される領域において、セルコンタクトプラグ6に届く第3コンタクトホールC3が形成される。

【0028】

尚、基板1上にセルコンタクトプラグ6が形成されているため、第3コンタクトホールC3の底部は、第1コンタクトホールC1の底部よりも浅い場所に位置している。また、以下の説明において、第2コンタクトホールC2は選択トランジスタのゲート電極3につながるコンタクトホールであるとする。周辺トランジスタのゲート電極3の場合も同様である。

【0029】

次に、図6に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。更に、フォトリソグラフィー技術によって、所定のパターンを有するレジストマスク12がTi膜11上に形成される。ここで、レジストマスク12は、第1コンタクトホールC1を覆うように、すなわち、周辺トランジスタが形成された領域上に選択的に形成される。第2、第3コンタクトホールC2、C3上にはレジストマスク12は形成されない。

【0030】

次に、上記レジストマスク12を用いたドライエッチングあるいはウェットエッチングにより、Ti膜11及びCo膜10が選択的に除去される。レジストマスク12は第1コンタクトホールC1を覆うように形成されているので、第1コンタクトホールC1上のTi膜11及びCo膜10は除去されない。一方、ゲート電極3及びセルコンタクトプラグ6上のTi膜11及びCo膜10が除去される。レジストマスク12が除去されると、図7に示された構造が得られる。

【0031】

次に、400℃程度の熱処理が実施され、シリサイド反応が発生する。余剰なCo膜10とキャップ膜であるTi膜11が混酸等により除去されると、図8に示される構造が得られる。図8において、周辺トランジスタが形成される領域における第1コンタクトホールC1の底部にCoSi21が形成されている。一方、第2及び第3コンタクトホールC2、C3の底部にはシリサイドは形成されていない。つまり、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成されている。

【0032】

次に、図9に示されるように、周辺トランジスタ領域のコンタクトホールC1内に、CoSi21と接続される第1コンタクトプラグ31が埋め込まれる。第1コンタクトプラグ31とCoSi21は、周辺トランジスタのソース/ドレイン拡散層5と上層配線との間を接続するコンタクトとしての役割を果たす。また、選択トランジスタのゲート電極3上のコンタクトホールC2内に、ワード線(上層配線)と接続される第2コンタクトプラグ32が埋め込まれる。第2コンタクトプラグ32は、ゲート電極3とワード線との間を接続するコンタクトとしての役割を果たす。また、選択トランジスタのセルコンタクトプラグ6上のコンタクトホールC3内に、第3コンタクトプラグ33が埋め込まれる。セルコンタクトプラグ6と第3コンタクトプラグ33との間にはシリサイドは形成されていない。これら第3コンタクトプラグ33と上記セルコンタクトプラグ6は、選択トランジスタの拡散層4とビット線あるいはメモリセルのキャパシタとの間を接続するコンタクトとしての役割を果たす。これら第1〜第3コンタクトプラグ31〜33は、W/TiN/Tiの積層構造を有している。

【0033】

その後、第3コンタクトプラグ33につながるようにメモリセルのキャパシタが形成される。また、所定のパターンを有するワード線、ビット線及び上層配線が形成される。

【0034】

以上に説明されたように、本実施の形態によれば、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1中にのみCoSi21が選択的に形成される。これにより、周辺トランジスタのソース/ドレイン拡散層5につながるコンタクトのコンタクト抵抗が低減される。また、第2コンタクトホールC2の底部にはシリサイドは形成されない。従って、界面数の増加のせいでコンタクト抵抗が上昇することが防止される。更に、第3コンタクトホールC3の底部にはシリサイドは形成されない。従って、凝集によるコンタクト抵抗の増加が抑制される。このように、本実施の形態によれば、全体としてコンタクト抵抗を低減することが可能となる。

【0035】

2.第2の実施の形態

図10〜図12は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。第2の実施の形態において、図5に示された状態までは第1の実施の形態と同様の工程によって製造される。

【0036】

次に、図10に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。

【0037】

次に、光が照射されると可溶性になるポジ型レジストが全面に塗布される。次に、レティクルを用いることなしに全面露光処理が行われる。ここで、上述の通り、基板1上にセルコンタクトプラグ6が形成されているため、第1コンタクトホールC1の底部は、第2及び第3コンタクトホールC2,C3の底部よりも深い場所に位置している。従って、第1〜第3コンタクトホールC1〜C3のうち第2及び第3コンタクトホールC2,C3の穴底にのみ光が届くように露光量を調節することが可能である。つまり、第1コンタクトホールC1底部のポジ型レジストの性質を変えないように露光処理を実施することが可能である。ポジ型レジストの除去工程においては、メモリセルの選択トランジスタ領域、すなわち光が照射された領域のレジストだけが除去される。その結果、図11に示されるように、第1コンタクトホールC1内にのみレジストマスク40が選択的に形成される。

【0038】

次に、上記レジストマスク40を用いたドライエッチングあるいはウェットエッチングにより、Ti膜11及びCo膜10が選択的に除去される。レジストマスク40は第1コンタクトホールC1の穴底に形成されているので、第1コンタクトホールC1底部のTi膜11及びCo膜10は除去されない。一方、ゲート電極3及びセルコンタクトプラグ6上のTi膜11及びCo膜10は除去される。レジストマスク40が除去されると、図12に示された構造が得られる。

【0039】

その後、第1の実施の形態と同様に、400℃程度の熱処理が実施される。これにより、既出の図8で示されたように、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成される。続いて、既出の図9に示されたように、第1〜第3コンタクトプラグ31〜33が第1〜第3コンタクトホールC1〜C3のそれぞれに埋め込まれる。

【0040】

以上に説明された第2の実施の形態によれば、第1の実施の形態と同じ効果が得られる。更に、レティクルを使用することなくフォトレジストをパターニングできるため、微細加工が容易になるという追加的な効果が得られる。

【0041】

3.第3の実施の形態

第3の実施の形態において、図5に示された状態までは第1の実施の形態と同様の工程によって製造される。ここで、図13に示されるように、第1〜第3コンタクトホールC1〜C3の穴径(直径)は、それぞれr1,r2,r3であるとする。また、第1〜第3コンタクトホールC1〜C3の深さは、それぞれt1,t2,t3であるとする。

【0042】

次に、既出の図10に示されるように、CoSiの材料となるCo膜10がスパッタ法により全面に堆積される。また、Co膜10の酸化防止のため、Ti膜11がキャップ膜として全面に堆積される。

【0043】

次に、図14に示されるように、ウエハが水平面から角度θだけ傾けられる。ここで、角度θは、次の関係式(1)を満たすように設定される:

r1/t1<tanθ≦r2/t2≦r3/t3 ・・・(1)

この状態でスパッタエッチングが実施されると、Co膜10とTi膜11は部分的にスパッタエッチングされることになる。具体的には、第2コンタクトホールC2及び第3コンタクトホールC3からはCo膜10とTi膜11が除去されるが、第1コンタクトホールC1の底部からはCo膜10とTi膜11は除去されない。すなわち、第1コンタクトホールC1の底部にのみ金属膜を残すことが可能である(図12参照)。

【0044】

その後、第1の実施の形態と同様に、400℃程度の熱処理が実施される。これにより、既出の図8に示されたように、第1〜第3コンタクトホールC1〜C3のうち、第1コンタクトホールC1の底部にのみCoSi21が選択的に形成される。続いて、既出の図9に示されたように、第1〜第3コンタクトプラグ31〜33が第1〜第3コンタクトホールC1〜C3のそれぞれに埋め込まれる。

【0045】

以上に説明された第3の実施の形態によれば、第1の実施の形態と同じ効果が得られる。更に、第1コンタクトホールC1の底部だけにシリサイドを選択的に形成するために、フォトリソグラフィー技術を行う必要がない。従って、製造プロセスが単純化されるという追加的な効果が得られる。

【図面の簡単な説明】

【0046】

【図1】図1は、従来の半導体記憶装置の製造工程を示す断面図である。

【図2】図2は、従来の半導体記憶装置の製造工程を示す断面図である。

【図3】図3は、従来の半導体記憶装置の製造工程を示す断面図である。

【図4】図4は、従来の半導体記憶装置の製造工程を示す断面図である。

【図5】図5は、本発明の第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図6】図6は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図7】図7は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図8】図8は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図9】図9は、第1の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図10】図10は、本発明の第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図11】図11は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図12】図12は、第2の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図13】図13は、本発明の第3の実施の形態に係る半導体記憶装置の製造工程を示す断面図である。

【図14】図14は、第3の実施の形態に係る半導体記憶装置の製造方法を示す概念図である。

【符号の説明】

【0047】

1 基板

2 素子分離構造

3 ゲート電極(ポリサイドゲート)

4 ソース/ドレイン拡散層

5 ソース/ドレイン拡散層

6 セルコンタクトプラグ

7 層間絶縁膜

10 Co膜

11 Ti膜

12 レジストマスク

21 コバルトシリサイド

31 第1コンタクトプラグ

32 第2コンタクトプラグ

33 第3コンタクトプラグ

40 レジストマスク

C1 第1コンタクトホール(周辺トランジスタのソース/ドレイン上)

C2 第2コンタクトホール(選択トランジスタのゲート上)

C3 第3コンタクトホール(選択トランジスタのソース/ドレイン上)

【特許請求の範囲】

【請求項1】

基板上に形成されたメモリセルと、

前記基板上に形成された周辺トランジスタと

を具備し、

前記メモリセルは、

前記基板上に形成された選択トランジスタと、

前記選択トランジスタに接続されたキャパシタと

を備え、

前記周辺トランジスタの拡散層は第1コンタクトを介して上層配線に接続され、

前記周辺トランジスタ及び前記選択トランジスタのゲートは第2コンタクトを介して上層配線に接続され、

前記選択トランジスタの拡散層は第3コンタクトを介してビット線あるいは前記キャパシタに接続され、

前記第1及び第3コンタクトのうち、前記第1コンタクト中にのみシリサイドが選択的に形成された

半導体記憶装置。

【請求項2】

請求項1に記載の半導体記憶装置であって、

前記シリサイドは、前記第1コンタクトの底部に形成された

半導体記憶装置。

【請求項3】

請求項2に記載の半導体記憶装置であって、

前記第3コンタクトは、

前記選択トランジスタの拡散層上に形成された第1プラグと、

前記第1プラグ上に前記シリサイドを介さずに形成された第2プラグと

を含み、

前記第1コンタクトの底部は、前記第2プラグの底部よりも深い場所に位置する

半導体記憶装置。

【請求項4】

請求項1乃至3のいずれかに記載の半導体記憶装置であって、

前記シリサイドはコバルトシリサイドである

半導体記憶装置。

【請求項5】

(A)基板上にメモリセルの選択トランジスタ及び周辺トランジスタを形成する工程と、

(B)前記選択トランジスタの拡散層上に第1プラグを形成する工程と、

(C)全面に層間絶縁膜を形成する工程と、

(D)前記層間絶縁膜をエッチングすることによって、前記周辺トランジスタの拡散層、前記選択トランジスタ及び前記周辺トランジスタのゲート、及び前記第1プラグのそれぞれに届く第1、第2、第3コンタクトホールを形成する工程と、

(E)前記第1〜第3コンタクトホールのうち、前記第1コンタクトホールの底部にのみシリサイドを選択的に形成する工程と

を有する

半導体記憶装置の製造方法。

【請求項6】

請求項5に記載の半導体記憶装置の製造方法であって、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)前記第1コンタクトホール上にレジストマスクを選択的に形成する工程と、

(c)前記レジストマスクを用いたエッチングにより前記金属膜を選択的に除去する工程と、

(d)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項7】

請求項5に記載の半導体記憶装置の製造方法であって、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)全面にポジ型のレジストを塗布する工程と、

(c)前記第1〜第3コンタクトホールのうち前記第2及び第3コンタクトホールの穴底にのみ光が届くように露光処理を行う工程と、

(d)光が照射された前記レジストを除去することによって、前記第1コンタクトホール内にのみレジストマスクを選択的に形成する工程と、

(e)前記レジストマスクを用いたエッチングにより前記金属膜を選択的に除去する工程と、

(f)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項8】

請求項5に記載の半導体記憶装置の製造方法であって、

前記第1〜第3コンタクトホールの穴径はそれぞれ、r1,r2,r3で表され、

前記第1〜第3コンタクトホールの深さはそれぞれ、t1,t2,t3で表され、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)ウエハを水平面から角度θだけ傾けてスパッタエッチングを実施することによって、前記金属膜の一部を除去する工程と、

ここで、前記角度θは、次の関係式を満たし:

r1/t1<tanθ≦r2/t2≦r3/t3、

(c)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項9】

請求項5乃至8のいずれかに記載の半導体記憶装置の製造方法であって、

更に、

(F)前記シリサイドと上層配線との間を接続するプラグを、前記第1コンタクトホール内に埋め込む工程と、

(G)前記ゲートと上層配線との間を接続するプラグを、前記第2コンタクトホール内に埋め込む工程と、

(H)前記第1プラグと前記メモリセルのキャパシタとを接続する第2プラグを、前記第3コンタクトホール内に埋め込む工程と

を有する

半導体記憶装置の製造方法。

【請求項10】

請求項5乃至9のいずれかに記載の半導体記憶装置の製造方法であって、

前記シリサイドはコバルトシリサイドである

半導体記憶装置の製造方法。

【請求項1】

基板上に形成されたメモリセルと、

前記基板上に形成された周辺トランジスタと

を具備し、

前記メモリセルは、

前記基板上に形成された選択トランジスタと、

前記選択トランジスタに接続されたキャパシタと

を備え、

前記周辺トランジスタの拡散層は第1コンタクトを介して上層配線に接続され、

前記周辺トランジスタ及び前記選択トランジスタのゲートは第2コンタクトを介して上層配線に接続され、

前記選択トランジスタの拡散層は第3コンタクトを介してビット線あるいは前記キャパシタに接続され、

前記第1及び第3コンタクトのうち、前記第1コンタクト中にのみシリサイドが選択的に形成された

半導体記憶装置。

【請求項2】

請求項1に記載の半導体記憶装置であって、

前記シリサイドは、前記第1コンタクトの底部に形成された

半導体記憶装置。

【請求項3】

請求項2に記載の半導体記憶装置であって、

前記第3コンタクトは、

前記選択トランジスタの拡散層上に形成された第1プラグと、

前記第1プラグ上に前記シリサイドを介さずに形成された第2プラグと

を含み、

前記第1コンタクトの底部は、前記第2プラグの底部よりも深い場所に位置する

半導体記憶装置。

【請求項4】

請求項1乃至3のいずれかに記載の半導体記憶装置であって、

前記シリサイドはコバルトシリサイドである

半導体記憶装置。

【請求項5】

(A)基板上にメモリセルの選択トランジスタ及び周辺トランジスタを形成する工程と、

(B)前記選択トランジスタの拡散層上に第1プラグを形成する工程と、

(C)全面に層間絶縁膜を形成する工程と、

(D)前記層間絶縁膜をエッチングすることによって、前記周辺トランジスタの拡散層、前記選択トランジスタ及び前記周辺トランジスタのゲート、及び前記第1プラグのそれぞれに届く第1、第2、第3コンタクトホールを形成する工程と、

(E)前記第1〜第3コンタクトホールのうち、前記第1コンタクトホールの底部にのみシリサイドを選択的に形成する工程と

を有する

半導体記憶装置の製造方法。

【請求項6】

請求項5に記載の半導体記憶装置の製造方法であって、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)前記第1コンタクトホール上にレジストマスクを選択的に形成する工程と、

(c)前記レジストマスクを用いたエッチングにより前記金属膜を選択的に除去する工程と、

(d)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項7】

請求項5に記載の半導体記憶装置の製造方法であって、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)全面にポジ型のレジストを塗布する工程と、

(c)前記第1〜第3コンタクトホールのうち前記第2及び第3コンタクトホールの穴底にのみ光が届くように露光処理を行う工程と、

(d)光が照射された前記レジストを除去することによって、前記第1コンタクトホール内にのみレジストマスクを選択的に形成する工程と、

(e)前記レジストマスクを用いたエッチングにより前記金属膜を選択的に除去する工程と、

(f)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項8】

請求項5に記載の半導体記憶装置の製造方法であって、

前記第1〜第3コンタクトホールの穴径はそれぞれ、r1,r2,r3で表され、

前記第1〜第3コンタクトホールの深さはそれぞれ、t1,t2,t3で表され、

前記(E)工程は、

(a)全面に前記シリサイドの材料となる金属膜を堆積する工程と、

(b)ウエハを水平面から角度θだけ傾けてスパッタエッチングを実施することによって、前記金属膜の一部を除去する工程と、

ここで、前記角度θは、次の関係式を満たし:

r1/t1<tanθ≦r2/t2≦r3/t3、

(c)熱処理によって前記第1コンタクトホールの底部に前記シリサイドを形成する工程と

を含む

半導体記憶装置の製造方法。

【請求項9】

請求項5乃至8のいずれかに記載の半導体記憶装置の製造方法であって、

更に、

(F)前記シリサイドと上層配線との間を接続するプラグを、前記第1コンタクトホール内に埋め込む工程と、

(G)前記ゲートと上層配線との間を接続するプラグを、前記第2コンタクトホール内に埋め込む工程と、

(H)前記第1プラグと前記メモリセルのキャパシタとを接続する第2プラグを、前記第3コンタクトホール内に埋め込む工程と

を有する

半導体記憶装置の製造方法。

【請求項10】

請求項5乃至9のいずれかに記載の半導体記憶装置の製造方法であって、

前記シリサイドはコバルトシリサイドである

半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2007−180181(P2007−180181A)

【公開日】平成19年7月12日(2007.7.12)

【国際特許分類】

【出願番号】特願2005−375412(P2005−375412)

【出願日】平成17年12月27日(2005.12.27)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成19年7月12日(2007.7.12)

【国際特許分類】

【出願日】平成17年12月27日(2005.12.27)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]