半導体記憶装置

【課題】高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

半導体記憶装置に関するものである。

【背景技術】

【0002】

セキュリティーを要する分野において、秘密鍵や複数者間の認証処理におけるチャレンジデータなどを生成するために、乱数発生器が用いられる。

【0003】

近年では、例えば、スマートフォンやタブレットPCなど、回路規模および消費電流の制約が厳しい環境においても、商用コンテンツの利用や課金・決済などに用いるために性能のよい乱数を必要とする環境が増えてきている。

【0004】

一方で、ここで例に挙げたスマートフォンやタブレットPCなどのモバイル機器においては、不揮発性メモリとして、例えば、NAND型フラッシュメモリ等が主流として用いられている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−55205号公報

【特許文献2】特開2008−117471号公報

【特許文献3】特開2004−326867号公報

【特許文献4】特開2008−269473号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【課題を解決するための手段】

【0007】

実施形態によれば、一態様に係る半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイと、乱数を発生させる乱数発生回路と、前記メモリセルアレイおよび前記乱数発生回路を制御するコントローラとを具備し、前記乱数生成回路は、生成した制御パラメータにより前記メモリセルを読み出したデータにもとづく乱数パラメータを生成させる乱数制御回路と、前記乱数パラメータをシード値として用いて前記乱数を発生させる擬似乱数生成回路とを備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る半導体記憶装置の全体構成例を示すブロック図。

【図2】図1中のブロック(BLOCK)を示す等価回路図。

【図3】消去状態のメモリセルを示す断面図。

【図4】電子を注入する際のメモリセルを示す断面図。

【図5】書き込み状態のメモリセルを示す断面図。

【図6】電子を放出する際のメモリセルを示す断面図。

【図7】2値メモリセルの閾値分布を示す図。

【図8】ベリファイ動作有無の閾値分布を示す図。

【図9】多値メモリセルの閾値分布を示す図。

【図10】多値メモリセルの劣化モードの閾値分布を示す図。

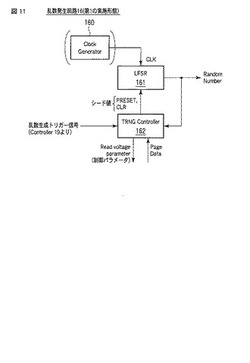

【図11】第1の実施形態に係る乱数発生回路を示すブロック図。

【図12】図11中の擬似乱数発生回路の構成例を示す等価回路図。

【図13】図11中の乱数制御回路の構成例を示すブロック図。

【図14A】図13中の制御パラメータ発生回路の構成例を示すブロック図。

【図14B】ページアドレス設定回路によって読み出し対象に設定されたページに記録されるデータを示す図。

【図15】図13中の積算回路の構成例を示すブロック図。

【図16】図15中の積算回路の構成例を示すブロック図。

【図17】制御パラメータによるデータ読み出しを示す図。

【図18】制御パラメータによるデータ読み出しを示す図。

【図19】制御パラメータと閾値分布との関係を示す図(MLC)。

【図20】制御パラメータと閾値分布との関係を示す図(SLC)。

【図21】第2の実施形態に係る乱数発生回路を示すブロック図。

【図22】第3の実施形態に係る乱数発生回路を示すブロック図。

【図23】第4の実施形態に係る乱数発生回路を示すブロック図。

【図24】第5の実施形態に係るシステムを示すブロック図。

【図25】比較例1に係るプロトコルを示すブロック図。

【図26】比較例2に係るプロトコルを示すブロック図。

【図27】第6の実施形態に係る構成例を示すブロック図。

【図28】第6の実施形態に係る認証フローを示すフロー図。

【図29】第7の実施形態に係る構成例を示すブロック図。

【図30】第7の実施形態に係る認証フローを示すフロー図。

【図31】第8の実施形態に係る構成例を示すブロック図。

【図32】第8の実施形態に係る認証フローを示すフロー図。

【図33】第8の実施形態に係る秘密情報のデータ転送を示すブロック図。

【図34】第9の実施形態に係る構成例を示すブロック図。

【図35】第9の実施形態に係る認証フローを示すフロー図。

【図36】第10の実施形態に係る構成例を示すブロック図。

【図37】第10の実施形態に係る認証フローを示すフロー図。

【図38】第11の実施形態に係る構成例を示すブロック図。

【図39】第11の実施形態に係る認証フローを示すフロー図。

【図40】第12の実施形態に係る構成例を示すブロック図。

【図41】第12の実施形態に係る認証フローを示すフロー図。

【図42】第13の実施形態に係るID retrieval process(1)を示すブロック図。

【図43】第13の実施形態に係るID retrieval process(2)を示すブロック図。

【図44】第13の実施形態に係るID retrieval process(3)を示すブロック図。

【図45】第13の実施形態に係るID retrieval process(4)を示すブロック図。

【図46】第14の実施形態に係るID biding process(1)を示すブロック図。

【図47】第14の実施形態に係るID biding process(2)を示すブロック図。

【図48】第15の実施形態に係る構成例を示すブロック図。

【図49】第16の実施形態に係る構成例を示すブロック図。

【図50】第17の実施形態に係る構成例を示すブロック図。

【発明を実施するための形態】

【0009】

[乱数発生器(乱数発生回路)について]

まず、実施形態の説明の前に、乱数発生器(乱数発生回路)の概要について説明する。

【0010】

上述のように、セキュリティーを要する分野において、秘密鍵や複数者間の認証処理におけるチャレンジデータなどを生成するために、乱数発生器が用いられる。この乱数発生器は、大別すると、以下の2つに分類される。

【0011】

第1には、確定的乱数発生器(Deterministic RNG)もしくは疑似乱数発生器(Pseudo RNG)と呼ばれているものがある。これらの乱数発生器は、所定の初期値(シード)を設定することで乱数を発生する。確定的乱数発生器の例としては、FIPS 140-2 Annex Cに列挙されている暗号器に基づくものや、簡易的なものとしては線形帰還シフトレジスタ(LFSR:Linear Feedback Shift Resistor)からなるM系列発生器などが存在する。確定的乱数発生器は、ソフトウェア単独、ハードウェア単独、両者の併用など、の構成をとることができる。

【0012】

第2には、不確定的乱数発生器(Nondeterministic RNG)もしくは物理乱数発生器(Physical RNG)と呼ばれているものであり、主としてハードウェアから構成される。不確定的乱数発生器の例としては、電気回路の熱雑音(ジョンソンノイズ)を増幅した回路や、高速発振回路と非周期の平滑化回路による構成などが存在する。

【0013】

ここで、上記乱数発生器から生成される乱数として要求される主な性能としては、以下の3つの性能がある。

【0014】

「予測困難性」:予測困難性とは、観測された乱数から、次段の乱数を予測できないことをいう。そのためには、例えば、非周期性、非規則性等が求められる。

【0015】

「一様性」:一様性とは、出力される乱数において、0と1との出現確率が統計的に同等であることをいう。

【0016】

「長周期性」:長周期性とは、出力される乱数が再度出力される周期が十分に長いことをいう。

【0017】

ここで、一様性、長周期性については、確定的乱数発生器として上に例として挙げたM系列発生器を適切なレジスタ段数で構成することで実現可能である。一方で、予測困難性については、M系列発生器では観測された乱数列から容易にM系列発生器の構成が判明するため、出力乱数が予測でき、要求性能を満たすことが困難である。このため、コンテンツ保護や決済用セキュリティーの秘密鍵生成などに用いる場合、前述のFIPS 140-2 Annex Cに列挙された暗号器に基づくものを用いるか、もしくはICカードなどでは不確定的乱数発生器を独自の方法構成することなどが必要である。

【0018】

しかしながら、暗号器に基づく確定的乱数発生器は、ハードウェアにより実現する場合は多倍長演算回路や多段非線形回路などを要し、通常数10K〜100Kゲート以上の回路規模を要する。一方で、不確定的乱数発生器として例に挙げた熱雑音増幅回路でも、熱雑音は大きい場合でも数十μV で、演算増幅器や差動アンプを使い、4 〜 5 桁増幅して、更に0と1 のバランスを調整する回路が付加されるため、回路規模は大きくなる。また、高速発振回路と非周期の平滑化回路による構成でも、発振回路が持つ周期性が乱数に残ってしまう傾向があり、更に消費電流が大きくなるという傾向がある。

【0019】

そのため、上記のように、回路規模および消費電流の制約が厳しい環境においては、上記に挙げたものを適用することは困難である。

【0020】

近年では、上述したように、スマートフォンやタブレットPCなど、回路規模および消費電流の制約が厳しい環境においても、商用コンテンツの利用や課金・決済などに用いるために性能のよい乱数を必要とする環境が増えてきている。

【0021】

一方で、ここで例に挙げたスマートフォンやタブレットPCなどのモバイル機器においては、不揮発性メモリとして、例えば、NAND型フラッシュメモリ等が主流として用いられるという現状がある。

【0022】

そのため、NAND型フラッシュメモリ等の半導体記憶装置が、乱数生成機能を有している場合の利用価値は高い。

【0023】

そこで、以下の実施形態では、半導体記憶装置として、NAND型フラッシュメモリを一例に挙げ、半導体記憶装置内に乱数発生器を構成する具体例について提案する。

【0024】

以下、実施形態について図面を参照して説明する。この説明においては、半導体記憶装置の一例として、NAND型フラッシュメモリを挙げて説明するが、これに限られることはない。尚、この説明においては、全図にわたり共通の部分には共通の参照符号を付す。

【0025】

[第1の実施形態]

第1の実施形態に係る半導体記憶装置について、図1乃至図20を用いて説明する。

【0026】

<1.構成例>

1−1.全体構成例

まず、図1を用い、第1の実施形態に係る半導体記憶装置の全体構成例について説明する。図示するように、本例では、NAND型フラッシュメモリが一例として示される。

【0027】

本例に係るNAND型フラッシュメモリは、メモリセルアレイ11、乱数発生回路16、制御回路19、ビット線制御回路52、カラムデコーダ53、データ入出力バッファ54、データ入出力端子55、ワード線駆動回路56、制御信号入力端子58、電源発生回路59を備える。

【0028】

メモリセルアレイ11は、複数のブロック(BLOCK1〜BLOCKn)により構成される。複数のブロック(BLOCK1〜BLOCKn)のそれぞれは、ワード線およびビット線の交差位置に配置される複数のメモリセルを備える。詳細については、後述する。

【0029】

乱数発生回路16は、外部から入力される乱数トリガーコマンドに伴い制御回路19から出力される乱数トリガー信号に従い、所定の乱数を必要に応じて発生させる。発生された乱数は、制御回路19の制御に従い、秘密鍵や認証処理におけるチャレンジデータの生成などに用いられ、また必要に応じて、データ入出力端子55を介して外部のホスト装置に送信される。

【0030】

本例に係る乱数発生回路16は、所定の初期値(シード値)を設定することで乱数を発生させる擬似乱数発生回路等を備えるものであり、擬似乱数発生回路としては、例えば、線形帰還シフトレジスタ(LFSR: Linear Feedback Shift Resistor)等がある。詳細については、後述する。

【0031】

ビット線制御回路52は、ビット線を介してメモリセルアレイ11中のメモリセルのデータを読み出し、ビット線を介してメモリセルアレイ11中のメモリセルの状態を検出する。また、ビット線制御回路52は、ビット線を介してメモリセルアレイ11中のメモリセルに書き込み制御電圧を印加してメモリセルに書き込みを行う。

【0032】

ビット線制御回路52内には、図示しないページバッファ等のデータ記憶回路が設けられ、このデータ記憶回路は、カラムデコーダ53によって選択される。データ記憶回路に読み出されたメモリセルのデータは、データ入出力バッファ54を介してデータ入出力端子55から外部へ出力される。

【0033】

データ入出力端子55は、例えば、外部のホスト装置等に接続される。データ入出力端子55は、例えば8ビット、または16ビットのバス幅を有している。NAND型フラッシュメモリはトグルモードインターフェース(toggle mode interface)などの高速インターフェース規格をサポートしてもよい。トグルモードインターフェースでは、例えば、データストローブ信号(DQS)の立ち上がり、立ち下がり両エッジに同期してデータ入出力端子55を介したデータ転送が行われる。

【0034】

ホスト装置は、例えば、マイクロコンピュータ等であって、データ入出力端子55から出力されたデータを受ける。ホスト装置は、NAND型フラッシュメモリの動作を制御する各種コマンドCMD(書き込みコマンド、読み出しコマンド、消去コマンド、ステータスリードコマンド、乱数トリガーコマンド等)、アドレスADD、およびデータDTを出力する。ホスト装置からデータ入出力端子55に入力された書き込みデータDTは、データ入出力バッファ54を介して、カラムデコーダ53によって選択された上記データ記憶回路(図示せず)に供給される。一方、コマンドCMDおよびアドレスADDは、制御回路19に供給される。

【0035】

ワード線駆動回路56は、制御回路19の制御に従い、メモリセルアレイ11中のワード線を選択し、選択されたワード線に読み出し、書き込みあるいは消去に必要な電圧を印加する。

【0036】

電圧発生回路59は、制御回路19の制御に従い、図示中の接続された上記構成回路の動作に必要な電圧を供給する。例えば、電圧発生回路59は、ホスト装置から供給される外部電圧を昇圧して、読み出し、書き込みあるいは消去時にワード線に印加される電圧を生成する。

【0037】

制御回路(Controller)19は、NAND型フラッシュメモリの全体の動作を制御するために、接続される各回路に必要な制御信号および制御電圧を与える。制御回路19は、メモリセルアレイ11、乱数発生回路16、ビット線制御回路52、カラムデコーダ53、データ入出力バッファ54、ワード線駆動回路56、電圧発生回路59に接続される。接続された上記構成回路は、制御回路19によって制御される。

【0038】

制御回路19は、制御信号入力端子58に接続され、ホスト装置から制御信号入力端子58を介して入力されるWE(ライト・イネーブル)信号、RE(リード・イネーブル)信号、ALE(アドレス・ラッチ・イネーブル)信号、CLE(コマンド・ラッチ・イネーブル)信号等の制御信号の組み合わせによって制御される。

【0039】

ここで、機能的に表現すれば、上記ワード線駆動回路56、ビット線制御回路52、カラムデコーダ53、制御回路19は、データ書き込み回路、データ読み出し回路、およびデータ消去回路を構成する。ホスト装置は、NAND型フラッシュメモリが書き込み、読み出し、消去などの内部動作を実行中であるか否かを、図示せぬRY/BY(レディー/ビジー)信号出力端子をモニタすることで検知する。制御回路19は、RY/BY信号出力端子を介して、RY/BY信号を出力する。

【0040】

1−2.ブロック(BLOCK)の構成例

次に、図2を用い、第1の実施形態に係るメモリセルアレイを構成するブロック(BLOCK)の構成例について説明する。ここでは、図1中の一ブロック(BLOCK1)を一例に挙げて説明する。ここで、このブロックBLOCK1中のメモリセルは、一括してデータ消去されるため、ブロックはデータ消去単位である。

【0041】

ブロックBLOCK1は、ワード線方向(WL方向)に配置される複数のメモリセルユニットMUから構成される。メモリセルユニットMUは、WL方向と交差するビット線方向(BL方向)に配置され、電流経路が直列接続される8個のメモリセルMC0〜MC7からなるNANDストリング(メモリセルストリング)と、NANDストリングの電流経路の一端に接続されるソース側の選択トランジスタS1と、NANDストリングの電流経路の他端に接続されるドレイン側の選択トランジスタS2とから構成される。

【0042】

尚、本例では、メモリセルユニットMUは、8個のメモリセルMC0〜MC7から構成されるが、2つ以上のメモリセル、例えば、56個、32個等から構成されていればよく、8個に限定されるというものではない。

【0043】

ソース側の選択トランジスタS1の電流経路の他端はソース線SLに接続される。ドレイン側の選択トランジスタS2の電流経路の他端は、各メモリセルユニットMUに対応してメモリセルユニットMUの上方に設けられ、BL方向に延出するビット線BLm−1に接続される。

【0044】

ワード線WL0〜WL7は、WL方向に延び、WL方向の複数のメモリセルの制御ゲート電極に共通に接続される。選択ゲート線SGSは、WL方向に延び、WL方向の複数の選択トランジスタS1に共通に接続される。選択ゲート線SGDも、WL方向に延び、WL方向の複数の選択トランジスタS2に共通に接続される。

【0045】

また、ワード線WL0〜WL7ごとにページ(PAGE)が存在する。例えば、図中の破線で囲って示すように、ワード線WL7には、ページ7(PAGE7)が存在する。このページ(PAGE)ごとに、後述するデータ読み出し動作、データ書き込み動作が行われるため、ページ(PAGE)はデータ読み出し単位であり、データ書き込み単位である。

【0046】

1−3.メモリセルMCについて

次に、図3乃至図6を用い、セル構成およびデータ書き込み等がされる場合のメモリセルMCについて説明する。

【0047】

図3は、消去状態(Erase state)のメモリセルMCを示す。図示するように、メモリセルMCは、半導体基板(Si-sub)51上に、トンネル絶縁膜(Tunnel Oxide)TO、浮遊ゲート(Floating Gate)FG、ゲート間絶縁膜(Inter-gate Oxide)IGO、および制御ゲート(Control Gate)CGが順次積層され、半導体基板51中にこの積層構造を挟むように隔離してソース(Source)およびドレイン(Drain)が設けられる。

【0048】

消去状態のメモリセルMCは、浮遊ゲートFGに電子が注入されておらず、浮遊ゲートFGは正に帯電している。

【0049】

図4は、浮遊ゲートに電子を注入する(Inserting election)際のメモリセルMCを示す。図示するように、制御ゲートCGに書き込み電圧Vpgmを与えることで、ソースドレインのチャネルを介してトンネル絶縁膜TOをトンネルさせた電子が、浮遊ゲートFGに注入される。以下、浮遊ゲートFGに電子を注入する動作を、データ書き込みと表現する場合がある。

【0050】

図5は、書き込み状態(Programmed state)のメモリセルMCを示す。図示するように、書き込み状態のメモリセルMCは、浮遊ゲートFGに電子が注入されており、浮遊ゲートFGは負に帯電している。浮遊ゲートFGに電子が十分に注入されることにより、書き込み状態のメモリセルMCの閾値電圧は、消去状態のメモリセルMCの閾値電圧よりも高くなる。メモリセルMCは、この閾値電圧の変化を利用してデータを記憶する。

【0051】

図6は、浮遊ゲートから電子を放出する(Extracting election)際のメモリセルMCを示す。図示するように、半導体基板51に消去電圧Veraを与えることで、浮遊ゲートFGに注入された電子を、トンネル絶縁膜TOをトンネルさせて、半導体基板51に放出する。以下、浮遊ゲートFGから電子を放出する動作を、データ消去と表現する場合がある。

【0052】

なお、本例の場合、データ書き込み、データ読み出しは、上述のページ(PAGE)単位で行われる。また、データ消去は、上述のブロック(BLOCK)単位で行われる。

【0053】

1−4.閾値電圧分布について

次に、メモリセルの閾値電圧分布について説明する。

【0054】

1−4−1.2値メモリセル(SLC:Single Level Cell)の閾値分布

まず、図7を用い、2値メモリセル(SLC:Single Level Cell)の閾値分布について説明する。

【0055】

2値メモリセルの閾値分布(Vth分布)では、上記に示した動作により、メモリセルにデータを記録した後において、図示するような’1’、’0’の分布を示す。ここでは、消去状態(Erase state)に’1’を割り当て、書き込み状態(Programmed state)に’0’を割り当てている。

【0056】

なお、データ書き込み動作およびデータ消去動作の際には、書き込み電圧または消去電圧の印加後に、各メモリセルの閾値電圧を検査し、目標レベルに到達しないセルについては再度データ書き込み、またはデータ消去動作を継続的に制御して行うベリファイ(Verify)動作を行う。そのため、’1’、’0’分布には、上記ベリファイ動作が完了した否かを判定するためのベリファイレベル(Verify level)が設けられる。

【0057】

ここで、制御の例としては、制御回路(Controller)19により、データ書き込み動作において、制御ゲートに印加する電圧を増す、電圧印加時間を増す、電圧印加回数を増す等を複合的に行うことで、各メモリセルの閾値電圧を目標レベルに到達させる。また、データ消去においても、同様に、半導体基板51中のpウェル(Pwell)に印加する電圧を増す、電圧印加時間を増す、電圧印加回数を増すなどを複合的に行うことで、各メモリセルの閾値電圧を目標レベルに到達させる。このようにして、書き込まれたデータは、図示するように所定の’1’、’0’の分布幅を持つ。

【0058】

データの読出しにおいては、’0’分布と’1’分布との中間に読み出し電圧(Threshold of read level)を設定することで、各メモリセルがいずれのデータを保持しているかを判別する。具体的には、制御ゲートCGに読み出し電圧を印加した際に、メモリセルMCがオン状態となれば’1’と判別し、メモリセルMCがオフ状態のままであれば’0’と判別する。

【0059】

1−4−2.ベリファイ動作について

次に、図8を用い、ベリファイ動作前後の閾値分布について説明する。

【0060】

図8(a)は、上記ベリファイ動作を行わない場合(Without verify)の閾値分布を示す。図8(b)は、上記ベリファイ動作を行った場合(With verify)の閾値分布を示す。

【0061】

図示するように、ベリファイ動作を行った場合のほうが、行わない場合に比べて、閾値分布が狭くなる。これは、個々のメモリセルによって1回の書き込み電圧の印加で注入される電子の量にばらつきがあり、早く書き込まれるメモリセルと、遅く書き込まれるメモリセルとが存在するためである。

【0062】

図8(a)では、ベリファイ動作を行わないため、既に十分電子が注入されたメモリセルに対しても書き込みが継続され、結果として閾値分布全体が広がっている。一方図8(b)では、1回の書き込み電圧の印加毎に各メモリセルの閾値電圧を検査し、ベリファイレベルに到達したメモリセルについては以降の電子注入を禁止(抑制)し、ベリファイレベルに到達しないメモリセルについては再度書き込み電圧を印加して電子注入を継続する。結果として、ベリファイ動作を行わない場合と比較して、閾値分布は狭くなる。

【0063】

1−4−3.多値メモリセル(MLC:Multi Level Cell)の閾値分布

次に、図9を用い、多値メモリセル(MLC:Multi Level Cell)の閾値分布について説明する。

【0064】

多値メモリセルでは、上記した書き込み状態(Programmed state)における電子の注入量を細かく制御することで、例えば1個のメモリセルに2ビットを保持する場合は4つの閾値分布を形成し、また1個のメモリセルに3ビットを保持する場合は8つの閾値分布を形成する。

【0065】

多値メモリセルの閾値分布(Vth分布)のうち、本例では、1個のメモリセルに2ビットのデータを記録する例を示す。そのため、4つの閾値分布に対して、閾値電圧の低い方から順に、図示するような’11’、’01’、’00’、’10’を割り当てる。なお、以下では便宜的に、4つの閾値分布を閾値電圧の低い方から順に’E’レベル、’A’レベル、’B’レベル、’C’レベルと記載する場合がある。

【0066】

多値メモリセルのデータ書き込みの場合でも、上記2値メモリセルのデータ書き込みと同様に、目標とする閾値電圧に到達するよう、適宜書き込み動作を制御する。また、’11’、’01’、’00’、’10’分布には、同様にそれぞれベリファイレベル(Verify level)が設けられる。

【0067】

多値メモリセルにおいて、データ読み出しの際には、各分布の中間において、読み出しの電圧TH1, TH2, TH3を設定することで、各メモリセルが’11’、’01’、’00’、’10’のいずれのデータを保持しているかを判別する。

【0068】

ここで、TH2以上か否かによって識別可能なビットすなわち以下図面におけるMSBビットと、TH1以上かつTH3以下か否かによって識別可能なビットすなわち以下図面におけるLSBビットは、各々異なるページにアサインされることが多く、各々Lower page、Upper pageなどと呼ばれる。つまり、TH1, TH2, TH3を同時に用いて1つのページを読み出すのではなく、Lower pageを読み出す場合はTH2を、Upper pageを読み出す場合はTH1及びTH3を用いる。

【0069】

1−4−4.劣化モードの閾値分布

まず、図10を用い、劣化モードの閾値分布について説明する。ここでは、多値メモリセルにおける劣化モードを一例に挙げる。

【0070】

上記のように、メモリセルにデータを書き込んだ後、同メモリセルもしくは同メモリセルに近接メモリするセルに対してデータ読出しやデータ書込み動作を行うと、同セルの制御ゲートCGと半導体基板51中のpウェル(Pwell)との間で、書き込み電圧よりも小さいが所定の電圧が印加されるため、弱い書込み状態となり、閾値電圧が高い方向へとシフトする(Direction of read / program disturb)。これは、リードディスターブ、プログラムディスターブと称され、閾値分布の幅が広くなり、読み出し性能の劣化を生じ得る。これらディスターブは、NAND型フラッシュメモリの利用状況によって大きく左右される。

【0071】

メモリセルが受けるプログラムディスターブの影響に関しては、例えば、特開2008−117471号公報(米国特許番号7613048として登録された米国出願11/934330が優先権基礎として主張する)に開示されている。メモリセルが受けるリードディスターブの影響に関しては、例えば、特開2004−326867号公報(米国特許番号7099190として登録された米国出願10/822177が優先権基礎として主張する)に開示されている。これらの全内容は参照により組み込まれる。

【0072】

一方、メモリセルにデータを書き込んだ後、一定期間放置すると、浮遊ゲートFG中に保持されている電子がデトラップされ、閾値電圧が低い方向へとシフトする(Direction of data retention)。これは、データリテンションと呼ばれ、閾値分布の幅が広くなり、読み出し性能の劣化を生じ得る。データリテンションは、放置時間、放置時の温度・湿度などの環境によって大きく左右される。また、メモリセルの書き換え回数(例えば、消去回数)が多くなると、データリテンションが悪化することが知られている。

【0073】

メモリセルのデータリテンション特性に関しては、例えば、特開2008−269473号公報(米国出願12/107984が優先権基礎として主張する)に開示されており、これらの全内容は参照により組み込まれる。

【0074】

このほか、データ書き込みの直後において、トンネル酸化膜TOにトラップされた電子が、浮遊ゲートFGにトラップされた電子と見掛け上区別がつかないため、これが抜け落ちるか否かで閾値電圧が変化するという現象も生じ得る。例えば、本例のようなNAND型フラッシュメモリの場合、製造プロセス微細化に伴って高密度化されているため、浮遊ゲートFGに保持できる電子量が減少し、トンネル酸化膜TOにトラップされた電子の相対寄与率が上がることから、劣化モードとして大きな要因となり得る。

【0075】

以上のように、NAND型フラッシュメモリのメモリセルは、その利用状況、利用環境などの多様な要因により、データ書込み後の閾値電圧分布の状態が変動する。また、再生時の環境においても、温度など利用環境により、閾値電圧分布は一定ではない。更に、それら特性は、製造時のばらつきによっても大きく変動するため、各NAND型フラッシュメモリにおける各メモリセルの状態を予測することはほぼ不可能といえる。

【0076】

そこで、本例では、もともとNAND型フラッシュメモリが物理的に有するこの予測困難性を、乱数生成回路16における予測困難性に利用する。そのことで、回路規模および消費電力の増大を極小化でき、高性能な乱数を生成することができる。具体的な構成等については、後述する。

【0077】

なお、本例では、半導体記憶装置として、NAND型フラッシュメモリを一例に挙げて説明しているが、これに限られることはない。例えば、DRAM(Dynamic Random Access Memory)やMRAM(Magnetic Random Access Memory)等の半導体記憶装置においても、NAND型フラッシュメモリと同様に、読み出しデータ等がばらつく現象が発生しているからである。

【0078】

1−5.乱数発生回路16について

次に、図11を用い、第1の実施形態に係る乱数発生回路16の構成例について説明する。

図示するように、第1の実施形態に係る乱数生成回路16は、クロック発生回路160、線形帰還シフトレジスタ161、およびTRNGコントローラ162を備える。

【0079】

クロック発生回路(Clock Generator)160は、所定のクロックCLKを、線形帰還シフトレジスタ161に供給する。なお、クロック発生回路160は、必ずしも乱数発生回路160内に配置される必要はなく、NAND型フラッシュメモリが有するものから必要なクロックCLKを供給されても良い。または、NAND型フラッシュメモリ外部から供給されるクロックCLKを用いても良い。

【0080】

線形帰還シフトレジスタ(LFSR: Linear Feedback Shift Resistor)(擬似乱数発生回路)161は、供給された動作クロックCLKにより、所定の初期値を以って動作を開始し、TRNGコントローラ162から入力される信号PRESET, CLRにより、乱数(Random Number)を発生させる。

【0081】

TRNGコントローラ(TRNG Controller)(乱数制御回路)162は、制御回路(Controller)19から供給される乱数生成トリガー信号を受け取り、処理を開始する。ここで、制御回路(Controller)19からから供給される乱数生成トリガー信号としては、NAND型フラッシュメモリの外部のホスト装置から入力された乱数生成に係わる要求コマンド(乱数トリガーコマンド)などを用いて発生させた信号などを用いても良い。あるいは、NAND型フラッシュメモリに新たな制御信号入力端子を追加し、当該制御信号入力端子からの入力に従い乱数生成トリガー信号を生成しても良い。

【0082】

TRNGコントローラ162は、乱数生成トリガー信号を受領後、LFSR161から入力された乱数を用いて、読み出し電圧設定パラメータ(Read voltage parameter)を設定する。読み出し電圧設定パラメータ(Read voltage parameter)は、この乱数生成回路16の外部にあるデータ入出力バッファ54等を介して、制御回路(Controller)19へと出力される。または、乱数生成回路16から制御回路(Controller)19へ直接読み出し電圧設定パラメータ(Read voltage parameter)を出力しても良い。

【0083】

続いて、制御回路(Controller)19は、同読み出し電圧設定パラメータ(Read voltage parameter)に従って、メモリセルアレイ11に対してデータ読み出し動作を行う。このデータ読み出し処理がなされたデータ(Page Data)は、順次、ビット線制御回路52中のページバッファ等を介して、TRNG Controller162へと入力される。

【0084】

続いて、TRNG Controller162は、読み出しデータに依存したPRESET値(シード値)を生成し、同PRESET値をLFSR161へと供給する。

【0085】

続いて、LFSR161は受領したPRESET値を自身のレジスタに格納し、これをシード値として利用し、乱数を生成する。

【0086】

上記一連の動作により、LFSR161の初期動作時に設定されているシード値が固定であっても、乱数生成トリガー信号が入力されるまでの時間自身が乱数生成パラメータとして寄与する。さらに、同LFSR161から出力される乱数によって定められた読み出し電圧設定パラメータ(Read voltage parameter)により、読み出しデータが変化するため、これを再度LFSR161のシード値としてセットすることにより、乱数性を向上させることができる。

【0087】

ここで、乱数生成トリガー信号が、LFSR161の動作開始時から常に固定時間経過後に入力された場合では、読み出し電圧設定パラメータ(Read voltage parameter)は、固定となる。しかし、その場合でも前述のように、NAND型フラッシュメモリが有する劣化モードや、環境依存性などにより、読み出されるデータは一意ではないため、シード値も変化することが十分に期待できる。

【0088】

尚、本構成例では、LFSR161を利用する形態について示したが、要求レベルに応じて他の疑似乱数発生器などを代わりに用いることも可能である。例えば、より高度な乱数生成機能を提供したい場合、TRNG Controller162を物理乱数シードとして利用し、LFSR161に代わってFIPS 140-2に示されているようなAES(Advanced Encryption System)暗号に基づく疑似乱数発生器や、楕円曲線暗号に基づく疑似乱数発生器、離散対数暗号に基づく疑似乱数発生器などを用いることも可能である。これに対して、本実施形態に係る乱数生成回路16は、疑似乱数発生器の弱点ともなり得るシード設定方法に対して有効な解決策と言える。

【0089】

その他、前記一連の動作を更に複数回繰り返すことで、乱数性を更に向上させることができる。すなわち、仮にLFSR161が出力する読み出し電圧設定パラメータ(Read voltage parameter)が固定化され、読み出したデータの乱数性が低い場合においても、1bitでも異なっていれば、次段の処理に用いる読み出し電圧設定パラメータ(Read voltage parameter)も異なるため、乱数性が向上する。

【0090】

1−5−1.線形帰還シフトレジスタ(LFSR)161の構成例

次に、図12を用い、第1の実施形態に係る線形帰還シフトレジスタ(LFSR: Linear Feedback Shift Resistor)161の構成例について説明する。

図示するように、第1の実施形態に係る線形帰還シフトレジスタ(LFSR)161は、複数のレジスタ回路RG1〜RG16および排他的論理和回路XOR1〜XOR4から構成される。

【0091】

複数のレジスタ回路RG1〜RG16のそれぞれのPRE端子にはレジスタ設定信号受領部としてTRNGコントローラ162よりPRESET信号が入力され、CLR端子にはレジスタ設定信号受領部としてTRNGコントローラ162よりCLR信号が入力され、D端子にはデータ入力部としてXOR4の出力または前段のレジスタ回路の出力が入力され、C端子にはクロック入力部としてクロック発生回路160よりクロックCLKが入力され、Q端子はデータ出力部として出力データを出力する。複数のレジスタ回路RG1〜RG16は、前段の出力Qが次段の入力Dとなるように直列に接続される。

本例では、後述するように16ビットの例を示すために、最終段のレジスタ回路RG16の出力Qを乱数(Random Number)として用いる。必要なビット数に応じて、必要なレジスタ回路RG1〜RG16の出力Qを乱数(Random Number)として用いることが可能である。

【0092】

排他的論理和回路XOR1〜XOR4は、その入力および出力が直列に接続される。排他的論理和回路XOR4の他方の入力はレジスタ回路RG12の出力Qに接続され、出力はレジスタ回路RG1の入力Dに接続される。排他的論理和回路XOR3の他方の入力はレジスタ回路RG13の出力Qに接続され、出力は排他的論理和回路XOR4の入力に接続される。排他的論理和回路XOR2の他方の入力はレジスタ回路RG14の出力Qに接続され、出力は排他的論理和回路XOR3の入力に接続される。排他的論理和回路XOR1の入力はレジスタ回路RG15、16の出力Qに接続され、出力は排他的論理和回路XOR2の入力に接続される。

【0093】

上記レジスタ回路RG1〜RG16と同様に、排他的論理和回路XOR1〜XOR4についても、必要なビット数および対応するレジスタ回路RGに合わせて、必要に応じて配置することが可能である。

【0094】

本例のような疑似乱数の生成に用いる場合、最大巡回周期を有する多項式に従って、LFSR161中のレジスタ回路RG1〜16と排他的論理和回路XOR1〜XOR4とが接続される。本例のような構成によって出力された乱数系列は、M系列などと称される。

【0095】

1−5−2.TRNGコントローラ(TRNG Controller)162の構成例

次に、図13を用い、第1の実施形態に係るTRNGコントローラ(TRNG Controller)162の構成例について説明する。

図示するように、TRNG コントローラ(乱数制御回路)162は、読み出し電圧設定パラメータ発生回路162Aおよび積算回路162Bにより構成される。

【0096】

読み出し電圧設定パラメータ発生回路(Read voltage parameter generator)(パラメータ発生回路)162Aは、LFSR161の出力(output)を乱数生成トリガー信号によってラッチした後、LFSR出力を後述するパラメータに展開して、読み出し電圧設定パラメータ(Read voltage parameter)として出力する。

【0097】

積算回路(Accumulators)162Bは、メモリセルアレイ11より読み出した読み出しデータ(Page Data)を受領した後、積算処理を行い、ランダムシード値(Random seed)を、LFSR161へ出力する。このランダムシード値(Random seed)は、LFSR161のレジスタ設定用パラメータである上記PRESET信号, CLR信号の形式として出力される。

【0098】

1−5−3.パラメータ発生回路(Read voltage parameter generator)162Aの構成例

次に、図14Aを用い、上記図13中のパラメータ発生回路(Read voltage parameter generator)162Aの構成例について説明する。

図示するように、パラメータ発生回路162Aは、ページアドレス設定回路(Page address setting)162A−1、読出し電圧設定回路(Vth level setting)162A−2を備える。

【0099】

ページアドレス設定回路(Page address setting)162A−1は、コントローラ19からの乱数生成トリガー信号を受けて、LFSR161の出力値を用いて、読み出すPage addressの制御パラメータを生成する。これは、各Pageに記録されているデータが異なる場合、ベースとなるデータを変更することが乱数性の向上に更に寄与するためである。

【0100】

ここで、図14Bを用いて、ページアドレス設定回路162A−1によって読み出し対象に設定されたページに記録されているデータについて説明する。読み出し対象ページに記録されているデータは、乱数列によって撹拌されたデータであること、NAND型フラッシュメモリ毎に異なるデータを含むこと、同ページ内のデータは外部から読み出すことができないこと、所定タイミングで更新されること、などを満たしていることが望ましい。

【0101】

乱数列によって撹拌されたデータであること(Randomized data)、については、後述するように読み出されたデータは所定サイズ毎に区切られたセグメント単位で積算処理をするため、セグメント内においてデータの偏りがないことが望ましいためである。仮に、セグメント内のデータに偏りがあった場合、例えばデータの全てが1、もしくは0であった場合、設定された読出し電圧によっては読み出しデータの変動が生じない場合が起こりうるためであり、1と0の生起確率ができるだけ同じ、すなわち乱数列によって撹拌されたデータであることが望ましい。

【0102】

NAND型フラッシュメモリ毎に異なるデータを含むこと(Chip unique data)、については、全てのデータが全てのNAND型フラッシュメモリチップで共通である場合、読出し電圧と読み出しデータ間の関係において、全チップで共通の傾向が生じる可能性があるためであり、少なくとも一部のデータが異なっていることが望ましい。

【0103】

同ページ内のデータは外部から読み出すことができないこと(Read inhibited area)、については、読み出しページ内のデータが攻撃者に入手されるか否かによって、攻撃の難易度が大きく異なるためである。例えば、何らかの手法により読み出し電圧が攻撃者に取得された場合、ページに記録されているデータと前記読み出し電圧の組み合わせから、フリップする可能性のあるビットを予想する難易度は、攻撃者がデータを把握しているか否かによって大きく異なるためである。

【0104】

所定タイミングで更新されること(Renewal data)、については記録されているデータの少なくとも一部が更新されると、読み出すデータが必ず異なることが保証され、ひいてはランダムシード値が必ず更新されるためである。更新のタイミングとしては、NAND型フラッシュメモリの電源立ち上げ後、NAND型フラッシュメモリに乱数生成に係わるコマンドが入力された後、乱数生成後、などが考えられる。更新データとしては、更新用データフィールドをページデータの一部に設けて、同フィールド内のデータの加算による更新、同フィールド内のデータとして生成した乱数を記録、同フィールド内のデータとして記録済みデータと生成した乱数の排他的論理和を記録、などの方法が考えられる。

【0105】

読出し電圧設定回路(Vth level setting)162A−2は、コントローラ19からの乱数生成トリガー信号を受けて、LFSR161の出力値を用いて、セルアレイからページを読み出す際の読み出し電圧の制御パラメータを生成する。

【0106】

上記回路162A−1、162A−2が生成する両パラメータが、読み出し電圧設定パラメータ(Read voltage parameter)信号として出力される。それは、読み出すページが、多値メモリセルの前述のLower page、Upper pageのどちらに相当するかによって、読出し電圧設定回路(Vth level setting)162A−2から出力される必要なパラメータが相違してくるからである。

【0107】

1−5−4.積算回路(Accumulators)162Bの構成例

次に、図15を用い、上記図13中のTRNG Controller162内の積算回路(Accumulators)162Bの構成例について説明する。

図示するように、積算回路(Accumulators)162Bは、複数の積算回路(Accumulator)(1)-(N)を有し、読みだしたページデータ(Page Data)からLFSR161へのシード設定値(Accumulated data)を算出する。

【0108】

メモリセルアレイ11より読み出され、複数の積算回路(Accumulator)(1)-(N)に入力されるページデータ(Page Data)は、所定のデータ長毎に分割され、各々積算処理がなされる。分割された各データをセグメント(Segment 1- N)と呼ぶ。積算回路(Accumulator)(1)-(N)は、セグメントのビット加算を行う。ここで、ビット加算とは排他的論理和を用い、すなわちセグメント内のビットにおいて、1の個数が奇数であれば1を、偶数であれば0を出力する。

【0109】

複数の積算回路(Accumulator)(1)-(N)の個数は、必要に応じて配置すれば良い。例えば、本例では、LFSR161への出力ビットが、16ビットであれば良いため、積算回路の個数は、16個(N=16)である。

【0110】

本例に係る積算回路(Accumulators)162Bの構成により、積算処理をすることによって、仮に読出しデータのほとんど全てが前回の読出しデータと同じであっても、1ビットでも異なるものが存在すれば積算結果が異なるため、情報エントロピーを増加させる効果があり、そのため乱数性の向上に寄与できる。

【0111】

また、各セグメント毎(Segment 1- N)に算出された積算データは、各々LFSR161のシード設定値へと利用される。

【0112】

尚、本例では、複数の積算回路を有する場合を記しているが、単一の積算部のみを用い、セグメント境界毎にリセットを行う構成も同様に可能である。

【0113】

また、以下のように単一のレジスタ回路と単一の排他的論理和回路から構成されるフィードバックレジスタを用いるだけで、積算部を構成することが可能である。

【0114】

1−5−4.積算回路(Accumulator)(1)の構成例

次に、図16を用い、上記図15中の積算回路(Accumulator)の構成例について説明する。ここでは、積算回路(Accumulator)(1)を例に挙げる。

【0115】

図示するように、本例に係る積算回路(Accumulator)(1)は、排他的論理和回路XOR0およびレジスタ回路RG0から構成される。

【0116】

排他的論理和回路XOR0の入力にはセグメントデータ(Segment Data(1))、レジスタ回路RG0の出力Qが入力され、出力はレジスタ回路RG0の入力Dに接続される。

【0117】

レジスタ回路RG0には、それぞれクロックCLK、プリチャージ信号PRE、クリア信号CLRが入力され、出力端子Qから積算信号(Accumulated data)が出力される。

【0118】

このように、本例に係る積算回路(Accumulator)では、単一のレジスタ回路と単一排他的論理和回路から構成されるフィードバックレジスタのみで構成することが可能である。その他の積算回路(Accumulator)(2)-(N)についても同様である。

【0119】

<2.制御パラメータ(Read voltage parameter)によるデータ読み出し動作>

次に、図17乃至図20を用い、上記構成例により設定される読み出し電圧設定パラメータ(Read voltage parameter)によるデータ読み出し動作について説明する。

【0120】

2−1.多値メモリセルにおけるデータ読み出し('A', 'B', 'C')

まず、図17を用い、多値メモリセルにおける読み出し電圧設定パラメータによるデータ読み出しについて説明する。図示するように、ここでは、読み出し電圧TH1’/Th2’/Th3’を、閾値電圧分布’A’、’B’、’C’の中心基準とする場合である。

【0121】

TRNGコントローラ(TRNG Controller)162によって指定された読み出し電圧設定パラメータ(Read voltage parameter)は、制御回路19の制御により、メモリセルアレイ11の所定ページを読み出す際の読み出し電圧として利用される。

【0122】

通常のデータ読出しにおいて、データ読み出し基準(読み出し電圧)は、図示するTH1/Th2/Th3のように、各閾値電圧分布の間の中間レベルを目標に設定されている。

【0123】

しかしながら、本例に係る読み出し電圧設定パラメータ(Read voltage parameter)によれば、各閾値電圧分布の分布’A’、’B’、’C’の中心点、すなわち図中の読み出し電圧TH1’/Th2’/Th3’を、データ読み出し基準として設定する。このように、データ読み出し基準を、各閾値電圧分布の分布’A’、’B’、’C’の中心に設定することで、微小な閾値電圧レベルの変動においても、検出ビットのフリップ数を最大化することが可能となる。

【0124】

より具体的には、閾値電圧分布の分布’A’、’B’、’C’の中心点を基準とし、一定の幅を読み出し電圧TH1’/Th2’/Th3’の設定範囲とし、同範囲内において、LFSR161から出力された乱数を基に、TRNG Controller162は読み出し電圧設定パラメータ(Read voltage parameter)を選択する。詳細については、後述する。

【0125】

2−2.多値メモリセルにおけるデータ読み出し('E', 'A', 'B')

次に、図18を用い、多値メモリセルにおける制御パラメータによるデータ読み出しについて説明する。

【0126】

図示する例は、読み出し電圧TH1’/Th2’/Th3’を、閾値電圧分布’E’、’A’、’B’の中間レベルを目標に設定する点で、上記図17に示した例と相違する。

【0127】

必要に応じて、このように設定することも同様に可能である。

【0128】

2−3.読み出し電圧設定パラメータ(Read voltage parameter)と閾値電圧との関係(MLC)

次に、図19を用い、2−1及び2−2において説明した多値メモリセル(MLC)における読み出し電圧設定パラメータ(Read voltage parameter)と閾値電圧との関係について、両例を包含した具体的なパラメータ設定方法を説明する。

【0129】

上記パラメータ設定回路(Vth parametter setting)162A−2が出力する読み出し電圧設定パラメータ(Read voltage parameter)と、多値モードにおける各閾値電圧の関係例は、図示するようになる。

【0130】

図示するように、本例では、閾値電圧分布’E’、’A’、’B’、’C’について、読み出し電圧設定パラメータ(Read voltage parameter)によって、合計0レベルから32レベルまで選択する場合の例が示される。

【0131】

例えば、閾値電圧分布’E’では、閾値電圧分布’E’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を0レベルから7レベルまで所定間隔で区切っている。閾値電圧分布’A’では、閾値電圧分布’ A’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を8レベルから15レベルまで所定間隔で区切っている。閾値電圧分布’B’では、閾値電圧分布’ B’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を16レベルから23レベルまで所定間隔で区切っている。閾値電圧分布’C’では、閾値電圧分布’ C’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を24レベルから31レベルまで所定間隔で区切っている

2−3.読み出し電圧設定パラメータ(Read voltage parameter)と閾値電圧との関係(SLC)

次に、図20を用い、2値メモリセル(SLC:Single Level Cell)における読み出し電圧設定パラメータ(Read voltage parameter)と閾値電圧との関係について説明する。

【0132】

図示するように、閾値電圧分布’E’、’A’について、読み出し電圧設定パラメータ(Read voltage parameter)によって、合計0レベルから15レベルまで選択する場合の例が示される。

【0133】

例えば、閾値電圧分布’E’では、閾値電圧分布’E’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を0レベルから7レベルまで所定間隔で区切っている。閾値電圧分布’A’では、閾値電圧分布’A’の中心点を基準とし、一定の幅を設定範囲として設け、同範囲を8レベルから15レベルまで所定間隔で区切っている。

【0134】

この2値メモリセルの場合では、LFSR161の出力値4bitの値を10進数表現した値が上記Level iに各々相当する。SLC記録の場合、読み出し電圧パラメータ(Read voltage parameter)は、単一のため、LFSR161の出力値4bitによって選択された一つの閾値電圧パラメータをTH’として用いる。

【0135】

<3.作用効果>

第1の実施形態に係る半導体記憶装置によれば、少なくとも下記(1)乃至(4)の効果が得られる。

【0136】

(1)高性能な乱数を生成することができ、予測困難性を向上できる。

上記のように、第1の実施形態に係るNAND型フラッシュメモリは、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数を発生する乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御する制御回路(Controller)19とを少なくとも具備する。

【0137】

乱数生成回路16は、生成した読み出し電圧設定パラメータ(Read voltage parameter)によりメモリセルMCを読み出したデータにもとづく乱数パラメータ(PRESET, CLR)を生成する乱数制御回路162と、乱数パラメータ(PRESET,CLR)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

【0138】

上記のように、本例に係る乱数発生回路16は、メモリセルMCを読み出したデータにもとづく乱数パラメータ(PRESET,CLR)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161を備える。

【0139】

このように、本例では、第一に、乱数を生成させる構成として、NAND型フラッシュメモリの読出しデータにおける閾値電圧分布の時変性を利用することができる。

【0140】

より具体的には、図10を用いた劣化モードの閾値電圧分布において説明したように、NAND型フラッシュメモリのメモリセルは、その利用状況、利用環境などの多様な要因により、データ書き込み後の閾値電圧分布の状態が変動する。また、再生時の環境においても、温度など利用環境により、閾値電圧分布は一定ではない。更に、それら特性は、製造時のばらつきによっても大きく変動するため、各NAND型フラッシュメモリにおける各メモリセルの状態を予測することはほぼ不可能といえる。

【0141】

このように、本例では、もともと本来的にNAND型フラッシュメモリが物理的に有するこの予測困難性を、乱数生成回路16が生成する乱数(Random number)の予測困難性に利用することができる。

【0142】

従って、高性能な乱数(Random number)を生成することができ、予測困難性を向上できる点で有利である。

【0143】

(2)乱数の一様性と長周期性とを保証することができる。

さらに、乱数生成回路16が備える擬似乱数生成回路161は、発生させた乱数(Random number)を乱数制御回路162に再び帰還させる。

【0144】

上記構成によれば、第二に、生成された高性能な上記乱数(Random number)を、乱数制御回路162のいわば初期値として再び用いることで、乱数(Random number)の一様性と長周期性とを保証することができる。

【0145】

(3)乱数発生回路16の回路規模および消費電力の増大を極小化できる。

上記のように、本例では、乱数発生回路16が乱数を生成させる構成として、もともと本来的にNAND型フラッシュメモリが物理的に有する予測困難性を利用する。

【0146】

従って、本例に係る乱数発生回路16は、高度な乱数を発生させるために、回路規模を増大させる必要もなく、また消費電力の増大もなく、これらを極小化できる点で有利である。

【0147】

このように、本例に係る乱数発生回路16は、回路規模および消費電流の制約が厳しい、例えば、近年のスマートフォンやタブレットPCなどの環境においても、商用コンテンツの利用や課金・決済などに用いるための高性能な乱数を発生させるものとして適用することが可能となる。

【0148】

一方で、ここで例に挙げたスマートフォンやタブレットPCなどのモバイル機器においては、不揮発性メモリとして、例えば、NAND型フラッシュメモリ等が主流として用いられるという現状がある。

【0149】

そのため、本例のように、NAND型フラッシュメモリが、コントローラ19と独立した乱数生成回路16を備える構成の利用価値は高いと言える。また、製造コストの低減に対しても有利である。

【0150】

(4)シード値(RESET, CLR)の情報エントロピーを高め、乱数性を向上できる。

本例に係る乱数制御回路162は、乱数を乱数生成トリガー信号トリガーとしてラッチして閾値電圧の読み出し電圧設定パラメータ信号(Read voltage parameter)を生成するパラメータ発生回路162Aと、読み出しデータ(Page Data)について積算処理を行ったシード値(RESET, CLR)を生成する積算回路162Bとを備える。

【0151】

上記の構成のように、メモリセルアレイ11から読み出されたデータ(Page Data)は、積算回路162Bによる所定のセグメント単位での積算による平滑化処理を行うことで、発生されるシード値(RESET, CLR)の情報エントロピーを高めることができる。

【0152】

そのため、情報エントロピーを高め、乱数性を向上できる点で有利である。

【0153】

[第2の実施形態(乱数発生回路のその他の構成例)]

次に、第2の実施形態に係る半導体記憶装置について、図21を用いて説明する。この実施形態は、乱数発生回路16のその他の構成例に関するものである。この説明において、上記第1の実施形態と重複する部分の詳細な説明を省略する。

【0154】

<乱数発生回路16の構成例>

図21に示すように、第2の実施形態に係る乱数生成回路16は、LFSR1(161−1)、LFSR2(161−2)およびTRNG Controller162を備え、LFSR1(161−1)およびLFSR2(161−2)には、Clock Generator 1(160−1)およびClock Generator 2(160−2)より動作クロックCLK1, CLK2がそれぞれ供給される点で、上記第1の実施形態と相違する。

【0155】

Clock Generator 1(160−1)は、外部から供給されるフリーラントリガー信号によって、動作がイネーブルされる。ここで、フリーラントリガー信号としては、例えば、NAND型フラッシュメモリのインターフェースにおけるチップ・イネーブル信号(CE)、アドレス・ラッチ・イネーブル信号(ALE)、コマンド・ラッチ・イネーブル信号(CLE)を用いても良い。また、前記イネーブル信号は、単独で用いてもよいし、複合的に用いてもよい。更に、他の信号、例えばリード・イネーブル信号(RE)、ライト・イネーブル信号(WE)などを用いてもよい。Clock Generator 1(160−1)は、フリーラントリガー信号がONの場合に動作し、LFSR1にクロックCLK1を供給する。

【0156】

LFSR1(161−1)は、供給されたクロックCLK1により、所定の初期値を持って動作を開始し、乱数1を段数1として出力する。前記外部から供給されるイネーブル信号の供給時間によって、LFSR1(161−1)が動作する期間、すなわちLFSR1(161−1)から出力される値は更新されていく。

【0157】

TRNG Controller162は、コントローラ19から供給される乱数生成トリガー信号を受け取り、処理を開始する。ここで外部から供給される乱数生成トリガー信号としては、NAND型フラッシュメモリの外部から入力された乱数生成に係わる要求コマンドなどをトリガーとして発生させた信号などを用いる。TRG Controller162は、トリガー信号を受領後、LFSR1(161−1)から入力された乱数1を用いて、読み出し電圧設定パラメータ(Read voltage parameter)を設定する。

【0158】

同読み出し電圧設定パラメータ(Read voltage parameter)は、乱数生成回路16の外部へと出力され、NAND型フラッシュメモリのコントローラ19、同パラメータに従って所定のセルアレイに対してデータ読出し処理を行う。前記読出し処理がなされたデータは、順次TRNG Controller162へと入力される。TRNG Controller162は、読み出しデータに依存したシード値(PRESET, CLR)を生成し、同シード値を段数2としてLFSR2へと供給する。

【0159】

LFSR2(161−2)は、受領したシード値(PRESET, CLR)を、内包するレジスタに格納し、このシード値を用いて、乱数(Random Number)を生成する。

【0160】

本例のLFSR1(161−1)、LFSR2(161−2)およびTRNG Controller162は、上記第1の実施形態で説明したLFSR(擬似乱数発生回路)161およびTRNG Controller(乱数制御回路)162と同様の構成である。

【0161】

なお、Clock Generator 1(160−1)とClock Generator 2(160−2)は乱数生成回路16の内部に有していてもよいし、NAND型フラッシュメモリが有するクロック生成器を流用してもよい。また、Clock Generator 2(160−2)を用意せず、Clock Generator 1(160−1)のクロックをLFSR1(161−1)及びLFSR2(160−2)の動作クロックとして供給してもよい。NAND型フラッシュメモリがもともと有するクロック生成器と乱数生成回路16に用いるクロック生成器では、要求される動作周波数帯が異なる場合が多く、また動作が必要とするタイミングも異なる。例えば、NAND型フラッシュメモリが有するクロック生成器は、例えば、数十〜数百メガヘルツ等の高速周波数で動作する必要があるが、乱数生成回路16においては生成する乱数のサイズ及び要求動作時間にもよるが、一般には低速であってもよい。この場合、高速なNAND型フラッシュメモリがもともと有するクロック生成器とは別に、本例のような低速なクロック生成器を用意することで、消費電力の低減に寄与できる。

【0162】

また、NAND型フラッシュメモリの一般動作に用いるクロックとしては出来るだけクロックの品質が良い方が望ましいが、乱数生成回路16として見た場合は、動作クロックの品質にばらつきがある方が望ましい。これは、品質ばらつきが予測困難性に寄与するためである。ここでいう品質とは、例えばクロックジッタの量や、温度変化によるクロック周波数変動性などである。また、本例のように、クロック生成器を複数用意することは、前述の品質ばらつき要因を増やすことに相当し、乱数性の向上に寄与する。これらは、乱数性の要求性能と回路サイズ・消費電力などのペナルティをどのように設計するかに依存する。本例では、いずれにおいても適用することが可能である。

【0163】

その他の構成、動作等に関しては、上記第1の実施形態と実質的に同様である。

【0164】

<作用効果>

第2の実施形態に係る半導体記憶装置によれば、少なくとも上記(1)乃至(4)と同様の効果が得られる。

【0165】

さらに、第2の実施形態に係る乱数生成回路16は、LFSR1(161−1)、LFSR2(161−2)およびTRNG Controller162を備え、LFSR1(161−1)およびLFSR2(161−2)には、Clock Generator 1(160−1)およびClock Generator 2(160−2)より動作クロックCLK1, CLK2がそれぞれ供給される。

【0166】

このように、擬似乱数発生回路であるLFSR1(161−1)、LFSR2(161−2)を2つに分ける構成により、LFSR1(161−1)とLFSR2(161−2)とに入力される信号の長さの違いを利用し、長期周期性を更に向上できる点で有利である。

【0167】

本例では、Clock Generator 1(160−1)に入力されるフリーラント信号と、Clock Generator 2(160−2)に入力される乱数トリガー信号との長さの違いを利用して、段数1としての乱数1と、段数2としてのシード値(PRESET, CLR)とを生成する。そのため、本例では、段数1は、段数2よりも小さい(段数1<段数2)方が望ましい。

【0168】

Clock Generator 1(160−1)、Clock Generator 2(160−2)のバリエーションに関しては、上述の通りである。

【0169】

[第3の実施形態(乱数発生回路のその他の構成例)]

次に、第3の実施形態に係る半導体記憶装置について、図22を用いて説明する。この実施形態は、乱数発生回路16のその他の構成例に関するものである。この説明において、上記説明と重複する部分の詳細な説明を省略する。

【0170】

<乱数発生回路16の構成例>

図22に示すように、第3の実施形態に係る乱数生成回路16は、LFSR1のシード設定に加えて、LFSR2から出力される疑似乱数に対して、更にTRNG Controller162から出力される物理乱数を用いるための排他的論理和回路XOR9をさらに備える点で、上記第2の実施形態と相違する。

【0171】

<作用効果>

第3の実施形態に係る半導体記憶装置によれば、少なくとも上記(1)乃至(4)と同様の効果が得られる。

【0172】

第3の実施形態に係る乱数生成回路16は、LFSR1のシード設定に加えて、LFSR2から出力される疑似乱数に対して、更にTRNG Controller162から出力される物理乱数を用いるための排他的論理和回路XOR9をさらに備える。

【0173】

上記構成により、シード値のみならず、TRNG Controller162から出力される物理乱数を加えることにより、出力される乱数列(Random number)自体にも予測困難性を付与することが可能となる。従って、より乱数性を向上できる点で更に有利である。

【0174】

なお、TRNG Controller162から出力される物理乱数のみだと、乱数の要件である一様性が保証できない場合には、疑似乱数と組み合わせても良い。

【0175】

[第4の実施形態(乱数発生回路のその他の構成例)]

次に、第4の実施形態に係る半導体記憶装置について、図23を用いて説明する。この実施形態は、乱数発生回路16のその他の構成例に関するものである。この説明において、上記説明と重複する部分の詳細な説明を省略する。

【0176】

<乱数発生回路16の構成例>

図23に示すように、第4の実施形態に係る乱数生成回路16は、LFSR1(161−1)に対してもTRNG Controller162からのシード値(PRESET, CLR)が入力されることにより、シード設定処理を行う点で、上記第3の実施形態と相違する。

【0177】

<作用効果>

第4の実施形態に係る半導体記憶装置によれば、少なくとも上記(1)乃至(4)と同様の効果が得られる。

【0178】

第4の実施形態に係る乱数生成回路16の構成によれば、LFSR1(161−1)に対してもTRNG Controller162からのシード値(PRESET, CLR)が入力されることにより、読出し電圧設定パラメータ自身の乱数性を向上できる。

【0179】

そのため、ひいては最終的に出力される乱数列(Ramdom Number)の向上に寄与することができる点で有利である。

【0180】

[第5の実施形態(システムの一例)]

次に、第5の実施形態に係るシステムについて、図24を用いて説明する。第5の実施形態に係るシステムは、上記実施形態に係る半導体記憶装置を含めたシステム例に関するものである。この説明において、上記説明と重複する部分の詳細な説明を省略する。

【0181】

<システム構成例>

図24に示すように、第5の実施形態に係るシステムは、例えばeMMC、SD(登録商標)Card等が適用され得る上記第1乃至第4の実施形態に係る半導体装置100と、例えばPC、Smart phone、Tablet PC等が適用され得るホスト装置200とを備えるものである。

【0182】

半導体記憶装置100は、上記の乱数発生回路16としてのRNGを備える。さらに、コントローラ19は、クリプトエンジン190を備える点で、上記実施形態と相違する。

【0183】

クリプトエンジン190は、乱数発生回路16が生成した乱数を、ホスト装置200からの乱数要求に応じて、安全な経路(Secure channel)199を通じて、ホスト装置側のクリプトエンジン290に通知する。

【0184】

ホスト装置200は、クリプトエンジン190と、アプリケーションインターフェイス210と、所定のアプリケーション220を備える。

【0185】

その他の構成、動作等に関しては、上記第1の実施形態と実質的に同様である。

【0186】

<作用効果>

第5の実施形態に係る半導体記憶装置によれば、少なくとも上記(1)乃至(4)と同様の効果が得られる。

【0187】

さらに、本例では、コントローラ19が、乱数発生回路16が生成した乱数を、ホスト装置200からの乱数要求に応じて、安全な経路(Secure channel)199を通じて、ホスト装置側のクリプトエンジン290に通知するクリプトエンジン190を備える。

【0188】

このように、クリプトエンジン190が、安全な経路(Secure channel)を通じて、乱数発生回路16が生成した乱数を通知することで、システム全体の安全性をより向上できる点で有利である。

【0189】

以下、上記第1乃至第5の実施形態に係る乱数発生回路16により発生させた乱数を用いて、認証を行う具体例について、さらに比較例1、2および第7乃至第16の実施形態を用いて説明する。

【0190】

[比較例1(HB+プロトコルの一例)]

まず、図25を用い、比較例1について説明する。この比較例1は、HB+プロトコルの一例に関するものである。

【0191】

HB+プロトコルは、2000年にHopper とBlumらによって提案された、軽量の認証プロトコルであるHBプロトコルの改良プロトコルである。HBプロトコルは、雑音下におけるパリティ値の同定が困難であるということ(LPN:Learning Parity with Noise)に基づいており、受動攻撃に対する安全性が証明されている。ただし、HBプロトコルは、リーダー(Reader)へのなりすましといった能動攻撃に対して脆弱性がある。この点を解決するために、2005年にJuelsらにより、HB+プロトコルとして提案されたものである。

【0192】

HB+プロトコルの概要は、図25のように図示される。ここで、図25中の、a,b,x,yはベクトルであり、ν,zはビットである。

【0193】

図示するように、HB+プロトコルでは、被認証コンポーネントであるタグ(Tag)と、認証コンポーネントであるリーダー(Reader)とが、各々秘密情報ベクトルx, yを共有する。

【0194】

タグは、リーダーに対して一時乱数ベクトルbを渡す。

【0195】

続いて、リーダーは、タグに対して一時乱数ベクトルaを渡す。

【0196】

続いて、タグは、乱数aと秘密情報ベクトルxの内積(a・x)および乱数bと秘密情報ベクトルyとの内積(b・y)を計算する。さらに、タグは、ηの確率で1となる変数νを生成する。そして、内積(a・x)、内積(b・y)、変数νをそれぞれ加算して、z= ax(+)by(+)νを算出する。ここで、axは内積(a・x)を意味し、(+)は排他的論理和を意味する。

【0197】

続いて、タグは、算出したzを、リーダーへと送信する。

【0198】

続いて、リーダーは、受領したzと、自身で計算したax(+)byとを比較し、一致不一致を検査する。上記一連の処理を1単位として1ラウンドと称することもある。

【0199】

これら上記1ラウンドの処理を複数回(例えば、数十回〜数万回程度)繰り返し、前述の不一致確率が、所定値tを下回った場合、タグが秘密情報を保持しているとみなし、認証が成功する。

【0200】

尚、ax(+)byは、秘密情報x,yと、結合ベクトルa,bとのそれぞれの内積である。そのため、x,yの結合ベクトルxyを秘密情報とおき、a,bの結合ベクトルをConcat(a,b)とした場合、ax(+)byをConcat(a,b)xyと表現することも可能である。

【0201】

[比較例2(Random HB#プロトコルの一例)]

次に、図26を用い、比較例2について説明する。この比較例2は、Random HB#プロトコルの一例に関するものである。Random HB#プロトコルは、上記比較例1に示したHB+プロトコルが更に改良されたプロトコルである。

【0202】

上記HB+プロトコルは、受動的な攻撃と能動的な攻撃に対して解決策を提供したものの、Gilbertらによって提案された中間者攻撃に対して脆弱性がある傾向にある。この点を解決するために、GilbertらによりHB+プロトコルの改良方式プロトコルとして、Random HB#プロトコルとして提案されたものである。

【0203】

Random HB#プロトコルの概要は、図26のように図示される。ここで、図26中のX,Yは行列であり、a,b,z,νはベクトルである。

図示するように、Random HB#プロトコルでは、タグ(Tag)とリーダー(Reader)とが、各々秘密情報行列X, Yを共有する。

【0204】

まず、タグは、リーダーに対して一時乱数ベクトルbを渡す。

【0205】

続いて、リーダーは、タグに対して一時乱数ベクトルaを渡す。

【0206】

続いて、タグは、乱数aと秘密情報行列xとの内積(aX)および乱数bと秘密情報行列yとの内積(bY)を計算する。ここで、X, Yは行列、a, bはベクトルであることから、各々の内積結果は、ベクトルとなる。また、タグは、ηの確率で1となる変数ベクトルνを生成する。そして、タグは、上記の値を加算して、z= aX(+)bY(+)νを算出する。ここでzはベクトルである。

【0207】

続いて、タグは、算出したzを、リーダーへと送信する。

【0208】

続いて、リーダーは、受領したzと自身で計算したaX(+)bYとのビット加算、すなわち排他的論理和演算を行った結果を用い、aX(+)bY(+)zのハミング重みHwt(aX(+)bY(+)z)を計算する。ハミング重みHwt(aX(+)bY(+)z)が、所定値t*clenを下回った場合、タグが秘密情報を保持しているとみなし、認証が成功する。ただし、η≦t<0.5、clenはAX(+)BYのビット長とする。

【0209】

尚、aX(+)bYは秘密情報XとYの結合行列とaとbの結合ベクトルの内積であることから、X,Yの結合行列XYを秘密情報とおき、aとbの結合ベクトルをConcat(a,b)とした場合、aX(+)bYをConcat(a,b)XYと表現することも可能である。

【0210】

<実装上の改善点>

しかしながら、上記比較例1、2に係るプロトコルでは、例えば、NAND型フラッシュメモリ等に具体的に実装しようとした場合等に、以下(I)〜(IV)のような改善点が考えられる。

【0211】

(I)秘密情報X及びYの共有手段

前述のように、上記比較例1、2では、リーダーとタグとは、秘密情報X, Yを共有している必要がある。しかしながら、上記比較例1、2では、秘密情報X, Yを共有するための具体的な共有方法が提示されていない。

【0212】

そのため、仮にすべてのリーダーとタグとで同一のX, Yを事前に共有していた場合、一旦X, Yが露見してしまうと、システム全てに致命的な影響を与える。一方でタグ毎に異なるX, Yを適用した場合、リーダー側では全てのタグに適用されているX, Yを保持している、もしくはそれを統合的に管理しているデータベースへのアクセスなどが要求される。

その結果、リーダー側への負担が大きくなる。

【0213】

尚、これに関連する先行技術として、特開2000−357213号公報において、演算処理機能を有する記録媒体に複製コンテンツを記録する記録装置と該記録媒体との間の相互認証方法において、前記記録媒体は、少なくとも該記録媒体に依存する第1の情報と、前記記録装置と相互認証を行う際に該記録装置と共有すべき該記録媒体に依存する第2の情報とを記憶し、前記記録装置は、前記記録媒体から得られた前記第1の情報に基づき該記録媒体との間の相互認証を行う際に用いる認証情報を生成し、この生成された認証情報と前記第2の情報とを用いて前記記録装置と前記記録媒体との間で相互認証を行うことを特徴とする方法が提案されている。

【0214】

(II)コンポーネントPに対し、秘密情報X及びYを効率的に記録する手段

上記HB+プロトコル、Random HB#プロトコルにおいては、いわゆる上記LPN問題を現実的な計算量で同定を困難とするためには相応の秘密情報量、すなわちX, Yは相応のデータサイズである必要がある。ここで、X, Yが全てのタグで共通であれば、ハードワイヤードロジックで構成することも可能であるが、X,Yをタグ毎に異ならせる場合、タグはX, Yを保持するために十分なメモリ容量を持つ必要がある。また、これと同時にタグ製造において同データを個別に記録する必要性があり、記録時間はすなわち製造時間へと反映される。

その結果、メモリ容量の増加と記録時間の増加により、タグのコスト増大を招く。

【0215】

(III)コンポーネントPが保持する秘密情報X及びY損傷に対する保護手段

コンポーネントPが内部メモリにてX, Yを保持している場合、認証に用いる場合は同X, Yのデータ完全性が要求されるが、先行文献ではこれらについて言及されていない。データ完全性を保証するには、タグ内部のメモリにはエラー訂正符号を付与したX, Yを保有し、認証時に訂正処理を行うなどの方法が考えられる。しかしながら、一般に廉価メモリは必ずしも訂正機能を有しているわけではなく、メモリ側に訂正機能がない場合はメモリ以外のタグ内コンポーネントとして同訂正機能を有す必要がある。

その結果、タグのコスト増大を招く。

【0216】

(IV)秘密情報X及びY露見時の秘密情報更新手段

上記Random HB#コンポーネントは、各々受動攻撃、能動攻撃、一定条件下での中間者攻撃に対する耐性が認められているものの、近年では一般化された中間者攻撃に対する脆弱性が報告されるなど、X, Yが露見する可能性を排除することはできない。X, Yの露見には、それ相応の攻撃コストが要求されるものの、一旦X,Yが露見した場合、同X,Yを用いた偽造タグなどの製造が可能となるため、仮にX, Yが露見した場合でも新たなX, Yへと移行できるように、秘密情報の更新手段がある方が望ましい。

【0217】

そこで、上記の点を考慮し、以下において、実施形態について図面を参照して説明する。なお、これまでRFIDのリーダーとタグとを一例にとって説明をした。しかしながら、同様の要件はNAND型フラッシュメモリなどの回路面積が即座にコストに直結するメモリチップにおいても同様である。そのため、以下実施形態では、認証コンポーネントとしてのリーダー(Reader)としてNAND型フラッシュメモリを認証するホストデバイス(Host)、被認証コンポーネントとしてのタグ(Tag)としてNAND型フラッシュメモリ(NAND chip)を、一例に挙げて説明する。しかし、これに限られることはない。例えば、NOR型フラッシュメモリ、抵抗変化式メモリ(ReRAM: Resistive Random Access Memory)、磁気抵抗メモリ(MRAM: Magnetoresistive Random Access Memory)、相変化メモリ(PRAM: Phase change Random Access Memory)、および強誘電体メモリ(FeRAM: Ferroelectric Random Access Memory)、ハードディスクドライブやソリッドステートドライブなどの演算機能及びメモリを有するストレージデバイス、RFIDやICカードなどの認証を要するコンポーネント、汎用演算素子と汎用メモリを有した計算器とソフトウェアから構成されるシステムなど、多様な実装形態に適用できる。尚、この説明においては、全図にわたり共通の部分には共通の参照符号を付す。

【0218】

[第6の実施形態]

図25および図26を用い、第6の実施形態に係る認証コンポーネント、被認証コンポーネントおよびその認証方法について説明する。

【0219】

<11.構成例(メモリシステム)>

まず、図27を用い、第6の実施形態に係る構成例について説明する。

図27に示すメモリシステムは、被認証コンポーネントであるNANDフラッシュメモリ10、認証コンポーネントであるホストデバイス20、両者を仲介するコントローラ19を備える。図示するように、ホスト20は、コントローラ19と呼ばれるNAND型フラッシュメモリ10に対するアクセス機能を有したデバイスを経由してNAND型フラッシュメモリにアクセスする。

【0220】

ここで、半導体製品の製造工程について記載する。半導体製品の製造工程は、主に基板ウエハー上に回路を形成する前工程と、前記ウエハーを個片に切り分けた後、配線や樹脂パッケージ封入などを行う後工程に分けられる。ここで、コントローラ19は、前工程においてNAND型フラッシュメモリ10内に包含されるよう構成される場合、前工程においては包含されないが後工程において同一パッケージに包含されるよう構成される場合、NAND型フラッシュメモリ10とは異なるチップの形態をとる場合、など様々な場合がある。図27を含め、以下ではコントローラ19は、NAND型フラッシュメモリ10とは異なるチップの形態をとる場合を例にとっている。しかしながら、本実施形態は、上記いずれのケースにおいても適用可能である。以下、特に断りのない限り、ホストデバイス20とNAND型フラッシュメモリ10間のデータや命令のやり取りにおいては、多くの場合コントローラが仲介するものであるが、これは省略することとする。なお、NAND型フラッシュメモリ10およびコントローラ19の構成例については、後述する。

【0221】

図27に示す各コンポーネント、データ処理については、以下の通り説明する。図示するように、秘密情報X, Yを共有する方法と、同方法をNAND型フラッシュメモリ10に適用する場合の構成が示される。

【0222】

11−1.NAND型フラッシュメモリ

NAND型フラッシュメモリ10は、被認証コンポーネントである。本例に係るNAND型フラッシュメモリ10は、セルアレイ11、およびセルアレイ11の周辺領域に配置されるデータキャッシュ12、圧縮演算回路13、バイアスドRNG14、出力部15、乱数生成器16、順序交換回路18、ビット毎加算回路C1等を備える。

【0223】

セルアレイ(Cell array)11には、図示しないビット線およびワード線の交差位置にマトリックス状に複数のメモリセルが配置される。メモリセルは、半導体基板上に順次、トンネル絶縁膜、浮遊ゲート、層間絶縁膜、およびワード線と接続される制御ゲートをそれぞれ備える。ビット線方向のメモリセルの電流経路は直列接続され、セルユニットを形成する。セルユニットは、ビット線、ソース線に接続される選択トランジスタにより選択される。ワード線方向の複数のメモリセルは、データ読み出しおよびデータ書き込みの単位である1ページ(Page)を形成する。また、複数のページはデータ消去の単位であるブロック(Block)を形成する。

【0224】

セルアレイ(Cell array)11は、ロム領域11−1、秘匿領域11−2、一般領域11−3を備える。

ロム領域(Rom area)11−1は、データ記録が禁止され、データ読み出しが許可される領域である。本例に係るロム領域11−1には、秘密情報XYを暗号化し、更に訂正符号が付与されたデータXYE(xe bits)が記録される。暗号化には、対称鍵暗号であるAES(Advanced Encryption Standard)などの暗号器を、暗号モードはCTR(Counter)、CBC(Cipher block chain)などを利用しても良いし、非対称暗号であるECDSA(楕円曲線暗号)やRSAなどを利用しても良い。また誤り訂正符号としては、BCH符号、Reed Solomon符号、LDPC(Low density parity check)符号などを利用してもよい。このように、本例は、いずれの暗号方法、訂正符号にも適用することが可能である。ここで、XYEとは、秘密情報XYが暗号化され、更に訂正符号が付与されたものとして表記される。また、(xe bits)とは、ビット数を表記する。

【0225】

秘匿領域(Hidden area)11−2は、NAND型フラッシュメモリ10の外に対してはデータ記録が禁止され、データ読出も禁止される領域である(Read Program inhibit)。本例に係る秘匿領域11−2には、上記認証に用いるX, Yに対応するデータXYが記録される。

【0226】

一般領域(User area)11−3は、データ記録およびデータ読み出しのいずれも自由に可能な領域である。一般領域11−3には、例えば、写真などの画像データや、動画データ等が記録される。

【0227】

尚、上記におけるロム領域、秘匿領域、一般領域は、物理的構成を異ならせることで実現してもよいし、物理的構成は同一であるがNAND型フラッシュメモリ内の論理的制御で実現してもよい。ここで、論理的制御とは、領域ごとにNAND型フラッシュメモリ外からのアクセスを制御する識別子を設け、これを保持し、NAND型フラッシュメモリが外部から当該領域へのアクセスを受領した際に、同識別子によってアクセス制御を行う、などの方法である。

【0228】

また、セルアレイ(Cell array)11を構成する個々のメモリセルは、複数ビットを記憶するものであってもよいし(MLC: Multi Level Cell)、1ビットを記憶するものであってもよい(SLC: Single Level Cell)。更に、ロム領域及び秘匿領域についてはSLCで利用する構成とし、一般領域についてはMLCで利用する構成としてもよい。この時、SLC領域とMLC領域とはセルアレイの物理的構成が異なっていてもよいし、MLCとして利用可能なメモリセルの一部のビットのみを使用して、疑似的なSLC領域として利用してもよい。

【0229】

データキャッシュ(Data Cache)12は、セルアレイ11から読出したデータを一時的に記憶する。

【0230】

バイアスドRNG(Biased RNG)14は、所定確率ηにて1となる乱数νを生成する。尚、バイアスドRNGの入力元として下記の乱数生成器を用いてもよく、その場合乱数生成器から出力される複数の乱数列に対して、論理積や論理和などの演算を行うことで所定確率ηに対応した乱数を生成することが可能である。

【0231】

乱数生成器(RNG: Random Number Generator)16は、認証に用いる乱数Nonce_N(a bit)を生成する。この乱数発生器16は、上述した上記第1乃至第5の実施形態に係る乱数発生回路16を用いることが可能である。この際、例えば、乱数発生器16が、図27に示す破線の経路により、読み出しデータData、および乱数トリガー信号を同様に受けることにより、同様に適用でき、同様の効果を得ることが可能である。

【0232】

順序交換回路(Permutation & Concatenation)18は、両者が共有したXYを用いて、ホスト20から入力される乱数Nonce_Hと、メモリ10から入力される乱数Nonce_Nとから構成した乱数Nonce(c bits)を生成する。ここで、aはNonce_Nのビット長を意味し、bはNonce_Hのビット長を意味し、cは圧縮演算回路の1処理当たりに入力されるビット長を意味する。すなわち、順序交換回路(Permutation & Concatenation)から出力される個々の乱数Nonceは圧縮演算回路の1処理用のデータであり、1処理用にNonce_NとNonceHの総ビットを用いてもよいし、部分ごとに選択的に用いてもよい。

【0233】

圧縮演算回路(Compress (ex. inner product))13は、データキャッシュ12の出力XY(c bit each)と順序交換回路13の出力(c bits)について内積演算などの所定の演算を行い、データCを出力する。

【0234】

ビット毎加算回路C1は、圧縮演算回路13の出力ビットに対して、バイアスドRNGによって生成されたνを付与したz=C+νを、出力部15へ出力する。尚、前述の通り、ビット加算とは排他的論理和を意味する。すなわち、ビット毎加算回路は、2入力データのビット毎の排他的論理和を出力する。

【0235】

出力部15は、ビット毎加算回路C1の結果(z=C+ν)を、コントローラ19を介してホスト20に出力する。

【0236】

なお、上記セルアレイ11以外のデータキャッシュ12等の構成要素は、メモリコントローラ19に配置されることも同様に可能である。

【0237】

11−2.ホスト

本例に係るホスト(Host)20は、訂正処理部21、暗号の復号部22、鍵保持部23、データ一時記憶部25、圧縮演算部26、乱数生成部27、順序交換部29、判定部30等を備える。

【0238】

訂正処理部(ECC)21は、NAND型フラッシュメモリ10のロム領域11−1から読み出されたデータXYEに誤り訂正処理(ECC)を行う。

【0239】

復号部(Decrypt)22は、読み出したデータXYEに対してエラー訂正処理を行った後、鍵保持部23が保持する鍵KEYによりデータデータXYE復号して、XYを得る。

【0240】

データ一時記憶部(Data cache)25は、復号したXYを一時的に保持する。これにより、ホストデバイス20とNAND型フラッシュメモリ20は、秘密情報XYを共有できる。

【0241】

圧縮演算部(Compress (ex inner product))26は、データキャッシュ25の出力(c bit each)と順序交換回路29の出力(c bits)とについて内積演算などの所定の演算を行い、データCを出力する。

【0242】

乱数生成部(RNG)27は、ホストの一時乱数Nonce_H (b bit)を生成する。

【0243】

順序交換部(Permutation & Concatenation)29は、両者は共有したXYを用いて、ホスト20から入力される乱数Nonce_Hと、メモリ10から入力される乱数Nonce_Nとから構成した乱数Nonce(c bits)を生成する。

【0244】

判定部(Accept if Hwt(Z(+)C) ≦ t*clen)30は、圧縮演算部26の出力Cおよび出力部15の出力Zについて、上記のようにハミング重みHwt(Z(+)C)を行い、ハミング重みHwt(Z(+)C)が、所定値t*clenを下回った場合、秘密情報を保持しているとみなし、認証成功と判定する。ただし、η≦t<0.5、clenはZ(+)Cのビット長とする。

【0245】

このように、ホスト20は、バイアスドRNG処理27を除き、判定部30により同様の処理によって得られたCとzとを比較することで、被認証コンポーネントであるNAND型フラッシュメモリ10の正当性を確認する。

【0246】

尚、上記構成による同様の処理を複数回行うことで最終的に正当性を確認することも可能である。例えば、本図では、Cが複数ビットである場合を例としており、比較判定方法はzとCの加算ビット系列におけるハミング重みを判定に用いている。もし、Cが単一ビットであった場合、前述のHB+プロトコルと同様に、前述の処理は複数回行う必要があり、この場合はHB+プロトコルと同様にエラー変数の生起確率に基づいてzとCの不一致率を検査すればよい。

【0247】

11−3.変形例

上記に限られず、本例の構成は、以下のように必要に応じて、変形することが可能である。

【0248】

圧縮処理について、図25及び図26で示した比較例1、2に係る内積計算に対応しても良いが、必ずしも内積計算でなくともよい。例えば、圧縮処理を、LFSR(Linear Feedback Shift Registor)で構成する演算器に対してXYを基とするデータとNonce_H及びNonce_Nを基とするデータを入力し、全入力後のLFSR中のレジスタ値の一部もしくは全てを圧縮結果として用いてもよい。または、LFSRとしてCRC演算器を用いてもよい。更に、圧縮処理に用いる関数としてハッシュ関数を用いてもよい。ハッシュ関数は暗号器に基づいていてもよく、基づいていなくてもよい。いずれの演算方法を用いても本実施例にて提案している方法を適用することが可能である。また安全性の根拠となっているLPN問題に属していることに変わりはない。尚、ここで圧縮処理とは可逆圧縮であるか、非可逆圧縮であるか、は問わず、少なくとも入力されたデータよりも小さく、かつ入力データに依存するデータを出力する処理を意味する。

【0249】

また、圧縮計算部に対してNonce_HとNonceNを元に生成したNonceを送出する処理について説明する。NonceはNonce_HとNonceNを所定の順序によって結合し送出されるデータであり、結合・送出方法としては、単純な順送りデータ結合・送出、互いのデータを交互に挿入したインターリーブデータ結合・送出などの方法であってよく、また前述の方法により複数回データを送出しても良い。いずれにせよ、Nonceは、Nonce_N及びNonceHの少なくとも一部のデータより生成されたデータであり、cビット長のデータとなる。ここで、Nonce_Nのデータ長はaとおき、Nonce_Hのデータ長はbとおき、両者の合計データ長をdとおく。仮にc=dであり、かつデータを複数回送出しない場合、圧縮計算部からの出力は1ビットとなる。仮にc=dであり、かつデータを複数回送出する場合、圧縮計算部からの出力は1ビットが複数回出力される。仮にc<dであり、かつデータを複数回送出する場合、圧縮計算部からの出力は1ビットが複数回出力される。

【0250】

一方、Nonceとの圧縮を計算するXYにおいても、XY中のデータがcビット単位で圧縮計算部へと送出される。ここで、XYデータのビットサイズxはcと等しいもしくは整数倍である。cと等しい場合、圧縮計算部の出力は1ビットとなる。cの整数倍である場合、圧縮計算部の出力は1ビットが複数回となる。代表的な組み合わせについて記すと、

・c=d=xの場合、圧縮計算部の出力は1ビット

・c=d<xの場合、圧縮計算部の出力は1ビットが複数回

・c<d, c<xの場合、圧縮計算部の出力は1ビットが複数回

となる。尚、前記は圧縮計算部が2入力を1ビットに圧縮する場合の例であり、圧縮計算部が2入力を複数ビットに圧縮する場合は、1回あたりの出力値自体も複数ビットとなる。

【0251】

<20.認証フロー>

次に、図28に沿って、図27に示した構成におけるメモリシステムの認証フローについて説明する。

【0252】

認証開始(Start)すると、ステップS11の際、ホストデバイス10は、NAND型フラッシュメモリ10へXYEの読出し命令(Read XYE)を送出する。

【0253】

続いて、ステップS12の際、NAND型フラッシュメモリ10は、上記読出し命令に従って、XYEをセルアレイ11−1よりロード(load XYE)し、これをホストデバイス20へと送出する。

【0254】

続いて、ステップS13の際、ホストデバイス20は、受領したXYEに対して、上記復号処理を行い、XYを得る(Retrieve XY)。

【0255】

続いて、ステップS14の際、ホストデバイス20は、認証要求(Request authentication)を、NAND型フラッシュメモリ10へ送出する。ここで、認証要求にはNonce_Hを含んでいてもよい。

【0256】

続いて、ステップS15の際、NAND型フラッシュメモリ10は、Nonce_Hを受領し、XYをロードする(Load XY (if required))。

【0257】

続いて、ステップS16の際、NAND型フラッシュメモリ10は、Nonce_Nおよびνを生成する(Create Nonce_N, Create ν)。

【0258】

続いて、ステップS17の際、NAND型フラッシュメモリ10は、上記のように、生成されたνを付与し、Zを計算する。NAND型フラッシュメモリ10は、Nonce_N及びZをホスト20へと送出する。

【0259】

続いて、ステップS18の際、ホスト20は、それらデータNonce_N及びZを受領後、内積演算などの所定の演算を行い、データCを計算する。

【0260】

続いて、ステップS19の際、ホスト20は、ZとCのビット毎XOR値の系列に対してハミング重みHwt(Z(+)C)を計算し、これが所定値t*clenを下回るか否かの判定処理(Check Hwt(Z(+)C) ≦ t*clen)を行う。ここで、上記のように、tはNANDフラッシュメモリ10がZの算出時に用いたエラービットもしくはエラーベクトルνにおけるエラー付与確率(もしくはデータ中の1の出現確率)ηに基づく値であり、η≦t<0.5であるとする。またclenはCのビット長とする。

【0261】

続いて、ステップS20の際、上記ステップST19の判定結果が所定を下回らなかった場合(fail)、ホスト20は、失敗としてこの動作を停止する。

【0262】

続いて、ステップS21の際、上記ステップST19の判定結果が所定を下回った場合(Success)、ホスト20は、あらかじめ定められたラウンド数に達しているか否かを判定する(Enough round ?)。ここで、ラウンド数とは前記認証要求処理から前記判定処理までの一連の処理を指す。ラウンド数に達していない場合(No)には、再度認証要求処理(S14〜)を繰り返す。

【0263】

続いて、ステップS22の際、ラウンド数に達している場合(Yes)には、認証が成功したとみなし、ホストデバイス10は、必要に応じて、前記XYに基づきMedia IDを算出する処理を行う。Media IDの算出処理、Media IDの利用方法(S23以下)については後述する。

【0264】

以上の動作により、第6の実施形態に係る認証フローを終了する(End)。

【0265】

尚、Nonce_N、Nonce_H、νのパラメータは、ラウンド毎に異なるものを用いる必要がある。また、NAND型フラッシュメモリ10が認証要求を受領した際、前認証要求時のXYがData Cacheにロードされたままであった場合、セルアレイからのXYのロードを省略し、Data cache内の値を用いてもよい。また、ステップS17の後、Data cache内のXYを消去してもよい。特に、NAND型フラッシュメモリ10がData cacheへのアクセス機能を外部に提供している場合、認証に要するデータZを計算した段階でData cache内の秘密情報XYを消去することはセキュリティー上有用である。

【0266】

<30.作用効果>

第6の実施形態に係る構成およびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも下記(11)の効果が得られる。

【0267】

(11)認証コンポーネント、被認証コンポーネント間で、異なる秘密情報XYの秘密状態を維持したまま共有でき、共有した秘密情報に基づく軽量な計算によって認証できる。

【0268】

本例に係るNAND型フラッシュメモリ10は、秘密情報XYを記録禁止・読出禁止領域である秘匿領域11−2に保持し、同秘密情報XYを暗号化し更に訂正符号を付与したXYEを記録禁止・読出許可領域であるロム領域11−1に保持する。さらに、ホスト20は、XYEを読み出してエラー訂正処理21、復号化処理22をする機能、および復号に用いる鍵23により、NAND型フラッシュメモリ10およびホスト20の両者で、秘密情報XYを共有することができる。そのため、認証・被認証コンポーネントは、共有した秘密情報XYで、認証を行うことができる(ST11〜ST23)。

【0269】

また、NAND型フラッシュメモリ10とホストデバイス20は、各々一時乱数を生成するRNG16,17、順序交換部18,29、圧縮計算部13,26、一時乱数のビット毎加算部C1,26、送出部15を備える。また、NAND型フラッシュメモリ10は、バイアスドRNG14を備える。ホスト20は、NAND型フラッシュメモリ20から送出されたZとホストデバイス内部で計算したCとを比較し認証を行う判定部30を備える。

【0270】

このように、第6の実施形態では、秘密情報XYを記録禁止・読出禁止領域である秘匿領域11−2に保持し、これを用いてデータZを生成するため、秘匿性を保持できる。さらに、秘密情報XYを暗号化し更に訂正符号を付与したXYEを記録禁止・読出許可領域であるロム領域11−1に保持する。ホスト20は、ここから読み出したXYEに対して、エラー訂正処理21、および鍵23を用いた復号化処理22を行うことで、XYを共有する。そのため、認証・被認証コンポーネント間で、異なるXYを秘密状態を維持したまま共有できる。

【0271】

従って、第6の実施形態に係る構成およびその認証方法によれば、認証・被認証コンポーネント間で、異なるXYを秘密状態を維持したまま共有でき、共有した秘密情報に基づく軽量な計算によって認証できる点で有利である。

【0272】

[第7の実施形態]

次に、図29および図30を用い、第7の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。なお、以下の説明において、上記第6の実施形態と重複する部分の説明については、省略する。

【0273】

<構成例(メモリシステム)>

図29を用い、第7の実施形態に係る構成例について説明する。

図示するように、第7の実施形態に係る構成例では、NAND型フラッシュメモリ10が、ロム領域11−1,秘匿領域11−2に、それぞれ複数のXYEおよび複数のXYを記憶する点で、上記第6の実施形態と相違する。ここで、iとjが異なる場合、XY[i]≠XY[j]、XYE[i]≠XYE[j]である。

【0274】

このように、複数のXYEおよび複数のXYの組を保持することで、秘密情報X及びY露見時の秘密情報の更新手段を提供することができる。仮にある1つのXYとXYEの組が中間者攻撃その他によって露見し、露見したXY及びXYEを流用した偽造デバイスが製造された場合でも、本例では、ホスト20が保持するKEY[1]23を更新(例えば、KEY[1]=> 更新KEY[2])することができる。このように、露見したXY及びXYE以外の組を利用することで、偽造デバイスの排除が可能となる。各XY[i]の暗号化に用いられるKEYはiが異なる場合、異なるものである方が望ましい。

【0275】

その他は、上記第6の実施形態と実質的に同様であるため、詳細な説明を省略する。

【0276】

<認証フロー>

次に、図30に沿って、第7の実施形態に係る認証動作について説明する。

第7の実施形態では、NAND型フラッシュメモリ10内には複数のXY及び複数のXYEが記録されているため、ホスト20がいずれのXYを用いるかを選択することで、認証を行う。

【0277】

そのため、第7の実施形態では、ステップS14の際に、ホスト20が、認証を要求する(Request authentication)場合、いずれのXYを用いるかを指定するパラメータiを、乱数Nonce_Hとともに、NAND型フラッシュメモリ10に送出する点で、相違する。

【0278】

その他は、上記第6の実施形態と実質的に同様であるため、詳細な説明を省略する。

【0279】

<作用効果>

第7の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。

【0280】

さらに、第7の実施形態では、NAND型フラッシュメモリ10が、ロム領域11−1、秘匿領域11−2に、それぞれ複数のXYEおよび複数のXYを記憶する点で、上記第6の実施形態と相違する。

【0281】

このように、複数のXYEおよび複数のXYの組を保持することで、秘密情報X及びY露見時の秘密情報の更新手段を提供することができる。仮にある1つのXYとXYEの組が中間者攻撃その他によって露見し、露見したXY及びXYEを流用した偽造デバイスが製造された場合でも、本例では、ホスト20が保持するKEY[1]23を更新(例えば、KEY[1]=> 更新KEY[2])することができる。

【0282】

そのため、第7の実施形態に係る認証フローでは、ステップS14の際に、ホスト20が、認証を要求する(Request authentication)場合、いずれのXYを用いるかを指定するパラメータiを、乱数Nonce_Hとともに、NAND型フラッシュメモリ10に送出する。

【0283】

このように、第7の実施形態では、NAND型フラッシュメモリ10が、複数のXY及び複数のXYEを有し、ホストデバイスからの命令によりXYEを選択的に送出する機能を有し、ホストデバイスからの命令により認証に用いるXYを選択的に設定する。また、ホストデバイスは、自身が保持する鍵に対応するXYEを選択的に読み出す機能を有し、それを復号する機能を有し、また自身が保持する鍵を所定の条件下で更新する機能を有する。

【0284】

その結果、露見したXY及びXYE以外の組を利用することで、偽造デバイスの排除が可能となる点で有利である。

【0285】

[第8の実施形態]

次に、図31乃至図33を用い、第8の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。

【0286】

<構成例(メモリシステム)>

図31を用い、第8の実施形態に係る構成例について説明する。

図示するように、本例に係るNAND型フラッシュメモリ10は、ロム領域11−1B、秘匿領域11−2Bに、複数のXYsubEおよび複数のXYsubをそれぞれ記憶する点で、上記第7の実施形態と相違する。ここで、iとjが異なる場合、XYsub[i]≠XYsub[j]、XYsubE[i]≠XYsubE[j]である。XYsubEはXYsubを暗号化した後、訂正符号を付与したデータである。

【0287】

XYsubは、XYと同様に記録禁止・読出禁止領域(秘匿領域)11−2Bに記録され、XYsubEは、XYEと同様に記録禁止・読出許可領域(ロム領域)11−1Bに記録される。

【0288】

ここで、XYmainのデータサイズは、XYsubよりも大きい(データサイズ:XYmain > XYsub)。また、XYmainとXYsubから構成されるデータが、前述の秘密情報XYに対応する。

【0289】

このように、第8の実施形態では、XYの組に加え、XYsub[i], XYsubE[i]の組を更に備えるため、秘密情報X及びYを効率的に記録することができる点で有利である。詳細については、後述する。

【0290】

さらに、NAND型フラッシュメモリ10は、上記XYsubを格納するためのデータキャッシュ12B、およびXYmainと XYsubとをビット毎加算するためのビット毎加算部C2を備える。ビット毎加算部C2の出力値が、前述の認証に用いられるXY値に相当する。ここで、XYmainとXYsubのビット長が異なることから、ビット加算C2においては、XYsubの繰り返しデータが適用される。

【0291】

例えば、本図にあるように所定の演算としては、ビット加算が考えられ、XYmainのデータサイズがXYsubのデータサイズの整数倍であった場合、XYmainのデータを保持するData cacheからはXYmainが順送りに送出され、XYsubのデータを保持するData cacheからはXYsubが順送りかつ繰り返し送出される構成が考えられる。XYsubを保持するData cacheはリングバッファと考えてもよい。また、ビット毎加算以外にもXYmainとXYsubの結合値をXYとしてもよいし、XYmainとXYsubのインターリーブ結合値をXYとしてもよいし、XYmainとXYsubをLFSRに入力しLFSRの所定レジスタの値をXYとしてもよい。すなわち、本実施例ではビット毎加算部としているが、2入力から構成したデータをXYとして用いるいずれの演算方法も適用可能である。

【0292】

同様に、ホスト20は、読み出したXYsubEに対応するための、訂正処理部21B、暗号の復号部22B、鍵保持部23B、データ記憶部25B、加算部C3を更に備える。ホスト20は、上記構成により、同様に、エラー訂正処理を行い、対応するKEY_XYsubにより復号することでXYsubを得る。これにより、ホストデバイスとNAND型フラッシュメモリ間で、秘密情報XYmain及びXYsubを共有できる。ここで、本図においてはKEY_XYmainとKEY_XYsubは異なるオブジェクトとして描かれているが、実際には同じ鍵であっても良い。また、各XYsub[i]の暗号化に用いられるKEY_XYsubはiが異なる場合、異なるものである方が望ましい。さらに、ホストデバイス20、メモリ10は、XYmainとXYsubを用いて所定の演算を行ったXY値により、認証処理を行う。

【0293】

<認証フロー>

次に、図32に沿って、第8の実施形態に係る認証動作について説明する。

第8の実施形態では、NAND型フラッシュメモリ10内にはXYmainに加えてXYsubが、またそれらを暗号化したXYmainE及びXYsubEが記録される。

【0294】

そのため、図示するように、対応するステップS13において、ホスト10は、XYmainE , XYsubEを更に読み出して復号をし、秘密情報XYmain,XYsubに基づく秘密情報XYを生成する(Create XY)。続いて、ホスト20は、秘密情報XYmainとXYsubから導出された情報を用いて、同様の認証を行う。

【0295】

また、NAND型フラッシュメモリ10側においても同様に、ステップS15において、読み出した秘密情報XYmain,XYsubに基づいて秘密情報XYを生成する(Create XY)点で、上記第7の実施形態と相違する。

【0296】

<作用効果>

第8の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。さらに、第8の実施形態では、(12)の効果が得られる。

【0297】

(12)秘密情報X,Yを効率的に記録することができ、記録時間を高速化できる点で有利である。

【0298】

第8の実施形態では、NAND型フラッシュメモリ10が、複数のXYsub及び複数のXYsubEを有し、ホスト20からの命令によりXYsubEを選択的に送出し、ホスト20からの命令により認証に用いるXYsubを選択的に設定し、選択されたXYsubとXYを所定の演算で導出した値により認証を行う。

【0299】

また、ホストデバイスは、自身が保持する鍵23Bに対応するXYsubEを選択的に読み出し、それを復号する機能22Bを有し、また自身が保持する鍵23Bを所定の条件下で更新する機能を更に有し、選択したXYsubとXYmainを所定の演算で導出した値により認証30を行う。

【0300】

このように、XYmainの組に加え、XYsub[i], XYsubE[i]の組を更に備えるため、秘密情報X及びYを効率的に記録することができる点で有利である。

【0301】

より具体的には、例えば、図33のように示される。図示するように、NAND型フラッシュメモリの製造工程において、XYmain、XYmainE、XYsub、XYsubEの複数の組は、XY発生装置(XY GEN)により生成され、書き込み装置(Writer)により、複数のNAND型フラッシュメモリ(ここでは、Chip1〜Chip4)にデータ書き込みがされる。

【0302】

ここで、XYmain及びXYmainEのデータは、複数のチップChip1〜Chip4から構成される集団内(例えばロット)で同一のデータで良い。一方、XYsub及びXYsubEは、チップChip1〜Chip4毎に異なるデータ(XYsub1〜XYsub4及びXYsubE1〜XYsubE4)とする必要がある。

【0303】

このように、第8の実施形態では、データ書き込み動作において、データ量の多いXYmain及びXYmainEを複数のチップChip1〜Chip4で共通化することにより、メモリへのデータ書き込みプロセスを最適化でき、効率的に記録することが可能となる。

【0304】

仮に、XYmain及びXYmainEをハードワイヤードで構成する場合、実際に記録するデータは、データサイズが小さいXYsub及びXYsubEとなり記録時間を短縮できる。また、仮にXYmain及びXYmainEをセル上に記録する場合において、集団内で同一であることにより、NAND型フラッシュメモリへのデータ記録装置に対して記録データを転送する時間を短縮できる。先に述べたように、記録時間の増加は、コストの増加となるため、第8の実施形態によれば、製造コストを低減することができるというメリットも大きい。

【0305】

[第9の実施形態(多重記録される一例)]

次に、図34および図35を用い、第9の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。

【0306】

<構成例(メモリシステム)>

図34を用い、第9の実施形態に係る構成例について説明する。

第9の実施形態では、メモリ10の秘匿領域11−2に、複数のXY[i]を多重に複製した情報11−2A,11−2B,11−2Cを更に有する点で、上記第7の実施形態と相違する。

【0307】

すなわち、第7の実施形態におけるXY[i]を複製したデータは、図34において、XY[i,1],XY[i,2],...,XY[i,n]によって示され、1≦i≦mに対しXY[i,1]=XY[i,2]=…=XY[i,n]である。また、1≦j≦nに対しXY[1,j]≠XY[2,j]≠…≠XY[m,j]である。

【0308】

ここで、XYEがECCが付与されている一方で、XYにはECCが付与されていないため、NAND型フラッシュメモリ内でセルから読み出したデータにエラーが含まれている場合、NAND型フラッシュメモリが認証に用いるXYの完全性が失われることも考えられる。しかしながら、本例のように、複数のXY[i]を複製した情報11−2A,11−2B,11−2Cを更に有することにより、検査・選択部12−0により、前記エラーが含まれているかどうかを複製データ間でのデータ比較により検出することができる。

【0309】

そのため、本例のメモリは、XY[i]を複製した情報11−2A,11−2B,11−2Cに対応するための検査・選択部(Check sum & select)12−0を更に備える点で、第7の実施形態と相違する。

【0310】

図34において、セル11−2からロードされた少なくとも2つ以上のXYのデータセットは所定の上記同様の方法により比較を行うことでエラーが含まれているか否かを検査する。仮にエラーが含まれていた場合もしくはエラーが除去できない場合、異なる2つ以上のXYのデータセットを再度ロードし、同様に検査する。これをエラーが含まれていないもしくは除去できるデータセットが見つかるまで繰り返し、同データセットが見つかった場合それを認証に用いる。上記所定の方法の例としては、2つのXYをロードし、ビット毎にXOR値を算出した後、XOR値がすべて0であるかどうか、により検査する方法が考えられる。また、3つ以上のXYをロードし、多数決判定によってビット毎にエラーを除去したXYを得る方法も考えられる。また、本図においては、XYの複製データはすべて同一データとしているが、複製データのうち奇数番号のデータと偶数番号のデータの極性が反転しているように相補関係にあるデータを構成して事前に記録しておく方法も考えられる。この場合、前記相補関係にある2つのXYをロードし、ビット毎にXOR値を算出した後、XOR値がすべて1であるかどうか、により検査することが可能である。

【0311】

<認証フロー>

次に、図35に沿って、第9の実施形態に係る認証動作について説明する。

図示するように、第9の実施形態では、NAND型フラッシュメモリ10の秘匿領域11−2内に、複数のXYが多重記録される。

【0312】

そのため、ステップS15の際、NAND型フラッシュメモリ10は、少なくとも2つ以上のXYを読み出し、比較し、エラーを含んでいないXYを用いて認証を行う(Load / compare XYs)。

【0313】

<作用効果>

第9の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。

【0314】

さらに、第9の実施形態によれば、メモリ10の秘匿領域11−2に、複数のXY[i]を複製した情報11−2A,11−2B,11−2Cを更に有する。

【0315】

ここで、XYEがECCが付与されている一方で、XYにはECCが付与されていないため、NAND型フラッシュメモリ内でセルから読み出したデータにエラーが含まれている場合、NAND型フラッシュメモリが認証に用いるXYの完全性が失われることも考えられる。

【0316】

しかしながら、第9の実施形態によれば、複数のXY[i]を複製した情報11−2A,11−2B,11−2Cを更に有することにより、検査・選択部12−0により、前記エラーが含まれているかどうかを複製データ間でのデータ比較により検出することができる。結果、メモリ10内でセルから読み出したデータにエラーが含まれている場合であっても、メモリ10が認証に用いるXYの完全性が失われることを防止できる点で更に有利である。

【0317】

[第10の実施形態]

次に、図36および図37を用い、第10の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。

【0318】

<構成例(メモリシステム)>

図36を用い、第10の実施形態に係る構成例について説明する。第10の実施形態に係る構成例は、上記第3、第9の実施形態を組み合わせたものに関する一例である。

【0319】

図示するように、第10の実施形態に係るNAND型フラッシュメモリ10は、秘匿領域11−2に、XYsub及びXYsubEについても複製データXYsub[i,j]及びXYsubE[i,j]を記録する点で、上記第9の実施形態と相違する。

【0320】

また、上記に対応するための検査・選択部12−0Bおよびデータキャッシュ12Bを更に備える。

【0321】

<認証フロー>

次に、図37に沿って、第10の実施形態に係る認証動作について説明する。

第10の実施形態では、NAND型フラッシュメモリ10内に、更にXYsubも多重記録される(XYsub[i,j]及びXYsubE[i,j])。

【0322】

そのため、ステップS15の際、NAND型フラッシュメモリ10は、更に少なくとも2つ以上のXYsubを読み出し、比較し、エラーを含んでいないXYsubを用いて認証を行う(Load / compare XYs and XYsubs)。

【0323】

<作用効果>

第10の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。

【0324】

さらに、第10の実施形態によれば、NAND型フラッシュメモリ10は、秘匿領域11−2に、XYsub及びXYsubEについても複製データXYsub[i,j]及びXYsubE[i,j]を記録する。

【0325】

必要に応じて、本例のような構成および方法を適用することが可能である。

【0326】

[第11の実施形態]

次に、図38および図39を用い、第11の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。

【0327】

<構成例(メモリシステム)>

図38を用い、第11の実施形態に係る構成例について説明する。

第11の実施形態でも同様に、NAND型フラッシュメモリ10が、更に複数のXY[i]を複製した情報を有する。すなわち、先の第7の実施形態におけるXY[i]を複製したデータは本図においてXY[i,1],XY[i,2],...,XY[i,n]によって示され、1≦i≦mに対しXY[i,1]=XY[i,2]=…=XY[i,n]である。また、1≦j≦nに対しXY[1,j]≠XY[2,j]≠…≠XY[m,j]である。

【0328】

ここで、XYデータを複製することは第9の実施形態と同様であるが、本第11の実施形態においては、NAND型フラッシュメモリ10側では複製データの比較処理を行わず、その代わりにホスト20で比較処理を行う点で、相違する。そのため、本例では、ホスト20が、多数決判定部(Majority check)30を備える点で、相違する。

【0329】

すなわち、NAND型フラッシュメモリ10は、ホスト20により指定されたiに応じ、XY[i,1],XY[i,2],...,XY[i,n]のうち少なくとも2つ以上をロードし、各々のXYに対して前述の認証処理を行う。ここで、各々のXYに対しては同一のNonce_N及び同一のNonce_Hを利用し、またバイアスドRNGによって生成されたνについても同一のものを適用する。

【0330】

NAND型フラッシュメモリ10の送信部15は、複数のXYに対して、他のパラメータが同一な条件で複数のz(z[i,1],z[i,2],…,z[i,n])を計算し、ホスト20に送出する。

【0331】

ホストデバイスは、複数のz(z[i,1],z[i,2],…,z[i,n])を受領した後、多数決判定部31により、多数決判定を行い、単一のzを得る。ここで、各zが複数のビット要素で構成されていた場合、圧縮計算部の出力が複数ビットからなる場合、前記多数決判定はビット要素毎に行う。

【0332】

ホストデバイスは、多数決判定によってエラーを除去したZを得たのち、前述と同様の判定処理30を行うことで、NAND型フラッシュメモリ10を認証する。

【0333】

<認証フロー>

次に、図39に沿って、第11の実施形態に係る認証動作について説明する。

第11の実施形態では、NAND型フラッシュメモリ10内に多重記録されているXYを用いて、NAND型フラッシュメモリが複数のZを計算し、送出し、ホストデバイスは複数のZを多数決処理することで単一のZを得て、認証を行う。

【0334】

そのため、ステップS17の際、NAND型フラッシュメモリ10は、計算した複数のZ,jをホスト20に送信する。

【0335】

続いて、ステップS18の際、ホスト20は、複数のZの多数決判定部(Majority check)を更に行う点で、相違する。

【0336】

<作用効果>

第11の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。

【0337】

さらに、第11の実施形態では、NAND型フラッシュメモリ10が、更に複数のXY[i]を複製した情報を有する。さらに、ホスト20が、多数決判定部(Majority check)30を備える。

【0338】

そのため、計算資源に制約のあるNAND型フラッシュメモリ10での比較処理を軽減でき、計算資源に余裕のあるホスト20に比較処理(多数決処理)30を依頼することができる。結果、NAND型フラッシュメモリ10へのコスト増加を抑制することができ、エラーの除去が可能となる点で有利である。

【0339】

[第12の実施形態]

次に、図40および図41を用い、第12の実施形態に係る認証・被認証コンポーネントおよびその認証方法について説明する。

【0340】

<構成例(メモリシステム)>

図40を用い、第12の実施形態に係る構成例について説明する。第12の実施形態は、上記第3、第11の実施形態を組み合わせたものの一例に関する。

【0341】

図示するように、NAND型フラッシュメモリ10は、XYsub及びXYsubEについても複製データ11−2B,11−1Bを更に記録する。上記第11の実施形態と同様に、複数のXYに対する認証用データzを算出して算出部15でホスト20に送信し、ホスト20側で多数決処理30を行う。

【0342】

<認証フロー>

次に、図41に沿って、第12の実施形態に係る認証動作について説明する。

第12の実施形態では、NAND型フラッシュメモリ10内に、多重記録されているXYmain及びXYsubを用いて、NAND型フラッシュメモリが複数のZを計算し、送出し、ホストデバイスは複数のZを多数決処理することで単一のZを得て、認証を行う。

【0343】

そのため、ステップS11の際、ホスト20は、多重記録されているXYmain及びXYsubの読み出し要求(Read XYmainE and XYsubE)を行う。

【0344】

続いて、ステップS12の際、NAND型フラッシュメモリ10は、多重記録されているXYmain及びXYsubを読み出し(Load XYmainE and XYsubE)、ホスト20に送信(XYmainE and XYsubE)する。

【0345】

<作用効果>

第12の実施形態に係る認証・被認証コンポーネントおよびその認証方法によれば、上記(I)〜(IV)を改善でき、少なくとも上記(11)の効果が得られる。

【0346】

さらに、第12の実施形態では、NAND型フラッシュメモリ10が、XYsub及びXYsubEについても複製データ11−2B,11−1Bを更に記録する。上記第11の実施形態と同様に、複数のXYに対する認証用データzを算出して算出部15でホスト20に送信し、ホスト20側で多数決処理30を行う。

【0347】

このように、必要に応じ、本例を適用することが可能である。

【0348】

[第13の実施形態(Media ID retrieve process)]

次に、図42乃至図45を用い、第13の実施形態について説明する。第8の実施形態は、上記ステップS22において、メディアID(Media ID)を算出する種々の処理(Media ID retrieve process)に関するものである。

【0349】

ID retrieve process(1)

ID retrieve process(1)は、図42のように示される。図示するように、この例(1)では、ステップRS1の際、上記の認証に用いられたXYmain及びXYsubに対して、各々一方向性関数処理(One-way function)が行われる。その結果が、Media IDとして扱われる。

【0350】

ここで、一方向性関数処理としては、例えば、SHA-1、SHA-256、AEG-Hなどの暗号に基づく一方向性演算を用いることが可能である。

【0351】

ID retrieve process(2)

ID retrieve process(2)は、図43のように示される。図示するように、この例(2)では、ステップRS1,RS2の際、上記認証に用いられたXYmain及びXYsubは、前述の認証処理においてXYmainE及びXYsubEの復号に用いられたKEY_XYmainとKEY_XYsubのいずれか一方に相当するKEY_XYを用いて、更に復号処理(Decode)が行われる。

【0352】

続いて、ステップRS3の際、同様の一方向性関数処理(One-way function)が行われ、その結果がMedia IDとして扱われる。

【0353】

ID retrieve process(3)

ID retrieve process(3)は、図44のように示される。図示するように、この例(3)では、ステップRS1,RS2の際、上記の認証に用いられたXYmain及びXYsubは、上記認証処理においてXYmainE及びXYsubEの復号に用いられたKEY_XYmain及びKEY_XYsubを用いて、更に復号処理(Decode)が行われる。

【0354】

続いて、ステップRS3の際、同様の一方向性関数処理(One-way function)が行われ、その結果がMedia IDとして扱われる。

【0355】

ID retrieve process(4)

ID retrieve process(4)は、図45のように示される。図示するように、この例(4)では、ステップRS1,RS2の際、ステップRS1,RS2の際、上記の認証に用いられたXYmain及びXYsubは、上記認証処理においてXYmainE及びXYsubEの復号に用いられたKEY_XYmain及びKEY_XYsub と異なるKEY_XYmain2及びKEY_XYsub2を用いて、更に復号処理(Decode)が行われる。ここで、KEY_XYmain2及びKEY_XYsub2は同一の値であってもよい。

【0356】

続いて、ステップRS3の際、同様の一方向性関数処理(One-way function)が行われ、その結果がMedia IDとして扱われる。

【0357】

[第14の実施形態(Media ID binding process)]

次に、図46乃至図47を用い、第14の実施形態について説明する。第14の実施形態は、Media IDの利用方法(Media ID binding process)に関するものである。

ここで、例えば、商用動画コンテンツ等を物理媒体に記録し、再生する場合、同物理媒体に固有な識別情報をコンテンツ記録時の暗号処理に用いてコンテンツを同物理媒体にバインドする方法がとられる。

【0358】

コンテンツ再生時は、前記識別情報に基づく復号処理もしくは検査処理などを行い、再生された識別情報とコンテンツ記録時の暗号処理に用いられた識別情報が一致しない場合、コンテンツの再生を停止するなどの方法がとられる。ここで物理媒体としては、例えば、SDカードなどのリムーバブルメディアの場合や、携帯電話などに内蔵されているエンベデッドメモリなどが考えられる。

【0359】

いずれにおいても、前記方法の目的は、あるメディアに記録された暗号処理済みコンテンツを、別のメディアへと不正複製された場合、不正複製コンテンツの再生を停止させることである。そのための情報として、メディア毎に異なる上記識別情報(メディアID)を利用している。

【0360】

ID binding process(1)

ID binding process(1)は、図46のように示される。図示するように、この例(1)では、MAC(Message Authentication Code)生成処理を行い、これを不正複製の防止に用いる。

【0361】

具体的には、ステップBP1の際、前記識別情報としてMedia IDを用いる方法例として、コンテンツ暗号化に用いられるContent Keyにより、Media ID及びその他の情報に対し、MAC生成処理を行う。

【0362】

続いて、コンテンツをメディアに記録する装置においては、同MACを生成し、これをメディアに記録しておく。コンテンツをメディアから再生する装置においては、記録されているMACをMedia ID、Content Keyにより検査し、正当性が確認された場合はコンテンツを再生し、正当性が確認されない場合はコンテンツの再生を停止するなどの方法を適用することが可能である。

【0363】

ID binding process(2)

ID binding process(2)は、図47のように示される。図示するように、この例(1)では、コンテンツ暗号化に用いられるContent Keyを生成するための情報として、Media IDを利用する。

【0364】

ステップBP1の際、コンテンツをメディアに記録する装置においては、Content Key Precursorと、Media ID及びContent Key Precursorを一方向性処理(One-way function)する。

【0365】

メディアに記録する装置においては、処理されたContent Keyによって暗号化されたコンテンツを記録しておく。

【0366】

コンテンツをメディアから再生する装置においては、記録されているContent Key PrecursorとMedia IDを同様の一方向性処理をすることでContent Keyを得て、コンテンツの復号と再生を行う。ここで、Media IDが一致しない場合、すなわち記録されているデータが異なるメディアに不正複製された場合など、には導出したContent Keyとコンテンツ暗号化に用いられているContent Keyが一致しないため、コンテンツの復号に失敗し、再生は停止される。

【0367】

[第15の実施形態(メモリ、記憶・再生ホストの一例)]

次に、図48を用い、第15の実施形態について説明する。第15の実施形態は、上記実施形態の構成を組み合わせたメモリカード(inc. NAND chip)10,記録ホスト(Recoding Device)20A,再生ホスト(Playback Device)20Bのシステムにおいて、上記認証を行い、上記メディアIDを用い、ホスト20Bにてコンテンツを再生する一例に関するものである。

【0368】

記録ホスト(Recoding Device)20Aがコンテンツをメモリカード(inc. NAND chip)10に記録するに際し、まずメモリカード(inc. NAND chip)10と記録ホスト(Recoding Device)20Aの間で、上記実施形態における認証処理を行う。ここで、認証処理が成立した後、上記実施形態におけるID retrieval processを行う。次いで、上記実施形態におけるID binding process(1)により生成したMACをメモリカード(inc. NAND chip)10に記録する。合わせて、ID binding process(1)において用いたContent Keyにより暗号化したコンテンツ(Encrypted Content)も記録する。更に、Content Key自身も安全な形で記録する。ここで安全な形とは、メモリカード(inc. NAND chip)10と記録ホスト(Recoding Device)20Aの間で認証が成立した後にアクセスが可能となるモリカード(inc. NAND chip)10内の記録エリアであってもよい。また、ここでいう認証は本願において記載されている認証方法でもよいし、メモリカード(inc. NAND chip)10が持つ別の認証機能によって実現してもよい。また、安全な形の別な例としては、メモリカード(inc. NAND chip)10もしくは記録ホスト(Recoding Device)20Aが有する鍵によって暗号化した形であってもよい。

【0369】

再生ホスト(Playback Device)20Bがコンテンツをメモリカード(inc. NAND chip)10から読出し、再生するに際し、まずメモリカード(inc. NAND chip)10と再生ホスト(Playback Device)20Bの間で、上記実施形態における認証処理を行う。ここで、認証処理が成立した後、上記実施形態におけるID retrieval processを行う。次いで、上記実施形態におけるID binding process(1)に対応する処理により、メモリカード(inc. NAND chip)10に記録されているMACを検証する。その後、Content Keyをメモリカード(inc. NAND chip)10より読出し、暗号化したコンテンツ(Encrypted Content)の復号を行うことでコンテンツを再生する。

【0370】

[第16の実施形態(メモリ、記憶・再生ホストのその他の一例)]

次に、図49を用い、第16の実施形態について説明する。第16の実施形態は、上記実施形態の構成を組み合わせたメモリカード(inc. NAND chip)10、記録ホスト(Recoding Device)20A、再生ホスト(Playback Device)20Bのシステムにおいて、上記認証を行い、上記メディアIDを用い、ホスト20Bにてコンテンツを再生する一例に関するものである。

【0371】

記録ホスト(Recoding Device)20Aがコンテンツをメモリカード(inc. NAND chip)10に記録するに際し、まずメモリカード(inc. NAND chip)10と記録ホスト(Recoding Device)20Aの間で、上記実施形態における認証処理を行う。ここで、認証処理が成立した後、上記実施形態におけるID retrieval processを行う。次いで、上記実施形態におけるID binding process(1)により生成したContent Keyをメモリカード(inc. NAND chip)10に記録する。合わせて、ID binding process(2)において生成したContent Keyにより暗号化したコンテンツ(Encrypted Content)も記録する。更に、Content Key Precursor自身も安全な形で記録する。

【0372】

ここで安全な形とは、メモリカード(inc. NAND chip)10と記録ホスト(Recoding Device)20Aの間で認証が成立した後にアクセスが可能となるモリカード(inc. NAND chip)10内の記録エリアであってもよい。また、ここでいう認証は本願において記載されている認証方法でもよいし、メモリカード(inc. NAND chip)10が持つ別の認証機能によって実現してもよい。また、安全な形の別な例としては、メモリカード(inc. NAND chip)10もしくは記録ホスト(Recoding Device)20Aが有する鍵によって暗号化した形であってもよい。

【0373】

再生ホスト(Playback Device)20Bがコンテンツをメモリカード(inc. NAND chip)10から読出し、再生するに際し、まずメモリカード(inc. NAND chip)10と再生ホスト(Playback Device)20Bの間で、上記実施形態における認証処理を行う。ここで、認証処理が成立した後、上記実施形態におけるID retrieval processを行う。次いで、上記実施形態におけるID binding process(2)に対応する処理により、メモリカード(inc. NAND chip)10に記録されているContent Key PrecursorからContent Keyを生成する。その後、暗号化したコンテンツ(Encrypted Content)の復号を行うことでコンテンツを再生する。

【0374】

[第16の実施形態(メモリ、コントローラ、ホストの一例)]

次に、図50を用い、第12実施形態について説明する。第12実施形態は、上記実施形態に適用可能な上記NAND型フラッシュメモリ10、コントローラ19、およびホスト20の一例に関するものである。本例では、メモリカードとしてSDカード(登録商標)を一例に挙げる。

【0375】

図示するように、本例では、メモリカードと接続されるホスト装置の機能ブロックも示されている。各機能ブロックは、ハードウェア、コンピュータソフトウェアのいずれかまたは両者を組み合わせたものとして実現することができる。このため、各ブロックがこれらのいずれでもあることが明確となるように、概してそれらの機能の観点から以下に説明する。このような機能が、ハードウェアとして実行されるか、またはソフトウェアとして実行されるかは、具体的な実施態様またはシステム全体に課される設計制約に依存する。当業者は、具体的な実施態様ごとに、種々の方法でこれらの機能を実現し得るが、いずれの実現の手法も本発明の範疇に含まれる。

【0376】

ホスト20は、アプリケーション、オペレーティング・システム等のソフトウェア211を備えている。ソフトウェア211は、ユーザから、メモリカードへのデータの書き込み、メモリカードからのデータの読み出しを指示される。ソフトウェア211は、データの書き込みおよび読み出しをファイルシステム212に指示する。ファイルシステム212は、管理対象の記憶媒体に記録されているファイルデータを管理するための仕組みであり、記憶媒体の記憶領域内に管理情報を記録し、この管理情報を用いてファイルデータを管理する。

【0377】

ホスト20は、SDインターフェース213を有する。SDインターフェース213は、ホスト20とメモリカードとの間のインターフェース処理を行うのに必要なハードウェア、ソフトウェアからなる。ホスト20は、SDインターフェース213を介してメモリカードと通信を行う。SDインターフェース213は、ホスト20とメモリカードとが通信するのに必要な様々な取り決めを規定し、後述のメモリカードのSDインターフェース231と相互に認識可能な各種のコマンドの組を備えている。また、SDインターフェース213は、メモリカードのSDインターフェース231と接続可能なハードウェア上の構成(ピンの配置、数等)も含む。

【0378】

メモリカードは、NAND型フラッシュメモリ10、メモリ10を制御するためのコントローラ19を有する。メモリカードは、ホスト20に接続されたとき、およびオフ状態のホスト20に挿入された状態でホスト20がオンされたときに電源供給を受けて初期化動作を行った後、ホスト1からのアクセスに応じた処理を行う。

【0379】

NAND型メモリ10は、データを不揮発に記憶し、複数のメモリセルからなるページと呼ばれる単位でデータの書き込みおよび読み出しを行う。ページには、各ページに固有の物理アドレスが割り当てられている。また、メモリ10は、複数のページからなる物理ブロック(消去ブロック)と呼ばれる単位でデータの消去を行う。なお、物理ブロック単位で物理アドレスが割り当てられていることもある。

【0380】

コントローラ19は、メモリ10によるデータの記憶状態を管理する。記憶状態の管理とは、どの物理アドレスのページ(または物理ブロック)が、どの論理アドレスのデータを保持しているかの関係、およびどの物理アドレスのページ(または物理ブロック)が消去状態(何も書き込まれていない、または無効なデータを保持している状態)であるかを管理することを含んでいる。

【0381】

コントローラ19は、SDインターフェース31、MPU(micro processing unit)32、ROM(read only memory)33、RAM(『random access memory』)34、NANDインターフェース35を含んでいる。

【0382】

SDインターフェース31は、ホスト20とコントローラ19との間のインターフェース処理を行うのに必要なハードウェア、ソフトウェアからなり、SDインターフェース13と同様に、両者の通信を可能とする取り決めを規定し、各種のコマンドの組を備え、ハードウェア上の構成(ピンの配置、数等)も含む。メモリカード(コントローラ22)は、SDインターフェース31を介してとホスト1と通信を行う。SDインターフェース31は、レジスタ36を含んでいる。

【0383】

MPU32は、メモリカード2全体の動作を司る。MPU32は、例えば、メモリカード2が電源供給を受けた際に、ROM33内に格納されているファームウェア(制御プログラム)をRAM34上に読み出して所定の処理を実行する。MPU32は、制御プログラムに従って各種のテーブルをRAM34上で作成したり、ホスト1から受けたコマンドに従ってメモリ21に対する所定の処理を実行したりする。

【0384】

ROM33は、MPU32により制御される制御プログラムなどを格納する。RAM34は、MPU32の作業エリアとして使用され、制御プログラムや各種のテーブルを一時的に記憶する。このようなテーブルとして、ファイルシステム12によってデータに割り当てられた論理アドレスを有するデータを実際に記憶しているページの物理アドレスの変換テーブル(論物テーブル)が含まれる。NANDインターフェース35は、コントローラ22とメモリ21とのインターフェース処理を行う。

【0385】

NAND型フラッシュメモリ10内の記憶領域は、保存されるデータの種類に応じて、例えばシステムデータ領域、機密データ領域、保護データ領域、ユーザデータ領域等を含んでいる。システムデータ領域は、コントローラ19が、その動作に必要なデータを保存するためにメモリ10内で確保しておく領域である。機密データ領域は、暗号化に用いる鍵情報や認証時に使用する機密データを保存しており、ホスト20からアクセスできない。保護データ領域は、重要なデータ、セキュアなデータを格納する。ユーザデータ領域は、ホスト20が自由にアクセスおよび使用することが可能で、例えばAVコンテンツファイルや画像データ等のユーザデータを格納する。なお、コントローラ19は、ユーザデータ領域の一部を確保し、自身の動作に必要な制御データ(論物テーブル等)を保存する。

【0386】

本発明のいくつか実施形態を説明したが、これら実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0387】

11…メモリセルアレイ、16…乱数発生回路、19…コントローラ、161…擬似乱数発生回路(LFSR)、162…乱数制御回路(TRNG Controller)。

【技術分野】

【0001】

半導体記憶装置に関するものである。

【背景技術】

【0002】

セキュリティーを要する分野において、秘密鍵や複数者間の認証処理におけるチャレンジデータなどを生成するために、乱数発生器が用いられる。

【0003】

近年では、例えば、スマートフォンやタブレットPCなど、回路規模および消費電流の制約が厳しい環境においても、商用コンテンツの利用や課金・決済などに用いるために性能のよい乱数を必要とする環境が増えてきている。

【0004】

一方で、ここで例に挙げたスマートフォンやタブレットPCなどのモバイル機器においては、不揮発性メモリとして、例えば、NAND型フラッシュメモリ等が主流として用いられている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−55205号公報

【特許文献2】特開2008−117471号公報

【特許文献3】特開2004−326867号公報

【特許文献4】特開2008−269473号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【課題を解決するための手段】

【0007】

実施形態によれば、一態様に係る半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイと、乱数を発生させる乱数発生回路と、前記メモリセルアレイおよび前記乱数発生回路を制御するコントローラとを具備し、前記乱数生成回路は、生成した制御パラメータにより前記メモリセルを読み出したデータにもとづく乱数パラメータを生成させる乱数制御回路と、前記乱数パラメータをシード値として用いて前記乱数を発生させる擬似乱数生成回路とを備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る半導体記憶装置の全体構成例を示すブロック図。

【図2】図1中のブロック(BLOCK)を示す等価回路図。

【図3】消去状態のメモリセルを示す断面図。

【図4】電子を注入する際のメモリセルを示す断面図。

【図5】書き込み状態のメモリセルを示す断面図。

【図6】電子を放出する際のメモリセルを示す断面図。

【図7】2値メモリセルの閾値分布を示す図。

【図8】ベリファイ動作有無の閾値分布を示す図。

【図9】多値メモリセルの閾値分布を示す図。

【図10】多値メモリセルの劣化モードの閾値分布を示す図。

【図11】第1の実施形態に係る乱数発生回路を示すブロック図。

【図12】図11中の擬似乱数発生回路の構成例を示す等価回路図。

【図13】図11中の乱数制御回路の構成例を示すブロック図。

【図14A】図13中の制御パラメータ発生回路の構成例を示すブロック図。

【図14B】ページアドレス設定回路によって読み出し対象に設定されたページに記録されるデータを示す図。

【図15】図13中の積算回路の構成例を示すブロック図。

【図16】図15中の積算回路の構成例を示すブロック図。

【図17】制御パラメータによるデータ読み出しを示す図。

【図18】制御パラメータによるデータ読み出しを示す図。

【図19】制御パラメータと閾値分布との関係を示す図(MLC)。

【図20】制御パラメータと閾値分布との関係を示す図(SLC)。

【図21】第2の実施形態に係る乱数発生回路を示すブロック図。

【図22】第3の実施形態に係る乱数発生回路を示すブロック図。

【図23】第4の実施形態に係る乱数発生回路を示すブロック図。

【図24】第5の実施形態に係るシステムを示すブロック図。

【図25】比較例1に係るプロトコルを示すブロック図。

【図26】比較例2に係るプロトコルを示すブロック図。

【図27】第6の実施形態に係る構成例を示すブロック図。

【図28】第6の実施形態に係る認証フローを示すフロー図。

【図29】第7の実施形態に係る構成例を示すブロック図。

【図30】第7の実施形態に係る認証フローを示すフロー図。

【図31】第8の実施形態に係る構成例を示すブロック図。

【図32】第8の実施形態に係る認証フローを示すフロー図。

【図33】第8の実施形態に係る秘密情報のデータ転送を示すブロック図。

【図34】第9の実施形態に係る構成例を示すブロック図。

【図35】第9の実施形態に係る認証フローを示すフロー図。

【図36】第10の実施形態に係る構成例を示すブロック図。

【図37】第10の実施形態に係る認証フローを示すフロー図。

【図38】第11の実施形態に係る構成例を示すブロック図。

【図39】第11の実施形態に係る認証フローを示すフロー図。

【図40】第12の実施形態に係る構成例を示すブロック図。

【図41】第12の実施形態に係る認証フローを示すフロー図。

【図42】第13の実施形態に係るID retrieval process(1)を示すブロック図。

【図43】第13の実施形態に係るID retrieval process(2)を示すブロック図。

【図44】第13の実施形態に係るID retrieval process(3)を示すブロック図。

【図45】第13の実施形態に係るID retrieval process(4)を示すブロック図。

【図46】第14の実施形態に係るID biding process(1)を示すブロック図。

【図47】第14の実施形態に係るID biding process(2)を示すブロック図。

【図48】第15の実施形態に係る構成例を示すブロック図。

【図49】第16の実施形態に係る構成例を示すブロック図。

【図50】第17の実施形態に係る構成例を示すブロック図。

【発明を実施するための形態】

【0009】

[乱数発生器(乱数発生回路)について]

まず、実施形態の説明の前に、乱数発生器(乱数発生回路)の概要について説明する。

【0010】

上述のように、セキュリティーを要する分野において、秘密鍵や複数者間の認証処理におけるチャレンジデータなどを生成するために、乱数発生器が用いられる。この乱数発生器は、大別すると、以下の2つに分類される。

【0011】

第1には、確定的乱数発生器(Deterministic RNG)もしくは疑似乱数発生器(Pseudo RNG)と呼ばれているものがある。これらの乱数発生器は、所定の初期値(シード)を設定することで乱数を発生する。確定的乱数発生器の例としては、FIPS 140-2 Annex Cに列挙されている暗号器に基づくものや、簡易的なものとしては線形帰還シフトレジスタ(LFSR:Linear Feedback Shift Resistor)からなるM系列発生器などが存在する。確定的乱数発生器は、ソフトウェア単独、ハードウェア単独、両者の併用など、の構成をとることができる。

【0012】

第2には、不確定的乱数発生器(Nondeterministic RNG)もしくは物理乱数発生器(Physical RNG)と呼ばれているものであり、主としてハードウェアから構成される。不確定的乱数発生器の例としては、電気回路の熱雑音(ジョンソンノイズ)を増幅した回路や、高速発振回路と非周期の平滑化回路による構成などが存在する。

【0013】

ここで、上記乱数発生器から生成される乱数として要求される主な性能としては、以下の3つの性能がある。

【0014】

「予測困難性」:予測困難性とは、観測された乱数から、次段の乱数を予測できないことをいう。そのためには、例えば、非周期性、非規則性等が求められる。

【0015】

「一様性」:一様性とは、出力される乱数において、0と1との出現確率が統計的に同等であることをいう。

【0016】

「長周期性」:長周期性とは、出力される乱数が再度出力される周期が十分に長いことをいう。

【0017】

ここで、一様性、長周期性については、確定的乱数発生器として上に例として挙げたM系列発生器を適切なレジスタ段数で構成することで実現可能である。一方で、予測困難性については、M系列発生器では観測された乱数列から容易にM系列発生器の構成が判明するため、出力乱数が予測でき、要求性能を満たすことが困難である。このため、コンテンツ保護や決済用セキュリティーの秘密鍵生成などに用いる場合、前述のFIPS 140-2 Annex Cに列挙された暗号器に基づくものを用いるか、もしくはICカードなどでは不確定的乱数発生器を独自の方法構成することなどが必要である。

【0018】

しかしながら、暗号器に基づく確定的乱数発生器は、ハードウェアにより実現する場合は多倍長演算回路や多段非線形回路などを要し、通常数10K〜100Kゲート以上の回路規模を要する。一方で、不確定的乱数発生器として例に挙げた熱雑音増幅回路でも、熱雑音は大きい場合でも数十μV で、演算増幅器や差動アンプを使い、4 〜 5 桁増幅して、更に0と1 のバランスを調整する回路が付加されるため、回路規模は大きくなる。また、高速発振回路と非周期の平滑化回路による構成でも、発振回路が持つ周期性が乱数に残ってしまう傾向があり、更に消費電流が大きくなるという傾向がある。

【0019】

そのため、上記のように、回路規模および消費電流の制約が厳しい環境においては、上記に挙げたものを適用することは困難である。

【0020】

近年では、上述したように、スマートフォンやタブレットPCなど、回路規模および消費電流の制約が厳しい環境においても、商用コンテンツの利用や課金・決済などに用いるために性能のよい乱数を必要とする環境が増えてきている。

【0021】

一方で、ここで例に挙げたスマートフォンやタブレットPCなどのモバイル機器においては、不揮発性メモリとして、例えば、NAND型フラッシュメモリ等が主流として用いられるという現状がある。

【0022】

そのため、NAND型フラッシュメモリ等の半導体記憶装置が、乱数生成機能を有している場合の利用価値は高い。

【0023】

そこで、以下の実施形態では、半導体記憶装置として、NAND型フラッシュメモリを一例に挙げ、半導体記憶装置内に乱数発生器を構成する具体例について提案する。

【0024】

以下、実施形態について図面を参照して説明する。この説明においては、半導体記憶装置の一例として、NAND型フラッシュメモリを挙げて説明するが、これに限られることはない。尚、この説明においては、全図にわたり共通の部分には共通の参照符号を付す。

【0025】

[第1の実施形態]

第1の実施形態に係る半導体記憶装置について、図1乃至図20を用いて説明する。

【0026】

<1.構成例>

1−1.全体構成例

まず、図1を用い、第1の実施形態に係る半導体記憶装置の全体構成例について説明する。図示するように、本例では、NAND型フラッシュメモリが一例として示される。

【0027】

本例に係るNAND型フラッシュメモリは、メモリセルアレイ11、乱数発生回路16、制御回路19、ビット線制御回路52、カラムデコーダ53、データ入出力バッファ54、データ入出力端子55、ワード線駆動回路56、制御信号入力端子58、電源発生回路59を備える。

【0028】

メモリセルアレイ11は、複数のブロック(BLOCK1〜BLOCKn)により構成される。複数のブロック(BLOCK1〜BLOCKn)のそれぞれは、ワード線およびビット線の交差位置に配置される複数のメモリセルを備える。詳細については、後述する。

【0029】

乱数発生回路16は、外部から入力される乱数トリガーコマンドに伴い制御回路19から出力される乱数トリガー信号に従い、所定の乱数を必要に応じて発生させる。発生された乱数は、制御回路19の制御に従い、秘密鍵や認証処理におけるチャレンジデータの生成などに用いられ、また必要に応じて、データ入出力端子55を介して外部のホスト装置に送信される。

【0030】

本例に係る乱数発生回路16は、所定の初期値(シード値)を設定することで乱数を発生させる擬似乱数発生回路等を備えるものであり、擬似乱数発生回路としては、例えば、線形帰還シフトレジスタ(LFSR: Linear Feedback Shift Resistor)等がある。詳細については、後述する。

【0031】

ビット線制御回路52は、ビット線を介してメモリセルアレイ11中のメモリセルのデータを読み出し、ビット線を介してメモリセルアレイ11中のメモリセルの状態を検出する。また、ビット線制御回路52は、ビット線を介してメモリセルアレイ11中のメモリセルに書き込み制御電圧を印加してメモリセルに書き込みを行う。

【0032】

ビット線制御回路52内には、図示しないページバッファ等のデータ記憶回路が設けられ、このデータ記憶回路は、カラムデコーダ53によって選択される。データ記憶回路に読み出されたメモリセルのデータは、データ入出力バッファ54を介してデータ入出力端子55から外部へ出力される。

【0033】

データ入出力端子55は、例えば、外部のホスト装置等に接続される。データ入出力端子55は、例えば8ビット、または16ビットのバス幅を有している。NAND型フラッシュメモリはトグルモードインターフェース(toggle mode interface)などの高速インターフェース規格をサポートしてもよい。トグルモードインターフェースでは、例えば、データストローブ信号(DQS)の立ち上がり、立ち下がり両エッジに同期してデータ入出力端子55を介したデータ転送が行われる。

【0034】

ホスト装置は、例えば、マイクロコンピュータ等であって、データ入出力端子55から出力されたデータを受ける。ホスト装置は、NAND型フラッシュメモリの動作を制御する各種コマンドCMD(書き込みコマンド、読み出しコマンド、消去コマンド、ステータスリードコマンド、乱数トリガーコマンド等)、アドレスADD、およびデータDTを出力する。ホスト装置からデータ入出力端子55に入力された書き込みデータDTは、データ入出力バッファ54を介して、カラムデコーダ53によって選択された上記データ記憶回路(図示せず)に供給される。一方、コマンドCMDおよびアドレスADDは、制御回路19に供給される。

【0035】

ワード線駆動回路56は、制御回路19の制御に従い、メモリセルアレイ11中のワード線を選択し、選択されたワード線に読み出し、書き込みあるいは消去に必要な電圧を印加する。

【0036】

電圧発生回路59は、制御回路19の制御に従い、図示中の接続された上記構成回路の動作に必要な電圧を供給する。例えば、電圧発生回路59は、ホスト装置から供給される外部電圧を昇圧して、読み出し、書き込みあるいは消去時にワード線に印加される電圧を生成する。

【0037】

制御回路(Controller)19は、NAND型フラッシュメモリの全体の動作を制御するために、接続される各回路に必要な制御信号および制御電圧を与える。制御回路19は、メモリセルアレイ11、乱数発生回路16、ビット線制御回路52、カラムデコーダ53、データ入出力バッファ54、ワード線駆動回路56、電圧発生回路59に接続される。接続された上記構成回路は、制御回路19によって制御される。

【0038】

制御回路19は、制御信号入力端子58に接続され、ホスト装置から制御信号入力端子58を介して入力されるWE(ライト・イネーブル)信号、RE(リード・イネーブル)信号、ALE(アドレス・ラッチ・イネーブル)信号、CLE(コマンド・ラッチ・イネーブル)信号等の制御信号の組み合わせによって制御される。

【0039】

ここで、機能的に表現すれば、上記ワード線駆動回路56、ビット線制御回路52、カラムデコーダ53、制御回路19は、データ書き込み回路、データ読み出し回路、およびデータ消去回路を構成する。ホスト装置は、NAND型フラッシュメモリが書き込み、読み出し、消去などの内部動作を実行中であるか否かを、図示せぬRY/BY(レディー/ビジー)信号出力端子をモニタすることで検知する。制御回路19は、RY/BY信号出力端子を介して、RY/BY信号を出力する。

【0040】

1−2.ブロック(BLOCK)の構成例

次に、図2を用い、第1の実施形態に係るメモリセルアレイを構成するブロック(BLOCK)の構成例について説明する。ここでは、図1中の一ブロック(BLOCK1)を一例に挙げて説明する。ここで、このブロックBLOCK1中のメモリセルは、一括してデータ消去されるため、ブロックはデータ消去単位である。

【0041】

ブロックBLOCK1は、ワード線方向(WL方向)に配置される複数のメモリセルユニットMUから構成される。メモリセルユニットMUは、WL方向と交差するビット線方向(BL方向)に配置され、電流経路が直列接続される8個のメモリセルMC0〜MC7からなるNANDストリング(メモリセルストリング)と、NANDストリングの電流経路の一端に接続されるソース側の選択トランジスタS1と、NANDストリングの電流経路の他端に接続されるドレイン側の選択トランジスタS2とから構成される。

【0042】

尚、本例では、メモリセルユニットMUは、8個のメモリセルMC0〜MC7から構成されるが、2つ以上のメモリセル、例えば、56個、32個等から構成されていればよく、8個に限定されるというものではない。

【0043】

ソース側の選択トランジスタS1の電流経路の他端はソース線SLに接続される。ドレイン側の選択トランジスタS2の電流経路の他端は、各メモリセルユニットMUに対応してメモリセルユニットMUの上方に設けられ、BL方向に延出するビット線BLm−1に接続される。

【0044】

ワード線WL0〜WL7は、WL方向に延び、WL方向の複数のメモリセルの制御ゲート電極に共通に接続される。選択ゲート線SGSは、WL方向に延び、WL方向の複数の選択トランジスタS1に共通に接続される。選択ゲート線SGDも、WL方向に延び、WL方向の複数の選択トランジスタS2に共通に接続される。

【0045】

また、ワード線WL0〜WL7ごとにページ(PAGE)が存在する。例えば、図中の破線で囲って示すように、ワード線WL7には、ページ7(PAGE7)が存在する。このページ(PAGE)ごとに、後述するデータ読み出し動作、データ書き込み動作が行われるため、ページ(PAGE)はデータ読み出し単位であり、データ書き込み単位である。

【0046】

1−3.メモリセルMCについて

次に、図3乃至図6を用い、セル構成およびデータ書き込み等がされる場合のメモリセルMCについて説明する。

【0047】

図3は、消去状態(Erase state)のメモリセルMCを示す。図示するように、メモリセルMCは、半導体基板(Si-sub)51上に、トンネル絶縁膜(Tunnel Oxide)TO、浮遊ゲート(Floating Gate)FG、ゲート間絶縁膜(Inter-gate Oxide)IGO、および制御ゲート(Control Gate)CGが順次積層され、半導体基板51中にこの積層構造を挟むように隔離してソース(Source)およびドレイン(Drain)が設けられる。

【0048】

消去状態のメモリセルMCは、浮遊ゲートFGに電子が注入されておらず、浮遊ゲートFGは正に帯電している。

【0049】

図4は、浮遊ゲートに電子を注入する(Inserting election)際のメモリセルMCを示す。図示するように、制御ゲートCGに書き込み電圧Vpgmを与えることで、ソースドレインのチャネルを介してトンネル絶縁膜TOをトンネルさせた電子が、浮遊ゲートFGに注入される。以下、浮遊ゲートFGに電子を注入する動作を、データ書き込みと表現する場合がある。

【0050】

図5は、書き込み状態(Programmed state)のメモリセルMCを示す。図示するように、書き込み状態のメモリセルMCは、浮遊ゲートFGに電子が注入されており、浮遊ゲートFGは負に帯電している。浮遊ゲートFGに電子が十分に注入されることにより、書き込み状態のメモリセルMCの閾値電圧は、消去状態のメモリセルMCの閾値電圧よりも高くなる。メモリセルMCは、この閾値電圧の変化を利用してデータを記憶する。

【0051】

図6は、浮遊ゲートから電子を放出する(Extracting election)際のメモリセルMCを示す。図示するように、半導体基板51に消去電圧Veraを与えることで、浮遊ゲートFGに注入された電子を、トンネル絶縁膜TOをトンネルさせて、半導体基板51に放出する。以下、浮遊ゲートFGから電子を放出する動作を、データ消去と表現する場合がある。

【0052】

なお、本例の場合、データ書き込み、データ読み出しは、上述のページ(PAGE)単位で行われる。また、データ消去は、上述のブロック(BLOCK)単位で行われる。

【0053】

1−4.閾値電圧分布について

次に、メモリセルの閾値電圧分布について説明する。

【0054】

1−4−1.2値メモリセル(SLC:Single Level Cell)の閾値分布

まず、図7を用い、2値メモリセル(SLC:Single Level Cell)の閾値分布について説明する。

【0055】

2値メモリセルの閾値分布(Vth分布)では、上記に示した動作により、メモリセルにデータを記録した後において、図示するような’1’、’0’の分布を示す。ここでは、消去状態(Erase state)に’1’を割り当て、書き込み状態(Programmed state)に’0’を割り当てている。

【0056】