半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置に関する。

【背景技術】

【0002】

抵抗変化型メモリの一つに磁気ランダムアクセスメモリ(MRAM(Magnetic Random Access Memory))がある。MRAMの書込み方式には、磁場書込み方式およびスピン注入書込み方式がある。このうちスピン注入書込み方式は、磁性体のサイズが小さくなる程、磁化反転に必要なスピン注入電流が小さくなるという性質を有するため、高集積化、低消費電力化および高性能化に有利である。

【0003】

スピン注入書込み方式のMTJ(Magnetic Tunnel Junction)素子は、2枚の強磁性層とこれらに挟まれた非磁性バリア層(絶縁薄膜)とからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層の磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。2枚の強磁性層の磁化配列が平行状態(P(Parallel)状態)の場合に、MTJ素子は低抵抗状態となり、2枚の強磁性層の磁化配列が非平行状態(AP(Anti Parallel)状態)の場合に、MTJ素子は高抵抗状態となる。

【0004】

P状態を書き込むときには、MTJ素子をAP状態からP状態へ反転させるために必要な電流を流さなくてはならない。また、AP状態を書き込むときは、MTJをP状態からAP状態へ反転させるのに必要な電流を流さなくてはならない。

【0005】

従来からMRAMでは、MTJ素子に充分大きな書込み電流を流すために、1つのMTJ素子に対して2つのセルトランジスタが設けられていた。各セルトランジスタのソースおよびドレインの一方はMTJ素子の下端に接続され、各セルトランジスタのソースおよびドレインの他方はビアコンタクトを介してビット線に接続されている。従って、2つのセルトランジスタに対応する2つのビアコンタクトの分だけレイアウト面積が大きくなる。従来のMRAMのメモリセルのサイズは、16F2(Fは、Feature Size)である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−192636号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【課題を解決するための手段】

【0008】

本実施形態によれば、本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に従ったMRAMのメモリチップを示すブロック図。

【図2】単一のメモリセルMCの構成を示す説明図。

【図3】第1の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図。

【図4】図3の4−4線に沿った断面図。

【図5】図3の5−5線に沿った断面図。

【図6】図3の6−6線に沿った断面図。

【図7】データ読出し時における第1のビット線BL1と第2のビット線BL2との間の等価回路図、および、選択MTJおよび2つの通過MTJ素子の抵抗値の組み合わせと第1のビット線BL1および第2のビット線BL2の間の抵抗値Rtotalとの関係を示す表。

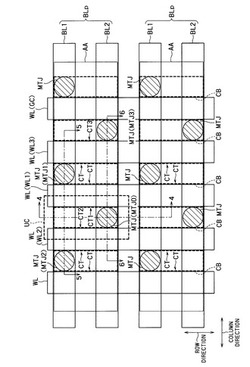

【図8】第2の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図。

【図9】図8の9−9線に沿った断面図。

【図10】図8の10−10線に沿った断面図。

【図11】図8の11−11線に沿った断面図。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

【0011】

(第1の実施形態)

図1は、第1の実施形態に従った磁気ランダムアクセスメモリ(以下、MRAM)のメモリチップを示すブロック図である。尚、本実施形態は、MRAM以外の抵抗変化型素子を用いたメモリ(例えば、PCRAM、RRAM等)にも適用可能である。

【0012】

本実施形態によるMRAMは、メモリセルアレイMCAと、センスアンプSAと、メインデータコントローラMDCと、DQバッファDQBと、カラムコントローラCCと、ロウコントローラRCと、クロックバッファCLKBと、コマンドコントローラCMDCと、アドレスコントローラADDCと、アレイコントローラACとを備えている。

【0013】

メモリセルアレイMCAは、マトリクス状に二次元配置された複数のメモリセルMCを備えている。各メモリセルMCはビット線BL(あるいはビット線対)とワード線WLとの交点に対応して配置されている。ビット線BLは、カラム方向に延伸している。ワード線WLは、カラム方向に対して直交するロウ方向に延伸している。

【0014】

センスアンプSAは、ビット線BLを介してメモリセルMCに接続されており、メモリセルMCのデータを検出するように構成されている。ライトドライバWDは、ビット線BLを介してメモリセルMCに接続されており、メモリセルMCにデータを書き込むように構成されている。

【0015】

メインデータコントローラMDCは、DQバッファDQBから受け取ったデータを、カラムコントローラCCの制御を受けて、所望のカラムに書き込むようにライトドライバWDへ転送し、あるいは、カラムコントローラCCの制御を受けて、所望のカラムから読み出したデータをDQバッファDQBへ転送する。また、メインデータコントローラMDCは、後述するように、ライトマスクデータWMまたは書込み禁止領域アドレスWOADDに従って、データの書込みを禁止するように構成されている。

【0016】

DQバッファDQBは、DQパッドDQを介して読出しデータを一時的に保持し、その読出しデータをメモリチップ1の外部へ出力する。あるいは、DQバッファDQBは、DQパッドDQを介して書込みデータをメモリチップ1の外部から受け取り、一時的に保持する。

【0017】

カラムコントローラCCは、カラムアドレスに従って所望のカラムのビット線BLを選択的に駆動するようにセンスアンプSAまたはライトドライバWDを動作させる。

【0018】

ロウコントローラRCは、ロウアドレスに従って所望のワード線WLを選択的に駆動させるようにワード線ドライバWLDを動作させる。

【0019】

クロックバッファCLKBは、メモリチップ1全体の動作のタイミングを決定するクロック信号を入力する。

【0020】

コマンドコントローラCMDCは、読出し動作、書込み動作等の各種動作を示すコマンドを受け取り、それらのコマンドに従ってカラムコントローラCCおよびロウコントローラRCを制御する。

【0021】

アドレスコントローラADDCは、ロウアドレスおよびカラムアドレス等を受け取り、これらのアドレスをデコードし、カラムコントローラCCおよびロウコントローラRCにこれらのアドレスを送る。

【0022】

アレイコントローラACは、メモリセルアレイMCAの全体的な制御を行う。

【0023】

図2は、単一のメモリセルMCの構成を示す説明図である。各メモリセルMCは、それぞれ磁気トンネル接合素子(MTJ(Magnetic Tunnel Junction)素子)と、セルトランジスタCTとを含む。MTJ素子およびセルトランジスタCTは、ビット線BLとソース線SLとの間に直列に接続されている。メモリセルMCにおいて、セルトランジスタCTがビット線BL側に配置され、MTJ素子がソース線SL側に配置されている。セルトランジスタCTのゲートは、ワード線WLに接続されている。

【0024】

TMR(tunneling magnetoresistive)効果を利用したMTJ素子は、2枚の強磁性層とこれらに挟まれた非磁性層(絶縁薄膜)とからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層の磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。例えば、低抵抗状態をデータ“0”と定義し、高抵抗状態をデータ“1”と定義すれば、MTJ素子に1ビットデータを記録することができる。もちろん、低抵抗状態をデータ“1”と定義し、高抵抗状態をデータ“0”と定義してもよい。例えば、MTJ素子は、固定層、トンネルバリア層、記録層を順次積層して構成される。固定層Pおよび記録層Frは、強磁性体で構成されており、トンネルバリア層は、絶縁膜からなる。固定層Pは、磁化の向きが固定されている層であり、記録層Frは、磁化の向きが可変であり、その磁化の向きによってデータを記憶する。

【0025】

書込み時に矢印A1の向きに反転閾値電流以上の電流を流すと、固定層Pの磁化の向きに対して記録層Frのそれがアンチパラレル状態となり、高抵抗状態(データ“1”)となる。書込み時に矢印A2の向きに反転閾値電流以上の電流を流すと、固定層Pと記録層Frとのそれぞれの磁化の向きがパラレル状態となり、低抵抗状態(データ“0”)となる。このように、TMJ素子は、電流の方向によって異なるデータを書き込むことができる。

【0026】

図3は、第1の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図である。図4は、図3の4−4線に沿った断面図である。図5は、図3の5−5線に沿った断面図である。図6は、図3の6−6線に沿った断面図である。

【0027】

本実施形態によるMRAMでは、図3に示すように、第1のビット線BL1および第2のビット線BL2がカラム方向に延伸しており、ワード線WLがカラム方向とほぼ直交するロウ方向に延伸している。互いに隣接する第1および第2のビット線BL1、BL2は、1対のビット線ペアBLpを成す。ビット線ペアBLpは、それぞれアクティブエリアAAに対応して設けられている。ビット線ペアBLpの第1および第2のビット線BL1、BL2は、ビアコンタクトV1を介して、同一のアクティブエリアAA上に設けられたMTJ素子の上端に電気的に接続されている。MTJ素子の下端は、セルトランジスタCTのソースまたはドレインに電気的に接続されている。

【0028】

平面レイアウトにおいては、隣接する2つのワード線WL間にMTJ素子が設けられている。隣接する2つのワード線WL間に設けられたMTJ素子は、該2つのワード線WLを共有している。該2つのワード線WLは、セルトランジスタCTのゲート電極GCとして機能し、該2つのワード線WL間に設けられたMTJ素子のいずれかを選択するときにそれぞれに対応するセルトランジスタCTを導通状態にする。

【0029】

アクティブエリアAAは、メモリセルアレイMCA内においてカラム方向に連続して延伸しており、従って、ビット線ペアBLpに対応してカラム方向に配列されたMTJ素子は、アクティブエリアAAを共有している。アクティブエリアAAは、ロウ方向において素子分離領域STI(Shallow Trench Isolation)によって分離されている。

【0030】

図5および図6に示すように、本実施形態によるMRAMは、半導体基板としてのシリコン基板10と、シリコン基板10上に形成されたアクティブエリアAAとを備えている。アクティブエリアAA上に形成されたセルトランジスタCTは、ソース層S、ドレイン層Dおよびゲート電極GCを備えている。ゲート電極GCは、ゲート絶縁膜20によってシリコン基板10から絶縁されており、絶縁膜30によってコンタクトプラグCBから絶縁されている。

【0031】

図5に示すように、第1のビット線BL1に沿った断面では、セルトランジスタCTのソース層S上には、コンタクトプラグCBが設けられている。コンタクトプラグCB上には、下部電極LEが設けられており、下部電極LE上にMTJ素子が設けられている。これにより、セルトランジスタCTのソース層Sは、コンタクトプラグCBおよび下部電極LEを介して第1の記憶素子としてのMTJ素子の下端に電気的に接続されている。さらに、MTJ素子上には、上部電極UEが設けられており、上部電極UE上にはビアコンタクトV1が設けられている。ビアコンタクトV1上には第1のビット線BL1が設けられている。これにより、第1の記憶素子としてのMTJ素子の上端は、上部電極UEおよびビアコンタクトV1を介して第1のビット線BL1に接続されている。

【0032】

図6に示すように、第2のビット線BL2に沿った断面では、セルトランジスタCTのドレイン層D上に、コンタクトプラグCBが設けられている。コンタクトプラグCB上には、下部電極LEが設けられており、下部電極LE上にMTJ素子が設けられている。これにより、セルトランジスタCTのドレイン層Dは、コンタクトプラグCBおよび下部電極LEを介して第2の記憶素子としてのMTJ素子の下端に電気的に接続されている。さらに、MTJ素子上には、上部電極UEが設けられており、上部電極UE上にはビアコンタクトV1が設けられている。ビアコンタクトV1上には第2のビット線BL2が設けられている。これにより、第2の記憶素子としてのMTJ素子の上端は、上部電極UEおよびビアコンタクトV1を介して第2のビット線BL2に接続されている。

【0033】

即ち、第1のビット線BL1は、図5に示すように、ビアコンタクトV1およびMTJ素子等を介してセルトランジスタCTのソース層Sに電気的に接続されており、そのセルトランジスタCTのドレイン層Dは、図6に示すように、MTJ素子およびビアコンタクトV1等を介して第2のビット線BL2に接続される。これにより、2つのMTJ素子および1つのセルトランジスタCTが第1のビット線BL1と第2のビット線BL2との間に直列に接続されることになる。換言すると、各セルトランジスタCTの両端は、それぞれMTJ素子を介して第1または第2のビット線BL1,BL2に接続されている。

【0034】

このように、MTJ素子の一端はセルトランジスタCTのソース層Sまたはドレイン層Dに電気的に接続され、MTJ素子の他端は第1または第2のビット線BL1、BL2に接続されている。そして、第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。

【0035】

図4に示すように、ロウ方向の断面では、MTJ素子の下端は、アクティブエリアAAのロウ方向の幅と同じ幅(長さ)を有するコンタクトプラグCBに接続されている。そして、セルトランジスタCTのドレイン層D(またはソース層S)が、コンタクトプラグCBの下に該コンタクトプラグCBに沿って形成されている。これにより、MTJ素子の下端は、セルトランジスタCTのドレイン層D(またはソース層S)に電気的に接続されている。

【0036】

尚、セルトランジスタCTのソース層Sおよびドレイン層Dとの呼称は、便宜的なものであり、電流の流れる方向によってソース層Sとドレイン層Dとの位置関係は逆になることともある。また、セルトランジスタCTのゲート電極GC自体が、ワード線WLとして機能してもよいが、ワード線WLは、ゲート電極GCとは別のレイヤに設けられてもよい。この場合、ゲート電極GCは、コンタクト(図示せず)を介していずれかのワード線WLに電気的に接続される。

【0037】

図3に示すように、第1および第2のビット線BL1、BL2のそれぞれに接続され、かつ、ロウ方向およびカラム方向に対して傾斜する方向に隣接する2つのMTJ素子が1つのセルトランジスタCTを共有している。これらの隣接する2つのMTJ素子は、ワード線WLの両側に設けられている。また、本実施形態では、第1のビット線BL1とアクティブエリアAA(セルトランジスタCTのソース層S)との間の接続、および、第2のビット線BL2とアクティブエリアAA(セルトランジスタCTのドレイン層D)との間の接続の全てに、MTJ素子が介在している。従って、第1のビット線BL1と第2のビット線BL2との間において、2つのMTJ素子および1つのセルトランジスタCTは、MTJ、CT、MTJの順に直列に接続されることになる。データ書込みおよびデータ読出し時における電流は、第1のビット線BL1と第2のビット線BL2との間において、2つのMTJ素子および1つのセルトランジスタCTを介して流れることになる。

【0038】

さらに、各セルトランジスタCTの両端は、それぞれMTJ素子を介して第1または第2のビット線BL1、BL2に接続されている。そして、第1のビット線BL1に接続された1つのMTJ素子(例えば、MTJ1)の両側にある2つのワード線(例えば、WL1およびWL3)は、第2のビット線BL2に接続された2つのMTJ素子(例えば、MTJ0、MTJ3)と隣接する。セルトランジスタCTは、1つのMTJ素子(例えば、MTJ1)と2つのMTJ素子(例えば、MTJ0、MTJ3)との間にそれぞれ設けられている。これにより、データ書込みおよびデータ読出し時において1つの選択MTJ素子に流す電流は、2つのセルトランジスタCTを介して駆動されることになる。

【0039】

尚、本実施形態では、第1のビット線BL1および第2のビット線BL2は、同一の配線層で形成されている。従って、第1および第2のビット線BL1、BL2は、1度のリソグラフィ工程およびエッチング工程によって形成され得る。

【0040】

データ読出し動作またはデータ書込み動作において、第1のビット線BL1に接続された1つの第1のMTJ素子を選択する場合、第2のビット線BL2に接続された複数の第2のMTJ素子を介して第1のMTJ素子へ電流を流す。このとき、1つの第1のMTJ素子がデータ書込みまたはデータ読出しの対象となる選択MTJ素子であり、複数の第2のMTJ素子は非選択MTJ素子である。例えば、図3においてMTJ素子MTJ1に電流を選択的に流す場合、MTJ1の両側にある2本のワード線WL1、WL3を駆動する。これにより、第2のビット線BL2からの電流は、MTJ素子MTJ1に斜め方向に隣接する2つのMTJ素子MTJ0およびMTJ3を介してアクティブエリアAAへ流れ、次に、MTJ0およびMTJ3のそれぞれに接続する2つのセルトランジスタCT1、CT3を介してMTJ素子MTJ1へ流れる。その後、MTJ1を通過した電流は、第1のビット線BL1へ流れる。

【0041】

逆に、第2のビット線BL2に接続された1つの第2のMTJ素子を選択する場合、第1のビット線BL1に接続された複数の第1のMTJ素子を介して第2のMTJ素子へ電流を流す。このとき、1つの第2のMTJ素子がデータ書込みまたはデータ読出しの対象となる選択MTJ素子であり、複数の第1のMTJ素子は非選択MTJ素子である。例えば、図3においてMTJ素子MTJ0に電流を選択的に流す場合、MTJ0の両側にある2本のワード線WL1、WL2を駆動する。これにより、第1のビット線BL1からの電流は、MTJ素子MTJ0に斜め方向に隣接する2つのMTJ素子MTJ1およびMTJ2を介してアクティブエリアAAへ流れ、次に、MTJ1およびMTJ2のそれぞれに接続する2つのセルトランジスタCT1、CT2を介してMTJ素子MTJ0へ流れる。その後、MTJ0を通過した電流は、第2のビット線BL2へ流れる。

【0042】

本実施形態では、いずれのMTJ素子を選択しても、2つの非選択のMTJ素子(通過MTJ素子ともいう)を通過した電流が1つの選択MTJ素子に流れる。2つの非選択のMTJ素子のそれぞれに流れる電流をImtjとすれば、選択MTJ素子に2×Imtjの電流を流すことができる。

【0043】

従って、電流Imtjを流したときにMTJ素子の磁化配列が反転せず、電流2×Imtjを流したときにMTJ素子の磁化配列が反転すれば、選択MTJ素子のみにデータを書き込むことができる。このようなMTJ素子は、通過電流の変化に対する反転確率の増加を急峻にする(即ち、反転確率の増加率を大きくする)ことによって実現できる。これにより、通過電流がImtjである場合に、MTJ素子はディスターブをほとんど受けず、一方で、通過電流が2×Imtjである場合に、MTJ素子の磁化配列は充分に反転することができる。即ち、選択MTJ素子のみにデータを書き込むことができ、そのときに電流が通過する2つの通過MTJ素子にはデータは書き込まれない。

【0044】

データ読出し動作では、そもそも磁化配列が反転しない程度の電流しか選択MTJ素子に流さない。よって、選択MTJ素子に隣接する2つの通過MTJ素子には、その読出し電流の半分の電流しか流れないので、通過MTJ素子ではディスターブをほとんど受けない。

【0045】

しかし、選択MTJ素子の読出し電流は、2つの通過MTJ素子のデータ状態(抵抗値)によって変化することに注意する必要がある。これは、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalが、選択MTJおよび2つの通過MTJ素子の合成抵抗になるからである。

【0046】

図7(A)は、データ読出し時における第1のビット線BL1と第2のビット線BL2との間の等価回路図である。図7(B)は、選択MTJおよび2つの通過MTJ素子の抵抗値の組み合わせと第1のビット線BL1および第2のビット線BL2の間の抵抗値Rtotalとの関係を示す表である。

【0047】

図7(A)に示すように、選択MTJ素子MTJ0および通過MTJ素子MTJ1、MTJ2は、データ読出し時に抵抗として考えることができる。通過MTJ素子MTj1、MTJ2は、選択MTJ素子MTJ0と第1のビット線BL2との間に並列に接続される。尚、セルトランジスタCTは導通状態であり、その抵抗値は、MTJ素子MTJ0〜MTJ2の抵抗値に対して無視できる。

【0048】

図7(B)に示すように本実施形態では、選択MTJ素子のデータだけでなく、通過MTJ素子のデータによって抵抗値(読み出し電流)が変化することが分かる。例えば、P状態のMTJ素子の抵抗値を7Kオームとし、AP状態のMTJ素子の抵抗値を21Kオームとする。

【0049】

この場合、選択MTJ素子MTJ0がP状態(データ“0”)であれば、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalは、2つの通過MTJ素子のデータ状態によって、10.5Kオーム〜17.5Kオームの範囲で変化し得る。選択MTJ素子MTJ0がAP状態(データ“1”)であれば、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalは、2つの通過MTJ素子のデータ状態によって、24.5Kオーム〜31.5Kオームの範囲で変化し得る。

【0050】

従って、選択MTJ素子MTJ0がデータ“0”であるときの抵抗値Rtotalと、選択MTJ素子MTJ0がデータ“1”であるときの抵抗値Rtotalとの間のマージンは、7Kオームになる。この抵抗値Rtotalのマージンは、選択MTJ素子MTJ0のみの抵抗値のマージン(14Kオーム)と比べて小さいが、データの読出し動作においては充分と言える。

【0051】

以上のような構成を有するMRAMのユニットセル(単位メモリセル)UC(図3の破線枠)の面積は、8F2である。ユニットセルUCは、平面レイアウトの一単位を示すパターンであり、このパターンをシリコン基板10の平面内に繰り返すことによってメモリセルアレイMCAの平面レイアウトが形成される。ここで、F(Feature Size)は、リソグラフィ技術およびエッチング技術を用いた最小加工寸法である。このユニットセルUCの面積は、従来のそれ(16F2)の半分である。

【0052】

本実施形態によるMRAMの第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。第1のビット線BL1とアクティブエリアAAとの間の接続、および、第2のビット線BL2とアクティブエリアAAとの間の接続の全てに、MTJ素子が介在する。即ち、第1および第2のビット線BL1、BL2において、ビアコンタクトおよびコンタクトプラグ等のコンタクトだけでアクティブエリアAAに接続されている部分は無い。

【0053】

従って、本実施形態は、MTJ素子の平面レイアウトにおける配置密度を高めることができ、従って、ユニットセル(メモリセル)UCのレイアウト面積を従来よりも小さくすることができる。

【0054】

一方、選択MTJ素子に電流を流すときには、該選択MTJ素子に隣接する複数の通過MTJ素子および2つのセルトランジスタを介して電流が該選択MTJ素子に供給される。従って、反転閾値電流よりも充分に大きな書込み電流を選択MTJ素子に供給することができる。

【0055】

その結果、本実施形態は、ユニットセルのサイズを従来よりも小さくすることができ、かつ、MTJ素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保することができる。

【0056】

(第2の実施形態)

図8は、第2の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図である。図9は、図8の9−9線に沿った断面図である。図10は、図8の10−10線に沿った断面図である。図11は、図8の11−11線に沿った断面図である。尚、図8の5−5線に沿った断面図は、図5に示すものと同様である。

【0057】

第1の実施形態では、第1および第2のビット線BL1、BL2は、同一の配線層で形成されている。これに対し、第2の実施形態では、図9および図10に示すように、第2の実施形態による第1のビット線BL1および第2のビット線BL2は、それぞれ異なる金属配線層M1およびM2で形成されている。また、第1のビット線BL1および第2のビット線BL2は、それぞれカラム方向に異なる位置でMTJ素子を介してセルトランジスタCTのソース層Sまたはドレイン層Dに電気的に接続されている。これにより、ビット線ペアBLpを成す第1のビット線BL1と第2のビット線BL2との間の電気的絶縁状態を維持しつつ、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができる。

【0058】

図9に示すように、第2のビット線BL2は、金属配線層M1よりも上層である金属配線層M2で形成されている。従って、第2のビット線BL2は、図9および図11に示すように、深いビアコンタクトV1を介して上部電極UEに接続されている。図10に示すように、第1のビット線BL1は、金属配線層M2よりも下層である金属配線層M1で形成されている。従って、第1のビット線BL1は、比較的浅いビアコンタクトV1を介して上部電極UEに接続されている。

【0059】

図9に示すように、ビット線ペアBLpにおいて第1のビット線BL1と第2のビット線BL2との間にはスペースが無い。従って、第1のビット線BL1と第2のビット線BL2に接続されているビアコンタクトV1との間の短絡を防止するために、保護絶縁膜40が第1のビット線BL1の側面および上面を被覆するように設けられている。これにより、第2のビット線BL2に接続されているビアコンタクトV1を形成する際に、コンタクトホールは、リソグラフィによるフォトレジストおよび保護絶縁膜40をマスクとしてエッチングすることによって形成され得る。保護絶縁膜40の材料は、層間絶縁膜ILD(Interlayer Dielectric)の材料に対してエッチング速度の遅い材料で形成される。例えば、層間絶縁膜ILDがシリコン酸化膜で形成されている場合、保護絶縁膜40は、シリコン窒化膜で形成されている。第2の実施形態のその他の構成は、第1の実施形態の対応する構成と同様でよい。

【0060】

第2の実施形態によれば、図8に示すように、平面レイアウトにおいて、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができので、ユニットセルUCの面積がさらに小さくなり得る。例えば、図8に示すユニットセルUCの面積は、6F2である。

【0061】

第2の実施形態によるMRAMの動作は、第1の実施形態によるMRAMの動作と同様でよい。

【0062】

第2の実施形態によるMRAMの第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。第1のビット線BL1とアクティブエリアAAとの間の接続、および、第2のビット線BL2とアクティブエリアAAとの間の接続の全てに、MTJ素子が介在する。即ち、第1および第2のビット線BL1、BL2において、ビアコンタクトおよびコンタクトプラグ等のコンタクトだけでアクティブエリアAAに接続されている部分は無い。また、第2の実施形態におけるデータ読出しまたはデータ書込み動作は、第1の実施形態のそれらと同様である。従って、第2の実施形態は、第1の実施形態と同様の効果を得ることができる。

【0063】

さらに、第2の実施形態によれば、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができので、ユニットセルUCの面積が第1の実施形態のそれよりも小さくなる。

【0064】

以上から第2の実施形態も、ユニットセルのサイズを従来よりも小さくすることができ、かつ、MTJ素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保することができる。

【0065】

ただし、第2の実施形態では、上層側の第2のビット線BL2に接続されたビアコンタクトV1と下層側の第1のビット線BL1との間の間隔が狭くなるので、保護絶縁膜40を第1のビット線BL1の上面および側面に形成する工程が必要になる。また、第1および第2のビット線BL1、BL2のために2層の金属配線層M1,M2が必要になる。

【0066】

さらに、第2の実施形態では、平面レイアウトにおいて、第2のビット線BL2と第1のビット線BL1との間の間隔が無くなるので、セルトランジスタCTのゲート幅が第1の実施形態におけるセルトランジスタCTのゲート幅よりも狭くなる。しかし、2つのセルトランジスタCTを介して1つの選択MTJ素子に電流を流しているので、第2の実施形態によるMRAMは、反転閾値電流以上の電流を選択MTJ素子に流すことは可能である。

【0067】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0068】

MTJ・・・MTJ素子、CT・・・セルトランジスタ、S・・・ソース層、D・・・ドレイン層、BL1、BL2・・・ビット線、WL・・・ワード線、AA・・・アクティブエリア、STI・・・素子分離領域、V1・・・ビアコンタクト、CB・・・コンタクトプラグ、UE・・・上部電極、LE・・・下部電極、10・・・シリコン基板、20・・・ゲート絶縁膜、40・・・保護絶縁膜

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置に関する。

【背景技術】

【0002】

抵抗変化型メモリの一つに磁気ランダムアクセスメモリ(MRAM(Magnetic Random Access Memory))がある。MRAMの書込み方式には、磁場書込み方式およびスピン注入書込み方式がある。このうちスピン注入書込み方式は、磁性体のサイズが小さくなる程、磁化反転に必要なスピン注入電流が小さくなるという性質を有するため、高集積化、低消費電力化および高性能化に有利である。

【0003】

スピン注入書込み方式のMTJ(Magnetic Tunnel Junction)素子は、2枚の強磁性層とこれらに挟まれた非磁性バリア層(絶縁薄膜)とからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層の磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。2枚の強磁性層の磁化配列が平行状態(P(Parallel)状態)の場合に、MTJ素子は低抵抗状態となり、2枚の強磁性層の磁化配列が非平行状態(AP(Anti Parallel)状態)の場合に、MTJ素子は高抵抗状態となる。

【0004】

P状態を書き込むときには、MTJ素子をAP状態からP状態へ反転させるために必要な電流を流さなくてはならない。また、AP状態を書き込むときは、MTJをP状態からAP状態へ反転させるのに必要な電流を流さなくてはならない。

【0005】

従来からMRAMでは、MTJ素子に充分大きな書込み電流を流すために、1つのMTJ素子に対して2つのセルトランジスタが設けられていた。各セルトランジスタのソースおよびドレインの一方はMTJ素子の下端に接続され、各セルトランジスタのソースおよびドレインの他方はビアコンタクトを介してビット線に接続されている。従って、2つのセルトランジスタに対応する2つのビアコンタクトの分だけレイアウト面積が大きくなる。従来のMRAMのメモリセルのサイズは、16F2(Fは、Feature Size)である。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−192636号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【課題を解決するための手段】

【0008】

本実施形態によれば、本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に従ったMRAMのメモリチップを示すブロック図。

【図2】単一のメモリセルMCの構成を示す説明図。

【図3】第1の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図。

【図4】図3の4−4線に沿った断面図。

【図5】図3の5−5線に沿った断面図。

【図6】図3の6−6線に沿った断面図。

【図7】データ読出し時における第1のビット線BL1と第2のビット線BL2との間の等価回路図、および、選択MTJおよび2つの通過MTJ素子の抵抗値の組み合わせと第1のビット線BL1および第2のビット線BL2の間の抵抗値Rtotalとの関係を示す表。

【図8】第2の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図。

【図9】図8の9−9線に沿った断面図。

【図10】図8の10−10線に沿った断面図。

【図11】図8の11−11線に沿った断面図。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

【0011】

(第1の実施形態)

図1は、第1の実施形態に従った磁気ランダムアクセスメモリ(以下、MRAM)のメモリチップを示すブロック図である。尚、本実施形態は、MRAM以外の抵抗変化型素子を用いたメモリ(例えば、PCRAM、RRAM等)にも適用可能である。

【0012】

本実施形態によるMRAMは、メモリセルアレイMCAと、センスアンプSAと、メインデータコントローラMDCと、DQバッファDQBと、カラムコントローラCCと、ロウコントローラRCと、クロックバッファCLKBと、コマンドコントローラCMDCと、アドレスコントローラADDCと、アレイコントローラACとを備えている。

【0013】

メモリセルアレイMCAは、マトリクス状に二次元配置された複数のメモリセルMCを備えている。各メモリセルMCはビット線BL(あるいはビット線対)とワード線WLとの交点に対応して配置されている。ビット線BLは、カラム方向に延伸している。ワード線WLは、カラム方向に対して直交するロウ方向に延伸している。

【0014】

センスアンプSAは、ビット線BLを介してメモリセルMCに接続されており、メモリセルMCのデータを検出するように構成されている。ライトドライバWDは、ビット線BLを介してメモリセルMCに接続されており、メモリセルMCにデータを書き込むように構成されている。

【0015】

メインデータコントローラMDCは、DQバッファDQBから受け取ったデータを、カラムコントローラCCの制御を受けて、所望のカラムに書き込むようにライトドライバWDへ転送し、あるいは、カラムコントローラCCの制御を受けて、所望のカラムから読み出したデータをDQバッファDQBへ転送する。また、メインデータコントローラMDCは、後述するように、ライトマスクデータWMまたは書込み禁止領域アドレスWOADDに従って、データの書込みを禁止するように構成されている。

【0016】

DQバッファDQBは、DQパッドDQを介して読出しデータを一時的に保持し、その読出しデータをメモリチップ1の外部へ出力する。あるいは、DQバッファDQBは、DQパッドDQを介して書込みデータをメモリチップ1の外部から受け取り、一時的に保持する。

【0017】

カラムコントローラCCは、カラムアドレスに従って所望のカラムのビット線BLを選択的に駆動するようにセンスアンプSAまたはライトドライバWDを動作させる。

【0018】

ロウコントローラRCは、ロウアドレスに従って所望のワード線WLを選択的に駆動させるようにワード線ドライバWLDを動作させる。

【0019】

クロックバッファCLKBは、メモリチップ1全体の動作のタイミングを決定するクロック信号を入力する。

【0020】

コマンドコントローラCMDCは、読出し動作、書込み動作等の各種動作を示すコマンドを受け取り、それらのコマンドに従ってカラムコントローラCCおよびロウコントローラRCを制御する。

【0021】

アドレスコントローラADDCは、ロウアドレスおよびカラムアドレス等を受け取り、これらのアドレスをデコードし、カラムコントローラCCおよびロウコントローラRCにこれらのアドレスを送る。

【0022】

アレイコントローラACは、メモリセルアレイMCAの全体的な制御を行う。

【0023】

図2は、単一のメモリセルMCの構成を示す説明図である。各メモリセルMCは、それぞれ磁気トンネル接合素子(MTJ(Magnetic Tunnel Junction)素子)と、セルトランジスタCTとを含む。MTJ素子およびセルトランジスタCTは、ビット線BLとソース線SLとの間に直列に接続されている。メモリセルMCにおいて、セルトランジスタCTがビット線BL側に配置され、MTJ素子がソース線SL側に配置されている。セルトランジスタCTのゲートは、ワード線WLに接続されている。

【0024】

TMR(tunneling magnetoresistive)効果を利用したMTJ素子は、2枚の強磁性層とこれらに挟まれた非磁性層(絶縁薄膜)とからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層の磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。例えば、低抵抗状態をデータ“0”と定義し、高抵抗状態をデータ“1”と定義すれば、MTJ素子に1ビットデータを記録することができる。もちろん、低抵抗状態をデータ“1”と定義し、高抵抗状態をデータ“0”と定義してもよい。例えば、MTJ素子は、固定層、トンネルバリア層、記録層を順次積層して構成される。固定層Pおよび記録層Frは、強磁性体で構成されており、トンネルバリア層は、絶縁膜からなる。固定層Pは、磁化の向きが固定されている層であり、記録層Frは、磁化の向きが可変であり、その磁化の向きによってデータを記憶する。

【0025】

書込み時に矢印A1の向きに反転閾値電流以上の電流を流すと、固定層Pの磁化の向きに対して記録層Frのそれがアンチパラレル状態となり、高抵抗状態(データ“1”)となる。書込み時に矢印A2の向きに反転閾値電流以上の電流を流すと、固定層Pと記録層Frとのそれぞれの磁化の向きがパラレル状態となり、低抵抗状態(データ“0”)となる。このように、TMJ素子は、電流の方向によって異なるデータを書き込むことができる。

【0026】

図3は、第1の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図である。図4は、図3の4−4線に沿った断面図である。図5は、図3の5−5線に沿った断面図である。図6は、図3の6−6線に沿った断面図である。

【0027】

本実施形態によるMRAMでは、図3に示すように、第1のビット線BL1および第2のビット線BL2がカラム方向に延伸しており、ワード線WLがカラム方向とほぼ直交するロウ方向に延伸している。互いに隣接する第1および第2のビット線BL1、BL2は、1対のビット線ペアBLpを成す。ビット線ペアBLpは、それぞれアクティブエリアAAに対応して設けられている。ビット線ペアBLpの第1および第2のビット線BL1、BL2は、ビアコンタクトV1を介して、同一のアクティブエリアAA上に設けられたMTJ素子の上端に電気的に接続されている。MTJ素子の下端は、セルトランジスタCTのソースまたはドレインに電気的に接続されている。

【0028】

平面レイアウトにおいては、隣接する2つのワード線WL間にMTJ素子が設けられている。隣接する2つのワード線WL間に設けられたMTJ素子は、該2つのワード線WLを共有している。該2つのワード線WLは、セルトランジスタCTのゲート電極GCとして機能し、該2つのワード線WL間に設けられたMTJ素子のいずれかを選択するときにそれぞれに対応するセルトランジスタCTを導通状態にする。

【0029】

アクティブエリアAAは、メモリセルアレイMCA内においてカラム方向に連続して延伸しており、従って、ビット線ペアBLpに対応してカラム方向に配列されたMTJ素子は、アクティブエリアAAを共有している。アクティブエリアAAは、ロウ方向において素子分離領域STI(Shallow Trench Isolation)によって分離されている。

【0030】

図5および図6に示すように、本実施形態によるMRAMは、半導体基板としてのシリコン基板10と、シリコン基板10上に形成されたアクティブエリアAAとを備えている。アクティブエリアAA上に形成されたセルトランジスタCTは、ソース層S、ドレイン層Dおよびゲート電極GCを備えている。ゲート電極GCは、ゲート絶縁膜20によってシリコン基板10から絶縁されており、絶縁膜30によってコンタクトプラグCBから絶縁されている。

【0031】

図5に示すように、第1のビット線BL1に沿った断面では、セルトランジスタCTのソース層S上には、コンタクトプラグCBが設けられている。コンタクトプラグCB上には、下部電極LEが設けられており、下部電極LE上にMTJ素子が設けられている。これにより、セルトランジスタCTのソース層Sは、コンタクトプラグCBおよび下部電極LEを介して第1の記憶素子としてのMTJ素子の下端に電気的に接続されている。さらに、MTJ素子上には、上部電極UEが設けられており、上部電極UE上にはビアコンタクトV1が設けられている。ビアコンタクトV1上には第1のビット線BL1が設けられている。これにより、第1の記憶素子としてのMTJ素子の上端は、上部電極UEおよびビアコンタクトV1を介して第1のビット線BL1に接続されている。

【0032】

図6に示すように、第2のビット線BL2に沿った断面では、セルトランジスタCTのドレイン層D上に、コンタクトプラグCBが設けられている。コンタクトプラグCB上には、下部電極LEが設けられており、下部電極LE上にMTJ素子が設けられている。これにより、セルトランジスタCTのドレイン層Dは、コンタクトプラグCBおよび下部電極LEを介して第2の記憶素子としてのMTJ素子の下端に電気的に接続されている。さらに、MTJ素子上には、上部電極UEが設けられており、上部電極UE上にはビアコンタクトV1が設けられている。ビアコンタクトV1上には第2のビット線BL2が設けられている。これにより、第2の記憶素子としてのMTJ素子の上端は、上部電極UEおよびビアコンタクトV1を介して第2のビット線BL2に接続されている。

【0033】

即ち、第1のビット線BL1は、図5に示すように、ビアコンタクトV1およびMTJ素子等を介してセルトランジスタCTのソース層Sに電気的に接続されており、そのセルトランジスタCTのドレイン層Dは、図6に示すように、MTJ素子およびビアコンタクトV1等を介して第2のビット線BL2に接続される。これにより、2つのMTJ素子および1つのセルトランジスタCTが第1のビット線BL1と第2のビット線BL2との間に直列に接続されることになる。換言すると、各セルトランジスタCTの両端は、それぞれMTJ素子を介して第1または第2のビット線BL1,BL2に接続されている。

【0034】

このように、MTJ素子の一端はセルトランジスタCTのソース層Sまたはドレイン層Dに電気的に接続され、MTJ素子の他端は第1または第2のビット線BL1、BL2に接続されている。そして、第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。

【0035】

図4に示すように、ロウ方向の断面では、MTJ素子の下端は、アクティブエリアAAのロウ方向の幅と同じ幅(長さ)を有するコンタクトプラグCBに接続されている。そして、セルトランジスタCTのドレイン層D(またはソース層S)が、コンタクトプラグCBの下に該コンタクトプラグCBに沿って形成されている。これにより、MTJ素子の下端は、セルトランジスタCTのドレイン層D(またはソース層S)に電気的に接続されている。

【0036】

尚、セルトランジスタCTのソース層Sおよびドレイン層Dとの呼称は、便宜的なものであり、電流の流れる方向によってソース層Sとドレイン層Dとの位置関係は逆になることともある。また、セルトランジスタCTのゲート電極GC自体が、ワード線WLとして機能してもよいが、ワード線WLは、ゲート電極GCとは別のレイヤに設けられてもよい。この場合、ゲート電極GCは、コンタクト(図示せず)を介していずれかのワード線WLに電気的に接続される。

【0037】

図3に示すように、第1および第2のビット線BL1、BL2のそれぞれに接続され、かつ、ロウ方向およびカラム方向に対して傾斜する方向に隣接する2つのMTJ素子が1つのセルトランジスタCTを共有している。これらの隣接する2つのMTJ素子は、ワード線WLの両側に設けられている。また、本実施形態では、第1のビット線BL1とアクティブエリアAA(セルトランジスタCTのソース層S)との間の接続、および、第2のビット線BL2とアクティブエリアAA(セルトランジスタCTのドレイン層D)との間の接続の全てに、MTJ素子が介在している。従って、第1のビット線BL1と第2のビット線BL2との間において、2つのMTJ素子および1つのセルトランジスタCTは、MTJ、CT、MTJの順に直列に接続されることになる。データ書込みおよびデータ読出し時における電流は、第1のビット線BL1と第2のビット線BL2との間において、2つのMTJ素子および1つのセルトランジスタCTを介して流れることになる。

【0038】

さらに、各セルトランジスタCTの両端は、それぞれMTJ素子を介して第1または第2のビット線BL1、BL2に接続されている。そして、第1のビット線BL1に接続された1つのMTJ素子(例えば、MTJ1)の両側にある2つのワード線(例えば、WL1およびWL3)は、第2のビット線BL2に接続された2つのMTJ素子(例えば、MTJ0、MTJ3)と隣接する。セルトランジスタCTは、1つのMTJ素子(例えば、MTJ1)と2つのMTJ素子(例えば、MTJ0、MTJ3)との間にそれぞれ設けられている。これにより、データ書込みおよびデータ読出し時において1つの選択MTJ素子に流す電流は、2つのセルトランジスタCTを介して駆動されることになる。

【0039】

尚、本実施形態では、第1のビット線BL1および第2のビット線BL2は、同一の配線層で形成されている。従って、第1および第2のビット線BL1、BL2は、1度のリソグラフィ工程およびエッチング工程によって形成され得る。

【0040】

データ読出し動作またはデータ書込み動作において、第1のビット線BL1に接続された1つの第1のMTJ素子を選択する場合、第2のビット線BL2に接続された複数の第2のMTJ素子を介して第1のMTJ素子へ電流を流す。このとき、1つの第1のMTJ素子がデータ書込みまたはデータ読出しの対象となる選択MTJ素子であり、複数の第2のMTJ素子は非選択MTJ素子である。例えば、図3においてMTJ素子MTJ1に電流を選択的に流す場合、MTJ1の両側にある2本のワード線WL1、WL3を駆動する。これにより、第2のビット線BL2からの電流は、MTJ素子MTJ1に斜め方向に隣接する2つのMTJ素子MTJ0およびMTJ3を介してアクティブエリアAAへ流れ、次に、MTJ0およびMTJ3のそれぞれに接続する2つのセルトランジスタCT1、CT3を介してMTJ素子MTJ1へ流れる。その後、MTJ1を通過した電流は、第1のビット線BL1へ流れる。

【0041】

逆に、第2のビット線BL2に接続された1つの第2のMTJ素子を選択する場合、第1のビット線BL1に接続された複数の第1のMTJ素子を介して第2のMTJ素子へ電流を流す。このとき、1つの第2のMTJ素子がデータ書込みまたはデータ読出しの対象となる選択MTJ素子であり、複数の第1のMTJ素子は非選択MTJ素子である。例えば、図3においてMTJ素子MTJ0に電流を選択的に流す場合、MTJ0の両側にある2本のワード線WL1、WL2を駆動する。これにより、第1のビット線BL1からの電流は、MTJ素子MTJ0に斜め方向に隣接する2つのMTJ素子MTJ1およびMTJ2を介してアクティブエリアAAへ流れ、次に、MTJ1およびMTJ2のそれぞれに接続する2つのセルトランジスタCT1、CT2を介してMTJ素子MTJ0へ流れる。その後、MTJ0を通過した電流は、第2のビット線BL2へ流れる。

【0042】

本実施形態では、いずれのMTJ素子を選択しても、2つの非選択のMTJ素子(通過MTJ素子ともいう)を通過した電流が1つの選択MTJ素子に流れる。2つの非選択のMTJ素子のそれぞれに流れる電流をImtjとすれば、選択MTJ素子に2×Imtjの電流を流すことができる。

【0043】

従って、電流Imtjを流したときにMTJ素子の磁化配列が反転せず、電流2×Imtjを流したときにMTJ素子の磁化配列が反転すれば、選択MTJ素子のみにデータを書き込むことができる。このようなMTJ素子は、通過電流の変化に対する反転確率の増加を急峻にする(即ち、反転確率の増加率を大きくする)ことによって実現できる。これにより、通過電流がImtjである場合に、MTJ素子はディスターブをほとんど受けず、一方で、通過電流が2×Imtjである場合に、MTJ素子の磁化配列は充分に反転することができる。即ち、選択MTJ素子のみにデータを書き込むことができ、そのときに電流が通過する2つの通過MTJ素子にはデータは書き込まれない。

【0044】

データ読出し動作では、そもそも磁化配列が反転しない程度の電流しか選択MTJ素子に流さない。よって、選択MTJ素子に隣接する2つの通過MTJ素子には、その読出し電流の半分の電流しか流れないので、通過MTJ素子ではディスターブをほとんど受けない。

【0045】

しかし、選択MTJ素子の読出し電流は、2つの通過MTJ素子のデータ状態(抵抗値)によって変化することに注意する必要がある。これは、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalが、選択MTJおよび2つの通過MTJ素子の合成抵抗になるからである。

【0046】

図7(A)は、データ読出し時における第1のビット線BL1と第2のビット線BL2との間の等価回路図である。図7(B)は、選択MTJおよび2つの通過MTJ素子の抵抗値の組み合わせと第1のビット線BL1および第2のビット線BL2の間の抵抗値Rtotalとの関係を示す表である。

【0047】

図7(A)に示すように、選択MTJ素子MTJ0および通過MTJ素子MTJ1、MTJ2は、データ読出し時に抵抗として考えることができる。通過MTJ素子MTj1、MTJ2は、選択MTJ素子MTJ0と第1のビット線BL2との間に並列に接続される。尚、セルトランジスタCTは導通状態であり、その抵抗値は、MTJ素子MTJ0〜MTJ2の抵抗値に対して無視できる。

【0048】

図7(B)に示すように本実施形態では、選択MTJ素子のデータだけでなく、通過MTJ素子のデータによって抵抗値(読み出し電流)が変化することが分かる。例えば、P状態のMTJ素子の抵抗値を7Kオームとし、AP状態のMTJ素子の抵抗値を21Kオームとする。

【0049】

この場合、選択MTJ素子MTJ0がP状態(データ“0”)であれば、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalは、2つの通過MTJ素子のデータ状態によって、10.5Kオーム〜17.5Kオームの範囲で変化し得る。選択MTJ素子MTJ0がAP状態(データ“1”)であれば、第1のビット線BL1と第2のビット線BL2との間の抵抗値Rtotalは、2つの通過MTJ素子のデータ状態によって、24.5Kオーム〜31.5Kオームの範囲で変化し得る。

【0050】

従って、選択MTJ素子MTJ0がデータ“0”であるときの抵抗値Rtotalと、選択MTJ素子MTJ0がデータ“1”であるときの抵抗値Rtotalとの間のマージンは、7Kオームになる。この抵抗値Rtotalのマージンは、選択MTJ素子MTJ0のみの抵抗値のマージン(14Kオーム)と比べて小さいが、データの読出し動作においては充分と言える。

【0051】

以上のような構成を有するMRAMのユニットセル(単位メモリセル)UC(図3の破線枠)の面積は、8F2である。ユニットセルUCは、平面レイアウトの一単位を示すパターンであり、このパターンをシリコン基板10の平面内に繰り返すことによってメモリセルアレイMCAの平面レイアウトが形成される。ここで、F(Feature Size)は、リソグラフィ技術およびエッチング技術を用いた最小加工寸法である。このユニットセルUCの面積は、従来のそれ(16F2)の半分である。

【0052】

本実施形態によるMRAMの第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。第1のビット線BL1とアクティブエリアAAとの間の接続、および、第2のビット線BL2とアクティブエリアAAとの間の接続の全てに、MTJ素子が介在する。即ち、第1および第2のビット線BL1、BL2において、ビアコンタクトおよびコンタクトプラグ等のコンタクトだけでアクティブエリアAAに接続されている部分は無い。

【0053】

従って、本実施形態は、MTJ素子の平面レイアウトにおける配置密度を高めることができ、従って、ユニットセル(メモリセル)UCのレイアウト面積を従来よりも小さくすることができる。

【0054】

一方、選択MTJ素子に電流を流すときには、該選択MTJ素子に隣接する複数の通過MTJ素子および2つのセルトランジスタを介して電流が該選択MTJ素子に供給される。従って、反転閾値電流よりも充分に大きな書込み電流を選択MTJ素子に供給することができる。

【0055】

その結果、本実施形態は、ユニットセルのサイズを従来よりも小さくすることができ、かつ、MTJ素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保することができる。

【0056】

(第2の実施形態)

図8は、第2の実施形態によるMRAMのメモリセルアレイMCAの部分的な平面レイアウト図である。図9は、図8の9−9線に沿った断面図である。図10は、図8の10−10線に沿った断面図である。図11は、図8の11−11線に沿った断面図である。尚、図8の5−5線に沿った断面図は、図5に示すものと同様である。

【0057】

第1の実施形態では、第1および第2のビット線BL1、BL2は、同一の配線層で形成されている。これに対し、第2の実施形態では、図9および図10に示すように、第2の実施形態による第1のビット線BL1および第2のビット線BL2は、それぞれ異なる金属配線層M1およびM2で形成されている。また、第1のビット線BL1および第2のビット線BL2は、それぞれカラム方向に異なる位置でMTJ素子を介してセルトランジスタCTのソース層Sまたはドレイン層Dに電気的に接続されている。これにより、ビット線ペアBLpを成す第1のビット線BL1と第2のビット線BL2との間の電気的絶縁状態を維持しつつ、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができる。

【0058】

図9に示すように、第2のビット線BL2は、金属配線層M1よりも上層である金属配線層M2で形成されている。従って、第2のビット線BL2は、図9および図11に示すように、深いビアコンタクトV1を介して上部電極UEに接続されている。図10に示すように、第1のビット線BL1は、金属配線層M2よりも下層である金属配線層M1で形成されている。従って、第1のビット線BL1は、比較的浅いビアコンタクトV1を介して上部電極UEに接続されている。

【0059】

図9に示すように、ビット線ペアBLpにおいて第1のビット線BL1と第2のビット線BL2との間にはスペースが無い。従って、第1のビット線BL1と第2のビット線BL2に接続されているビアコンタクトV1との間の短絡を防止するために、保護絶縁膜40が第1のビット線BL1の側面および上面を被覆するように設けられている。これにより、第2のビット線BL2に接続されているビアコンタクトV1を形成する際に、コンタクトホールは、リソグラフィによるフォトレジストおよび保護絶縁膜40をマスクとしてエッチングすることによって形成され得る。保護絶縁膜40の材料は、層間絶縁膜ILD(Interlayer Dielectric)の材料に対してエッチング速度の遅い材料で形成される。例えば、層間絶縁膜ILDがシリコン酸化膜で形成されている場合、保護絶縁膜40は、シリコン窒化膜で形成されている。第2の実施形態のその他の構成は、第1の実施形態の対応する構成と同様でよい。

【0060】

第2の実施形態によれば、図8に示すように、平面レイアウトにおいて、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができので、ユニットセルUCの面積がさらに小さくなり得る。例えば、図8に示すユニットセルUCの面積は、6F2である。

【0061】

第2の実施形態によるMRAMの動作は、第1の実施形態によるMRAMの動作と同様でよい。

【0062】

第2の実施形態によるMRAMの第1および第2のビット線BL1、BL2は、両方とも同一のアクティブエリアAAに対してMTJ素子を介して接続されている。第1のビット線BL1とアクティブエリアAAとの間の接続、および、第2のビット線BL2とアクティブエリアAAとの間の接続の全てに、MTJ素子が介在する。即ち、第1および第2のビット線BL1、BL2において、ビアコンタクトおよびコンタクトプラグ等のコンタクトだけでアクティブエリアAAに接続されている部分は無い。また、第2の実施形態におけるデータ読出しまたはデータ書込み動作は、第1の実施形態のそれらと同様である。従って、第2の実施形態は、第1の実施形態と同様の効果を得ることができる。

【0063】

さらに、第2の実施形態によれば、第1のビット線BL1と第2のビット線BL2との間のスペースを無くすことができので、ユニットセルUCの面積が第1の実施形態のそれよりも小さくなる。

【0064】

以上から第2の実施形態も、ユニットセルのサイズを従来よりも小さくすることができ、かつ、MTJ素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保することができる。

【0065】

ただし、第2の実施形態では、上層側の第2のビット線BL2に接続されたビアコンタクトV1と下層側の第1のビット線BL1との間の間隔が狭くなるので、保護絶縁膜40を第1のビット線BL1の上面および側面に形成する工程が必要になる。また、第1および第2のビット線BL1、BL2のために2層の金属配線層M1,M2が必要になる。

【0066】

さらに、第2の実施形態では、平面レイアウトにおいて、第2のビット線BL2と第1のビット線BL1との間の間隔が無くなるので、セルトランジスタCTのゲート幅が第1の実施形態におけるセルトランジスタCTのゲート幅よりも狭くなる。しかし、2つのセルトランジスタCTを介して1つの選択MTJ素子に電流を流しているので、第2の実施形態によるMRAMは、反転閾値電流以上の電流を選択MTJ素子に流すことは可能である。

【0067】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0068】

MTJ・・・MTJ素子、CT・・・セルトランジスタ、S・・・ソース層、D・・・ドレイン層、BL1、BL2・・・ビット線、WL・・・ワード線、AA・・・アクティブエリア、STI・・・素子分離領域、V1・・・ビアコンタクト、CB・・・コンタクトプラグ、UE・・・上部電極、LE・・・下部電極、10・・・シリコン基板、20・・・ゲート絶縁膜、40・・・保護絶縁膜

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板に形成されたアクティブエリアと、

前記アクティブエリアに形成された複数のセルトランジスタと、

互いに対をなす第1のビット線および第2のビット線と、

前記第1および前記第2のビット線と交差する複数のワード線と、

一端が前記セルトランジスタのソースまたはドレインに電気的に接続され、他端が前記第1または前記第2のビット線に接続された複数の記憶素子とを備え、

前記第1および前記第2のビット線は、両方とも同一の前記アクティブエリアに対して前記記憶素子を介して接続されていることを特徴とする半導体記憶装置。

【請求項2】

データ読出しまたはデータ書込みにおいて、

前記記憶素子のうち前記第1のビット線に接続された1つの第1の記憶素子を選択する場合、前記記憶素子のうち前記第2のビット線に接続された複数の第2の記憶素子を介して前記第1の記憶素子へ電流を流し、

前記記憶素子のうち前記第2のビット線に接続された1つの第2の記憶素子を選択する場合、前記記憶素子のうち前記第1のビット線に接続された複数の第1の記憶素子を介して前記第2の記憶素子へ電流を流すことを特徴とする請求項1に記載の半導体記憶装置。

【請求項3】

前記第1のビット線と前記アクティブエリアとの間の接続、および、前記第2のビット線と前記アクティブエリアとの間の接続の全てに、前記記憶素子が介在することを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項4】

各前記セルトランジスタの両端は、それぞれ前記記憶素子を介して前記第1または前記第2のビット線に接続されていることを特徴とする請求項1から請求項3のいずれかに記載の半導体記憶装置。

【請求項5】

前記第1のビット線に接続された1つの第1の記憶素子の両側にある2つの前記ワード線は、前記第2のビット線に接続された2つの第2の記憶素子と隣接し、

2つの前記セルトランジスタは、1つの前記第1の記憶素子と2つの前記第2の記憶素子との間にそれぞれ設けられていることを特徴とする請求項1から請求項4に記載の半導体記憶装置。

【請求項6】

同一の前記アクティブエリアに共通に接続された前記記憶素子が各前記ワード線の両側に設けられていることを特徴とする請求項1から請求項5のいずれかに記載の半導体記憶装置。

【請求項7】

前記記憶素子のうち第1の記憶素子の一端が前記第1のビット線に接続されており、

前記第1の記憶素子の他端が前記セルトランジスタのソースおよびドレインの一方に接続されており、

前記記憶素子のうち第2の記憶素子の一端が該セルトランジスタのソースおよびドレインの他方に接続されており、

前記第2の記憶素子の他端が前記第2のビット線に接続されていることを特徴とする請求項1から請求項6のいずれかに記載の半導体記憶装置。

【請求項8】

前記第1および前記第2のビット線は、同じ配線層で形成されていることを特徴とする請求項1に記載の半導体記憶装置。

【請求項9】

前記第1および前記第2のビット線は、異なる配線層で形成されていることを特徴とする請求項1から請求項7のいずれかに記載の半導体記憶装置。

【請求項10】

前記記憶素子は、磁気トンネル接合素子であることを特徴とする請求項1から請求項9のいずれかに記載の半導体記憶装置。

【請求項1】

半導体基板と、

前記半導体基板に形成されたアクティブエリアと、

前記アクティブエリアに形成された複数のセルトランジスタと、

互いに対をなす第1のビット線および第2のビット線と、

前記第1および前記第2のビット線と交差する複数のワード線と、

一端が前記セルトランジスタのソースまたはドレインに電気的に接続され、他端が前記第1または前記第2のビット線に接続された複数の記憶素子とを備え、

前記第1および前記第2のビット線は、両方とも同一の前記アクティブエリアに対して前記記憶素子を介して接続されていることを特徴とする半導体記憶装置。

【請求項2】

データ読出しまたはデータ書込みにおいて、

前記記憶素子のうち前記第1のビット線に接続された1つの第1の記憶素子を選択する場合、前記記憶素子のうち前記第2のビット線に接続された複数の第2の記憶素子を介して前記第1の記憶素子へ電流を流し、

前記記憶素子のうち前記第2のビット線に接続された1つの第2の記憶素子を選択する場合、前記記憶素子のうち前記第1のビット線に接続された複数の第1の記憶素子を介して前記第2の記憶素子へ電流を流すことを特徴とする請求項1に記載の半導体記憶装置。

【請求項3】

前記第1のビット線と前記アクティブエリアとの間の接続、および、前記第2のビット線と前記アクティブエリアとの間の接続の全てに、前記記憶素子が介在することを特徴とする請求項1または請求項2に記載の半導体記憶装置。

【請求項4】

各前記セルトランジスタの両端は、それぞれ前記記憶素子を介して前記第1または前記第2のビット線に接続されていることを特徴とする請求項1から請求項3のいずれかに記載の半導体記憶装置。

【請求項5】

前記第1のビット線に接続された1つの第1の記憶素子の両側にある2つの前記ワード線は、前記第2のビット線に接続された2つの第2の記憶素子と隣接し、

2つの前記セルトランジスタは、1つの前記第1の記憶素子と2つの前記第2の記憶素子との間にそれぞれ設けられていることを特徴とする請求項1から請求項4に記載の半導体記憶装置。

【請求項6】

同一の前記アクティブエリアに共通に接続された前記記憶素子が各前記ワード線の両側に設けられていることを特徴とする請求項1から請求項5のいずれかに記載の半導体記憶装置。

【請求項7】

前記記憶素子のうち第1の記憶素子の一端が前記第1のビット線に接続されており、

前記第1の記憶素子の他端が前記セルトランジスタのソースおよびドレインの一方に接続されており、

前記記憶素子のうち第2の記憶素子の一端が該セルトランジスタのソースおよびドレインの他方に接続されており、

前記第2の記憶素子の他端が前記第2のビット線に接続されていることを特徴とする請求項1から請求項6のいずれかに記載の半導体記憶装置。

【請求項8】

前記第1および前記第2のビット線は、同じ配線層で形成されていることを特徴とする請求項1に記載の半導体記憶装置。

【請求項9】

前記第1および前記第2のビット線は、異なる配線層で形成されていることを特徴とする請求項1から請求項7のいずれかに記載の半導体記憶装置。

【請求項10】

前記記憶素子は、磁気トンネル接合素子であることを特徴とする請求項1から請求項9のいずれかに記載の半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−256693(P2012−256693A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2011−128442(P2011−128442)

【出願日】平成23年6月8日(2011.6.8)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願日】平成23年6月8日(2011.6.8)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]