半導体記憶装置

【課題】専用のテスト端子を設けずにパッケージング後のテストを実施可能とする。

【解決手段】半導体記憶装置1は、メモリバンク11と、メモリバンク21と、メモリバンク11用のコントローラ12と、メモリバンク21用のコントローラ22と、を有し、コントローラ12は、メモリバンク11のテストモード時に、メモリバンク11用のテスト端子としてメモリバンク21用の外部端子SCL2を流用し、コントローラ22は、メモリバンク21のテストモード時に、メモリバンク21用のテスト端子としてメモリバンク11用の外部端子SCL1を流用する。

【解決手段】半導体記憶装置1は、メモリバンク11と、メモリバンク21と、メモリバンク11用のコントローラ12と、メモリバンク21用のコントローラ22と、を有し、コントローラ12は、メモリバンク11のテストモード時に、メモリバンク11用のテスト端子としてメモリバンク21用の外部端子SCL2を流用し、コントローラ22は、メモリバンク21のテストモード時に、メモリバンク21用のテスト端子としてメモリバンク11用の外部端子SCL1を流用する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体記憶装置に関するものである。

【背景技術】

【0002】

従来より、複数のメモリバンクを有するマルチポート型の半導体記憶装置(例えばデュアルポートEEPROM[electrically erasable programmable read only memory])が提案されている。

【0003】

なお、上記に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−262698号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記従来の半導体記憶装置では、パッケージサイズを縮小するために、外部端子数の削減が強く求められており、通常動作時に必須でないテスト端子を設ける余地は殆どなかった。そのため、半導体記憶装置に任意の外部電圧を印加する必要のあるテスト(例えばメモリセルのスレッショルド電圧を測定するためのアナログ特性テスト)については、ウェハレベルでのプローブテストとして実施せざるを得なかった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、専用のテスト端子を設けることなく、パッケージング後に所望のテストを実施することが可能なマルチポート型の半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体記憶装置は、第1メモリバンクと、第2メモリバンクと、第1メモリバンク用の第1コントローラと、第2メモリバンク用の第2コントローラと、を有し、前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1メモリバンク用の第1テスト端子として前記第2メモリバンク用の外部端子を流用し、前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2メモリバンク用の第2テスト端子として前記第1メモリバンク用の外部端子を流用する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成る半導体記憶装置において、前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1テスト端子から前記第1メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第1テスト端子の接続先を切り替え、前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2テスト端子から前記第2メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第2テスト端子の接続先を切り替える構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成る半導体記憶装置において、前記第1コントローラは、所定の外部端子に通常時と異なるトリガ電圧が印加されている状態で、前記第1メモリバンク用の第1信号端子に特定コマンドが入力されたときに、前記第1メモリバンクのテストモードに移行し、前記第2コントローラは、前記所定の外部端子に前記トリガ電圧が印加されている状態で、前記第2メモリバンク用の第2信号端子に前記特定コマンドが入力されたときに、前記第2メモリバンクのテストモードに移行する構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成る半導体記憶装置において、前記第1信号端子と前記第2信号端子は互いにパッケージの対辺に設けられている構成(第4の構成)にするとよい。

【0011】

また、本発明に係る表示装置は、識別データを格納する第1メモリバンクとタイミング制御データを格納する第2メモリバンクを有する上記第4の構成から成る半導体記憶装置と、表示データに基づいて映像を表示する表示部と、前記第2メモリバンクから前記タイミング制御データを読み出して前記表示部のタイミング制御を行うタイミングコントローラと、を有する構成(第5の構成)とされている。

【0012】

また、本発明に係る表示データ生成装置は、上記第5の構成から成る表示装置に表示データを出力する表示データ出力部と、前記表示装置に設けられた半導体記憶装置の第1メモリバンクから識別データを読み出して前記表示データ出力部を制御するマイコンと、を有する構成(第6の構成)とされている。

【0013】

また、本発明に係る表示システムは、上記第5の構成から成る表示装置と、上記第6の構成から成る表示データ生成装置と、を有する構成(第7の構成)とされている。

【0014】

また、本発明に係る電子機器は、上記第1〜第4いずれかの構成から成る半導体記憶装置を有する構成(第8の構成)とされている。

【発明の効果】

【0015】

本発明によれば、専用のテスト端子を設けることなく、パッケージング後に所望のテストを実施することが可能なマルチポート型の半導体記憶装置を提供することができる。

【図面の簡単な説明】

【0016】

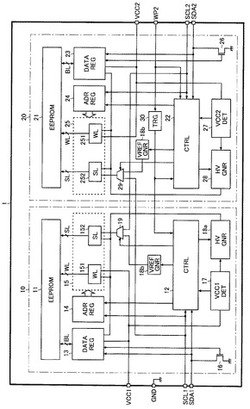

【図1】半導体記憶装置の一構成例を示すブロック図

【図2】I2Cシリアルデータ通信の概要を示すタイミングチャート

【図3】メモリバンクの一構成例を示す回路図

【図4】メモリセルの縦構造を示す垂直断面図

【図5】スレッショルド電圧Vthの分布状態図

【図6】半導体記憶装置を用いたアプリケーションの一例を示すブロック図

【発明を実施するための形態】

【0017】

<半導体記憶装置>

図1は、半導体記憶装置の一構成例を示すブロック図である。本構成例の半導体記憶装置1は、互いに独立して形成された2ポート分のメモリ回路10及び20を有するデュアルポートEEPROMである。

【0018】

なお、半導体記憶装置1は、外部との電気的接続を確立する手段として、8本の外部端子(電源端子VCC1及びVCC2、クロック端子SCL1及びSCL2、データ端子SDA1及びSDA2、接地端子GND、及び、ライトプロテクト端子WP2)を有する。電源端子VCC1、クロック端子SCL1、及び、データ端子SDA1は、基本的にメモリ回路10の専用端子であり、電源端子VCC2、クロック端子SCL2、データ端子SDA2、及び、ライトプロテクト端子WP2は、基本的にメモリ回路20の専用端子である。一方、接地端子GNDは、メモリ回路10及び20の共用端子である。

【0019】

このように、2ポート分のメモリ回路10及び20を互いに独立して形成することにより、メモリ回路10及び20の動作状態を個別に制御することができる。例えば、電源端子VCC1及びVCC2の一方に電源電圧Vccを供給し、他方を接地状態またはオープン状態とすれば、電源電圧Vccが供給された方のメモリ回路のみを動作させることが可能となる。もちろん、電源端子VCC1及びVCC2の双方に電源電圧Vccを供給すれば、メモリ回路10及び20をいずれも動作させることが可能であり、逆に、電源端子VCC1及びVCC2の双方を接地状態またはオープン状態とすれば、メモリ回路10及び20をいずれも停止させることが可能である。

【0020】

なお、メモリ回路10用の信号端子(クロック端子SCL1及びデータ端子SDA1)と、メモリ回路20用の信号端子(クロック端子SCL2及びデータ端子SDA2)は、互いにパッケージの対辺に設けることが望ましい。このようなピン配置を採用することにより、信号線の誤接続や不要な引き回しをできる限り低減することが可能となる。

【0021】

メモリ回路10は、メモリバンク11と、メモリコントローラ12と、データレジスタ13と、アドレスレジスタ14と、アドレスデコーダ15と、オープンドレイン出力部16と、電源電圧検出部17と、高電圧生成部18aと、内部参照電圧生成部18bと、セレクタ19と、を有する。

【0022】

メモリバンク11は、メモリコントローラ12によって制御されるメモリセルの集合体(例えば2kビット)である。

【0023】

メモリコントローラ12は、クロック端子SCL1とデータ端子SDA1を用いて装置外部のマスタ(不図示)と2線式のI2Cシリアルデータ通信を行い、マスタから与えられる各種コマンドに応じてメモリバンク11のリード/ライト制御などを行う。図2は、I2Cシリアルデータ通信の概要を示すタイミングチャートである。I2Cシリアルデータ通信は、スタートコンディション(S)の入力によって開始され、ストップコンディション(P)の入力によって終了される。データ(DATA)は常に8ビット長であり、1バイト分(8ビット長)のデータ転送毎にアクノリッジ(ACK)が要求される。なお、スタートコンディション(S)の入力直後には、7ビット長のスレーブアドレス(ADDRESS)と1ビット長のリード/ライトフラグ(R/W)が入力される。

【0024】

データレジスタ13は、メモリバンク11のリードデータやライトデータを一時的に格納する。ビットラインBLを介してメモリバンク11のメモリセルから読み出されたリードデータは、データレジスタ13に一時格納された後、オープンドレイン出力部16を介してデータ端子SDA1に出力される。一方、データ端子SDA1から入力されたライトデータは、データレジスタ13に一時格納された後、ビットラインBLを介してメモリバンク11のメモリセルに書き込まれる。

【0025】

アドレスレジスタ14は、メモリコントローラ12の指示に基づいて、データ端子SDA1から入力されたメモリバンク11のアドレスデータを一時的に格納する。

【0026】

アドレスデコーダ15は、メモリコントローラ12の指示に基づいて、アドレスレジスタ14に一時格納されたアドレスデータを読み出し、メモリバンク11のワードラインWLとセンスラインSLを各々駆動する。アドレスデコーダ15に含まれるワードライン駆動部151には、電源電圧Vccと高電圧HVが供給されている。また、アドレスデコーダ15に含まれるセンスライン駆動部152には、内部参照電圧VREFと高電圧HVが供給されている。ただし、メモリバンク11のテストモード時において、センスライン駆動部152には、内部参照電圧VREFに代えて任意のテスト電圧(外部参照電圧)Vrefが供給される。これについては、後ほど詳細に説明する。

【0027】

オープンドレイン出力部16は、データレジスタ13の出力に応じてオン/オフされるNチャネル型MOS[metal oxide semiconductor]電界効果トランジスタである。データレジスタ13の出力がハイレベルである場合、NMOSFETがオンとなり、データ端子SDA1がローレベルとなる。一方、データレジスタ13の出力がローレベルである場合、NMOSFETがオフとなり、データ端子SDA1がハイレベルとなる。

【0028】

電源電圧検出部17は、電源端子VCC1に印加される電源電圧Vccが所定の閾値電圧よりも高いか否かを検出し、その検出結果をメモリコントローラ12に出力する。この検出結果を受けたメモリコントローラ12は、例えば、電源電圧Vccが閾値電圧よりも低いときにメモリバンク11への書き込み動作を禁止する。このような構成とすることにより、減電時におけるメモリバンク11への誤書き込みを防止することができる。

【0029】

高電圧生成部18aは、メモリコントローラ12の指示に基づいて、電源電圧Vccから高電圧HV(>Vcc)を生成する。高電圧生成部18aとしては、チャージポンプ回路などを用いることができる。高電圧生成部18aは、メモリバンク11への書き込み動作時にのみ駆動される。

【0030】

内部参照電圧生成部18bは、メモリコントローラ12の指示に基づいて、電源電圧Vccから内部参照電圧VREF(例えば0.8V)を生成する。内部参照電圧生成部18bは、メモリバンク11の読み出し動作時にのみ駆動される。

【0031】

セレクタ19は、メモリコントローラ12の指示に基づいて、メモリバンク11の通常モード時には、内部参照電圧VREFをセンスライン駆動部152に供給する一方、メモリバンク11のテストモード時には、メモリバンク11用のテスト端子(クロック端子SCL2またはデータ端子SDA2を流用)に印加されるテスト電圧(外部参照電圧)Vrefをセンスライン駆動部152に供給するように、センスライン駆動部152への電圧供給経路を切り替える。

【0032】

メモリ回路20は、基本的にメモリ回路10と同一の構成から成り、メモリバンク21と、メモリコントローラ22と、データレジスタ23と、アドレスレジスタ24と、アドレスデコーダ25と、オープンドレイン出力部26と、電源電圧検出部27と、高電圧生成部28aと、内部参照電圧生成部28bと、セレクタ29とを有する。メモリ回路20を形成する構成要素21〜29の動作は、基本的にメモリ回路10を形成する構成要素11〜19の動作と同一であり、構成要素11〜19の動作を各々説明する中で用いた符号のうち、「11」〜「19」、「151」〜「152」、「VCC1」、「SCL1」、「SDA1」、「SCL2」、及び、「SDA2」を、それぞれ、「21」〜「29」、「251」〜「252」、「VCC2」、「SCL2」、「SDA2」、「SCL1」、及び、「SDA1」と読み替えれば足りるので、ここでは冗長的な説明を割愛する。

【0033】

ただし、メモリコントローラ22は、ライトプロテクト端子WP2に入力されるライトプロテクト信号に応じて、メモリバンク21への書き込み動作を許可/禁止する、というメモリコントローラ12にはない特有の機能を備えている。例えば、ライトプロテクト信号がハイレベル(Vcc)であるときには、メモリバンク21への書き込み動作が禁止され、ライトプロテクト信号がローレベル(GND)であるときには、メモリバンク21への書き込み動作が許可される。このようなライトプロテクト機能を備えた構成であれば、メモリバンク21への誤書込みを防止することができる。

【0034】

また、半導体記憶装置1には、メモリ回路10及び20のほかに、トリガ電圧検出部30が集積化されている。トリガ電圧検出部30は、ライトプロテクト端子WP2に通常時と異なるトリガ電圧TRG(ライトプロテクト信号のハイレベル(Vcc)よりも高い高電圧(例えば2×Vcc))が印加されているか否かを検出し、その検出結果をメモリコントローラ12及び22に送出する。メモリコントローラ12及び22は、トリガ電圧検出部30の検出結果をテストモードへの移行トリガとして用いる。このような構成とすることにより、ライトプロテクト端子WP2に本来の機能とは異なる機能(テストイネーブル端子としての機能)を付加することができるので、外部端子数の削減を図ることが可能となる。なお、半導体記憶装置1のテストモードについては、後ほど詳細に説明する。

【0035】

<メモリバンク>

次に、メモリバンク11(メモリバンク21についても同様)の内部構成について、詳細な説明を行う。図3は、メモリバンク11の一構成例を示す回路図である。図3に示すように、メモリバンク11には、ワードラインWL、センスラインSL、ビットラインBL、及び、共通ソースラインASGが張り巡らされており、これらの制御ラインには、メモリセルトランジスタMTと選択用トランジスタSTから成るメモリセルCELLが複数接続されている。

【0036】

1バイト分のメモリセルCELL1〜CELL8に着目して接続関係を説明する。選択用トランジスタST1〜ST8のドレインは、それぞれビットラインBL1〜BL8に接続されている。選択用トランジスタST1〜ST8のソースは、それぞれメモリセルトランジスタMT1〜MT8のドレインに接続されている。選択用トランジスタST1〜ST8のゲートは、いずれもワードラインWL1に接続されている。メモリセルトランジスタMT1〜MT8のソースは、いずれも共通ソースラインASGに接続されている。共通ソースラインASGは、イネーブルトランジスタETを介して接地端に接続されている。メモリセルトランジスタMT1〜MT8のゲート(コントロールラインCLに相当)は、いずれもバイト選択トランジスタBT1を介してセンスラインSL1に接続されている。バイト選択トランジスタBT1のゲートは、ワードラインWL1に接続されている。

【0037】

図4は、メモリセルCELLの縦構造を示す垂直断面図である。先述した通り、メモリセルCELLは、選択用トランジスタSTとメモリセルトランジスタMTを有する。

【0038】

メモリセルトランジスタMTは、そのドレインDMとソースSMに挟まれたシリコン基板内の伝導チャネルとコントロールゲートCGとの間に、フローティングゲート(周囲と絶縁されたゲート)FGを有する構造とされており、コントロールゲートCGからみたメモリセルトランジスタMTのスレッショルド電圧VthがフローティングゲートFGに蓄積されている電荷量に応じて変化することを利用して、データの記憶が行われる。

【0039】

なお、メモリセルトランジスタMTのフローティングゲートFGとドレインDMに挟まれた絶縁体は、その一部が薄くなっており、この部分(トンネル絶縁膜)を介するトンネル効果によって、フローティングゲートFGに対する電子の注入及び放出が行われる。

【0040】

そして、メモリセルトランジスタMTのフローティングゲートFGに蓄積される電荷量を制御することにより、図5で示すように、メモリセルトランジスタMTのスレッショルド電圧Vthを2つの状態に分布させ、この2つの分布にそれぞれ「0」と「1」を対応させることにより、1つのメモリセルCELLに1ビットのデータが記憶される。

【0041】

上記構成から成るメモリセルCELL1にデータ「1」を書き込む場合には、ワードラインWL1とセンスラインSL1(コントロールラインCL1)に高電圧HVが印加されて、ビットラインBL1と共通ソースラインASGに接地電圧が印加される。このとき、選択用トランジスタSTはオンとなり、メモリセルトランジスタMTのトンネル絶縁膜には高電圧HVが印加される。従って、フローティングゲートFGに電子が注入されて、フローティングゲートFGが電子を蓄積した状態となる。このとき、メモリセルトランジスタMTのスレッショルド電圧Vthは、図5の読出電圧VRD(例えば内部参照電圧VREF)よりも高くなる。この状態は、メモリセルCELL1にデータ「1」が書き込まれた状態に相当する。

【0042】

一方、メモリセルCELL1にデータ「0」を書き込む場合(すなわちデータ「1」を消去する場合)には、ワードラインWL1とビットラインBL1に高電圧HVが印加されて、センスラインSL1(コントロールラインCL1)に接地電圧が印加されて、共通ソースラインASGがオープン状態とされる。このとき、選択用トランジスタSTはオンとなり、メモリセルトランジスタMTのトンネル絶縁膜には高電圧HVが印加される。従って、フローティングゲートFGから電子が放出されて、フローティングゲートFGは電子が欠乏した状態となる。このとき、メモリセルトランジスタMTのスレッショルド電圧Vthは、図5の読出電圧VRD(例えば内部参照電圧VREF)よりも低くなる。この状態は、データ「0」が書き込まれた状態(データ「1」が消去された状態)に相当する。

【0043】

なお、メモリセルCELL1からデータを読み出す際には、センスラインSL1(コントロールラインCL1)に読出電圧VRD(例えば内部参照電圧VREF)を印加し、ワードラインWL1に電源電圧Vccを印加し、共通ソースラインASGに接地電圧を印加した状態で、ハイインピーダンスとされたビットラインBL1に電流が流れるか否かを判定すればよい。ビットラインBL1に電流が流れなければ、メモリセルトランジスタMTのスレッショルド電圧Vthが読出電圧VRDよりも高い状態(すなわち、データ「1」が書き込まれた状態)であると判定することができる。一方、ビットラインBL1に電流が流れれば、メモリセルトランジスタMTのスレッショルド電圧Vthが読出電圧VRDよりも低い状態(すなわち、データ「0」が書き込まれた状態)であると判定することができる。

【0044】

<テストモード>

次に、半導体記憶装置1のテストモードについて説明する。コントローラ12は、ライトプロテクト端子WP2にトリガ電圧TRG(例えば2×Vcc)が印加されている状態で、データ端子SDA1にテストモード移行コマンドが入力されたときに、メモリバンク11のテストモードに移行し、メモリバンク11用のテスト端子としてメモリバンク21用のクロック端子SCL2を流用する。より具体的に述べると、コントローラ12は、メモリバンク11のテストモード時に、クロック端子SCL2からメモリバンク11のメモリセルトランジスタに任意のゲート電圧(テスト電圧(外部参照電圧)Vref)が印加されるように、セレクタ19の切替制御を行う。

【0045】

上記と同様に、コントローラ22は、ライトプロテクト端子WP2にトリガ電圧TRGが印加されている状態で、データ端子SDA2にテストモード移行コマンドが入力されたときに、メモリバンク21のテストモードに移行し、メモリバンク21用のテスト端子としてメモリバンク11用のクロック端子SCL1を流用する。より具体的に述べると、コントローラ22は、メモリバンク21のテストモード時に、クロック端子SCL1からメモリバンク21のメモリセルトランジスタに任意のゲート電圧(テスト電圧(外部参照電圧)Vref)が印加されるように、セレクタ29の切替制御を行う。

【0046】

例えば、メモリセルCELL1(図3を参照)からデータを読み出す際、読出電圧VRDとしてセンスラインSL1に印加されるテスト電圧(外部参照電圧)Vrefを連続的または段階的に変化させていくことにより、メモリセルCELL1のスレッショルド電圧Vthを測定することができる。先出の図5で示したように、メモリセルCELLのスレッショルド電圧Vthは、ある程度のばらつきを持って分布している。従って、半導体記憶装置1の出荷時にスレッショルド電圧Vthを測定し、既定の読出電圧VRD(例えば内部参照電圧VREF)に対するマージンを確認しておくことは、製品の信頼性を高める上で非常に重要である。

【0047】

このように、本願の発明者らは、デュアルポートEEPROMの出荷検査時に2ポート分のメモリバンク同時に動作させる必要がないという点に着目し、鋭意研究の末、一方のメモリバンクをテストモードで動作させている際には、他方のメモリバンクを非動作状態とした上で、一方のメモリバンク用のテスト端子として他方のメモリバンク用の外部端子を流用するという着想を得て、上記構成から成る半導体記憶装置1を創作するに至った。

【0048】

上記構成から成る半導体記憶装置1であれば、専用のテスト端子を設けることなく、パッケージング後に所望のテスト(例えばメモリセルのスレッショルド電圧を測定するためのアナログ特性テスト)を実施することができるので、パッケージの大型化を招くことなく、製品の信頼性を高めることが可能となる。

【0049】

<アプリケーション>

図6は、半導体記憶装置を用いたアプリケーションの一例を示すブロック図である。本構成例の表示システムZは、表示装置Xと表示データ生成装置Yを有する。

【0050】

表示装置Xは、半導体記憶装置X1と、表示部X2と、タイミングコントローラX3とを有する。半導体記憶装置X1は、拡張ディスプレイ識別データd1(いわゆるEDID[extended display identification data])を格納する第1メモリバンクと、タイミング制御データd2を格納する第2メモリバンクを有する。半導体記憶装置X1としては、先述の半導体記憶装置1を好適に用いることができる。表示部X2は、表示データ生成装置Yから入力される表示データd3に基づいて映像を表示する。表示部X2としては、液晶ディスプレイ、プラズマディスプレイ、有機ELディスプレイなどを用いることができる。タイミングコントローラX3は、半導体記憶装置1の第2メモリバンクからタイミング制御データd2を読み出して表示部X2のタイミング制御を行う。

【0051】

表示データ生成装置Yは、表示データ出力部Y1とマイコンY2を有する。表示データ出力部Y1は、表示装置Xに表示データd3を出力する。マイコンY2は、表示装置Xに設けられた半導体記憶装置X1の第1メモリバンクから拡張ディスプレイ識別データd1を読み出して表示データ出力部Y1の出力制御(出力解像度の最適化など)を行う。

【0052】

表示システムZは、表示装置Xと表示データ生成装置Yを内蔵した一つの電子機器(ノート型パソコン、携帯電話、及び、タブレット端末など)として構築することができる。この場合、表示装置Xは、表示パネルなどを備えた表示モジュールに相当し、表示データ生成装置Yは、携帯機器の本体モジュールに相当する。また、表示システムZは、各々独立した表示装置Xと表示データ生成装置Yによって構築することもできる。この場合、表示装置Xは、テレビやモニタなどに相当し、表示データ生成装置Yは、光ディスク再生機器などに相当する。

【0053】

上記したように、同一の表示システムZ内に複数のメモリを必要とするアプリケーションにおいて、デュアルポートEEPROMを用いる構成であれば、シングルポートEEPROMを複数用いるよりも、マザーボード上における占有面積を削減して、システムの小型化に貢献することが可能となる。また、部品点数の削減によるシステムの信頼性向上を図ることも可能となる。さらに、EEPROMの1パッケージ化によるパッケージコスト削減効果も享受することが可能となる。

【0054】

<その他の変形例>

なお、上記の実施形態では、テレビやモニタなどの表示装置に搭載されたデュアルポートEEPROMに本発明を適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、複数のメモリバンクを有するマルチポート型の半導体記憶装置及びこれを用いた電子機器全般について、その用途を問わず、広く一般的に適用することが可能である。また、テストの内容もメモリセルのアナログ特性テストに限定されるものではない。

【0055】

また、複数のメモリバンクに各々アクセスするためのポートは、同種の規格(例えば、I2C)に準拠したものであってもよいし、或いは、異種の規格(例えば、I2C、SPI[Serial Peripheral Interface]、及び、マイクロワイヤ)に準拠したものであってもよい。また、複数のメモリバンクは、同一の容量を有するものであってもよいし、異なる容量を有するものであってもよい。また、ポート数(メモリバンクの搭載数)は3つ以上でもよい。また、半導体記憶装置は、シングルチップパッケージとしてもよいし、マルチチップパッケージとしてもよい。

【0056】

このように、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0057】

本発明に係る半導体記憶装置は、例えば、同一のシステム内に複数のメモリを必要とするアプリケーション全般で利用することが可能である。

【符号の説明】

【0058】

1 半導体記憶装置

10、20 メモリ回路

11、21 メモリバンク

12、22 メモリコントローラ

13、23 データレジスタ

14、24 アドレスレジスタ

15、25 アドレスデコーダ

151、251 ワードライン駆動部

152、252 センスライン駆動部

16、26 オープンドレイン出力部(NMOSFET)

17、27 電源電圧検出部

18a、28a 高電圧生成部

18b、28b 内部参照電圧生成部

19、29 セレクタ

30 トリガ電圧検出部

VCC1、VCC2 電源端子

SCL1、SCL2 クロック端子(テスト端子としても流用)

SDA1、SDA2 データ端子

GND 接地端子

WP2 ライトプロテクト端子

WL ワードライン

CL コントロールライン

SL センスライン

BL ビットライン

ASG 共通ソースライン

CELL メモリセル

ST 選択用トランジスタ

DS ドレイン

SS ソース

G ゲート

MT メモリセルトランジスタ

DM ドレイン

SM ソース

CG コントロールゲート

FG フローティングゲート

X 表示装置

X1 半導体記憶装置

X2 表示部

X3 タイミングコントローラ

Y 表示データ生成装置

Y1 表示データ出力部

Y2 マイコン

Z 表示システム

【技術分野】

【0001】

本発明は、半導体記憶装置に関するものである。

【背景技術】

【0002】

従来より、複数のメモリバンクを有するマルチポート型の半導体記憶装置(例えばデュアルポートEEPROM[electrically erasable programmable read only memory])が提案されている。

【0003】

なお、上記に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−262698号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記従来の半導体記憶装置では、パッケージサイズを縮小するために、外部端子数の削減が強く求められており、通常動作時に必須でないテスト端子を設ける余地は殆どなかった。そのため、半導体記憶装置に任意の外部電圧を印加する必要のあるテスト(例えばメモリセルのスレッショルド電圧を測定するためのアナログ特性テスト)については、ウェハレベルでのプローブテストとして実施せざるを得なかった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、専用のテスト端子を設けることなく、パッケージング後に所望のテストを実施することが可能なマルチポート型の半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体記憶装置は、第1メモリバンクと、第2メモリバンクと、第1メモリバンク用の第1コントローラと、第2メモリバンク用の第2コントローラと、を有し、前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1メモリバンク用の第1テスト端子として前記第2メモリバンク用の外部端子を流用し、前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2メモリバンク用の第2テスト端子として前記第1メモリバンク用の外部端子を流用する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成る半導体記憶装置において、前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1テスト端子から前記第1メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第1テスト端子の接続先を切り替え、前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2テスト端子から前記第2メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第2テスト端子の接続先を切り替える構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成る半導体記憶装置において、前記第1コントローラは、所定の外部端子に通常時と異なるトリガ電圧が印加されている状態で、前記第1メモリバンク用の第1信号端子に特定コマンドが入力されたときに、前記第1メモリバンクのテストモードに移行し、前記第2コントローラは、前記所定の外部端子に前記トリガ電圧が印加されている状態で、前記第2メモリバンク用の第2信号端子に前記特定コマンドが入力されたときに、前記第2メモリバンクのテストモードに移行する構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成る半導体記憶装置において、前記第1信号端子と前記第2信号端子は互いにパッケージの対辺に設けられている構成(第4の構成)にするとよい。

【0011】

また、本発明に係る表示装置は、識別データを格納する第1メモリバンクとタイミング制御データを格納する第2メモリバンクを有する上記第4の構成から成る半導体記憶装置と、表示データに基づいて映像を表示する表示部と、前記第2メモリバンクから前記タイミング制御データを読み出して前記表示部のタイミング制御を行うタイミングコントローラと、を有する構成(第5の構成)とされている。

【0012】

また、本発明に係る表示データ生成装置は、上記第5の構成から成る表示装置に表示データを出力する表示データ出力部と、前記表示装置に設けられた半導体記憶装置の第1メモリバンクから識別データを読み出して前記表示データ出力部を制御するマイコンと、を有する構成(第6の構成)とされている。

【0013】

また、本発明に係る表示システムは、上記第5の構成から成る表示装置と、上記第6の構成から成る表示データ生成装置と、を有する構成(第7の構成)とされている。

【0014】

また、本発明に係る電子機器は、上記第1〜第4いずれかの構成から成る半導体記憶装置を有する構成(第8の構成)とされている。

【発明の効果】

【0015】

本発明によれば、専用のテスト端子を設けることなく、パッケージング後に所望のテストを実施することが可能なマルチポート型の半導体記憶装置を提供することができる。

【図面の簡単な説明】

【0016】

【図1】半導体記憶装置の一構成例を示すブロック図

【図2】I2Cシリアルデータ通信の概要を示すタイミングチャート

【図3】メモリバンクの一構成例を示す回路図

【図4】メモリセルの縦構造を示す垂直断面図

【図5】スレッショルド電圧Vthの分布状態図

【図6】半導体記憶装置を用いたアプリケーションの一例を示すブロック図

【発明を実施するための形態】

【0017】

<半導体記憶装置>

図1は、半導体記憶装置の一構成例を示すブロック図である。本構成例の半導体記憶装置1は、互いに独立して形成された2ポート分のメモリ回路10及び20を有するデュアルポートEEPROMである。

【0018】

なお、半導体記憶装置1は、外部との電気的接続を確立する手段として、8本の外部端子(電源端子VCC1及びVCC2、クロック端子SCL1及びSCL2、データ端子SDA1及びSDA2、接地端子GND、及び、ライトプロテクト端子WP2)を有する。電源端子VCC1、クロック端子SCL1、及び、データ端子SDA1は、基本的にメモリ回路10の専用端子であり、電源端子VCC2、クロック端子SCL2、データ端子SDA2、及び、ライトプロテクト端子WP2は、基本的にメモリ回路20の専用端子である。一方、接地端子GNDは、メモリ回路10及び20の共用端子である。

【0019】

このように、2ポート分のメモリ回路10及び20を互いに独立して形成することにより、メモリ回路10及び20の動作状態を個別に制御することができる。例えば、電源端子VCC1及びVCC2の一方に電源電圧Vccを供給し、他方を接地状態またはオープン状態とすれば、電源電圧Vccが供給された方のメモリ回路のみを動作させることが可能となる。もちろん、電源端子VCC1及びVCC2の双方に電源電圧Vccを供給すれば、メモリ回路10及び20をいずれも動作させることが可能であり、逆に、電源端子VCC1及びVCC2の双方を接地状態またはオープン状態とすれば、メモリ回路10及び20をいずれも停止させることが可能である。

【0020】

なお、メモリ回路10用の信号端子(クロック端子SCL1及びデータ端子SDA1)と、メモリ回路20用の信号端子(クロック端子SCL2及びデータ端子SDA2)は、互いにパッケージの対辺に設けることが望ましい。このようなピン配置を採用することにより、信号線の誤接続や不要な引き回しをできる限り低減することが可能となる。

【0021】

メモリ回路10は、メモリバンク11と、メモリコントローラ12と、データレジスタ13と、アドレスレジスタ14と、アドレスデコーダ15と、オープンドレイン出力部16と、電源電圧検出部17と、高電圧生成部18aと、内部参照電圧生成部18bと、セレクタ19と、を有する。

【0022】

メモリバンク11は、メモリコントローラ12によって制御されるメモリセルの集合体(例えば2kビット)である。

【0023】

メモリコントローラ12は、クロック端子SCL1とデータ端子SDA1を用いて装置外部のマスタ(不図示)と2線式のI2Cシリアルデータ通信を行い、マスタから与えられる各種コマンドに応じてメモリバンク11のリード/ライト制御などを行う。図2は、I2Cシリアルデータ通信の概要を示すタイミングチャートである。I2Cシリアルデータ通信は、スタートコンディション(S)の入力によって開始され、ストップコンディション(P)の入力によって終了される。データ(DATA)は常に8ビット長であり、1バイト分(8ビット長)のデータ転送毎にアクノリッジ(ACK)が要求される。なお、スタートコンディション(S)の入力直後には、7ビット長のスレーブアドレス(ADDRESS)と1ビット長のリード/ライトフラグ(R/W)が入力される。

【0024】

データレジスタ13は、メモリバンク11のリードデータやライトデータを一時的に格納する。ビットラインBLを介してメモリバンク11のメモリセルから読み出されたリードデータは、データレジスタ13に一時格納された後、オープンドレイン出力部16を介してデータ端子SDA1に出力される。一方、データ端子SDA1から入力されたライトデータは、データレジスタ13に一時格納された後、ビットラインBLを介してメモリバンク11のメモリセルに書き込まれる。

【0025】

アドレスレジスタ14は、メモリコントローラ12の指示に基づいて、データ端子SDA1から入力されたメモリバンク11のアドレスデータを一時的に格納する。

【0026】

アドレスデコーダ15は、メモリコントローラ12の指示に基づいて、アドレスレジスタ14に一時格納されたアドレスデータを読み出し、メモリバンク11のワードラインWLとセンスラインSLを各々駆動する。アドレスデコーダ15に含まれるワードライン駆動部151には、電源電圧Vccと高電圧HVが供給されている。また、アドレスデコーダ15に含まれるセンスライン駆動部152には、内部参照電圧VREFと高電圧HVが供給されている。ただし、メモリバンク11のテストモード時において、センスライン駆動部152には、内部参照電圧VREFに代えて任意のテスト電圧(外部参照電圧)Vrefが供給される。これについては、後ほど詳細に説明する。

【0027】

オープンドレイン出力部16は、データレジスタ13の出力に応じてオン/オフされるNチャネル型MOS[metal oxide semiconductor]電界効果トランジスタである。データレジスタ13の出力がハイレベルである場合、NMOSFETがオンとなり、データ端子SDA1がローレベルとなる。一方、データレジスタ13の出力がローレベルである場合、NMOSFETがオフとなり、データ端子SDA1がハイレベルとなる。

【0028】

電源電圧検出部17は、電源端子VCC1に印加される電源電圧Vccが所定の閾値電圧よりも高いか否かを検出し、その検出結果をメモリコントローラ12に出力する。この検出結果を受けたメモリコントローラ12は、例えば、電源電圧Vccが閾値電圧よりも低いときにメモリバンク11への書き込み動作を禁止する。このような構成とすることにより、減電時におけるメモリバンク11への誤書き込みを防止することができる。

【0029】

高電圧生成部18aは、メモリコントローラ12の指示に基づいて、電源電圧Vccから高電圧HV(>Vcc)を生成する。高電圧生成部18aとしては、チャージポンプ回路などを用いることができる。高電圧生成部18aは、メモリバンク11への書き込み動作時にのみ駆動される。

【0030】

内部参照電圧生成部18bは、メモリコントローラ12の指示に基づいて、電源電圧Vccから内部参照電圧VREF(例えば0.8V)を生成する。内部参照電圧生成部18bは、メモリバンク11の読み出し動作時にのみ駆動される。

【0031】

セレクタ19は、メモリコントローラ12の指示に基づいて、メモリバンク11の通常モード時には、内部参照電圧VREFをセンスライン駆動部152に供給する一方、メモリバンク11のテストモード時には、メモリバンク11用のテスト端子(クロック端子SCL2またはデータ端子SDA2を流用)に印加されるテスト電圧(外部参照電圧)Vrefをセンスライン駆動部152に供給するように、センスライン駆動部152への電圧供給経路を切り替える。

【0032】

メモリ回路20は、基本的にメモリ回路10と同一の構成から成り、メモリバンク21と、メモリコントローラ22と、データレジスタ23と、アドレスレジスタ24と、アドレスデコーダ25と、オープンドレイン出力部26と、電源電圧検出部27と、高電圧生成部28aと、内部参照電圧生成部28bと、セレクタ29とを有する。メモリ回路20を形成する構成要素21〜29の動作は、基本的にメモリ回路10を形成する構成要素11〜19の動作と同一であり、構成要素11〜19の動作を各々説明する中で用いた符号のうち、「11」〜「19」、「151」〜「152」、「VCC1」、「SCL1」、「SDA1」、「SCL2」、及び、「SDA2」を、それぞれ、「21」〜「29」、「251」〜「252」、「VCC2」、「SCL2」、「SDA2」、「SCL1」、及び、「SDA1」と読み替えれば足りるので、ここでは冗長的な説明を割愛する。

【0033】

ただし、メモリコントローラ22は、ライトプロテクト端子WP2に入力されるライトプロテクト信号に応じて、メモリバンク21への書き込み動作を許可/禁止する、というメモリコントローラ12にはない特有の機能を備えている。例えば、ライトプロテクト信号がハイレベル(Vcc)であるときには、メモリバンク21への書き込み動作が禁止され、ライトプロテクト信号がローレベル(GND)であるときには、メモリバンク21への書き込み動作が許可される。このようなライトプロテクト機能を備えた構成であれば、メモリバンク21への誤書込みを防止することができる。

【0034】

また、半導体記憶装置1には、メモリ回路10及び20のほかに、トリガ電圧検出部30が集積化されている。トリガ電圧検出部30は、ライトプロテクト端子WP2に通常時と異なるトリガ電圧TRG(ライトプロテクト信号のハイレベル(Vcc)よりも高い高電圧(例えば2×Vcc))が印加されているか否かを検出し、その検出結果をメモリコントローラ12及び22に送出する。メモリコントローラ12及び22は、トリガ電圧検出部30の検出結果をテストモードへの移行トリガとして用いる。このような構成とすることにより、ライトプロテクト端子WP2に本来の機能とは異なる機能(テストイネーブル端子としての機能)を付加することができるので、外部端子数の削減を図ることが可能となる。なお、半導体記憶装置1のテストモードについては、後ほど詳細に説明する。

【0035】

<メモリバンク>

次に、メモリバンク11(メモリバンク21についても同様)の内部構成について、詳細な説明を行う。図3は、メモリバンク11の一構成例を示す回路図である。図3に示すように、メモリバンク11には、ワードラインWL、センスラインSL、ビットラインBL、及び、共通ソースラインASGが張り巡らされており、これらの制御ラインには、メモリセルトランジスタMTと選択用トランジスタSTから成るメモリセルCELLが複数接続されている。

【0036】

1バイト分のメモリセルCELL1〜CELL8に着目して接続関係を説明する。選択用トランジスタST1〜ST8のドレインは、それぞれビットラインBL1〜BL8に接続されている。選択用トランジスタST1〜ST8のソースは、それぞれメモリセルトランジスタMT1〜MT8のドレインに接続されている。選択用トランジスタST1〜ST8のゲートは、いずれもワードラインWL1に接続されている。メモリセルトランジスタMT1〜MT8のソースは、いずれも共通ソースラインASGに接続されている。共通ソースラインASGは、イネーブルトランジスタETを介して接地端に接続されている。メモリセルトランジスタMT1〜MT8のゲート(コントロールラインCLに相当)は、いずれもバイト選択トランジスタBT1を介してセンスラインSL1に接続されている。バイト選択トランジスタBT1のゲートは、ワードラインWL1に接続されている。

【0037】

図4は、メモリセルCELLの縦構造を示す垂直断面図である。先述した通り、メモリセルCELLは、選択用トランジスタSTとメモリセルトランジスタMTを有する。

【0038】

メモリセルトランジスタMTは、そのドレインDMとソースSMに挟まれたシリコン基板内の伝導チャネルとコントロールゲートCGとの間に、フローティングゲート(周囲と絶縁されたゲート)FGを有する構造とされており、コントロールゲートCGからみたメモリセルトランジスタMTのスレッショルド電圧VthがフローティングゲートFGに蓄積されている電荷量に応じて変化することを利用して、データの記憶が行われる。

【0039】

なお、メモリセルトランジスタMTのフローティングゲートFGとドレインDMに挟まれた絶縁体は、その一部が薄くなっており、この部分(トンネル絶縁膜)を介するトンネル効果によって、フローティングゲートFGに対する電子の注入及び放出が行われる。

【0040】

そして、メモリセルトランジスタMTのフローティングゲートFGに蓄積される電荷量を制御することにより、図5で示すように、メモリセルトランジスタMTのスレッショルド電圧Vthを2つの状態に分布させ、この2つの分布にそれぞれ「0」と「1」を対応させることにより、1つのメモリセルCELLに1ビットのデータが記憶される。

【0041】

上記構成から成るメモリセルCELL1にデータ「1」を書き込む場合には、ワードラインWL1とセンスラインSL1(コントロールラインCL1)に高電圧HVが印加されて、ビットラインBL1と共通ソースラインASGに接地電圧が印加される。このとき、選択用トランジスタSTはオンとなり、メモリセルトランジスタMTのトンネル絶縁膜には高電圧HVが印加される。従って、フローティングゲートFGに電子が注入されて、フローティングゲートFGが電子を蓄積した状態となる。このとき、メモリセルトランジスタMTのスレッショルド電圧Vthは、図5の読出電圧VRD(例えば内部参照電圧VREF)よりも高くなる。この状態は、メモリセルCELL1にデータ「1」が書き込まれた状態に相当する。

【0042】

一方、メモリセルCELL1にデータ「0」を書き込む場合(すなわちデータ「1」を消去する場合)には、ワードラインWL1とビットラインBL1に高電圧HVが印加されて、センスラインSL1(コントロールラインCL1)に接地電圧が印加されて、共通ソースラインASGがオープン状態とされる。このとき、選択用トランジスタSTはオンとなり、メモリセルトランジスタMTのトンネル絶縁膜には高電圧HVが印加される。従って、フローティングゲートFGから電子が放出されて、フローティングゲートFGは電子が欠乏した状態となる。このとき、メモリセルトランジスタMTのスレッショルド電圧Vthは、図5の読出電圧VRD(例えば内部参照電圧VREF)よりも低くなる。この状態は、データ「0」が書き込まれた状態(データ「1」が消去された状態)に相当する。

【0043】

なお、メモリセルCELL1からデータを読み出す際には、センスラインSL1(コントロールラインCL1)に読出電圧VRD(例えば内部参照電圧VREF)を印加し、ワードラインWL1に電源電圧Vccを印加し、共通ソースラインASGに接地電圧を印加した状態で、ハイインピーダンスとされたビットラインBL1に電流が流れるか否かを判定すればよい。ビットラインBL1に電流が流れなければ、メモリセルトランジスタMTのスレッショルド電圧Vthが読出電圧VRDよりも高い状態(すなわち、データ「1」が書き込まれた状態)であると判定することができる。一方、ビットラインBL1に電流が流れれば、メモリセルトランジスタMTのスレッショルド電圧Vthが読出電圧VRDよりも低い状態(すなわち、データ「0」が書き込まれた状態)であると判定することができる。

【0044】

<テストモード>

次に、半導体記憶装置1のテストモードについて説明する。コントローラ12は、ライトプロテクト端子WP2にトリガ電圧TRG(例えば2×Vcc)が印加されている状態で、データ端子SDA1にテストモード移行コマンドが入力されたときに、メモリバンク11のテストモードに移行し、メモリバンク11用のテスト端子としてメモリバンク21用のクロック端子SCL2を流用する。より具体的に述べると、コントローラ12は、メモリバンク11のテストモード時に、クロック端子SCL2からメモリバンク11のメモリセルトランジスタに任意のゲート電圧(テスト電圧(外部参照電圧)Vref)が印加されるように、セレクタ19の切替制御を行う。

【0045】

上記と同様に、コントローラ22は、ライトプロテクト端子WP2にトリガ電圧TRGが印加されている状態で、データ端子SDA2にテストモード移行コマンドが入力されたときに、メモリバンク21のテストモードに移行し、メモリバンク21用のテスト端子としてメモリバンク11用のクロック端子SCL1を流用する。より具体的に述べると、コントローラ22は、メモリバンク21のテストモード時に、クロック端子SCL1からメモリバンク21のメモリセルトランジスタに任意のゲート電圧(テスト電圧(外部参照電圧)Vref)が印加されるように、セレクタ29の切替制御を行う。

【0046】

例えば、メモリセルCELL1(図3を参照)からデータを読み出す際、読出電圧VRDとしてセンスラインSL1に印加されるテスト電圧(外部参照電圧)Vrefを連続的または段階的に変化させていくことにより、メモリセルCELL1のスレッショルド電圧Vthを測定することができる。先出の図5で示したように、メモリセルCELLのスレッショルド電圧Vthは、ある程度のばらつきを持って分布している。従って、半導体記憶装置1の出荷時にスレッショルド電圧Vthを測定し、既定の読出電圧VRD(例えば内部参照電圧VREF)に対するマージンを確認しておくことは、製品の信頼性を高める上で非常に重要である。

【0047】

このように、本願の発明者らは、デュアルポートEEPROMの出荷検査時に2ポート分のメモリバンク同時に動作させる必要がないという点に着目し、鋭意研究の末、一方のメモリバンクをテストモードで動作させている際には、他方のメモリバンクを非動作状態とした上で、一方のメモリバンク用のテスト端子として他方のメモリバンク用の外部端子を流用するという着想を得て、上記構成から成る半導体記憶装置1を創作するに至った。

【0048】

上記構成から成る半導体記憶装置1であれば、専用のテスト端子を設けることなく、パッケージング後に所望のテスト(例えばメモリセルのスレッショルド電圧を測定するためのアナログ特性テスト)を実施することができるので、パッケージの大型化を招くことなく、製品の信頼性を高めることが可能となる。

【0049】

<アプリケーション>

図6は、半導体記憶装置を用いたアプリケーションの一例を示すブロック図である。本構成例の表示システムZは、表示装置Xと表示データ生成装置Yを有する。

【0050】

表示装置Xは、半導体記憶装置X1と、表示部X2と、タイミングコントローラX3とを有する。半導体記憶装置X1は、拡張ディスプレイ識別データd1(いわゆるEDID[extended display identification data])を格納する第1メモリバンクと、タイミング制御データd2を格納する第2メモリバンクを有する。半導体記憶装置X1としては、先述の半導体記憶装置1を好適に用いることができる。表示部X2は、表示データ生成装置Yから入力される表示データd3に基づいて映像を表示する。表示部X2としては、液晶ディスプレイ、プラズマディスプレイ、有機ELディスプレイなどを用いることができる。タイミングコントローラX3は、半導体記憶装置1の第2メモリバンクからタイミング制御データd2を読み出して表示部X2のタイミング制御を行う。

【0051】

表示データ生成装置Yは、表示データ出力部Y1とマイコンY2を有する。表示データ出力部Y1は、表示装置Xに表示データd3を出力する。マイコンY2は、表示装置Xに設けられた半導体記憶装置X1の第1メモリバンクから拡張ディスプレイ識別データd1を読み出して表示データ出力部Y1の出力制御(出力解像度の最適化など)を行う。

【0052】

表示システムZは、表示装置Xと表示データ生成装置Yを内蔵した一つの電子機器(ノート型パソコン、携帯電話、及び、タブレット端末など)として構築することができる。この場合、表示装置Xは、表示パネルなどを備えた表示モジュールに相当し、表示データ生成装置Yは、携帯機器の本体モジュールに相当する。また、表示システムZは、各々独立した表示装置Xと表示データ生成装置Yによって構築することもできる。この場合、表示装置Xは、テレビやモニタなどに相当し、表示データ生成装置Yは、光ディスク再生機器などに相当する。

【0053】

上記したように、同一の表示システムZ内に複数のメモリを必要とするアプリケーションにおいて、デュアルポートEEPROMを用いる構成であれば、シングルポートEEPROMを複数用いるよりも、マザーボード上における占有面積を削減して、システムの小型化に貢献することが可能となる。また、部品点数の削減によるシステムの信頼性向上を図ることも可能となる。さらに、EEPROMの1パッケージ化によるパッケージコスト削減効果も享受することが可能となる。

【0054】

<その他の変形例>

なお、上記の実施形態では、テレビやモニタなどの表示装置に搭載されたデュアルポートEEPROMに本発明を適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、複数のメモリバンクを有するマルチポート型の半導体記憶装置及びこれを用いた電子機器全般について、その用途を問わず、広く一般的に適用することが可能である。また、テストの内容もメモリセルのアナログ特性テストに限定されるものではない。

【0055】

また、複数のメモリバンクに各々アクセスするためのポートは、同種の規格(例えば、I2C)に準拠したものであってもよいし、或いは、異種の規格(例えば、I2C、SPI[Serial Peripheral Interface]、及び、マイクロワイヤ)に準拠したものであってもよい。また、複数のメモリバンクは、同一の容量を有するものであってもよいし、異なる容量を有するものであってもよい。また、ポート数(メモリバンクの搭載数)は3つ以上でもよい。また、半導体記憶装置は、シングルチップパッケージとしてもよいし、マルチチップパッケージとしてもよい。

【0056】

このように、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0057】

本発明に係る半導体記憶装置は、例えば、同一のシステム内に複数のメモリを必要とするアプリケーション全般で利用することが可能である。

【符号の説明】

【0058】

1 半導体記憶装置

10、20 メモリ回路

11、21 メモリバンク

12、22 メモリコントローラ

13、23 データレジスタ

14、24 アドレスレジスタ

15、25 アドレスデコーダ

151、251 ワードライン駆動部

152、252 センスライン駆動部

16、26 オープンドレイン出力部(NMOSFET)

17、27 電源電圧検出部

18a、28a 高電圧生成部

18b、28b 内部参照電圧生成部

19、29 セレクタ

30 トリガ電圧検出部

VCC1、VCC2 電源端子

SCL1、SCL2 クロック端子(テスト端子としても流用)

SDA1、SDA2 データ端子

GND 接地端子

WP2 ライトプロテクト端子

WL ワードライン

CL コントロールライン

SL センスライン

BL ビットライン

ASG 共通ソースライン

CELL メモリセル

ST 選択用トランジスタ

DS ドレイン

SS ソース

G ゲート

MT メモリセルトランジスタ

DM ドレイン

SM ソース

CG コントロールゲート

FG フローティングゲート

X 表示装置

X1 半導体記憶装置

X2 表示部

X3 タイミングコントローラ

Y 表示データ生成装置

Y1 表示データ出力部

Y2 マイコン

Z 表示システム

【特許請求の範囲】

【請求項1】

第1メモリバンクと、

第2メモリバンクと、

第1メモリバンク用の第1コントローラと、

第2メモリバンク用の第2コントローラと、

を有し、

前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1メモリバンク用の第1テスト端子として前記第2メモリバンク用の外部端子を流用し、

前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2メモリバンク用の第2テスト端子として前記第1メモリバンク用の外部端子を流用する、

ことを特徴とする半導体記憶装置。

【請求項2】

前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1テスト端子から前記第1メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第1テスト端子の接続先を切り替え、

前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2テスト端子から前記第2メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第2テスト端子の接続先を切り替える、

ことを特徴とする請求項1に記載の半導体記憶装置。

【請求項3】

前記第1コントローラは、所定の外部端子に通常時と異なるトリガ電圧が印加されている状態で、前記第1メモリバンク用の第1信号端子に特定コマンドが入力されたときに、前記第1メモリバンクのテストモードに移行し、

前記第2コントローラは、前記所定の外部端子に前記トリガ電圧が印加されている状態で、前記第2メモリバンク用の第2信号端子に前記特定コマンドが入力されたときに、前記第2メモリバンクのテストモードに移行する、

ことを特徴とする請求項2に記載の半導体記憶装置。

【請求項4】

前記第1信号端子と前記第2信号端子は、互いにパッケージの対辺に設けられている、

ことを特徴とする請求項3に記載の半導体記憶装置。

【請求項5】

識別データを格納する第1メモリバンクとタイミング制御データを格納する第2メモリバンクを有する請求項4に記載の半導体記憶装置と、

表示データに基づいて映像を表示する表示部と、

前記第2メモリバンクから前記タイミング制御データを読み出して前記表示部のタイミング制御を行うタイミングコントローラと、

を有することを特徴とする表示装置。

【請求項6】

請求項5に記載の表示装置に表示データを出力する表示データ出力部と、

前記表示装置に設けられた半導体記憶装置の第1メモリバンクから識別データを読み出して前記表示データ出力部を制御するマイコンと、

を有することを特徴とする表示データ生成装置。

【請求項7】

請求項5に記載の表示装置と、

請求項6に記載の表示データ生成装置と、

を有することを特徴とする表示システム。

【請求項8】

請求項1〜請求項4のいずれか一項に記載の半導体記憶装置を有する、

ことを特徴とする電子機器。

【請求項1】

第1メモリバンクと、

第2メモリバンクと、

第1メモリバンク用の第1コントローラと、

第2メモリバンク用の第2コントローラと、

を有し、

前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1メモリバンク用の第1テスト端子として前記第2メモリバンク用の外部端子を流用し、

前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2メモリバンク用の第2テスト端子として前記第1メモリバンク用の外部端子を流用する、

ことを特徴とする半導体記憶装置。

【請求項2】

前記第1コントローラは、前記第1メモリバンクのテストモード時に、前記第1テスト端子から前記第1メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第1テスト端子の接続先を切り替え、

前記第2コントローラは、前記第2メモリバンクのテストモード時に、前記第2テスト端子から前記第2メモリバンクのメモリセルトランジスタに任意のゲート電圧が印加されるように、前記第2テスト端子の接続先を切り替える、

ことを特徴とする請求項1に記載の半導体記憶装置。

【請求項3】

前記第1コントローラは、所定の外部端子に通常時と異なるトリガ電圧が印加されている状態で、前記第1メモリバンク用の第1信号端子に特定コマンドが入力されたときに、前記第1メモリバンクのテストモードに移行し、

前記第2コントローラは、前記所定の外部端子に前記トリガ電圧が印加されている状態で、前記第2メモリバンク用の第2信号端子に前記特定コマンドが入力されたときに、前記第2メモリバンクのテストモードに移行する、

ことを特徴とする請求項2に記載の半導体記憶装置。

【請求項4】

前記第1信号端子と前記第2信号端子は、互いにパッケージの対辺に設けられている、

ことを特徴とする請求項3に記載の半導体記憶装置。

【請求項5】

識別データを格納する第1メモリバンクとタイミング制御データを格納する第2メモリバンクを有する請求項4に記載の半導体記憶装置と、

表示データに基づいて映像を表示する表示部と、

前記第2メモリバンクから前記タイミング制御データを読み出して前記表示部のタイミング制御を行うタイミングコントローラと、

を有することを特徴とする表示装置。

【請求項6】

請求項5に記載の表示装置に表示データを出力する表示データ出力部と、

前記表示装置に設けられた半導体記憶装置の第1メモリバンクから識別データを読み出して前記表示データ出力部を制御するマイコンと、

を有することを特徴とする表示データ生成装置。

【請求項7】

請求項5に記載の表示装置と、

請求項6に記載の表示データ生成装置と、

を有することを特徴とする表示システム。

【請求項8】

請求項1〜請求項4のいずれか一項に記載の半導体記憶装置を有する、

ことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−105513(P2013−105513A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249571(P2011−249571)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]