半導体記憶装置

【課題】半導体記憶装置のスイッチング耐久性の向上を図る。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

【解決手段】実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路とを備えている。制御回路は、選択ビット線を0ボルトにし、選択ワード線に0ボルトよりも高い第1の電位を与え、非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、選択セルアレイブロックに第1の方向で隣接し選択ビット線を選択セルアレイブロックと共有する隣接セルアレイブロックにおける、選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、選択メモリセルの抵抗変化膜の抵抗状態を変化させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置に関する。

【背景技術】

【0002】

新しい不揮発性半導体記憶装置として、ワード線と、ビット線と、これらに挟持された記録層としての抵抗変化膜とを複数積み重ねた構造が提案されている。抵抗変化膜に対する印加電圧の大きさ、極性、印加時間の制御などによって、抵抗変化膜を相対的に抵抗が異なる少なくとも2つの抵抗状態に切り替えることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−80041号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体記憶装置のスイッチング耐久性の向上を図る。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路と、を備えている。それぞれの前記セルアレイブロックは、第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、を有する。前記複数のセルアレイブロックは、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している。前記制御回路は、前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる。

【図面の簡単な説明】

【0006】

【図1】実施形態の半導体記憶装置の構成を示すブロック図。

【図2】実施形態の半導体記憶装置のメモリセルアレイの一部の模式斜視図。

【図3】実施形態の半導体記憶装置のメモリセルの模式断面図。

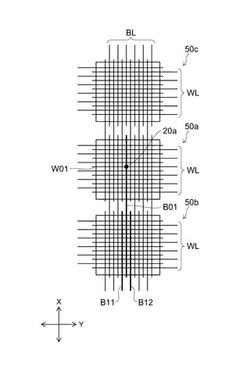

【図4】実施形態の半導体記憶装置のメモリセルアレイの一部の模式平面図。

【図5】第1実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図6】第2実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図7】第3実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図8】第4実施形態の半導体記憶装置の動作を説明するための模式平面図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

図1は、実施形態の半導体記憶装置の構成を示すブロック図である。

【0009】

実施形態の半導体記憶装置は、いわゆる3次元クロスポイント型のメモリセルアレイ1を有する。メモリセルアレイ1は、後述するように、3次元配列された複数のメモリセルと、メモリセルを介在させて積層された複数のビット線及びワード線を有する。

【0010】

カラム制御回路2はメモリセルアレイ1のビット線の電位を制御し、ロウ制御回路3はメモリセルアレイ1のワード線の電位を制御する。ビット線及びワード線の電位制御により、メモリセルに対するデータ消去、データ書き込み、データ読み出しが制御される。

【0011】

メモリセルアレイ1は、複数のセルアレイブロックと呼ばれる単位ごとに分けられることも可能であり、その場合、個々のセルアレイブロックごとにカラム制御回路2とロウ制御回路3を有していてもよいし、複数のセルアレイブロックでカラム制御回路2とロウ制御回路3を共有してもよい。

【0012】

カラム制御回路2は、データ入出力バッファ6に接続されている。データ入出力バッファ6は、外部のホストコントローラ9に外部I/O線を介して接続され、書き込みデータの受け取り、消去命令の受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ6は、ホストコントローラ9から受け取った書き込みデータをカラム制御回路2に送り、また、カラム制御回路2から読み出したデータを受け取る。また、読み出しデータはカラム制御回路2にラッチされ、データ入出力バッファ6及び外部I/O線を介して外部に出力することも可能である。

【0013】

メモリセルを選択するためのアドレスデータは、外部からステートマシン8を介してカラム制御回路2やロウ制御回路3に送られる。また、ホストコントローラ9からのコマンドデータはコマンドインターフェイス7に送られる。

【0014】

コマンドインターフェイス7は、ホストコントローラ9からの制御信号を受け、データ入出力バッファ6に入力されたデータが、書き込みデータか、コマンドデータか、アドレスデータかを判断し、コマンドデータであれば受け取りコマンド信号としてステートマシン8に転送する。

【0015】

ステートマシン8は、半導体記憶装置全体を管理する。すなわち、ステートマシン8は、ホストコントローラ9からのコマンドを受け、読み出し、書き込み、消去、データの入出力管理などを行う。

【0016】

また、ホストコントローラ9は、ステートマシン8が管理するステータス情報を受け取り、動作結果を判断することも可能である。また、前記ステータス情報は、書き込み、消去の制御にも利用される。

【0017】

メモリセルアレイ1は、基板(例えばシリコン基板)上に形成される。カラム制御回路2、ロウ制御回路3などは、メモリセルアレイ1の直下の基板表面に形成可能である。この場合、半導体記憶装置のチップ面積は、ほぼメモリセルアレイ1の面積に等しくすることが可能である。

【0018】

また、ステートマシン8によってパルスジェネレータ4が制御される。この制御により、パルスジェネレータ4は任意の電圧、任意のタイミングのパルスを出力することが可能となる。パルスジェネレータ4で生成されたパルスは、ロウ制御回路3で選択された任意のワード線へ転送することが可能である。

【0019】

図2は、メモリセルアレイ1の一部の模式斜視図である。

【0020】

メモリセルアレイ1は、複数のワード線WLと複数のビット線BLを有する。さらに、メモリセルアレイ1は、ワード線WLとビット線BLとの間に挟持されたピラー状の複数の積層体10を有する。

【0021】

ワード線WLとビット線BLとは、平面視で非平行であり、3次元的に交差している。各積層体10は、ワード線WLとビット線BLとが交差するクロスポイントで、ワード線WLとビット線BLとの間に設けられている。

【0022】

各ビット線BLは第1の方向Xに延び、各ワード線WLは第2の方向Yに延びている。第1の方向Xと第2の方向Yとは交差し、図2においては例えば直交している。複数の積層体10が2次元方向(XY方向)に例えばマトリクス状に配列され、さらに、そのマトリクス状のアレイが、XY平面に対して直交するZ方向に複数積層されている。図2は、例えば、3行×3列のアレイが4層分積層された部分を表す。

【0023】

各ワード線WLは、上下の積層体10間で共有されている。同様に、各ビット線BLは、上下の積層体10間で共有されている。この構造は、レイヤー数の低減による低コスト化を図れる。

【0024】

あるいは、ワード線WL/積層体10/ビット線BL/層間絶縁膜/ワード線WL/積層体10/ビット線BLを繰り返した構造であってもよい。この構造は、一つの配線(ビット線BLまたはワード線WL)に接続するメモリセルの数を低減でき、高速動作に適している。

【0025】

図3に、積層体10の断面構造を表す。図3は、図2における1層分のアレイのYZ断面に対応する。

【0026】

積層体10は、ビット線BLとワード線WLとの間に直列接続されたメモリセル20と非オーミック素子14とを有する。

【0027】

メモリセル20は、上部電極13と、下部電極11と、これら上部電極13と下部電極11との間に設けられた抵抗変化膜12とを有する。

【0028】

抵抗変化膜12は、電圧、電流、熱、化学エネルギー等で、相対的に抵抗が低い状態(セット状態)と抵抗が高い状態(リセット状態)とをスイッチング可能で、データを不揮発に記憶する。

【0029】

非オーミック素子14として、例えば、PN接合ダイオード、PIN(P-Intrinsic-N)ダイオード、ショットキーダイオード等の各種ダイオード、あるいは、MIM(Metal-Insulator-Metal)素子、SIS(Silicon-Insulator-Silicon)素子などを用いることができる。

【0030】

非オーミック素子14としてダイオードを使用する場合、メモリセル20のユニポーラ動作が可能である。すなわち、抵抗変化膜12に印加する電圧の大きさや印加時間の制御により、抵抗変化膜12の抵抗状態を変化させることができる。

【0031】

また、非オーミック素子14として、MIM素子、SIS素子等を使用する場合、メモリセル20のバイポーラ動作が可能である。すなわち、抵抗変化膜12に印加する電圧の極性を変えることで、抵抗変化膜12の抵抗状態を変化させることができる。

【0032】

メモリセル20における下部電極11及び上部電極13は、バリアメタルや接着層としての機能も担うことが可能で、例えば、Pt、Au、Ag、TiAlN、SrRuO、Ru、RuN、Ir、Co、Ti、TiN、TaN、LaNiO、Al、PtIrOx、PtRhOx、Rh、TaAlNなどを用いることができる。また、非オーミック素子14とワード線WLとの間に設けられた層15は、バリアメタルや接着層として機能し、例えば、Ti、TiNなどを用いることができる。

【0033】

ビット線BLおよびワード線WLとしては、耐熱性に優れ、かつ、低抵抗材料が望ましく、例えば、W、WSi、NiSi、CoSiなどを用いることができる。

【0034】

抵抗変化膜12は、相対的に抵抗が異なる少なくとも2つの状態に、例えば電気的に切り替え可能である。相対的に抵抗が低い状態をセット状態とし、セット状態よりも抵抗が高い状態をリセット状態とする。

【0035】

低抵抗状態(セット状態)の抵抗変化膜12にリセット電圧が印加されると、抵抗変化膜12は高抵抗状態(リセット状態)に切り替わることができる。高抵抗状態(リセット状態)の抵抗変化膜12に、リセット電圧よりも高い、もしくはリセット電圧と極性が異なるセット電圧が印加されると、抵抗変化膜12は低抵抗状態(セット状態)に切り替わることができる。

【0036】

図4は、メモリセルアレイ1における、ある一層分の一部の模式平面図である。

【0037】

メモリセルアレイ1の各レイヤーは、複数のセルアレイブロック50に分けられている。複数のセルアレイブロック50は、ビット線BLが延びる方向である第1の方向Xと、ワード線WLが延びる方向である第2の方向Yに、例えばマトリクス状に配列されている。

【0038】

各ビット線BLは、第1の方向Xに配列されたすべてのセルアレイブロック50間をつないではいない。同様に、各ワード線WLは、第2の方向Yに配列されたすべてのセルアレイブロック50間をつないではいない。これにより、配線長の増大を抑え、ビット線BLやワード線WLにおける電圧降下(IRドロップ)や、非選択メモリセルからのリーク電流を抑制することができる。

【0039】

ただし、各ビット線BLは、個々のセルアレイブロック50単位では分断されてはおらず、第1の方向Xで隣接する例えば2つのセルアレイブロック50間で共有されている。同様に、各ワード線WLは、個々のセルアレイブロック50単位では分断されてはおらず、第2の方向Yで隣接する例えば2つのセルアレイブロック50間で共有されている。これにより、チップ面積の増大を抑制できる。

【0040】

図4の第1の方向Xにおいて、例えば上2つのセルアレイブロック50間で共有するビット線BLと、下2つのセルアレイブロック50間で共有するビット線BLとは、第2の方向Yに交互に配列されている。

【0041】

図4の第2の方向Yにおいて、例えば左2つのセルアレイブロック50間で共有するワード線WLと、右2つのセルアレイブロック50間で共有するワード線WLとは、第1の方向Xに交互に配列されている。

【0042】

次に、メモリセルの例えば書き込み動作(セット動作)について説明する。

【0043】

動作対象(書き込み)対象のメモリセルを選択メモリセル(単に選択セルともいう)とし、選択セル以外のメモリセルを非選択メモリセル(単に非選択セルともいう)とする。また、選択セルに接続されているビット線BLを選択ビット線とし、選択ビット線以外のビット線BLを非選択ビット線とする。選択セルに接続されているワード線WLを選択ワード線とし、選択ワード線以外のワード線WLを非選択ワード線とする。

【0044】

以下に説明する動作において、選択ビット線及び非選択ビット線の電位は、図1に示すカラム制御回路2によって制御され、選択ワード線及び非選択ワード線の電位は、図1に示すロウ制御回路3によって制御される。

【0045】

(第1実施形態)

図5は、半導体記憶装置の動作の第1実施形態を説明するための模式平面図である。

【0046】

図5において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。選択セル20aは、選択ビット線B01と、選択ワード線W01とのクロスポイントに設けられている。

【0047】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図5には、選択セルアレイブロック50aに対して第1の方向Xで隣接する例えば2つの隣接セルアレイブロック50b、50cを表す。隣接セルアレイブロック50bは、選択セルアレイブロック50aに対して図5において下で隣接している。隣接セルアレイブロック50cは、選択セルアレイブロック50aに対して図5において上で隣接している。

【0048】

選択セルアレイブロック50aと隣接セルアレイブロック50cとの間で共有されたビット線BLと、選択セルアレイブロック50aと隣接セルアレイブロック50bとの間で共有されたビット線BLとは、例えば第2の方向Yに交互に配列されている。

【0049】

選択ビット線B01には0ボルトの電位が与えられ、選択ワード線W01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0050】

このとき、非選択ビット線及び非選択ワード線には、0ボルトよりも高く第1の電位VPGMよりも低い第2の電位(例えば、VPGM/2)が与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0051】

ここで、隣接するセルアレイブロック間でビット線を共有している構造の場合、以下に説明する問題が懸念される。

【0052】

例えば、図5において、選択セルアレイブロック50aと選択ビット線B01を共有している隣接セルアレイブロック50bにおける、選択ビット線B01とこれに隣接する非選択ビット線B11との間の配線間容量、または選択ビット線B01とこれに隣接する非選択ビット線B12との間の配線間容量が、書き込み動作に影響を与える場合がある。すなわち、選択セル20aの抵抗変化膜12が低抵抗状態(セット状態)になり、抵抗が低くなると、上記配線間容量に充電された電荷が瞬間的に選択セル20aの抵抗変化膜12に流れてしまう。

【0053】

そこで、実施形態によれば、非選択ビット線の制御系統を2系統設け、選択ビット線B01に他ブロックで隣接する非選択ビット線B11及びB12は、他の非選択ビット線とは独立して制御する。

【0054】

具体的には、上記書き込み動作時、非選択ビット線B11及びB12を、選択ビット線B01と同じ0ボルトにする。すなわち、他の非選択ビット線は、書き込み動作時、第2の電位に上昇されるのに対して、非選択ビット線B11及びB12は、選択ビット線B01とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0055】

隣接セルアレイブロック50bで、隣接する選択ビット線B01、非選択ビット線B11及びB12(図5において太線で表すビット線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0056】

隣接セルアレイブロック50bのワード線WLはすべて非選択であり、第2の電位(VPGM/2)が与えられる。そのため、隣接セルアレイブロック50bにおける、非選択ビット線B11及びB12に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0057】

なお、非選択ビット線B11及びB12は、選択ビット線B01と同電位(0ボルト)にすることに限らず、選択ビット線B01との電位差が、他の非選択ビット線と選択ビット線B01との間の電位差(VPGM/2)よりも小さければ、上記配線間容量による過渡的な電流の抑制効果が得られる。すなわち、非選択ビット線B11及びB12には、0ボルト以上で上記第2の電位(VPGM/2)よりも低い第3の電位を与えることができる。

【0058】

非選択ビット線B11及びB12を0ボルトにすると、隣接セルアレイブロック50bにおける非選択ビット線B11またはB12と、非選択ワード線との間の非選択セルに(VPGM/2)の電圧がかかる。

【0059】

一方、非選択ビット線B11及びB12に0ボルトより高い電位(ただし、(VPGM/2)より低い電位)を与えると、隣接セルアレイブロック50bにおける非選択ビット線B11またはB12と、非選択ワード線との間の非選択セルには(VPGM/2)よりも小さい電圧がかかる。このため、その非選択セルの誤セット動作防止の確実性を高くできる。

【0060】

(第2実施形態)

図6は、半導体記憶装置の動作の第2実施形態を説明するための模式平面図である。

【0061】

第2実施形態では、複数の選択セル20aを同時に選択し、並列動作させる。図6において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。

【0062】

選択セル20aは、選択ビット線B01と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B02と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B03と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B04と選択ワード線W01とのクロスポイントに設けられている。

【0063】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図6には、選択セルアレイブロック50aに対して第1の方向Xで隣接する例えば2つの隣接セルアレイブロック50b、50cを表す。隣接セルアレイブロック50bは、選択セルアレイブロック50aに対して図6において下で隣接している。隣接セルアレイブロック50cは、選択セルアレイブロック50aに対して図6において上で隣接している。

【0064】

選択セルアレイブロック50aと隣接セルアレイブロック50cとの間で共有されたビット線BLと、選択セルアレイブロック50aと隣接セルアレイブロック50bとの間で共有されたビット線BLとは、例えば第2の方向Yに交互に配列されている。

【0065】

選択ビット線B01、B02、B03及びB04には0ボルトの電位が与えられ、選択ワード線W01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0066】

このとき、非選択ビット線及び非選択ワード線には、0ボルトよりも高く第1の電位VPGMよりも低い第2の電位(例えば、VPGM/2)が与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0067】

ただし、第2実施形態においても、第1実施形態と同様、選択ビット線B01、B02、B03及びB04に対して他ブロックで隣接する非選択ビット線B11、B12、B13、B14及びB15は、他の非選択ビット線とは独立して制御する。すなわち、第2実施形態によれば、非選択ビット線の制御系統を2系統設けている。

【0068】

具体的には、上記書き込み動作時、非選択ビット線B11、B12、B13、B14及びB15を、選択ビット線B01、B02、B03及びB04と同じ0ボルトにする。すなわち、他の非選択ビット線は、書き込み動作時、第2の電位に上昇されるのに対して、非選択ビット線B11、B12、B13、B14及びB15は、選択ビット線B01、B02、B03及びB04とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0069】

隣接セルアレイブロック50bで、隣接する選択ビット線B01、B02、B03及びB04と、非選択ビット線B11、B12、B13、B14及びB15(図6において太線で表すビット線)との電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0070】

隣接セルアレイブロック50bのワード線WLはすべて非選択であり、第2の電位(VPGM/2)が与えられる。そのため、隣接セルアレイブロック50bにおける、非選択ビット線B11、B12、B13、B14及びB15に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0071】

なお、第2実施形態においても、非選択ビット線B11、B12、B13、B14及びB15は、選択ビット線B01、B02、B03及びB04と同電位(0ボルト)にすることに限らず、0ボルト以上で上記第2の電位(VPGM/2)よりも低い第3の電位に制御すれば、上記配線間容量による過渡的な電流の抑制効果が得られる。

【0072】

(第3実施形態)

図7は、半導体記憶装置の動作の第3実施形態を説明するための模式平面図である。

【0073】

図7において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。選択セル20aは、選択ビット線B01と、選択ワード線W01とのクロスポイントに設けられている。

【0074】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図7には、選択セルアレイブロック50aに対して第2の方向Yで隣接する隣接セルアレイブロック50bを表す。

【0075】

前述した第1及び第2実施形態は、抵抗変化膜12に対して逆極性の電圧をかけることで抵抗状態を変化させるいわゆるバイポーラ動作に適用される。これに対して、第3実施形態は、抵抗変化膜12に対する印加電圧の大きさや印加時間の制御により、抵抗変化膜12の抵抗状態を変化させるいわゆるユニポーラ動作に適用される。

【0076】

このユニポーラ動作においては、選択ワード線W01には0ボルトの電位が与えられ、選択ビット線B01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0077】

このとき、非選択ビット線には0ボルトが与えられ、非選択ワード線には上記第1の電位VPGMが与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0078】

ただし、第3実施形態においては、非選択ワード線の制御系統を2系統設け、選択ワード線W01に対して他ブロックで隣接する非選択ワード線W11及びW12は、他の非選択ワード線とは独立して制御する。

【0079】

具体的には、上記書き込み動作時、非選択ワード線W11及びW12を、選択ワード線W01と同じ0ボルトにする。すなわち、他の非選択ワード線は、書き込み動作時、第1の電位に上昇されるのに対して、非選択ワード線W11及びW12は、選択ワード線W01とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0080】

隣接セルアレイブロック50bで、隣接する選択ワード線W01、非選択ワード線W11及びW12(図7において太線で表すワード線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0081】

隣接セルアレイブロック50bのビット線BLはすべて非選択であり、0ボルトである。そのため、隣接セルアレイブロック50bにおける、非選択ワード線W11及びW12に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0082】

(第4実施形態)

図8は、半導体記憶装置の動作の第4実施形態を説明するための模式平面図である。

【0083】

第4実施形態では、複数の選択セル20aを同時に選択し、並列動作させる。図8において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。

【0084】

選択セル20aは、選択ワード線W01と、選択ビット線B01とのクロスポイントに設けられている。また、選択セル20aは、選択ワード線W02と、選択ビット線B01とのクロスポイントに設けられている。また、選択セル20aは、選択ワード線W03と、選択ビット線B01とのクロスポイントに設けられている。

【0085】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図8には、選択セルアレイブロック50aに対して第2の方向Yで隣接する隣接セルアレイブロック50bを表す。

【0086】

第4実施形態もユニポーラ動作に適用される。このユニポーラ動作においては、選択ワード線W01、W02及びW03には0ボルトの電位が与えられ、選択ビット線B01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0087】

このとき、非選択ビット線には0ボルトが与えられ、非選択ワード線には上記第1の電位VPGMが与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0088】

ただし、第4実施形態においても、第3実施形態と同様、非選択ワード線の制御系統を2系統設け、選択ワード線W01、W02及びW03に対して他ブロックで隣接する非選択ワード線W11、W12、W13及びW14は、他の非選択ワード線とは独立して制御する。

【0089】

具体的には、上記書き込み動作時、非選択ワード線W11、W12、W13及びW14を、選択ワード線W01、W02及びW03と同じ0ボルトにする。すなわち、他の非選択ワード線は、書き込み動作時、第1の電位に上昇されるのに対して、非選択ワード線W11、W12、W13及びW14は、選択ワード線W01、W02及びW03とともに、電位が上昇されず、書き込み時あるいは書き込み動作の前後で0ボルトに保持される。

【0090】

隣接セルアレイブロック50bで、隣接する選択ワード線W01、W02及びW03、非選択ワード線W11、W12、W13及びW14(図8において太線で表すワード線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0091】

隣接セルアレイブロック50bのビット線BLはすべて非選択であり、0ボルトである。そのため、隣接セルアレイブロック50bにおける、非選択ワード線W11、W12、W13及びW14に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0092】

前述した実施形態は、選択セルに対する書き込み動作(セット動作)時に限らず、消去動作(リセット動作)時にも適用可能である。

【0093】

例えば、図5に示すバイポーラ動作において、消去動作時は、選択ビット線B01に第1の電位VPGMを与え、選択ワード線W01を0ボルトにする。

【0094】

このとき、図7を参照して説明した動作と同様の動作を適用できる。すなわち、選択ワード線W01の電位と、隣接セルアレイブロック50bにおける選択ワード線W01に隣接する非選択ワード線W11及びW12の電位を上昇させずに0ボルトに保持することにより、それらの配線間容量を抑制し、選択セル20aに配線間容量から過渡的に電流が流れるのを防ぐことができる。

【0095】

なお、抵抗変化膜が高抵抗状態から低抵抗状態になる動作を消去動作、低抵抗状態から高抵抗状態になる動作を書き込み動作とする場合もある。

【0096】

いずれにしても、抵抗変化膜が低抵抗状態から高抵抗状態に変化するときよりも、高抵抗状態から低抵抗状態に変化して選択セルの抵抗が低くなったときに、配線間容量の電荷が選択セルに流れやすく、選択セルの動作が大きな影響を受けやすい。

【0097】

したがって、選択セルの抵抗変化膜を高抵抗状態から低抵抗状態に変化させるときに、選択配線(選択ビット線または選択ワード線)、および隣接セルアレイブロックにおける選択配線に隣接する非選択配線(非選択ビット線または非選択ワード線)の電位を0ボルトもしくは上記第3の電位に制御すると有効である。

【0098】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0099】

1…メモリセルアレイ、10…積層体、12…抵抗変化膜、20…メモリセル、20a…選択メモリセル、50…セルアレイブロック、50a…選択セルアレイブロック、50b,50c…隣接セルアレイブロック、BL…ビット線、B01,B02,B03,B04…選択ビット線、WL…ワード線、W01,W02,W03…選択ワード線

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置に関する。

【背景技術】

【0002】

新しい不揮発性半導体記憶装置として、ワード線と、ビット線と、これらに挟持された記録層としての抵抗変化膜とを複数積み重ねた構造が提案されている。抵抗変化膜に対する印加電圧の大きさ、極性、印加時間の制御などによって、抵抗変化膜を相対的に抵抗が異なる少なくとも2つの抵抗状態に切り替えることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−80041号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体記憶装置のスイッチング耐久性の向上を図る。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体記憶装置は、複数のセルアレイブロックと、制御回路と、を備えている。それぞれの前記セルアレイブロックは、第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、を有する。前記複数のセルアレイブロックは、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している。前記制御回路は、前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる。

【図面の簡単な説明】

【0006】

【図1】実施形態の半導体記憶装置の構成を示すブロック図。

【図2】実施形態の半導体記憶装置のメモリセルアレイの一部の模式斜視図。

【図3】実施形態の半導体記憶装置のメモリセルの模式断面図。

【図4】実施形態の半導体記憶装置のメモリセルアレイの一部の模式平面図。

【図5】第1実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図6】第2実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図7】第3実施形態の半導体記憶装置の動作を説明するための模式平面図。

【図8】第4実施形態の半導体記憶装置の動作を説明するための模式平面図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

図1は、実施形態の半導体記憶装置の構成を示すブロック図である。

【0009】

実施形態の半導体記憶装置は、いわゆる3次元クロスポイント型のメモリセルアレイ1を有する。メモリセルアレイ1は、後述するように、3次元配列された複数のメモリセルと、メモリセルを介在させて積層された複数のビット線及びワード線を有する。

【0010】

カラム制御回路2はメモリセルアレイ1のビット線の電位を制御し、ロウ制御回路3はメモリセルアレイ1のワード線の電位を制御する。ビット線及びワード線の電位制御により、メモリセルに対するデータ消去、データ書き込み、データ読み出しが制御される。

【0011】

メモリセルアレイ1は、複数のセルアレイブロックと呼ばれる単位ごとに分けられることも可能であり、その場合、個々のセルアレイブロックごとにカラム制御回路2とロウ制御回路3を有していてもよいし、複数のセルアレイブロックでカラム制御回路2とロウ制御回路3を共有してもよい。

【0012】

カラム制御回路2は、データ入出力バッファ6に接続されている。データ入出力バッファ6は、外部のホストコントローラ9に外部I/O線を介して接続され、書き込みデータの受け取り、消去命令の受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ6は、ホストコントローラ9から受け取った書き込みデータをカラム制御回路2に送り、また、カラム制御回路2から読み出したデータを受け取る。また、読み出しデータはカラム制御回路2にラッチされ、データ入出力バッファ6及び外部I/O線を介して外部に出力することも可能である。

【0013】

メモリセルを選択するためのアドレスデータは、外部からステートマシン8を介してカラム制御回路2やロウ制御回路3に送られる。また、ホストコントローラ9からのコマンドデータはコマンドインターフェイス7に送られる。

【0014】

コマンドインターフェイス7は、ホストコントローラ9からの制御信号を受け、データ入出力バッファ6に入力されたデータが、書き込みデータか、コマンドデータか、アドレスデータかを判断し、コマンドデータであれば受け取りコマンド信号としてステートマシン8に転送する。

【0015】

ステートマシン8は、半導体記憶装置全体を管理する。すなわち、ステートマシン8は、ホストコントローラ9からのコマンドを受け、読み出し、書き込み、消去、データの入出力管理などを行う。

【0016】

また、ホストコントローラ9は、ステートマシン8が管理するステータス情報を受け取り、動作結果を判断することも可能である。また、前記ステータス情報は、書き込み、消去の制御にも利用される。

【0017】

メモリセルアレイ1は、基板(例えばシリコン基板)上に形成される。カラム制御回路2、ロウ制御回路3などは、メモリセルアレイ1の直下の基板表面に形成可能である。この場合、半導体記憶装置のチップ面積は、ほぼメモリセルアレイ1の面積に等しくすることが可能である。

【0018】

また、ステートマシン8によってパルスジェネレータ4が制御される。この制御により、パルスジェネレータ4は任意の電圧、任意のタイミングのパルスを出力することが可能となる。パルスジェネレータ4で生成されたパルスは、ロウ制御回路3で選択された任意のワード線へ転送することが可能である。

【0019】

図2は、メモリセルアレイ1の一部の模式斜視図である。

【0020】

メモリセルアレイ1は、複数のワード線WLと複数のビット線BLを有する。さらに、メモリセルアレイ1は、ワード線WLとビット線BLとの間に挟持されたピラー状の複数の積層体10を有する。

【0021】

ワード線WLとビット線BLとは、平面視で非平行であり、3次元的に交差している。各積層体10は、ワード線WLとビット線BLとが交差するクロスポイントで、ワード線WLとビット線BLとの間に設けられている。

【0022】

各ビット線BLは第1の方向Xに延び、各ワード線WLは第2の方向Yに延びている。第1の方向Xと第2の方向Yとは交差し、図2においては例えば直交している。複数の積層体10が2次元方向(XY方向)に例えばマトリクス状に配列され、さらに、そのマトリクス状のアレイが、XY平面に対して直交するZ方向に複数積層されている。図2は、例えば、3行×3列のアレイが4層分積層された部分を表す。

【0023】

各ワード線WLは、上下の積層体10間で共有されている。同様に、各ビット線BLは、上下の積層体10間で共有されている。この構造は、レイヤー数の低減による低コスト化を図れる。

【0024】

あるいは、ワード線WL/積層体10/ビット線BL/層間絶縁膜/ワード線WL/積層体10/ビット線BLを繰り返した構造であってもよい。この構造は、一つの配線(ビット線BLまたはワード線WL)に接続するメモリセルの数を低減でき、高速動作に適している。

【0025】

図3に、積層体10の断面構造を表す。図3は、図2における1層分のアレイのYZ断面に対応する。

【0026】

積層体10は、ビット線BLとワード線WLとの間に直列接続されたメモリセル20と非オーミック素子14とを有する。

【0027】

メモリセル20は、上部電極13と、下部電極11と、これら上部電極13と下部電極11との間に設けられた抵抗変化膜12とを有する。

【0028】

抵抗変化膜12は、電圧、電流、熱、化学エネルギー等で、相対的に抵抗が低い状態(セット状態)と抵抗が高い状態(リセット状態)とをスイッチング可能で、データを不揮発に記憶する。

【0029】

非オーミック素子14として、例えば、PN接合ダイオード、PIN(P-Intrinsic-N)ダイオード、ショットキーダイオード等の各種ダイオード、あるいは、MIM(Metal-Insulator-Metal)素子、SIS(Silicon-Insulator-Silicon)素子などを用いることができる。

【0030】

非オーミック素子14としてダイオードを使用する場合、メモリセル20のユニポーラ動作が可能である。すなわち、抵抗変化膜12に印加する電圧の大きさや印加時間の制御により、抵抗変化膜12の抵抗状態を変化させることができる。

【0031】

また、非オーミック素子14として、MIM素子、SIS素子等を使用する場合、メモリセル20のバイポーラ動作が可能である。すなわち、抵抗変化膜12に印加する電圧の極性を変えることで、抵抗変化膜12の抵抗状態を変化させることができる。

【0032】

メモリセル20における下部電極11及び上部電極13は、バリアメタルや接着層としての機能も担うことが可能で、例えば、Pt、Au、Ag、TiAlN、SrRuO、Ru、RuN、Ir、Co、Ti、TiN、TaN、LaNiO、Al、PtIrOx、PtRhOx、Rh、TaAlNなどを用いることができる。また、非オーミック素子14とワード線WLとの間に設けられた層15は、バリアメタルや接着層として機能し、例えば、Ti、TiNなどを用いることができる。

【0033】

ビット線BLおよびワード線WLとしては、耐熱性に優れ、かつ、低抵抗材料が望ましく、例えば、W、WSi、NiSi、CoSiなどを用いることができる。

【0034】

抵抗変化膜12は、相対的に抵抗が異なる少なくとも2つの状態に、例えば電気的に切り替え可能である。相対的に抵抗が低い状態をセット状態とし、セット状態よりも抵抗が高い状態をリセット状態とする。

【0035】

低抵抗状態(セット状態)の抵抗変化膜12にリセット電圧が印加されると、抵抗変化膜12は高抵抗状態(リセット状態)に切り替わることができる。高抵抗状態(リセット状態)の抵抗変化膜12に、リセット電圧よりも高い、もしくはリセット電圧と極性が異なるセット電圧が印加されると、抵抗変化膜12は低抵抗状態(セット状態)に切り替わることができる。

【0036】

図4は、メモリセルアレイ1における、ある一層分の一部の模式平面図である。

【0037】

メモリセルアレイ1の各レイヤーは、複数のセルアレイブロック50に分けられている。複数のセルアレイブロック50は、ビット線BLが延びる方向である第1の方向Xと、ワード線WLが延びる方向である第2の方向Yに、例えばマトリクス状に配列されている。

【0038】

各ビット線BLは、第1の方向Xに配列されたすべてのセルアレイブロック50間をつないではいない。同様に、各ワード線WLは、第2の方向Yに配列されたすべてのセルアレイブロック50間をつないではいない。これにより、配線長の増大を抑え、ビット線BLやワード線WLにおける電圧降下(IRドロップ)や、非選択メモリセルからのリーク電流を抑制することができる。

【0039】

ただし、各ビット線BLは、個々のセルアレイブロック50単位では分断されてはおらず、第1の方向Xで隣接する例えば2つのセルアレイブロック50間で共有されている。同様に、各ワード線WLは、個々のセルアレイブロック50単位では分断されてはおらず、第2の方向Yで隣接する例えば2つのセルアレイブロック50間で共有されている。これにより、チップ面積の増大を抑制できる。

【0040】

図4の第1の方向Xにおいて、例えば上2つのセルアレイブロック50間で共有するビット線BLと、下2つのセルアレイブロック50間で共有するビット線BLとは、第2の方向Yに交互に配列されている。

【0041】

図4の第2の方向Yにおいて、例えば左2つのセルアレイブロック50間で共有するワード線WLと、右2つのセルアレイブロック50間で共有するワード線WLとは、第1の方向Xに交互に配列されている。

【0042】

次に、メモリセルの例えば書き込み動作(セット動作)について説明する。

【0043】

動作対象(書き込み)対象のメモリセルを選択メモリセル(単に選択セルともいう)とし、選択セル以外のメモリセルを非選択メモリセル(単に非選択セルともいう)とする。また、選択セルに接続されているビット線BLを選択ビット線とし、選択ビット線以外のビット線BLを非選択ビット線とする。選択セルに接続されているワード線WLを選択ワード線とし、選択ワード線以外のワード線WLを非選択ワード線とする。

【0044】

以下に説明する動作において、選択ビット線及び非選択ビット線の電位は、図1に示すカラム制御回路2によって制御され、選択ワード線及び非選択ワード線の電位は、図1に示すロウ制御回路3によって制御される。

【0045】

(第1実施形態)

図5は、半導体記憶装置の動作の第1実施形態を説明するための模式平面図である。

【0046】

図5において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。選択セル20aは、選択ビット線B01と、選択ワード線W01とのクロスポイントに設けられている。

【0047】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図5には、選択セルアレイブロック50aに対して第1の方向Xで隣接する例えば2つの隣接セルアレイブロック50b、50cを表す。隣接セルアレイブロック50bは、選択セルアレイブロック50aに対して図5において下で隣接している。隣接セルアレイブロック50cは、選択セルアレイブロック50aに対して図5において上で隣接している。

【0048】

選択セルアレイブロック50aと隣接セルアレイブロック50cとの間で共有されたビット線BLと、選択セルアレイブロック50aと隣接セルアレイブロック50bとの間で共有されたビット線BLとは、例えば第2の方向Yに交互に配列されている。

【0049】

選択ビット線B01には0ボルトの電位が与えられ、選択ワード線W01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0050】

このとき、非選択ビット線及び非選択ワード線には、0ボルトよりも高く第1の電位VPGMよりも低い第2の電位(例えば、VPGM/2)が与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0051】

ここで、隣接するセルアレイブロック間でビット線を共有している構造の場合、以下に説明する問題が懸念される。

【0052】

例えば、図5において、選択セルアレイブロック50aと選択ビット線B01を共有している隣接セルアレイブロック50bにおける、選択ビット線B01とこれに隣接する非選択ビット線B11との間の配線間容量、または選択ビット線B01とこれに隣接する非選択ビット線B12との間の配線間容量が、書き込み動作に影響を与える場合がある。すなわち、選択セル20aの抵抗変化膜12が低抵抗状態(セット状態)になり、抵抗が低くなると、上記配線間容量に充電された電荷が瞬間的に選択セル20aの抵抗変化膜12に流れてしまう。

【0053】

そこで、実施形態によれば、非選択ビット線の制御系統を2系統設け、選択ビット線B01に他ブロックで隣接する非選択ビット線B11及びB12は、他の非選択ビット線とは独立して制御する。

【0054】

具体的には、上記書き込み動作時、非選択ビット線B11及びB12を、選択ビット線B01と同じ0ボルトにする。すなわち、他の非選択ビット線は、書き込み動作時、第2の電位に上昇されるのに対して、非選択ビット線B11及びB12は、選択ビット線B01とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0055】

隣接セルアレイブロック50bで、隣接する選択ビット線B01、非選択ビット線B11及びB12(図5において太線で表すビット線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0056】

隣接セルアレイブロック50bのワード線WLはすべて非選択であり、第2の電位(VPGM/2)が与えられる。そのため、隣接セルアレイブロック50bにおける、非選択ビット線B11及びB12に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0057】

なお、非選択ビット線B11及びB12は、選択ビット線B01と同電位(0ボルト)にすることに限らず、選択ビット線B01との電位差が、他の非選択ビット線と選択ビット線B01との間の電位差(VPGM/2)よりも小さければ、上記配線間容量による過渡的な電流の抑制効果が得られる。すなわち、非選択ビット線B11及びB12には、0ボルト以上で上記第2の電位(VPGM/2)よりも低い第3の電位を与えることができる。

【0058】

非選択ビット線B11及びB12を0ボルトにすると、隣接セルアレイブロック50bにおける非選択ビット線B11またはB12と、非選択ワード線との間の非選択セルに(VPGM/2)の電圧がかかる。

【0059】

一方、非選択ビット線B11及びB12に0ボルトより高い電位(ただし、(VPGM/2)より低い電位)を与えると、隣接セルアレイブロック50bにおける非選択ビット線B11またはB12と、非選択ワード線との間の非選択セルには(VPGM/2)よりも小さい電圧がかかる。このため、その非選択セルの誤セット動作防止の確実性を高くできる。

【0060】

(第2実施形態)

図6は、半導体記憶装置の動作の第2実施形態を説明するための模式平面図である。

【0061】

第2実施形態では、複数の選択セル20aを同時に選択し、並列動作させる。図6において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。

【0062】

選択セル20aは、選択ビット線B01と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B02と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B03と選択ワード線W01とのクロスポイントに設けられている。また、選択セル20aは、選択ビット線B04と選択ワード線W01とのクロスポイントに設けられている。

【0063】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図6には、選択セルアレイブロック50aに対して第1の方向Xで隣接する例えば2つの隣接セルアレイブロック50b、50cを表す。隣接セルアレイブロック50bは、選択セルアレイブロック50aに対して図6において下で隣接している。隣接セルアレイブロック50cは、選択セルアレイブロック50aに対して図6において上で隣接している。

【0064】

選択セルアレイブロック50aと隣接セルアレイブロック50cとの間で共有されたビット線BLと、選択セルアレイブロック50aと隣接セルアレイブロック50bとの間で共有されたビット線BLとは、例えば第2の方向Yに交互に配列されている。

【0065】

選択ビット線B01、B02、B03及びB04には0ボルトの電位が与えられ、選択ワード線W01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0066】

このとき、非選択ビット線及び非選択ワード線には、0ボルトよりも高く第1の電位VPGMよりも低い第2の電位(例えば、VPGM/2)が与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0067】

ただし、第2実施形態においても、第1実施形態と同様、選択ビット線B01、B02、B03及びB04に対して他ブロックで隣接する非選択ビット線B11、B12、B13、B14及びB15は、他の非選択ビット線とは独立して制御する。すなわち、第2実施形態によれば、非選択ビット線の制御系統を2系統設けている。

【0068】

具体的には、上記書き込み動作時、非選択ビット線B11、B12、B13、B14及びB15を、選択ビット線B01、B02、B03及びB04と同じ0ボルトにする。すなわち、他の非選択ビット線は、書き込み動作時、第2の電位に上昇されるのに対して、非選択ビット線B11、B12、B13、B14及びB15は、選択ビット線B01、B02、B03及びB04とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0069】

隣接セルアレイブロック50bで、隣接する選択ビット線B01、B02、B03及びB04と、非選択ビット線B11、B12、B13、B14及びB15(図6において太線で表すビット線)との電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0070】

隣接セルアレイブロック50bのワード線WLはすべて非選択であり、第2の電位(VPGM/2)が与えられる。そのため、隣接セルアレイブロック50bにおける、非選択ビット線B11、B12、B13、B14及びB15に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0071】

なお、第2実施形態においても、非選択ビット線B11、B12、B13、B14及びB15は、選択ビット線B01、B02、B03及びB04と同電位(0ボルト)にすることに限らず、0ボルト以上で上記第2の電位(VPGM/2)よりも低い第3の電位に制御すれば、上記配線間容量による過渡的な電流の抑制効果が得られる。

【0072】

(第3実施形態)

図7は、半導体記憶装置の動作の第3実施形態を説明するための模式平面図である。

【0073】

図7において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。選択セル20aは、選択ビット線B01と、選択ワード線W01とのクロスポイントに設けられている。

【0074】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図7には、選択セルアレイブロック50aに対して第2の方向Yで隣接する隣接セルアレイブロック50bを表す。

【0075】

前述した第1及び第2実施形態は、抵抗変化膜12に対して逆極性の電圧をかけることで抵抗状態を変化させるいわゆるバイポーラ動作に適用される。これに対して、第3実施形態は、抵抗変化膜12に対する印加電圧の大きさや印加時間の制御により、抵抗変化膜12の抵抗状態を変化させるいわゆるユニポーラ動作に適用される。

【0076】

このユニポーラ動作においては、選択ワード線W01には0ボルトの電位が与えられ、選択ビット線B01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0077】

このとき、非選択ビット線には0ボルトが与えられ、非選択ワード線には上記第1の電位VPGMが与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0078】

ただし、第3実施形態においては、非選択ワード線の制御系統を2系統設け、選択ワード線W01に対して他ブロックで隣接する非選択ワード線W11及びW12は、他の非選択ワード線とは独立して制御する。

【0079】

具体的には、上記書き込み動作時、非選択ワード線W11及びW12を、選択ワード線W01と同じ0ボルトにする。すなわち、他の非選択ワード線は、書き込み動作時、第1の電位に上昇されるのに対して、非選択ワード線W11及びW12は、選択ワード線W01とともに、電位が上昇されず、書き込み動作時あるいは書き込み動作の前後で0ボルトに保持される。

【0080】

隣接セルアレイブロック50bで、隣接する選択ワード線W01、非選択ワード線W11及びW12(図7において太線で表すワード線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0081】

隣接セルアレイブロック50bのビット線BLはすべて非選択であり、0ボルトである。そのため、隣接セルアレイブロック50bにおける、非選択ワード線W11及びW12に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0082】

(第4実施形態)

図8は、半導体記憶装置の動作の第4実施形態を説明するための模式平面図である。

【0083】

第4実施形態では、複数の選択セル20aを同時に選択し、並列動作させる。図8において、書き込み対象(セット動作対象)の選択セル20aを模式的に黒丸で表す。

【0084】

選択セル20aは、選択ワード線W01と、選択ビット線B01とのクロスポイントに設けられている。また、選択セル20aは、選択ワード線W02と、選択ビット線B01とのクロスポイントに設けられている。また、選択セル20aは、選択ワード線W03と、選択ビット線B01とのクロスポイントに設けられている。

【0085】

選択セル20aを含むセルアレイブロックを、選択セルアレイブロック50aとする。また、図8には、選択セルアレイブロック50aに対して第2の方向Yで隣接する隣接セルアレイブロック50bを表す。

【0086】

第4実施形態もユニポーラ動作に適用される。このユニポーラ動作においては、選択ワード線W01、W02及びW03には0ボルトの電位が与えられ、選択ビット線B01には、0ボルトよりも高い正電位である第1の電位VPGMが与えられる。これにより、選択セル20aの抵抗変化膜12は、高抵抗状態(リセット状態)から低抵抗状態(セット状態)に変化させられる。

【0087】

このとき、非選択ビット線には0ボルトが与えられ、非選択ワード線には上記第1の電位VPGMが与えられ、ダイオードなどの非オーミック素子14の整流性によって、非選択セルの抵抗変化膜12には動作電圧が印加されない。したがって、非選択セルに対する書き込み動作(セット動作)は行われない。

【0088】

ただし、第4実施形態においても、第3実施形態と同様、非選択ワード線の制御系統を2系統設け、選択ワード線W01、W02及びW03に対して他ブロックで隣接する非選択ワード線W11、W12、W13及びW14は、他の非選択ワード線とは独立して制御する。

【0089】

具体的には、上記書き込み動作時、非選択ワード線W11、W12、W13及びW14を、選択ワード線W01、W02及びW03と同じ0ボルトにする。すなわち、他の非選択ワード線は、書き込み動作時、第1の電位に上昇されるのに対して、非選択ワード線W11、W12、W13及びW14は、選択ワード線W01、W02及びW03とともに、電位が上昇されず、書き込み時あるいは書き込み動作の前後で0ボルトに保持される。

【0090】

隣接セルアレイブロック50bで、隣接する選択ワード線W01、W02及びW03、非選択ワード線W11、W12、W13及びW14(図8において太線で表すワード線)の電位を同電位にすることで、それらの配線間容量を抑制することができる。この結果、書き込み動作時に選択セル20aに瞬間的に過剰電流が流れるのを防ぐことができる。これにより、スイッチング耐久性を向上させ、書き込み可能回数の低減を抑制し、信頼性の高い半導体記憶装置を提供することができる。

【0091】

隣接セルアレイブロック50bのビット線BLはすべて非選択であり、0ボルトである。そのため、隣接セルアレイブロック50bにおける、非選択ワード線W11、W12、W13及びW14に接続された非選択セルに対する書き込み動作(セット動作)は行われない。

【0092】

前述した実施形態は、選択セルに対する書き込み動作(セット動作)時に限らず、消去動作(リセット動作)時にも適用可能である。

【0093】

例えば、図5に示すバイポーラ動作において、消去動作時は、選択ビット線B01に第1の電位VPGMを与え、選択ワード線W01を0ボルトにする。

【0094】

このとき、図7を参照して説明した動作と同様の動作を適用できる。すなわち、選択ワード線W01の電位と、隣接セルアレイブロック50bにおける選択ワード線W01に隣接する非選択ワード線W11及びW12の電位を上昇させずに0ボルトに保持することにより、それらの配線間容量を抑制し、選択セル20aに配線間容量から過渡的に電流が流れるのを防ぐことができる。

【0095】

なお、抵抗変化膜が高抵抗状態から低抵抗状態になる動作を消去動作、低抵抗状態から高抵抗状態になる動作を書き込み動作とする場合もある。

【0096】

いずれにしても、抵抗変化膜が低抵抗状態から高抵抗状態に変化するときよりも、高抵抗状態から低抵抗状態に変化して選択セルの抵抗が低くなったときに、配線間容量の電荷が選択セルに流れやすく、選択セルの動作が大きな影響を受けやすい。

【0097】

したがって、選択セルの抵抗変化膜を高抵抗状態から低抵抗状態に変化させるときに、選択配線(選択ビット線または選択ワード線)、および隣接セルアレイブロックにおける選択配線に隣接する非選択配線(非選択ビット線または非選択ワード線)の電位を0ボルトもしくは上記第3の電位に制御すると有効である。

【0098】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0099】

1…メモリセルアレイ、10…積層体、12…抵抗変化膜、20…メモリセル、20a…選択メモリセル、50…セルアレイブロック、50a…選択セルアレイブロック、50b,50c…隣接セルアレイブロック、BL…ビット線、B01,B02,B03,B04…選択ビット線、WL…ワード線、W01,W02,W03…選択ワード線

【特許請求の範囲】

【請求項1】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルトを与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を相対的に高抵抗状態から低抵抗状態に変化させる制御回路と、

を備え、

前記選択ビット線、および前記隣接セルアレイブロックにおける前記選択ビット線に隣接する前記非選択ビット線は、前記抵抗変化膜の前記抵抗状態の変化の前後で0ボルトに保持される半導体記憶装置。

【請求項2】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる制御回路と、

を備えた半導体記憶装置。

【請求項3】

前記選択ビット線、および前記隣接セルアレイブロックにおける前記選択ビット線に隣接する前記非選択ビット線は、前記抵抗変化膜の前記抵抗状態の変化の前後で0ボルトに保持される請求項2記載の半導体記憶装置。

【請求項4】

0ボルトの前記選択ビット線と、前記第1の電位が与えられた前記選択ワード線との間に接続された前記選択メモリセルにおける前記抵抗変化膜は、相対的に高抵抗状態から低抵抗状態に変化させられる請求項2記載の半導体記憶装置。

【請求項5】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第2の方向で隣接するセルアレイブロック間で前記ワード線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線に第1の電位を与え、前記選択メモリセルに接続された選択ワード線を0ボルトにし、前記選択ビット線以外の非選択ビット線を0ボルトにし、前記選択メモリセルを含む選択セルアレイブロックに前記第2の方向で隣接し前記選択ワード線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ワード線に隣接する非選択ワード線を0ボルトにし、前記0ボルトにされた非選択ワード線以外の他の非選択ワード線に前記第1の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる制御回路と、

を備えた半導体記憶装置。

【請求項6】

0ボルトの前記選択ワード線と、前記第1の電位が与えられた前記選択ビット線との間に接続された前記選択メモリセルにおける前記抵抗変化膜は、相対的に高抵抗状態から低抵抗状態に変化させられる請求項5記載の半導体記憶装置。

【請求項1】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルトを与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を相対的に高抵抗状態から低抵抗状態に変化させる制御回路と、

を備え、

前記選択ビット線、および前記隣接セルアレイブロックにおける前記選択ビット線に隣接する前記非選択ビット線は、前記抵抗変化膜の前記抵抗状態の変化の前後で0ボルトに保持される半導体記憶装置。

【請求項2】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第1の方向で隣接するセルアレイブロック間で前記ビット線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線を0ボルトにし、前記選択メモリセルに接続された選択ワード線に0ボルトよりも高い第1の電位を与え、前記選択ワード線以外の非選択ワード線に0ボルトよりも高く前記第1の電位よりも低い第2の電位を与え、前記選択メモリセルを含む選択セルアレイブロックに前記第1の方向で隣接し前記選択ビット線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ビット線に隣接する非選択ビット線に0ボルト以上で前記第2の電位よりも低い第3の電位を与え、前記第3の電位が与えられた非選択ビット線以外の他の非選択ビット線に前記第2の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる制御回路と、

を備えた半導体記憶装置。

【請求項3】

前記選択ビット線、および前記隣接セルアレイブロックにおける前記選択ビット線に隣接する前記非選択ビット線は、前記抵抗変化膜の前記抵抗状態の変化の前後で0ボルトに保持される請求項2記載の半導体記憶装置。

【請求項4】

0ボルトの前記選択ビット線と、前記第1の電位が与えられた前記選択ワード線との間に接続された前記選択メモリセルにおける前記抵抗変化膜は、相対的に高抵抗状態から低抵抗状態に変化させられる請求項2記載の半導体記憶装置。

【請求項5】

第1の方向に延びる複数のビット線と、前記第1の方向に対して交差する第2の方向に延びる複数のワード線と、前記ビット線と前記ワード線との交差部で前記ビット線と前記ワード線との間に設けられ、抵抗変化膜を含む複数のメモリセルと、をそれぞれが有する複数のセルアレイブロックであって、前記第2の方向で隣接するセルアレイブロック間で前記ワード線を共有している複数のセルアレイブロックと、

前記複数のメモリセルの中から選択された選択メモリセルに接続された選択ビット線に第1の電位を与え、前記選択メモリセルに接続された選択ワード線を0ボルトにし、前記選択ビット線以外の非選択ビット線を0ボルトにし、前記選択メモリセルを含む選択セルアレイブロックに前記第2の方向で隣接し前記選択ワード線を前記選択セルアレイブロックと共有する隣接セルアレイブロックにおける、前記選択ワード線に隣接する非選択ワード線を0ボルトにし、前記0ボルトにされた非選択ワード線以外の他の非選択ワード線に前記第1の電位を与えて、前記選択メモリセルの前記抵抗変化膜の抵抗状態を変化させる制御回路と、

を備えた半導体記憶装置。

【請求項6】

0ボルトの前記選択ワード線と、前記第1の電位が与えられた前記選択ビット線との間に接続された前記選択メモリセルにおける前記抵抗変化膜は、相対的に高抵抗状態から低抵抗状態に変化させられる請求項5記載の半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−109796(P2013−109796A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−252371(P2011−252371)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]