半導体記憶装置

【課題】マーチパターンテストではアドレスデコーダの配線の遅延を検知できない。

【解決手段】半導体記憶装置のアドレスデコーダは,アドレスサイクルの第1のタイミングで,複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,アドレスレジスタと内部アドレス信号線網の間に設けられ,アドレスレジスタが出力した第1と第2の内部アドレス信号を,アドレスサイクルの第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,内部アドレス信号線網を介して複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれのワード線又はビット線を選択する複数のアドレスデコード回路とを有する。

【解決手段】半導体記憶装置のアドレスデコーダは,アドレスサイクルの第1のタイミングで,複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,アドレスレジスタと内部アドレス信号線網の間に設けられ,アドレスレジスタが出力した第1と第2の内部アドレス信号を,アドレスサイクルの第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,内部アドレス信号線網を介して複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれのワード線又はビット線を選択する複数のアドレスデコード回路とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置におけるアドレスデコーダでは,配線などにオープン不良が存在すると,異なるアドレスで同じメモリセルが選択される等不具合が発生する。

【0003】

アドレスデコーダの故障検出では,一般的にアドレスをインクリメントまたはデクリメントさせるマーチパターンで変化させながらデータの書き込みと読み出しを繰り返すテストが行われる。例えば,3ビットのアドレス信号線を有するメモリでは,アドレスをインクリメントする場合,アドレス信号は000(0番地)から111(7番地)まで順に与えられる。マーチパターンによるテストでは,アドレスを順にインクリメントもしくはデクリメントし,所望のメモリセルに書き込んだデータが正常に読み出せるかどうかを確認する。なお,このような不具合を検知する装置として特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭56−148789号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

また,オープン不良のように配線が断線しているのではなく,製造時のプロセスばらつき等に起因して配線に形状のばらつきがある場合,アドレスデコーダの出力となるワード線の駆動に遅延が生じ,読み出し時間が遅延し要求されるアクセスタイムを実現できず不具合となる。

【0006】

しかし,アドレスデコーダに配線形状ばらつき等による遅延が存在する場合,マーチパターンによるテストでは,アドレスがインクリメントまたはデクリメントされてもあるアドレス信号はHレベル又はLレベルから変化しないケースがあるため,アドレス配線の遅延を検知することができない。マーチパターンの代わりに,アドレス配線の遅延を検知できる他のテストパターンを使用するとテスト工数が増加してしまう。

【0007】

そこで,本発明の目的は,アドレス配線の遅延による不良を検出できる半導体記憶装置を提供することとする。

【課題を解決するための手段】

【0008】

半導体記憶装置の第1の側面は,

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【発明の効果】

【0009】

半導体記憶装置の第1の側面によれば,アドレス配線の遅延による不良を検出できる。

【図面の簡単な説明】

【0010】

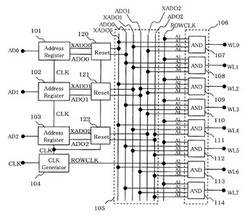

【図1】アドレスデコーダを示す図である。

【図2】図1のアドレスデコーダに6番地の入力アドレス信号を供給した場合の信号波形を示す図である。

【図3】図1のアドレスデコーダの配線に遅延が生じた場合の信号波形を示す図である。

【図4】アドレスデコーダに対するマーチパターンのテストにおける信号波形を示す図である。

【図5】アドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【図6】第1の実施の形態におけるアドレスデコーダを示す図である。

【図7】第1の実施の形態におけるリセット回路を示す図である。

【図8】第1の実施の形態におけるアドレスデコード回路を示す図である。

【図9】第1の実施の形態における内部アドレス信号の波形を示す図である。

【図10】第1の実施の形態における実施の形態におけるアドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【図11】第2の実施の形態におけるSRAMの構成図である。

【図12】第2の実施の形態におけるクロックバッファ,アドレスレジスタ,アウトプットデータバッファを示す図である。

【図13】第2の実施の形態におけるリセット回路を示す図である。

【図14】第2の実施の形態における通常モード時の内部アドレス信号の波形を示す図である。

【図15】第2の実施の形態におけるテストモード時の内部アドレス信号の波形を示す図である。

【図16】第2の実施の形態におけるテストモード時,かつアドレス配線遅延が存在する時の内部アドレス信号の波形を示す図である。

【発明を実施するための形態】

【0011】

以下,図面を用いて本発明の実施の形態について説明する。

【0012】

図1は,アドレスデコーダを示す図である。図1のアドレスデコーダは,3ビットの入力アドレス信号をデコードするための回路であり,アドレスレジスタ101,102,103と,外部クロック信号CLKからロウクロック信号ROWCLKを生成するクロックジェネレータ104と,内部アドレス信号線網105と,アドレスデコード回路群106とを有する。

【0013】

また,アドレスレジスタ101は最下位ビットの入力アドレス信号AD0を供給され,クロック信号CLKに応答して,入力アドレス信号AD0と同相の内部アドレス信号ADO0と,内部アドレス信号線ADO0を反転した逆相の内部アドレス信号線XADO0を出力する。同様に,アドレスレジスタ102,103は2ビット目の入力アドレス信号AD1,最上位ビットの入力アドレス信号AD2をそれぞれ供給され,クロック信号CLKに応答して,互いに論理が反転した内部アドレス信号ADO1,XADO1,ADO2,XADO2を出力する。

【0014】

例えば,6番地の入力アドレス信号,すなわちLレベルのAD0,HレベルのAD1,AD2がアドレスレジスタ101〜103に供給された場合,内部アドレス信号ADO0はLレベル,XADO0はHレベル,ADO1はHレベル,XADO1はLレベル,ADO2はHレベル,XADO2はLレベルとなる。

【0015】

内部アドレス信号線網は,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2にそれぞれ対応した内部アドレス信号線を有する。

【0016】

アドレスデコード回路群106は,0番地から7番地までの各アドレスに対応したアドレスデコード回路107〜114を有しており,各アドレスデコード回路には,ロウクロック信号ROWCLK用のクロック配線A1と内部アドレス信号線A2〜A4を介して,アドレスに応じた内部アドレス信号が供給されて論理積演算を行い,選択されたワード線WL0〜WL7に駆動信号を出力する。例えば,0番地用のアドレスデコード回路107は,クロック配線A1を介してロウクロック信号ROWCLK,内部アドレス信号線A2を介して内部アドレス信号XADO0,内部アドレス信号線A3を介して内部アドレス信号XADO1,内部アドレス信号線A4を介してXADO2を供給されて,それらの内部アドレス信号が全てHの場合にワード線WL0を選択して駆動する。

【0017】

図2は,図1のアドレスデコーダに6番地の入力アドレス信号を供給した場合の信号波形を示す図である。図2では,図1のアドレスデコーダにおいて,1番地のアドレスからサイクルC1で6番地,サイクルC2で1番地のアドレスに順に変更した場合における,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2と,アドレスデコード回路113のクロック配線A1および内部アドレス信号線A2〜A4の入力信号AND113_A1〜AND113_A4と,ワード線WL6の信号波形を記載している。なお,図1に示すように,クロック配線A1および内部アドレス信号線A2〜A4は,ロウクロック信号ROWCLK,と内部アドレス信号XADO0,ADO1,ADO2をそれぞれ供給されている。

【0018】

サイクルC1で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,クロック信号CLKに応答して,時間ta〜ta+Δtの間でHレベルとなる。また,時間Taにおけるクロック信号CLKの立ち上がりに応答して,アドレスレジスタが内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2を時間taで立ち上げる。

【0019】

さらにロウクロック信号ROWCLKの立ち上がりに応答して,アドレスデコード回路113の入力信号AND113_A1〜AND113_A4が立ち上がる。入力信号AND113_A1〜AND113_A4の立ち上がりに応答して,アドレスデコード回路113は各信号の論理積をとり,時間taでワード線WL6を駆動する。そして,時間Taから所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力される。なお,アクセスタイムとは,クロック信号CLKが立ち上がってから,メモリのデータが出力されるまでの時間を意味する。

【0020】

ここで,もし図1のアドレスデコーダの配線に形状ばらつき等による遅延が生じた場合,各信号の波形は図2ではなく図3のようになる。図3は,図1のアドレスデコーダの配線に遅延が生じた場合の信号波形を示す図である。アドレスデコード回路113の内部アドレス信号線A4に遅延が存在すると,図3のように入力信号AND113_A4とワード線WL6の立ち上がりタイミングに遅延が生じる。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となってしまう。そのため,仕様通りのアクセスタイムAT60を実現するためには,テスト段階において,このようなアドレス配線の遅延を検出することが必要である。

【0021】

次に,図1のアドレスデコーダに対して,アドレスをインクリメントさせるマーチパターンでテストを行う場合について述べる。図4は,アドレスデコーダに対するマーチパターンのテストにおける信号波形を示す図である。また,図5は,アドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【0022】

図4では,サイクルC0〜C7の各タイミングでアドレスを0番地から7番地まで順にインクリメントしており,入力アドレス信号AD0〜AD2に応じた内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2の波形をクロック信号CLKとともに記載している。マーチパターンのテストでは,アドレスを変更しても論理レベルが変動しない信号が存在する。例えば,内部アドレス信号ADO2は,サイクルC4の4番地のテストを行うまではLレベルであったが,4番地の入力アドレス信号をアドレスレジスタ101〜103に供給しクロック信号CLKが立ち上がった以降はHレベルである。

【0023】

このマーチパターンのテストにおいて,図3の場合と同じようにアドレスデコード回路113の内部アドレス信号線A4に遅延が存在すると,アドレスデコード回路113の入力信号AND113_A1〜AND113_A4の波形は,図5のようになる。図5は,図4のマーチパターンのテストにおいて,アドレスを5番地から6番地へインクリメントしたときの各波形を示している。

【0024】

サイクルC6で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6〜t6+Δtの間でHレベルとなる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XADO0,ADO1がHレベルとなり,ADO0,XADO1がLレベルとなる。内部アドレス信号ADO2,XADO2は,5番地から6番地にアドレスが変更されても入力アドレス信号AD2に変化がないため,それぞれHレベル,Lレベルのままである。そのため,ロウクロック信号ROWCLKの立ち上がりに応答して,入力信号AND113_A1,AND113_A2,AND113_A3は立ち上がるが,AND113_A4はHレベルのままである。

【0025】

図3では,アドレスを1番地から6番地に変更すると内部アドレス信号ADO2がLレベルからHレベルになるため入力信号AND113_A4の立ち上がりの遅延を検出できているが,図5では,アドレスを5番地から6番地に変更しても内部アドレス信号ADO2がHレベルのままとなっているために,6番地の入力アドレス信号をアドレスレジスタ101〜103に供給しても入力信号AND113_A4の立ち上がり遅延を検出できていない。そのため,ワード線WL6は遅延することなく時間t6で駆動され,アクセスタイムはAT60となる。

【0026】

このようにマーチパターンでは,入力アドレス信号の論理レベルがアドレスの変更前後で変化しない場合があるために,図5のように内部アドレス信号線の遅延が検出されないことが発生する。この遅延を検出できるように,マーチパターンの替わりに,任意のアドレスを基準にして他の全番地にアクセスするギャロッピングパターンや,図3のようなアドレスを反転させるテストパターン等の他のテストパターンを使ってテストを行うと,テスト内容が複雑になるだけでなくテスト工数が増加するため望ましくない。

【0027】

[第1の実施の形態]

そこで,第1の実施の形態では,内部アドレス信号線の遅延を検出できるように,アドレスサイクル毎に入力アドレス信号に応じてHレベル又はLレベルになった内部アドレス信号を一方の論理レベルにリセットする。具体的には,アドレスサイクルを制御するクロック信号CLKの第1のエッジ(例えば立ち上がりエッジ)に応答して,入力アドレス信号に応じてHレベルにされた内部アドレス信号を,クロック信号CLKの第2のエッジ(例えば立ち下がりエッジ)に応答してLレベルにリセットする。

【0028】

図6は,第1の実施の形態におけるアドレスデコーダを示す図である。図6のアドレスデコーダは,アドレスレジスタ101〜103と内部アドレス信号線網105との間に,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2を,クロック信号CLKの立ち下がりに応答してLレベルにリセットするリセット回路120〜122を有する。アドレスレジスタ101〜103で生成された内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2は,各リセット回路120〜122によりクロック信号CLKの立ち下がりに応答してLレベルにリセットされ,内部アドレス信号線網105の各信号線も同様にLレベルにリセットされる。

【0029】

図7は,第1の実施の形態におけるリセット回路を示す図である。なお,図7は,例として図6のアドレスデコーダにおけるリセット回路120の回路図を記載しており,(1)と(2)の2通りの回路図を示している。

【0030】

図7(1)の回路図は,NANDゲート701,703とインバータ702,704とを有するリセット回路120を示している。例えば,クロック信号CLKの立ち上がりに応答してアドレスレジスタ101で生成された内部アドレス信号ADO,XADOがそれぞれHレベル,LレベルでNANDゲート701,703に入力された場合,クロック信号CLKがHレベルの間は,インバータ702,704は内部アドレス信号のHレベル,Lレベルをそのまま出力する。しかし,クロック信号CLKがLレベルになると,インバータ702から出力される内部アドレス信号はLレベルとなり,内部アドレス信号ADOはHレベルからLレベルにリセットされる。インバータ704の出力は,内部アドレス信号XADO0がLレベルであったため,クロック信号CLKの立ち下がり後もLレベルを維持する。

【0031】

図7(2)の回路図は,インバータ705と,CMOSトランスファゲート706,707とNMOSトランジスタ708,709とを有するリセット回路120を示している。例として,クロック信号CLKの立ち上がりに応答してアドレスレジスタ101で生成された内部アドレス信号ADO,XADOがそれぞれHレベル,LレベルでNANDゲート701,703に入力された場合について説明する。まず,クロック信号CLKの立ち上がり後のHレベルの間は,CMOSトランスファゲート706,707はともにONとなり,NMOSトランジスタ708,709はともにOFFとなるため,リセット回路は内部アドレス信号ADO,XADOのHレベル,Lレベルをそのまま出力する。クロック信号CLKがLレベルになると,CMOSトランスファゲート706,707はOFFとなり,NMOSトランジスタ708,709はともにONとなるため,内部アドレス信号ADOはHレベルからLレベルにリセットされ,内部アドレス信号XADO0はLレベルを維持する。

【0032】

図8は,第1の実施の形態におけるアドレスデコード回路を示す図である。図8のアドレスデコード回路は図6のアドレスデコード回路107〜114に該当する。図8において,アドレスデコード回路は,PMOSトランジスタ801,806と,NMOSトランジスタ802〜805と,インバータ807〜809とを有する。例えば,アドレスデコード回路113では,クロック配線A1および内部アドレス信号線A2〜A4には,ロウクロック信号ROWCLKと内部アドレス信号XADO0,ADO1,ADO2とをそれぞれ供給される。そして,内部アドレス信号線A2〜A4にHレベルの信号が供給されると,クロック配線A1のロウクロック信号ROWCLKがHレベルに立ち上がったタイミングで,NMOSトランジスタ802〜805はONとなり,PMOSトランジスタ801,806はOFFし,その結果インバータ807〜809を介して出力される信号はHレベルとなる。これが選択状態である。内部アドレス信号線A2〜A4のいずれかがLレベルの場合は,ロウクロック信号ROWCLKがHレベルになっても,インバータ809の出力は非選択レベルのLレベルである。

【0033】

図9は,第1の実施の形態における内部アドレス信号の波形を示す図である。なお,図9では,入力アドレス信号AD0〜AD2と,クロック信号CLKと,アドレスレジスタ101〜103及びリセット回路120〜122により生成された内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2とを記載している。また,入力アドレスは図4と同様にマーチパターンにより選択されている。例えば,0番地のアドレスを選択した場合では,クロック信号CLKの立ち上がりに応答して,入力アドレス信号AD0〜AD2に応じてHレベルにされた内部アドレス信号XADO0,XADO1,XADO2は,時間T0+ΔTでクロック信号CLKがHレベルからLレベルに立ち下がったことに応答して,時間L0で全てLレベルにリセットされている。このリセット動作は,アドレスサイクル毎に行われる。したがって,第1,第2の内部アドレス信号のいずれか一方は,アドレスサイクル毎に必ずクロック信号CLKの立ち上がりに応答して,LレベルからHレベルに立ち上がることになる。この立ち上がり動作は,内部アドレス信号線の遅延特性の影響を受けることになる。

【0034】

次に,図5の場合と同じように,図9のアドレスデコーダにおいてアドレスデコード回路113の内部アドレス信号線A4に遅延が存在したときの各波形について,図10を用いて説明する。図10は,第1の実施の形態におけるアドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。図10では,図9における5番地と6番地の入力アドレス信号が入力された場合について,アドレスデコード回路113に入力されるロウクロック信号CLKと内部アドレス信号である入力信号AND113_A1〜AND113_A4と,アドレスデコード回路113から出力されるワード線WL6の駆動信号波形を記載している。なお,アドレスデコード回路113のクロック配線A1および内部アドレス信号線A2〜A4は,ロウクロック信号ROWCLKと内部アドレス信号XADO0,ADO1,ADO2とをそれぞれ供給されている。

【0035】

5番地のアドレスが入力されたとき,そのアドレスサイクル内の時間T5+ΔTでクロック信号CLKの立ち下がりに応答してHレベルだった内部アドレス信号ADO0,XADO1,ADO2はリセットされLレベルになり,XADO0,ADO1,XADO2はLレベルを維持する。そして,サイクルC6で6番地のアドレスが入力されるときは,各内部アドレス信号はLレベルとなっている。この点が,図4のリセット回路を有しないアドレスデコーダの場合の波形(図10中の内部アドレス信号ADO2,AND113_A4の波線)とは異なる。例えば,内部アドレス信号ADO2は,図4では5番地から6番地に入力アドレスが変更されてもHレベルのままであるが,図10では時間T5+ΔTでリセットされて6番地のアドレスが入力されるときはLレベルとなっている。

【0036】

サイクルC6で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6〜t6+Δtの間でHレベルとなる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XADO0,ADO1,ADO2がLレベルからHレベルへ立ち上がる。

【0037】

次に,ロウクロック信号ROWCLKの立ち上がりに応答して,時間t6にアドレスデコード回路113の入力信号AND113_A1〜AND113_A3が立ち上がる。アドレスデコード回路113の内部アドレス信号線A4に遅延が存在するため,入力信号AND113_A4は,時間t6からD1だけ遅れて立ち上がる。そして,アドレスデコード回路113は各信号の論理積演算を行い,時間t6よりD1だけ遅れてワード線WL6に駆動信号を出力する。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となる。なお,この遅延AT61がBIST回路により検出され不良品と判断される。最後に,時間T6+ΔTでクロック信号CLKがLレベルに立ち下がったのに応答して,各内部アドレス信号はLレベルにリセットされ,それに併せて入力信号AND113_A2〜A4もLレベルにリセットされる。

【0038】

以上のように,クロック信号CLKの立ち下がりに応答して内部アドレス信号をリセットすることで,図4の内部アドレス信号ADO2の波形のような,アドレスが変更されてもHレベルが維持されることは発生しなくなる。そのため,マーチパターンによるテストの場合でも,内部アドレス信号線の遅延を検出することが可能となる。

【0039】

また,第1の実施の形態では,図6のようにワード線のアドレスデコード回路群106について内部アドレス信号線遅延を検出したが,同様にしてビット線のアドレスデコード回路についても内部アドレス信号線遅延を検出することが可能である。

【0040】

[第2の実施の形態]

第2の実施の形態は,第1の実施の形態で記載したリセット回路をSRAMに適用した場合の形態である。リセット回路により常に内部アドレス信号のリセット動作を行うと消費電力の増大を招くため,第2の実施の形態ではリセット動作が必要なテストのときにのみリセット動作を行い内部アドレス信号線の不具合を検知できるようにしておき,通常時はリセット動作を行わないようにする。

【0041】

図11は,第2の実施の形態におけるSRAMの構成図である。図11のSRAMは,BIST回路1101と,クロックバッファ1102と,ライトイネーブルレジスタ1103と,アドレスレジスタ1104と,リセット回路1105,1115と,クロックジェネレータ1107と,ロウデコーダバッファ1106と,インプットデータレジスタ1109と,ライトアンプ1110と,コラムデコーダ1108と,コラムセレクタ1111と,複数のメモリセルがマトリックス状に配列されたメモリセルマトリックス1112と,センスアンプ1113と,アウトプットデータレジスタ1114とを有する。

【0042】

上記のSRAMは,例えば大規模なLSIチップ内に埋め込まれる。その場合,SRAMの各入力,出力端子はLSIチップの外部端子として設けられない。そこで,SRAMの動作テストを行うためにBIST(built in self−test)回路1101が設けられている。

【0043】

BIST回路1101は,テスト用アドレス信号TAD,テスト用イネーブル信号TWE,モード選択信号MST,テスト用入力データTDIを生成し,SRAMが出力するテスト用出力データTDOを入力とする。なお,モード選択信号MSTによって,SRAMのテストをするか否かを決定する。以下,テストのときの動作をテストモードとし,テストでないときの通常動作を通常モードとする。クロックバッファ1102は,クロック信号CLKとモード選択信号MSTとを入力とする。そして,クロック信号CLKに基づいて,非反転および反転論理レベルを有するクロック信号CLK,XCLKを出力する。また,クロックバッファ1102は,モード選択信号MSTに基づいて,SRAMの動作をテストモードまたは動作モードに制御し,非反転および反転論理レベルを有する動作制御信号BM,XBMを出力する。モード選択信号MSTがLレベルのとき通常モード,Hレベルのときテストモードとする。

【0044】

ライトイネーブルレジスタ1103は,動作制御信号BM,XBMに基づいて,通常モード時はライトイネーブル信号WE,テストモード時はテスト用ライトイネーブル信号TWEを入力とする。なお,ライトイネーブル信号WE,テスト用ライトイネーブル信号TWEは,メモリセルへデータの書き込みが行われるときに活性化される。

【0045】

アドレスレジスタ1104は,動作制御信号BM,XBMに基づいて,通常モード時は入力アドレス信号AD,テストモード時はテスト用入力アドレス信号TADを入力し,通常モード時はロウ側の内部アドレス信号RADとコラム側の内部アドレス信号CADを出力する。

【0046】

リセット回路1105,1115は,図6のように,アドレスレジスタ1104とロウデコーダバッファ1106に接続される内部アドレス信号RAD,CADの信号線網との間に設けられる。そして,クロックバッファ1102より出力されたクロック信号XCLKと動作制御信号BMに応答して,通常モード時はリセットをせずに内部アドレス信号RAD,CADを出力し,テストモード時は内部アドレス信号RAD,CADをリセットする。

【0047】

クロックジェネレータ1107は,クロックバッファ1106から入力されるクロック信号CLKに基づいて,ロウデコーダバッファ1106の起動信号となるロウクロック信号ROWCLKと,ライトアンプ1110,センスアンプ1113,コラムデコーダ1108の起動信号となるコラムクロック信号COLCLK等のクロックを生成する。

【0048】

ロウデコーダバッファ1106は,図6のようにロウ側の内部アドレス信号RADの内部アドレス信号線網を有し,ロウ側の内部アドレス信号RADとロウクロック信号ROWCLKとに基づいてワード線選択信号を生成し,さらにそのワード線選択信号に応答してメモリセルマトリックス1112の1つのワード線を選択する。

【0049】

コラムデコーダ1108は,図6のようにコラム側の内部アドレス信号CADの内部アドレス信号線網を有し,コラムクロック信号COLCLKに基づいてコラム側の内部アドレス信号CADをデコードしてコラム選択信号を生成する。

【0050】

コラムセレクタ1111は,コラムデコーダ1108で生成されたコラム選択信号に応答してメモリセルマトリックス1112の所定のビット線を選択し,ライトアンプ1110またはセンスアンプ1113に接続する。

【0051】

インプットデータレジスタ1109はクロックバッファ1102で生成した動作制御信号BM,XBMに基づいて,通常モード時は入力データDI,テストモード時はBIST回路1101で生成したテスト用入力データTDIを入力とする。

【0052】

ライトアンプ1110は,インプットデータレジスタ1109を介して入力された入力データDIまたはテスト用入力データTDIを増幅して,コラムセレクタ1111を介して所定のビット線を駆動する。これにより,メモリセルにデータが書き込まれる。

【0053】

センスアンプ1113は,コラムクロック信号COLCLKに応答し,コラムセレクタ1111を介して接続された所定の1対のビット線の電位差を増幅し,その増幅信号をアウトプットデータバッファ1114へ出力する。これにより,メモリセルからデータが読みだされる。

【0054】

アウトプットデータバッファ1114は,動作制御信号BM,XBMに基づいて,センスアンプ1113から出力された増幅信号を,通常モード時は出力データDO,テストモード時はテスト用出力データTDOとして出力する。なお,テスト用出力データTDOはBIST回路1101へ入力され検証される。

【0055】

図12は,第2の実施の形態におけるクロックバッファ,アドレスレジスタ,アウトプットデータバッファを示す図である。

【0056】

図12(1)はクロックバッファ1102の回路図である。クロックバッファ1102は,モード選択信号MSTから互いに逆相の動作制御信号BM,XBMを生成する動作制御信号生成回路1200と,クロック信号CLKをバッファリングし互いに逆相のクロック信号CLKとXCLKを生成するクロックバッファ回路1203とを有する。また,動作制御信号生成回路1200は,インバータ1201,1202を有し,動作制御信号BMはモード選択信号MSTの非反転論理レベルの信号であり,動作制御信号XBMはモード選択信号の反転論理レベルの信号である。一方,クロックバッファ回路1203はインバータ1204〜1208を有し,入力クロック信号CLKをそのまま出力したクロック信号CLKと,反転したクロック信号XCLKとを出力する。

【0057】

図12(2)はアドレスレジスタ1104の回路図であり,入力アドレス信号AD又はTADに基づいてロウ側の内部アドレス信号RADを生成する部分について示している。アドレスレジスタ1104は,CMOSトランスファゲート1211〜1216と,インバータ1217〜1222を有する。なお,アドレスレジスタ1104は,CMOSトランスファゲート1213,1214,ラッチ回路を構成するインバータ1218,1219を有する前段部と,CMOSトランスファゲート1215,1216,ラッチ回路を構成するインバータ1220,1221を有する後段部とに分けられるマスタースレーブ型ラッチ回路の構成となっている。CMOSトランスファゲート1213,1216はクロック信号CLKがHレベルのときOFF,LレベルのときONとなる。CMOSトランスファゲート1214,1215はクロック信号がLレベルのときOFF,HレベルのときONとなる。

【0058】

通常モードのとき,すなわち動作制御信号BMがLレベル,XBMがHレベルのとき,CMOSトランスファゲート1211,1212はそれぞれON,OFFされて,インバータ1217には入力アドレス信号ADが供給される。クロック信号CLKがLレベルのときCMOSトランスファゲート1213,1216がON,CMOSトランスファゲート1214,1215はOFFされて,インバータ1217で反転された入力アドレス信号ADが前段部に取り込まれる。次に,クロック信号CLKがHレベルのとき,CMOSトランスファゲート1213,1216がOFF,CMOSトランスファゲート1214,1215はONされて,前段部のラッチ回路1218,1219が入力アドレス信号ADをラッチし,前段部から入力アドレス信号ADが後段部へ出力される。そして,クロック信号CLKがLレベルになったときに,後段部のラッチ回路1220,1221が内部アドレス信号ADをラッチする。このとき,後段部のラッチ回路から反転された内部アドレス信号AD,すなわちロウ側の内部アドレス信号XRADが出力され,インバータ1222からは,入力アドレス信号ADと同じ論理レベルの内部アドレス信号RADが出力される。

【0059】

テストモードのとき,すなわち動作制御信号BMがHレベル,XBMがLレベルのとき,CMOSトランスファゲート1211,1212はそれぞれOFF,ONされ,インバータ1217にはHレベルのテスト用入力アドレス信号TADが供給される。そして,通常モードと同様にして入力アドレス信号TADが取り込まれ,テスト用入力アドレス信号TADを反転した論理レベルの内部アドレス信号XRADと,テスト用入力アドレス信号TADと同じ論理レベルの内部アドレス信号RADが出力される。

【0060】

図12(3)は,アウトプットデータバッファ1114の回路図であり,インバータ1230〜1237を有する。センスアンプ1113から出力された信号SA,動作制御信号BM,XBMを入力とする。通常モード時,すなわち動作制御信号BMがLレベルであれば,出力データDOは信号SAと同じ論理レベルとなり,出力データTDOはLレベルとなる。テストモード時,すなわち動作制御信号BMがHレベルであれば,出力データDOはLレベルとなり,出力データTDOは増幅信号SAと同じ論理レベルとなる。

【0061】

図13は,第2の実施の形態におけるリセット回路を示す図である。なお,図13は,例として図11のアドレスデコーダにおけるリセット回路1105の回路図を記載しており,(1)と(2)の2通りの回路図を示している。

【0062】

図13(1)の回路図は,NANDゲート1301〜1303とインバータ1304,1305とを有するリセット回路1105を示している。図7(1)に記載したリセット回路120と異なる点は,リセット回路1105が動作制御信号BMとクロック信号XCLKを入力とするNANDゲート1301を有することである。

【0063】

通常モード時,すなわち動作制御信号BMがLレベルの場合,クロック信号XCLKの論理レベルにかかわらず,NANDゲート1301の出力はHレベルとなり,インバータ1304,1305はロウ側の内部アドレス信号RAD,XRADをそのまま出力する。つまり,通常モード時,セット回路1105は内部アドレス信号RAD,XRADをリセットせずにそのまま出力する。

【0064】

一方,テストモード時,動作制御信号BMがHレベルの場合,NANDゲート1301は,クロック信号XCLKを反転して出力する。つまりクロック信号CLKがHレベル,XCLKがLレベルの間は,NANDゲート1301の出力はHレベルとなり,インバータ1304,1305は内部アドレス信号RAD,XRADをそのまま出力する。クロック信号CLKがLレベル,XCLKがHレベルになると,NANDゲート1301の出力はLレベルとなり,内部アドレス信号RAD,XRADのうちHレベルの信号はLレベルにリセットされ,Lレベルの信号はクロック信号CLKの立ち下がり後もLレベルを維持する。つまり,リセット回路1105は,テストモード時はクロック信号CLKの立ち下がりエッジで内部アドレス信号RAD又はXRADをHレベルからLレベルにリセットする動作を行う。

【0065】

図13(2)の回路図は,NANDゲート1310と,インバータ1311と,CMOSトランスファゲート1312,1313とNMOSトランジスタ1314,1315とを有するリセット回路1105を示している。

【0066】

通常モード時,すなわち動作制御信号BMがLレベルの場合,クロック信号XCLKの論理レベルにかかわらずNANDゲート1310の出力はHレベルとなり,CMOSトランスファゲート1312,1313はともにONとなり,NMOSトランジスタ1314,1315はともにOFFとなるため,リセット回路は内部アドレス信号RAD,XRADをそのまま出力する。このように,通常モード時,リセット回路1105は内部アドレス信号RAD,XRADをリセットせずにそのまま出力する。

【0067】

テストモード時,動作制御信号BMがHレベルの場合,NANDゲート1310は,クロック信号XCLKを反転して出力する。つまりクロック信号CLKがHレベル,XCLKがLレベルの間は,NANDゲート1310の出力はHレベルとなり,CMOSトランスファゲート1312,1313はともにONとなり,NMOSトランジスタ1314,1315はともにOFFとなるため,リセット回路は内部アドレス信号RAD,XRADをそのまま出力する。クロック信号CLKがLレベル,XCLKがHレベルになると,NANDゲート1310の出力はLレベルとなり,CMOSトランスファゲート1312,1313はともにOFFとなり,NMOSトランジスタ1314,1315はともにONとなるため,内部アドレス信号RAD,XRADのうちHレベルの信号はLレベルにリセットされ,Lレベルの信号はクロック信号CLKの立ち下がり後もLレベルを維持する。つまり,リセット回路1105は,テストモード時はクロック信号CLKの立ち下がりエッジで内部アドレス信号RAD又はXRADをHレベルからLレベルにリセットする動作を行う。

【0068】

図14は,第2の実施の形態における通常モード時の内部アドレス信号の波形を示す図である。図14では,例として,通常時にマーチパターンにより5番地と6番地のアドレスを順に選択した場合における,3ビットの内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2と,5番地のワード線WL5および6番地のワード線WL6の駆動信号との波形を記載している。

【0069】

通常モード,つまりモード選択信号MSTがLレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセットされない。そのため,サイクルC5で5番地の入力アドレス信号ADがアドレスレジスタ1104に供給されると,時間T5+ΔTにクロック信号CLKが立ち下がっても,内部アドレス信号RAD0,XRAD1,RAD2はリセットされずにHレベルのままである。そして,サイクルC6で6番地の入力アドレス信号ADがアドレスレジスタ1104に供給されると,時間T6のクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XRAD0はHレベルとなり,RAD0はLレベルになる。同様にして,内部アドレス信号RAD1はHレベルとなり,XRAD1はLレベルになる。内部アドレス信号RAD2,XRAD2はそれぞれHレベル,Lレベルのままである。また,時間T6におけるクロック信号CLKの立ち上がりに応答して時間t6でロウクロック信号ROWCLK立ち上がる。そして,ロウデコーダバッファ1106は,ロウクロック信号ROWCLKと内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2に基づいて,時間t6でワード線WL6を駆動する。時間T6から所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力される。

【0070】

図15は,第2の実施の形態におけるテストモード時の内部アドレス信号の波形を示す図である。例として,テストモード時にマーチパターンにより5番地と6番地のアドレスを順に選択した場合における,3ビットの内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2と,5番地のワード線WL5および6番地のワード線WL6の駆動信号との波形を記載している。

【0071】

テストモード,つまりモード選択信号MSTがHレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセット回路1105でリセットされる。サイクルC5で5番地の入力アドレス信号TADがアドレスレジスタ1104に供給されると,時間T5+ΔTでクロック信号CLKの立ち下がりに応答して内部アドレス信号RAD0,XRAD1,RAD2はリセットされLレベルになり,XRAD0,RAD1,XRAD2はLレベルを維持する。そしてサイクルC6で6番地の入力アドレス信号TADがアドレスレジスタ1104に供給されると,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XRAD0,RAD1,RAD2がLレベルからHレベルへ立ち上がる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して時間t6でロウクロック信号ROWCLK立ち上がる。そして,ロウデコーダバッファ1106は,ロウクロック信号ROWCLKと内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2に基づいて,時間t6でワード線WL6を駆動する。時間T6から所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータTDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力される。最後に,時間T6+ΔTでクロック信号CLKがLレベルに立ち下がったのに応答して,各内部アドレス信号はLレベルにリセットされる。

【0072】

次に,ロウデコーダバッファ1106内に内部アドレス信号線の遅延があった場合について説明する。図9と同様に,クロック配線A1と内部アドレス信号線A2〜A4を有し,クロック配線A1と内部アドレス信号線A2〜A4を介してロウクロック信号CLKと内部アドレス信号XRAD,RAD1,RAD2を供給されるアドレスデコード回路113をロウデコーダバッファ1106が有し,内部アドレス信号線A4に遅延が存在する場合である。

【0073】

図16は,第2の実施の形態におけるテストモード時,かつアドレス配線遅延が存在する時の内部アドレス信号の波形を示す図である。

【0074】

テストモード,つまりモード選択信号MSTがHレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセット回路1105でリセットされる。内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2は図15と同様の波形となる。しかし,アドレスデコード回路113の内部アドレス信号線の入力信号AND113_A4は,内部アドレス信号線に遅延が存在するために,D1だけ遅延してLレベルからHレベルとなる。そして,ロウデコーダバッファ1106は,D1だけ遅れてワード線WL6に駆動信号を出力する。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータTDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となる。

【0075】

以上のように,通常モードとテストモードとでSRAMの動作を分けて,通常モード時はリセット動作を行わずに内部アドレス信号をアドレスレジスタ1104からそのまま出力し,テストモード時はリセット回路1105で内部アドレス信号をリセットすることによって,テストのときにだけ,ロウデータの入力信号に内部アドレス信号線の遅延の影響が発生するようにでき,遅延の有無を検出することが可能となる。

【0076】

なお,第2の実施の形態では,図11のようにアドレスレジスタ1104とロウデコーダバッファ1106内の内部アドレス信号線網との間にリセット回路1105を設けたが,アドレスレジスタ1104とコラムデコーダ1108内の内部アドレス信号線網との間にリセット回路を同様に設けることで,テストモード時にコラムデコーダ1108の内部アドレス信号線の遅延についても検知することが可能である。

【0077】

以上の実施の形態をまとめると,次の付記のとおりである。

【0078】

(付記1)

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力する複数のアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【0079】

(付記2)

付記1において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジである半導体記憶装置。

【0080】

(付記3)

付記2において

さらに,外部からの動作選択信号に基づいて,テストモードであるか否かを検出するテストモード信号回路を有し,

前記テストモード信号回路がテストモードであることを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を前記クロック信号の第2のエッジに応答して所定の論理レベルにリセットし,

前記テストモード信号回路がテストモードでないことを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号をリセットしない半導体記憶装置。

【0081】

(付記4)

付記2において

前記リセット回路は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットし,

前記アドレスデコード回路は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとる半導体記憶装置。

【0082】

(付記5)

付記2において

さらに,前記クロック信号に基づいてロウクロック信号又はコラムクロック信号を生成するクロックジェネレータを有し,

前記アドレスデコード回路は,前記ロウクロック信号又はコラムクロック信号の第1のエッジに応答して前記組合せを論理演算し前記ワード線又はビット線を駆動する半導体記憶装置。

【0083】

(付記6)

付記2において

前記リセット回路は,前記第1,第2の内部アドレス信号とクロック信号とについてNAND演算とNOT演算を行う半導体記憶装置。

【0084】

(付記7)

付記2において

前記リセット回路は,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第1の内部アドレス信号が供給される第1のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第2の内部アドレス信号が供給される第2のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードがグランド電圧に接続され,もう一方のノードは第1のトランスファゲートの他方のノードに接続される第1のNMOSトランジスタと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードにグランド電圧に接続され,もう一方のノードは第2のトランスファゲートの他方のノードに接続される第2のNMOSトランジスタとを有する半導体記憶装置。

【0085】

(付記8)

ワード線およびビット線の交差位置に配置されるメモリセルを選択するために入力された複数の入力アドレス信号をデコードするアドレスデコード方法において,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を生成し内部アドレス信号線に出力する内部アドレス信号生成工程と,

前記内部アドレス信号線を伝播してきた前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを論理演算する論理演算工程と

前記論理演算工程の後に,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで,前記第1と第2の内部アドレス信号を一定の論理レベルにリセットするリセット工程とを有するアドレスデコード方法。

【0086】

(付記9)

付記8において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジであるアドレスデコード方法。

【0087】

(付記10)

付記9において

前記リセット工程はテストモードのときに行われ,前記テストモードではない通常モードのときは行われないアドレスデコード方法。

【0088】

(付記11)

付記9において

前記論理演算工程は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとり,

前記リセット工程は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットするアドレスデコード方法。

【0089】

(付記12)

付記9において

さらに,論理演算工程の前に,前記クロック信号に基づいてロウクロック信号又はコラムクロック信号を生成するクロック生成工程を有し,

前記論理演算工程は,前記ロウクロック信号又はコラムクロック信号のエッジに応答して前記組合せを論理演算し前記ワード線又はビット線を駆動するアドレスデコード方法。

【符号の説明】

【0090】

AD0〜AD2:入力アドレス信号

ADO0〜ADO2,XADO0〜XADO2:内部アドレス信号

CLK:クロック信号

ROWCLK:ロウクロック信号

AND:アドレスデコード回路

WL0〜WL6:ワード線

AD,TAD:入力アドレス信号

RAD,CAD:内部アドレス信号

WE,TWE:ライトイネーブル信号

MST:モード選択信号

BM,XBM:動作制御信号

DI:入力データ

DO:出力データ

【技術分野】

【0001】

本発明は,半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置におけるアドレスデコーダでは,配線などにオープン不良が存在すると,異なるアドレスで同じメモリセルが選択される等不具合が発生する。

【0003】

アドレスデコーダの故障検出では,一般的にアドレスをインクリメントまたはデクリメントさせるマーチパターンで変化させながらデータの書き込みと読み出しを繰り返すテストが行われる。例えば,3ビットのアドレス信号線を有するメモリでは,アドレスをインクリメントする場合,アドレス信号は000(0番地)から111(7番地)まで順に与えられる。マーチパターンによるテストでは,アドレスを順にインクリメントもしくはデクリメントし,所望のメモリセルに書き込んだデータが正常に読み出せるかどうかを確認する。なお,このような不具合を検知する装置として特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭56−148789号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

また,オープン不良のように配線が断線しているのではなく,製造時のプロセスばらつき等に起因して配線に形状のばらつきがある場合,アドレスデコーダの出力となるワード線の駆動に遅延が生じ,読み出し時間が遅延し要求されるアクセスタイムを実現できず不具合となる。

【0006】

しかし,アドレスデコーダに配線形状ばらつき等による遅延が存在する場合,マーチパターンによるテストでは,アドレスがインクリメントまたはデクリメントされてもあるアドレス信号はHレベル又はLレベルから変化しないケースがあるため,アドレス配線の遅延を検知することができない。マーチパターンの代わりに,アドレス配線の遅延を検知できる他のテストパターンを使用するとテスト工数が増加してしまう。

【0007】

そこで,本発明の目的は,アドレス配線の遅延による不良を検出できる半導体記憶装置を提供することとする。

【課題を解決するための手段】

【0008】

半導体記憶装置の第1の側面は,

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力するアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【発明の効果】

【0009】

半導体記憶装置の第1の側面によれば,アドレス配線の遅延による不良を検出できる。

【図面の簡単な説明】

【0010】

【図1】アドレスデコーダを示す図である。

【図2】図1のアドレスデコーダに6番地の入力アドレス信号を供給した場合の信号波形を示す図である。

【図3】図1のアドレスデコーダの配線に遅延が生じた場合の信号波形を示す図である。

【図4】アドレスデコーダに対するマーチパターンのテストにおける信号波形を示す図である。

【図5】アドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【図6】第1の実施の形態におけるアドレスデコーダを示す図である。

【図7】第1の実施の形態におけるリセット回路を示す図である。

【図8】第1の実施の形態におけるアドレスデコード回路を示す図である。

【図9】第1の実施の形態における内部アドレス信号の波形を示す図である。

【図10】第1の実施の形態における実施の形態におけるアドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【図11】第2の実施の形態におけるSRAMの構成図である。

【図12】第2の実施の形態におけるクロックバッファ,アドレスレジスタ,アウトプットデータバッファを示す図である。

【図13】第2の実施の形態におけるリセット回路を示す図である。

【図14】第2の実施の形態における通常モード時の内部アドレス信号の波形を示す図である。

【図15】第2の実施の形態におけるテストモード時の内部アドレス信号の波形を示す図である。

【図16】第2の実施の形態におけるテストモード時,かつアドレス配線遅延が存在する時の内部アドレス信号の波形を示す図である。

【発明を実施するための形態】

【0011】

以下,図面を用いて本発明の実施の形態について説明する。

【0012】

図1は,アドレスデコーダを示す図である。図1のアドレスデコーダは,3ビットの入力アドレス信号をデコードするための回路であり,アドレスレジスタ101,102,103と,外部クロック信号CLKからロウクロック信号ROWCLKを生成するクロックジェネレータ104と,内部アドレス信号線網105と,アドレスデコード回路群106とを有する。

【0013】

また,アドレスレジスタ101は最下位ビットの入力アドレス信号AD0を供給され,クロック信号CLKに応答して,入力アドレス信号AD0と同相の内部アドレス信号ADO0と,内部アドレス信号線ADO0を反転した逆相の内部アドレス信号線XADO0を出力する。同様に,アドレスレジスタ102,103は2ビット目の入力アドレス信号AD1,最上位ビットの入力アドレス信号AD2をそれぞれ供給され,クロック信号CLKに応答して,互いに論理が反転した内部アドレス信号ADO1,XADO1,ADO2,XADO2を出力する。

【0014】

例えば,6番地の入力アドレス信号,すなわちLレベルのAD0,HレベルのAD1,AD2がアドレスレジスタ101〜103に供給された場合,内部アドレス信号ADO0はLレベル,XADO0はHレベル,ADO1はHレベル,XADO1はLレベル,ADO2はHレベル,XADO2はLレベルとなる。

【0015】

内部アドレス信号線網は,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2にそれぞれ対応した内部アドレス信号線を有する。

【0016】

アドレスデコード回路群106は,0番地から7番地までの各アドレスに対応したアドレスデコード回路107〜114を有しており,各アドレスデコード回路には,ロウクロック信号ROWCLK用のクロック配線A1と内部アドレス信号線A2〜A4を介して,アドレスに応じた内部アドレス信号が供給されて論理積演算を行い,選択されたワード線WL0〜WL7に駆動信号を出力する。例えば,0番地用のアドレスデコード回路107は,クロック配線A1を介してロウクロック信号ROWCLK,内部アドレス信号線A2を介して内部アドレス信号XADO0,内部アドレス信号線A3を介して内部アドレス信号XADO1,内部アドレス信号線A4を介してXADO2を供給されて,それらの内部アドレス信号が全てHの場合にワード線WL0を選択して駆動する。

【0017】

図2は,図1のアドレスデコーダに6番地の入力アドレス信号を供給した場合の信号波形を示す図である。図2では,図1のアドレスデコーダにおいて,1番地のアドレスからサイクルC1で6番地,サイクルC2で1番地のアドレスに順に変更した場合における,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2と,アドレスデコード回路113のクロック配線A1および内部アドレス信号線A2〜A4の入力信号AND113_A1〜AND113_A4と,ワード線WL6の信号波形を記載している。なお,図1に示すように,クロック配線A1および内部アドレス信号線A2〜A4は,ロウクロック信号ROWCLK,と内部アドレス信号XADO0,ADO1,ADO2をそれぞれ供給されている。

【0018】

サイクルC1で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,クロック信号CLKに応答して,時間ta〜ta+Δtの間でHレベルとなる。また,時間Taにおけるクロック信号CLKの立ち上がりに応答して,アドレスレジスタが内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2を時間taで立ち上げる。

【0019】

さらにロウクロック信号ROWCLKの立ち上がりに応答して,アドレスデコード回路113の入力信号AND113_A1〜AND113_A4が立ち上がる。入力信号AND113_A1〜AND113_A4の立ち上がりに応答して,アドレスデコード回路113は各信号の論理積をとり,時間taでワード線WL6を駆動する。そして,時間Taから所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力される。なお,アクセスタイムとは,クロック信号CLKが立ち上がってから,メモリのデータが出力されるまでの時間を意味する。

【0020】

ここで,もし図1のアドレスデコーダの配線に形状ばらつき等による遅延が生じた場合,各信号の波形は図2ではなく図3のようになる。図3は,図1のアドレスデコーダの配線に遅延が生じた場合の信号波形を示す図である。アドレスデコード回路113の内部アドレス信号線A4に遅延が存在すると,図3のように入力信号AND113_A4とワード線WL6の立ち上がりタイミングに遅延が生じる。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となってしまう。そのため,仕様通りのアクセスタイムAT60を実現するためには,テスト段階において,このようなアドレス配線の遅延を検出することが必要である。

【0021】

次に,図1のアドレスデコーダに対して,アドレスをインクリメントさせるマーチパターンでテストを行う場合について述べる。図4は,アドレスデコーダに対するマーチパターンのテストにおける信号波形を示す図である。また,図5は,アドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。

【0022】

図4では,サイクルC0〜C7の各タイミングでアドレスを0番地から7番地まで順にインクリメントしており,入力アドレス信号AD0〜AD2に応じた内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2の波形をクロック信号CLKとともに記載している。マーチパターンのテストでは,アドレスを変更しても論理レベルが変動しない信号が存在する。例えば,内部アドレス信号ADO2は,サイクルC4の4番地のテストを行うまではLレベルであったが,4番地の入力アドレス信号をアドレスレジスタ101〜103に供給しクロック信号CLKが立ち上がった以降はHレベルである。

【0023】

このマーチパターンのテストにおいて,図3の場合と同じようにアドレスデコード回路113の内部アドレス信号線A4に遅延が存在すると,アドレスデコード回路113の入力信号AND113_A1〜AND113_A4の波形は,図5のようになる。図5は,図4のマーチパターンのテストにおいて,アドレスを5番地から6番地へインクリメントしたときの各波形を示している。

【0024】

サイクルC6で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6〜t6+Δtの間でHレベルとなる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XADO0,ADO1がHレベルとなり,ADO0,XADO1がLレベルとなる。内部アドレス信号ADO2,XADO2は,5番地から6番地にアドレスが変更されても入力アドレス信号AD2に変化がないため,それぞれHレベル,Lレベルのままである。そのため,ロウクロック信号ROWCLKの立ち上がりに応答して,入力信号AND113_A1,AND113_A2,AND113_A3は立ち上がるが,AND113_A4はHレベルのままである。

【0025】

図3では,アドレスを1番地から6番地に変更すると内部アドレス信号ADO2がLレベルからHレベルになるため入力信号AND113_A4の立ち上がりの遅延を検出できているが,図5では,アドレスを5番地から6番地に変更しても内部アドレス信号ADO2がHレベルのままとなっているために,6番地の入力アドレス信号をアドレスレジスタ101〜103に供給しても入力信号AND113_A4の立ち上がり遅延を検出できていない。そのため,ワード線WL6は遅延することなく時間t6で駆動され,アクセスタイムはAT60となる。

【0026】

このようにマーチパターンでは,入力アドレス信号の論理レベルがアドレスの変更前後で変化しない場合があるために,図5のように内部アドレス信号線の遅延が検出されないことが発生する。この遅延を検出できるように,マーチパターンの替わりに,任意のアドレスを基準にして他の全番地にアクセスするギャロッピングパターンや,図3のようなアドレスを反転させるテストパターン等の他のテストパターンを使ってテストを行うと,テスト内容が複雑になるだけでなくテスト工数が増加するため望ましくない。

【0027】

[第1の実施の形態]

そこで,第1の実施の形態では,内部アドレス信号線の遅延を検出できるように,アドレスサイクル毎に入力アドレス信号に応じてHレベル又はLレベルになった内部アドレス信号を一方の論理レベルにリセットする。具体的には,アドレスサイクルを制御するクロック信号CLKの第1のエッジ(例えば立ち上がりエッジ)に応答して,入力アドレス信号に応じてHレベルにされた内部アドレス信号を,クロック信号CLKの第2のエッジ(例えば立ち下がりエッジ)に応答してLレベルにリセットする。

【0028】

図6は,第1の実施の形態におけるアドレスデコーダを示す図である。図6のアドレスデコーダは,アドレスレジスタ101〜103と内部アドレス信号線網105との間に,内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2を,クロック信号CLKの立ち下がりに応答してLレベルにリセットするリセット回路120〜122を有する。アドレスレジスタ101〜103で生成された内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2は,各リセット回路120〜122によりクロック信号CLKの立ち下がりに応答してLレベルにリセットされ,内部アドレス信号線網105の各信号線も同様にLレベルにリセットされる。

【0029】

図7は,第1の実施の形態におけるリセット回路を示す図である。なお,図7は,例として図6のアドレスデコーダにおけるリセット回路120の回路図を記載しており,(1)と(2)の2通りの回路図を示している。

【0030】

図7(1)の回路図は,NANDゲート701,703とインバータ702,704とを有するリセット回路120を示している。例えば,クロック信号CLKの立ち上がりに応答してアドレスレジスタ101で生成された内部アドレス信号ADO,XADOがそれぞれHレベル,LレベルでNANDゲート701,703に入力された場合,クロック信号CLKがHレベルの間は,インバータ702,704は内部アドレス信号のHレベル,Lレベルをそのまま出力する。しかし,クロック信号CLKがLレベルになると,インバータ702から出力される内部アドレス信号はLレベルとなり,内部アドレス信号ADOはHレベルからLレベルにリセットされる。インバータ704の出力は,内部アドレス信号XADO0がLレベルであったため,クロック信号CLKの立ち下がり後もLレベルを維持する。

【0031】

図7(2)の回路図は,インバータ705と,CMOSトランスファゲート706,707とNMOSトランジスタ708,709とを有するリセット回路120を示している。例として,クロック信号CLKの立ち上がりに応答してアドレスレジスタ101で生成された内部アドレス信号ADO,XADOがそれぞれHレベル,LレベルでNANDゲート701,703に入力された場合について説明する。まず,クロック信号CLKの立ち上がり後のHレベルの間は,CMOSトランスファゲート706,707はともにONとなり,NMOSトランジスタ708,709はともにOFFとなるため,リセット回路は内部アドレス信号ADO,XADOのHレベル,Lレベルをそのまま出力する。クロック信号CLKがLレベルになると,CMOSトランスファゲート706,707はOFFとなり,NMOSトランジスタ708,709はともにONとなるため,内部アドレス信号ADOはHレベルからLレベルにリセットされ,内部アドレス信号XADO0はLレベルを維持する。

【0032】

図8は,第1の実施の形態におけるアドレスデコード回路を示す図である。図8のアドレスデコード回路は図6のアドレスデコード回路107〜114に該当する。図8において,アドレスデコード回路は,PMOSトランジスタ801,806と,NMOSトランジスタ802〜805と,インバータ807〜809とを有する。例えば,アドレスデコード回路113では,クロック配線A1および内部アドレス信号線A2〜A4には,ロウクロック信号ROWCLKと内部アドレス信号XADO0,ADO1,ADO2とをそれぞれ供給される。そして,内部アドレス信号線A2〜A4にHレベルの信号が供給されると,クロック配線A1のロウクロック信号ROWCLKがHレベルに立ち上がったタイミングで,NMOSトランジスタ802〜805はONとなり,PMOSトランジスタ801,806はOFFし,その結果インバータ807〜809を介して出力される信号はHレベルとなる。これが選択状態である。内部アドレス信号線A2〜A4のいずれかがLレベルの場合は,ロウクロック信号ROWCLKがHレベルになっても,インバータ809の出力は非選択レベルのLレベルである。

【0033】

図9は,第1の実施の形態における内部アドレス信号の波形を示す図である。なお,図9では,入力アドレス信号AD0〜AD2と,クロック信号CLKと,アドレスレジスタ101〜103及びリセット回路120〜122により生成された内部アドレス信号ADO0,XADO0,ADO1,XADO1,ADO2,XADO2とを記載している。また,入力アドレスは図4と同様にマーチパターンにより選択されている。例えば,0番地のアドレスを選択した場合では,クロック信号CLKの立ち上がりに応答して,入力アドレス信号AD0〜AD2に応じてHレベルにされた内部アドレス信号XADO0,XADO1,XADO2は,時間T0+ΔTでクロック信号CLKがHレベルからLレベルに立ち下がったことに応答して,時間L0で全てLレベルにリセットされている。このリセット動作は,アドレスサイクル毎に行われる。したがって,第1,第2の内部アドレス信号のいずれか一方は,アドレスサイクル毎に必ずクロック信号CLKの立ち上がりに応答して,LレベルからHレベルに立ち上がることになる。この立ち上がり動作は,内部アドレス信号線の遅延特性の影響を受けることになる。

【0034】

次に,図5の場合と同じように,図9のアドレスデコーダにおいてアドレスデコード回路113の内部アドレス信号線A4に遅延が存在したときの各波形について,図10を用いて説明する。図10は,第1の実施の形態におけるアドレスデコーダに対するマーチパターンテストにて遅延が生じた場合の信号波形を示す図である。図10では,図9における5番地と6番地の入力アドレス信号が入力された場合について,アドレスデコード回路113に入力されるロウクロック信号CLKと内部アドレス信号である入力信号AND113_A1〜AND113_A4と,アドレスデコード回路113から出力されるワード線WL6の駆動信号波形を記載している。なお,アドレスデコード回路113のクロック配線A1および内部アドレス信号線A2〜A4は,ロウクロック信号ROWCLKと内部アドレス信号XADO0,ADO1,ADO2とをそれぞれ供給されている。

【0035】

5番地のアドレスが入力されたとき,そのアドレスサイクル内の時間T5+ΔTでクロック信号CLKの立ち下がりに応答してHレベルだった内部アドレス信号ADO0,XADO1,ADO2はリセットされLレベルになり,XADO0,ADO1,XADO2はLレベルを維持する。そして,サイクルC6で6番地のアドレスが入力されるときは,各内部アドレス信号はLレベルとなっている。この点が,図4のリセット回路を有しないアドレスデコーダの場合の波形(図10中の内部アドレス信号ADO2,AND113_A4の波線)とは異なる。例えば,内部アドレス信号ADO2は,図4では5番地から6番地に入力アドレスが変更されてもHレベルのままであるが,図10では時間T5+ΔTでリセットされて6番地のアドレスが入力されるときはLレベルとなっている。

【0036】

サイクルC6で6番地の入力アドレス信号がアドレスレジスタ101〜103に供給されると,クロックジェネレータ104から出力されるロウクロック信号ROWCLKは,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6〜t6+Δtの間でHレベルとなる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XADO0,ADO1,ADO2がLレベルからHレベルへ立ち上がる。

【0037】

次に,ロウクロック信号ROWCLKの立ち上がりに応答して,時間t6にアドレスデコード回路113の入力信号AND113_A1〜AND113_A3が立ち上がる。アドレスデコード回路113の内部アドレス信号線A4に遅延が存在するため,入力信号AND113_A4は,時間t6からD1だけ遅れて立ち上がる。そして,アドレスデコード回路113は各信号の論理積演算を行い,時間t6よりD1だけ遅れてワード線WL6に駆動信号を出力する。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータがセンスアンプ,出力回路等を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となる。なお,この遅延AT61がBIST回路により検出され不良品と判断される。最後に,時間T6+ΔTでクロック信号CLKがLレベルに立ち下がったのに応答して,各内部アドレス信号はLレベルにリセットされ,それに併せて入力信号AND113_A2〜A4もLレベルにリセットされる。

【0038】

以上のように,クロック信号CLKの立ち下がりに応答して内部アドレス信号をリセットすることで,図4の内部アドレス信号ADO2の波形のような,アドレスが変更されてもHレベルが維持されることは発生しなくなる。そのため,マーチパターンによるテストの場合でも,内部アドレス信号線の遅延を検出することが可能となる。

【0039】

また,第1の実施の形態では,図6のようにワード線のアドレスデコード回路群106について内部アドレス信号線遅延を検出したが,同様にしてビット線のアドレスデコード回路についても内部アドレス信号線遅延を検出することが可能である。

【0040】

[第2の実施の形態]

第2の実施の形態は,第1の実施の形態で記載したリセット回路をSRAMに適用した場合の形態である。リセット回路により常に内部アドレス信号のリセット動作を行うと消費電力の増大を招くため,第2の実施の形態ではリセット動作が必要なテストのときにのみリセット動作を行い内部アドレス信号線の不具合を検知できるようにしておき,通常時はリセット動作を行わないようにする。

【0041】

図11は,第2の実施の形態におけるSRAMの構成図である。図11のSRAMは,BIST回路1101と,クロックバッファ1102と,ライトイネーブルレジスタ1103と,アドレスレジスタ1104と,リセット回路1105,1115と,クロックジェネレータ1107と,ロウデコーダバッファ1106と,インプットデータレジスタ1109と,ライトアンプ1110と,コラムデコーダ1108と,コラムセレクタ1111と,複数のメモリセルがマトリックス状に配列されたメモリセルマトリックス1112と,センスアンプ1113と,アウトプットデータレジスタ1114とを有する。

【0042】

上記のSRAMは,例えば大規模なLSIチップ内に埋め込まれる。その場合,SRAMの各入力,出力端子はLSIチップの外部端子として設けられない。そこで,SRAMの動作テストを行うためにBIST(built in self−test)回路1101が設けられている。

【0043】

BIST回路1101は,テスト用アドレス信号TAD,テスト用イネーブル信号TWE,モード選択信号MST,テスト用入力データTDIを生成し,SRAMが出力するテスト用出力データTDOを入力とする。なお,モード選択信号MSTによって,SRAMのテストをするか否かを決定する。以下,テストのときの動作をテストモードとし,テストでないときの通常動作を通常モードとする。クロックバッファ1102は,クロック信号CLKとモード選択信号MSTとを入力とする。そして,クロック信号CLKに基づいて,非反転および反転論理レベルを有するクロック信号CLK,XCLKを出力する。また,クロックバッファ1102は,モード選択信号MSTに基づいて,SRAMの動作をテストモードまたは動作モードに制御し,非反転および反転論理レベルを有する動作制御信号BM,XBMを出力する。モード選択信号MSTがLレベルのとき通常モード,Hレベルのときテストモードとする。

【0044】

ライトイネーブルレジスタ1103は,動作制御信号BM,XBMに基づいて,通常モード時はライトイネーブル信号WE,テストモード時はテスト用ライトイネーブル信号TWEを入力とする。なお,ライトイネーブル信号WE,テスト用ライトイネーブル信号TWEは,メモリセルへデータの書き込みが行われるときに活性化される。

【0045】

アドレスレジスタ1104は,動作制御信号BM,XBMに基づいて,通常モード時は入力アドレス信号AD,テストモード時はテスト用入力アドレス信号TADを入力し,通常モード時はロウ側の内部アドレス信号RADとコラム側の内部アドレス信号CADを出力する。

【0046】

リセット回路1105,1115は,図6のように,アドレスレジスタ1104とロウデコーダバッファ1106に接続される内部アドレス信号RAD,CADの信号線網との間に設けられる。そして,クロックバッファ1102より出力されたクロック信号XCLKと動作制御信号BMに応答して,通常モード時はリセットをせずに内部アドレス信号RAD,CADを出力し,テストモード時は内部アドレス信号RAD,CADをリセットする。

【0047】

クロックジェネレータ1107は,クロックバッファ1106から入力されるクロック信号CLKに基づいて,ロウデコーダバッファ1106の起動信号となるロウクロック信号ROWCLKと,ライトアンプ1110,センスアンプ1113,コラムデコーダ1108の起動信号となるコラムクロック信号COLCLK等のクロックを生成する。

【0048】

ロウデコーダバッファ1106は,図6のようにロウ側の内部アドレス信号RADの内部アドレス信号線網を有し,ロウ側の内部アドレス信号RADとロウクロック信号ROWCLKとに基づいてワード線選択信号を生成し,さらにそのワード線選択信号に応答してメモリセルマトリックス1112の1つのワード線を選択する。

【0049】

コラムデコーダ1108は,図6のようにコラム側の内部アドレス信号CADの内部アドレス信号線網を有し,コラムクロック信号COLCLKに基づいてコラム側の内部アドレス信号CADをデコードしてコラム選択信号を生成する。

【0050】

コラムセレクタ1111は,コラムデコーダ1108で生成されたコラム選択信号に応答してメモリセルマトリックス1112の所定のビット線を選択し,ライトアンプ1110またはセンスアンプ1113に接続する。

【0051】

インプットデータレジスタ1109はクロックバッファ1102で生成した動作制御信号BM,XBMに基づいて,通常モード時は入力データDI,テストモード時はBIST回路1101で生成したテスト用入力データTDIを入力とする。

【0052】

ライトアンプ1110は,インプットデータレジスタ1109を介して入力された入力データDIまたはテスト用入力データTDIを増幅して,コラムセレクタ1111を介して所定のビット線を駆動する。これにより,メモリセルにデータが書き込まれる。

【0053】

センスアンプ1113は,コラムクロック信号COLCLKに応答し,コラムセレクタ1111を介して接続された所定の1対のビット線の電位差を増幅し,その増幅信号をアウトプットデータバッファ1114へ出力する。これにより,メモリセルからデータが読みだされる。

【0054】

アウトプットデータバッファ1114は,動作制御信号BM,XBMに基づいて,センスアンプ1113から出力された増幅信号を,通常モード時は出力データDO,テストモード時はテスト用出力データTDOとして出力する。なお,テスト用出力データTDOはBIST回路1101へ入力され検証される。

【0055】

図12は,第2の実施の形態におけるクロックバッファ,アドレスレジスタ,アウトプットデータバッファを示す図である。

【0056】

図12(1)はクロックバッファ1102の回路図である。クロックバッファ1102は,モード選択信号MSTから互いに逆相の動作制御信号BM,XBMを生成する動作制御信号生成回路1200と,クロック信号CLKをバッファリングし互いに逆相のクロック信号CLKとXCLKを生成するクロックバッファ回路1203とを有する。また,動作制御信号生成回路1200は,インバータ1201,1202を有し,動作制御信号BMはモード選択信号MSTの非反転論理レベルの信号であり,動作制御信号XBMはモード選択信号の反転論理レベルの信号である。一方,クロックバッファ回路1203はインバータ1204〜1208を有し,入力クロック信号CLKをそのまま出力したクロック信号CLKと,反転したクロック信号XCLKとを出力する。

【0057】

図12(2)はアドレスレジスタ1104の回路図であり,入力アドレス信号AD又はTADに基づいてロウ側の内部アドレス信号RADを生成する部分について示している。アドレスレジスタ1104は,CMOSトランスファゲート1211〜1216と,インバータ1217〜1222を有する。なお,アドレスレジスタ1104は,CMOSトランスファゲート1213,1214,ラッチ回路を構成するインバータ1218,1219を有する前段部と,CMOSトランスファゲート1215,1216,ラッチ回路を構成するインバータ1220,1221を有する後段部とに分けられるマスタースレーブ型ラッチ回路の構成となっている。CMOSトランスファゲート1213,1216はクロック信号CLKがHレベルのときOFF,LレベルのときONとなる。CMOSトランスファゲート1214,1215はクロック信号がLレベルのときOFF,HレベルのときONとなる。

【0058】

通常モードのとき,すなわち動作制御信号BMがLレベル,XBMがHレベルのとき,CMOSトランスファゲート1211,1212はそれぞれON,OFFされて,インバータ1217には入力アドレス信号ADが供給される。クロック信号CLKがLレベルのときCMOSトランスファゲート1213,1216がON,CMOSトランスファゲート1214,1215はOFFされて,インバータ1217で反転された入力アドレス信号ADが前段部に取り込まれる。次に,クロック信号CLKがHレベルのとき,CMOSトランスファゲート1213,1216がOFF,CMOSトランスファゲート1214,1215はONされて,前段部のラッチ回路1218,1219が入力アドレス信号ADをラッチし,前段部から入力アドレス信号ADが後段部へ出力される。そして,クロック信号CLKがLレベルになったときに,後段部のラッチ回路1220,1221が内部アドレス信号ADをラッチする。このとき,後段部のラッチ回路から反転された内部アドレス信号AD,すなわちロウ側の内部アドレス信号XRADが出力され,インバータ1222からは,入力アドレス信号ADと同じ論理レベルの内部アドレス信号RADが出力される。

【0059】

テストモードのとき,すなわち動作制御信号BMがHレベル,XBMがLレベルのとき,CMOSトランスファゲート1211,1212はそれぞれOFF,ONされ,インバータ1217にはHレベルのテスト用入力アドレス信号TADが供給される。そして,通常モードと同様にして入力アドレス信号TADが取り込まれ,テスト用入力アドレス信号TADを反転した論理レベルの内部アドレス信号XRADと,テスト用入力アドレス信号TADと同じ論理レベルの内部アドレス信号RADが出力される。

【0060】

図12(3)は,アウトプットデータバッファ1114の回路図であり,インバータ1230〜1237を有する。センスアンプ1113から出力された信号SA,動作制御信号BM,XBMを入力とする。通常モード時,すなわち動作制御信号BMがLレベルであれば,出力データDOは信号SAと同じ論理レベルとなり,出力データTDOはLレベルとなる。テストモード時,すなわち動作制御信号BMがHレベルであれば,出力データDOはLレベルとなり,出力データTDOは増幅信号SAと同じ論理レベルとなる。

【0061】

図13は,第2の実施の形態におけるリセット回路を示す図である。なお,図13は,例として図11のアドレスデコーダにおけるリセット回路1105の回路図を記載しており,(1)と(2)の2通りの回路図を示している。

【0062】

図13(1)の回路図は,NANDゲート1301〜1303とインバータ1304,1305とを有するリセット回路1105を示している。図7(1)に記載したリセット回路120と異なる点は,リセット回路1105が動作制御信号BMとクロック信号XCLKを入力とするNANDゲート1301を有することである。

【0063】

通常モード時,すなわち動作制御信号BMがLレベルの場合,クロック信号XCLKの論理レベルにかかわらず,NANDゲート1301の出力はHレベルとなり,インバータ1304,1305はロウ側の内部アドレス信号RAD,XRADをそのまま出力する。つまり,通常モード時,セット回路1105は内部アドレス信号RAD,XRADをリセットせずにそのまま出力する。

【0064】

一方,テストモード時,動作制御信号BMがHレベルの場合,NANDゲート1301は,クロック信号XCLKを反転して出力する。つまりクロック信号CLKがHレベル,XCLKがLレベルの間は,NANDゲート1301の出力はHレベルとなり,インバータ1304,1305は内部アドレス信号RAD,XRADをそのまま出力する。クロック信号CLKがLレベル,XCLKがHレベルになると,NANDゲート1301の出力はLレベルとなり,内部アドレス信号RAD,XRADのうちHレベルの信号はLレベルにリセットされ,Lレベルの信号はクロック信号CLKの立ち下がり後もLレベルを維持する。つまり,リセット回路1105は,テストモード時はクロック信号CLKの立ち下がりエッジで内部アドレス信号RAD又はXRADをHレベルからLレベルにリセットする動作を行う。

【0065】

図13(2)の回路図は,NANDゲート1310と,インバータ1311と,CMOSトランスファゲート1312,1313とNMOSトランジスタ1314,1315とを有するリセット回路1105を示している。

【0066】

通常モード時,すなわち動作制御信号BMがLレベルの場合,クロック信号XCLKの論理レベルにかかわらずNANDゲート1310の出力はHレベルとなり,CMOSトランスファゲート1312,1313はともにONとなり,NMOSトランジスタ1314,1315はともにOFFとなるため,リセット回路は内部アドレス信号RAD,XRADをそのまま出力する。このように,通常モード時,リセット回路1105は内部アドレス信号RAD,XRADをリセットせずにそのまま出力する。

【0067】

テストモード時,動作制御信号BMがHレベルの場合,NANDゲート1310は,クロック信号XCLKを反転して出力する。つまりクロック信号CLKがHレベル,XCLKがLレベルの間は,NANDゲート1310の出力はHレベルとなり,CMOSトランスファゲート1312,1313はともにONとなり,NMOSトランジスタ1314,1315はともにOFFとなるため,リセット回路は内部アドレス信号RAD,XRADをそのまま出力する。クロック信号CLKがLレベル,XCLKがHレベルになると,NANDゲート1310の出力はLレベルとなり,CMOSトランスファゲート1312,1313はともにOFFとなり,NMOSトランジスタ1314,1315はともにONとなるため,内部アドレス信号RAD,XRADのうちHレベルの信号はLレベルにリセットされ,Lレベルの信号はクロック信号CLKの立ち下がり後もLレベルを維持する。つまり,リセット回路1105は,テストモード時はクロック信号CLKの立ち下がりエッジで内部アドレス信号RAD又はXRADをHレベルからLレベルにリセットする動作を行う。

【0068】

図14は,第2の実施の形態における通常モード時の内部アドレス信号の波形を示す図である。図14では,例として,通常時にマーチパターンにより5番地と6番地のアドレスを順に選択した場合における,3ビットの内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2と,5番地のワード線WL5および6番地のワード線WL6の駆動信号との波形を記載している。

【0069】

通常モード,つまりモード選択信号MSTがLレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセットされない。そのため,サイクルC5で5番地の入力アドレス信号ADがアドレスレジスタ1104に供給されると,時間T5+ΔTにクロック信号CLKが立ち下がっても,内部アドレス信号RAD0,XRAD1,RAD2はリセットされずにHレベルのままである。そして,サイクルC6で6番地の入力アドレス信号ADがアドレスレジスタ1104に供給されると,時間T6のクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XRAD0はHレベルとなり,RAD0はLレベルになる。同様にして,内部アドレス信号RAD1はHレベルとなり,XRAD1はLレベルになる。内部アドレス信号RAD2,XRAD2はそれぞれHレベル,Lレベルのままである。また,時間T6におけるクロック信号CLKの立ち上がりに応答して時間t6でロウクロック信号ROWCLK立ち上がる。そして,ロウデコーダバッファ1106は,ロウクロック信号ROWCLKと内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2に基づいて,時間t6でワード線WL6を駆動する。時間T6から所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力される。

【0070】

図15は,第2の実施の形態におけるテストモード時の内部アドレス信号の波形を示す図である。例として,テストモード時にマーチパターンにより5番地と6番地のアドレスを順に選択した場合における,3ビットの内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2と,5番地のワード線WL5および6番地のワード線WL6の駆動信号との波形を記載している。

【0071】

テストモード,つまりモード選択信号MSTがHレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセット回路1105でリセットされる。サイクルC5で5番地の入力アドレス信号TADがアドレスレジスタ1104に供給されると,時間T5+ΔTでクロック信号CLKの立ち下がりに応答して内部アドレス信号RAD0,XRAD1,RAD2はリセットされLレベルになり,XRAD0,RAD1,XRAD2はLレベルを維持する。そしてサイクルC6で6番地の入力アドレス信号TADがアドレスレジスタ1104に供給されると,時間T6におけるクロック信号CLKの立ち上がりに応答して,時間t6で内部アドレス信号XRAD0,RAD1,RAD2がLレベルからHレベルへ立ち上がる。また,時間T6におけるクロック信号CLKの立ち上がりに応答して時間t6でロウクロック信号ROWCLK立ち上がる。そして,ロウデコーダバッファ1106は,ロウクロック信号ROWCLKと内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2に基づいて,時間t6でワード線WL6を駆動する。時間T6から所定のアクセスタイムAT60が経過した後,ワード線WL6に接続されるメモリセルのうち,コラムアドレスが選択されるメモリセルのデータTDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力される。最後に,時間T6+ΔTでクロック信号CLKがLレベルに立ち下がったのに応答して,各内部アドレス信号はLレベルにリセットされる。

【0072】

次に,ロウデコーダバッファ1106内に内部アドレス信号線の遅延があった場合について説明する。図9と同様に,クロック配線A1と内部アドレス信号線A2〜A4を有し,クロック配線A1と内部アドレス信号線A2〜A4を介してロウクロック信号CLKと内部アドレス信号XRAD,RAD1,RAD2を供給されるアドレスデコード回路113をロウデコーダバッファ1106が有し,内部アドレス信号線A4に遅延が存在する場合である。

【0073】

図16は,第2の実施の形態におけるテストモード時,かつアドレス配線遅延が存在する時の内部アドレス信号の波形を示す図である。

【0074】

テストモード,つまりモード選択信号MSTがHレベルである場合であるため,内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2はリセット回路1105でリセットされる。内部アドレス信号RAD0〜RAD2,XRAD0〜XRAD2は図15と同様の波形となる。しかし,アドレスデコード回路113の内部アドレス信号線の入力信号AND113_A4は,内部アドレス信号線に遅延が存在するために,D1だけ遅延してLレベルからHレベルとなる。そして,ロウデコーダバッファ1106は,D1だけ遅れてワード線WL6に駆動信号を出力する。その結果,ワード線WL6に接続されるメモリセルのうち,コラムアドレスで選択されるメモリセルのデータTDOがセンスアンプ1113,アウトプットデータバッファ1114を介して出力されるタイミングが,アクセスタイムAT60から遅延したAT61となる。

【0075】

以上のように,通常モードとテストモードとでSRAMの動作を分けて,通常モード時はリセット動作を行わずに内部アドレス信号をアドレスレジスタ1104からそのまま出力し,テストモード時はリセット回路1105で内部アドレス信号をリセットすることによって,テストのときにだけ,ロウデータの入力信号に内部アドレス信号線の遅延の影響が発生するようにでき,遅延の有無を検出することが可能となる。

【0076】

なお,第2の実施の形態では,図11のようにアドレスレジスタ1104とロウデコーダバッファ1106内の内部アドレス信号線網との間にリセット回路1105を設けたが,アドレスレジスタ1104とコラムデコーダ1108内の内部アドレス信号線網との間にリセット回路を同様に設けることで,テストモード時にコラムデコーダ1108の内部アドレス信号線の遅延についても検知することが可能である。

【0077】

以上の実施の形態をまとめると,次の付記のとおりである。

【0078】

(付記1)

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力する複数のアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【0079】

(付記2)

付記1において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジである半導体記憶装置。

【0080】

(付記3)

付記2において

さらに,外部からの動作選択信号に基づいて,テストモードであるか否かを検出するテストモード信号回路を有し,

前記テストモード信号回路がテストモードであることを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を前記クロック信号の第2のエッジに応答して所定の論理レベルにリセットし,

前記テストモード信号回路がテストモードでないことを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号をリセットしない半導体記憶装置。

【0081】

(付記4)

付記2において

前記リセット回路は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットし,

前記アドレスデコード回路は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとる半導体記憶装置。

【0082】

(付記5)

付記2において

さらに,前記クロック信号に基づいてロウクロック信号又はコラムクロック信号を生成するクロックジェネレータを有し,

前記アドレスデコード回路は,前記ロウクロック信号又はコラムクロック信号の第1のエッジに応答して前記組合せを論理演算し前記ワード線又はビット線を駆動する半導体記憶装置。

【0083】

(付記6)

付記2において

前記リセット回路は,前記第1,第2の内部アドレス信号とクロック信号とについてNAND演算とNOT演算を行う半導体記憶装置。

【0084】

(付記7)

付記2において

前記リセット回路は,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第1の内部アドレス信号が供給される第1のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第2の内部アドレス信号が供給される第2のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードがグランド電圧に接続され,もう一方のノードは第1のトランスファゲートの他方のノードに接続される第1のNMOSトランジスタと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードにグランド電圧に接続され,もう一方のノードは第2のトランスファゲートの他方のノードに接続される第2のNMOSトランジスタとを有する半導体記憶装置。

【0085】

(付記8)

ワード線およびビット線の交差位置に配置されるメモリセルを選択するために入力された複数の入力アドレス信号をデコードするアドレスデコード方法において,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を生成し内部アドレス信号線に出力する内部アドレス信号生成工程と,

前記内部アドレス信号線を伝播してきた前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを論理演算する論理演算工程と

前記論理演算工程の後に,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで,前記第1と第2の内部アドレス信号を一定の論理レベルにリセットするリセット工程とを有するアドレスデコード方法。

【0086】

(付記9)

付記8において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジであるアドレスデコード方法。

【0087】

(付記10)

付記9において

前記リセット工程はテストモードのときに行われ,前記テストモードではない通常モードのときは行われないアドレスデコード方法。

【0088】

(付記11)

付記9において

前記論理演算工程は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとり,

前記リセット工程は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットするアドレスデコード方法。

【0089】

(付記12)

付記9において

さらに,論理演算工程の前に,前記クロック信号に基づいてロウクロック信号又はコラムクロック信号を生成するクロック生成工程を有し,

前記論理演算工程は,前記ロウクロック信号又はコラムクロック信号のエッジに応答して前記組合せを論理演算し前記ワード線又はビット線を駆動するアドレスデコード方法。

【符号の説明】

【0090】

AD0〜AD2:入力アドレス信号

ADO0〜ADO2,XADO0〜XADO2:内部アドレス信号

CLK:クロック信号

ROWCLK:ロウクロック信号

AND:アドレスデコード回路

WL0〜WL6:ワード線

AD,TAD:入力アドレス信号

RAD,CAD:内部アドレス信号

WE,TWE:ライトイネーブル信号

MST:モード選択信号

BM,XBM:動作制御信号

DI:入力データ

DO:出力データ

【特許請求の範囲】

【請求項1】

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力する複数のアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【請求項2】

請求項1において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジである半導体記憶装置。

【請求項3】

請求項2において

さらに,外部からの動作選択信号に基づいて,テストモードであるか否かを検出するテストモード信号回路を有し,

前記テストモード信号回路がテストモードであることを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を前記クロック信号の第2のエッジに応答して所定の論理レベルにリセットし,

前記テストモード信号回路がテストモードでないことを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号をリセットしない半導体記憶装置。

【請求項4】

請求項2において

前記リセット回路は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットし,

前記アドレスデコード回路は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとる半導体記憶装置。

【請求項5】

請求項2において

前記リセット回路は,前記第1,第2の内部アドレス信号とクロック信号とについてNAND演算とNOT演算を行う半導体記憶装置。

【請求項6】

請求項2において

前記リセット回路は,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第1の内部アドレス信号が供給される第1のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第2の内部アドレス信号が供給される第2のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードがグランド電圧に接続され,もう一方のノードは第1のトランスファゲートの他方のノードに接続される第1のNMOSトランジスタと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードにグランド電圧に接続され,もう一方のノードは第2のトランスファゲートの他方のノードに接続される第2のNMOSトランジスタとを有する半導体記憶装置。

【請求項7】

ワード線およびビット線の交差位置に配置されるメモリセルを選択するために入力された複数の入力アドレス信号をデコードするアドレスデコード方法において,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を生成し内部アドレス信号線に出力する内部アドレス信号生成工程と,

前記内部アドレス信号線を伝播してきた前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを論理演算する論理演算工程と

前記論理演算工程の後に,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで,前記第1と第2の内部アドレス信号を一定の論理レベルにリセットするリセット工程とを有するアドレスデコード方法。

【請求項1】

複数のワード線とビット線と前記ワード線およびビット線の交差位置に配置される複数のメモリセルとを有するメモリセルアレイと,

前記メモリセルを選択するために入力された複数の入力アドレス信号をデコードしてワード線又はビット線を選択するアドレスデコーダとを有し,

前記アドレスデコーダは,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を出力する複数のアドレスレジスタと,

前記複数の入力アドレス信号の第1と第2の内部アドレス信号を伝播する複数の内部アドレス信号線を有する内部アドレス信号線網と,

前記アドレスレジスタと前記内部アドレス信号線網の間に設けられ,前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで一定の論理レベルにリセットするリセット回路と,

前記内部アドレス信号線網を介して前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを供給され,当該組合せを論理演算してそれぞれの前記ワード線又はビット線を選択する複数のアドレスデコード回路とを有する半導体記憶装置。

【請求項2】

請求項1において,

前記アドレスサイクルの第1,第2のタイミングは,前記アドレスサイクルに同期したクロック信号の第1のエッジと第2のエッジである半導体記憶装置。

【請求項3】

請求項2において

さらに,外部からの動作選択信号に基づいて,テストモードであるか否かを検出するテストモード信号回路を有し,

前記テストモード信号回路がテストモードであることを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号を前記クロック信号の第2のエッジに応答して所定の論理レベルにリセットし,

前記テストモード信号回路がテストモードでないことを検出したとき,前記リセット回路は前記アドレスレジスタが出力した前記第1と第2の内部アドレス信号をリセットしない半導体記憶装置。

【請求項4】

請求項2において

前記リセット回路は,前記クロック信号の第2のエッジに応答して前記第1と第2の内部アドレス信号をLレベルにリセットし,

前記アドレスデコード回路は,前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せの論理積をとる半導体記憶装置。

【請求項5】

請求項2において

前記リセット回路は,前記第1,第2の内部アドレス信号とクロック信号とについてNAND演算とNOT演算を行う半導体記憶装置。

【請求項6】

請求項2において

前記リセット回路は,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第1の内部アドレス信号が供給される第1のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードに前記第2の内部アドレス信号が供給される第2のトランスファゲートと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードがグランド電圧に接続され,もう一方のノードは第1のトランスファゲートの他方のノードに接続される第1のNMOSトランジスタと,

ゲートに前記クロック信号が供給され,ソースまたはドレインのうちの一方のノードにグランド電圧に接続され,もう一方のノードは第2のトランスファゲートの他方のノードに接続される第2のNMOSトランジスタとを有する半導体記憶装置。

【請求項7】

ワード線およびビット線の交差位置に配置されるメモリセルを選択するために入力された複数の入力アドレス信号をデコードするアドレスデコード方法において,

アドレスサイクルの第1のタイミングで,前記複数の入力アドレス信号それぞれの非反転及び反転論理レベルを有する第1と第2の内部アドレス信号を生成し内部アドレス信号線に出力する内部アドレス信号生成工程と,

前記内部アドレス信号線を伝播してきた前記複数の入力アドレス信号の第1と第2の内部アドレス信号の組合せを論理演算する論理演算工程と

前記論理演算工程の後に,前記アドレスサイクルの前記第1のタイミング後の第2のタイミングで,前記第1と第2の内部アドレス信号を一定の論理レベルにリセットするリセット工程とを有するアドレスデコード方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−54806(P2013−54806A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−192862(P2011−192862)

【出願日】平成23年9月5日(2011.9.5)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月5日(2011.9.5)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]