半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,半導体記憶装置に関する。

【背景技術】

【0002】

一般的なDRAMにおいて,メモリセルは,ワード線とビット線の交差位置に配置され,情報を記憶するキャパシタと,情報の読み書きのためのトランジスタを有する。また,トランジスタは,ゲートをワード線に接続され,ソースをビット線に接続され,ドレインをキャパシタのストレージノードに接続されており,キャパシタは,ストレージノードに記憶データに対応する電荷を蓄積し,ストレージノードに対抗する電極,セルプレート電極は所定の電圧を受ける。読み出し時には,選択され駆動されたワード線によりONされたトランジスタを介してキャパシタに蓄積された電荷がビット線に転送され,ビット線に生じた微少電圧をセンスアンプが増幅する。

【0003】

また,DRAMのビット線構造には,代表的なものとして,オープンビット線方式とフォールデッドビット線方式があり,ビット線とセンスアンプの配置が異なる。フォールデッドビット線方式では,一対のビット線がセンスアンプの片側に延び,各メモリセルの面積は8F2が限界とされている。それに対して,オープンビット線方式では,一対のビット線がセンスアンプを中心に互いに逆方向に延び,各メモリセルの面積を6F2とすることができる。セル面積を小さくできる点でオープンビット線方式はフォールデッドビット線方式より有利であり,例えば特許文献1,2ではオープンビット線方式が採用されている。

【0004】

一方,このようなDRAMに対して情報の読み出しやリフレッシュを行う際,ビット線やセルプレート電極におけるノイズ等による誤作動が問題となっており,特許文献3,4等によるノイズ対策が検討されてきた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−157289号公報

【特許文献2】特開2000−260885号公報

【特許文献3】再公表特許WO00/051184号公報

【特許文献4】特開2002−298576号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

オープンビット線方式では,シールデッド方式よりも一般的にノイズに弱い。読み出し時におけるセンスアンプの増幅動作において,センスアンプが供給電源から長い距離で離れていると,電源線の内部抵抗等により,駆動されたセンスアンプがビット線の電位を高電位内部電圧と低電位内部電圧とに増幅する時に,駆動電流により高電位内部電圧は低下し,低電位内部電圧は上昇する傾向にある。そのため,駆動電圧のアンバランスによりセンスアンプの動作マージンが小さくなってしまい,誤動作が生じる可能性がある。

【0007】

そこで,本発明の目的は,オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供することとする。

【課題を解決するための手段】

【0008】

半導体記憶装置の第1の側面は,

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【発明の効果】

【0009】

半導体記憶装置の第1の側面によれば,センスアンプによるビット線の増幅動作時に発生する電源ノイズを軽減することができる。

【図面の簡単な説明】

【0010】

【図1】本実施の形態におけるDRAMの構成を示すブロック図である。

【図2】本実施の形態におけるオープンビット線方式のメモリセルアレイを示す図である。

【図3】本実施の形態におけるオープンビット線方式のメモリセルのレイアウトと回路を示す図である。

【図4】本実施の形態におけるセンスアンプ回路を示す図である。

【図5】本実施の形態におけるセンスアンプドライバ回路を示す図である。

【図6】本実施の形態における通常モードでのビット線とワード線の電圧の波形を示す図である。

【図7】本実施の形態におけるオーバードライブモードでのビット線とワード線の電圧の波形を示す図である。

【図8】本実施の形態におけるオープンビット線方式のメモリセルアレイと内部電源回路を示す図である。

【図9】第1の実施の形態におけるメモリセルアレイを示す図である。

【図10】第1の実施の形態におけるビット線とワード線の電圧の波形を示す図である。

【図11】第2の実施の形態におけるメモリセルアレイを示す図である。

【図12】第3の実施の形態におけるメモリセルアレイを示す図である。

【図13】第4の実施の形態におけるメモリセルアレイを示す図である。

【図14】第5の実施の形態におけるメモリセルアレイを示す図である。

【図15】第6の実施の形態におけるメモリセルアレイを示す図である。

【図16】第7の実施の形態におけるメモリセルアレイを示す図である。

【図17】第8の実施の形態におけるメモリセルアレイを示す図である。

【図18】第9の実施の形態におけるメモリセルアレイを示す図である。

【図19】第10の実施の形態におけるメモリセルアレイを示す図である。

【図20】第10の実施の形態におけるスイッチ回路を示す図である。

【発明を実施するための形態】

【0011】

以下,図面を用いて本発明の実施の形態について説明する。

【0012】

図1は,本実施の形態におけるDRAMの構成を示すブロック図である。図1のDRAMは,チップ1上に,クロックバッファ2,コマンドデコーダ3,アドレスバッファ4,I/Oバッファ5,アドレスコントローラ6,バーストコントローラ7,メモリコアコントローラ8,バンク9−1〜9−4を有する。

【0013】

また,バンク9−1〜9−4はそれぞれ,複数のメモリセルがマトリックス状に配列されたメモリセルアレイ10,ロウアドレスコントローラ11,コラムアドレスコントローラ12,リードアンプ13,ライトアンプ14を有する。

【0014】

クロックバッファ2は,クロック信号CLK及びクロックイネーブル信号CKEに基づき,内部クロック信号を各機能ブロックへ供給する。

【0015】

コマンドデコーダ3は,チップセレクト信号CSB,ロウアドレスストローブ信号RASB,コラムアドレスストローブ信号CASB,ライトイネーブル信号WEB等のコマンド信号を供給され,コマンド信号のアクティブ,リード,ライト,リフレッシュ,等に応じてメモリコアコントローラ8に動作制御信号を出力する。

【0016】

アドレスバッファ4は,コマンドデコーダ3からの信号に応答してアドレス信号AD及びバンクアドレス信号BAを入力し,内部アドレス信号,内部バンクアドレス信号を出力する。

【0017】

I/Oバッファ5は,データ端子DQに供給される書き込みデータWDを入力し,後述されるデータCWDを出力、また、後述されるデータCRDを受けて読み出し信号RDをデータ端子DQに出力する。

【0018】

アドレスコントローラ6は,アドレスバッファ4からの内部アドレス信号に基づきロウアドレス信号をロウアドレスコントローラ11に,コラムアドレス信号をバーストコントローラ7に出力する。また,アドレスコントローラ6は,アドレスバッファ4からの内部アドレス信号と内部バンクアドレス信号とをメモリコアコントローラ8に出力する。

【0019】

バーストコントローラ7は,アドレスコントローラ6からのコラムアドレス信号を初期コラムアドレスとし,バースト長に応じて初期コラムアドレスを順次インクリメントしたコラムアドレス信号をコラムアドレスコントローラ12に出力する。

【0020】

メモリコアコントローラ8は,コマンドデコーダ3からのコマンド信号と,アドレスコントローラ6からの内部アドレス信号と内部バンク信号とに応じて,バンクの選択,メモリセルアレイ10の書き込み動作や読み出し動作等を制御するタイミング信号を出力する。

【0021】

ロウアドレスコントローラ11は,メモリセルアレイ10のワード線を選択するためにアドレスコントローラ6からのロウアドレス信号をデコードする。

【0022】

コラムアドレスコントローラ12は,メモリセルアレイ10のビット線を選択するためにバーストコントローラ11からのコラムアドレス信号をデコードする。

【0023】

リードアンプ13は,メモリコアコントローラ8からのタイミング信号に応答してメモリセルのデータを読み出して,読み出しデータCRDを出力する。

【0024】

ライトアンプ14は,I/Oバッファ5の出力データCWDを受け,メモリコアコントローラ8からのタイミング信号に応答してメモリセルアレイに書き込みデータ信号を出力する。

【0025】

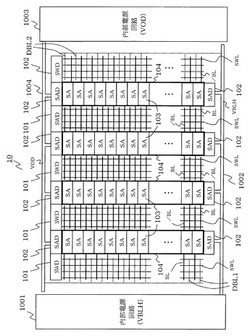

図2は,本実施の形態におけるオープンビット線方式のメモリセルアレイを示す図であり、図1のメモリセルアレイ10に対応している。

【0026】

オープンビット線方式では,図2に示すように,列方向(図中水平方向)に一対のビット線BL,/BLがセンスアンプユニットSA103を中心に両方向に延びて配置される。そしてこのセンスアンプユニット103を行方向(図中垂直方向)に配置したセンスアンプ群104が複数(図中は4つ),列方向に配置されている。各センスアンプ群104は,メモリ内の複数の内部電源回路よりセンスアンプドライバSAD102を介して,高電位内部電圧VBLH,低電位内部電圧VBLL,オーバードライブ電圧VODを供給される。また,各センスアンプ群104は,プリチャージ電圧生成回路よりプリチャージ電圧VBLPを供給される。なお,プリチャージ電圧VBLPは高電位内部電圧VBLHと低電位内部電圧VBLLの例えば中間電圧であり,オーバードライブ電圧VODは高電位内部電圧VBLHよりも高い昇圧電圧である。また,サブワードデコーダ(SWD)101は,ロウアドレスコントローラ11からのデコード信号をデコードしサブワード線SWLを駆動する。メモリセルアレイ103の列方向の両端105,106では,センスアンプ群104に接続されたビット線BL,/BLのうち,両端側の複数のビット線にそれぞれ平行に複数の未使用ビット線(点線)DBL1,DBL2が配置されている。

【0027】

メモリセルアレイ10の列方向の両端105,106にある未使用ビット線DBL1, DBL2はセンスアンプ群104に接続されていない。

【0028】

図3は,本実施の形態におけるオープンビット線方式のメモリセルのレイアウトと回路を示す図である。

【0029】

図3の(1)は,図2のメモリセルアレイ10の左端領域105内の一部の領域を拡大したものである。センスアンプ群104の各センスアンプユニットSA103に接続するビット線BL10〜13と,センスアンプユニットSA103に接続されていない未使用ビット線DBL14〜17が列方向(水平方向)に延びて配置されており,サブワード線SWL10〜13とダミーワード線ISOWL14,15が行方向(垂直方向)に延びて配置されている。ビット線BL10〜13及び未使用ビット線DBL14〜17と,サブワード線SWL10〜13との交差位置に,領域201を単位セルとするメモリセルが配置されている。なお,ダミーワード線ISOWL14,15は,水平方向に隣り合うメモリセルのソース,ドレイン領域間を電気的に分離するために配置され,常時Lレベルに維持される。

【0030】

図3の(1)では,メモリセルアレイの左端にはセンスアンプ群104がないため,ビット線BL10〜13と未使用ビット線DBL14〜17とを交互に配置している。ただし,隣接するセンスアンプ群104の間の領域においても,それぞれのセンスアンプ群104に接続するビット線を図3の(1)の形状のように交互に配置し,ビット線とサブワード線との全ての交差位置に単位セル領域201を配置することで,各メモリセルのサイズを6F2とすることができ,大容量化を実現させている。

【0031】

図3の(2)は単位セル領域201の回路図である。単位セル領域201は,N型セルトランジスタTR21とキャパシタ202とを有する。また,N型セルトランジスタTR21のゲートはサブワード線SWL10とに接続され,N型セルトランジスタTR21とキャパシタ202とはストレージノードコンタクト203で接続し,N型セルトランジスタTR21とビット線BL10とはビット線コンタクト204で接続する。キャパシタ202のセルプレート電極205はセルプレート電圧VCPが印加されている。

【0032】

例えば,メモリセルアレイ10からデータを読み出す場合,サブワードデコーダ101によりサブワード線SWL10が選択されたとき,交差位置全てのN型セルトランジスタTR21がONし,キャパシタ202に蓄積された電荷がビット線BL10〜13に転送され,ビット線BL10〜13の電圧はキャパシタ内の電荷の有無に応じて微少電圧ΔVだけ上昇又は下降する。

【0033】

図4は,本実施の形態におけるセンスアンプ回路を示す図である。図4のセンスアンプユニット103はセンスアンプ回路401とプリチャージ回路402とコラムゲート回路403を有し,センスアンプユニット103を中心に一対のビット線BL,/BLが反対方向に延びている。

【0034】

センスアンプ回路401は,ラッチ回路を構成するP型トランジスタTR41,42とN型トランジスタTR43,44を有し,P型トランジスタTR41,42はセンスアンプドライバ102よりオーバードライブ電圧VOD又は高電位内部電圧VBLHをセンスアンプ駆動信号PSAとして供給され,N型トランジスタTR43,44は低電位内部電圧VBLLをセンスアンプ駆動信号NSAとして供給される。サブワード線の立ち上がりに応じてビット線BL,/BLに微少電圧差ΔVが生じたときに,センスアンプ回路401は,センスアンプ駆動信号PSAにより、電位が高い側のビット線の電圧をオーバードライブ電圧VODまたは高電位内部電圧VBLHに駆動し,センスアンプ駆動信号NSAにより、低い側のビット線の電圧を低電位内部電圧VBLLに駆動して,電圧差を増幅する。

【0035】

プリチャージ回路402は,N型トランジスタTR45〜47を有し,プリチャージ電圧生成回路よりプリチャージ電圧VBLPを供給されている。また,N型トランジスタTR45〜47の各ゲートにはイコライズ信号EQLが供給されており,プリチャージ回路402はHレベルのイコライズ信号EQLに応答してビット線BL,/BLを短絡すると共にプリチャージ電圧VBLPに維持する。

【0036】

コラムゲート回路403は,N型トランジスタで構成されるコラム選択ゲートTR48,49を有し,それぞれのゲートにはコラム選択信号CLが供給されている。また,コラムゲート回路403は,Hレベルのコラム選択信号CLに応答してコラム選択ゲートTR48,49をONし,増幅されたビット線電圧をローカルデータバスLDB,/LDB等を介してリードアンプ13へ出力する。

【0037】

図5は,本実施の形態におけるセンスアンプドライバ回路を示す図である。図5の(1)は,高電位内部電圧VBLHと低電位内部電圧VBLLとを用いた場合(以下通常動作モードとよぶ。)のセンスアンプドライバ102である。一方,図5の(2)はオーバードライブ方式を採用した場合(以下オーバードライブモードと呼ぶ。)のセンスアンプドライバ102である。

【0038】

図5の(1)では,センスアンプドライバ102は,インバータ501とP型トランジスタTR51とN型トランジスタTR52とを有する。センスアンプイネーブル信号SAEZのHレベルに応答し,高電位内部電圧VBLHでセンスアンプ駆動信号PSAをHレベルに駆動し,低電位内部電圧VBLLでセンスアンプ駆動信号NSAをLレベルに駆動する。

【0039】

図5の(2)では,センスアンプドライバ102は高電圧駆動回路502と低電圧駆動回路503を有する。高電圧駆動回路502は,N型トランジスタTR54,55を有し,N型トランジスタTR54,55はそれぞれゲートにセンスアンプイネーブル信号SAEOZ,SAEAZが供給されている。センスアンプイネーブル信号SAEOZのHレベルに応答してN型トランジスタTR54をONにしてオーバードライブ電圧VODでセンスアンプ駆動信号PSAを駆動し,所定の時間を経過した後N型トランジスタTR54をOFFにし,センスアンプイネーブル信号SAEAZのHレベルに応答してN型トランジスタTR55をONにして高電圧VBLHでセンスアンプ駆動信号PSAを駆動する。一方,低電圧駆動回路503は,N型トランジスタTR56を有し,N型トランジスタTR56のゲートにはセンスアンプイネーブル信号SAEZが供給されている。低電圧駆動回路503は,センスアンプイネーブル信号SAEZのHレベルに応答して,低電位内部電圧VBLLでセンスアンプ駆動信号NSAを駆動する。尚、これは構成の一例であり、これに限定されるものではない。例えば、TR54はP型トランジスタで構成し、SAEOZは逆相の信号としてもよい。

【0040】

図6は,本実施の形態における通常モードでのビット線とワード線の電圧の波形を示す図である。図6の波形は,図1〜図5に示すメモリセルアレイからデータを読み出す場合における,ビット線とワード線の電圧の変化を示している。

【0041】

図6に実線で表わしている波形BL10−1,/BL10−1は,図5(1)のセンスアンプドライバ102による高電位内部電圧VBLHと低電位内部電圧VBLLとを用いた通常動作モードの場合における一対のビット線BL10−1,/BL10−1の波形である。まず,非選択状態の電圧VWLLのサブワード線SWL10がサブワードドライバ101によって駆動され,図3の(2)のメモリセルのN型セルトランジスタTR21がONし,キャパシタ202に蓄積されていた電荷がビット線BL10−1に分配される。その結果,時間T0ではともにプリチャージ電圧VBLPであったビット線BL10−1と/BL10−1との間に,時間T1で電圧差ΔVが生じる。また,この時間T1でセンスアンプイネーブル信号SAEZの立ち上がりに応答して図5の(1)のセンスアンプドライバ102から高電位内部電圧VBLHでHレベルに駆動されたセンスアンプ駆動信号PSAnと,低電位内部電圧VBLLでLレベルに駆動されたセンスアンプ駆動信号NSAとが,図4のセンスアンプ回路401に供給され,センスアンプ回路401が増幅動作を開始する。これによりビット線BL10−1は高電位内部電圧VBLHに駆動され,ビット線/BL10−1は低電位内部電圧VBLLに駆動される。そして,コラムゲート回路403が増幅されたビット線BLと/BLの電圧差をローカルデータバスLDB,/LDB等を介してリードアンプ13へ出力する。サブワード線SWL10が立ち下げられた後,時間T3でセンスアンプイネーブル信号SAEZがLレベルに立ち下がると,イコライズ信号EQLの立ち上がりに応答して,プリチャージ回路402により一対のビット線BL10−1,/BL10−1は短絡されると共にプリチャージ電圧VBLPにプリチャージされる。

【0042】

図7は,本実施の形態におけるオーバードライブモードでのビット線とワード線の電圧の波形を示す図である。図7に実線で表わしている波形BL10−2,/BL10−2はオーバードライブモードの場合における一対のビット線BL10−2,/BL10−2の波形であり,破線で表わしている波形PSAoは,オーバードライブモードの場合における図5(2)のPSAに対応する波形である。通常動作モードとは異なり,この場合では,時間T1にセンスアンプイネーブル信号SAEOZ,SAEZに応答してセンスアンプドライバ102からオーバードライブ電圧VODでHレベルに駆動されたセンスアンプ駆動信号PSAと,低電位内部電圧VBLLでLレベルに駆動されたセンスアンプ駆動信号NSAとがセンスアンプ回路401に供給され,センスアンプ回路401は微少電圧ΔVの増幅を開始する。これにより,センスアンプ回路401は,通常動作モードよりも速くビット線BL10−2をオーバードライブ電圧VODに駆動すると共に,ビット線/BL10−2を低電位内部電圧VBLLに駆動する。時間T2にセンスアンプイネーブル信号SAEOZがLレベルに立ち下がり,センスアンプイネーブル信号SAEAZがHレベルに立ち上がると,センスアンプドライバ102によりセンスアンプ駆動信号PSAが高電位内部電圧VBLHに駆動され,ビット線BL10−2は高電位内部電圧VBLHに駆動される。

【0043】

このようにして,メモリセルアレイ10の行方向に配置されたサブワード線の1本がサブワードドライバ101により駆動されると,そのサブワード線に交差するビット線に接続するセンスアンプ群104,すなわちサブワード線を挟む2つのセンスアンプ群104にてそれぞれ,通常動作モード又はオーバードライブモードにてビット線対の電圧の増幅動作が行われる。

【0044】

しかし,この増幅動作では,電源ノイズによって,メモリ内の内部電源回路からセンスアンプ群104に供給される駆動電圧,すなわちVOD−VBLP若しくはVBLH‐VBLPとVBLP‐VBLLにアンバランスが生じる。上記のとおり,サブワードドライバ101によってサブワード線SWL10が選択され,ビット線BLが/BLよりも微少電圧ΔVだけ昇圧すると,センスアンプ駆動信号PSA,NSAを供給されたセンスアンプユニット103で増幅動作が行われる。具体的には,図4のセンスアンプ回路401のPMOSトランジスタTR42のゲート・ソース間電圧がTR41よりも上回るため,センスアンプドライバ102を介して,オーバードライブ電圧VOD又は高電位内部電圧VBLHの内部電源回路から駆動電流がビット線BLに流入し,ビット線BLの電圧が上昇する。また,N型トランジスタTR43のゲート・ソース間電圧がTR44よりも上回るため,センスアンプドライバ102を介して,低電位内部電圧VBLLの内部電源回路へビット線/BLから駆動電流が流出し,ビット線/BLの電圧が降下する。このとき,各内部電源回路とセンスアンプドライバ102との距離が長くなるに従い,各内部電源回路とセンスアンプドライバ102を接続する内部電源配線の抵抗が大きくなる。そのため,センスアンプ回路401に供給されるオーバードライブ電圧VOD又は高電位内部電圧VBLHの電圧が一時的に低下する内部電源ノイズが大きくなり,また,低電位内部電圧VBLLの電圧が一時的に上昇する内部電源ノイズが大きくなる。その一例として,図8を説明する。

【0045】

図8は,本実施の形態におけるオープンビット線方式のメモリセルアレイと内部電源回路を示す図である。図8のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,高電位内部電圧VBLHを生成する内部電源回路701,703を配置し,内部電源配線702,704を介してそれぞれ低電位内部電圧VBLL,高電位内部電圧VBLHを各センスアンプドライバ102に供給している。

【0046】

メモリセルアレイ10の列方向の左端のセンスアンプ群104は内部電源回路703から最も離れており,内部電源配線704が長いため抵抗が大きい。その結果,増幅動作時には,左端のセンスアンプ群104に内部電源配線704を経由して供給される高電位内部電圧VBLHが一時的に大きく低下する。一方,内部電源回路701に対しては,左端のセンスアンプ群104がもっとも近接しており,内部電源配線702は短く抵抗は小さいため,その内部電源配線702を経由して供給される低電位内部電圧VBLLのノイズは小さい。そのため左端のセンスアンプ群104では,プリチャージ電圧VBLPに対する昇圧レベル(VBLH)は,プリチャージ電圧VBLPに対する降圧レベル(VBLL)より小さくなり,この駆動電圧のアンバランスに起因して,センスアンプ回路401が逆論理に誤動作する可能性が高くなる。

【0047】

同様にして,メモリセルアレイ10の列方向の右端のセンスアンプ群104は,高電位内部電圧VBLHの電源ノイズは小さいが,低電位内部電圧VBLLの電源ノイズは大きく,同様に駆動電圧のアンバランスが生じ,誤作動を招くことがある。

【0048】

このように,電源ノイズによって駆動電圧のアンバランスが生じたことでセンスアンプの動作マージンが小さくなる。そして,増幅動作時に仮にビット線BL又は/BLがメモリセルアレイ10の行方向に隣接するビット線のカップリングノイズの影響をさらに受けると,ビット線BLと/BLの電圧レベルが逆転しDRAMの誤動作が引き起こされやすくなる。

【0049】

そこで以下の実施の形態では,上記を鑑み,電源ノイズを軽減した半導体記憶装置について説明する。

【0050】

[第1の実施の形態]

図9は,第1の実施の形態におけるメモリセルアレイを示す図である。図9のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,高電位内部電圧VBLHを生成する内部電源回路801,803を配置し,内部電源配線802,804を介してそれぞれ低電位内部電圧VBLL,高電位内部電圧VBLHを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路803の内部電源配線804に接続し,右端の未使用ビット線DBL2は左端の内部電源回路801の内部電源配線802に接続している。この構成により内部電源回路803,801から内部電源配線804,802を介して,内部電源回路803,801の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれ高電位内部電圧VBLH,低電位内部電圧VBLLに充電され,各内部電圧VBLH,VBLLの電源キャパシタとして動作し,各内部電圧VBLH,VBLLの両端位置での電源ノイズを吸収する。

【0051】

図9に示したメモリセルアレイの動作の例として,通常動作モードにおける動作について説明する。図10は,第1の実施の形態におけるビット線とワード線の電圧の波形を示す図である。

【0052】

図10では,通常動作モードにおいて,図9の列方向(水平方向)の左端のメモリセルアレイ内のサブワード線SWL10が選択されたときの左端のセンスアンプ群104に接続する一対のビット線BL10−3,/BL10−3と,未使用ビット線DBL1とセンスアンプ群104に供給される高電位内部電圧VHとの電圧の変化を示している。実線がビット線BL10−3,/BL10−3の波形,太線が未使用ビット線DBL1の波形,破線がセンスアンプ群104に供給される高電位内部電圧VHの波形である。

【0053】

サブワード線SWL10が,時間T10でサブワードドライバ101によって駆動され,非選択電圧VWLLから昇圧電圧VWLHに立ち上がると,図3の(2)のメモリセルのN型セルトランジスタTR21がONし,キャパシタ202に蓄積された電荷がビット線BL10−3に分配される。その結果,ともにプリチャージ電圧VBLPであったビット線BL10−3と/BL10−3との間に,時間T11で電圧差ΔVが生じる。また,サブワード線SWL10が駆動されたことで,未使用ビット線DBL1とサブワード線SWL10の交差位置に配置された未使用セルのN型セルトランジスタTR21がONするため,内部電源回路803から内部電源配線804と未使用ビット線DBL1を介して未使用セルのキャパシタ202に電荷が流入する。この影響を受けて,未使用ビット線DBL1とそれに接続される内部電源配線804の電圧は,サブワード線SWD10の立ち上がり時に高電位内部電圧VBLHからわずかに下がるが,内部電源回路803から電荷を供給されるため,再び高電位内部電圧VBLHとなる。

【0054】

そして時間T11に,センスアンプイネーブル信号SAEZの立ち上がりに応答して図5の(1)のセンスアンプドライバ102によりセンスアンプ駆動信号PSAが高電位内部電圧VBLHに立ち上がり,センスアンプ駆動信号NSAが低電位内部電圧VBLLに立ち下がり,図4のセンスアンプ回路401の増幅動作が開始する。このとき,センスアンプ回路401の駆動動作による電流により,内部電源配線804から図9中の左端のセンスアンプ群104に供給される電圧が波形N(鎖線)のように低下することでセンスアンプ回路401の駆動電圧VBLH‐VBLP,VBLP‐VBLLにアンバランスが生じ,動作が反転する可能性があった。しかし,本実施の形態による例では,時間ΔTで左端のセンスアンプ群104に近接する未使用ビット線DBL1とその未使用セルのキャパシタ202とに蓄積された電荷により内部電源配線804からセンスアンプ群104に供給される内部電圧の低下が軽減され,センスアンプの誤動作が抑制される。未使用ビット線DBL1は,時間ΔTの間に電圧が高電位内部電圧VBLHより若干下がるが,内部電源803から電荷を供給されるため再び高電位内部電圧VBLHとなる。

【0055】

時間T12にサブワード線SWL10が非選択状態となり,時間T13に未使用セルのN型セルトランジスタTR21がOFFされる。サブワード線SWL10が非選択状態となった後でも,未使用ビット線DBL1は,内部電源配線804を介して内部電源回路803に接続しているため,高電位内部電圧VBLHに駆動されたままである。

【0056】

時間T14でセンスアンプイネーブル信号SAEZがLレベルに立ち下がると,センスアンプ回路401の動作は停止し,イコライズ信号EQLの立ち上がりに応答して,プリチャージ回路402により一対のビット線BL10−3,/BL10−3はプリチャージ電圧VBLPにプリチャージされる。

【0057】

このように図9のメモリセルアレイ10では,時間T10以前と時間T13以降は,未使用ビット線DBL1が,時間T10からT13までの間は未使用ビット線DBL1と未使用セルのキャパシタ202とが電源安定化容量として作用する。

【0058】

したがって,センスアンプイネーブル信号SAEZの立ち上がりによりセンスアンプユニット103がビット線対を駆動する時の駆動電流で内部電源配線804が供給する電圧が低下する時に,未使用ビット線DBL1と未使用セルのキャパシタ202とが電源安定化容量として作用し,その電圧低下を抑制することができる。

【0059】

低電位内部電圧VBLLの内部電源回路801に接続している,メモリセルアレイ10の右端にある未使用ビット線DBL2と未使用セルのキャパシタ202についても,上記と同様な原理で電源安定化容量として作用し,ビット線/BL10−3を低電位内部電圧VBLLに降圧するときに発生する電源ノイズ(低電位内部電圧VBLLの上昇)を軽減することができる。

【0060】

以上より,未使用ビット線や未使用セルのキャパシタ202を電源安定化容量として使用することにより,電源ノイズを軽減して,センスアンプユニット103の駆動電圧のアンバランスを防ぐことができる。

【0061】

[第2の実施の形態]

低電位内部電圧VBLLがグランド電源である場合,通常,低電位内部電圧VBLLはセンスアンプドライバ102だけでなく,ロウアドレスコントローラ11等他の機能回路にも使用されることが多いため,低電位内部電圧VBLLを生成する内部電源回路の内部電源配線がチップ1上に張り巡らされている。そのため低電位内部電圧VBLLを生成する内部電源回路の内部電源配線の抵抗が低く,図4のセンスアンプ回路401がビット線/BLを低電位内部電圧VBLLへ増幅するときの電源ノイズが小さい。

【0062】

一方,高電位内部電圧VBLHやオーバードライブ電圧VODは用途が限定されており,それぞれの内部電源回路の内部電源配線は限られたエリアに配置されている。そのため,低電位内部電圧VBLLと比較すると,高電位内部電圧VBLHやオーバードライブ電圧VODを生成する内部電源回路の内部電源配線の抵抗は大きく,図4のセンスアンプ回路401がビット線BLを高電位内部電圧VBLH又はオーバードライブ電圧VODに増幅するときの電源ノイズも大きい。そこで,第2の実施の形態では,高電位内部電圧VBLHやオーバードライブ電圧VODの内部電源回路を使用する。

【0063】

図11は,第2の実施の形態におけるメモリセルアレイを示す図である。図11のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLH,オーバードライブ電圧VODを生成する内部電源回路1001,1003を配置し,内部電源配線1002,1004を介してそれぞれ高電位内部電圧VBLH,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は内部電源配線1004に接続し,右端の未使用ビット線DBL2は内部電源配線1002に接続している。この構成により内部電源回路1003,1001から内部電源配線1004,1002を介して,内部電源回路1003,1001の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれオーバードライブ電圧VOD,高電位内部電圧VBLHに充電され,各内部電圧VOD,VBLHの電源キャパシタとして動作し,各内部電圧VOD,VBLHの電源ノイズを吸収する。なお,図11では,低電位内部電圧VBLLの内部電源配線は省略されている。

【0064】

このように,第2の実施の形態では,高電位内部電圧VBLHとオーバードライブ電圧VODの電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。

【0065】

[第3の実施の形態]

図12は,第3の実施の形態におけるメモリセルアレイを示す図である。図12のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,オーバードライブ電圧VODを生成する内部電源回路1101,1103を配置し,内部電源配線1102,1104を介してそれぞれ低電位内部電圧VBLL,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路1103の内部電源配線1104に接続し,右端の未使用ビット線DBL2は左端の内部電源回路1101の内部電源配線1102に接続している。この構成により内部電源回路1103,1101から内部電源配線1104,1102を介して,内部電源回路1103,1101の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれオーバードライブ電圧VOD,低電位内部電圧VBLLに充電され,各内部電圧VOD,VBLLの電源キャパシタとして動作し,各内部電圧VOD,VBLLの両端位置での電源ノイズを吸収する。

【0066】

このように,第3の実施の形態では,低電位内部電圧VBLLとオーバードライブ電圧VODの電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。したがって,第2の実施の形態とは異なり,低電位内部電圧VBLLの電源ノイズが大きく,また,図4のセンスアンプ回路401が,オーバードライブモードでビット線BL,/BLの電圧レベルを早く増幅することを優先するような場合には,第3の実施の形態が適している。

【0067】

[第4の実施の形態]

図13は,第4の実施の形態におけるメモリセルアレイを示す図である。図13のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の左端にオーバードライブ電圧VOD,高電位内部電圧VBLHを生成する内部電源回路1201と1202を配置し,右端に低電位内部電圧VBLLを生成する内部電源回路1204を配置し,それぞれ内部電源配線1205,1203,1206を介してオーバードライブ電圧VOD,高電位内部電圧VBLH,低電位内部電圧VBLLを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路1204の内部電源配線1206に接続し,右端の未使用ビット線DBL2は左端の内部電源回路1201の内部電源配線1205に接続し,右端の未使用ビット線DBL3は左端の内部電源回路1202の内部電源配線1203に接続している。つまり,左端に内部電源回路1201,1202を配置しているため,右端の未使用ビット線をDBL2,DBL3の2組に分けて,それぞれを内部電源回路1201,1202に接続している。

【0068】

この構成により内部電源回路1204,1201,1202から内部電源配線1206,1205,1203を介して,内部電源回路1204,1201,1202の反対の端にある未使用ビット線DBL1,DBL2,DBL3の配線容量はそれぞれ低電位内部電圧VBLL,オーバードライブ電圧VOD,高電位内部電圧VBLHに充電され,各内部電圧VBLL,VOD,VBLHの電源キャパシタとして動作し,各内部電圧VBLL,VOD,VBLHの両端位置での電源ノイズを吸収する。

【0069】

このように,第4の実施の形態では,高電位内部電圧VBLH,オーバードライブ電圧VOD,低電位内部電圧VBLLの全ての電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。

【0070】

また,オーバードライブ電圧VOD,高電位内部電圧VBLH,低電位内部電圧VBLLの内部電源回路の配置について,図13に限定せずに,各内部電圧の電源ノイズの大きさに応じて内部電源回路を配置することもできる。例えば,オーバードライブ電圧VODの電源ノイズが高電位内部電圧VBLH,低電位内部電圧VBLLの電源ノイズよりも大きい場合には,オーバードライブ電圧VODの内部電源回路が,未使用ビット線の電源安定化容量としての作用効果を最も得られることが望ましい。そこで,このような場合には左端に高電位内部電圧VBLHと低電位内部電圧VBLLの内部電源回路,右端にオーバードライブ電圧VODの内部電源回路を配置する。そして,高電位内部電圧VBLHと低電位内部電圧VBLLの内部電源回路は,右端の未使用ビット線に接続し,オーバードライブ電圧VODの内部電源回路は左端の全ての未使用ビット線と接続する。

【0071】

なお,図13では,メモリセルアレイ10の右端にある未使用ビット線DBL2とDBL3はビット線/BLを挟んで,DBL3,/BL,DBL2,/BL,DBL3,/BL,DBL2・・・と,交互にサブワード線SWLと交差しているが,これに限定されない。例えば,DBL2,/BL,DBL2,/BL,DBL2,/BL,DBL3,/BL,DBL3,/BL,DBL3・・・等何本かおきに未使用ビット線DBL2とDBL3が入れ換わるように配置し,又は,メモリセルアレイ10の行方向(垂直方向)に上半分には未使用ビット線DBL2を配置し,下半分には未使用ビット線DBL3を配置する等のようにすることも可能である。

【0072】

[第5の実施の形態]

図14は,第5の実施の形態におけるメモリセルアレイを示す図である。図14のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLH,オーバードライブ電圧VODを生成する内部電源回路1301,1303を配置し,内部電源配線1302,1304を介してそれぞれ高電位内部電圧VBLH,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1と右端の未使用ビット線DBL2は左端の内部電源回路1301の内部電源配線1302に接続し,左端の未使用ビット線DBL3と右端の未使用ビット線DBL4は右端の内部電源回路1303の内部電源配線1304に接続している。この構成により内部電源回路1301から内部電源配線1302を介して,未使用ビット線DBL1とDBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。また,内部電源回路1303から内部電源配線1304を介して,未使用ビット線DBL3とDBL4の配線容量はオーバードライブ電圧VODに充電され,オーバードライブ電圧VODの電源キャパシタとして動作し,オーバードライブ電圧VODの電源ノイズを吸収する。

【0073】

このように,内部電源回路と両端にある未使用ビット線とを接続することにより,内部電源回路の近くにあるセンスアンプ群に対しても,未使用ビット線や未使用セルの電源安定化容量の効果があり,内部電圧VBLH,VODの電圧降下を防ぐことができる。

【0074】

なお,未使用ビット線DBL1〜DBL4の配置については図14に限定されない。図14では,メモリセルアレイ10の左端にある未使用ビット線DBL1とDBL3はそれぞれビット線BLを挟んで,DBL3,BL,DBL1,BL,DBL3,BL,DBL1・・・・交互にサブワード線SWLと交差しているが,これに限定されない。例えば,DBL1,BL,DBL1,BL,DBL3,BL,DBL3・・・等何本かおきに未使用ビット線DBL2とDBL3が入れ換わるように配置し,又は,メモリセルアレイ10の行方向(垂直方向)に上半分には未使用ビット線DBL3を配置し下半分には未使用ビット線DBL1を配置する等のようにすることも可能である。右端の未使用ビット線DBL2とDBL4についても同様のことが言える。

【0075】

さらに,内部電源回路と未使用ビット線との接続の組合せについても,図14の配置に限定されない。例えば,左端の内部電源回路1301と右端の未使用ビット線DBL2を接続し,右端の内部電源回路1303と左端の未使用ビット線DBL1,DBL3および右端の未使用ビット線DBL4とを接続して,内部電源回路1303のオーバードライブ電圧VOD側の電源安定化容量を増やし電源ノイズをより小さくすることができる。

【0076】

[第6の実施の形態]

図15は,第6の実施の形態におけるメモリセルアレイを示す図である。図15は,図14のオーバードライブ電源VODを生成する内部電源回路1303を,低電位内部電圧VBLLを生成する内部電源回路1403に置き換えたものである。

【0077】

この構成により高電位内部電圧VBLHを生成する内部電源回路1401から内部電源配線1402を介して,未使用ビット線DBL1とDBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。また,低電位内部電圧VBLLを生成する内部電源回路1403から内部電源配線1404を介して,未使用ビット線DBL3とDBL4の配線容量は低電位内部電圧VBLLに充電され,低電位内部電圧VBLLの電源キャパシタとして動作し,低電位内部電圧VBLLの電源ノイズを吸収する。

【0078】

したがって,第5の実施の形態と同様に,内部電源回路と両端にある未使用ビット線とを接続することにより,内部電源回路の近くにあるセンスアンプ群に対しても,未使用ビット線や未使用セルの電源安定化容量の効果があり,内部電圧VBLH,VBLLの電源ノイズを防ぐことができる。

【0079】

なお,未使用ビット線DBL1〜DBL4の配置,内部電源回路と未使用ビット線との接続の組合せについては,第5の実施の形態と同様,図15に限定されない。

【0080】

[第7の実施の形態]

図16は,第7の実施の形態におけるメモリセルアレイを示す図である。図16のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLHを生成する内部電源回路1501,1503を配置し,内部電源配線1502,1504を介してそれぞれ高電位内部電圧VBLHを各センスアンプドライバ102に供給している。左端の未使用ビット線DBL1と右端の未使用ビット線DBL2は,共に内部電源配線1502と1504に接続している。この構成により内部電源回路1501,1503から内部電源配線1502,1504を介して,未使用ビット線DBL1,DBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。

【0081】

したがって,第7の実施の形態は,例えば,高電位内部電圧VBLHの電源ノイズが他の内部電源VOD,VBLLと比べて大きく,図9のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,高電位内部電圧VBLHについて多くの電源安定化容量が必要な場合に適している。

【0082】

[第8の実施の形態]

図17は,第8の実施の形態におけるメモリセルアレイを示す図である。図17は,図16の内部電源回路1501,1503を低電位内部電圧VBLLを生成する内部電源回路1601,1603に置き換えたものである。この構成により内部電源回路1601,1603から内部電源配線1602,1604を介して,未使用ビット線DBL1,DBL2の配線容量は低電位内部電圧VBLLに充電され,低電位内部電圧VBLLの電源キャパシタとして動作し,低電位内部電圧VBLLの電源ノイズを吸収する。

【0083】

したがって,第8の実施の形態は,例えば,低電位内部電圧VBLLの電源ノイズが他の内部電源VBLH,VODと比べて大きく,図9のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,低電位内部電圧VBLLについて多くの電源安定化容量が必要な場合に適している。

【0084】

[第9の実施の形態]

図18は,第9の実施の形態におけるメモリセルアレイを示す図である。図18は,図16の内部電源回路1501,1503をオーバードライブ電圧VODを生成する内部電源回路1701,1703に置き換えたものである。この構成により内部電源回路1701,1703から内部電源配線1702,1704を介して,未使用ビット線DBL1,DBL2の配線容量はオーバードライブ電圧VODに充電され,オーバードライブ電圧VODの電源キャパシタとして動作し,オーバードライブ電圧VODの電源ノイズを吸収する。

【0085】

したがって,第9の実施の形態は,例えば,オーバードライブ電圧VODの電源ノイズが他の内部電源VBLH,VBLLと比べて大きく,図11のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,オーバードライブ電圧VODについて多くの電源安定化容量が必要な場合に適している。

【0086】

[第10の実施の形態]

上記の第1〜第9の実施の形態では,未使用ビット線と内部電源配線とを接続し,未使用ビット線を電源安定化容量として使用している。しかし,DRAMの出荷前に行われるストレス試験では,各ビット線間の短絡箇所を検出するために,メモリセルアレイ10の列方向(水平方向)の両端の未使用ビット線を,テストケースに応じた電圧で駆動できるようにすることも要求される。そこで,第10の実施の形態では未使用ビット線と内部電源配線との間にスイッチ回路を配置し,ストレス試験の時に未使用ビット線と内部電源配線との接続を解除して任意の電圧で駆動できるようにする。

【0087】

図19は,第10の実施の形態におけるメモリセルアレイを示す図である。図19のメモリセルアレイ10は,図11に示したメモリセルアレイの列方向(水平方向)の両端にスイッチ回路SW1,SW2を配置したものである。スイッチ回路SW1,SW2は内部電源配線1804,1802と未使用ビット線DBL1,DBL2とを接続する。したがって,スイッチ回路SW1,SW2のスイッチがONのときは,未使用ビット線DBL1とDBL2は,各内部電圧VOD,VBLHの電源キャパシタとして動作し,各内部電圧VOD,VBLHの電源ノイズを吸収する。一方,ストレステスト等の試験を行うときは,スイッチ回路SW1,SW2は,内部電源配線1804,1802と未使用ビット線DBL1,DBL2との接続を解除して,未使用ビット線DBL1とDBL2をテストケースに応じた電圧で駆動する。

【0088】

図20は,第10の実施の形態におけるスイッチ回路を示す図である。図20のスイッチ回路は,NORゲート1901と,NANDゲート1902〜1904,インバータ1905,1906と,P型トランジスタTR191,TR192と,N型トランジスタTR193,TR194とを有し,図19のスイッチ回路SW1をあらわしている。P型トランジスタTR191,TR192のソースは,オーバードライブ電圧VOD,高電位内部電圧VBLHを生成する内部電源回路に接続されており,N型トランジスタTR193,TR194のソースは,プリチャージ電圧生成回路,低電位内部電圧VBLLを生成するの内部電源回路に接続している。試験信号TESTは,未使用ビット線DBL1と内部電源配線1804との接続を制御し,試験電圧選択信号TS1,TS2は,未使用ビット線DBL1と内部電源配線1804との接続を解除したときにおける未使用ビット線DBL1の駆動電圧を,高電位内部電圧VBLH,プリチャージ電圧VBLP,低電位内部電圧VBLLのいずれかに制御する。

【0089】

例えば,未使用ビット線DBL1を電源安定化容量として使用するときは,試験信号TESTをLレベルにしてP型トランジスタTR191をONにして,未使用ビット線DBL1をオーバードライブ電圧VODに接続する。ストレス試験の時は,未使用ビット線DBL1と内部電源配線1804との接続を解除するため,試験信号TESTをHレベルにしてP型トランジスタTR191をOFFにする。そして,試験電圧信号TS1,TS2をそれぞれHレベル,Lレベルにすると,未使用ビット線DBL1は高電位内部電圧VBLHで駆動される。また,試験電圧信号TS1,TS2がともにLレベルであれば,未使用ビット線DBL1はプリチャージ電圧VBLPで駆動し,試験電圧信号TS1,TS2がLレベル,Hレベルであれば,低電位内部電圧VBLLで駆動する。

【0090】

以上のとおり,スイッチ回路SW1は,未使用ビット線をオーバードライブ電圧VODを生成する内部電源回路の内部電源配線と接続し,ストレステストの時には,未使用ビット線を内部電圧VBLH,VBLP,VBLLのいずれかに駆動することができる。

【0091】

スイッチ回路SW2についても,図19と同様なスイッチ回路を使用することで,未使用ビット線DBL2を電源安定化容量として使用するだけでなく,ストレス試験時に未使用ビット線DBL2をテストケースに応じた電圧で駆動することができる。

【0092】

以上の実施の形態をまとめると,次の付記のとおりである。

【0093】

(付記1)

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【0094】

(付記2)

付記1において,

前記ワード線は,該ワード線を挟む隣接する2つのセンスアンプ群にそれぞれ接続する前記ビット線に交互に交差し,前記メモリセルアレイの前記列方向の両端では前記ビット線及び未使用ビット線とに交互に交差する半導体記憶装置。

【0095】

(付記3)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に第1及び第2の内部電源を生成する第1及び第2の内部電源回路をそれぞれ配置し,前記第1端の前記複数の未使用ビット線は,前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0096】

(付記4)

付記3において,

前記第1の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記プリチャージ電圧より低く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動される半導体記憶装置。

【0097】

(付記5)

付記3において,

前記第1及び第2の内部電源はビット線のプリチャージ電圧より高く,前記第1の内部電源は前記第2の内部電源より高く,

さらに,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路を有し,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第3の内部電源に駆動され,その後,第1の内部電源に駆動された方のビット線は,第2の内部電源に駆動される半導体記憶装置。

【0098】

(付記6)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源を生成する第1の内部電源回路を,第2端に第2及び第3の内部電源を生成する第2及び第3の内部電源回路を配置し,前記第1端の前記複数の未使用ビット線のうち,一部は前記第2の内部電源回路の第2の内部電源配線に接続し,残りは前記第3の内部電源回路の第3の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0099】

(付記7)

付記6において,

前記第1の内部電源は前記プリチャージ電圧より低く,前記第2及び第3の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記第3の内部電源より高く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動され,その後,第2の内部電源に駆動された方のビット線は,第3の内部電源に駆動される半導体記憶装置。

【0100】

(付記8)

付記1又は2において,

さらに前記メモリアレイの前記列方向の前記他方に配置された複数の未使用ビット線に加えて,一端に配置された複数の未使用ビット線が,前記内部電源配線に接続されている半導体記憶装置。

【0101】

(付記9)

付記8において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源回路を,第2端に第2の内部電源回路を配置し,前記第1端には複数の第1及び第2の未使用ビット線を配置し,前記第2端には複数の第3及び第4の未使用ビット線を配置し,前記第1及び第3の未使用ビット線は前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2及び第4の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0102】

(付記10)

付記9において,

付記4と同じ。

【0103】

(付記11)

付記9において,

付記5と同じ。

【0104】

(付記12)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に前記内部電源回路を配置し,前記第1端及び第2端の前記複数の未使用ビット線は共に,前記第1端及び第2端の前記内部電源回路の内部電源配線にそれぞれ接続する半導体記憶装置。

【0105】

(付記13)

付記12において,

前記一対のビット線は,プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに,前記プリチャージ電圧より高い第1の内部電源又は前記プリチャージ電圧より低い第3の内部電源に駆動され,その後,前記第1の内部電源に駆動された方のビット線は,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源に駆動され,

前記第1,第2又は第3の内部電源は,前記内部電源回路で生成される半導体記憶装置。

【0106】

(付記14)

付記1又は2において,

通常動作時は,前記未使用ビット線と前記内部電源配線とを接続し,テスト時は前記未使用ビット線をテスト用電圧に接続するスイッチ回路を有する半導体記憶装置。

【0107】

(付記15)

付記14において,

プリチャージ電圧を生成するプリチャージ電圧生成回路と,ビット線の前記プリチャージ電圧より高い第1の内部電源を生成する第1の内部電源回路と,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源を生成する第2の内部電源回路と,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路とを有し,

前記内部電源配線は,前記第1,第2又は第3の内部電源回路の内部電源配線であり,

前記テスト用電圧は,前記第1,第2及び第3の内部電源回路のうち前記内部電源配線と接続する内部電源回路を除いた内部電源回路,又は前記プリチャージ電圧生成回路である半導体記憶装置。

【符号の説明】

【0108】

BL,/BL:ビット線

DBL:未使用ビット線

SWL:サブワード線

SA :センスアンプユニット

SAD:センスアンプドライバ

SWD:サブワードデコーダ

VBLH :高電位内部電圧

VBLL :低電位内部電圧

VBLP :プリチャージ電圧

VOD :オーバードライブ電圧

【技術分野】

【0001】

本発明は,半導体記憶装置に関する。

【背景技術】

【0002】

一般的なDRAMにおいて,メモリセルは,ワード線とビット線の交差位置に配置され,情報を記憶するキャパシタと,情報の読み書きのためのトランジスタを有する。また,トランジスタは,ゲートをワード線に接続され,ソースをビット線に接続され,ドレインをキャパシタのストレージノードに接続されており,キャパシタは,ストレージノードに記憶データに対応する電荷を蓄積し,ストレージノードに対抗する電極,セルプレート電極は所定の電圧を受ける。読み出し時には,選択され駆動されたワード線によりONされたトランジスタを介してキャパシタに蓄積された電荷がビット線に転送され,ビット線に生じた微少電圧をセンスアンプが増幅する。

【0003】

また,DRAMのビット線構造には,代表的なものとして,オープンビット線方式とフォールデッドビット線方式があり,ビット線とセンスアンプの配置が異なる。フォールデッドビット線方式では,一対のビット線がセンスアンプの片側に延び,各メモリセルの面積は8F2が限界とされている。それに対して,オープンビット線方式では,一対のビット線がセンスアンプを中心に互いに逆方向に延び,各メモリセルの面積を6F2とすることができる。セル面積を小さくできる点でオープンビット線方式はフォールデッドビット線方式より有利であり,例えば特許文献1,2ではオープンビット線方式が採用されている。

【0004】

一方,このようなDRAMに対して情報の読み出しやリフレッシュを行う際,ビット線やセルプレート電極におけるノイズ等による誤作動が問題となっており,特許文献3,4等によるノイズ対策が検討されてきた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−157289号公報

【特許文献2】特開2000−260885号公報

【特許文献3】再公表特許WO00/051184号公報

【特許文献4】特開2002−298576号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

オープンビット線方式では,シールデッド方式よりも一般的にノイズに弱い。読み出し時におけるセンスアンプの増幅動作において,センスアンプが供給電源から長い距離で離れていると,電源線の内部抵抗等により,駆動されたセンスアンプがビット線の電位を高電位内部電圧と低電位内部電圧とに増幅する時に,駆動電流により高電位内部電圧は低下し,低電位内部電圧は上昇する傾向にある。そのため,駆動電圧のアンバランスによりセンスアンプの動作マージンが小さくなってしまい,誤動作が生じる可能性がある。

【0007】

そこで,本発明の目的は,オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供することとする。

【課題を解決するための手段】

【0008】

半導体記憶装置の第1の側面は,

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【発明の効果】

【0009】

半導体記憶装置の第1の側面によれば,センスアンプによるビット線の増幅動作時に発生する電源ノイズを軽減することができる。

【図面の簡単な説明】

【0010】

【図1】本実施の形態におけるDRAMの構成を示すブロック図である。

【図2】本実施の形態におけるオープンビット線方式のメモリセルアレイを示す図である。

【図3】本実施の形態におけるオープンビット線方式のメモリセルのレイアウトと回路を示す図である。

【図4】本実施の形態におけるセンスアンプ回路を示す図である。

【図5】本実施の形態におけるセンスアンプドライバ回路を示す図である。

【図6】本実施の形態における通常モードでのビット線とワード線の電圧の波形を示す図である。

【図7】本実施の形態におけるオーバードライブモードでのビット線とワード線の電圧の波形を示す図である。

【図8】本実施の形態におけるオープンビット線方式のメモリセルアレイと内部電源回路を示す図である。

【図9】第1の実施の形態におけるメモリセルアレイを示す図である。

【図10】第1の実施の形態におけるビット線とワード線の電圧の波形を示す図である。

【図11】第2の実施の形態におけるメモリセルアレイを示す図である。

【図12】第3の実施の形態におけるメモリセルアレイを示す図である。

【図13】第4の実施の形態におけるメモリセルアレイを示す図である。

【図14】第5の実施の形態におけるメモリセルアレイを示す図である。

【図15】第6の実施の形態におけるメモリセルアレイを示す図である。

【図16】第7の実施の形態におけるメモリセルアレイを示す図である。

【図17】第8の実施の形態におけるメモリセルアレイを示す図である。

【図18】第9の実施の形態におけるメモリセルアレイを示す図である。

【図19】第10の実施の形態におけるメモリセルアレイを示す図である。

【図20】第10の実施の形態におけるスイッチ回路を示す図である。

【発明を実施するための形態】

【0011】

以下,図面を用いて本発明の実施の形態について説明する。

【0012】

図1は,本実施の形態におけるDRAMの構成を示すブロック図である。図1のDRAMは,チップ1上に,クロックバッファ2,コマンドデコーダ3,アドレスバッファ4,I/Oバッファ5,アドレスコントローラ6,バーストコントローラ7,メモリコアコントローラ8,バンク9−1〜9−4を有する。

【0013】

また,バンク9−1〜9−4はそれぞれ,複数のメモリセルがマトリックス状に配列されたメモリセルアレイ10,ロウアドレスコントローラ11,コラムアドレスコントローラ12,リードアンプ13,ライトアンプ14を有する。

【0014】

クロックバッファ2は,クロック信号CLK及びクロックイネーブル信号CKEに基づき,内部クロック信号を各機能ブロックへ供給する。

【0015】

コマンドデコーダ3は,チップセレクト信号CSB,ロウアドレスストローブ信号RASB,コラムアドレスストローブ信号CASB,ライトイネーブル信号WEB等のコマンド信号を供給され,コマンド信号のアクティブ,リード,ライト,リフレッシュ,等に応じてメモリコアコントローラ8に動作制御信号を出力する。

【0016】

アドレスバッファ4は,コマンドデコーダ3からの信号に応答してアドレス信号AD及びバンクアドレス信号BAを入力し,内部アドレス信号,内部バンクアドレス信号を出力する。

【0017】

I/Oバッファ5は,データ端子DQに供給される書き込みデータWDを入力し,後述されるデータCWDを出力、また、後述されるデータCRDを受けて読み出し信号RDをデータ端子DQに出力する。

【0018】

アドレスコントローラ6は,アドレスバッファ4からの内部アドレス信号に基づきロウアドレス信号をロウアドレスコントローラ11に,コラムアドレス信号をバーストコントローラ7に出力する。また,アドレスコントローラ6は,アドレスバッファ4からの内部アドレス信号と内部バンクアドレス信号とをメモリコアコントローラ8に出力する。

【0019】

バーストコントローラ7は,アドレスコントローラ6からのコラムアドレス信号を初期コラムアドレスとし,バースト長に応じて初期コラムアドレスを順次インクリメントしたコラムアドレス信号をコラムアドレスコントローラ12に出力する。

【0020】

メモリコアコントローラ8は,コマンドデコーダ3からのコマンド信号と,アドレスコントローラ6からの内部アドレス信号と内部バンク信号とに応じて,バンクの選択,メモリセルアレイ10の書き込み動作や読み出し動作等を制御するタイミング信号を出力する。

【0021】

ロウアドレスコントローラ11は,メモリセルアレイ10のワード線を選択するためにアドレスコントローラ6からのロウアドレス信号をデコードする。

【0022】

コラムアドレスコントローラ12は,メモリセルアレイ10のビット線を選択するためにバーストコントローラ11からのコラムアドレス信号をデコードする。

【0023】

リードアンプ13は,メモリコアコントローラ8からのタイミング信号に応答してメモリセルのデータを読み出して,読み出しデータCRDを出力する。

【0024】

ライトアンプ14は,I/Oバッファ5の出力データCWDを受け,メモリコアコントローラ8からのタイミング信号に応答してメモリセルアレイに書き込みデータ信号を出力する。

【0025】

図2は,本実施の形態におけるオープンビット線方式のメモリセルアレイを示す図であり、図1のメモリセルアレイ10に対応している。

【0026】

オープンビット線方式では,図2に示すように,列方向(図中水平方向)に一対のビット線BL,/BLがセンスアンプユニットSA103を中心に両方向に延びて配置される。そしてこのセンスアンプユニット103を行方向(図中垂直方向)に配置したセンスアンプ群104が複数(図中は4つ),列方向に配置されている。各センスアンプ群104は,メモリ内の複数の内部電源回路よりセンスアンプドライバSAD102を介して,高電位内部電圧VBLH,低電位内部電圧VBLL,オーバードライブ電圧VODを供給される。また,各センスアンプ群104は,プリチャージ電圧生成回路よりプリチャージ電圧VBLPを供給される。なお,プリチャージ電圧VBLPは高電位内部電圧VBLHと低電位内部電圧VBLLの例えば中間電圧であり,オーバードライブ電圧VODは高電位内部電圧VBLHよりも高い昇圧電圧である。また,サブワードデコーダ(SWD)101は,ロウアドレスコントローラ11からのデコード信号をデコードしサブワード線SWLを駆動する。メモリセルアレイ103の列方向の両端105,106では,センスアンプ群104に接続されたビット線BL,/BLのうち,両端側の複数のビット線にそれぞれ平行に複数の未使用ビット線(点線)DBL1,DBL2が配置されている。

【0027】

メモリセルアレイ10の列方向の両端105,106にある未使用ビット線DBL1, DBL2はセンスアンプ群104に接続されていない。

【0028】

図3は,本実施の形態におけるオープンビット線方式のメモリセルのレイアウトと回路を示す図である。

【0029】

図3の(1)は,図2のメモリセルアレイ10の左端領域105内の一部の領域を拡大したものである。センスアンプ群104の各センスアンプユニットSA103に接続するビット線BL10〜13と,センスアンプユニットSA103に接続されていない未使用ビット線DBL14〜17が列方向(水平方向)に延びて配置されており,サブワード線SWL10〜13とダミーワード線ISOWL14,15が行方向(垂直方向)に延びて配置されている。ビット線BL10〜13及び未使用ビット線DBL14〜17と,サブワード線SWL10〜13との交差位置に,領域201を単位セルとするメモリセルが配置されている。なお,ダミーワード線ISOWL14,15は,水平方向に隣り合うメモリセルのソース,ドレイン領域間を電気的に分離するために配置され,常時Lレベルに維持される。

【0030】

図3の(1)では,メモリセルアレイの左端にはセンスアンプ群104がないため,ビット線BL10〜13と未使用ビット線DBL14〜17とを交互に配置している。ただし,隣接するセンスアンプ群104の間の領域においても,それぞれのセンスアンプ群104に接続するビット線を図3の(1)の形状のように交互に配置し,ビット線とサブワード線との全ての交差位置に単位セル領域201を配置することで,各メモリセルのサイズを6F2とすることができ,大容量化を実現させている。

【0031】

図3の(2)は単位セル領域201の回路図である。単位セル領域201は,N型セルトランジスタTR21とキャパシタ202とを有する。また,N型セルトランジスタTR21のゲートはサブワード線SWL10とに接続され,N型セルトランジスタTR21とキャパシタ202とはストレージノードコンタクト203で接続し,N型セルトランジスタTR21とビット線BL10とはビット線コンタクト204で接続する。キャパシタ202のセルプレート電極205はセルプレート電圧VCPが印加されている。

【0032】

例えば,メモリセルアレイ10からデータを読み出す場合,サブワードデコーダ101によりサブワード線SWL10が選択されたとき,交差位置全てのN型セルトランジスタTR21がONし,キャパシタ202に蓄積された電荷がビット線BL10〜13に転送され,ビット線BL10〜13の電圧はキャパシタ内の電荷の有無に応じて微少電圧ΔVだけ上昇又は下降する。

【0033】

図4は,本実施の形態におけるセンスアンプ回路を示す図である。図4のセンスアンプユニット103はセンスアンプ回路401とプリチャージ回路402とコラムゲート回路403を有し,センスアンプユニット103を中心に一対のビット線BL,/BLが反対方向に延びている。

【0034】

センスアンプ回路401は,ラッチ回路を構成するP型トランジスタTR41,42とN型トランジスタTR43,44を有し,P型トランジスタTR41,42はセンスアンプドライバ102よりオーバードライブ電圧VOD又は高電位内部電圧VBLHをセンスアンプ駆動信号PSAとして供給され,N型トランジスタTR43,44は低電位内部電圧VBLLをセンスアンプ駆動信号NSAとして供給される。サブワード線の立ち上がりに応じてビット線BL,/BLに微少電圧差ΔVが生じたときに,センスアンプ回路401は,センスアンプ駆動信号PSAにより、電位が高い側のビット線の電圧をオーバードライブ電圧VODまたは高電位内部電圧VBLHに駆動し,センスアンプ駆動信号NSAにより、低い側のビット線の電圧を低電位内部電圧VBLLに駆動して,電圧差を増幅する。

【0035】

プリチャージ回路402は,N型トランジスタTR45〜47を有し,プリチャージ電圧生成回路よりプリチャージ電圧VBLPを供給されている。また,N型トランジスタTR45〜47の各ゲートにはイコライズ信号EQLが供給されており,プリチャージ回路402はHレベルのイコライズ信号EQLに応答してビット線BL,/BLを短絡すると共にプリチャージ電圧VBLPに維持する。

【0036】

コラムゲート回路403は,N型トランジスタで構成されるコラム選択ゲートTR48,49を有し,それぞれのゲートにはコラム選択信号CLが供給されている。また,コラムゲート回路403は,Hレベルのコラム選択信号CLに応答してコラム選択ゲートTR48,49をONし,増幅されたビット線電圧をローカルデータバスLDB,/LDB等を介してリードアンプ13へ出力する。

【0037】

図5は,本実施の形態におけるセンスアンプドライバ回路を示す図である。図5の(1)は,高電位内部電圧VBLHと低電位内部電圧VBLLとを用いた場合(以下通常動作モードとよぶ。)のセンスアンプドライバ102である。一方,図5の(2)はオーバードライブ方式を採用した場合(以下オーバードライブモードと呼ぶ。)のセンスアンプドライバ102である。

【0038】

図5の(1)では,センスアンプドライバ102は,インバータ501とP型トランジスタTR51とN型トランジスタTR52とを有する。センスアンプイネーブル信号SAEZのHレベルに応答し,高電位内部電圧VBLHでセンスアンプ駆動信号PSAをHレベルに駆動し,低電位内部電圧VBLLでセンスアンプ駆動信号NSAをLレベルに駆動する。

【0039】

図5の(2)では,センスアンプドライバ102は高電圧駆動回路502と低電圧駆動回路503を有する。高電圧駆動回路502は,N型トランジスタTR54,55を有し,N型トランジスタTR54,55はそれぞれゲートにセンスアンプイネーブル信号SAEOZ,SAEAZが供給されている。センスアンプイネーブル信号SAEOZのHレベルに応答してN型トランジスタTR54をONにしてオーバードライブ電圧VODでセンスアンプ駆動信号PSAを駆動し,所定の時間を経過した後N型トランジスタTR54をOFFにし,センスアンプイネーブル信号SAEAZのHレベルに応答してN型トランジスタTR55をONにして高電圧VBLHでセンスアンプ駆動信号PSAを駆動する。一方,低電圧駆動回路503は,N型トランジスタTR56を有し,N型トランジスタTR56のゲートにはセンスアンプイネーブル信号SAEZが供給されている。低電圧駆動回路503は,センスアンプイネーブル信号SAEZのHレベルに応答して,低電位内部電圧VBLLでセンスアンプ駆動信号NSAを駆動する。尚、これは構成の一例であり、これに限定されるものではない。例えば、TR54はP型トランジスタで構成し、SAEOZは逆相の信号としてもよい。

【0040】

図6は,本実施の形態における通常モードでのビット線とワード線の電圧の波形を示す図である。図6の波形は,図1〜図5に示すメモリセルアレイからデータを読み出す場合における,ビット線とワード線の電圧の変化を示している。

【0041】

図6に実線で表わしている波形BL10−1,/BL10−1は,図5(1)のセンスアンプドライバ102による高電位内部電圧VBLHと低電位内部電圧VBLLとを用いた通常動作モードの場合における一対のビット線BL10−1,/BL10−1の波形である。まず,非選択状態の電圧VWLLのサブワード線SWL10がサブワードドライバ101によって駆動され,図3の(2)のメモリセルのN型セルトランジスタTR21がONし,キャパシタ202に蓄積されていた電荷がビット線BL10−1に分配される。その結果,時間T0ではともにプリチャージ電圧VBLPであったビット線BL10−1と/BL10−1との間に,時間T1で電圧差ΔVが生じる。また,この時間T1でセンスアンプイネーブル信号SAEZの立ち上がりに応答して図5の(1)のセンスアンプドライバ102から高電位内部電圧VBLHでHレベルに駆動されたセンスアンプ駆動信号PSAnと,低電位内部電圧VBLLでLレベルに駆動されたセンスアンプ駆動信号NSAとが,図4のセンスアンプ回路401に供給され,センスアンプ回路401が増幅動作を開始する。これによりビット線BL10−1は高電位内部電圧VBLHに駆動され,ビット線/BL10−1は低電位内部電圧VBLLに駆動される。そして,コラムゲート回路403が増幅されたビット線BLと/BLの電圧差をローカルデータバスLDB,/LDB等を介してリードアンプ13へ出力する。サブワード線SWL10が立ち下げられた後,時間T3でセンスアンプイネーブル信号SAEZがLレベルに立ち下がると,イコライズ信号EQLの立ち上がりに応答して,プリチャージ回路402により一対のビット線BL10−1,/BL10−1は短絡されると共にプリチャージ電圧VBLPにプリチャージされる。

【0042】

図7は,本実施の形態におけるオーバードライブモードでのビット線とワード線の電圧の波形を示す図である。図7に実線で表わしている波形BL10−2,/BL10−2はオーバードライブモードの場合における一対のビット線BL10−2,/BL10−2の波形であり,破線で表わしている波形PSAoは,オーバードライブモードの場合における図5(2)のPSAに対応する波形である。通常動作モードとは異なり,この場合では,時間T1にセンスアンプイネーブル信号SAEOZ,SAEZに応答してセンスアンプドライバ102からオーバードライブ電圧VODでHレベルに駆動されたセンスアンプ駆動信号PSAと,低電位内部電圧VBLLでLレベルに駆動されたセンスアンプ駆動信号NSAとがセンスアンプ回路401に供給され,センスアンプ回路401は微少電圧ΔVの増幅を開始する。これにより,センスアンプ回路401は,通常動作モードよりも速くビット線BL10−2をオーバードライブ電圧VODに駆動すると共に,ビット線/BL10−2を低電位内部電圧VBLLに駆動する。時間T2にセンスアンプイネーブル信号SAEOZがLレベルに立ち下がり,センスアンプイネーブル信号SAEAZがHレベルに立ち上がると,センスアンプドライバ102によりセンスアンプ駆動信号PSAが高電位内部電圧VBLHに駆動され,ビット線BL10−2は高電位内部電圧VBLHに駆動される。

【0043】

このようにして,メモリセルアレイ10の行方向に配置されたサブワード線の1本がサブワードドライバ101により駆動されると,そのサブワード線に交差するビット線に接続するセンスアンプ群104,すなわちサブワード線を挟む2つのセンスアンプ群104にてそれぞれ,通常動作モード又はオーバードライブモードにてビット線対の電圧の増幅動作が行われる。

【0044】

しかし,この増幅動作では,電源ノイズによって,メモリ内の内部電源回路からセンスアンプ群104に供給される駆動電圧,すなわちVOD−VBLP若しくはVBLH‐VBLPとVBLP‐VBLLにアンバランスが生じる。上記のとおり,サブワードドライバ101によってサブワード線SWL10が選択され,ビット線BLが/BLよりも微少電圧ΔVだけ昇圧すると,センスアンプ駆動信号PSA,NSAを供給されたセンスアンプユニット103で増幅動作が行われる。具体的には,図4のセンスアンプ回路401のPMOSトランジスタTR42のゲート・ソース間電圧がTR41よりも上回るため,センスアンプドライバ102を介して,オーバードライブ電圧VOD又は高電位内部電圧VBLHの内部電源回路から駆動電流がビット線BLに流入し,ビット線BLの電圧が上昇する。また,N型トランジスタTR43のゲート・ソース間電圧がTR44よりも上回るため,センスアンプドライバ102を介して,低電位内部電圧VBLLの内部電源回路へビット線/BLから駆動電流が流出し,ビット線/BLの電圧が降下する。このとき,各内部電源回路とセンスアンプドライバ102との距離が長くなるに従い,各内部電源回路とセンスアンプドライバ102を接続する内部電源配線の抵抗が大きくなる。そのため,センスアンプ回路401に供給されるオーバードライブ電圧VOD又は高電位内部電圧VBLHの電圧が一時的に低下する内部電源ノイズが大きくなり,また,低電位内部電圧VBLLの電圧が一時的に上昇する内部電源ノイズが大きくなる。その一例として,図8を説明する。

【0045】

図8は,本実施の形態におけるオープンビット線方式のメモリセルアレイと内部電源回路を示す図である。図8のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,高電位内部電圧VBLHを生成する内部電源回路701,703を配置し,内部電源配線702,704を介してそれぞれ低電位内部電圧VBLL,高電位内部電圧VBLHを各センスアンプドライバ102に供給している。

【0046】

メモリセルアレイ10の列方向の左端のセンスアンプ群104は内部電源回路703から最も離れており,内部電源配線704が長いため抵抗が大きい。その結果,増幅動作時には,左端のセンスアンプ群104に内部電源配線704を経由して供給される高電位内部電圧VBLHが一時的に大きく低下する。一方,内部電源回路701に対しては,左端のセンスアンプ群104がもっとも近接しており,内部電源配線702は短く抵抗は小さいため,その内部電源配線702を経由して供給される低電位内部電圧VBLLのノイズは小さい。そのため左端のセンスアンプ群104では,プリチャージ電圧VBLPに対する昇圧レベル(VBLH)は,プリチャージ電圧VBLPに対する降圧レベル(VBLL)より小さくなり,この駆動電圧のアンバランスに起因して,センスアンプ回路401が逆論理に誤動作する可能性が高くなる。

【0047】

同様にして,メモリセルアレイ10の列方向の右端のセンスアンプ群104は,高電位内部電圧VBLHの電源ノイズは小さいが,低電位内部電圧VBLLの電源ノイズは大きく,同様に駆動電圧のアンバランスが生じ,誤作動を招くことがある。

【0048】

このように,電源ノイズによって駆動電圧のアンバランスが生じたことでセンスアンプの動作マージンが小さくなる。そして,増幅動作時に仮にビット線BL又は/BLがメモリセルアレイ10の行方向に隣接するビット線のカップリングノイズの影響をさらに受けると,ビット線BLと/BLの電圧レベルが逆転しDRAMの誤動作が引き起こされやすくなる。

【0049】

そこで以下の実施の形態では,上記を鑑み,電源ノイズを軽減した半導体記憶装置について説明する。

【0050】

[第1の実施の形態]

図9は,第1の実施の形態におけるメモリセルアレイを示す図である。図9のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,高電位内部電圧VBLHを生成する内部電源回路801,803を配置し,内部電源配線802,804を介してそれぞれ低電位内部電圧VBLL,高電位内部電圧VBLHを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路803の内部電源配線804に接続し,右端の未使用ビット線DBL2は左端の内部電源回路801の内部電源配線802に接続している。この構成により内部電源回路803,801から内部電源配線804,802を介して,内部電源回路803,801の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれ高電位内部電圧VBLH,低電位内部電圧VBLLに充電され,各内部電圧VBLH,VBLLの電源キャパシタとして動作し,各内部電圧VBLH,VBLLの両端位置での電源ノイズを吸収する。

【0051】

図9に示したメモリセルアレイの動作の例として,通常動作モードにおける動作について説明する。図10は,第1の実施の形態におけるビット線とワード線の電圧の波形を示す図である。

【0052】

図10では,通常動作モードにおいて,図9の列方向(水平方向)の左端のメモリセルアレイ内のサブワード線SWL10が選択されたときの左端のセンスアンプ群104に接続する一対のビット線BL10−3,/BL10−3と,未使用ビット線DBL1とセンスアンプ群104に供給される高電位内部電圧VHとの電圧の変化を示している。実線がビット線BL10−3,/BL10−3の波形,太線が未使用ビット線DBL1の波形,破線がセンスアンプ群104に供給される高電位内部電圧VHの波形である。

【0053】

サブワード線SWL10が,時間T10でサブワードドライバ101によって駆動され,非選択電圧VWLLから昇圧電圧VWLHに立ち上がると,図3の(2)のメモリセルのN型セルトランジスタTR21がONし,キャパシタ202に蓄積された電荷がビット線BL10−3に分配される。その結果,ともにプリチャージ電圧VBLPであったビット線BL10−3と/BL10−3との間に,時間T11で電圧差ΔVが生じる。また,サブワード線SWL10が駆動されたことで,未使用ビット線DBL1とサブワード線SWL10の交差位置に配置された未使用セルのN型セルトランジスタTR21がONするため,内部電源回路803から内部電源配線804と未使用ビット線DBL1を介して未使用セルのキャパシタ202に電荷が流入する。この影響を受けて,未使用ビット線DBL1とそれに接続される内部電源配線804の電圧は,サブワード線SWD10の立ち上がり時に高電位内部電圧VBLHからわずかに下がるが,内部電源回路803から電荷を供給されるため,再び高電位内部電圧VBLHとなる。

【0054】

そして時間T11に,センスアンプイネーブル信号SAEZの立ち上がりに応答して図5の(1)のセンスアンプドライバ102によりセンスアンプ駆動信号PSAが高電位内部電圧VBLHに立ち上がり,センスアンプ駆動信号NSAが低電位内部電圧VBLLに立ち下がり,図4のセンスアンプ回路401の増幅動作が開始する。このとき,センスアンプ回路401の駆動動作による電流により,内部電源配線804から図9中の左端のセンスアンプ群104に供給される電圧が波形N(鎖線)のように低下することでセンスアンプ回路401の駆動電圧VBLH‐VBLP,VBLP‐VBLLにアンバランスが生じ,動作が反転する可能性があった。しかし,本実施の形態による例では,時間ΔTで左端のセンスアンプ群104に近接する未使用ビット線DBL1とその未使用セルのキャパシタ202とに蓄積された電荷により内部電源配線804からセンスアンプ群104に供給される内部電圧の低下が軽減され,センスアンプの誤動作が抑制される。未使用ビット線DBL1は,時間ΔTの間に電圧が高電位内部電圧VBLHより若干下がるが,内部電源803から電荷を供給されるため再び高電位内部電圧VBLHとなる。

【0055】

時間T12にサブワード線SWL10が非選択状態となり,時間T13に未使用セルのN型セルトランジスタTR21がOFFされる。サブワード線SWL10が非選択状態となった後でも,未使用ビット線DBL1は,内部電源配線804を介して内部電源回路803に接続しているため,高電位内部電圧VBLHに駆動されたままである。

【0056】

時間T14でセンスアンプイネーブル信号SAEZがLレベルに立ち下がると,センスアンプ回路401の動作は停止し,イコライズ信号EQLの立ち上がりに応答して,プリチャージ回路402により一対のビット線BL10−3,/BL10−3はプリチャージ電圧VBLPにプリチャージされる。

【0057】

このように図9のメモリセルアレイ10では,時間T10以前と時間T13以降は,未使用ビット線DBL1が,時間T10からT13までの間は未使用ビット線DBL1と未使用セルのキャパシタ202とが電源安定化容量として作用する。

【0058】

したがって,センスアンプイネーブル信号SAEZの立ち上がりによりセンスアンプユニット103がビット線対を駆動する時の駆動電流で内部電源配線804が供給する電圧が低下する時に,未使用ビット線DBL1と未使用セルのキャパシタ202とが電源安定化容量として作用し,その電圧低下を抑制することができる。

【0059】

低電位内部電圧VBLLの内部電源回路801に接続している,メモリセルアレイ10の右端にある未使用ビット線DBL2と未使用セルのキャパシタ202についても,上記と同様な原理で電源安定化容量として作用し,ビット線/BL10−3を低電位内部電圧VBLLに降圧するときに発生する電源ノイズ(低電位内部電圧VBLLの上昇)を軽減することができる。

【0060】

以上より,未使用ビット線や未使用セルのキャパシタ202を電源安定化容量として使用することにより,電源ノイズを軽減して,センスアンプユニット103の駆動電圧のアンバランスを防ぐことができる。

【0061】

[第2の実施の形態]

低電位内部電圧VBLLがグランド電源である場合,通常,低電位内部電圧VBLLはセンスアンプドライバ102だけでなく,ロウアドレスコントローラ11等他の機能回路にも使用されることが多いため,低電位内部電圧VBLLを生成する内部電源回路の内部電源配線がチップ1上に張り巡らされている。そのため低電位内部電圧VBLLを生成する内部電源回路の内部電源配線の抵抗が低く,図4のセンスアンプ回路401がビット線/BLを低電位内部電圧VBLLへ増幅するときの電源ノイズが小さい。

【0062】

一方,高電位内部電圧VBLHやオーバードライブ電圧VODは用途が限定されており,それぞれの内部電源回路の内部電源配線は限られたエリアに配置されている。そのため,低電位内部電圧VBLLと比較すると,高電位内部電圧VBLHやオーバードライブ電圧VODを生成する内部電源回路の内部電源配線の抵抗は大きく,図4のセンスアンプ回路401がビット線BLを高電位内部電圧VBLH又はオーバードライブ電圧VODに増幅するときの電源ノイズも大きい。そこで,第2の実施の形態では,高電位内部電圧VBLHやオーバードライブ電圧VODの内部電源回路を使用する。

【0063】

図11は,第2の実施の形態におけるメモリセルアレイを示す図である。図11のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLH,オーバードライブ電圧VODを生成する内部電源回路1001,1003を配置し,内部電源配線1002,1004を介してそれぞれ高電位内部電圧VBLH,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は内部電源配線1004に接続し,右端の未使用ビット線DBL2は内部電源配線1002に接続している。この構成により内部電源回路1003,1001から内部電源配線1004,1002を介して,内部電源回路1003,1001の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれオーバードライブ電圧VOD,高電位内部電圧VBLHに充電され,各内部電圧VOD,VBLHの電源キャパシタとして動作し,各内部電圧VOD,VBLHの電源ノイズを吸収する。なお,図11では,低電位内部電圧VBLLの内部電源配線は省略されている。

【0064】

このように,第2の実施の形態では,高電位内部電圧VBLHとオーバードライブ電圧VODの電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。

【0065】

[第3の実施の形態]

図12は,第3の実施の形態におけるメモリセルアレイを示す図である。図12のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に低電位内部電圧VBLL,オーバードライブ電圧VODを生成する内部電源回路1101,1103を配置し,内部電源配線1102,1104を介してそれぞれ低電位内部電圧VBLL,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路1103の内部電源配線1104に接続し,右端の未使用ビット線DBL2は左端の内部電源回路1101の内部電源配線1102に接続している。この構成により内部電源回路1103,1101から内部電源配線1104,1102を介して,内部電源回路1103,1101の反対の端にある未使用ビット線DBL1,DBL2の配線容量はそれぞれオーバードライブ電圧VOD,低電位内部電圧VBLLに充電され,各内部電圧VOD,VBLLの電源キャパシタとして動作し,各内部電圧VOD,VBLLの両端位置での電源ノイズを吸収する。

【0066】

このように,第3の実施の形態では,低電位内部電圧VBLLとオーバードライブ電圧VODの電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。したがって,第2の実施の形態とは異なり,低電位内部電圧VBLLの電源ノイズが大きく,また,図4のセンスアンプ回路401が,オーバードライブモードでビット線BL,/BLの電圧レベルを早く増幅することを優先するような場合には,第3の実施の形態が適している。

【0067】

[第4の実施の形態]

図13は,第4の実施の形態におけるメモリセルアレイを示す図である。図13のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の左端にオーバードライブ電圧VOD,高電位内部電圧VBLHを生成する内部電源回路1201と1202を配置し,右端に低電位内部電圧VBLLを生成する内部電源回路1204を配置し,それぞれ内部電源配線1205,1203,1206を介してオーバードライブ電圧VOD,高電位内部電圧VBLH,低電位内部電圧VBLLを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1は右端の内部電源回路1204の内部電源配線1206に接続し,右端の未使用ビット線DBL2は左端の内部電源回路1201の内部電源配線1205に接続し,右端の未使用ビット線DBL3は左端の内部電源回路1202の内部電源配線1203に接続している。つまり,左端に内部電源回路1201,1202を配置しているため,右端の未使用ビット線をDBL2,DBL3の2組に分けて,それぞれを内部電源回路1201,1202に接続している。

【0068】

この構成により内部電源回路1204,1201,1202から内部電源配線1206,1205,1203を介して,内部電源回路1204,1201,1202の反対の端にある未使用ビット線DBL1,DBL2,DBL3の配線容量はそれぞれ低電位内部電圧VBLL,オーバードライブ電圧VOD,高電位内部電圧VBLHに充電され,各内部電圧VBLL,VOD,VBLHの電源キャパシタとして動作し,各内部電圧VBLL,VOD,VBLHの両端位置での電源ノイズを吸収する。

【0069】

このように,第4の実施の形態では,高電位内部電圧VBLH,オーバードライブ電圧VOD,低電位内部電圧VBLLの全ての電源ノイズを軽減して,駆動電圧のアンバランスを防ぐことができる。

【0070】

また,オーバードライブ電圧VOD,高電位内部電圧VBLH,低電位内部電圧VBLLの内部電源回路の配置について,図13に限定せずに,各内部電圧の電源ノイズの大きさに応じて内部電源回路を配置することもできる。例えば,オーバードライブ電圧VODの電源ノイズが高電位内部電圧VBLH,低電位内部電圧VBLLの電源ノイズよりも大きい場合には,オーバードライブ電圧VODの内部電源回路が,未使用ビット線の電源安定化容量としての作用効果を最も得られることが望ましい。そこで,このような場合には左端に高電位内部電圧VBLHと低電位内部電圧VBLLの内部電源回路,右端にオーバードライブ電圧VODの内部電源回路を配置する。そして,高電位内部電圧VBLHと低電位内部電圧VBLLの内部電源回路は,右端の未使用ビット線に接続し,オーバードライブ電圧VODの内部電源回路は左端の全ての未使用ビット線と接続する。

【0071】

なお,図13では,メモリセルアレイ10の右端にある未使用ビット線DBL2とDBL3はビット線/BLを挟んで,DBL3,/BL,DBL2,/BL,DBL3,/BL,DBL2・・・と,交互にサブワード線SWLと交差しているが,これに限定されない。例えば,DBL2,/BL,DBL2,/BL,DBL2,/BL,DBL3,/BL,DBL3,/BL,DBL3・・・等何本かおきに未使用ビット線DBL2とDBL3が入れ換わるように配置し,又は,メモリセルアレイ10の行方向(垂直方向)に上半分には未使用ビット線DBL2を配置し,下半分には未使用ビット線DBL3を配置する等のようにすることも可能である。

【0072】

[第5の実施の形態]

図14は,第5の実施の形態におけるメモリセルアレイを示す図である。図14のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLH,オーバードライブ電圧VODを生成する内部電源回路1301,1303を配置し,内部電源配線1302,1304を介してそれぞれ高電位内部電圧VBLH,オーバードライブ電圧VODを各センスアンプドライバ102に供給している。そして,左端の未使用ビット線DBL1と右端の未使用ビット線DBL2は左端の内部電源回路1301の内部電源配線1302に接続し,左端の未使用ビット線DBL3と右端の未使用ビット線DBL4は右端の内部電源回路1303の内部電源配線1304に接続している。この構成により内部電源回路1301から内部電源配線1302を介して,未使用ビット線DBL1とDBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。また,内部電源回路1303から内部電源配線1304を介して,未使用ビット線DBL3とDBL4の配線容量はオーバードライブ電圧VODに充電され,オーバードライブ電圧VODの電源キャパシタとして動作し,オーバードライブ電圧VODの電源ノイズを吸収する。

【0073】

このように,内部電源回路と両端にある未使用ビット線とを接続することにより,内部電源回路の近くにあるセンスアンプ群に対しても,未使用ビット線や未使用セルの電源安定化容量の効果があり,内部電圧VBLH,VODの電圧降下を防ぐことができる。

【0074】

なお,未使用ビット線DBL1〜DBL4の配置については図14に限定されない。図14では,メモリセルアレイ10の左端にある未使用ビット線DBL1とDBL3はそれぞれビット線BLを挟んで,DBL3,BL,DBL1,BL,DBL3,BL,DBL1・・・・交互にサブワード線SWLと交差しているが,これに限定されない。例えば,DBL1,BL,DBL1,BL,DBL3,BL,DBL3・・・等何本かおきに未使用ビット線DBL2とDBL3が入れ換わるように配置し,又は,メモリセルアレイ10の行方向(垂直方向)に上半分には未使用ビット線DBL3を配置し下半分には未使用ビット線DBL1を配置する等のようにすることも可能である。右端の未使用ビット線DBL2とDBL4についても同様のことが言える。

【0075】

さらに,内部電源回路と未使用ビット線との接続の組合せについても,図14の配置に限定されない。例えば,左端の内部電源回路1301と右端の未使用ビット線DBL2を接続し,右端の内部電源回路1303と左端の未使用ビット線DBL1,DBL3および右端の未使用ビット線DBL4とを接続して,内部電源回路1303のオーバードライブ電圧VOD側の電源安定化容量を増やし電源ノイズをより小さくすることができる。

【0076】

[第6の実施の形態]

図15は,第6の実施の形態におけるメモリセルアレイを示す図である。図15は,図14のオーバードライブ電源VODを生成する内部電源回路1303を,低電位内部電圧VBLLを生成する内部電源回路1403に置き換えたものである。

【0077】

この構成により高電位内部電圧VBLHを生成する内部電源回路1401から内部電源配線1402を介して,未使用ビット線DBL1とDBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。また,低電位内部電圧VBLLを生成する内部電源回路1403から内部電源配線1404を介して,未使用ビット線DBL3とDBL4の配線容量は低電位内部電圧VBLLに充電され,低電位内部電圧VBLLの電源キャパシタとして動作し,低電位内部電圧VBLLの電源ノイズを吸収する。

【0078】

したがって,第5の実施の形態と同様に,内部電源回路と両端にある未使用ビット線とを接続することにより,内部電源回路の近くにあるセンスアンプ群に対しても,未使用ビット線や未使用セルの電源安定化容量の効果があり,内部電圧VBLH,VBLLの電源ノイズを防ぐことができる。

【0079】

なお,未使用ビット線DBL1〜DBL4の配置,内部電源回路と未使用ビット線との接続の組合せについては,第5の実施の形態と同様,図15に限定されない。

【0080】

[第7の実施の形態]

図16は,第7の実施の形態におけるメモリセルアレイを示す図である。図16のメモリセルアレイ10は,図2に示したメモリセルアレイ10の列方向(水平方向)の両端に高電位内部電圧VBLHを生成する内部電源回路1501,1503を配置し,内部電源配線1502,1504を介してそれぞれ高電位内部電圧VBLHを各センスアンプドライバ102に供給している。左端の未使用ビット線DBL1と右端の未使用ビット線DBL2は,共に内部電源配線1502と1504に接続している。この構成により内部電源回路1501,1503から内部電源配線1502,1504を介して,未使用ビット線DBL1,DBL2の配線容量は高電位内部電圧VBLHに充電され,高電位内部電圧VBLHの電源キャパシタとして動作し,高電位内部電圧VBLHの電源ノイズを吸収する。

【0081】

したがって,第7の実施の形態は,例えば,高電位内部電圧VBLHの電源ノイズが他の内部電源VOD,VBLLと比べて大きく,図9のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,高電位内部電圧VBLHについて多くの電源安定化容量が必要な場合に適している。

【0082】

[第8の実施の形態]

図17は,第8の実施の形態におけるメモリセルアレイを示す図である。図17は,図16の内部電源回路1501,1503を低電位内部電圧VBLLを生成する内部電源回路1601,1603に置き換えたものである。この構成により内部電源回路1601,1603から内部電源配線1602,1604を介して,未使用ビット線DBL1,DBL2の配線容量は低電位内部電圧VBLLに充電され,低電位内部電圧VBLLの電源キャパシタとして動作し,低電位内部電圧VBLLの電源ノイズを吸収する。

【0083】

したがって,第8の実施の形態は,例えば,低電位内部電圧VBLLの電源ノイズが他の内部電源VBLH,VODと比べて大きく,図9のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,低電位内部電圧VBLLについて多くの電源安定化容量が必要な場合に適している。

【0084】

[第9の実施の形態]

図18は,第9の実施の形態におけるメモリセルアレイを示す図である。図18は,図16の内部電源回路1501,1503をオーバードライブ電圧VODを生成する内部電源回路1701,1703に置き換えたものである。この構成により内部電源回路1701,1703から内部電源配線1702,1704を介して,未使用ビット線DBL1,DBL2の配線容量はオーバードライブ電圧VODに充電され,オーバードライブ電圧VODの電源キャパシタとして動作し,オーバードライブ電圧VODの電源ノイズを吸収する。

【0085】

したがって,第9の実施の形態は,例えば,オーバードライブ電圧VODの電源ノイズが他の内部電源VBLH,VBLLと比べて大きく,図11のように内部電源回路と内部電源回路の反対側の端の未使用ビット線とを接続しただけでは電源ノイズを小さくすることができず,オーバードライブ電圧VODについて多くの電源安定化容量が必要な場合に適している。

【0086】

[第10の実施の形態]

上記の第1〜第9の実施の形態では,未使用ビット線と内部電源配線とを接続し,未使用ビット線を電源安定化容量として使用している。しかし,DRAMの出荷前に行われるストレス試験では,各ビット線間の短絡箇所を検出するために,メモリセルアレイ10の列方向(水平方向)の両端の未使用ビット線を,テストケースに応じた電圧で駆動できるようにすることも要求される。そこで,第10の実施の形態では未使用ビット線と内部電源配線との間にスイッチ回路を配置し,ストレス試験の時に未使用ビット線と内部電源配線との接続を解除して任意の電圧で駆動できるようにする。

【0087】

図19は,第10の実施の形態におけるメモリセルアレイを示す図である。図19のメモリセルアレイ10は,図11に示したメモリセルアレイの列方向(水平方向)の両端にスイッチ回路SW1,SW2を配置したものである。スイッチ回路SW1,SW2は内部電源配線1804,1802と未使用ビット線DBL1,DBL2とを接続する。したがって,スイッチ回路SW1,SW2のスイッチがONのときは,未使用ビット線DBL1とDBL2は,各内部電圧VOD,VBLHの電源キャパシタとして動作し,各内部電圧VOD,VBLHの電源ノイズを吸収する。一方,ストレステスト等の試験を行うときは,スイッチ回路SW1,SW2は,内部電源配線1804,1802と未使用ビット線DBL1,DBL2との接続を解除して,未使用ビット線DBL1とDBL2をテストケースに応じた電圧で駆動する。

【0088】

図20は,第10の実施の形態におけるスイッチ回路を示す図である。図20のスイッチ回路は,NORゲート1901と,NANDゲート1902〜1904,インバータ1905,1906と,P型トランジスタTR191,TR192と,N型トランジスタTR193,TR194とを有し,図19のスイッチ回路SW1をあらわしている。P型トランジスタTR191,TR192のソースは,オーバードライブ電圧VOD,高電位内部電圧VBLHを生成する内部電源回路に接続されており,N型トランジスタTR193,TR194のソースは,プリチャージ電圧生成回路,低電位内部電圧VBLLを生成するの内部電源回路に接続している。試験信号TESTは,未使用ビット線DBL1と内部電源配線1804との接続を制御し,試験電圧選択信号TS1,TS2は,未使用ビット線DBL1と内部電源配線1804との接続を解除したときにおける未使用ビット線DBL1の駆動電圧を,高電位内部電圧VBLH,プリチャージ電圧VBLP,低電位内部電圧VBLLのいずれかに制御する。

【0089】

例えば,未使用ビット線DBL1を電源安定化容量として使用するときは,試験信号TESTをLレベルにしてP型トランジスタTR191をONにして,未使用ビット線DBL1をオーバードライブ電圧VODに接続する。ストレス試験の時は,未使用ビット線DBL1と内部電源配線1804との接続を解除するため,試験信号TESTをHレベルにしてP型トランジスタTR191をOFFにする。そして,試験電圧信号TS1,TS2をそれぞれHレベル,Lレベルにすると,未使用ビット線DBL1は高電位内部電圧VBLHで駆動される。また,試験電圧信号TS1,TS2がともにLレベルであれば,未使用ビット線DBL1はプリチャージ電圧VBLPで駆動し,試験電圧信号TS1,TS2がLレベル,Hレベルであれば,低電位内部電圧VBLLで駆動する。

【0090】

以上のとおり,スイッチ回路SW1は,未使用ビット線をオーバードライブ電圧VODを生成する内部電源回路の内部電源配線と接続し,ストレステストの時には,未使用ビット線を内部電圧VBLH,VBLP,VBLLのいずれかに駆動することができる。

【0091】

スイッチ回路SW2についても,図19と同様なスイッチ回路を使用することで,未使用ビット線DBL2を電源安定化容量として使用するだけでなく,ストレス試験時に未使用ビット線DBL2をテストケースに応じた電圧で駆動することができる。

【0092】

以上の実施の形態をまとめると,次の付記のとおりである。

【0093】

(付記1)

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【0094】

(付記2)

付記1において,

前記ワード線は,該ワード線を挟む隣接する2つのセンスアンプ群にそれぞれ接続する前記ビット線に交互に交差し,前記メモリセルアレイの前記列方向の両端では前記ビット線及び未使用ビット線とに交互に交差する半導体記憶装置。

【0095】

(付記3)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に第1及び第2の内部電源を生成する第1及び第2の内部電源回路をそれぞれ配置し,前記第1端の前記複数の未使用ビット線は,前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0096】

(付記4)

付記3において,

前記第1の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記プリチャージ電圧より低く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動される半導体記憶装置。

【0097】

(付記5)

付記3において,

前記第1及び第2の内部電源はビット線のプリチャージ電圧より高く,前記第1の内部電源は前記第2の内部電源より高く,

さらに,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路を有し,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第3の内部電源に駆動され,その後,第1の内部電源に駆動された方のビット線は,第2の内部電源に駆動される半導体記憶装置。

【0098】

(付記6)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源を生成する第1の内部電源回路を,第2端に第2及び第3の内部電源を生成する第2及び第3の内部電源回路を配置し,前記第1端の前記複数の未使用ビット線のうち,一部は前記第2の内部電源回路の第2の内部電源配線に接続し,残りは前記第3の内部電源回路の第3の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0099】

(付記7)

付記6において,

前記第1の内部電源は前記プリチャージ電圧より低く,前記第2及び第3の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記第3の内部電源より高く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動され,その後,第2の内部電源に駆動された方のビット線は,第3の内部電源に駆動される半導体記憶装置。

【0100】

(付記8)

付記1又は2において,

さらに前記メモリアレイの前記列方向の前記他方に配置された複数の未使用ビット線に加えて,一端に配置された複数の未使用ビット線が,前記内部電源配線に接続されている半導体記憶装置。

【0101】

(付記9)

付記8において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源回路を,第2端に第2の内部電源回路を配置し,前記第1端には複数の第1及び第2の未使用ビット線を配置し,前記第2端には複数の第3及び第4の未使用ビット線を配置し,前記第1及び第3の未使用ビット線は前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2及び第4の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【0102】

(付記10)

付記9において,

付記4と同じ。

【0103】

(付記11)

付記9において,

付記5と同じ。

【0104】

(付記12)

付記1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に前記内部電源回路を配置し,前記第1端及び第2端の前記複数の未使用ビット線は共に,前記第1端及び第2端の前記内部電源回路の内部電源配線にそれぞれ接続する半導体記憶装置。

【0105】

(付記13)

付記12において,

前記一対のビット線は,プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに,前記プリチャージ電圧より高い第1の内部電源又は前記プリチャージ電圧より低い第3の内部電源に駆動され,その後,前記第1の内部電源に駆動された方のビット線は,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源に駆動され,

前記第1,第2又は第3の内部電源は,前記内部電源回路で生成される半導体記憶装置。

【0106】

(付記14)

付記1又は2において,

通常動作時は,前記未使用ビット線と前記内部電源配線とを接続し,テスト時は前記未使用ビット線をテスト用電圧に接続するスイッチ回路を有する半導体記憶装置。

【0107】

(付記15)

付記14において,

プリチャージ電圧を生成するプリチャージ電圧生成回路と,ビット線の前記プリチャージ電圧より高い第1の内部電源を生成する第1の内部電源回路と,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源を生成する第2の内部電源回路と,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路とを有し,

前記内部電源配線は,前記第1,第2又は第3の内部電源回路の内部電源配線であり,

前記テスト用電圧は,前記第1,第2及び第3の内部電源回路のうち前記内部電源配線と接続する内部電源回路を除いた内部電源回路,又は前記プリチャージ電圧生成回路である半導体記憶装置。

【符号の説明】

【0108】

BL,/BL:ビット線

DBL:未使用ビット線

SWL:サブワード線

SA :センスアンプユニット

SAD:センスアンプドライバ

SWD:サブワードデコーダ

VBLH :高電位内部電圧

VBLL :低電位内部電圧

VBLP :プリチャージ電圧

VOD :オーバードライブ電圧

【特許請求の範囲】

【請求項1】

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【請求項2】

請求項1において,

前記ワード線は,該ワード線を挟む隣接する2つのセンスアンプ群にそれぞれ接続する前記ビット線に交互に交差し,前記メモリセルアレイの前記列方向の両端では前記ビット線及び未使用ビット線とに交互に交差する半導体記憶装置。

【請求項3】

請求項1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に第1及び第2の内部電源を生成する第1及び第2の内部電源回路をそれぞれ配置し,前記第1端の前記複数の未使用ビット線は,前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【請求項4】

請求項3において,

前記第1の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記プリチャージ電圧より低く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動される半導体記憶装置。

【請求項5】

請求項3において,

前記第1及び第2の内部電源はビット線のプリチャージ電圧より高く,前記第1の内部電源は前記第2の内部電源より高く,

さらに,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路を有し,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第3の内部電源に駆動され,その後,第1の内部電源に駆動された方のビット線は,第2の内部電源に駆動される半導体記憶装置。

【請求項6】

請求項1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源を生成する第1の内部電源回路を,第2端に第2及び第3の内部電源を生成する第2及び第3の内部電源回路を配置し,前記第1端の前記複数の未使用ビット線のうち,一部は前記第2の内部電源回路の第2の内部電源配線に接続し,残りは前記第3の内部電源回路の第3の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【請求項7】

請求項6において,

前記第1の内部電源は前記プリチャージ電圧より低く,前記第2及び第3の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記第3の内部電源より高く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動され,その後,第2の内部電源に駆動された方のビット線は,第3の内部電源に駆動される半導体記憶装置。

【請求項8】

請求項1又は2において,

さらに前記メモリアレイの前記列方向の前記他方に配置された複数の未使用ビット線に加えて,一端に配置された複数の未使用ビット線が,前記内部電源配線に接続されている半導体記憶装置。

【請求項9】

請求項1又は2において,

通常動作時は,前記未使用ビット線と前記内部電源配線とを接続し,テスト時は前記未使用ビット線をテスト用電圧に接続するスイッチ回路を有する半導体記憶装置。

【請求項10】

請求項9において,

プリチャージ電圧を生成するプリチャージ電圧生成回路と,ビット線の前記プリチャージ電圧より高い第1の内部電源を生成する第1の内部電源回路と,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源を生成する第2の内部電源回路と,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路とを有し,

前記内部電源配線は,前記第1,第2又は第3の内部電源回路の内部電源配線であり,

前記テスト用電圧は,前記第1,第2及び第3の内部電源回路のうち前記内部電源配線と接続する内部電源回路を除いた内部電源回路,又は前記プリチャージ電圧生成回路である半導体記憶装置。

【請求項1】

列方向に両側に延びる一対のビット線に接続するセンスアンプを複数,前記列方向に直交する行方向に配置したセンスアンプ群と,

複数の前記センスアンプ群が列方向に配置され,前記列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,前記列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち前記列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,前記複数のビット線及び前記複数の未使用ビット線と前記複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,

前記メモリセルアレイの前記列方向の一端に配置され,前記複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,

前記メモリセルアレイの前記列方向の他端に配置された複数の未使用ビット線が前記内部電源配線に接続されている半導体記憶装置。

【請求項2】

請求項1において,

前記ワード線は,該ワード線を挟む隣接する2つのセンスアンプ群にそれぞれ接続する前記ビット線に交互に交差し,前記メモリセルアレイの前記列方向の両端では前記ビット線及び未使用ビット線とに交互に交差する半導体記憶装置。

【請求項3】

請求項1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端及び第2端に第1及び第2の内部電源を生成する第1及び第2の内部電源回路をそれぞれ配置し,前記第1端の前記複数の未使用ビット線は,前記第2の内部電源回路の第2の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【請求項4】

請求項3において,

前記第1の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記プリチャージ電圧より低く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動される半導体記憶装置。

【請求項5】

請求項3において,

前記第1及び第2の内部電源はビット線のプリチャージ電圧より高く,前記第1の内部電源は前記第2の内部電源より高く,

さらに,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路を有し,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第3の内部電源に駆動され,その後,第1の内部電源に駆動された方のビット線は,第2の内部電源に駆動される半導体記憶装置。

【請求項6】

請求項1又は2において,

前記メモリセルアレイの前記列方向の両端の第1端に第1の内部電源を生成する第1の内部電源回路を,第2端に第2及び第3の内部電源を生成する第2及び第3の内部電源回路を配置し,前記第1端の前記複数の未使用ビット線のうち,一部は前記第2の内部電源回路の第2の内部電源配線に接続し,残りは前記第3の内部電源回路の第3の内部電源配線に接続し,前記第2端の前記複数の未使用ビット線は,前記第1の内部電源回路の第1の内部電源配線に接続する半導体記憶装置。

【請求項7】

請求項6において,

前記第1の内部電源は前記プリチャージ電圧より低く,前記第2及び第3の内部電源はビット線のプリチャージ電圧より高く,前記第2の内部電源は前記第3の内部電源より高く,

前記一対のビット線は,前記プリチャージ電圧にプリチャージされ,前記センスアンプが駆動されたときに前記第1又は第2の内部電源に駆動され,その後,第2の内部電源に駆動された方のビット線は,第3の内部電源に駆動される半導体記憶装置。

【請求項8】

請求項1又は2において,

さらに前記メモリアレイの前記列方向の前記他方に配置された複数の未使用ビット線に加えて,一端に配置された複数の未使用ビット線が,前記内部電源配線に接続されている半導体記憶装置。

【請求項9】

請求項1又は2において,

通常動作時は,前記未使用ビット線と前記内部電源配線とを接続し,テスト時は前記未使用ビット線をテスト用電圧に接続するスイッチ回路を有する半導体記憶装置。

【請求項10】

請求項9において,

プリチャージ電圧を生成するプリチャージ電圧生成回路と,ビット線の前記プリチャージ電圧より高い第1の内部電源を生成する第1の内部電源回路と,前記プリチャージ電圧より高く前記第1の内部電源より低い第2の内部電源を生成する第2の内部電源回路と,前記プリチャージ電圧より低い第3の内部電源を生成する第3の内部電源回路とを有し,

前記内部電源配線は,前記第1,第2又は第3の内部電源回路の内部電源配線であり,

前記テスト用電圧は,前記第1,第2及び第3の内部電源回路のうち前記内部電源配線と接続する内部電源回路を除いた内部電源回路,又は前記プリチャージ電圧生成回路である半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−89269(P2013−89269A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−228517(P2011−228517)

【出願日】平成23年10月18日(2011.10.18)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月18日(2011.10.18)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]