半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体

【課題】本発明は、デバッグを高精度に、かつ、効率的に行う半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関する。

【解決手段】MFPコントローラボード1の画像処理ASIC13は、I/F21から入力される画像データに対して、複数のアルゴ処理部22a〜22nが適宜の順序で所定の画像処理を施してI/F23から外部に出力するが、デバッグ時に、スキャナエミュレータ110から入力されて、I/F21及びアルゴ処理部22a〜22nから出力される画像データのハッシュ値をハッシュ計算部24a〜24n+1で生成して、それぞれ結果保存レジスタ25a〜25n+1に保持する。この結果保存レジスタ25a〜25n+1のハッシュ値をデバッガ端末100が取り出すことでデバッグすることができる。

【解決手段】MFPコントローラボード1の画像処理ASIC13は、I/F21から入力される画像データに対して、複数のアルゴ処理部22a〜22nが適宜の順序で所定の画像処理を施してI/F23から外部に出力するが、デバッグ時に、スキャナエミュレータ110から入力されて、I/F21及びアルゴ処理部22a〜22nから出力される画像データのハッシュ値をハッシュ計算部24a〜24n+1で生成して、それぞれ結果保存レジスタ25a〜25n+1に保持する。この結果保存レジスタ25a〜25n+1のハッシュ値をデバッガ端末100が取り出すことでデバッグすることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関し、詳細には、画像処理におけるデバッグ、評価、解析等を効率的に行う情報を取得することのできるマイクロコンピュータ、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)等の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関する。

【背景技術】

【0002】

複合装置、ファクシミリ装置、複写装置、プリンタ装置及びコンピュータ等の画像データの処理を行う画像処理装置においては、高機能化に伴って、搭載するソフトウェア及びハードウェア構成が大規模かつ複雑化し、問題が発生した場合の原因の究明が困難となってきているが、市場の要求にタイムリーに対応するためには、早急な原因究明が求められる。

【0003】

画像処理装置には、近時、高機能な画像処理用の半導体集積回路、例えば、ASICが搭載され、ASICは、内部に複数の画像処理モジュールを搭載して、これらの複数のモジュールで画像処理した画像データを外部に出力する。

【0004】

ところが、従来のASICは、入力画像データと出力画像データの状態のみが分かるだけで、ASIC内部での処理途中の画像データの状態を把握することができない。その結果、意図する画像データが出力されない場合に、ASIC内部のどの画像処理モジュールの処理段階で問題が発生しているのかを把握することができない。

【0005】

そして、従来、複数の画像処理手段間の画像パスを転送される画像データのうち、指定された画像処理手段間の画像パスを流れる画像データを、デバッグ専用のバスを用いて取り出してデバッグする技術が提案されている(特許文献1参照)。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記従来技術にあっては、複数の画像パスのうち指定された画像パスを流れる画像データを、デバッグ専用バスを用いて取り出してデバッグしているため、ASIC等の半導体集積回路に、デバッグ専用のインターフェイスを実装する必要があるとともに、複数個所のデータ値を比較してデバッグすることができず、デバッグ専用のインターフェイスを用いることなく、より高精度で利用性の高いデバッグ行う上で、改良の必要があった。

【0007】

そこで、本発明は、専用のデバッグインターフェイスを用いることなく、一度に複数の処理段階のデータを比較して、デバッグを高精度に、かつ、効率的に行うことのできる半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明は、上記目的を達成するために、入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路において、前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成し、生成した各特徴量をそれぞれ特徴量保持手段に保持することを特徴としている。

【0009】

また、本発明は、前記特徴量が、前記画像データに関するハッシュ値であることを特徴としてもよい。

【0010】

さらに、本発明は、前記特徴量生成手段の生成する前記特徴量の期待値を外部からの設定入力に応じて該特徴量生成手段毎に期待値保持手段に保持し、前記特徴量保持手段の保持する前記特徴量と該期待値を比較して比較結果を出力することを特徴としてもよい。

【0011】

また、本発明は、前記特徴量と前記期待値との比較結果が異なる前記特徴量生成手段を特定する特定情報を特定情報保持手段に保持することを特徴としてもよい。

【0012】

さらに、本発明は、前記画像データの最大画素値を検出し、該最大画素値における前記特徴量を生成することを特徴としてもよい。

【0013】

また、本発明は、前記画像データ以外のデータを処理するデータ処理モジュールの出力するデータの特徴量を生成し、該データ特徴量をデータ特徴量保持手段に保持することを特徴としてもよい。

【発明の効果】

【0014】

本発明によれば、専用のデバッグインターフェイスを用いることなく、一度に複数の処理段階のデータを比較して、デバッグを高精度に、かつ、効率的に行うことができる。

【図面の簡単な説明】

【0015】

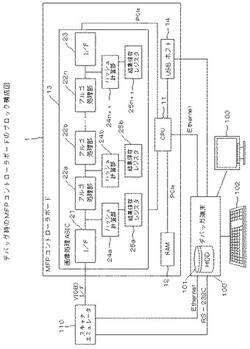

【図1】本発明の第1実施例を適用したデバッグ時のMFPコントローラボードのブロック構成図。

【図2】ハッシュ計算部の詳細なブロック構成部

【図3】CRC部の回路構成図。

【図4】デバッガ端末のモニタ表示の一例を示す図。

【図5】有効領域計算部による有効領域計算処理を示すフローチャート。

【図6】本発明の第2実施例を適用した画像処理ASICのブロック構成図。

【図7】第2実施例のハッシュ計算部の詳細なブロック構成図。

【図8】第3実施例の画像処理ASICのブロック構成図。

【発明を実施するための形態】

【0016】

以下、本発明の好適な実施例を添付図面に基づいて詳細に説明する。なお、以下に述べる実施例は、本発明の好適な実施例であるので、技術的に好ましい種々の限定が付されているが、本発明の範囲は、以下の説明によって不当に限定されるものではなく、また、本実施の形態で説明される構成の全てが本発明の必須の構成要件ではない。

【実施例1】

【0017】

図1〜図5は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第1実施例を示す図であり、図1は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第1実施例を適用したMFPコントローラボード1の要部ブロック構成図である。

【0018】

図1において、MFPコントローラボード1は、スキャナ機能、プリンタ機能、ファクシミリ機能、データ送受信機能等の複数の機能を搭載したMFP(Multi Function Peripheral:複合装置)のコントローラボードに適用され、MFPの搭載する各機能を制御するとともに、画像処理を実行する。

【0019】

MFPコントローラボード1は、CPU(Central Processing Unit )11、RAM(Random Access Memory)12、画像処理ASIC(画像処理用半導体集積回路)13及びUSBホストポート14等を搭載しており、CPU11とRAM12及びコントローラボード13は、応答を待たずに次の要求を発行できる高速のスプリットトランザクションのバス、例えば、PCIe(Peripheral Component Interconnect Express)で接続されている。

【0020】

RAM12には、MFPの基本プログラムや本発明のデバッグプログラム及び必要なシステムデータが格納されるとともに、CPU11のワークメモリとして利用され、また、画像処理ASIC13で処理された画像データを一時格納するメモリとして利用される。

【0021】

CPU11は、RAM12内の基本プログラムに基づいてRAM12をワークメモリとして利用しつつMFPの各部を制御して、MFPとしての基本処理を実行するとともに、デバッグ時には、イーサネット(Ethernet:登録商標)等によって接続されるデバッガ端末100からの命令によってRAM12内のデバッグプログラムを立ち上げて、画像処理ASIC13に後述するデバッグ方法を実行させる。

【0022】

USBホストポート14は、MFPコントローラボード1がMFPに搭載されているときには、MFPと画像データの授受を行うコンピュータ等の外部のUSBホスト装置が接続され、図1に示すように、デバッグ時には、デバッガ端末100が接続される。USBホストポート14は、該USBホスト装置やデバッガ端末100と通信するための物理的・電気的I/Fを制御する機能及びUSBプロトコルを制御する機能を有し、USBホスト装置やデバッガ端末100と通信する。

【0023】

画像処理ASIC13は、画像データの処理、例えば、スキャナで読み取られた画像データ等の入力画像データに対して、プリンタで印刷出力するのに適した画像データへの画像処理、ネットワークを介したデータ転送に適した画像データへの画像処理、データ蓄積部へのデータ蓄積に適した画像処理等の画像処理を実行して、一旦RAM12に蓄積し、その後、図示しないプリンタ、ネットワークインターフェイス、あるいは、ハードディスク等に出力する。

【0024】

画像処理ASIC13は、画像データ入力側に配置されたI/F(インターフェイス)21、縦列に接続されたアルゴ処理部22a〜22n、画像データの出力側に配置されたI/F23、ハッシュ計算部24a〜24n+1及び結果保存レジスタ25a〜25n+1等を搭載している。

【0025】

I/F(入力ポート)21には、MFPコントローラボード1外、例えば、MFPのスキャナや外部のコンピュータ等からの画像データが入力され、I/F21は、該画像データを受け取って先頭のアルゴ処理部22a及びハッシュ計算部24aに出力する。

【0026】

各段のアルゴ処理部(画像処理モジュール)22a〜22nは、順次縦列に接続され、CPU11によって設定されたパラメータやレジスタ値に基づいて前段のI/F21やアルゴ処理部22a〜22n-1から入力される画像データに対して所定の画像処理を施して、次段のアルゴ処理部22b〜22nまたはI/F23に出力するとともに、次段のアルゴ処理部22b〜22nまたはI/F23との間に接続されているハッシュ計算部22b〜22n+1に出力する。アルゴ処理部22a〜22nは、入力される画像データに対して、例えば、γ補正処理、変倍処理、編集処理、補正処理等の画像処理を順次行う。

【0027】

I/F(出力ポート)23は、CPU11にPCIeによって接続され、画像処理の完了した画像データをCPU11に転送する。

【0028】

CPU11は、画像処理ASIC13で画像処理の完了した画像データが送られてくると、該画像データを一旦RAM12に保管する。

【0029】

ハッシュ計算部(特徴量生成手段)24a〜24n+1は、I/F21と先頭のアルゴ処理部22aとの間、各アルゴ処理部22a〜22nの間及び最終段のアルゴ処理部22nとインターフェイス23との間に接続され、それぞれ接続されているモジュール間の前段側のモジュールであるI/F21またはアルゴ処理部22a〜22n+1の出力する画像データのハッシュ値を生成(計算)して、生成結果を結果保存レジスタ25a〜25n+1に保管する。この結果保存レジスタ25a〜25n+1に保管されたハッシュ値は、CPU11が画像処理ASIC13を制御することにより、CPU11によってリードされる。

【0030】

ハッシュ計算部24a〜24n+1は、図2に示すようにブロック構成されており、有効領域計算部31とCRC部32等を備えている。

【0031】

有効領域計算部31には、クロック、ライン同期信号MFlag[1]、画像終端信号MFlag[0]、画像データSData、主走査領域開始点area_xs、主走査領域終了点area_xe、副走査領域開始点area_ys、副走査領域終了点area_ye、リセット信号reset、データリセット選択信号clearmode、領域情報選択信号areamode及びデータ制御信号MCmdが入力され、CRC部32には、クロック、画像データMData、データ制御信号MCmd及び有効領域計算部31からの計算対象領域信号Validとリセット信号resetが入力される。

【0032】

有効領域計算部31は、上記入力信号に基づいて、パラメータとコマンドから、CRC部32の計算対象領域信号ValidとCRC部32に与えるリセット信号resetを生成して、CRC部32に出力する。

【0033】

CRC部32は、4ビットの場合、例えば、図3に示すように、4つのフリップフロップFF32Fa〜32Fdと2つのXOR回路32Xa、32Xbを組み合わせて構成され、先頭のXOR回路32Xaに画像データMDataが入力されるとともに、最終段のフリップフロップ32Fdの出力が入力される。各フリップフロップ32Fa〜32Fdには、クロックClockが入力され、CRC部32は、各フリップフロップ32Fa〜32Fdが、入力データMDataをもとに、ハッシュ値としてCRC32ビット符号を生成する。CRC部32は、有効領域計算部31からの計算対象領域信号Valid、データ制御信号MCmd、画像データMData、クロックClock及び有効領域計算部31からのリセット信号resetを入力信号として、計算対象領域信号Validがアサートされている状態で、画像データMDataが入力されると、入力されたデータ列のCRC32符合(Result)を生成して、生成した結果であるCRC符号を結果保存レジスタ25a〜25n+1に蓄積する。CRC部32は、有効領域計算部31からのリセットreset信号がアサートされると、内部モジュールであるフリップフロップ32Fa〜32Fdに保持しているデータがクリアされる。

【0034】

結果保存レジスタ25a〜25n+1は、各ハッシュ計算部24a〜24n+1のCRC部32に接続され、CRC部32から出力されるCRC符号を保持する。

【0035】

MFPコントローラボード1は、デバッグ時には、図1に示すように、デバッガ端末100及びスキャナエミュレータ110が接続されて、デバッグ処理が行われる。

【0036】

デバッガ端末100は、通常のハードウェア構成のコンピュータ等が用いられ、ハードディスク(HDD)101を搭載しているとともに、キーボード102や図示しないマウス等の入力デバイス及、モニタ103等の出力デバイス及びMFPコントローラボード1及びスキャナエミュレータ110と接続して信号やデータの授受を行うUSBポート、ネットワークポート、RS−232Cポート等の入出力ポート等を備えている。デバッガ端末100は、MFPコントローラボード1とは、イーサネットやUSBによって接続され、スキャナエミュレータ110とは、イーサネットやRS−232Cによって接続される。デバッガ端末100は、スキャナエミュレータ110の動作の制御とMFPコントローラボード1のデバッグプログラム(評価プログラム)の制御を行い、内蔵するハードディスク101に、スキャナエミュレータ110がMFPコントローラボード1側に出力する画像データの元となるデータを保持している。デバッガ端末100は、モニタ103に、例えば、図4に示すように、スキャナエミュレータ、MFPコントローラボード1で動作しているプログラム動作状態等を表示出力し、キーボード102やマウス等の操作により、それらのプログラムの動作指示を行うことができる。

【0037】

スキャナエミュレータ110は、MFPコントローラボード1の適用されるMFPのスキャナユニットでの読み取りデータの入力を行う代わりに、デバッグ目的でMFPコントローラボード1に接続されて、デバッガ端末100からの指示に応じて、デバッガ端末100のハードディスク101に保存されているデータを受け取って、MFPコントローラボード1に入力する。

【0038】

すなわち、MFPコントローラボード1は、ROM、EEPROM(Electrically Erasable and Programmable Read Only Memory )、EPROM、フラッシュメモリ、フレキシブルディスク、CD−ROM(Compact Disc Read Only Memory )、CD−RW(Compact Disc Rewritable )、DVD(Digital Versatile Disk)、SD(Secure Digital)カード、MO(Magneto-Optical Disc)等のコンピュータが読み取り可能な記録媒体に記録されている本発明のデバッグ方法を実行するデバッグプログラムを読み込んでRAM12等に導入することで、後述する画像データに対して複数の画像処理モジュールであるアルゴ処理部22a〜22nで画像処理を施す場合の適否を、専用のデバッグインターフェイスを用いることなく、一度に複数の箇所のデータを比較して高精度・効率的に行うデバッグ方法を実行する画像処理用の半導体集積回路として構築されている。このデバッグプログラムは、アセンブラ、C、C++、C#、Java(登録商標)等のレガシープログラミング言語やオブジェクト指向ブログラミング言語等で記述されたコンピュータ実行可能なプログラムであり、上記記録媒体に格納して頒布することができる。

【0039】

そして、このRAM12上に格納されているデバッグプログラムは、デバッガ端末101からの命令により動作して、画像処理ASIC13の制御、RAM12上に展開されたデータと期待値との比較等の処理を行う。

【0040】

次に、本実施例の作用を説明する。本実施例のMFPコントローラボード1は、専用のデバッグインターフェイスを用いることなく、一度に複数の箇所のデータを比較してデバッグを高精度・効率的に行う。

【0041】

すなわち、MFPコントローラボード1は、デバッグ時には、図1に示したように、デバッガ端末100及びスキャナエミュレータ110に接続され、デバッガ端末100の指示に応じて、スキャナエミュレータ110から入力される画像データに対するI/F21及びアルゴ処理部22a〜22nでのデータ処理結果に対するハッシュ値を、各I/F21及びアルゴ処理部22a〜22nの下流側に接続されているハッシュ計算部24a〜24n+1で生成して、生成結果のハッシュ値を結果保持レジスタ25aに格納する。

【0042】

このとき、デバッガ端末100がMFPコントローラボード1とスキャナエミュレータ110にキーボード102等からの指示操作に応じてデバッグ処理の指示信号を出力し、MFPコントローラボード1は、CPU11が、該デバッガ端末100からのデバッグ処理指示信号に応じて、RAM12に格納されているデバッグプログラムを起動させて、ハッシュ計算部24a〜24n+1の動作を制御する。デバッグプログラムは、各ハッシュ計算部24a〜24n+1の演算結果に対する期待値を保持していて、画像転送後に、結果保存レジスタ25a〜25n+1に保管されているCRC符号と期待値との比較を行う。

【0043】

そして、ハッシュ計算部24a〜24n+1は、上述のように、有効領域計算部31とCRC部32を備えており、有効領域計算部31には、上述のように、クロック、ライン同期信号MFlag[1]、画像終端信号MFlag[0]、画像データSData、主走査領域開始点area_xs、主走査領域終了点area_xe、副走査領域開始点area_ys、副走査領域終了点area_ye、リセット信号reset、データリセット選択信号clearmode、領域情報選択信号areamode及びデータ制御信号MCmdが入力される。有効領域計算部31は、これらの入力信号に基づいて、パラメータとコマンドから、CRC部32の計算対象領域信号ValidとCRC部32に与えるリセット信号resetを生成して、CRC部32に出力する。CRC部32には、クロック、画像データMData、データ制御信号MCmd及び有効領域計算部31からの計算対象領域信号Validとリセット信号resetが入力され、CRC部32は、入力データMDataをもとに、ハッシュ値としてCRC32ビット符号を生成して、結果保存レジスタ25a〜25n+1に保管する。

【0044】

そして、ハッシュ計算部24a〜24n+1の有効領域計算部31は、図5に示すように、計算対象領域信号Validとリセット信号resetを生成して、CRC部32に出力する有効領域計算処理を行う。すなわち、有効領域計算部31は、データ制御信号MCmdをチェックして、データ制御信号MCmdがアイドル状態(MCmd[2:0]=IDLE)であるか、ライト状態(MCmd[2:0]=WR)であるかチェックし(ステップS101)、データ制御信号MCmdがライト状態となったことをトリガとして、動作を開始して、領域情報選択信号areamodeが有効(areamode=1)であるか、無効(areamode=0)であるかチェックする(ステップS102)。

【0045】

ステップS102で、areamode=0(領域情報無効)であると、有効領域計算部31は、計算対象領域信号Validをアサート状態(Valid=true)にし(ステップS103)、areamode=1(領域情報有効)であると、area*信号と送出している画素の位置関係から、計算対象領域信号Validをアサート状態にするかネゲート状態にするかを決定する(ステップS104)。すなわち、有効領域計算部31は、領域情報選択信号areamodeが領域情報有効(areamode=1)であると、画素位置xが、主走査領域開始点area_xsと主走査領域終了点area_xeの間(area_xs≦x≦area_xe)にあり、かつ、副走査領域開始点area_ysと副走査領域終了点area_yeの間(area_ys≦x≦area_ye)にあるかチェックし(ステップS104)、画素位置が主走査領域開始点area_xsと主走査領域終了点area_xeの間と副走査領域開始点area_ysと副走査領域終了点area_yeの間のいずれか、または、双方から外れているときには、計算対象領域信号Validをアサート状態(Valid=true)にする(ステップS103)。有効領域計算部31は、画素位置が主走査領域開始点area_xsと主走査領域終了点area_xeの間にあり、かつ、副走査領域開始点area_ysと副走査領域終了点area_yeの間にあるときには、計算対象領域信号Validをネゲート状態(Valid=false)にする(ステップS105)。

【0046】

有効領域計算部31は、計算対象領域信号Validの状態設定を完了すると(ステップS103、105)、主走査カウンタxのカウント値を「1」だけインクリメント(x=x+1)して(ステップS106)、ライン同期信号MFlag[1]がアサート(ライン同期信号MFlag[1]=EOF)されているかチェックし(ステップS107)、アサートされておらずネゲート状態のときには、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理する(ステップS101〜S107)。

【0047】

ステップS107で、ライン同期信号MFlag[1]がアサートされているときには、有効領域計算部31は、主走査カウンタxをリセット(x=0)し、副走査カウンタyのカウント値を「1」だけインクリメント(y=y+1)して(ステップS108)、画像終端信号MFlag[0]がアサート(画像終端信号MFlag[0]=EOF)されているかチェックする(ステップS109)。

【0048】

ステップS109で、画像終端信号MFlag[0]がアサートされていないときには、有効領域計算部31は、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理し(ステップS101〜S109)、画像終端信号MFlag[0]がアサートされているときには、副走査カウンタyをリセット(y=0)し(ステップS110)、データリセット選択信号clearmodeをチェックする(ステップS111)。

【0049】

ステップS111で、データリセット選択信号clearmodeが「0」のときには、有効領域計算部31は、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理し(ステップS101〜S111)、データリセット選択信号clearmodeが「1」のときには、CRC部32に対してリセット信号resetのパルスを送出した後(ステップS112)、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理する(ステップS101〜S112)。

【0050】

そして、CRC部32は、有効領域計算部31からの計算対象領域信号Validがアサートされている状態で、画像データMDataが入力されると、入力されたデータ列のCRC符合(Result)を生成して、生成した結果であるCRC符号を結果保存レジスタ25a〜25n+1に蓄積する。CRC部32は、有効領域計算部31からのリセットreset信号がアサートされると、内部モジュールであるフリップフロップ32Fa〜32Fdに保持しているデータがクリアされる。

【0051】

なお、上記説明においては、ハッシュ計算部24a〜24n+1は、画像データの示す1つの画像を1つの画像領域として、特徴量であるハッシュ値を生成しているが、1つの画像を複数の画像領域に分割してそれぞれの画像領域におけるハッシュ値を生成してもよい。

【0052】

このようにすると、1回のデバッグ処理で、画像データの画像における複数の画像領域に対してデバッグすることができる。

【0053】

そして、デバッグプログラムは、各ハッシュ計算部24a〜24n+1の演算結果に対する期待値を保持しており、CPU11は、デバッガ端末100からの指示命令に応じて、デバッグプログラムによって、画像データ転送後に、結果保存レジスタ25a〜25n+1の保管している各ハッシュ値であるCRC符号と該期待値との比較を行って、比較結果をデバッガ端末100に出力する。

【0054】

デバッガ端末100は、MFPコントローラボード1から送られてきたCRC符号と期待値との比較結果であるデバッグ結果をモニタ103に表示出力する等の方法で報知出力する。

【0055】

このように、本実施例のMFPコントローラボード1の画像処理ASIC13は、I/F21から入力される画像データに対して、複数のアルゴ処理部22a〜22nが適宜の順序で所定の画像処理を施してI/F23から外部に出力するが、このI/F21及びアルゴ処理部22a〜22nの出力する画像データの特徴量をハッシュ計算部24a〜24n+1で生成し、生成した各特徴量をそれぞれ結果保存レジスタ25a〜25n+1に保持している。

【0056】

したがって、デバッグ時に、デバッガ端末100からスキャナエミュレータ110を介して画像処理ASIC13にデバッグ用の画像データを入力することで、各ハッシュ計算部24a〜24n+1が特徴量を生成して、結果保持レジスタ25a〜25n+1に保存し、デバッガ端末100が適宜の結果保持レジスタ25a〜25n+1から特徴量を取り出すことで、画像処理ASIC13の複数の画像処理段階の特徴量を検査することができる。その結果、デバッグ専用のインターフェイスを用いることなく、デバッグを高精度にかつ効率的に行うことができる。

【0057】

また、本実施例の画像処理ASIC13は、前記ハッシュ計算部24a〜24n+1が、前記特徴量として、画像データに関するハッシュ値を生成している。

【0058】

したがって、少ないデータ量で高精度なデバッグ処理を行うことができる。

【0059】

さらに、本実施例の画像処理ASIC13は、ハッシュ計算部24a〜24n+1が、画像データの終端データに基づいて結果保持レジスタ25a〜25n+1の保持する特徴量をリセットしている。

【0060】

したがって、画像データの終端毎に適切に特徴量(ハッシュ値)を結果保持レジスタ25a〜25n+1に保存することができ、より一層高精度に、かつ、効率的にデバッグすることができる。

【0061】

そして、本実施例の画像処理ASIC13は、I/F21以降全てのアルゴ処理部22a〜22nのハッシュ値(特徴量)をハッシュ計算部24a〜24n+1で生成して、結果保持レジスタ25a〜25n+1に保存しているので、画像パスを画像データが通過したかを確認することができるとともに、どの画像処理段階で問題があるかを正確に確認することができる。

【実施例2】

【0062】

図6及び図7は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第2実施例を示す図であり、図6は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第2実施例を適用したMFPコントローラボード上の画像処理ASIC40のブロック構成図である。

【0063】

なお、本実施例は、上記第1実施例のMFPコントローラボード1と同様のMFPコントローラボード1に搭載された画像処理ASIC40に適用されたものであり、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付して、その説明を省略又は簡略化する。また、画像処理ASIC40の搭載されるMFPコントローラボード1は、画像処理ASIC40のデバッグ時には、第1実施例の場合と同様に、デバッガ端末100及びスキャナエミュレータ110が画像処理ASIC40を搭載するMFPコントローラボード1に接続される。

【0064】

そこで、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付すとともに、図示しない部分についても、必要に応じて、第1実施例で用いた符号をそのまま用いて説明する。

【0065】

図6において、画像処理ASIC40は、第1実施例の画像処理ASIC13と同様のI/F21、アルゴ処理部22a〜22n、I/F23、ハッシュ計算部24a〜24n+1、結果保存レジスタ25a〜25n+1を搭載しているとともに、最大画素値保持部41a〜41n+1、結果保存レジスタ42a〜42n+1、期待値比較部43a〜43n+1、期待値レジスタ44a〜44n+1及び割り込みコントローラ45を搭載している。

【0066】

最大画素値保持部41a〜41n+1は、インターフェイス21と先頭のアルゴ処理部22aとの間、各アルゴ処理部22a〜22nの間及び最終段のアルゴ処理部22nとインターフェイス23との間に、ハッシュ計算部24a〜24n+1に並列に接続され、結果保存レジスタ42a〜42n+1は、各最大画素値保持部41a〜41n+1に接続されている。最大画素値保持部41a〜41n+1は、画像データの画素値の最大値を保持し、保持した最大画素値を結果保存レジスタ42a〜42n+1に保存する。上記最大画素値保持部41a〜41n+1及び結果保存レジスタ42a〜42n+1は、全体として最大画素値検出手段として機能している。

【0067】

ハッシュ計算部24a〜24n+1は、第1実施例の場合と同様に、それぞれ接続されているモジュール間の前段側のモジュールであるI/F21またはアルゴ処理部22a〜22n+1の出力する画像データのハッシュ値を計算して、計算結果を結果保存レジスタ25a〜25n+1に保管するが、図7に示すように、有効領域計算部31が、ハッシュ計算完了信号を出力する。すなわち、有効領域計算部31は、図5のステップS109において、画像終端信号MFlag[0]がアサートされていないこと(MFlag[0]=1(=EOF))を検出したタイミングで、ハッシュ計算完了信号を期待値比較部43a〜43n+1に送出(アサート)する。

【0068】

結果保存レジスタ25a〜25n+1には、それぞれ期待値比較部43a〜43n+1が接続されており、期待値比較部43a〜43n+1には、それぞれ期待値レジスタ44a〜44n+1が接続されている。

【0069】

期待値レジスタ(期待値保持手段)44a〜44n+1は、画像処理ASIC40の起動前に、デバッガ端末100から期待値が設定される。

【0070】

この期待値は、画像処理ASIC40のアルゴリズムと同様の画像処理ASICのアルゴリズムで生成される特徴値であるハッシュ値であり、画像処理ASIC40の処理に問題がないときには、画像処理ASIC40のI/F21、アルゴ処理部22a〜22n+1で処理された画像データのハッシュ計算部24a〜24n+1で生成された特徴値であるハッシュ値と一致するハッシュ値である。

【0071】

期待値比較部(比較手段)43a〜43n+1は、画像処理ASIC40の起動後、ハッシュ計算完了信号がアサートされると、結果保存レジスタ25a〜25n+1のハッシュ計算部24a〜24n+1の計算結果であるハッシュ値と期待値比較レジスタ44a〜44n+1の期待値を比較し、ハッシュ値と期待値が異なっていると、割り込み信号Ha〜Hn+1を割り込みコントローラ45に出力する。

【0072】

割り込みコントローラ45は、各期待値比較部43a〜43n+1から割り込み信号Ha〜Hn+1が入力され、該割り込み信号Ha〜Hn+1が入力されると、画像処理ASIC1の外部、すなわち、デバッガ端末100に割り込み信号を出力する。また、割り込みコントローラ45は、期待値比較部43a〜43n+1のうちどの期待値比較部43a〜43n+1から割り込み信号が入力されたかの特定情報を保持するレジスタ(特定情報保持手段)を有しており、デバッガ端末100からこのレジスタの保持する期待値比較部43a〜43n+1を特定する特定情報を取得することで、画像データに対するいずれの段階で割り込みが発生したかを知ることができる。

【0073】

次に、本実施例の作用を説明する。本実施例の画像処理ASIC40は、各アルゴ処理部22a〜22n及びI/F21の出力する最大画素値に対するハッシュ値と予め設定されている期待値を比較して、相異があると割り込みを発生する。

【0074】

すなわち、画像処理ASIC40を搭載するMFPコントローラボード1は、デバッグ時に、デバッガ端末100及びスキャナエミュレータ110が接続され、画像処理ASIC40の起動前に、デバッガ端末100は、画像データの最大画素値の場合にI/F21及び各アルゴ処理部22a〜22n+1の出力する画像データに対するハッシュ値の期待値を、設定操作に応じて、画像処理ASIC40の各期待値レジスタ44a〜44n+1に格納する。

【0075】

画像処理ASIC40は、I/F21及び各アルゴ処理部22a〜22n+1の出力側に最大画素値保持部41a〜41n+1とハッシュ計算部24a〜24n+1が接続されており、各ハッシュ計算部24a〜24n+1が、各最大画素値保持部41a〜41n+1が検出して結果保持レジスタ42a〜42n+1に保存している画像データ中の最大画素値に対するハッシュ値を生成して結果保持レジスタ25a〜25n+1に保管するとともに、ハッシュ値生成が完了したことを通知するために、ハッシュ計算完了信号を期待値比較部43a〜43n+1に出力する。

【0076】

期待値比較部43a〜43n+1は、この結果保存レジスタ25a〜25n+1のハッシュ値と期待値レジスタ44a〜44n+1の期待値と比較し、ハッシュ値と期待値に相異があると、割り込みコントローラ45に割り込みを発生する。

【0077】

割り込みコントローラ45は、割り込み信号保持レジスタを備えており、期待値比較部43a〜43n+1から割り込み信号Ha〜Hn+1が入力されると、割り込み信号保持レジスタにどの期待値比較部43a〜43n+1から割り込み信号が入ったかの特定情報を保持するとともに、デバッガ端末100に割り込み信号を出力する。

【0078】

デバッガ端末100は、画像処理ASIC40の割り込みコントローラ45から割り込み信号が送られてくると、該割り込み信号の発生源である期待値比較部43a〜43n+1によるCRC符号と期待値との比較結果であるデバッグ結果をモニタ103に表示出力する等の方法で報知出力する。

【0079】

したがって、デバッガ端末100は、割り込みコントローラ45の割り込み信号保持レジスタの保持する特定情報を取得することで、画像データに対するいずれの段階で割り込みが発生したかを知ることができる。

【0080】

このように、本実施例の画像処理ASIC40は、ハッシュ計算部24a〜24n+1の生成する特徴量であるハッシュ値の期待値を、外部(デバッガ端末100)からの設定入力に応じてハッシュ計算部24a〜24n+1毎に期待値レジスタ44a〜44n+1に保持し、期待値比較部43a〜43n+1が、結果保持レジスタ25a〜25n+1の保持するハッシュ値と期待値レジスタ44a〜44n+1の保持する期待値を比較して比較結果を割り込みコントローラ45に出力している。

【0081】

したがって、画像処理ASIC40内において、期待した画像処理が適切に行われているか否かを容易に確認することができ、問題のある画像処理部分を適切かつ確実に特定することができる。

【0082】

また、本実施例の画像処理ASIC40は、割り込みコントローラ45が、期待値比較部43a〜43n+1による特徴量であるハッシュ値と期待値との比較結果が異なるハッシュ計算部24a〜24n+1を特定する特定情報である割り込み信号Ha〜Hn+1を保持するレジスタを備えている。

【0083】

したがって、外部からどのハッシュ計算部24a〜24n+1の生成したハッシュ値に以上があるかを簡単かつ容易に確認することができ、デバッグ処理をより一層簡単かつ高精度に行うことができる。

【0084】

さらに、本実施例の画像処理ASIC40は、画像データの最大画素値を最大画素値保持部41a〜41n+1で検出して、結果保持レジスタ42a〜42n+1に保持し、ハッシュ計算部24a〜24n+1で該最大画素値におけるハッシュ値を生成している。

【0085】

したがって、画像データの最大画素値に対する画像処理の適否を容易かつ高精度に判定することができる。

【実施例3】

【0086】

図8は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第3実施例を適用したMFPコントローラボード上の画像処理ASIC50のブロック構成図である。

【0087】

なお、本実施例は、上記第1実施例のMFPコントローラボード1と同様のMFPコントローラボード1に搭載された画像処理ASIC50に適用されたものであり、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付して、その説明を省略又は簡略化する。また、画像処理ASIC50の搭載されるMFPコントローラボード1は、画像処理ASIC50のデバッグ時には、第1実施例の場合と同様に、デバッガ端末100及びスキャナエミュレータ110が画像処理ASIC40を搭載するMFPコントローラボード1に接続される。

【0088】

図8において、画像処理ASIC50は、第1実施例の画像処理ASIC13と同様のI/F21、I/F23を備えているとともに、縦列に複数接続されたアルゴ処理部22a〜22nの一部(図8では、最終段)として、補正アルゴ処理部22mを備えており、また、I/F21及び各アルゴ処理部22a・・・及び補正アルゴ処理部22mには、ハッシュ計算部24a・・・及びハッシュ計算部24mが接続されている。また、各ハッシュ計算部24a・・・及びハッシュ計算部24mには、結果保持レジスタ25a・・・及び結果保持レジスタ25mが接続されている。

【0089】

また、アルゴ処理部22a〜22mの接続パスの途中に、補正信号生成部(データ処理モジュール)51が接続されており、補正信号生成部51の出力は、補正アルゴ処理部22mに入力される。補正処理生成部51の出力には、ハッシュ計算部(データ特徴量生成手段)24xが接続されており、ハッシュ計算部24xには、結果保持レジスタ(データ特徴量保持手段)25xが接続されている。

【0090】

補正信号生成部51は、画像の強調情報を生成して、画像データではない画像強調情報信号(画像データ以外のデータ)を補正アルゴ処理部22m及びハッシュ計算部24xに出力する。

【0091】

ハッシュ計算部24xは、補正信号生成部51の出力する画像強調情報信号のハッシュ値を生成(計算)して、生成結果を結果保存レジスタ25xに保管する。

【0092】

補正アルゴ処理部22mは、補正信号生成部51から入力される画像強調情報信号に基づいて、前段のアルゴ処理部22m-1から入力される所定のアルゴ処理済みの画像データに対して画像処理を施して、I/F23及びハッシュ計算部24mに出力する。ハッシュ計算部24mは、補正アルゴ処理部22mの画像処理した画像データのハッシュ値を計算して、計算結果を結果保存レジスタ25mに保管する。

【0093】

画像処理ASIC50を搭載するMFPコントローラボード1のCPU11は、結果保存レジスタ25a・・・及び結果保存レジスタ25x、結果保存レジスタ25mに保管されたハッシュ値を、リードする。

【0094】

次に、本実施例の作用を説明する。本実施例の画像処理ASIC50は、画像データ以外のデータのハッシュ値をも生成して、画像処理ASIC50内でのデータ処理の評価を行う。

【0095】

すなわち、画像処理ASIC50は、画像処理を行う複数のアルゴ処理部22a・・・及び補正アルゴ処理部22mが縦列に接続されており、このアルゴ処理部22a・・・及び補正アルゴ処理部22mの接続パスに、補正信号生成部51が接続されている。この補正信号生成部51は、画像データではなく、画像強調情報信号を生成して補正アルゴ処理部22mに出力し、補正アルゴ処理部22mがこの画像強調情報信号に基づいて、前段のアルゴ処理部22m-1から入力される画像データに対して画像強調処理を施してI/F23に出力する。

【0096】

そして、I/F21及びアルゴ処理部22a・・・及び補正アルゴ処理部22mに接続されているハッシュ計算部24a・・・及び24mは、第1実施例と同様に、画像データに対するハッシュ値を生成して結果保存レジスタ25a・・・及び結果保存レジスタ25mに保存する。

【0097】

ところが、ハッシュ計算部24xは、補正信号生成部51が出力するのが画像データ以外の画像強調情報信号であるが、この画像強調情報信号のハッシュ値を生成して、結果保存レジスタ25xに保存する。

【0098】

そして、画像処理ASIC50を搭載するMFPコントローラボード1のCPU11が、結果保存レジスタ25a・・・及び結果保存レジスタ25x、結果保存レジスタ25mに保管されたハッシュ値をリードし、外部のデバッガ端末100に出力する。

【0099】

このように、本実施例の画像処理ASIC50は、画像データ以外のデータを処理するデータ処理モジュールである補正信号生成部51、補正信号生成部51の出力するデータの特徴量であるハッシュ値を生成するデータ特徴量生成手段であるハッシュ計算部24x及びハッシュ計算部24xの生成するハッシュ値25xを保持するデータ特徴量保持手段である結果保存レジスタ25xを備えている。

【0100】

したがって、画像処理ASIC50の画像データ以外のデータを処理するモジュールのデータ処理についても特徴量を生成して、デバッグ専用のインターフェイスを用いることなく、デバッグを高精度にかつ効率的に行うことができる。

【0101】

なお、上記各説明においては、画像処理ASIC13、40、50のI/F21、アルゴ処理部22a〜22n+1、22m、I/F23が、縦列(直列)に接続されている場合について説明したが、縦列に接続されているものに限るものではなく、並列に接続されていたり、直列と並列が混在していても、同様に適用することができる。

【0102】

以上、本発明者によってなされた発明を好適な実施例に基づき具体的に説明したが、本発明は上記実施例で説明したものに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0103】

本発明は、画像処理におけるデバッグ、評価、解析等を効率的に行う情報を取得することのできるマイクロコンピュータ、DSP、ASIC等の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に利用することができる。

【符号の説明】

【0104】

1 MFPコントローラボード

11 CPU

12 RAM

13 画像処理ASIC

14 USBホストポート

21 I/F

22a〜22n アルゴ処理部

23 I/F

24a〜24n+1 ハッシュ計算部

25a〜25n+1 結果保存レジスタ

31 有効領域計算部

32 CRC部

FF32Fa〜32Fd フリップフロップ

32Xa、32Xb XOR回路

40 画像処理ASIC

41a〜41n+1 最大画素値保持部

42a〜42n+1 結果保存レジスタ

43a〜43n+1 期待値比較部

44a〜44n+1 期待値レジスタ

45 割り込みコントローラ

50 画像処理ASIC

22m 補正アルゴ処理部

24m ハッシュ計算部

24x ハッシュ計算部

25m 結果保持レジスタ

25x 結果保存レジスタ

100 デバッガ端末

101 ハードディスク

102 キーボード

103 モニタ

110 スキャナエミュレータ

【先行技術文献】

【特許文献】

【0105】

【特許文献1】特開2007−43571号公報

【技術分野】

【0001】

本発明は、半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関し、詳細には、画像処理におけるデバッグ、評価、解析等を効率的に行う情報を取得することのできるマイクロコンピュータ、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)等の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に関する。

【背景技術】

【0002】

複合装置、ファクシミリ装置、複写装置、プリンタ装置及びコンピュータ等の画像データの処理を行う画像処理装置においては、高機能化に伴って、搭載するソフトウェア及びハードウェア構成が大規模かつ複雑化し、問題が発生した場合の原因の究明が困難となってきているが、市場の要求にタイムリーに対応するためには、早急な原因究明が求められる。

【0003】

画像処理装置には、近時、高機能な画像処理用の半導体集積回路、例えば、ASICが搭載され、ASICは、内部に複数の画像処理モジュールを搭載して、これらの複数のモジュールで画像処理した画像データを外部に出力する。

【0004】

ところが、従来のASICは、入力画像データと出力画像データの状態のみが分かるだけで、ASIC内部での処理途中の画像データの状態を把握することができない。その結果、意図する画像データが出力されない場合に、ASIC内部のどの画像処理モジュールの処理段階で問題が発生しているのかを把握することができない。

【0005】

そして、従来、複数の画像処理手段間の画像パスを転送される画像データのうち、指定された画像処理手段間の画像パスを流れる画像データを、デバッグ専用のバスを用いて取り出してデバッグする技術が提案されている(特許文献1参照)。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記従来技術にあっては、複数の画像パスのうち指定された画像パスを流れる画像データを、デバッグ専用バスを用いて取り出してデバッグしているため、ASIC等の半導体集積回路に、デバッグ専用のインターフェイスを実装する必要があるとともに、複数個所のデータ値を比較してデバッグすることができず、デバッグ専用のインターフェイスを用いることなく、より高精度で利用性の高いデバッグ行う上で、改良の必要があった。

【0007】

そこで、本発明は、専用のデバッグインターフェイスを用いることなく、一度に複数の処理段階のデータを比較して、デバッグを高精度に、かつ、効率的に行うことのできる半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明は、上記目的を達成するために、入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路において、前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成し、生成した各特徴量をそれぞれ特徴量保持手段に保持することを特徴としている。

【0009】

また、本発明は、前記特徴量が、前記画像データに関するハッシュ値であることを特徴としてもよい。

【0010】

さらに、本発明は、前記特徴量生成手段の生成する前記特徴量の期待値を外部からの設定入力に応じて該特徴量生成手段毎に期待値保持手段に保持し、前記特徴量保持手段の保持する前記特徴量と該期待値を比較して比較結果を出力することを特徴としてもよい。

【0011】

また、本発明は、前記特徴量と前記期待値との比較結果が異なる前記特徴量生成手段を特定する特定情報を特定情報保持手段に保持することを特徴としてもよい。

【0012】

さらに、本発明は、前記画像データの最大画素値を検出し、該最大画素値における前記特徴量を生成することを特徴としてもよい。

【0013】

また、本発明は、前記画像データ以外のデータを処理するデータ処理モジュールの出力するデータの特徴量を生成し、該データ特徴量をデータ特徴量保持手段に保持することを特徴としてもよい。

【発明の効果】

【0014】

本発明によれば、専用のデバッグインターフェイスを用いることなく、一度に複数の処理段階のデータを比較して、デバッグを高精度に、かつ、効率的に行うことができる。

【図面の簡単な説明】

【0015】

【図1】本発明の第1実施例を適用したデバッグ時のMFPコントローラボードのブロック構成図。

【図2】ハッシュ計算部の詳細なブロック構成部

【図3】CRC部の回路構成図。

【図4】デバッガ端末のモニタ表示の一例を示す図。

【図5】有効領域計算部による有効領域計算処理を示すフローチャート。

【図6】本発明の第2実施例を適用した画像処理ASICのブロック構成図。

【図7】第2実施例のハッシュ計算部の詳細なブロック構成図。

【図8】第3実施例の画像処理ASICのブロック構成図。

【発明を実施するための形態】

【0016】

以下、本発明の好適な実施例を添付図面に基づいて詳細に説明する。なお、以下に述べる実施例は、本発明の好適な実施例であるので、技術的に好ましい種々の限定が付されているが、本発明の範囲は、以下の説明によって不当に限定されるものではなく、また、本実施の形態で説明される構成の全てが本発明の必須の構成要件ではない。

【実施例1】

【0017】

図1〜図5は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第1実施例を示す図であり、図1は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第1実施例を適用したMFPコントローラボード1の要部ブロック構成図である。

【0018】

図1において、MFPコントローラボード1は、スキャナ機能、プリンタ機能、ファクシミリ機能、データ送受信機能等の複数の機能を搭載したMFP(Multi Function Peripheral:複合装置)のコントローラボードに適用され、MFPの搭載する各機能を制御するとともに、画像処理を実行する。

【0019】

MFPコントローラボード1は、CPU(Central Processing Unit )11、RAM(Random Access Memory)12、画像処理ASIC(画像処理用半導体集積回路)13及びUSBホストポート14等を搭載しており、CPU11とRAM12及びコントローラボード13は、応答を待たずに次の要求を発行できる高速のスプリットトランザクションのバス、例えば、PCIe(Peripheral Component Interconnect Express)で接続されている。

【0020】

RAM12には、MFPの基本プログラムや本発明のデバッグプログラム及び必要なシステムデータが格納されるとともに、CPU11のワークメモリとして利用され、また、画像処理ASIC13で処理された画像データを一時格納するメモリとして利用される。

【0021】

CPU11は、RAM12内の基本プログラムに基づいてRAM12をワークメモリとして利用しつつMFPの各部を制御して、MFPとしての基本処理を実行するとともに、デバッグ時には、イーサネット(Ethernet:登録商標)等によって接続されるデバッガ端末100からの命令によってRAM12内のデバッグプログラムを立ち上げて、画像処理ASIC13に後述するデバッグ方法を実行させる。

【0022】

USBホストポート14は、MFPコントローラボード1がMFPに搭載されているときには、MFPと画像データの授受を行うコンピュータ等の外部のUSBホスト装置が接続され、図1に示すように、デバッグ時には、デバッガ端末100が接続される。USBホストポート14は、該USBホスト装置やデバッガ端末100と通信するための物理的・電気的I/Fを制御する機能及びUSBプロトコルを制御する機能を有し、USBホスト装置やデバッガ端末100と通信する。

【0023】

画像処理ASIC13は、画像データの処理、例えば、スキャナで読み取られた画像データ等の入力画像データに対して、プリンタで印刷出力するのに適した画像データへの画像処理、ネットワークを介したデータ転送に適した画像データへの画像処理、データ蓄積部へのデータ蓄積に適した画像処理等の画像処理を実行して、一旦RAM12に蓄積し、その後、図示しないプリンタ、ネットワークインターフェイス、あるいは、ハードディスク等に出力する。

【0024】

画像処理ASIC13は、画像データ入力側に配置されたI/F(インターフェイス)21、縦列に接続されたアルゴ処理部22a〜22n、画像データの出力側に配置されたI/F23、ハッシュ計算部24a〜24n+1及び結果保存レジスタ25a〜25n+1等を搭載している。

【0025】

I/F(入力ポート)21には、MFPコントローラボード1外、例えば、MFPのスキャナや外部のコンピュータ等からの画像データが入力され、I/F21は、該画像データを受け取って先頭のアルゴ処理部22a及びハッシュ計算部24aに出力する。

【0026】

各段のアルゴ処理部(画像処理モジュール)22a〜22nは、順次縦列に接続され、CPU11によって設定されたパラメータやレジスタ値に基づいて前段のI/F21やアルゴ処理部22a〜22n-1から入力される画像データに対して所定の画像処理を施して、次段のアルゴ処理部22b〜22nまたはI/F23に出力するとともに、次段のアルゴ処理部22b〜22nまたはI/F23との間に接続されているハッシュ計算部22b〜22n+1に出力する。アルゴ処理部22a〜22nは、入力される画像データに対して、例えば、γ補正処理、変倍処理、編集処理、補正処理等の画像処理を順次行う。

【0027】

I/F(出力ポート)23は、CPU11にPCIeによって接続され、画像処理の完了した画像データをCPU11に転送する。

【0028】

CPU11は、画像処理ASIC13で画像処理の完了した画像データが送られてくると、該画像データを一旦RAM12に保管する。

【0029】

ハッシュ計算部(特徴量生成手段)24a〜24n+1は、I/F21と先頭のアルゴ処理部22aとの間、各アルゴ処理部22a〜22nの間及び最終段のアルゴ処理部22nとインターフェイス23との間に接続され、それぞれ接続されているモジュール間の前段側のモジュールであるI/F21またはアルゴ処理部22a〜22n+1の出力する画像データのハッシュ値を生成(計算)して、生成結果を結果保存レジスタ25a〜25n+1に保管する。この結果保存レジスタ25a〜25n+1に保管されたハッシュ値は、CPU11が画像処理ASIC13を制御することにより、CPU11によってリードされる。

【0030】

ハッシュ計算部24a〜24n+1は、図2に示すようにブロック構成されており、有効領域計算部31とCRC部32等を備えている。

【0031】

有効領域計算部31には、クロック、ライン同期信号MFlag[1]、画像終端信号MFlag[0]、画像データSData、主走査領域開始点area_xs、主走査領域終了点area_xe、副走査領域開始点area_ys、副走査領域終了点area_ye、リセット信号reset、データリセット選択信号clearmode、領域情報選択信号areamode及びデータ制御信号MCmdが入力され、CRC部32には、クロック、画像データMData、データ制御信号MCmd及び有効領域計算部31からの計算対象領域信号Validとリセット信号resetが入力される。

【0032】

有効領域計算部31は、上記入力信号に基づいて、パラメータとコマンドから、CRC部32の計算対象領域信号ValidとCRC部32に与えるリセット信号resetを生成して、CRC部32に出力する。

【0033】

CRC部32は、4ビットの場合、例えば、図3に示すように、4つのフリップフロップFF32Fa〜32Fdと2つのXOR回路32Xa、32Xbを組み合わせて構成され、先頭のXOR回路32Xaに画像データMDataが入力されるとともに、最終段のフリップフロップ32Fdの出力が入力される。各フリップフロップ32Fa〜32Fdには、クロックClockが入力され、CRC部32は、各フリップフロップ32Fa〜32Fdが、入力データMDataをもとに、ハッシュ値としてCRC32ビット符号を生成する。CRC部32は、有効領域計算部31からの計算対象領域信号Valid、データ制御信号MCmd、画像データMData、クロックClock及び有効領域計算部31からのリセット信号resetを入力信号として、計算対象領域信号Validがアサートされている状態で、画像データMDataが入力されると、入力されたデータ列のCRC32符合(Result)を生成して、生成した結果であるCRC符号を結果保存レジスタ25a〜25n+1に蓄積する。CRC部32は、有効領域計算部31からのリセットreset信号がアサートされると、内部モジュールであるフリップフロップ32Fa〜32Fdに保持しているデータがクリアされる。

【0034】

結果保存レジスタ25a〜25n+1は、各ハッシュ計算部24a〜24n+1のCRC部32に接続され、CRC部32から出力されるCRC符号を保持する。

【0035】

MFPコントローラボード1は、デバッグ時には、図1に示すように、デバッガ端末100及びスキャナエミュレータ110が接続されて、デバッグ処理が行われる。

【0036】

デバッガ端末100は、通常のハードウェア構成のコンピュータ等が用いられ、ハードディスク(HDD)101を搭載しているとともに、キーボード102や図示しないマウス等の入力デバイス及、モニタ103等の出力デバイス及びMFPコントローラボード1及びスキャナエミュレータ110と接続して信号やデータの授受を行うUSBポート、ネットワークポート、RS−232Cポート等の入出力ポート等を備えている。デバッガ端末100は、MFPコントローラボード1とは、イーサネットやUSBによって接続され、スキャナエミュレータ110とは、イーサネットやRS−232Cによって接続される。デバッガ端末100は、スキャナエミュレータ110の動作の制御とMFPコントローラボード1のデバッグプログラム(評価プログラム)の制御を行い、内蔵するハードディスク101に、スキャナエミュレータ110がMFPコントローラボード1側に出力する画像データの元となるデータを保持している。デバッガ端末100は、モニタ103に、例えば、図4に示すように、スキャナエミュレータ、MFPコントローラボード1で動作しているプログラム動作状態等を表示出力し、キーボード102やマウス等の操作により、それらのプログラムの動作指示を行うことができる。

【0037】

スキャナエミュレータ110は、MFPコントローラボード1の適用されるMFPのスキャナユニットでの読み取りデータの入力を行う代わりに、デバッグ目的でMFPコントローラボード1に接続されて、デバッガ端末100からの指示に応じて、デバッガ端末100のハードディスク101に保存されているデータを受け取って、MFPコントローラボード1に入力する。

【0038】

すなわち、MFPコントローラボード1は、ROM、EEPROM(Electrically Erasable and Programmable Read Only Memory )、EPROM、フラッシュメモリ、フレキシブルディスク、CD−ROM(Compact Disc Read Only Memory )、CD−RW(Compact Disc Rewritable )、DVD(Digital Versatile Disk)、SD(Secure Digital)カード、MO(Magneto-Optical Disc)等のコンピュータが読み取り可能な記録媒体に記録されている本発明のデバッグ方法を実行するデバッグプログラムを読み込んでRAM12等に導入することで、後述する画像データに対して複数の画像処理モジュールであるアルゴ処理部22a〜22nで画像処理を施す場合の適否を、専用のデバッグインターフェイスを用いることなく、一度に複数の箇所のデータを比較して高精度・効率的に行うデバッグ方法を実行する画像処理用の半導体集積回路として構築されている。このデバッグプログラムは、アセンブラ、C、C++、C#、Java(登録商標)等のレガシープログラミング言語やオブジェクト指向ブログラミング言語等で記述されたコンピュータ実行可能なプログラムであり、上記記録媒体に格納して頒布することができる。

【0039】

そして、このRAM12上に格納されているデバッグプログラムは、デバッガ端末101からの命令により動作して、画像処理ASIC13の制御、RAM12上に展開されたデータと期待値との比較等の処理を行う。

【0040】

次に、本実施例の作用を説明する。本実施例のMFPコントローラボード1は、専用のデバッグインターフェイスを用いることなく、一度に複数の箇所のデータを比較してデバッグを高精度・効率的に行う。

【0041】

すなわち、MFPコントローラボード1は、デバッグ時には、図1に示したように、デバッガ端末100及びスキャナエミュレータ110に接続され、デバッガ端末100の指示に応じて、スキャナエミュレータ110から入力される画像データに対するI/F21及びアルゴ処理部22a〜22nでのデータ処理結果に対するハッシュ値を、各I/F21及びアルゴ処理部22a〜22nの下流側に接続されているハッシュ計算部24a〜24n+1で生成して、生成結果のハッシュ値を結果保持レジスタ25aに格納する。

【0042】

このとき、デバッガ端末100がMFPコントローラボード1とスキャナエミュレータ110にキーボード102等からの指示操作に応じてデバッグ処理の指示信号を出力し、MFPコントローラボード1は、CPU11が、該デバッガ端末100からのデバッグ処理指示信号に応じて、RAM12に格納されているデバッグプログラムを起動させて、ハッシュ計算部24a〜24n+1の動作を制御する。デバッグプログラムは、各ハッシュ計算部24a〜24n+1の演算結果に対する期待値を保持していて、画像転送後に、結果保存レジスタ25a〜25n+1に保管されているCRC符号と期待値との比較を行う。

【0043】

そして、ハッシュ計算部24a〜24n+1は、上述のように、有効領域計算部31とCRC部32を備えており、有効領域計算部31には、上述のように、クロック、ライン同期信号MFlag[1]、画像終端信号MFlag[0]、画像データSData、主走査領域開始点area_xs、主走査領域終了点area_xe、副走査領域開始点area_ys、副走査領域終了点area_ye、リセット信号reset、データリセット選択信号clearmode、領域情報選択信号areamode及びデータ制御信号MCmdが入力される。有効領域計算部31は、これらの入力信号に基づいて、パラメータとコマンドから、CRC部32の計算対象領域信号ValidとCRC部32に与えるリセット信号resetを生成して、CRC部32に出力する。CRC部32には、クロック、画像データMData、データ制御信号MCmd及び有効領域計算部31からの計算対象領域信号Validとリセット信号resetが入力され、CRC部32は、入力データMDataをもとに、ハッシュ値としてCRC32ビット符号を生成して、結果保存レジスタ25a〜25n+1に保管する。

【0044】

そして、ハッシュ計算部24a〜24n+1の有効領域計算部31は、図5に示すように、計算対象領域信号Validとリセット信号resetを生成して、CRC部32に出力する有効領域計算処理を行う。すなわち、有効領域計算部31は、データ制御信号MCmdをチェックして、データ制御信号MCmdがアイドル状態(MCmd[2:0]=IDLE)であるか、ライト状態(MCmd[2:0]=WR)であるかチェックし(ステップS101)、データ制御信号MCmdがライト状態となったことをトリガとして、動作を開始して、領域情報選択信号areamodeが有効(areamode=1)であるか、無効(areamode=0)であるかチェックする(ステップS102)。

【0045】

ステップS102で、areamode=0(領域情報無効)であると、有効領域計算部31は、計算対象領域信号Validをアサート状態(Valid=true)にし(ステップS103)、areamode=1(領域情報有効)であると、area*信号と送出している画素の位置関係から、計算対象領域信号Validをアサート状態にするかネゲート状態にするかを決定する(ステップS104)。すなわち、有効領域計算部31は、領域情報選択信号areamodeが領域情報有効(areamode=1)であると、画素位置xが、主走査領域開始点area_xsと主走査領域終了点area_xeの間(area_xs≦x≦area_xe)にあり、かつ、副走査領域開始点area_ysと副走査領域終了点area_yeの間(area_ys≦x≦area_ye)にあるかチェックし(ステップS104)、画素位置が主走査領域開始点area_xsと主走査領域終了点area_xeの間と副走査領域開始点area_ysと副走査領域終了点area_yeの間のいずれか、または、双方から外れているときには、計算対象領域信号Validをアサート状態(Valid=true)にする(ステップS103)。有効領域計算部31は、画素位置が主走査領域開始点area_xsと主走査領域終了点area_xeの間にあり、かつ、副走査領域開始点area_ysと副走査領域終了点area_yeの間にあるときには、計算対象領域信号Validをネゲート状態(Valid=false)にする(ステップS105)。

【0046】

有効領域計算部31は、計算対象領域信号Validの状態設定を完了すると(ステップS103、105)、主走査カウンタxのカウント値を「1」だけインクリメント(x=x+1)して(ステップS106)、ライン同期信号MFlag[1]がアサート(ライン同期信号MFlag[1]=EOF)されているかチェックし(ステップS107)、アサートされておらずネゲート状態のときには、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理する(ステップS101〜S107)。

【0047】

ステップS107で、ライン同期信号MFlag[1]がアサートされているときには、有効領域計算部31は、主走査カウンタxをリセット(x=0)し、副走査カウンタyのカウント値を「1」だけインクリメント(y=y+1)して(ステップS108)、画像終端信号MFlag[0]がアサート(画像終端信号MFlag[0]=EOF)されているかチェックする(ステップS109)。

【0048】

ステップS109で、画像終端信号MFlag[0]がアサートされていないときには、有効領域計算部31は、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理し(ステップS101〜S109)、画像終端信号MFlag[0]がアサートされているときには、副走査カウンタyをリセット(y=0)し(ステップS110)、データリセット選択信号clearmodeをチェックする(ステップS111)。

【0049】

ステップS111で、データリセット選択信号clearmodeが「0」のときには、有効領域計算部31は、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理し(ステップS101〜S111)、データリセット選択信号clearmodeが「1」のときには、CRC部32に対してリセット信号resetのパルスを送出した後(ステップS112)、ステップS101に戻って、データ制御信号MCmdのチェックから上記同様に処理する(ステップS101〜S112)。

【0050】

そして、CRC部32は、有効領域計算部31からの計算対象領域信号Validがアサートされている状態で、画像データMDataが入力されると、入力されたデータ列のCRC符合(Result)を生成して、生成した結果であるCRC符号を結果保存レジスタ25a〜25n+1に蓄積する。CRC部32は、有効領域計算部31からのリセットreset信号がアサートされると、内部モジュールであるフリップフロップ32Fa〜32Fdに保持しているデータがクリアされる。

【0051】

なお、上記説明においては、ハッシュ計算部24a〜24n+1は、画像データの示す1つの画像を1つの画像領域として、特徴量であるハッシュ値を生成しているが、1つの画像を複数の画像領域に分割してそれぞれの画像領域におけるハッシュ値を生成してもよい。

【0052】

このようにすると、1回のデバッグ処理で、画像データの画像における複数の画像領域に対してデバッグすることができる。

【0053】

そして、デバッグプログラムは、各ハッシュ計算部24a〜24n+1の演算結果に対する期待値を保持しており、CPU11は、デバッガ端末100からの指示命令に応じて、デバッグプログラムによって、画像データ転送後に、結果保存レジスタ25a〜25n+1の保管している各ハッシュ値であるCRC符号と該期待値との比較を行って、比較結果をデバッガ端末100に出力する。

【0054】

デバッガ端末100は、MFPコントローラボード1から送られてきたCRC符号と期待値との比較結果であるデバッグ結果をモニタ103に表示出力する等の方法で報知出力する。

【0055】

このように、本実施例のMFPコントローラボード1の画像処理ASIC13は、I/F21から入力される画像データに対して、複数のアルゴ処理部22a〜22nが適宜の順序で所定の画像処理を施してI/F23から外部に出力するが、このI/F21及びアルゴ処理部22a〜22nの出力する画像データの特徴量をハッシュ計算部24a〜24n+1で生成し、生成した各特徴量をそれぞれ結果保存レジスタ25a〜25n+1に保持している。

【0056】

したがって、デバッグ時に、デバッガ端末100からスキャナエミュレータ110を介して画像処理ASIC13にデバッグ用の画像データを入力することで、各ハッシュ計算部24a〜24n+1が特徴量を生成して、結果保持レジスタ25a〜25n+1に保存し、デバッガ端末100が適宜の結果保持レジスタ25a〜25n+1から特徴量を取り出すことで、画像処理ASIC13の複数の画像処理段階の特徴量を検査することができる。その結果、デバッグ専用のインターフェイスを用いることなく、デバッグを高精度にかつ効率的に行うことができる。

【0057】

また、本実施例の画像処理ASIC13は、前記ハッシュ計算部24a〜24n+1が、前記特徴量として、画像データに関するハッシュ値を生成している。

【0058】

したがって、少ないデータ量で高精度なデバッグ処理を行うことができる。

【0059】

さらに、本実施例の画像処理ASIC13は、ハッシュ計算部24a〜24n+1が、画像データの終端データに基づいて結果保持レジスタ25a〜25n+1の保持する特徴量をリセットしている。

【0060】

したがって、画像データの終端毎に適切に特徴量(ハッシュ値)を結果保持レジスタ25a〜25n+1に保存することができ、より一層高精度に、かつ、効率的にデバッグすることができる。

【0061】

そして、本実施例の画像処理ASIC13は、I/F21以降全てのアルゴ処理部22a〜22nのハッシュ値(特徴量)をハッシュ計算部24a〜24n+1で生成して、結果保持レジスタ25a〜25n+1に保存しているので、画像パスを画像データが通過したかを確認することができるとともに、どの画像処理段階で問題があるかを正確に確認することができる。

【実施例2】

【0062】

図6及び図7は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第2実施例を示す図であり、図6は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第2実施例を適用したMFPコントローラボード上の画像処理ASIC40のブロック構成図である。

【0063】

なお、本実施例は、上記第1実施例のMFPコントローラボード1と同様のMFPコントローラボード1に搭載された画像処理ASIC40に適用されたものであり、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付して、その説明を省略又は簡略化する。また、画像処理ASIC40の搭載されるMFPコントローラボード1は、画像処理ASIC40のデバッグ時には、第1実施例の場合と同様に、デバッガ端末100及びスキャナエミュレータ110が画像処理ASIC40を搭載するMFPコントローラボード1に接続される。

【0064】

そこで、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付すとともに、図示しない部分についても、必要に応じて、第1実施例で用いた符号をそのまま用いて説明する。

【0065】

図6において、画像処理ASIC40は、第1実施例の画像処理ASIC13と同様のI/F21、アルゴ処理部22a〜22n、I/F23、ハッシュ計算部24a〜24n+1、結果保存レジスタ25a〜25n+1を搭載しているとともに、最大画素値保持部41a〜41n+1、結果保存レジスタ42a〜42n+1、期待値比較部43a〜43n+1、期待値レジスタ44a〜44n+1及び割り込みコントローラ45を搭載している。

【0066】

最大画素値保持部41a〜41n+1は、インターフェイス21と先頭のアルゴ処理部22aとの間、各アルゴ処理部22a〜22nの間及び最終段のアルゴ処理部22nとインターフェイス23との間に、ハッシュ計算部24a〜24n+1に並列に接続され、結果保存レジスタ42a〜42n+1は、各最大画素値保持部41a〜41n+1に接続されている。最大画素値保持部41a〜41n+1は、画像データの画素値の最大値を保持し、保持した最大画素値を結果保存レジスタ42a〜42n+1に保存する。上記最大画素値保持部41a〜41n+1及び結果保存レジスタ42a〜42n+1は、全体として最大画素値検出手段として機能している。

【0067】

ハッシュ計算部24a〜24n+1は、第1実施例の場合と同様に、それぞれ接続されているモジュール間の前段側のモジュールであるI/F21またはアルゴ処理部22a〜22n+1の出力する画像データのハッシュ値を計算して、計算結果を結果保存レジスタ25a〜25n+1に保管するが、図7に示すように、有効領域計算部31が、ハッシュ計算完了信号を出力する。すなわち、有効領域計算部31は、図5のステップS109において、画像終端信号MFlag[0]がアサートされていないこと(MFlag[0]=1(=EOF))を検出したタイミングで、ハッシュ計算完了信号を期待値比較部43a〜43n+1に送出(アサート)する。

【0068】

結果保存レジスタ25a〜25n+1には、それぞれ期待値比較部43a〜43n+1が接続されており、期待値比較部43a〜43n+1には、それぞれ期待値レジスタ44a〜44n+1が接続されている。

【0069】

期待値レジスタ(期待値保持手段)44a〜44n+1は、画像処理ASIC40の起動前に、デバッガ端末100から期待値が設定される。

【0070】

この期待値は、画像処理ASIC40のアルゴリズムと同様の画像処理ASICのアルゴリズムで生成される特徴値であるハッシュ値であり、画像処理ASIC40の処理に問題がないときには、画像処理ASIC40のI/F21、アルゴ処理部22a〜22n+1で処理された画像データのハッシュ計算部24a〜24n+1で生成された特徴値であるハッシュ値と一致するハッシュ値である。

【0071】

期待値比較部(比較手段)43a〜43n+1は、画像処理ASIC40の起動後、ハッシュ計算完了信号がアサートされると、結果保存レジスタ25a〜25n+1のハッシュ計算部24a〜24n+1の計算結果であるハッシュ値と期待値比較レジスタ44a〜44n+1の期待値を比較し、ハッシュ値と期待値が異なっていると、割り込み信号Ha〜Hn+1を割り込みコントローラ45に出力する。

【0072】

割り込みコントローラ45は、各期待値比較部43a〜43n+1から割り込み信号Ha〜Hn+1が入力され、該割り込み信号Ha〜Hn+1が入力されると、画像処理ASIC1の外部、すなわち、デバッガ端末100に割り込み信号を出力する。また、割り込みコントローラ45は、期待値比較部43a〜43n+1のうちどの期待値比較部43a〜43n+1から割り込み信号が入力されたかの特定情報を保持するレジスタ(特定情報保持手段)を有しており、デバッガ端末100からこのレジスタの保持する期待値比較部43a〜43n+1を特定する特定情報を取得することで、画像データに対するいずれの段階で割り込みが発生したかを知ることができる。

【0073】

次に、本実施例の作用を説明する。本実施例の画像処理ASIC40は、各アルゴ処理部22a〜22n及びI/F21の出力する最大画素値に対するハッシュ値と予め設定されている期待値を比較して、相異があると割り込みを発生する。

【0074】

すなわち、画像処理ASIC40を搭載するMFPコントローラボード1は、デバッグ時に、デバッガ端末100及びスキャナエミュレータ110が接続され、画像処理ASIC40の起動前に、デバッガ端末100は、画像データの最大画素値の場合にI/F21及び各アルゴ処理部22a〜22n+1の出力する画像データに対するハッシュ値の期待値を、設定操作に応じて、画像処理ASIC40の各期待値レジスタ44a〜44n+1に格納する。

【0075】

画像処理ASIC40は、I/F21及び各アルゴ処理部22a〜22n+1の出力側に最大画素値保持部41a〜41n+1とハッシュ計算部24a〜24n+1が接続されており、各ハッシュ計算部24a〜24n+1が、各最大画素値保持部41a〜41n+1が検出して結果保持レジスタ42a〜42n+1に保存している画像データ中の最大画素値に対するハッシュ値を生成して結果保持レジスタ25a〜25n+1に保管するとともに、ハッシュ値生成が完了したことを通知するために、ハッシュ計算完了信号を期待値比較部43a〜43n+1に出力する。

【0076】

期待値比較部43a〜43n+1は、この結果保存レジスタ25a〜25n+1のハッシュ値と期待値レジスタ44a〜44n+1の期待値と比較し、ハッシュ値と期待値に相異があると、割り込みコントローラ45に割り込みを発生する。

【0077】

割り込みコントローラ45は、割り込み信号保持レジスタを備えており、期待値比較部43a〜43n+1から割り込み信号Ha〜Hn+1が入力されると、割り込み信号保持レジスタにどの期待値比較部43a〜43n+1から割り込み信号が入ったかの特定情報を保持するとともに、デバッガ端末100に割り込み信号を出力する。

【0078】

デバッガ端末100は、画像処理ASIC40の割り込みコントローラ45から割り込み信号が送られてくると、該割り込み信号の発生源である期待値比較部43a〜43n+1によるCRC符号と期待値との比較結果であるデバッグ結果をモニタ103に表示出力する等の方法で報知出力する。

【0079】

したがって、デバッガ端末100は、割り込みコントローラ45の割り込み信号保持レジスタの保持する特定情報を取得することで、画像データに対するいずれの段階で割り込みが発生したかを知ることができる。

【0080】

このように、本実施例の画像処理ASIC40は、ハッシュ計算部24a〜24n+1の生成する特徴量であるハッシュ値の期待値を、外部(デバッガ端末100)からの設定入力に応じてハッシュ計算部24a〜24n+1毎に期待値レジスタ44a〜44n+1に保持し、期待値比較部43a〜43n+1が、結果保持レジスタ25a〜25n+1の保持するハッシュ値と期待値レジスタ44a〜44n+1の保持する期待値を比較して比較結果を割り込みコントローラ45に出力している。

【0081】

したがって、画像処理ASIC40内において、期待した画像処理が適切に行われているか否かを容易に確認することができ、問題のある画像処理部分を適切かつ確実に特定することができる。

【0082】

また、本実施例の画像処理ASIC40は、割り込みコントローラ45が、期待値比較部43a〜43n+1による特徴量であるハッシュ値と期待値との比較結果が異なるハッシュ計算部24a〜24n+1を特定する特定情報である割り込み信号Ha〜Hn+1を保持するレジスタを備えている。

【0083】

したがって、外部からどのハッシュ計算部24a〜24n+1の生成したハッシュ値に以上があるかを簡単かつ容易に確認することができ、デバッグ処理をより一層簡単かつ高精度に行うことができる。

【0084】

さらに、本実施例の画像処理ASIC40は、画像データの最大画素値を最大画素値保持部41a〜41n+1で検出して、結果保持レジスタ42a〜42n+1に保持し、ハッシュ計算部24a〜24n+1で該最大画素値におけるハッシュ値を生成している。

【0085】

したがって、画像データの最大画素値に対する画像処理の適否を容易かつ高精度に判定することができる。

【実施例3】

【0086】

図8は、本発明の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体の第3実施例を適用したMFPコントローラボード上の画像処理ASIC50のブロック構成図である。

【0087】

なお、本実施例は、上記第1実施例のMFPコントローラボード1と同様のMFPコントローラボード1に搭載された画像処理ASIC50に適用されたものであり、本実施例の説明においては、上記第1実施例と同様の構成部分には、同一の符号を付して、その説明を省略又は簡略化する。また、画像処理ASIC50の搭載されるMFPコントローラボード1は、画像処理ASIC50のデバッグ時には、第1実施例の場合と同様に、デバッガ端末100及びスキャナエミュレータ110が画像処理ASIC40を搭載するMFPコントローラボード1に接続される。

【0088】

図8において、画像処理ASIC50は、第1実施例の画像処理ASIC13と同様のI/F21、I/F23を備えているとともに、縦列に複数接続されたアルゴ処理部22a〜22nの一部(図8では、最終段)として、補正アルゴ処理部22mを備えており、また、I/F21及び各アルゴ処理部22a・・・及び補正アルゴ処理部22mには、ハッシュ計算部24a・・・及びハッシュ計算部24mが接続されている。また、各ハッシュ計算部24a・・・及びハッシュ計算部24mには、結果保持レジスタ25a・・・及び結果保持レジスタ25mが接続されている。

【0089】

また、アルゴ処理部22a〜22mの接続パスの途中に、補正信号生成部(データ処理モジュール)51が接続されており、補正信号生成部51の出力は、補正アルゴ処理部22mに入力される。補正処理生成部51の出力には、ハッシュ計算部(データ特徴量生成手段)24xが接続されており、ハッシュ計算部24xには、結果保持レジスタ(データ特徴量保持手段)25xが接続されている。

【0090】

補正信号生成部51は、画像の強調情報を生成して、画像データではない画像強調情報信号(画像データ以外のデータ)を補正アルゴ処理部22m及びハッシュ計算部24xに出力する。

【0091】

ハッシュ計算部24xは、補正信号生成部51の出力する画像強調情報信号のハッシュ値を生成(計算)して、生成結果を結果保存レジスタ25xに保管する。

【0092】

補正アルゴ処理部22mは、補正信号生成部51から入力される画像強調情報信号に基づいて、前段のアルゴ処理部22m-1から入力される所定のアルゴ処理済みの画像データに対して画像処理を施して、I/F23及びハッシュ計算部24mに出力する。ハッシュ計算部24mは、補正アルゴ処理部22mの画像処理した画像データのハッシュ値を計算して、計算結果を結果保存レジスタ25mに保管する。

【0093】

画像処理ASIC50を搭載するMFPコントローラボード1のCPU11は、結果保存レジスタ25a・・・及び結果保存レジスタ25x、結果保存レジスタ25mに保管されたハッシュ値を、リードする。

【0094】

次に、本実施例の作用を説明する。本実施例の画像処理ASIC50は、画像データ以外のデータのハッシュ値をも生成して、画像処理ASIC50内でのデータ処理の評価を行う。

【0095】

すなわち、画像処理ASIC50は、画像処理を行う複数のアルゴ処理部22a・・・及び補正アルゴ処理部22mが縦列に接続されており、このアルゴ処理部22a・・・及び補正アルゴ処理部22mの接続パスに、補正信号生成部51が接続されている。この補正信号生成部51は、画像データではなく、画像強調情報信号を生成して補正アルゴ処理部22mに出力し、補正アルゴ処理部22mがこの画像強調情報信号に基づいて、前段のアルゴ処理部22m-1から入力される画像データに対して画像強調処理を施してI/F23に出力する。

【0096】

そして、I/F21及びアルゴ処理部22a・・・及び補正アルゴ処理部22mに接続されているハッシュ計算部24a・・・及び24mは、第1実施例と同様に、画像データに対するハッシュ値を生成して結果保存レジスタ25a・・・及び結果保存レジスタ25mに保存する。

【0097】

ところが、ハッシュ計算部24xは、補正信号生成部51が出力するのが画像データ以外の画像強調情報信号であるが、この画像強調情報信号のハッシュ値を生成して、結果保存レジスタ25xに保存する。

【0098】

そして、画像処理ASIC50を搭載するMFPコントローラボード1のCPU11が、結果保存レジスタ25a・・・及び結果保存レジスタ25x、結果保存レジスタ25mに保管されたハッシュ値をリードし、外部のデバッガ端末100に出力する。

【0099】

このように、本実施例の画像処理ASIC50は、画像データ以外のデータを処理するデータ処理モジュールである補正信号生成部51、補正信号生成部51の出力するデータの特徴量であるハッシュ値を生成するデータ特徴量生成手段であるハッシュ計算部24x及びハッシュ計算部24xの生成するハッシュ値25xを保持するデータ特徴量保持手段である結果保存レジスタ25xを備えている。

【0100】

したがって、画像処理ASIC50の画像データ以外のデータを処理するモジュールのデータ処理についても特徴量を生成して、デバッグ専用のインターフェイスを用いることなく、デバッグを高精度にかつ効率的に行うことができる。

【0101】

なお、上記各説明においては、画像処理ASIC13、40、50のI/F21、アルゴ処理部22a〜22n+1、22m、I/F23が、縦列(直列)に接続されている場合について説明したが、縦列に接続されているものに限るものではなく、並列に接続されていたり、直列と並列が混在していても、同様に適用することができる。

【0102】

以上、本発明者によってなされた発明を好適な実施例に基づき具体的に説明したが、本発明は上記実施例で説明したものに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0103】

本発明は、画像処理におけるデバッグ、評価、解析等を効率的に行う情報を取得することのできるマイクロコンピュータ、DSP、ASIC等の半導体集積回路、デバッグシステム、デバッグ方法、デバッグプログラム及び記録媒体に利用することができる。

【符号の説明】

【0104】

1 MFPコントローラボード

11 CPU

12 RAM

13 画像処理ASIC

14 USBホストポート

21 I/F

22a〜22n アルゴ処理部

23 I/F

24a〜24n+1 ハッシュ計算部

25a〜25n+1 結果保存レジスタ

31 有効領域計算部

32 CRC部

FF32Fa〜32Fd フリップフロップ

32Xa、32Xb XOR回路

40 画像処理ASIC

41a〜41n+1 最大画素値保持部

42a〜42n+1 結果保存レジスタ

43a〜43n+1 期待値比較部

44a〜44n+1 期待値レジスタ

45 割り込みコントローラ

50 画像処理ASIC

22m 補正アルゴ処理部

24m ハッシュ計算部

24x ハッシュ計算部

25m 結果保持レジスタ

25x 結果保存レジスタ

100 デバッガ端末

101 ハードディスク

102 キーボード

103 モニタ

110 スキャナエミュレータ

【先行技術文献】

【特許文献】

【0105】

【特許文献1】特開2007−43571号公報

【特許請求の範囲】

【請求項1】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路において、

前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成手段と、

前記各特徴量生成手段の生成する前記特徴量をそれぞれ保持する特徴量保持手段と、

を備えたことを特徴とする半導体集積回路。

【請求項2】

前記特徴量は、前記画像データに関するハッシュ値であることを特徴とする請求項1記載の半導体集積回路。

【請求項3】

前記特徴量生成手段は、前記画像データの終端データに基づいて前記特徴量保持手段の保持する特徴量をリセットすることを特徴とする請求項1または請求項2記載の半導体集積回路。

【請求項4】

前記半導体集積回路は、

前記特徴量生成手段の生成する前記特徴量の期待値を外部からの設定入力に応じて該特徴量生成手段毎に保持する期待値保持手段と、

前記特徴量保持手段の保持する前記特徴量と前記期待値保持手段の保持する前記期待値を比較して比較結果を出力する比較手段と、

をさらに備えていることを特徴とする請求項1から請求項3のいずれかに記載の半導体集積回路。

【請求項5】

前記半導体集積回路は、前記比較手段による前記特徴量と前記期待値との比較結果が異なる前記特徴量生成手段を特定する特定情報を保持する特定情報保持手段をさらに備えていることを特徴とする請求項4記載の半導体集積回路。

【請求項6】

前記半導体集積回路は、

前記画像データの最大画素値を検出する最大画素値検出手段を備え、

前記特徴量生成手段は、前記最大画素値における前記特徴量を生成することを特徴とする請求項1から請求項5のいずれかに記載の半導体集積回路。

【請求項7】

前記半導体集積回路は、

前記画像データ以外のデータを処理するデータ処理モジュールと、

前記データ処理モジュールの出力するデータの特徴量を生成するデータ特徴量生成手段と、

前記データ特徴量生成手段の生成する前記データ特徴量を保持するデータ特徴量保持手段と、

を備えていることを特徴とする請求項1から請求項6のいずれかに記載の半導体集積回路。

【請求項8】

前記特徴量生成手段は、前記画像データの示す1つの画像に対して複数の画像領域における特徴量を生成することを特徴とする請求項1から請求項5のいずれかに記載の半導体集積回路。

【請求項9】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路にデバッガ装置からデバッグ用の画像データを入力して該半導体集積回路のデバッグを行うデバッグシステムにおいて、

前記半導体集積回路は、請求項1から請求項8のいずれかに記載の半導体集積回路であって、

前記デバッガ装置は、

前記半導体集積回路に前記デバッグ用の画像データを入力し、前記半導体集積回路の適宜の前記特徴量保持手段から前記特徴量を取得して該半導体集積回路のデバッグを行うことを特徴とするデバッグシステム。

【請求項10】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路におけるデバッグ方法であって、

前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成処理ステップと、

前記各特徴量生成処理ステップで生成される前記特徴量をそれぞれ特徴量保持手段に保持させる特徴量保持処理ステップと、

を有することを特徴とするデバッグ方法。

【請求項11】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路におけるデバッグプログラムであって、

コンピュータに、

前記入力ポート及び/または前記画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成処理と、

前記各特徴量生成処理で生成される前記特徴量をそれぞれ特徴量保持手段に保持させる特徴量保持処理と、

を実行させることを特徴とするデバッグプログラム。

【請求項12】

請求項11記載のデバッグプログラムを記録したことを特徴とするコンピュータが読み取り可能な記録媒体。

【請求項1】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路において、

前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成手段と、

前記各特徴量生成手段の生成する前記特徴量をそれぞれ保持する特徴量保持手段と、

を備えたことを特徴とする半導体集積回路。

【請求項2】

前記特徴量は、前記画像データに関するハッシュ値であることを特徴とする請求項1記載の半導体集積回路。

【請求項3】

前記特徴量生成手段は、前記画像データの終端データに基づいて前記特徴量保持手段の保持する特徴量をリセットすることを特徴とする請求項1または請求項2記載の半導体集積回路。

【請求項4】

前記半導体集積回路は、

前記特徴量生成手段の生成する前記特徴量の期待値を外部からの設定入力に応じて該特徴量生成手段毎に保持する期待値保持手段と、

前記特徴量保持手段の保持する前記特徴量と前記期待値保持手段の保持する前記期待値を比較して比較結果を出力する比較手段と、

をさらに備えていることを特徴とする請求項1から請求項3のいずれかに記載の半導体集積回路。

【請求項5】

前記半導体集積回路は、前記比較手段による前記特徴量と前記期待値との比較結果が異なる前記特徴量生成手段を特定する特定情報を保持する特定情報保持手段をさらに備えていることを特徴とする請求項4記載の半導体集積回路。

【請求項6】

前記半導体集積回路は、

前記画像データの最大画素値を検出する最大画素値検出手段を備え、

前記特徴量生成手段は、前記最大画素値における前記特徴量を生成することを特徴とする請求項1から請求項5のいずれかに記載の半導体集積回路。

【請求項7】

前記半導体集積回路は、

前記画像データ以外のデータを処理するデータ処理モジュールと、

前記データ処理モジュールの出力するデータの特徴量を生成するデータ特徴量生成手段と、

前記データ特徴量生成手段の生成する前記データ特徴量を保持するデータ特徴量保持手段と、

を備えていることを特徴とする請求項1から請求項6のいずれかに記載の半導体集積回路。

【請求項8】

前記特徴量生成手段は、前記画像データの示す1つの画像に対して複数の画像領域における特徴量を生成することを特徴とする請求項1から請求項5のいずれかに記載の半導体集積回路。

【請求項9】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路にデバッガ装置からデバッグ用の画像データを入力して該半導体集積回路のデバッグを行うデバッグシステムにおいて、

前記半導体集積回路は、請求項1から請求項8のいずれかに記載の半導体集積回路であって、

前記デバッガ装置は、

前記半導体集積回路に前記デバッグ用の画像データを入力し、前記半導体集積回路の適宜の前記特徴量保持手段から前記特徴量を取得して該半導体集積回路のデバッグを行うことを特徴とするデバッグシステム。

【請求項10】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路におけるデバッグ方法であって、

前記入力ポート及び/または前記各画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成処理ステップと、

前記各特徴量生成処理ステップで生成される前記特徴量をそれぞれ特徴量保持手段に保持させる特徴量保持処理ステップと、

を有することを特徴とするデバッグ方法。

【請求項11】

入力ポートから入力される画像データに対して、複数の画像処理モジュールが適宜の順序で所定の画像処理を施して出力ポートから外部に出力する半導体集積回路におけるデバッグプログラムであって、

コンピュータに、

前記入力ポート及び/または前記画像処理モジュールの出力する画像データの特徴量を生成する特徴量生成処理と、

前記各特徴量生成処理で生成される前記特徴量をそれぞれ特徴量保持手段に保持させる特徴量保持処理と、

を実行させることを特徴とするデバッグプログラム。

【請求項12】

請求項11記載のデバッグプログラムを記録したことを特徴とするコンピュータが読み取り可能な記録媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−128883(P2011−128883A)

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願番号】特願2009−286665(P2009−286665)

【出願日】平成21年12月17日(2009.12.17)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願日】平成21年12月17日(2009.12.17)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]