半導体集積回路、当該半導体集積回路を搭載した非接触型情報媒体、及び半導体集積回路の駆動方法

【課題】 データが重畳された搬送波より駆動電源を得る半導体集積回路において、得られた電源電圧が過電圧状態となった場合でも誤判別なくデータを復調することができ、また、搬送波から供給される電源を効率的に利用することができる半導体集積回路等を提供する。

【解決手段】 電源回路111として二電圧整流回路を用いるとともに、データの復調に用いる電圧値の高い側の電源(VDDH)が所定の電圧値以上にならないように制御する電圧調整回路112に、抵抗141及び容量素子142を設け、搬送波の振幅が変化することによりVDDHの電圧値が変化した場合に、基準電圧としてレギュレータ回路1121に入力される電圧値を変化させるようにする。

【解決手段】 電源回路111として二電圧整流回路を用いるとともに、データの復調に用いる電圧値の高い側の電源(VDDH)が所定の電圧値以上にならないように制御する電圧調整回路112に、抵抗141及び容量素子142を設け、搬送波の振幅が変化することによりVDDHの電圧値が変化した場合に、基準電圧としてレギュレータ回路1121に入力される電圧値を変化させるようにする。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、半導体集積回路、当該半導体集積回路を搭載した非接触型情報媒体、及び半導体集積回路の駆動方法に関する。

【0002】

【従来の技術】近年、コイルの相互誘導現象を利用して、所定波長の電波を用いて電力の供給を行うとともにデータの送受信を行うようにした、ICカードなどの非接触型情報媒体が実用化の段階に入っている。係る非接触型情報媒体の一例としてのICカードは、ICカードとの間で電波の送受信を行うリーダーライターと当該ICカードとの間で通信が可能な距離によって、大きく近接型、近傍型などに分類されており、それぞれについての標準規格も整いつつあるところである。

【0003】特にリーダーライターから、1cmから約20cm程度までの距離で用いることが可能な近接型のICカードは、例えば定期券等の用途に用いるとすれば、駅の改札口などで定期入れからICカードを取り出すことなく、リーダーライターとの非接触状態での情報のやり取りに基づいて改札口のゲートの開閉制御を行うことも可能となるなど、極めて広い範囲で適用される可能性を有するものである。

【0004】しかしながら、広い範囲に適用されるにはICカードの小型軽量化が重要となる他、適用範囲が広がるほどICカードの取扱いが乱雑となる場合も増加すると予想されるため、係る乱雑な取扱いに対する故障のしにくさなども考慮して、ICカードなどの非接触型情報媒体には、複雑な回路を小さい面積に収めた半導体集積回路が搭載されるのが通常となっている。

【0005】以下、半導体集積回路を搭載した一般的な非接触型ICカードの構成について説明する。図13は、一般的な非接触型ICカードの構成の一例を模式的に示す機能ブロック図である。なお同図には、ICカード900の他に、ICカード900と電波の送受信を行うリーダーライター990も示されている。以下、同図に示されるICカード900の構成及び動作について簡単に説明する。

【0006】ICカード900には、リーダーライター990に接続されたアンテナコイル991との間で電波の送受信を行うためのアンテナコイル981が設けられており、アンテナコイル991から送信される電波を受けて、アンテナコイル981の両端に発生した交流電圧がICカード900に搭載された半導体集積回路910へと入力される。なお、982は同調用の容量素子である。

【0007】尚、受信用のアンテナコイル981は一般的には非接触型ICカード900の半導体集積回路910の外部に接続される。同調用の容量素子982は非接触型ICカード900の半導体集積回路910の外部に接続されることが多いが、半導体集積回路910の内部に構成される場合もある。ICカード900は、リーダーライター990から送信される、ASK変調(振幅変調)された信号を受信して、当該信号から半導体集積回路910の駆動用電力を得るとともに、リーダーライター990から伝送されるデータを取得する。リーダーライター990から送信される搬送波の具体的な構造の一例を図14に示す。同図に示されるように、ASK変調された搬送波は、振幅の小さい部分が0のデータを、振幅の大きい部分が1のデータを表している。

【0008】半導体集積回路910は、電源回路911、第1レギュレータ回路912、変復調回路913、ロジック回路914、不揮発性メモリ915、降圧回路916、第2レギュレータ回路917を含んでいる。なお、ここでは、降圧回路916を設ける場合について説明するが、後述の理由により降圧回路916の代わりに昇圧回路を用いることも可能である。

【0009】図15は、電源回路911の内部構成を示す図である。同図に示されるように、従来のICカード900では、電源回路911として一般的な全波整流回路9111及び平滑用の容量素子9112を用いており、ここで、アンテナコイル981の両端に発生した交流電圧が整流されて直流電圧VCCとなる。整流された電流は、第1レギュレータ回路912により所定の電圧値より高くならないように制御されて変復調回路913やメモリ915を動作させるための電圧となる他、降圧回路916により降圧され、第2レギュレータ回路917により所定の電圧値より高くならないように制御されてロジック回路914の駆動電力を供給する。

【0010】なお、図13には特に図示していないが、第1レギュレータ回路912を通過した電流はクロック生成回路などのアナログ回路に対して駆動電力を供給する。クロック生成回路とは、アンテナコイル981の両端に発生した交流電圧から、ロジック回路914及び不揮発性メモリ915を動作させるためのクロック信号を生成する回路である。

【0011】通常、ロジック回路914などのディジタル回路は比較的低い電圧(約2〜3V)で動作するのに対し、不揮発性メモリ915にはこれよりも高い電圧を供給する必要がある。例えばFeRAMでは約3〜7V、EEPROMでは約10V以上(書き込み、消去時)の電圧が必要である。これに対応するため、上記のように、従来の非接触型ICカード900では、電源回路911において発生した電圧を降圧回路916で降圧してロジック回路914に供給するようにしている。もっとも、電源回路911でロジック回路914を動作させるための低い電圧を発生させるようにして、昇圧回路で昇圧し、変復調回路913やクロック生成回路などのアナログ回路や不揮発性メモリ915を動作させるようにすることもできる。

【0012】また、図14に示したように、ICカード900とリーダーライター990との間で送受信されるデータは交流電圧に重畳されており、非接触型ICカード900がリーダーライター990からのデータを受信する場合には、変復調回路913で復調され、非接触型ICカード900がリーダーライター990にデータを送信する場合には、変復調回路913で変調される。非接触型ICカード900とリーダーライター990との間で送受信されるデータはロジック回路914で制御され、不揮発性メモリ915に蓄えられる。

【0013】さて、コイルの相互誘導現象を利用して電力の供給及びデータの送受信を行うようにした非接触型ICカード900では、電源供給源であるリーダーライター990と非接触型ICカード900との間の距離により、電源回路911において発生する電源電圧が変化する。特に上記両者の間の距離が非常に近くなると過電圧が発生し、非接触型ICカード900の内部回路を破壊する恐れがあることから、かかる不具合を防止するため、電源発生回路911の他に第1及び第2のレギュレータ回路912及び917を設けておき、一定電圧以上の電源電圧にならないような回路構成を行っている。

【0014】図16は、従来第1レギュレータ回路912として用いられていた回路の構成の一例を示す図である。電源回路911からの出力(図中、「VCC」で表す。)とグランドとの間には、2つのPチャネルMOSトランジスタ(以下、「PchMOSトランジスタ」と表記する。)931及び932が直列に接続され、第1のPchMOSトランジスタ931のゲートとドレインはショートされ、ソースはVCCに接続されている。

【0015】また、第1のPchMOSトランジスタ931のドレインは第2のPchMOSトランジスタ932のソースに接続されている。第2のPchMOSトランジスタ932のゲートは基準電圧発生回路933の出力に接続され、ドレインがグランドに接続されている。2つのPchMOSトランジスタ931、932の中間ノードは、第1のPNP型バイポーラトランジスタ934のベースに接続され、第1のPNP型バイポーラトランジスタ934のコレクタはグランドに接続され、エミッタは抵抗935を介してVCCに接続されている。また、第1のPNP型バイポーラトランジスタ934のエミッタは第2のPNP型バイポーラトランジスタ936のベースに接続され、そのコレクタはグランドに接続され、エミッタは内部の変復調回路913や不揮発性メモリ915への電源(図中、「VDD」と表す。)となる。

【0016】以上のように構成された第1レギュレータ回路912の動作について、以下に簡単に説明する。図1616の第1レギュレータ回路912の第2のPchMOSトランジスタ932のしきい値電圧をVGS、2つのPNP型バイポーラトランジスタ934、936のベース−エミッタ間電圧をそれぞれVBE1、VBE2、基準電圧発生回路933により発生させた基準電圧をVrefとすれば、電源回路911から出力されるVCCの電圧がVref+VGS+VBE1+VBE2より高くなった場合にはPNP型バイポーラトランジスタがオンしてレギュレータ回路から出力されるVDDの電圧をVref+VGS+VBE1+VBE2まで下げる。以下、第1レギュレータ回路912により調整される出力電圧VDDの暫定的な最大値(Vref+VGS+VBE1+VBE2)を「Vmax」と表す。この最大電圧制御の動作の詳細は以下の通りである。

【0017】第2のPchMOSトランジスタ932のゲート電圧には基準電圧発生回路933の出力が入力されるため、その電圧はVrefとなっている。第2のPchMOSトランジスタ932のしきい値をVGSとすればそのソース電圧はVref+VGSとなる。ソース電圧がこれより高くなった場合には、第2のPchMOSトランジスタ932がオンしてソース電圧をVref+VGSまで下げることになる。一方、第2のPchMOSトランジスタ932のソース電圧がVref+VGSより低い場合には、第2のPchMOSトランジスタ932はオフするので、電流が流れず、ソース電圧は第1のPchMOSトランジスタ931のドレインから流れ込む電流によりVref+VGSまで上昇する。従って、いずれの場合にも第2のPchMOSトランジスタ932のソース電圧はVref+VGSとなる。

【0018】次に、第1のPchMOSトランジスタ931の動作について説明する。上述したとおり第2のPchMOSトランジスタ932のソースと第1のPchMOSトランジスタ931のドレインとは接続されており、第1のPchMOSトランジスタ931のゲートとドレインも接続されている。第2のPchMOSトランジスタ932のソース電圧はVref+VGSであるから、第1のPchMOSトランジスタ931のゲート電圧はVref+VGSとなる。第1のPchMOSトランジスタ931のしきい値電圧をVGS2とすれば、VCCの電圧がVref+VGS+VGS2より高くなった場合には、第1のPchMOSトランジスタ931はオンする。

【0019】次に第1のPNP型バイポーラトランジスタ934の動作について説明する。前述したとおり第1のPNP型バイポーラトランジスタ934のベース電圧はVref+VGSとなっている。第1のPNP型バイポーラトランジスタ934のエミッタ−ベース間はPN接合のため、エミッタ−ベース間に電流を流すためには、ベース−エミッタ間電圧VBE1がダイオードの順方向電圧以上である必要がある。

【0020】従って、第1のPNP型バイポーラトランジスタ934に電流が流れている場合には、そのエミッタ電圧は、Vref+VGS+VBE1となっている。次に第2のPNP型バイポーラトランジスタ936の動作について説明する。第1のPNP型バイポーラトランジスタ934のエミッタは第2のPNP型バイポーラトランジスタ936のベースに接続されている。従って第2のPNP型バイポーラトランジスタ936のベース電圧はVref+VGS+VBE1である。第2のPNP型バイポーラトランジスタ936のベース−エミッタ間電圧をVBE2とすれば、第1のPNP型バイポーラトランジスタ934と同様に考えて、そのエミッタ電圧は、上記Vmax(=Vref+VGS+VBE1+VBE2)となる。

【0021】従って、エミッタ電圧がこれ以上になれば、第2のPNP型バイポーラトランジスタ936がオンして、エミッタ電圧をVmaxまで下げることになる。第2のPNP型バイポーラトランジスタ936のエミッタは第1レギュレータ回路912の出力であり、変復調回路913等への電源VDDである。すなわち、VDDの電圧はVmaxよりも高くならないように制御されることとなる。

【0022】尚、電源回路911より供給されるVCCの電圧が前記Vmaxよりも低い場合は、第2のPNP型バイポーラトランジスタ936はオンしないため、第1レギュレータ回路912は動作せず、第1レギュレータ回路912から出力されるVDDの電圧は電源回路911からのVCCの電圧と同じになる。

【0023】

【発明が解決しようとする課題】リーダーライター990と非接触型ICカード900との間のデータ転送にASK変調(振幅変調)された搬送波を用いた場合、前述したように搬送波の振幅の大きさによりデータの0、1が定められる。振幅の大きい方をデータ1、小さい方をデータ0とした場合、図14にも示したように、小さい方の振幅の大きさは0とするのではなく、ある程度の大きさの振幅が使われる。これはデータ0が続いた場合に搬送波が送られない状態となると、電源電圧(VCC、VDD)を発生させることができず、非接触型ICカード900を動作させることができないからである。

【0024】ここで、振幅が小さい方の振幅の大きさが前述したVmaxに対応する大きさに近い場合、データが遷移して振幅の大きい方となった場合にはVCCの電圧がVmaxより高くなるため第1レギュレータ回路912が動作し、VDDの電圧をVmaxまで下げる。従って、データ0の場合とデータ1の場合とで、変復調回路913に供給されるVDDの電圧の差が少なくなる。

【0025】一方、受信データ信号が0であるか1であるかは、上記VDDを変復調回路913で復調することにより判別している。従って、データ0とデータ1とに対応する電圧値の差が小さくなると、変復調回路913で両者の判別が出来なくなったり、ノイズが入った場合に誤動作を起こす可能性が生じる。さらに、振幅の小さい方の振幅の大きさがVmaxより高くなるような場合には、常に第1レギュレータ回路912が動作するため、第1レギュレータ回路912を通った後のVDDの値からでは、もはやデータ0とデータ1との判別は不可能である。

【0026】すなわち、リーダーライター990と非接触型ICカード900との間の距離が近すぎる場合には、データ0に対応するVDDの電圧も十分に高くなるため、データ0とデータ1の判別が難しくなり、リーダーライター990から送信されてきたデータを判別し、不揮発性メモリ915に書き込むことができなくなる結果となる。

【0027】以上のようにリーダーライター990と非接触型ICカード900との間の距離が近すぎる場合にはデータ判別が困難になるという問題点が発生するが、ASK変調された電波により電力を供給する非接触型ICカードでは、逆にリーダーライター990と非接触型ICカード900との距離が遠い場合の誤動作を防止する必要もある。

【0028】上記従来の電源回路911では、全波整流回路により発生した電圧を降圧回路により降圧させ、若しくは昇圧回路により昇圧することにより、アナログ回路や不揮発性メモリ915に供給する電圧とロジック回路914に供給する電圧とを生成していた。しかしながら、上記従来の方法では、電波により供給される電力を十分に活用できず、結果としてリーダーライター990と非接触型ICカード900との間の利用可能距離が短くなるという問題点もある。

【0029】本発明は、上記のような問題点に鑑みてなされたものであって、その第1の目的は、変復調回路に送られるデータ信号の電圧値が所定値以上に大きくならないような制御を行うレギュレータ回路が動作するような状況においても、データ0とデータ1の判別を行うことが可能な電圧値を供給することができる半導体集積回路を提供することにある。

【0030】本発明の第2の目的は、リーダーライター990から電波により供給される電力を効率的に利用することができ、リーダーライター990と非接触型ICカード900との間の利用可能距離を従来よりも延長することが可能な半導体集積回路を提供することである。

【0031】

【課題を解決するための手段】上記第1の目的を達成するために、本発明に係る半導体集積回路は、交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えることを特徴としている。

【0032】この構成を備える半導体集積回路によると、整流回路により整流された直流電力の電圧値が変化した場合には、それに連動して前記レギュレータ回路からの出力電圧の最大値も変化することになり、その結果、前記直流電力の電圧値がVmaxを超えるような場合でも、レギュレータ回路の出力から前記直流電力の電圧値の変化を検出することが可能となるため、上記に説明したようなデータの誤判別などの問題に対応することが可能となる。

【0033】ここで、例えば、前記基準電圧変更回路はCR時定数回路であり、第1の容量素子の一端が前記入力端子に接続され、抵抗素子の一端が前記基準電圧発生回路の出力端子に接続され、第1の容量素子と抵抗素子との中間点が前記制御端子に接続されるようにすることができる。この構成では、第1の容量素子によるカップリングのために、直流電力の電圧値の変化と連動して制御端子の電圧値が変化する。しかしながら、CR時定数回路の特性により決定される所定時間の経過後に、制御端子の電圧は所定の基準電圧に戻ることとなる。従って、上記したように直流電力の電圧値の変化を検出してデータの誤判別を防止することができるだけでなく、電源電圧が長時間にわたって所定の電圧を超えることによる内部回路への悪影響を少なくすることができる点でも好適である。

【0034】ここで、前記基準電圧変更回路はさらに、一端が前記制御端子に接続され、他の一端がグランドラインに接続される第2の容量素子を含むことが好ましい。この構成では、直流電力の電圧値が変化した場合の、レギュレータ回路の出力電圧の変化量を小さく抑えることができるので、内部回路に供給する電源として、より安定した電源が得られることになるからである。

【0035】また、前記基準電圧変更回路は、一端が前記入力端子に接続された第1の容量素子と、一端が前記基準電圧発生回路の出力端子に接続され、他端が前記第1の容量素子の他端と接続された第2の容量素子とを含み、前記制御端子が、前記第1の容量素子と前記第2の容量素子との中間点に接続されて構成されるようにしてもよい。この構成でも、直流電力の電圧値が変化した場合のレギュレータ回路の出力電圧の変化量を小さくすることができるからである。

【0036】ここで、前記第1の容量素子は、ソース、ドレイン及び基板が前記入力端子に接続され、ゲートは、前記基準電圧発生回路の出力端子に接続された素子の当該出力端子とは逆側の一端と、前記制御端子との中間点に接続されるMOSトランジスタにより構成されるようにすることができる。また、前記基準電圧変更回路はさらに、電源投入後、所定時間の経過後に、出力が第1の出力レベルから第2の出力レベルに変化するパワーオンリセット回路と、少なくとも三つの端子を有し、第1の端子が前記パワーオンリセット回路の出力に、第2の端子がグランドラインに接続されるとともに、前記パワーオンリセット回路の出力が第1の出力レベルの場合に第3の端子と前記第2の端子との間が導通状態となり、前記パワーオンリセット回路の出力が第2に出力レベルの場合に第3の端子と前記第2の端子との間が非通電状態となるスイッチング素子とを備え、前記スイッチング素子の第3の端子は、前記第1の容量素子と前記制御端子との中間点に接続されているものとすることが好ましい。半導体集積回路に駆動電力が供給され始めた時点においては、基準電圧発生回路が安定して動作せず、制御端子に適切な基準電圧が入力されない場合があるため、係る場合にレギュレータ回路が適切に動作しないことによる内部回路への悪影響を抑制することができるからである。

【0037】具体的には、前記パワーオンリセット回路は、一端がグランドラインに接続された容量素子と、電源投入後、前記容量素子が充電されるまでは出力が第1の出力レベルとなり、前記容量素子が充電された後は出力が第2の出力レベルとなるインバータ素子とを含むものを用いることができる。この場合、前記パワーオンリセット回路は、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、他端が前記整流回路の直流電力出力端子に接続されている抵抗素子と、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、前記整流回路から直流電力が出力されない状態となった場合に導通状態となることにより、前記容量素子に充電された電荷を放電させるスイッチング素子とを含むことが好ましい。一旦駆動電力が供給され、電力供給が中断した後で再度駆動電力が供給されたような場合に、パワーオンリセット回路を構成する容量素子が完全に放電しないことによる問題の発生を防止することができるからである。

【0038】なお、上記したような搬送波に重畳されたデジタルデータの誤判別は、具体的には、例えば、前記半導体集積回路はさらに、前記レギュレータ回路からの出力を微分する微分回路と、当該微分回路からの出力に基づき、前記直流電力の電圧値の変化を検出する検出手段とを備えることで実現することが可能である。また、本発明の第2の目的は、不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることを特徴とする半導体集積回路により達成される。

【0039】この構成では、電源回路として二電圧整流回路を用い、当該二電圧整流回路により並行して出力される二系統の直流電力を、それぞれ不揮発性メモリやデジタル回路の駆動電力として用いることができるので、各々の回路に適した電圧の駆動電力を供給することが可能となり、もって回路の消費電力の増大を抑え、電源電力を効率的に利用することができる。

【0040】従って、係る半導体集積回路を非接触型ICカードなどの非接触型情報媒体に搭載した場合には、例えば所定波長の電波により、外部から非接触状態で供給される駆動電力を効率的に利用することができるため、リーダーライターなどの電力供給源とICカードなどの非接触型情報媒体との間の距離が比較的遠い場合でも、電力の不足に起因する非接触型情報媒体の誤動作を抑制することができる。

【0041】

【発明の実施の形態】以下、本発明に係る半導体集積回路及び当該半導体集積回路を搭載した非接触型情報媒体の実施の形態について、図面を参照しながら説明する。

(実施の形態1)まず、本発明の第1の実施の形態について説明する。なお、本実施の形態では、半導体集積回路を搭載した非接触型情報媒体の一例として、半導体集積回路を非接触型ICカードに搭載した場合について説明を行う。

【0042】(1)非接触型ICカード100の全体構成図1は、本発明の実施の形態に係る非接触型ICカード100の全体構成を説明するためのブロック図である。同図に示されるように、本実施の形態の非接触型ICカード100には半導体集積回路110が搭載されており、当該半導体集積回路110は、電源回路111、電圧調整回路112、変復調回路113、ロジック回路114、不揮発性メモリ115、第2レギュレータ回路116を含んでいる。特に図示はしないが、変復調回路113以外のアナログ回路として、クロック生成回路なども含まれていることは上記従来技術の非接触型ICカードと同様である。

【0043】電源回路111に接続されているアンテナコイル181及び同調用の容量素子182、ロジック回路114及び不揮発性メモリ115については、上記従来技術のものと同様であるから、ここでの詳細な説明は省略する。以下、本実施の形態の電源回路111、電圧調整回路112などについて詳細に説明する。図2は、本実施の形態の電源回路111の構成を示す図である。同図に示されるように、電源回路111は、アンテナコイル181の両端に発生した交流電圧から、ロジック回路114に供給される約2〜4Vの電圧(VDDL)と、変復調回路113などのアナログ回路や不揮発性メモリ115に供給される約4〜8Vの電圧(VDDH)をそれぞれ個別に生成するように二電圧整流回路を用いて構成されている。

【0044】即ち、本実施の形態の電源回路111は、二つの整流用のダイオード121、122、及び二つの平滑用の容量素子123、124を備えている。端子125は容量素子123と容量素子124との結合点に接続され、端子126は、ダイオード121のアノード及びダイオード122のカソードに接続されている。ダイオード121のカソードは容量素子123のもう一方の端子とVDDH用出力端子127に、ダイオード122のアノードは、容量素子124のもう一方の端子とグランドに接続される端子129に、それぞれ接続されている。なお、二つの容量素子123、124の結合点は、VDDL用出力端子128に接続されている。

【0045】この電源回路111の動作原理について、図3を参照しながら説明する。アンテナコイル181に不図示のリーダライターからの電波があたると、まず、図3(a)に示されるように、アンテナコイル181両端に交流電圧(VB−VA)が発生する。ここで、VAとは端子125の電圧、VBとは端子126の電圧を表すものとする。電圧VBが電圧VAよりも高い場合には、端子126→ダイオード121→容量素子123→端子125という経路で電流が流れ、VDDH用出力端子127とVDDL用出力端子128との間に図3(b)に示すような電圧が発生する。前記したように、VDDH用出力端子127は、アナログ回路や不揮発性メモリ115等に電圧を供給する出力端子である。

【0046】一方、電圧VBが電圧VAよりも低い場合には、端子125→容量素子124→ダイオード122→端子126という経路で電流が流れ、グランドに接続された端子129とVDDL用出力端子128との間に、同じく図3(b)に示すような電圧が発生する。前記したように、VDDL用出力端子128は、ロジック回路114に電圧を供給する出力端子である。さらに、図3(c)に示すように、VDDH用出力端子127とVDDL用出力端子128との間に発生した電圧は、平滑用の容量素子123により、また、端子129とVDDL用出力端子128との間に発生した電圧は、平滑用の容量素子124により、それぞれ平滑化され、図3(d)に示すように、それぞれ直流電圧に変換される。したがって、VDDH用出力端子127とVDDL用出力端子128との間、及び端子129とVDDL用出力端子128との間に、ほぼ等しい電圧が発生する。

【0047】ここで、端子129を基準に考えると、VDDH用出力端子127の電圧は、VDDL用出力端子128の電圧のほぼ二倍となる。発生した電圧は、VDDH用出力端子127、VDDL用出力端子128から、それぞれ半導体集積回路110の中の変復調回路113、不揮発性メモリ115、およびロジック回路114などにそれぞれ供給され、これにより非接触型ICカード100の全体が動作する。比較的高い電圧(4V程度)を供給しなければ動作しない不揮発性メモリ115は、VDDH用出力端子127から電源の供給を受け、比較的低い電圧(2V程度)で動作するロジック回路114は、VDDL用出力端子128から電源の供給を受ける。もっとも、アナログ回路としての変復調回路113、クロック生成回路などについては、非接触型ICカード100の仕様などに応じて、VDDL用出力端子128から電源の供給を受けるようにしてもよい。

【0048】さて、以上に説明したように、本実施の形態では電源回路111に二電圧整流回路を用いているが、リーダーライターから送信されてくるデータを判別して不揮発性メモリ115に書込むためには、VDDH用出力端子127からの出力を変復調回路113に入力する必要があり、ここでVDDH用出力端子127からの電圧が一定以上とならないように、従来と同様のレギュレータ回路を接続するとすれば、リーダーライターと非接触型ICカード100との間の距離が近すぎた場合にデータの判別ができない場合が生じ得ることになる。本実施の形態の非接触型ICカード100では、電圧調整回路112として、従来のレギュレータ回路に所定の回路を付加した回路構成とすることにより、VDDH用出力端子127からの電圧を略一定以上とならないような制御を行うとともに、リーダーライターから送信されたデータが0から1、若しくは1から0に変化したことが検出できるようにしている。以下、本実施の形態における電圧調整回路112の詳細について説明する。

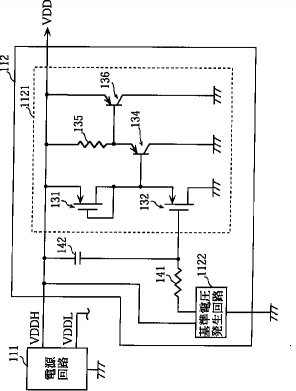

【0049】図4は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示される電圧調整回路112の中で、第1レギュレータ回路1121は、データが0であるか1であるかを判別するために変復調回路113に入力される電圧であるVDDHが、動作対象となる回路の最大定格電圧を超え、回路に問題が生じることを防止するために設けられるものであり、この第1レギュレータ回路1121及び基準電圧発生回路1122については、従来技術として説明したものと同様に動作するものであるから、ここでの詳細な説明は省略する。

【0050】本実施の形態の電圧調整回路112においては、第2のPchMOSトランジスタ132のゲートと基準電圧発生回路1122の出力との間に抵抗141が設けられているとともに、当該抵抗141の、第2のPchMOSトランジスタ132の側の端子と、電源回路111のVDDH用出力端子からの出力との間には、容量素子142が設けられている。この抵抗141と、容量素子142の動作により、電源回路111から供給されるVDDHの電圧値が、第1レギュレータ回路1121により電圧値が調整された場合の最大電圧値(Vmax)を超える場合においても、受信したデータが0から1へと変化した場合、若しくは1から0へと変化した場合をそれぞれ検出することが可能となるように構成されたものである。

【0051】以下、電圧調整回路112の動作について説明する。尚、以下の説明は、電源回路111から供給されるVDDHの電圧が十分に高い場合、即ち、少なくとも受信したデータが1(振幅の高い側)である場合に、VDDHの電圧がVmaxを超える場合について説明する。VDDHの電圧が十分に高くない場合は、第1レギュレータ回路1121が動作せず、受信したデータの値が1の場合に、第1レギュレータ回路1121への入力であるVDDHの電圧が第1レギュレータ回路1121により下げられることがないのであるから、データの値が0であるか1であるかの判別に特に困難は生じないからである。

【0052】なお、電源回路111より供給されるVDDHの電圧が上記Vmax(=Vref+VGS+VBE1+VBE2)より低い場合は、第2のPNP型バイポーラトランジスタ136がオンしないため、VDDの電圧は、電源回路111より供給されるVDDHの電圧と同じになる。まず、本実施の形態の電圧調整回路112の特徴である容量素子142の動作について説明する。容量素子142は、電源回路111より供給される電源電圧VDDHが安定状態にある場合には何も動作しない。以下にアンテナコイル181にリーダーライターから送信されたにASK変調(振幅変調)された電波が入力された場合について、図5を参照しながら説明する。ASK変調された信号は、図5(a)に示したような波形であり、これが電源回路111を通過することにより、整流、平滑され図5(b)のような波形になる。これがVDDHの波形である。なお、図中、点線はVmaxを示している。ここで、波の低いところをデータ0、高いところをデータ1とすれば、データ0からデータ1に遷移するところで電源電圧は急激に上昇する。ここで電源電圧の上昇幅をdVとする。第2のPchMOSトランジスタ132のベースは、容量素子142を介してVDDHに接続されており、従って、この容量素子142によるカップリングにより、VDDHの電圧がdV上昇した場合には、第2のPchMOSトランジスタ132のベース電圧もdVだけ上昇する。

【0053】このことは、第1レギュレータ回路1121から見れば、基準電圧発生回路1122から出力される基準電圧がdVだけ上昇したことと同じである。即ち、最終的に第1レギュレータ回路1121から出力されるVDDの最大値はVmax+dVとなる。一方、第2のPchMOSトランジスタ132のベースは抵抗141を介して基準電圧発生回路1122に接続されている。従って、基準電圧として第1レギュレータ回路1121に入力されることとなる電圧は、データが0から1に遷移した直後はVref+dVであるが、抵抗141と容量素子142との特性値より算出される時定数により、時間の経過とともにVrefに戻る。その結果、VDDの電圧の最大値もVmaxに戻る。

【0054】なお、抵抗141及び容量素子142の特性値について、抵抗141の抵抗値をR、容量素子142のキャパシタンスをCとすると、具体的には、R*Cの値がデータ転送速度よりも大きくなるように設定することが好ましい。例えばR=1MΩ、データ転送速度が4.7μ秒であるとすると、Cの値は4.7pFよりも大きくなるように設定する。

【0055】逆に、データ1からデータ0に遷移する場合も同様に考えることができる。この場合には、第1レギュレータ回路1121へと入力される基準電圧がdVだけ下降したのと同じことになるから、遷移直後の第1レギュレータ回路1121の出力VDDの最大値はVmax−dVとなり、時間の経過とともにVmaxへと戻ることになる。

【0056】この波形を図5(c)に示す。本実施の形態の復調回路113は、VDDの信号から微分信号を取得する微分回路を内部に備えており、この波形から対応する微分信号(パルス信号)を取得し、当該パルス信号をラッチすることにより、データが0から1、若しくは1から0へと遷移したことを検出することができるので、これにより、VDDHの電圧値が過電圧状態となった場合でも、受信したデータが0であるか1であるかを判別することができる。図5(d)は、上記微分信号の波形を示す図である。

【0057】なお、第2レギュレータ回路116については、過電圧状態となった場合でもデータの誤判別といった問題は生じないので、従来のものと同様のものを用いることができる。以上に説明したように、本実施の形態の非接触型ICカード100では、電源回路111として二電圧整流回路を用いて構成しているため、極めて簡単な構成で、VDDH用出力端子127に、主として不揮発性メモリ115を動作させるための4V以上の高い電圧を発生させる一方で、同時にVDDL用出力端子128に、ロジック回路114を動作させるための2V程度の低い電圧を発生させることができる。

【0058】従って、非接触型ICカード100の回路動作と直接関係のない電力消費の原因となる昇圧回路あるいは降圧回路を必要としないため、リーダーライターから供給される全ての電力を非接触型ICカード100の動作に使用することができ、通常の動作を安定させることができる他、非接触型ICカード100のリーダーライターからの距離が比較的遠い場合でも安定した動作を実現することが可能となり、両者の間で通信可能な距離を伸ばすことができる。

【0059】また、本実施の形態の非接触型ICカード100では、電源回路111の出力が過電圧状態となった場合でも、ASK変調された信号に含まれるデータが0から1に遷移したこと、及び1から0に遷移したことを検出することができるので、結果として受信したデータの誤判別が生じることを防止することができる。

(実施の形態2)次に、本発明の第2の実施の形態について説明する。本実施の形態の非接触型ICカードは電源回路111の回路構成が第1の実施の形態と異なっているので、以下、異なる部分を中心として説明し、第1の実施の形態と同様な部分については詳細な説明を省略する。

【0060】図6は、本実施の形態における電源回路111の構成を示す図である。同図に示されるように、本実施の形態と第1の実施の形態とにおける非接触型ICカード100の半導体集積回路を比較すると、第1の実施の形態における非接触型ICカード100の中の電源回路111においては、整流用として2個のダイオード121及び122が用いられていたが、本実施の形態における電源回路111では、整流用素子として、2個のNチャンネルMOSトランジスタ151、152で構成されている。

【0061】NチャンネルMOSトランジスタ151のソースとドレインは、端子126とVDDH用出力端子127とにそれぞれ接続され、ゲートは端子126に接続されている。NチャンネルMOSトランジスタ152のソースとドレインは、端子126と端子129とにそれぞれ接続され、ゲートは端子129に接続されている。このような構成により、その動作は図2に示した第1の実施の形態の電源回路111と同じになる。

【0062】通常、本発明に係る半導体集積回路は、CMOSプロセスを用いて製造される。従って、図2に示したようにダイオード121、122を用いる場合よりも、本実施の形態のようにMOSトランジスタを用いて、CMOSゲート回路を形成するのと同時にMOSトランジスタを形成するようにしたほうが、コスト面や、回路面積など、プロセス的に有利である。

【0063】(実施の形態3)次に、本発明の実施の形態3について説明する。本実施の形態の非接触型ICカードも電源回路111の回路構成が第1の実施の形態と異なっているので、以下、異なる部分を中心として説明し、第1の実施の形態と同様な部分については詳細な説明を省略する。

【0064】図7は、本実施の形態の電源回路111の構成を示す図である。本実施の形態における電源回路111では、整流用素子として2個のPチャンネルMOSトランジスタ153及び154を用いている。PチャンネルMOSトランジスタ153のソースとドレインは、端子126とVDDH用出力端子127とにそれぞれ接続され、ゲートはVHHD用出力端子127に接続されている。PチャンネルMOSトランジスタ154のソースとドレインは、端子126と端子129とにそれぞれ接続され、ゲートは端子126に接続されている。このような構成により、その動作は第1及び第2の実施の形態における電源回路111と同じになる。

【0065】本発明の半導体集積回路は、半導体基板としてコスト的に安価なP型の基板を使って製造されることが想定される。この場合、整流用のMOSトランジスタとしてNチャンネルのものを用いると、端子126の電圧が端子129の電圧よりも下がった時にP−ウェル内に流れる電流が基板全体に波及する。一方、本実施の形態のように、整流用のMOSトランジスタをPチャンネルで形成すると、端子126の電圧が端子129の電圧よりも下がった場合に流れる電流は、N−ウェル内で閉じるので、半導体集積回路全体の動作がより安定するという効果がある。

【0066】以上、第2及び第3の実施の形態では、電源回路111における二電圧整流回路に用いる整流用素子として、2個のNチャンネルMOSトランジスタを用いた場合と、2個のPチャンネルMOSトランジスタを用いた場合とについて説明した。ここで、整流ダイオードも含めて各種整流用素子を混合して用いることも可能であることは勿論であり、例えば整流用素子の1個をNチャンネルMOSトランジスタとし、他の1個をPチャンネルMOSトランジスタとしても、その動作は上記に説明したものと同じになる。

【0067】(実施の形態4)次に、本発明の第4の実施の形態について説明する。一般に回路を安定して動作させるためには電源電圧の変化は小さい方が好ましいため、本実施の形態では、VDDHの電圧の変化に対するVDDの電圧の変化を小さくする方法について説明する。なお、本実施の形態の非接触型ICカードは、電圧調整回路112の回路構成が第1の実施の形態と異なっているので、第1の実施の形態と異なる部分を中心として説明し、第1の実施の形態と同じ部分については詳細な説明を省略する。

【0068】図8は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、第1の実施の形態で説明した容量素子142とグランドとの間に、さらに第2の容量素子143を設けている。ここで、第1の容量素子142の容量をC1、第2の容量素子143の容量をC2とした場合、VDDHの電圧がdV変化したとすると、基準電圧発生回路1122からの基準電圧は、C1/(C1+C2)×dVだけ変化することになる。従って、VDDHの電圧がdV変化した場合のVDDの最大電圧は、Vmax±C1/(C1+C2)×dVとなり、第1の実施の形態に比べてVDDHの電圧の変化に対するVDDの電圧の変化を小さくすることができる。

【0069】(実施の形態5)次に、本発明の第5の実施の形態について説明する。本実施の形態では、第4の実施の形態と同様に、VDDHの電圧の変化に対するVDDの電圧の変化を小さくする別の方法について説明する。なお、本実施の形態の非接触型ICカードも、電圧調整回路112の回路構成が第1の実施の形態と異なっているのみであるから、第1の実施の形態と同じ部分については詳細な説明を省略する。

【0070】図9は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、基準電圧発生回路1122の出力と電源回路111からの出力との間に、直列に2つの容量素子142、144を設け、当該二つの容量素子の中間ノードをレギュレータ回路1121に入力するようにしている。ここで、電源回路111の側の第1の容量素子142の容量をC1、基準電圧発生回路1122の側の第2の容量素子144の容量をC2とした場合、レギュレータ回路1121に入力される電圧は、容量分割によりVref+(VDDH−Vref)×C1/(C1+C2)となる。従って、電源回路111からのVDDHの電圧がdVだけ変化した場合、レギュレータ回路1121に基準電圧として入力される電圧は、C1/(C1+C2)×dVだけ変化することになり、第4の実施の形態と同様に、VDDの電圧の変化を大きくしたくない場合に有効な方法となる。

【0071】(実施の形態6)次に、本発明の第6の実施の形態について説明する。図10は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、第1の実施の形態における容量素子142が、PchMOSトランジスタ145で構成されることを特徴としている。PchMOSトランジスタ145のゲートは、レギュレータ回路1121ヘの基準電圧の入力に接続され、PchMOSトランジスタ145のソース、ドレイン、及び基板は、電源回路111からの出力であるVDDHに接続されている。

【0072】PchMOSトランジスタ145のゲート電圧は、ソース、ドレイン、基板の電圧より低い。PchMOSトランジスタ145がオンし、容量素子として働くことができる。本実施の形態の構成にすることにより、MOSトランジスタのゲート容量を用いることができ、容量素子の面積を小さくすることができる。換言すればチップ面積を小さくすることができ、コストを削減することができる。

【0073】(実施の形態7)次に、本発明の第7の実施の形態について説明する。本実施の形態でも、これまでの実施の形態と電圧調整回路112の構成が異なっているので、以下、異なる部分について説明する。図11は、本実施の形態の電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、レギュレータ回路1121の入力ノードとグランドとの間にNchMOSトランジスタ146を備えている。さらにNchMOSトランジスタ146のゲートはパワーオンリセット回路147に接続されている。パワーオンリセット回路147は電源(VDDH)とグランドとの間に設けられた抵抗161、容量素子162、及び抵抗161、容量素子162の中間ノードを入力とするインバータ素子163で構成されている。なお、本実施の形態では、パワーオンリセット回路147をVDDHと接続するようにしたが、VDDLに接続するようにしてもよい。

【0074】本実施の形態のようにパワーオンリセット回路を設ける理由は、非接触型ICカード100がリーダーライターに接近することにより、電源回路111により電源電圧が発生した場合(以下、「電源投入時」という。)において、電源電圧の上昇が急激であることによる非接触型ICカード100の内部回路の破壊を防止することにある。従って、以下、電源投入時のパワーオンリセット回路147の動作について説明する。

【0075】非接触型ICカード100の用途などにもよるであろうが、電源投入時には電源電圧VDDH(若しくはVDDL)は急速に立ち上がることが多いと考えられる。しかしながら、抵抗161と容量素子162の中間ノードの電圧は、容量素子162が充電されるまでは上昇しない。すなわち、抵抗161を通して容量素子162が充電されるため、容量素子162を充電するまでにはある程度の時間がかかる。従ってインバータ素子163への入力は電源投入当初はLであり、ある程度の時間の後容量素子162が充電されHになる。逆にインバータ素子163の出力側から見れば、出力は当初Hであり、ある程度の時間の後Lになる。

【0076】容量素子162が充電され、インバータ素子163の出力がLになるまでの間はNchMOSトランジスタ146はオン状態となっている。ここで、本実施の形態の基準電圧発生回路1122は、電源投入直後は動作が不安定であり厳密な基準電圧を発生することは出来ない。一方で、電源投入時においても容量素子142によるカップリングは発生するため、VDDHの電圧が0からVまで上昇したとすれば、レギュレータ回路1121に入力される基準電圧ノードの電圧も少なくともVまで上昇することになる。

【0077】しかしながら、本実施の形態の構成では、インバータ素子163の出力がLとなるまでの間はNchMOSトランジスタ146がオン状態となっているため、グランドに電流が流れ、レギュレータ回路1121に入力される基準電圧の上昇が抑えられ、従って、VDDHの電圧とレギュレータ回路1121に入力される基準電圧との間に電圧差が生じるため、レギュレータ回路1121が動作し、出力されるVDDの電圧を下げる。すなわち電源投入時の電源電圧の上昇が大きすぎるような場合であっても、電源投入直後にレギュレータ回路1121を動作させることができることになる。これにより、非接触型ICカード100が急激にリーダーライターに接近し、電源回路111から出力される信号の電圧が急激に上昇したような場合に、レギュレータ回路1121が動作しないことで内部回路に過電圧の信号が流れることによる内部回路の破壊を防止することができる。

【0078】(実施の形態8)次に本発明の第8の実施の形態について説明する。本実施の形態では、第7の実施の形態において、パワーオンリセット回路147の構成を変更したものであるので、以下、第7の実施の形態と異なる点について説明する。図12は、本実施の形態の電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態のパワーオンリセット回路148は、抵抗161と並列にPchMOSトランジスタ164を備えたものである。以下、その動作について説明する。

【0079】最初の電源投入時は、PchMOSトランジスタ164が動作しないため、第7の実施の形態と同じ動作となる。その後、電源が切られ直ぐに再び電源が投入された場合、具体的には、非接触型ICカード100が一端リーダーライターから離れ、その後すぐに、再びリーダーライターに近づいたような場合について説明する。最初の電源投入により充電された容量素子162は、抵抗161を介して放電される。しかし、第7の実施の形態で説明したように、電源投入時の内部回路の破壊を防止するという目的のためには、一般的に抵抗161の抵抗値はあまり小さくはしない方が好ましいと考えられるため、抵抗161を介した容量素子162の放電には多少の時間がかかることになる。

【0080】このような場合に、PchMOSトランジスタ164がないとすれば、電源が一端切られた後、直ぐに再度電源が投入されたような場合には、容量素子162がまだ充電されたままになっている場合があり得る。かかる場合、再度の電源投入時のインバータ素子163の入力がHとなり、出力がLとなるため、電源投入時のNchMOSトランジスタ146がオフ状態となってしまう。

【0081】一方、電源再投入時には、容量素子142によるカップリングが再び発生し、レギュレータ回路1121に基準電圧として入力される電圧値が再び電源電圧まで上昇する。上記のような場合には、NchMOSトランジスタ146はオフ状態であるから、レギュレータ回路1121に基準電圧として入力される電圧と電源電圧とが等しくなるため、レギュレータ回路1121が動作しなくなってしまう。

【0082】本実施の形態では、電源が切られた場合にPchMOSトランジスタ164がオン状態となるため、容量素子162に充電された電荷を速やかに放電することができる。従って、再び電源が入れられた場合においてもインバータ素子163の入力をより確実にLとすることができる。その結果、電源再投入時のインバータ素子163の出力をHとしてNchMOSトランジスタ146をオン状態とすることができるため、容量素子142によるカップリングが発生しても、レギュレータ回路1121に基準電圧として入力される電圧と、VDDHの電圧との間に差が生じさせることができ、レギュレータ回路1121を動作させることができる。

【0083】<変形例>以上、本発明の種々の実施の形態について説明してきたが、本発明の内容が、上記実施の形態に示された具体例に限定されないことは勿論であり、例えば、以下のような変形例を考えることができる。

(1)本発明における半導体集積回路においては、レギュレータ回路1121、基準電圧発生回路1122の回路構成は特に限定されない。即ち、上記各実施の形態では、レギュレータ回路1121は、PchMOSトランジスタとPNP型バイポーラトランジスタにより構成しているが、全てバイポーラトランジスタで構成しても良いし、全てMOSトランジスタで構成してもよい。基準電圧を入力し、その値に応じて出力電圧の最大値が決まる形式のレギュレータ回路ならば本発明を適用することは可能である。

【0084】(2)基準電圧発生回路1122についても、電源電圧(VDDH)の変化に対して発生する基準電圧が変化しないものであれば、本発明に適用することはできる。一例をあげれば、本発明において実施の形態にあげたうちレギュレータ回路1121の基準電圧をグランドに接続し、その電源側に定電流回路を備えた回路構成が考えられる。

【0085】(3)容量素子の形式については、上記第6の実施の形態において、PchMOSトランジスタを例にとり説明したが、他の形式であってもよい。例えば、強誘電体キャパシタを用いてもよいし、層間容量を用いても良い。また、パワーオンリセット回路は、本実施の形態では、電源投入直後のみ作動するように時間制御により構成したものを例に示したが、一定電源電圧以下の場合に作動するように電圧制御の方法により構成しても良い。

【0086】(4)上記実施の形態では、電源回路111として二電圧整流回路を用いた場合について説明した。これは、リーダーライターから電波により供給される電力を有効に利用し、リーダーライターと非接触型情報媒体との間の距離が遠い場合でも誤動作等を防止することを可能とし、両者の間の利用可能距離を従来よりも延長することができるという効果を奏するものであるが、電源回路111の構成はこれに限定されるわけではなく、従来通りの全波整流回路を用いるようにしてもよい。

【0087】(5)また、上記第2の実施の形態から第3の実施の形態では、電源回路111の種々の構成について、また、第4の実施の形態から第8の実施の形態では、電圧調整回路112の種々の構成について、それぞれ説明したが、それらを適宜組合せて半導体集積回路を構成することも可能である。

【0088】

【発明の効果】以上のように、本発明の第1の半導体集積回路は、交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えているので、例えばICカードなどの非接触型情報媒体に搭載した場合に、搬送波から供給される電力が過電圧状態となったような場合でも、当該搬送波に重畳されたデータの誤判別などの問題点に対処することができるという効果がある。

【0089】また、本発明の第2の半導体集積回路は、不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることとしているので、例えば非接触型情報媒体に適用した場合、搬送波により供給される駆動電力の利用効率を向上させることができ、もって電力供給源と非接触型情報媒体との間の距離が離れた場合でも、従来より安定した動作を実現することができるという効果がある。

【図面の簡単な説明】

【図1】本発明の実施の形態に係る非接触型ICカード100の全体構成を説明するためのブロック図である。

【図2】本発明の第1の実施の形態における電源回路111の構成を示す図である。

【図3】二電圧整流回路を用いた電源回路111の動作原理について説明するための図である。

【図4】本発明の第1の実施の形態における電圧調整回路112の構成を示す図である。

【図5】第1の実施の形態における電圧調整回路112の動作について説明するための図である。

【図6】第2の実施の形態における電源回路111の構成を示す図である。

【図7】第3の実施の形態における電源回路111の構成を示す図である。

【図8】本発明の第4の実施の形態における電圧調整回路112の構成を示す図である。

【図9】本発明の第5の実施の形態における電圧調整回路112の構成を示す図である。

【図10】本発明の第6の実施の形態における電圧調整回路112の構成を示す図である。

【図11】本発明の第7の実施の形態における電圧調整回路112の構成を示す図である。

【図12】本発明の第8の実施の形態における電圧調整回路112の構成を示す図である。

【図13】従来の一般的な非接触型ICカードの構成の一例を模式的に示す機能ブロック図である。

【図14】リーダーライター990から送信される搬送波の具体的な構造の一例を示す図である。

【図15】従来の電源回路911の内部構成の一例を示す図である。

【図16】従来第1レギュレータ回路912として用いられていた回路の構成の一例を示す図である。

【符号の説明】

100 非接触型ICカード

110 半導体集積回路

111 電源回路

112 電圧調整回路

1121 第1レギュレータ回路

1122 基準電圧発生回路

113 変復調回路

114 ロジック回路

115 不揮発性メモリ

116 第2レギュレータ回路

【0001】

【発明の属する技術分野】本発明は、半導体集積回路、当該半導体集積回路を搭載した非接触型情報媒体、及び半導体集積回路の駆動方法に関する。

【0002】

【従来の技術】近年、コイルの相互誘導現象を利用して、所定波長の電波を用いて電力の供給を行うとともにデータの送受信を行うようにした、ICカードなどの非接触型情報媒体が実用化の段階に入っている。係る非接触型情報媒体の一例としてのICカードは、ICカードとの間で電波の送受信を行うリーダーライターと当該ICカードとの間で通信が可能な距離によって、大きく近接型、近傍型などに分類されており、それぞれについての標準規格も整いつつあるところである。

【0003】特にリーダーライターから、1cmから約20cm程度までの距離で用いることが可能な近接型のICカードは、例えば定期券等の用途に用いるとすれば、駅の改札口などで定期入れからICカードを取り出すことなく、リーダーライターとの非接触状態での情報のやり取りに基づいて改札口のゲートの開閉制御を行うことも可能となるなど、極めて広い範囲で適用される可能性を有するものである。

【0004】しかしながら、広い範囲に適用されるにはICカードの小型軽量化が重要となる他、適用範囲が広がるほどICカードの取扱いが乱雑となる場合も増加すると予想されるため、係る乱雑な取扱いに対する故障のしにくさなども考慮して、ICカードなどの非接触型情報媒体には、複雑な回路を小さい面積に収めた半導体集積回路が搭載されるのが通常となっている。

【0005】以下、半導体集積回路を搭載した一般的な非接触型ICカードの構成について説明する。図13は、一般的な非接触型ICカードの構成の一例を模式的に示す機能ブロック図である。なお同図には、ICカード900の他に、ICカード900と電波の送受信を行うリーダーライター990も示されている。以下、同図に示されるICカード900の構成及び動作について簡単に説明する。

【0006】ICカード900には、リーダーライター990に接続されたアンテナコイル991との間で電波の送受信を行うためのアンテナコイル981が設けられており、アンテナコイル991から送信される電波を受けて、アンテナコイル981の両端に発生した交流電圧がICカード900に搭載された半導体集積回路910へと入力される。なお、982は同調用の容量素子である。

【0007】尚、受信用のアンテナコイル981は一般的には非接触型ICカード900の半導体集積回路910の外部に接続される。同調用の容量素子982は非接触型ICカード900の半導体集積回路910の外部に接続されることが多いが、半導体集積回路910の内部に構成される場合もある。ICカード900は、リーダーライター990から送信される、ASK変調(振幅変調)された信号を受信して、当該信号から半導体集積回路910の駆動用電力を得るとともに、リーダーライター990から伝送されるデータを取得する。リーダーライター990から送信される搬送波の具体的な構造の一例を図14に示す。同図に示されるように、ASK変調された搬送波は、振幅の小さい部分が0のデータを、振幅の大きい部分が1のデータを表している。

【0008】半導体集積回路910は、電源回路911、第1レギュレータ回路912、変復調回路913、ロジック回路914、不揮発性メモリ915、降圧回路916、第2レギュレータ回路917を含んでいる。なお、ここでは、降圧回路916を設ける場合について説明するが、後述の理由により降圧回路916の代わりに昇圧回路を用いることも可能である。

【0009】図15は、電源回路911の内部構成を示す図である。同図に示されるように、従来のICカード900では、電源回路911として一般的な全波整流回路9111及び平滑用の容量素子9112を用いており、ここで、アンテナコイル981の両端に発生した交流電圧が整流されて直流電圧VCCとなる。整流された電流は、第1レギュレータ回路912により所定の電圧値より高くならないように制御されて変復調回路913やメモリ915を動作させるための電圧となる他、降圧回路916により降圧され、第2レギュレータ回路917により所定の電圧値より高くならないように制御されてロジック回路914の駆動電力を供給する。

【0010】なお、図13には特に図示していないが、第1レギュレータ回路912を通過した電流はクロック生成回路などのアナログ回路に対して駆動電力を供給する。クロック生成回路とは、アンテナコイル981の両端に発生した交流電圧から、ロジック回路914及び不揮発性メモリ915を動作させるためのクロック信号を生成する回路である。

【0011】通常、ロジック回路914などのディジタル回路は比較的低い電圧(約2〜3V)で動作するのに対し、不揮発性メモリ915にはこれよりも高い電圧を供給する必要がある。例えばFeRAMでは約3〜7V、EEPROMでは約10V以上(書き込み、消去時)の電圧が必要である。これに対応するため、上記のように、従来の非接触型ICカード900では、電源回路911において発生した電圧を降圧回路916で降圧してロジック回路914に供給するようにしている。もっとも、電源回路911でロジック回路914を動作させるための低い電圧を発生させるようにして、昇圧回路で昇圧し、変復調回路913やクロック生成回路などのアナログ回路や不揮発性メモリ915を動作させるようにすることもできる。

【0012】また、図14に示したように、ICカード900とリーダーライター990との間で送受信されるデータは交流電圧に重畳されており、非接触型ICカード900がリーダーライター990からのデータを受信する場合には、変復調回路913で復調され、非接触型ICカード900がリーダーライター990にデータを送信する場合には、変復調回路913で変調される。非接触型ICカード900とリーダーライター990との間で送受信されるデータはロジック回路914で制御され、不揮発性メモリ915に蓄えられる。

【0013】さて、コイルの相互誘導現象を利用して電力の供給及びデータの送受信を行うようにした非接触型ICカード900では、電源供給源であるリーダーライター990と非接触型ICカード900との間の距離により、電源回路911において発生する電源電圧が変化する。特に上記両者の間の距離が非常に近くなると過電圧が発生し、非接触型ICカード900の内部回路を破壊する恐れがあることから、かかる不具合を防止するため、電源発生回路911の他に第1及び第2のレギュレータ回路912及び917を設けておき、一定電圧以上の電源電圧にならないような回路構成を行っている。

【0014】図16は、従来第1レギュレータ回路912として用いられていた回路の構成の一例を示す図である。電源回路911からの出力(図中、「VCC」で表す。)とグランドとの間には、2つのPチャネルMOSトランジスタ(以下、「PchMOSトランジスタ」と表記する。)931及び932が直列に接続され、第1のPchMOSトランジスタ931のゲートとドレインはショートされ、ソースはVCCに接続されている。

【0015】また、第1のPchMOSトランジスタ931のドレインは第2のPchMOSトランジスタ932のソースに接続されている。第2のPchMOSトランジスタ932のゲートは基準電圧発生回路933の出力に接続され、ドレインがグランドに接続されている。2つのPchMOSトランジスタ931、932の中間ノードは、第1のPNP型バイポーラトランジスタ934のベースに接続され、第1のPNP型バイポーラトランジスタ934のコレクタはグランドに接続され、エミッタは抵抗935を介してVCCに接続されている。また、第1のPNP型バイポーラトランジスタ934のエミッタは第2のPNP型バイポーラトランジスタ936のベースに接続され、そのコレクタはグランドに接続され、エミッタは内部の変復調回路913や不揮発性メモリ915への電源(図中、「VDD」と表す。)となる。

【0016】以上のように構成された第1レギュレータ回路912の動作について、以下に簡単に説明する。図1616の第1レギュレータ回路912の第2のPchMOSトランジスタ932のしきい値電圧をVGS、2つのPNP型バイポーラトランジスタ934、936のベース−エミッタ間電圧をそれぞれVBE1、VBE2、基準電圧発生回路933により発生させた基準電圧をVrefとすれば、電源回路911から出力されるVCCの電圧がVref+VGS+VBE1+VBE2より高くなった場合にはPNP型バイポーラトランジスタがオンしてレギュレータ回路から出力されるVDDの電圧をVref+VGS+VBE1+VBE2まで下げる。以下、第1レギュレータ回路912により調整される出力電圧VDDの暫定的な最大値(Vref+VGS+VBE1+VBE2)を「Vmax」と表す。この最大電圧制御の動作の詳細は以下の通りである。

【0017】第2のPchMOSトランジスタ932のゲート電圧には基準電圧発生回路933の出力が入力されるため、その電圧はVrefとなっている。第2のPchMOSトランジスタ932のしきい値をVGSとすればそのソース電圧はVref+VGSとなる。ソース電圧がこれより高くなった場合には、第2のPchMOSトランジスタ932がオンしてソース電圧をVref+VGSまで下げることになる。一方、第2のPchMOSトランジスタ932のソース電圧がVref+VGSより低い場合には、第2のPchMOSトランジスタ932はオフするので、電流が流れず、ソース電圧は第1のPchMOSトランジスタ931のドレインから流れ込む電流によりVref+VGSまで上昇する。従って、いずれの場合にも第2のPchMOSトランジスタ932のソース電圧はVref+VGSとなる。

【0018】次に、第1のPchMOSトランジスタ931の動作について説明する。上述したとおり第2のPchMOSトランジスタ932のソースと第1のPchMOSトランジスタ931のドレインとは接続されており、第1のPchMOSトランジスタ931のゲートとドレインも接続されている。第2のPchMOSトランジスタ932のソース電圧はVref+VGSであるから、第1のPchMOSトランジスタ931のゲート電圧はVref+VGSとなる。第1のPchMOSトランジスタ931のしきい値電圧をVGS2とすれば、VCCの電圧がVref+VGS+VGS2より高くなった場合には、第1のPchMOSトランジスタ931はオンする。

【0019】次に第1のPNP型バイポーラトランジスタ934の動作について説明する。前述したとおり第1のPNP型バイポーラトランジスタ934のベース電圧はVref+VGSとなっている。第1のPNP型バイポーラトランジスタ934のエミッタ−ベース間はPN接合のため、エミッタ−ベース間に電流を流すためには、ベース−エミッタ間電圧VBE1がダイオードの順方向電圧以上である必要がある。

【0020】従って、第1のPNP型バイポーラトランジスタ934に電流が流れている場合には、そのエミッタ電圧は、Vref+VGS+VBE1となっている。次に第2のPNP型バイポーラトランジスタ936の動作について説明する。第1のPNP型バイポーラトランジスタ934のエミッタは第2のPNP型バイポーラトランジスタ936のベースに接続されている。従って第2のPNP型バイポーラトランジスタ936のベース電圧はVref+VGS+VBE1である。第2のPNP型バイポーラトランジスタ936のベース−エミッタ間電圧をVBE2とすれば、第1のPNP型バイポーラトランジスタ934と同様に考えて、そのエミッタ電圧は、上記Vmax(=Vref+VGS+VBE1+VBE2)となる。

【0021】従って、エミッタ電圧がこれ以上になれば、第2のPNP型バイポーラトランジスタ936がオンして、エミッタ電圧をVmaxまで下げることになる。第2のPNP型バイポーラトランジスタ936のエミッタは第1レギュレータ回路912の出力であり、変復調回路913等への電源VDDである。すなわち、VDDの電圧はVmaxよりも高くならないように制御されることとなる。

【0022】尚、電源回路911より供給されるVCCの電圧が前記Vmaxよりも低い場合は、第2のPNP型バイポーラトランジスタ936はオンしないため、第1レギュレータ回路912は動作せず、第1レギュレータ回路912から出力されるVDDの電圧は電源回路911からのVCCの電圧と同じになる。

【0023】

【発明が解決しようとする課題】リーダーライター990と非接触型ICカード900との間のデータ転送にASK変調(振幅変調)された搬送波を用いた場合、前述したように搬送波の振幅の大きさによりデータの0、1が定められる。振幅の大きい方をデータ1、小さい方をデータ0とした場合、図14にも示したように、小さい方の振幅の大きさは0とするのではなく、ある程度の大きさの振幅が使われる。これはデータ0が続いた場合に搬送波が送られない状態となると、電源電圧(VCC、VDD)を発生させることができず、非接触型ICカード900を動作させることができないからである。

【0024】ここで、振幅が小さい方の振幅の大きさが前述したVmaxに対応する大きさに近い場合、データが遷移して振幅の大きい方となった場合にはVCCの電圧がVmaxより高くなるため第1レギュレータ回路912が動作し、VDDの電圧をVmaxまで下げる。従って、データ0の場合とデータ1の場合とで、変復調回路913に供給されるVDDの電圧の差が少なくなる。

【0025】一方、受信データ信号が0であるか1であるかは、上記VDDを変復調回路913で復調することにより判別している。従って、データ0とデータ1とに対応する電圧値の差が小さくなると、変復調回路913で両者の判別が出来なくなったり、ノイズが入った場合に誤動作を起こす可能性が生じる。さらに、振幅の小さい方の振幅の大きさがVmaxより高くなるような場合には、常に第1レギュレータ回路912が動作するため、第1レギュレータ回路912を通った後のVDDの値からでは、もはやデータ0とデータ1との判別は不可能である。

【0026】すなわち、リーダーライター990と非接触型ICカード900との間の距離が近すぎる場合には、データ0に対応するVDDの電圧も十分に高くなるため、データ0とデータ1の判別が難しくなり、リーダーライター990から送信されてきたデータを判別し、不揮発性メモリ915に書き込むことができなくなる結果となる。

【0027】以上のようにリーダーライター990と非接触型ICカード900との間の距離が近すぎる場合にはデータ判別が困難になるという問題点が発生するが、ASK変調された電波により電力を供給する非接触型ICカードでは、逆にリーダーライター990と非接触型ICカード900との距離が遠い場合の誤動作を防止する必要もある。

【0028】上記従来の電源回路911では、全波整流回路により発生した電圧を降圧回路により降圧させ、若しくは昇圧回路により昇圧することにより、アナログ回路や不揮発性メモリ915に供給する電圧とロジック回路914に供給する電圧とを生成していた。しかしながら、上記従来の方法では、電波により供給される電力を十分に活用できず、結果としてリーダーライター990と非接触型ICカード900との間の利用可能距離が短くなるという問題点もある。

【0029】本発明は、上記のような問題点に鑑みてなされたものであって、その第1の目的は、変復調回路に送られるデータ信号の電圧値が所定値以上に大きくならないような制御を行うレギュレータ回路が動作するような状況においても、データ0とデータ1の判別を行うことが可能な電圧値を供給することができる半導体集積回路を提供することにある。

【0030】本発明の第2の目的は、リーダーライター990から電波により供給される電力を効率的に利用することができ、リーダーライター990と非接触型ICカード900との間の利用可能距離を従来よりも延長することが可能な半導体集積回路を提供することである。

【0031】

【課題を解決するための手段】上記第1の目的を達成するために、本発明に係る半導体集積回路は、交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えることを特徴としている。

【0032】この構成を備える半導体集積回路によると、整流回路により整流された直流電力の電圧値が変化した場合には、それに連動して前記レギュレータ回路からの出力電圧の最大値も変化することになり、その結果、前記直流電力の電圧値がVmaxを超えるような場合でも、レギュレータ回路の出力から前記直流電力の電圧値の変化を検出することが可能となるため、上記に説明したようなデータの誤判別などの問題に対応することが可能となる。

【0033】ここで、例えば、前記基準電圧変更回路はCR時定数回路であり、第1の容量素子の一端が前記入力端子に接続され、抵抗素子の一端が前記基準電圧発生回路の出力端子に接続され、第1の容量素子と抵抗素子との中間点が前記制御端子に接続されるようにすることができる。この構成では、第1の容量素子によるカップリングのために、直流電力の電圧値の変化と連動して制御端子の電圧値が変化する。しかしながら、CR時定数回路の特性により決定される所定時間の経過後に、制御端子の電圧は所定の基準電圧に戻ることとなる。従って、上記したように直流電力の電圧値の変化を検出してデータの誤判別を防止することができるだけでなく、電源電圧が長時間にわたって所定の電圧を超えることによる内部回路への悪影響を少なくすることができる点でも好適である。

【0034】ここで、前記基準電圧変更回路はさらに、一端が前記制御端子に接続され、他の一端がグランドラインに接続される第2の容量素子を含むことが好ましい。この構成では、直流電力の電圧値が変化した場合の、レギュレータ回路の出力電圧の変化量を小さく抑えることができるので、内部回路に供給する電源として、より安定した電源が得られることになるからである。

【0035】また、前記基準電圧変更回路は、一端が前記入力端子に接続された第1の容量素子と、一端が前記基準電圧発生回路の出力端子に接続され、他端が前記第1の容量素子の他端と接続された第2の容量素子とを含み、前記制御端子が、前記第1の容量素子と前記第2の容量素子との中間点に接続されて構成されるようにしてもよい。この構成でも、直流電力の電圧値が変化した場合のレギュレータ回路の出力電圧の変化量を小さくすることができるからである。

【0036】ここで、前記第1の容量素子は、ソース、ドレイン及び基板が前記入力端子に接続され、ゲートは、前記基準電圧発生回路の出力端子に接続された素子の当該出力端子とは逆側の一端と、前記制御端子との中間点に接続されるMOSトランジスタにより構成されるようにすることができる。また、前記基準電圧変更回路はさらに、電源投入後、所定時間の経過後に、出力が第1の出力レベルから第2の出力レベルに変化するパワーオンリセット回路と、少なくとも三つの端子を有し、第1の端子が前記パワーオンリセット回路の出力に、第2の端子がグランドラインに接続されるとともに、前記パワーオンリセット回路の出力が第1の出力レベルの場合に第3の端子と前記第2の端子との間が導通状態となり、前記パワーオンリセット回路の出力が第2に出力レベルの場合に第3の端子と前記第2の端子との間が非通電状態となるスイッチング素子とを備え、前記スイッチング素子の第3の端子は、前記第1の容量素子と前記制御端子との中間点に接続されているものとすることが好ましい。半導体集積回路に駆動電力が供給され始めた時点においては、基準電圧発生回路が安定して動作せず、制御端子に適切な基準電圧が入力されない場合があるため、係る場合にレギュレータ回路が適切に動作しないことによる内部回路への悪影響を抑制することができるからである。

【0037】具体的には、前記パワーオンリセット回路は、一端がグランドラインに接続された容量素子と、電源投入後、前記容量素子が充電されるまでは出力が第1の出力レベルとなり、前記容量素子が充電された後は出力が第2の出力レベルとなるインバータ素子とを含むものを用いることができる。この場合、前記パワーオンリセット回路は、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、他端が前記整流回路の直流電力出力端子に接続されている抵抗素子と、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、前記整流回路から直流電力が出力されない状態となった場合に導通状態となることにより、前記容量素子に充電された電荷を放電させるスイッチング素子とを含むことが好ましい。一旦駆動電力が供給され、電力供給が中断した後で再度駆動電力が供給されたような場合に、パワーオンリセット回路を構成する容量素子が完全に放電しないことによる問題の発生を防止することができるからである。

【0038】なお、上記したような搬送波に重畳されたデジタルデータの誤判別は、具体的には、例えば、前記半導体集積回路はさらに、前記レギュレータ回路からの出力を微分する微分回路と、当該微分回路からの出力に基づき、前記直流電力の電圧値の変化を検出する検出手段とを備えることで実現することが可能である。また、本発明の第2の目的は、不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることを特徴とする半導体集積回路により達成される。

【0039】この構成では、電源回路として二電圧整流回路を用い、当該二電圧整流回路により並行して出力される二系統の直流電力を、それぞれ不揮発性メモリやデジタル回路の駆動電力として用いることができるので、各々の回路に適した電圧の駆動電力を供給することが可能となり、もって回路の消費電力の増大を抑え、電源電力を効率的に利用することができる。

【0040】従って、係る半導体集積回路を非接触型ICカードなどの非接触型情報媒体に搭載した場合には、例えば所定波長の電波により、外部から非接触状態で供給される駆動電力を効率的に利用することができるため、リーダーライターなどの電力供給源とICカードなどの非接触型情報媒体との間の距離が比較的遠い場合でも、電力の不足に起因する非接触型情報媒体の誤動作を抑制することができる。

【0041】

【発明の実施の形態】以下、本発明に係る半導体集積回路及び当該半導体集積回路を搭載した非接触型情報媒体の実施の形態について、図面を参照しながら説明する。

(実施の形態1)まず、本発明の第1の実施の形態について説明する。なお、本実施の形態では、半導体集積回路を搭載した非接触型情報媒体の一例として、半導体集積回路を非接触型ICカードに搭載した場合について説明を行う。

【0042】(1)非接触型ICカード100の全体構成図1は、本発明の実施の形態に係る非接触型ICカード100の全体構成を説明するためのブロック図である。同図に示されるように、本実施の形態の非接触型ICカード100には半導体集積回路110が搭載されており、当該半導体集積回路110は、電源回路111、電圧調整回路112、変復調回路113、ロジック回路114、不揮発性メモリ115、第2レギュレータ回路116を含んでいる。特に図示はしないが、変復調回路113以外のアナログ回路として、クロック生成回路なども含まれていることは上記従来技術の非接触型ICカードと同様である。

【0043】電源回路111に接続されているアンテナコイル181及び同調用の容量素子182、ロジック回路114及び不揮発性メモリ115については、上記従来技術のものと同様であるから、ここでの詳細な説明は省略する。以下、本実施の形態の電源回路111、電圧調整回路112などについて詳細に説明する。図2は、本実施の形態の電源回路111の構成を示す図である。同図に示されるように、電源回路111は、アンテナコイル181の両端に発生した交流電圧から、ロジック回路114に供給される約2〜4Vの電圧(VDDL)と、変復調回路113などのアナログ回路や不揮発性メモリ115に供給される約4〜8Vの電圧(VDDH)をそれぞれ個別に生成するように二電圧整流回路を用いて構成されている。

【0044】即ち、本実施の形態の電源回路111は、二つの整流用のダイオード121、122、及び二つの平滑用の容量素子123、124を備えている。端子125は容量素子123と容量素子124との結合点に接続され、端子126は、ダイオード121のアノード及びダイオード122のカソードに接続されている。ダイオード121のカソードは容量素子123のもう一方の端子とVDDH用出力端子127に、ダイオード122のアノードは、容量素子124のもう一方の端子とグランドに接続される端子129に、それぞれ接続されている。なお、二つの容量素子123、124の結合点は、VDDL用出力端子128に接続されている。

【0045】この電源回路111の動作原理について、図3を参照しながら説明する。アンテナコイル181に不図示のリーダライターからの電波があたると、まず、図3(a)に示されるように、アンテナコイル181両端に交流電圧(VB−VA)が発生する。ここで、VAとは端子125の電圧、VBとは端子126の電圧を表すものとする。電圧VBが電圧VAよりも高い場合には、端子126→ダイオード121→容量素子123→端子125という経路で電流が流れ、VDDH用出力端子127とVDDL用出力端子128との間に図3(b)に示すような電圧が発生する。前記したように、VDDH用出力端子127は、アナログ回路や不揮発性メモリ115等に電圧を供給する出力端子である。

【0046】一方、電圧VBが電圧VAよりも低い場合には、端子125→容量素子124→ダイオード122→端子126という経路で電流が流れ、グランドに接続された端子129とVDDL用出力端子128との間に、同じく図3(b)に示すような電圧が発生する。前記したように、VDDL用出力端子128は、ロジック回路114に電圧を供給する出力端子である。さらに、図3(c)に示すように、VDDH用出力端子127とVDDL用出力端子128との間に発生した電圧は、平滑用の容量素子123により、また、端子129とVDDL用出力端子128との間に発生した電圧は、平滑用の容量素子124により、それぞれ平滑化され、図3(d)に示すように、それぞれ直流電圧に変換される。したがって、VDDH用出力端子127とVDDL用出力端子128との間、及び端子129とVDDL用出力端子128との間に、ほぼ等しい電圧が発生する。

【0047】ここで、端子129を基準に考えると、VDDH用出力端子127の電圧は、VDDL用出力端子128の電圧のほぼ二倍となる。発生した電圧は、VDDH用出力端子127、VDDL用出力端子128から、それぞれ半導体集積回路110の中の変復調回路113、不揮発性メモリ115、およびロジック回路114などにそれぞれ供給され、これにより非接触型ICカード100の全体が動作する。比較的高い電圧(4V程度)を供給しなければ動作しない不揮発性メモリ115は、VDDH用出力端子127から電源の供給を受け、比較的低い電圧(2V程度)で動作するロジック回路114は、VDDL用出力端子128から電源の供給を受ける。もっとも、アナログ回路としての変復調回路113、クロック生成回路などについては、非接触型ICカード100の仕様などに応じて、VDDL用出力端子128から電源の供給を受けるようにしてもよい。

【0048】さて、以上に説明したように、本実施の形態では電源回路111に二電圧整流回路を用いているが、リーダーライターから送信されてくるデータを判別して不揮発性メモリ115に書込むためには、VDDH用出力端子127からの出力を変復調回路113に入力する必要があり、ここでVDDH用出力端子127からの電圧が一定以上とならないように、従来と同様のレギュレータ回路を接続するとすれば、リーダーライターと非接触型ICカード100との間の距離が近すぎた場合にデータの判別ができない場合が生じ得ることになる。本実施の形態の非接触型ICカード100では、電圧調整回路112として、従来のレギュレータ回路に所定の回路を付加した回路構成とすることにより、VDDH用出力端子127からの電圧を略一定以上とならないような制御を行うとともに、リーダーライターから送信されたデータが0から1、若しくは1から0に変化したことが検出できるようにしている。以下、本実施の形態における電圧調整回路112の詳細について説明する。

【0049】図4は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示される電圧調整回路112の中で、第1レギュレータ回路1121は、データが0であるか1であるかを判別するために変復調回路113に入力される電圧であるVDDHが、動作対象となる回路の最大定格電圧を超え、回路に問題が生じることを防止するために設けられるものであり、この第1レギュレータ回路1121及び基準電圧発生回路1122については、従来技術として説明したものと同様に動作するものであるから、ここでの詳細な説明は省略する。

【0050】本実施の形態の電圧調整回路112においては、第2のPchMOSトランジスタ132のゲートと基準電圧発生回路1122の出力との間に抵抗141が設けられているとともに、当該抵抗141の、第2のPchMOSトランジスタ132の側の端子と、電源回路111のVDDH用出力端子からの出力との間には、容量素子142が設けられている。この抵抗141と、容量素子142の動作により、電源回路111から供給されるVDDHの電圧値が、第1レギュレータ回路1121により電圧値が調整された場合の最大電圧値(Vmax)を超える場合においても、受信したデータが0から1へと変化した場合、若しくは1から0へと変化した場合をそれぞれ検出することが可能となるように構成されたものである。

【0051】以下、電圧調整回路112の動作について説明する。尚、以下の説明は、電源回路111から供給されるVDDHの電圧が十分に高い場合、即ち、少なくとも受信したデータが1(振幅の高い側)である場合に、VDDHの電圧がVmaxを超える場合について説明する。VDDHの電圧が十分に高くない場合は、第1レギュレータ回路1121が動作せず、受信したデータの値が1の場合に、第1レギュレータ回路1121への入力であるVDDHの電圧が第1レギュレータ回路1121により下げられることがないのであるから、データの値が0であるか1であるかの判別に特に困難は生じないからである。

【0052】なお、電源回路111より供給されるVDDHの電圧が上記Vmax(=Vref+VGS+VBE1+VBE2)より低い場合は、第2のPNP型バイポーラトランジスタ136がオンしないため、VDDの電圧は、電源回路111より供給されるVDDHの電圧と同じになる。まず、本実施の形態の電圧調整回路112の特徴である容量素子142の動作について説明する。容量素子142は、電源回路111より供給される電源電圧VDDHが安定状態にある場合には何も動作しない。以下にアンテナコイル181にリーダーライターから送信されたにASK変調(振幅変調)された電波が入力された場合について、図5を参照しながら説明する。ASK変調された信号は、図5(a)に示したような波形であり、これが電源回路111を通過することにより、整流、平滑され図5(b)のような波形になる。これがVDDHの波形である。なお、図中、点線はVmaxを示している。ここで、波の低いところをデータ0、高いところをデータ1とすれば、データ0からデータ1に遷移するところで電源電圧は急激に上昇する。ここで電源電圧の上昇幅をdVとする。第2のPchMOSトランジスタ132のベースは、容量素子142を介してVDDHに接続されており、従って、この容量素子142によるカップリングにより、VDDHの電圧がdV上昇した場合には、第2のPchMOSトランジスタ132のベース電圧もdVだけ上昇する。

【0053】このことは、第1レギュレータ回路1121から見れば、基準電圧発生回路1122から出力される基準電圧がdVだけ上昇したことと同じである。即ち、最終的に第1レギュレータ回路1121から出力されるVDDの最大値はVmax+dVとなる。一方、第2のPchMOSトランジスタ132のベースは抵抗141を介して基準電圧発生回路1122に接続されている。従って、基準電圧として第1レギュレータ回路1121に入力されることとなる電圧は、データが0から1に遷移した直後はVref+dVであるが、抵抗141と容量素子142との特性値より算出される時定数により、時間の経過とともにVrefに戻る。その結果、VDDの電圧の最大値もVmaxに戻る。

【0054】なお、抵抗141及び容量素子142の特性値について、抵抗141の抵抗値をR、容量素子142のキャパシタンスをCとすると、具体的には、R*Cの値がデータ転送速度よりも大きくなるように設定することが好ましい。例えばR=1MΩ、データ転送速度が4.7μ秒であるとすると、Cの値は4.7pFよりも大きくなるように設定する。

【0055】逆に、データ1からデータ0に遷移する場合も同様に考えることができる。この場合には、第1レギュレータ回路1121へと入力される基準電圧がdVだけ下降したのと同じことになるから、遷移直後の第1レギュレータ回路1121の出力VDDの最大値はVmax−dVとなり、時間の経過とともにVmaxへと戻ることになる。

【0056】この波形を図5(c)に示す。本実施の形態の復調回路113は、VDDの信号から微分信号を取得する微分回路を内部に備えており、この波形から対応する微分信号(パルス信号)を取得し、当該パルス信号をラッチすることにより、データが0から1、若しくは1から0へと遷移したことを検出することができるので、これにより、VDDHの電圧値が過電圧状態となった場合でも、受信したデータが0であるか1であるかを判別することができる。図5(d)は、上記微分信号の波形を示す図である。

【0057】なお、第2レギュレータ回路116については、過電圧状態となった場合でもデータの誤判別といった問題は生じないので、従来のものと同様のものを用いることができる。以上に説明したように、本実施の形態の非接触型ICカード100では、電源回路111として二電圧整流回路を用いて構成しているため、極めて簡単な構成で、VDDH用出力端子127に、主として不揮発性メモリ115を動作させるための4V以上の高い電圧を発生させる一方で、同時にVDDL用出力端子128に、ロジック回路114を動作させるための2V程度の低い電圧を発生させることができる。

【0058】従って、非接触型ICカード100の回路動作と直接関係のない電力消費の原因となる昇圧回路あるいは降圧回路を必要としないため、リーダーライターから供給される全ての電力を非接触型ICカード100の動作に使用することができ、通常の動作を安定させることができる他、非接触型ICカード100のリーダーライターからの距離が比較的遠い場合でも安定した動作を実現することが可能となり、両者の間で通信可能な距離を伸ばすことができる。

【0059】また、本実施の形態の非接触型ICカード100では、電源回路111の出力が過電圧状態となった場合でも、ASK変調された信号に含まれるデータが0から1に遷移したこと、及び1から0に遷移したことを検出することができるので、結果として受信したデータの誤判別が生じることを防止することができる。

(実施の形態2)次に、本発明の第2の実施の形態について説明する。本実施の形態の非接触型ICカードは電源回路111の回路構成が第1の実施の形態と異なっているので、以下、異なる部分を中心として説明し、第1の実施の形態と同様な部分については詳細な説明を省略する。

【0060】図6は、本実施の形態における電源回路111の構成を示す図である。同図に示されるように、本実施の形態と第1の実施の形態とにおける非接触型ICカード100の半導体集積回路を比較すると、第1の実施の形態における非接触型ICカード100の中の電源回路111においては、整流用として2個のダイオード121及び122が用いられていたが、本実施の形態における電源回路111では、整流用素子として、2個のNチャンネルMOSトランジスタ151、152で構成されている。

【0061】NチャンネルMOSトランジスタ151のソースとドレインは、端子126とVDDH用出力端子127とにそれぞれ接続され、ゲートは端子126に接続されている。NチャンネルMOSトランジスタ152のソースとドレインは、端子126と端子129とにそれぞれ接続され、ゲートは端子129に接続されている。このような構成により、その動作は図2に示した第1の実施の形態の電源回路111と同じになる。

【0062】通常、本発明に係る半導体集積回路は、CMOSプロセスを用いて製造される。従って、図2に示したようにダイオード121、122を用いる場合よりも、本実施の形態のようにMOSトランジスタを用いて、CMOSゲート回路を形成するのと同時にMOSトランジスタを形成するようにしたほうが、コスト面や、回路面積など、プロセス的に有利である。

【0063】(実施の形態3)次に、本発明の実施の形態3について説明する。本実施の形態の非接触型ICカードも電源回路111の回路構成が第1の実施の形態と異なっているので、以下、異なる部分を中心として説明し、第1の実施の形態と同様な部分については詳細な説明を省略する。

【0064】図7は、本実施の形態の電源回路111の構成を示す図である。本実施の形態における電源回路111では、整流用素子として2個のPチャンネルMOSトランジスタ153及び154を用いている。PチャンネルMOSトランジスタ153のソースとドレインは、端子126とVDDH用出力端子127とにそれぞれ接続され、ゲートはVHHD用出力端子127に接続されている。PチャンネルMOSトランジスタ154のソースとドレインは、端子126と端子129とにそれぞれ接続され、ゲートは端子126に接続されている。このような構成により、その動作は第1及び第2の実施の形態における電源回路111と同じになる。

【0065】本発明の半導体集積回路は、半導体基板としてコスト的に安価なP型の基板を使って製造されることが想定される。この場合、整流用のMOSトランジスタとしてNチャンネルのものを用いると、端子126の電圧が端子129の電圧よりも下がった時にP−ウェル内に流れる電流が基板全体に波及する。一方、本実施の形態のように、整流用のMOSトランジスタをPチャンネルで形成すると、端子126の電圧が端子129の電圧よりも下がった場合に流れる電流は、N−ウェル内で閉じるので、半導体集積回路全体の動作がより安定するという効果がある。

【0066】以上、第2及び第3の実施の形態では、電源回路111における二電圧整流回路に用いる整流用素子として、2個のNチャンネルMOSトランジスタを用いた場合と、2個のPチャンネルMOSトランジスタを用いた場合とについて説明した。ここで、整流ダイオードも含めて各種整流用素子を混合して用いることも可能であることは勿論であり、例えば整流用素子の1個をNチャンネルMOSトランジスタとし、他の1個をPチャンネルMOSトランジスタとしても、その動作は上記に説明したものと同じになる。

【0067】(実施の形態4)次に、本発明の第4の実施の形態について説明する。一般に回路を安定して動作させるためには電源電圧の変化は小さい方が好ましいため、本実施の形態では、VDDHの電圧の変化に対するVDDの電圧の変化を小さくする方法について説明する。なお、本実施の形態の非接触型ICカードは、電圧調整回路112の回路構成が第1の実施の形態と異なっているので、第1の実施の形態と異なる部分を中心として説明し、第1の実施の形態と同じ部分については詳細な説明を省略する。

【0068】図8は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、第1の実施の形態で説明した容量素子142とグランドとの間に、さらに第2の容量素子143を設けている。ここで、第1の容量素子142の容量をC1、第2の容量素子143の容量をC2とした場合、VDDHの電圧がdV変化したとすると、基準電圧発生回路1122からの基準電圧は、C1/(C1+C2)×dVだけ変化することになる。従って、VDDHの電圧がdV変化した場合のVDDの最大電圧は、Vmax±C1/(C1+C2)×dVとなり、第1の実施の形態に比べてVDDHの電圧の変化に対するVDDの電圧の変化を小さくすることができる。

【0069】(実施の形態5)次に、本発明の第5の実施の形態について説明する。本実施の形態では、第4の実施の形態と同様に、VDDHの電圧の変化に対するVDDの電圧の変化を小さくする別の方法について説明する。なお、本実施の形態の非接触型ICカードも、電圧調整回路112の回路構成が第1の実施の形態と異なっているのみであるから、第1の実施の形態と同じ部分については詳細な説明を省略する。

【0070】図9は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、基準電圧発生回路1122の出力と電源回路111からの出力との間に、直列に2つの容量素子142、144を設け、当該二つの容量素子の中間ノードをレギュレータ回路1121に入力するようにしている。ここで、電源回路111の側の第1の容量素子142の容量をC1、基準電圧発生回路1122の側の第2の容量素子144の容量をC2とした場合、レギュレータ回路1121に入力される電圧は、容量分割によりVref+(VDDH−Vref)×C1/(C1+C2)となる。従って、電源回路111からのVDDHの電圧がdVだけ変化した場合、レギュレータ回路1121に基準電圧として入力される電圧は、C1/(C1+C2)×dVだけ変化することになり、第4の実施の形態と同様に、VDDの電圧の変化を大きくしたくない場合に有効な方法となる。

【0071】(実施の形態6)次に、本発明の第6の実施の形態について説明する。図10は、本実施の形態における電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、第1の実施の形態における容量素子142が、PchMOSトランジスタ145で構成されることを特徴としている。PchMOSトランジスタ145のゲートは、レギュレータ回路1121ヘの基準電圧の入力に接続され、PchMOSトランジスタ145のソース、ドレイン、及び基板は、電源回路111からの出力であるVDDHに接続されている。

【0072】PchMOSトランジスタ145のゲート電圧は、ソース、ドレイン、基板の電圧より低い。PchMOSトランジスタ145がオンし、容量素子として働くことができる。本実施の形態の構成にすることにより、MOSトランジスタのゲート容量を用いることができ、容量素子の面積を小さくすることができる。換言すればチップ面積を小さくすることができ、コストを削減することができる。

【0073】(実施の形態7)次に、本発明の第7の実施の形態について説明する。本実施の形態でも、これまでの実施の形態と電圧調整回路112の構成が異なっているので、以下、異なる部分について説明する。図11は、本実施の形態の電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態では、レギュレータ回路1121の入力ノードとグランドとの間にNchMOSトランジスタ146を備えている。さらにNchMOSトランジスタ146のゲートはパワーオンリセット回路147に接続されている。パワーオンリセット回路147は電源(VDDH)とグランドとの間に設けられた抵抗161、容量素子162、及び抵抗161、容量素子162の中間ノードを入力とするインバータ素子163で構成されている。なお、本実施の形態では、パワーオンリセット回路147をVDDHと接続するようにしたが、VDDLに接続するようにしてもよい。

【0074】本実施の形態のようにパワーオンリセット回路を設ける理由は、非接触型ICカード100がリーダーライターに接近することにより、電源回路111により電源電圧が発生した場合(以下、「電源投入時」という。)において、電源電圧の上昇が急激であることによる非接触型ICカード100の内部回路の破壊を防止することにある。従って、以下、電源投入時のパワーオンリセット回路147の動作について説明する。

【0075】非接触型ICカード100の用途などにもよるであろうが、電源投入時には電源電圧VDDH(若しくはVDDL)は急速に立ち上がることが多いと考えられる。しかしながら、抵抗161と容量素子162の中間ノードの電圧は、容量素子162が充電されるまでは上昇しない。すなわち、抵抗161を通して容量素子162が充電されるため、容量素子162を充電するまでにはある程度の時間がかかる。従ってインバータ素子163への入力は電源投入当初はLであり、ある程度の時間の後容量素子162が充電されHになる。逆にインバータ素子163の出力側から見れば、出力は当初Hであり、ある程度の時間の後Lになる。

【0076】容量素子162が充電され、インバータ素子163の出力がLになるまでの間はNchMOSトランジスタ146はオン状態となっている。ここで、本実施の形態の基準電圧発生回路1122は、電源投入直後は動作が不安定であり厳密な基準電圧を発生することは出来ない。一方で、電源投入時においても容量素子142によるカップリングは発生するため、VDDHの電圧が0からVまで上昇したとすれば、レギュレータ回路1121に入力される基準電圧ノードの電圧も少なくともVまで上昇することになる。

【0077】しかしながら、本実施の形態の構成では、インバータ素子163の出力がLとなるまでの間はNchMOSトランジスタ146がオン状態となっているため、グランドに電流が流れ、レギュレータ回路1121に入力される基準電圧の上昇が抑えられ、従って、VDDHの電圧とレギュレータ回路1121に入力される基準電圧との間に電圧差が生じるため、レギュレータ回路1121が動作し、出力されるVDDの電圧を下げる。すなわち電源投入時の電源電圧の上昇が大きすぎるような場合であっても、電源投入直後にレギュレータ回路1121を動作させることができることになる。これにより、非接触型ICカード100が急激にリーダーライターに接近し、電源回路111から出力される信号の電圧が急激に上昇したような場合に、レギュレータ回路1121が動作しないことで内部回路に過電圧の信号が流れることによる内部回路の破壊を防止することができる。

【0078】(実施の形態8)次に本発明の第8の実施の形態について説明する。本実施の形態では、第7の実施の形態において、パワーオンリセット回路147の構成を変更したものであるので、以下、第7の実施の形態と異なる点について説明する。図12は、本実施の形態の電圧調整回路112の構成を示す図である。同図に示されるように、本実施の形態のパワーオンリセット回路148は、抵抗161と並列にPchMOSトランジスタ164を備えたものである。以下、その動作について説明する。

【0079】最初の電源投入時は、PchMOSトランジスタ164が動作しないため、第7の実施の形態と同じ動作となる。その後、電源が切られ直ぐに再び電源が投入された場合、具体的には、非接触型ICカード100が一端リーダーライターから離れ、その後すぐに、再びリーダーライターに近づいたような場合について説明する。最初の電源投入により充電された容量素子162は、抵抗161を介して放電される。しかし、第7の実施の形態で説明したように、電源投入時の内部回路の破壊を防止するという目的のためには、一般的に抵抗161の抵抗値はあまり小さくはしない方が好ましいと考えられるため、抵抗161を介した容量素子162の放電には多少の時間がかかることになる。

【0080】このような場合に、PchMOSトランジスタ164がないとすれば、電源が一端切られた後、直ぐに再度電源が投入されたような場合には、容量素子162がまだ充電されたままになっている場合があり得る。かかる場合、再度の電源投入時のインバータ素子163の入力がHとなり、出力がLとなるため、電源投入時のNchMOSトランジスタ146がオフ状態となってしまう。

【0081】一方、電源再投入時には、容量素子142によるカップリングが再び発生し、レギュレータ回路1121に基準電圧として入力される電圧値が再び電源電圧まで上昇する。上記のような場合には、NchMOSトランジスタ146はオフ状態であるから、レギュレータ回路1121に基準電圧として入力される電圧と電源電圧とが等しくなるため、レギュレータ回路1121が動作しなくなってしまう。

【0082】本実施の形態では、電源が切られた場合にPchMOSトランジスタ164がオン状態となるため、容量素子162に充電された電荷を速やかに放電することができる。従って、再び電源が入れられた場合においてもインバータ素子163の入力をより確実にLとすることができる。その結果、電源再投入時のインバータ素子163の出力をHとしてNchMOSトランジスタ146をオン状態とすることができるため、容量素子142によるカップリングが発生しても、レギュレータ回路1121に基準電圧として入力される電圧と、VDDHの電圧との間に差が生じさせることができ、レギュレータ回路1121を動作させることができる。

【0083】<変形例>以上、本発明の種々の実施の形態について説明してきたが、本発明の内容が、上記実施の形態に示された具体例に限定されないことは勿論であり、例えば、以下のような変形例を考えることができる。

(1)本発明における半導体集積回路においては、レギュレータ回路1121、基準電圧発生回路1122の回路構成は特に限定されない。即ち、上記各実施の形態では、レギュレータ回路1121は、PchMOSトランジスタとPNP型バイポーラトランジスタにより構成しているが、全てバイポーラトランジスタで構成しても良いし、全てMOSトランジスタで構成してもよい。基準電圧を入力し、その値に応じて出力電圧の最大値が決まる形式のレギュレータ回路ならば本発明を適用することは可能である。

【0084】(2)基準電圧発生回路1122についても、電源電圧(VDDH)の変化に対して発生する基準電圧が変化しないものであれば、本発明に適用することはできる。一例をあげれば、本発明において実施の形態にあげたうちレギュレータ回路1121の基準電圧をグランドに接続し、その電源側に定電流回路を備えた回路構成が考えられる。

【0085】(3)容量素子の形式については、上記第6の実施の形態において、PchMOSトランジスタを例にとり説明したが、他の形式であってもよい。例えば、強誘電体キャパシタを用いてもよいし、層間容量を用いても良い。また、パワーオンリセット回路は、本実施の形態では、電源投入直後のみ作動するように時間制御により構成したものを例に示したが、一定電源電圧以下の場合に作動するように電圧制御の方法により構成しても良い。

【0086】(4)上記実施の形態では、電源回路111として二電圧整流回路を用いた場合について説明した。これは、リーダーライターから電波により供給される電力を有効に利用し、リーダーライターと非接触型情報媒体との間の距離が遠い場合でも誤動作等を防止することを可能とし、両者の間の利用可能距離を従来よりも延長することができるという効果を奏するものであるが、電源回路111の構成はこれに限定されるわけではなく、従来通りの全波整流回路を用いるようにしてもよい。

【0087】(5)また、上記第2の実施の形態から第3の実施の形態では、電源回路111の種々の構成について、また、第4の実施の形態から第8の実施の形態では、電圧調整回路112の種々の構成について、それぞれ説明したが、それらを適宜組合せて半導体集積回路を構成することも可能である。

【0088】

【発明の効果】以上のように、本発明の第1の半導体集積回路は、交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えているので、例えばICカードなどの非接触型情報媒体に搭載した場合に、搬送波から供給される電力が過電圧状態となったような場合でも、当該搬送波に重畳されたデータの誤判別などの問題点に対処することができるという効果がある。

【0089】また、本発明の第2の半導体集積回路は、不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることとしているので、例えば非接触型情報媒体に適用した場合、搬送波により供給される駆動電力の利用効率を向上させることができ、もって電力供給源と非接触型情報媒体との間の距離が離れた場合でも、従来より安定した動作を実現することができるという効果がある。

【図面の簡単な説明】

【図1】本発明の実施の形態に係る非接触型ICカード100の全体構成を説明するためのブロック図である。

【図2】本発明の第1の実施の形態における電源回路111の構成を示す図である。

【図3】二電圧整流回路を用いた電源回路111の動作原理について説明するための図である。

【図4】本発明の第1の実施の形態における電圧調整回路112の構成を示す図である。

【図5】第1の実施の形態における電圧調整回路112の動作について説明するための図である。

【図6】第2の実施の形態における電源回路111の構成を示す図である。

【図7】第3の実施の形態における電源回路111の構成を示す図である。

【図8】本発明の第4の実施の形態における電圧調整回路112の構成を示す図である。

【図9】本発明の第5の実施の形態における電圧調整回路112の構成を示す図である。

【図10】本発明の第6の実施の形態における電圧調整回路112の構成を示す図である。

【図11】本発明の第7の実施の形態における電圧調整回路112の構成を示す図である。

【図12】本発明の第8の実施の形態における電圧調整回路112の構成を示す図である。

【図13】従来の一般的な非接触型ICカードの構成の一例を模式的に示す機能ブロック図である。

【図14】リーダーライター990から送信される搬送波の具体的な構造の一例を示す図である。

【図15】従来の電源回路911の内部構成の一例を示す図である。

【図16】従来第1レギュレータ回路912として用いられていた回路の構成の一例を示す図である。

【符号の説明】

100 非接触型ICカード

110 半導体集積回路

111 電源回路

112 電圧調整回路

1121 第1レギュレータ回路

1122 基準電圧発生回路

113 変復調回路

114 ロジック回路

115 不揮発性メモリ

116 第2レギュレータ回路

【特許請求の範囲】

【請求項1】 交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えることを特徴とする半導体集積回路。

【請求項2】 前記基準電圧変更回路はCR時定数回路であり、第1の容量素子の一端が前記入力端子に接続され、抵抗素子の一端が基準電圧発生回路の出力端子に接続され、第1の容量素子と抵抗素子との中間点が前記制御端子に接続されることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】 前記基準電圧変更回路はさらに、一端が前記制御端子に接続され、他の一端がグランドラインに接続される第2の容量素子を含むことを特徴とする請求項2に記載の半導体集積回路。

【請求項4】 前記基準電圧変更回路は、一端が前記入力端子に接続された第1の容量素子と、一端が基準電圧発生回路の出力端子に接続され、他端が前記第1の容量素子の他端と接続された第2の容量素子とを含み、前記制御端子が、前記第1の容量素子と前記第2の容量素子との中間点に接続されて構成されることを特徴とする請求項1に記載の半導体集積回路。

【請求項5】 前記第1の容量素子は、ソース、ドレイン及び基板が前記入力端子に接続され、ゲートは、前記基準電圧発生回路の出力端子に接続された素子の当該出力端子とは逆側の一端と、前記制御端子との中間点に接続されるMOSトランジスタにより構成されることを特徴とする請求項2から4のいずれかに記載の半導体集積回路。

【請求項6】 前記基準電圧変更回路はさらに、電源投入後、所定時間の経過後に、出力が第1の出力レベルから第2の出力レベルに変化するパワーオンリセット回路と、少なくとも三つの端子を有し、第1の端子が前記パワーオンリセット回路の出力に、第2の端子がグランドラインに接続されるとともに、前記パワーオンリセット回路の出力が第1の出力レベルの場合に第3の端子と前記第2の端子との間が導通状態となり、前記パワーオンリセット回路の出力が第2に出力レベルの場合に第3の端子と前記第2の端子との間が非通電状態となるスイッチング素子とを備え、前記スイッチング素子の第3の端子は、前記第1の容量素子と前記制御端子との中間点に接続されていることを特徴とする請求項2から5のいずれかに記載の半導体集積回路。

【請求項7】 前記スイッチング素子は、MOSトランジスタであることを特徴とする請求項6に記載の半導体集積回路。

【請求項8】 前記パワーオンリセット回路は、一端がグランドラインに接続された容量素子と、電源投入後、前記容量素子が充電されるまでは出力が第1の出力レベルとなり、前記容量素子が充電された後は出力が第2の出力レベルとなるインバータ素子とを含むことを特徴とする請求項6又は7に記載の半導体集積回路。

【請求項9】 前記パワーオンリセット回路は、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、他端が前記整流回路の直流電力出力端子に接続されている抵抗素子と、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、前記整流回路から直流電力が出力されない状態となった場合に導通状態となることにより、前記容量素子に充電された電荷を放電させるスイッチング素子とを含むことを特徴とする請求項8に記載の半導体集積回路。

【請求項10】 全ての容量素子の少なくとも一つはMOSトランジスタにより構成されることを特徴とする請求項2から9のいずれかに記載の半導体集積回路。

【請求項11】 前記半導体集積回路はさらに、前記レギュレータ回路からの出力を微分する微分回路と、当該微分回路からの出力に基づき、前記直流電力の電圧値の変化を検出する検出手段とを備えることを特徴とする請求項1から10のいずれかに記載の半導体集積回路。

【請求項12】 前記整流回路は、電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路であることを特徴とする請求項1から11のいずれかに記載の半導体集積回路。

【請求項13】 前記半導体集積回路において、前記入力端子に、前記二電圧整流回路から出力される二系統の直流電力のうち電圧値が高い側が入力されることを特徴とする請求項12に記載の半導体集積回路。

【請求項14】 不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることを特徴とする半導体集積回路。

【請求項15】 前記交流電力は、デジタルデータによりASK変調された搬送波をアンテナコイルにより受信した場合に、当該アンテナコイルの両端に発生する交流電力であり、前記不揮発性メモリには、前記デジタルデータの少なくとも一部が書き込まれることを特徴とする請求項14に記載の半導体集積回路。

【請求項16】 前記二電圧整流回路は、第1の端子が、電圧値が高い側の直流電力を出力する第1の出力端子に接続され、第2の端子が、電圧値が低い側の直流電力を出力する第2の出力端子に接続された第1の容量素子と、第1の端子が、前記第1の容量素子の前記第2の端子と前記第2の出力端子との間に接続され、第2の端子が、グランドラインに接続された第3の出力端子に接続された第2の容量素子と、第1の端子が、前記交流電力の第1の入力端子に接続され、第2の端子が、前記第1の容量素子の前記第1の端子と前記第1の出力端子との間に接続され、第1の端子から第2の端子の方向にのみ通電させる第1の整流素子と、第1の端子が、前記第2の容量素子の前記第2の端子と前記第3の出力端子との間に接続され、第2の端子が、前記第1の入力端子と前記第1の整流素子との間に接続され、第1の端子から第2の端子の方向にのみ通電させる第2の整流素子とを含み、交流電力の第2の入力端子は、前記第1の容量素子の前記第2の端子と、前記第2の容量素子の前記第1の端子との間に接続されていることを特徴とする請求項14又は15のいずれかに記載の半導体集積回路。

【請求項17】 前記第1の整流素子及び前記第2の整流素子は、整流ダイオード、MOSトランジスタのいずれかからそれぞれ選択されたものであることを特徴とする請求項16に記載の半導体集積回路。

【請求項18】 前記第1の整流素子及び前記第2の整流素子は、いずれもPチャネルMOSトランジスタであることを特徴とする請求項16又は17のいずれかに記載の半導体集積回路。

【請求項19】 デジタルデータによりASK変調された搬送波を受信し、当該搬送波から電力を生成するとともに、前記デジタルデータを復調する非接触型情報媒体において、請求項1から13のいずれかに記載の半導体集積回路を搭載し、前記レギュレータ回路の出力から前記デジタルデータを復調することを特徴とする非接触型情報媒体。

【請求項20】 デジタルデータによりASK変調された搬送波を受信し、当該搬送波から回路の駆動電力を生成する非接触型情報媒体において、請求項14から18のいずれかに記載の半導体集積回路を搭載し、前記二電圧整流回路から出力される二系統の直流電力を、それぞれ所定の回路の駆動電力として用いることを特徴とする非接触型情報媒体。

【請求項21】 デジタルデータによりASK変調された搬送波をアンテナコイルで受信する受信ステップと、前記搬送波を受信することで、前記アンテナコイルの両端に発生する交流電力を整流する整流ステップとを含み、当該整流ステップにおいて整流された直流電力の電圧値が、基準電圧発生回路から制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を有する半導体集積回路を、当該レギュレータ回路から出力される直流電力により駆動する半導体集積回路の駆動方法において、前記ASK変調された搬送波の振幅の変化と連動して、前記制御端子に入力される基準電圧を変化させるとともに、前記レギュレータ回路の出力を微分することにより得られるパルス信号をラッチすることにより前記デジタルデータの値を判別する判別ステップを含むことを特徴とする半導体集積回路の駆動方法。

【請求項1】 交流電力を直流電力に整流する整流回路と、整流された直流電力が入力される入力端子と、出力端子と、基準電圧が入力される制御端子とを備え、前記出力端子から出力される電圧値が、前記制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を含む半導体集積回路において、前記直流電力の電圧値の変化に連動して、前記制御端子に入力される基準電圧を変更する基準電圧変更回路を備えることを特徴とする半導体集積回路。

【請求項2】 前記基準電圧変更回路はCR時定数回路であり、第1の容量素子の一端が前記入力端子に接続され、抵抗素子の一端が基準電圧発生回路の出力端子に接続され、第1の容量素子と抵抗素子との中間点が前記制御端子に接続されることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】 前記基準電圧変更回路はさらに、一端が前記制御端子に接続され、他の一端がグランドラインに接続される第2の容量素子を含むことを特徴とする請求項2に記載の半導体集積回路。

【請求項4】 前記基準電圧変更回路は、一端が前記入力端子に接続された第1の容量素子と、一端が基準電圧発生回路の出力端子に接続され、他端が前記第1の容量素子の他端と接続された第2の容量素子とを含み、前記制御端子が、前記第1の容量素子と前記第2の容量素子との中間点に接続されて構成されることを特徴とする請求項1に記載の半導体集積回路。

【請求項5】 前記第1の容量素子は、ソース、ドレイン及び基板が前記入力端子に接続され、ゲートは、前記基準電圧発生回路の出力端子に接続された素子の当該出力端子とは逆側の一端と、前記制御端子との中間点に接続されるMOSトランジスタにより構成されることを特徴とする請求項2から4のいずれかに記載の半導体集積回路。

【請求項6】 前記基準電圧変更回路はさらに、電源投入後、所定時間の経過後に、出力が第1の出力レベルから第2の出力レベルに変化するパワーオンリセット回路と、少なくとも三つの端子を有し、第1の端子が前記パワーオンリセット回路の出力に、第2の端子がグランドラインに接続されるとともに、前記パワーオンリセット回路の出力が第1の出力レベルの場合に第3の端子と前記第2の端子との間が導通状態となり、前記パワーオンリセット回路の出力が第2に出力レベルの場合に第3の端子と前記第2の端子との間が非通電状態となるスイッチング素子とを備え、前記スイッチング素子の第3の端子は、前記第1の容量素子と前記制御端子との中間点に接続されていることを特徴とする請求項2から5のいずれかに記載の半導体集積回路。

【請求項7】 前記スイッチング素子は、MOSトランジスタであることを特徴とする請求項6に記載の半導体集積回路。

【請求項8】 前記パワーオンリセット回路は、一端がグランドラインに接続された容量素子と、電源投入後、前記容量素子が充電されるまでは出力が第1の出力レベルとなり、前記容量素子が充電された後は出力が第2の出力レベルとなるインバータ素子とを含むことを特徴とする請求項6又は7に記載の半導体集積回路。

【請求項9】 前記パワーオンリセット回路は、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、他端が前記整流回路の直流電力出力端子に接続されている抵抗素子と、一端が前記容量素子と前記インバータ素子の入力端子との中間点に接続され、前記整流回路から直流電力が出力されない状態となった場合に導通状態となることにより、前記容量素子に充電された電荷を放電させるスイッチング素子とを含むことを特徴とする請求項8に記載の半導体集積回路。

【請求項10】 全ての容量素子の少なくとも一つはMOSトランジスタにより構成されることを特徴とする請求項2から9のいずれかに記載の半導体集積回路。

【請求項11】 前記半導体集積回路はさらに、前記レギュレータ回路からの出力を微分する微分回路と、当該微分回路からの出力に基づき、前記直流電力の電圧値の変化を検出する検出手段とを備えることを特徴とする請求項1から10のいずれかに記載の半導体集積回路。

【請求項12】 前記整流回路は、電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路であることを特徴とする請求項1から11のいずれかに記載の半導体集積回路。

【請求項13】 前記半導体集積回路において、前記入力端子に、前記二電圧整流回路から出力される二系統の直流電力のうち電圧値が高い側が入力されることを特徴とする請求項12に記載の半導体集積回路。

【請求項14】 不揮発性メモリと、当該不揮発性メモリに対するデジタルデータの書き込みを行うデジタル回路とを含み、整流された直流電力により駆動される半導体集積回路において、交流電力を整流して電圧値の異なる二系統の直流電力を並行して出力する二電圧整流回路を含み、当該二電圧整流回路から出力される電圧値が高い側の直流電力を前記不揮発性メモリとデジタル回路のうちの一方の駆動に用い、電圧値が低い側の直流電力を他方の駆動に用いることを特徴とする半導体集積回路。

【請求項15】 前記交流電力は、デジタルデータによりASK変調された搬送波をアンテナコイルにより受信した場合に、当該アンテナコイルの両端に発生する交流電力であり、前記不揮発性メモリには、前記デジタルデータの少なくとも一部が書き込まれることを特徴とする請求項14に記載の半導体集積回路。

【請求項16】 前記二電圧整流回路は、第1の端子が、電圧値が高い側の直流電力を出力する第1の出力端子に接続され、第2の端子が、電圧値が低い側の直流電力を出力する第2の出力端子に接続された第1の容量素子と、第1の端子が、前記第1の容量素子の前記第2の端子と前記第2の出力端子との間に接続され、第2の端子が、グランドラインに接続された第3の出力端子に接続された第2の容量素子と、第1の端子が、前記交流電力の第1の入力端子に接続され、第2の端子が、前記第1の容量素子の前記第1の端子と前記第1の出力端子との間に接続され、第1の端子から第2の端子の方向にのみ通電させる第1の整流素子と、第1の端子が、前記第2の容量素子の前記第2の端子と前記第3の出力端子との間に接続され、第2の端子が、前記第1の入力端子と前記第1の整流素子との間に接続され、第1の端子から第2の端子の方向にのみ通電させる第2の整流素子とを含み、交流電力の第2の入力端子は、前記第1の容量素子の前記第2の端子と、前記第2の容量素子の前記第1の端子との間に接続されていることを特徴とする請求項14又は15のいずれかに記載の半導体集積回路。

【請求項17】 前記第1の整流素子及び前記第2の整流素子は、整流ダイオード、MOSトランジスタのいずれかからそれぞれ選択されたものであることを特徴とする請求項16に記載の半導体集積回路。

【請求項18】 前記第1の整流素子及び前記第2の整流素子は、いずれもPチャネルMOSトランジスタであることを特徴とする請求項16又は17のいずれかに記載の半導体集積回路。

【請求項19】 デジタルデータによりASK変調された搬送波を受信し、当該搬送波から電力を生成するとともに、前記デジタルデータを復調する非接触型情報媒体において、請求項1から13のいずれかに記載の半導体集積回路を搭載し、前記レギュレータ回路の出力から前記デジタルデータを復調することを特徴とする非接触型情報媒体。

【請求項20】 デジタルデータによりASK変調された搬送波を受信し、当該搬送波から回路の駆動電力を生成する非接触型情報媒体において、請求項14から18のいずれかに記載の半導体集積回路を搭載し、前記二電圧整流回路から出力される二系統の直流電力を、それぞれ所定の回路の駆動電力として用いることを特徴とする非接触型情報媒体。

【請求項21】 デジタルデータによりASK変調された搬送波をアンテナコイルで受信する受信ステップと、前記搬送波を受信することで、前記アンテナコイルの両端に発生する交流電力を整流する整流ステップとを含み、当該整流ステップにおいて整流された直流電力の電圧値が、基準電圧発生回路から制御端子に入力される基準電圧に基づいて決定される電圧値を超えないように出力するレギュレータ回路を有する半導体集積回路を、当該レギュレータ回路から出力される直流電力により駆動する半導体集積回路の駆動方法において、前記ASK変調された搬送波の振幅の変化と連動して、前記制御端子に入力される基準電圧を変化させるとともに、前記レギュレータ回路の出力を微分することにより得られるパルス信号をラッチすることにより前記デジタルデータの値を判別する判別ステップを含むことを特徴とする半導体集積回路の駆動方法。

【図1】

【図2】

【図4】

【図5】

【図14】

【図3】

【図6】

【図7】

【図15】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図2】

【図4】

【図5】

【図14】

【図3】

【図6】

【図7】

【図15】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【公開番号】特開2001−125653(P2001−125653A)

【公開日】平成13年5月11日(2001.5.11)

【国際特許分類】

【出願番号】特願2000−153785(P2000−153785)

【出願日】平成12年5月24日(2000.5.24)

【出願人】(000005843)松下電子工業株式会社 (43)

【Fターム(参考)】

【公開日】平成13年5月11日(2001.5.11)

【国際特許分類】

【出願日】平成12年5月24日(2000.5.24)

【出願人】(000005843)松下電子工業株式会社 (43)

【Fターム(参考)】

[ Back to top ]