半導体集積回路、閾値設定方法、及び通信装置

【課題】複数の比較器に対して両端の閾値を適切な値に設定すると共にその間の閾値を等間隔に設定可能である半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、閾値設定動作により、第1及び第Nの比較器の閾値は、第1及び第Nの比較器による入力電圧と閾値との比較結果に応じて、それぞれ入力電圧の下限値近傍及び上限値近傍に設定され、閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定される。

【解決手段】半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、閾値設定動作により、第1及び第Nの比較器の閾値は、第1及び第Nの比較器による入力電圧と閾値との比較結果に応じて、それぞれ入力電圧の下限値近傍及び上限値近傍に設定され、閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定される。

【発明の詳細な説明】

【技術分野】

【0001】

本願開示は、一般に半導体集積回路に関し、詳しくは閾値設定可能な比較器を含む半導体集積回路、閾値設定方法、及び通信装置に関する。

【背景技術】

【0002】

全並列型あるいは直並列型AD(analog-to-digital)変換器においては、それぞれ異なる閾値を設定した複数の比較器に入力アナログ電圧を印加し、各比較器において入力アナログ電圧と閾値との比較を行なう。複数の比較器の出力はサーモメータコードとなり、この出力をエンコーダによりエンコードすることにより、電圧値を表現したバイナリコードに変換する。一般に、複数の比較器のそれぞれの閾値に相当する比較基準電圧を抵抗ラダーにより発生させ、各比較器に印加していた(例えば非特許文献1)。

【0003】

アナログ信号と比較基準電圧との電位差を判定する比較器には、素子バラツキに起因するオフセットバラツキが存在する。AD変換器の高速化のためには、比較器のトランジスタに短チャネル長素子を使った方が有利であるが、短チャネル長素子を用いると素子バラツキが大きくなり、結果としてオフセットバラツキが大きくなってしまう。オフセットバラツキをキャンセルするための一手法として、AD変換動作を実行する前に、前処理としてオフセットキャンセルを行う手法が報告されている(例えば非特許文献2)。しかしながらこの手法では、閾値を調整するための期間は、AD変換動作を実行できない。そこで、AD変換に必要な所定個数の比較器に加え、冗長な比較器を設け、所定個数の比較器を用いてAD変換動作を実行する一方で、冗長分の比較器の閾値をバックグラウンドにて調整する技術が報告されている(例えば非特許文献3)。閾値を調整後の比較器をAD変換用に切り換えて使用し、AD変換に使用していた比較器を冗長分に切り換えて閾値調整に回すことで、常時閾値調整しながらAD変換動作を実行することができる。また、抵抗ラダーを設けることなく、閾値をデジタル的に制御する機能を比較器に備えることにより、閾値を与える手法も報告されている(例えば非特許文献4)。電流が流れる抵抗ラダーを取り除くことで、消費電力を削減することができる。

【0004】

閾値をデジタル的に制御する機能を比較器に設けた場合、適切なデジタルコードを各比較器に設定することで、各比較器に適切な閾値を設定する。しかしながら、デジタルコードと実際の閾値との関係は、理想的な線形関係になく、デジタルコードを等間隔に設定しても閾値は等間隔とならない、という問題がある。即ち、ある所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。例えば、上記非特許文献4に開示されるAD変換では、オフチップでの手動作業により閾値の制御を行なっている。

【0005】

また複数の比較器の閾値のうちで上端と下端との閾値についても、入力アナログ電圧の電圧範囲の上限と下限とに対応した閾値に設定することが好ましい。しかしながら、デジタルコードと実際の閾値との関係には誤差があるために、デジタルコードを所定値に設定しても閾値を所望値に設定することにはならない、という問題がある。従って、複数の比較器の閾値のうちで上端と下端との閾値を適切な値に設定することが難しい、という問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−18008号公報

【特許文献2】特開2002−33663号公報

【特許文献3】特開2008−160593号公報

【非特許文献】

【0007】

【非特許文献1】Yasuhiko Fujita,Eiji Masuda, Shigemi Sakamoto, Tatsuo Sakaue, Yasushi Sato; A bulk CMOS 20MS/s7b flash ADC, IEEE International Solid-State Circuits Conference, vol. XXVII,pp. 56 - 57, February 1984

【非特許文献2】Yuko Tamba, Kazuo Yamakido; A CMOS 6b 500MSample/s ADC for a harddisk drive read channel, IEEE International Solid-State Circuits Conference,vol. XLII, pp. 324 - 325, February 1999

【非特許文献3】Sanroku Tsukamoto, Ian Dedic, Toshiaki Endo, Kazu-yoshi Kikuta,Kunihiko Goto, Osamu Kobayashi; A CMOS 6-b, 200 Msample/s, 3 V-supply A/Dconverter for a PRML read channel LSI, IEEE Journal of Solid-State Circuits,vol. 31, pp. 1831 - 1836, November 1996

【非特許文献4】Geert Van der Plas, Stefaan Decoutere, Stephane Donnay; A 0.16pJ/conversion-step 2.5mW 1.25GS/s 4b ADC in a90nm digital CMOS process, IEEE International Solid-State Circuits Conference,vol. XLIX, pp. 566 - 567, February 2006

【発明の概要】

【発明が解決しようとする課題】

【0008】

以上を鑑みると、複数の比較器に対して両端の閾値を適切な値に設定すると共にその間の閾値を等間隔に設定可能である半導体集積回路、閾値設定方法、及び通信装置が望まれる。

【課題を解決するための手段】

【0009】

半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、前記第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、前記第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、前記閾値設定動作により、前記第1及び第Nの比較器の閾値は、前記第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、それぞれ前記入力電圧の下限値近傍及び上限値近傍に設定され、前記閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定されることを特徴とする。

【0010】

閾値設定方法は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器のうちで、第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、前記第1及び第Nの比較器の閾値をそれぞれ前記入力電圧の下限値近傍及び上限値近傍に設定する段階と、前記第1乃至第Nの比較器のうちで、1<M<Nである第Mの比較器の閾値を前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定する動作を、1<M<Nである全ての第Mの比較器に対して実行する第1の段階と、前記第1の段階を複数回繰り返す第2の段階とを含むことを特徴とする。

【0011】

通信処理部とAD変換器とを含む通信装置において、前記AD変換器は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、前記第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、前記第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、前記閾値設定動作により、前記第1及び第Nの比較器の閾値は、前記第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、それぞれ前記入力電圧の下限値近傍及び上限値近傍に設定され、前記閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定されることを特徴とする。

【発明の効果】

【0012】

本願開示の少なくとも1つの実施例によれば、複数の比較器に対して両端の閾値を適切な値に設定すると共に、その間の閾値を等間隔に設定することができる。

【図面の簡単な説明】

【0013】

【図1】比較器の閾値を等間隔に設定する方法の一例を模式的に示す図である。

【図2】比較器の閾値が順番に並んでいない初期状態を模式的に示す図である。

【図3】複数の比較器の端の部分における閾値間距離の変化について説明するための図である。

【図4】比較器の両端の閾値を固定状態とした場合を示す図である。

【図5】冗長な比較器を設けた場合の閾値設定方法を模式的に示す図である。

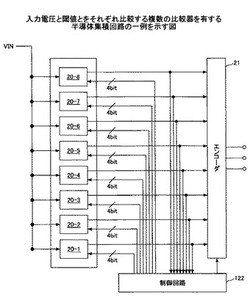

【図6】入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。

【図7】エンコーダの一例を示す図である。

【図8】図7の比較器及びエンコーダの動作のタイミングを示すタイミングチャートである。

【図9】制御回路による冗長比較器の閾値更新を説明するための図である。

【図10】比較器の閾値の更新動作のタイミングの一例を示すタイミングチャートである。

【図11】AD変換器の複数の比較器の更新動作の流れを示すフローチャートである。

【図12】比較器の一例を示す図である。

【図13】制御信号を生成する回路の一例を示す図である。

【図14】信号遷移速度を制御信号により制御可能なインバータの一例を示す図である。

【図15】信号遷移速度を制御信号により制御可能なインバータの別の一例を示す図である。

【図16】図12の比較器の動作の一例を示す図である。

【図17】比較器の別の一例を示す図である。

【図18】図17の比較器の動作の一例を示す図である。

【図19】通信装置の一例を示す図である。

【図20】制御回路による冗長比較器の閾値更新を説明するための図である。

【図21】閾値設定方法の計算機シミュレーションの結果を示す図である。

【図22】閾値設定方法の別の計算機シミュレーションの結果を示す図である。

【図23】入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。

【図24】制御回路の構成の一例を示す図である。

【図25】初期設定処理としての閾値設定動作及びその後の設定処理としての閾値更新動作の一例を示す図である。

【図26】下限値検出部の構成の一例を示す図である。

【図27】比較器C1の閾値を設定する閾値設定動作の一例を示すフローチャートである。

【図28】図27のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。

【図29】図27のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。

【図30】上限値検出部の構成の一例を示す図である。

【図31】比較器C6の閾値を設定する閾値設定動作の一例を示すフローチャートである。

【図32】図31のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。

【図33】図31のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。

【図34】両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。

【図35】両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。

【図36A】比較器C1の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図36B】比較器C1の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図37】図36A及び図36Bに示す閾値設定動作の一例を模式的に示す図である。

【図38】図36A及び図36Bに示す閾値設定動作の別の一例を模式的に示す図である。

【図39A】比較器C6の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図39B】比較器C6の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図40】図39A及び図39Bに示す閾値設定動作の一例を模式的に示す図である。

【図41】図39A及び図39Bに示す閾値設定動作の別の一例を模式的に示す図である。

【図42】比較器C1の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。

【図43】図42に示す閾値設定動作の一例を模式的に示す図である。

【図44】図42に示す閾値設定動作の別の一例を模式的に示す図である。

【図45】比較器C6の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。

【図46】閾値設定動作及び閾値更新動作の実行の仕方の別の一例を示す図である。

【発明を実施するための形態】

【0014】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0015】

図1は、比較器の閾値を等間隔に設定する方法の一例を模式的に示す図である。図1において、5つの○印が5つの比較器11乃至15を表わし、○印の水平方向の位置が各比較器に設定されている閾値の大きさを表わす。図面上から下に向かい時間が経過していき、閾値が変化していく様子が模式的に示されている。この例では、閾値0〜4の間を4等分して、5つの比較器11乃至15の閾値をそれぞれ0,1,2,3,4に設定する場合について示してある。

【0016】

閾値の範囲及び閾値間の間隔は、説明を簡単にするための一例に過ぎず、これに限定されるものではない。閾値の下端は0以外の数値であってよく、上端は4以外の数値であってよい。また4等分以外の数に等分してもよい。なお所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。従って、下端の閾値及び上端の閾値をそれぞれ0及び4に設定できるとは限らない。以下において、取り敢えずは、下端の閾値及び上端の閾値を適切な値(図1の例であれば閾値0及び4)に設定できると仮定して、その間を等分(図1の例であれば4等分)する場合について説明を進める。このようにしてまずは下端の閾値と上端の閾値との間を等分する閾値を設定する方法について説明し、その後に、下端の閾値及び上端の閾値を適切な値に設定する方法について説明する。

【0017】

図1に示す閾値設定方法では、比較器11乃至15の閾値を所定の条件に従い増減を繰り返していくことにより、閾値を徐々に位置を移動させ、閾値間の間隔が略等間隔となるように調整する。まず、第1乃至第5の比較器11乃至15のうち、1<M<5である第Mの比較器(即ち両端以外の比較器)に着目し、この第Mの比較器の閾値をTHMとする。また第M+1の比較器の閾値をTHM+1とする。このとき、第M+1の比較器と第Mの比較器との間の閾値差はTHM+1−THMである。図1において、例えばM=3として、第4の比較器14と第3の比較器13との間の閾値差TH4−TH3は、図示する距離b3である。まずこの状態において、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する。例えば第3の比較器13の場合であれば、b3をr倍(0<r<1)した距離だけ、第3の比較器13の閾値を増加させる(右にずらす)ことで、閾値を更新する。同様の処理を、各比較器11乃至14に対して実行する。比較器15の閾値については、上端の閾値4に設定することにより、上端の閾値4に拘束する。この動作により、最初の状態において各比較器11乃至15間の閾値差(閾値間距離)がb1乃至b4であったのが、閾値差b1’乃至b4’に変化する。以上の動作を、第1の更新動作とする。

【0018】

この変化後の状態において、第M−1の比較器と第Mの比較器とに着目する。これらの比較器の閾値差はTHM−1−THMである。図1において、例えばM=3として、第2の比較器12と第3の比較器13との間の閾値差TH2−TH3の絶対値は、図示する距離b2’である。この状態において、負の値である(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する。第3の比較器13の場合であれば、b2’をr倍(0<r<1)した距離だけ、第3の比較器13の閾値を減少させる(左にずらす)ことで、閾値を更新する。同様の処理を、各比較器12乃至15に対して実行する。比較器11の閾値については、下端の閾値0に設定することにより、下端の閾値0に拘束する。以上の動作を、第2の更新動作とする。

【0019】

上記の第1の更新動作と第2の更新動作とを、交互に複数回実行する。この際、第1の比較器11の閾値は、1回おきに0に設定されるので、常に0近傍に拘束されることになる。また第5の比較器15の閾値は、1回おきに4に設定されるので、常に4近傍に拘束されることになる。なお最初に実行するのは第1の更新動作ではなく第2の更新動作であってもよい。また、図1の例では、初期状態において、比較器11乃至15の閾値が比較器の番号順に従って順番に並んでいるが、これに限定されることはない。即ち比較器11乃至15の閾値が順番に並んでおらず、初期状態において、例えば第3の比較器13の閾値が第4の比較器14の閾値よりも大きくてもよい。

【0020】

図2は、比較器11乃至15の閾値が順番に並んでいない初期状態を模式的に示す図である。図2では、図1の表現方式と異なり、横方向に比較器の番号をとり、縦方向に閾値の値をとっている。図2に示す例では、第3の比較器13の閾値が第4の比較器14の閾値よりも大きくなっている。この場合、第3の比較器13の閾値を基準点とした第4の比較器14の閾値との閾値差b3は、負の値となる。従って、r・b3を加えることにより、第3の比較器13の閾値は減少する方向に更新される。この時、他の比較器については、閾値が増加する方向に更新される。

【0021】

図1に戻り、第1の更新動作において、第1の比較器11の閾値はr・b1だけ増加し、第2の比較器12の閾値はr・b2だけ増加する。閾値間距離b1に着目すると、r・b1だけ狭まり、r・b2だけ広がることになる。即ち、b1はr(b2−b1)だけ変化する。同様にして、b2はr(b3−b2)だけ変化し、b3はr(b4−b3)だけ変化する。b4については、初期状態の第5の比較器15の閾値を4−r・INとすれば、r(IN−b3)だけ変化する。第2の更新動作において、第1の比較器11の閾値はr・b1となっているので、b1はr(b1−b1’)だけ変化する。またb2はr(b1’−b2’)だけ変化し、b3はr(b2’−b3’)だけ変化し、b4はr(b3’−b4’)だけ変化する。

【0022】

例えば、b2に着目した場合、第1の更新動作によりb2はr(b3−b2)だけ変化するので、b2>b3であれば、b2は狭まる。またb2>b1であり、この大小関係が第1の更新動作後も続くのであれば、第2の更新動作によりb2’はr(b1’−b2’)だけ変化するので、b2’は狭まる。従って、着目閾値間距離は、その両側の閾値間距離よりも長い状態である間は、更新動作により狭まっていくことになる。同様にして、着目閾値間距離は、その両側の閾値間距離よりも短い状態である間は、更新動作により広がっていくことになる。これらのことをまとめれば、着目閾値間距離は、その両側の閾値間距離よりも長い又は短い状態である間は、更新動作により両側の閾値間距離に近づくように更新される。

【0023】

またb1<b2<b3の大小関係が続く限りは、第1の更新動作によりb2はr(b3−b2)だけ変化し広くなり、第2の更新動作によりb2’はr(b1’−b2’)だけ変化して狭くなる。仮にb1とb3とが変化しないと仮定すると、安定状態ではr(b3−b2)とr(b1−b2)とが等しくなるので、b2はb3及びb1との平均値となる。実際にはb1とb3とが変化するが、この場合も、b2はb3及びb1との平均値に向かい近づくように更新されていく。

【0024】

上述のように着目閾値間距離は、その両側の閾値間距離よりも長い又は短い状態である間は、更新動作により両側の閾値間距離に近づくように更新される。そして更に、着目閾値間距離は、両側の閾値間距離の間にある状態では、更新動作により両側の閾値間距離の平均に近づくように更新される。これらの特徴により、閾値間距離は、端から端まで、直線上に増加する、直線上に減少する、又は一定値であるの何れかの形に近づく方向に変化していくことが分かる。

【0025】

図3は、複数の比較器の端の部分における閾値間距離の変化について説明するための図である。図3は、図1に示す模式図の左端を着目して示しており、左端の閾値間距離b1がb1’更にはb1’’へと更新されていく様子を示している。ここで、

b1’=b1+r(b2−b1)

である。従って、b1’’は、

b1’’=b1’+r(b1−b1’)

=(1−r)b1’+rb1

=(1−r){b1+r(b2−b1)}+rb1

=b1+(r−r2)(b2−b1)

となる。ここでrは1より小さいので、(r−r2)は正である。従って、b2>b1であるならば、第1の更新動作及び第2の更新動作によりb1は広がる。逆に、b2<b1であるならば、第1の更新動作及び第2の更新動作によりb1は狭まる。従って、更新動作を繰り返していくことにより、b1がb2に等しくなる方向にb1の長さが変化していくことになる。

【0026】

b1とb2とが略等しい状態になった後において、第2の更新動作では、b2の長さは変化せずに略一定である。第1の更新動作では、b2はr(b3−b2)だけ変化するので、b3>b2であるならばb2は広がる。逆に、b3<b2であるならばb2は狭まる。従って、更新動作を繰り返していくことにより、b2がb3に等しくなる方向に変化していくことになる。

【0027】

このようにして、閾値を拘束されている左端から各閾値間距離が等しくなろうとする方向へ閾値間距離が変化していく。右端でも同様であり、閾値を拘束されている右端から各閾値間距離が等しくなる方向へ閾値間距離が変化していく。また前述のように、閾値間距離は、端から端まで、直線上に増加する、直線上に減少する、又は一定値であるの何れかの形に近づく方向に変化していく。従って、これらの変化の傾向が組み合わさり、最終的には、複数の閾値間距離が端から端まで一定の値である分布に近づいていく。即ち、比較器11乃至15の閾値が、下端閾値0から上端閾値4までの間に等間隔に並ぶような配置に近づいていく。

【0028】

なお第1の更新動作において、(THM+1−THM)のr倍をTHMに加えるように閾値更新をし、第2の更新動作において、(THM−1−THM)のr倍をTHMに加えるように閾値更新をする。この際、所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。このことから、隣接する比較器の閾値(THM+1やTHM+1)の値は正確には分からないし、着目比較器の閾値(THM)も正確には分からない。そこで例えば実際に着目比較器で入力電圧と閾値との比較結果を求め、更に隣接する比較器により当該入力電圧と閾値との比較結果を求め、これらの比較結果を比較してよい。入力電圧を変えながら複数回比較して、着目比較器のコードを徐々に変化させていくことで、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断することができる。このときの着目比較器のコード入力と、着目比較器の元のコード入力との差分を求め、この差分をr倍した値を元のコード入力に加えるようにして、閾値を更新してよい。

【0029】

なお上記の閾値設定方法は、厳密な数式解を求めるような性質のものではないので、若干のずれがあっても繰り返し動作により所望の閾値配置に収束する。従って、例えば2つのコードの差分をr倍しても閾値差を正確にr倍したことにはならないが、一般に0<r<1である条件であればrの値に関わらず収束するので、特に問題はない。同様に、図1の閾値調整において、時間の経過とともにrが変化したとしても、所望の閾値配置に問題なく収束する。即ち、rは必ずしも最初から最後まで同一値でなくともよい。但し、図1に示す模式図において、ある一段の更新動作(例えばb1乃至b4をb1’乃至b4’に更新する初段の更新動作)及びその直後の段の更新動作においては、rを各比較器11乃至15に対して同一値にしておくことが好ましい。また例えば、ある比較器に対して閾値更新を繰り返す途中で、一時的に閾値更新を停止してしまっても、その後再開すれば最終的には問題なく所望の閾値に収束する。

【0030】

0<r<1である条件であればrの値に関わらず収束するが、一般的には、例えばr=0.1程度の値が好ましい。例えばrが0.9等の大きい値では、各比較器11乃至15の閾値が0.9程度の振幅で増減し続けることになる。所望の閾値の近辺で各比較器の閾値が振動するのであるが、その振動幅が大きいので、あるタイミングで閾値更新動作を終了させたときに、0.9の誤差が存在することになる。それに対してrが0.1等の小さい値の場合、各比較器11乃至15の閾値が0.1程度の振幅で増減し続けることになる。所望の閾値の近辺で各比較器の閾値が振動し、その振動幅が小さいので、あるタイミングで閾値更新動作を終了させたときに、各比較器の閾値は所望の閾値に近い値となっている。一般にAD変換動作では、0.5LSB以下の誤差(微分非直線性誤差)が求められるので、0<r<0.5が一般的には許容できる範囲である。但し上述のように、0<r<1であれば収束する(即ち安定的な定位置での振動となる)。なおrが例えば0.01のように小さすぎると、収束するまで(即ち安定的な定位置での振動となるまで)に時間がかかる、即ち膨大な回数の閾値更新動作であってもよい。従って、所望の精度と収束時間とを勘案して、適切なrの値を採用すればよい。

【0031】

図4は、比較器11乃至15の両端の閾値を固定状態とした場合を示す図である。この場合であっても、図1の場合と同様の設定方法により、比較器11乃至15の閾値を略等間隔に設定することができる。

【0032】

即ち、まず例えば、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する第1の更新動作を実行する。更に、(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する第2の更新動作を実行する。これら第1の更新動作と第2の更新動作とを交互に複数回実行することで、比較器11乃至15の閾値が、下端閾値0から上端閾値4までの間に等間隔に並ぶような配置に近づいていく。この場合、第1の比較器11の閾値を0に固定することで、0の近傍に拘束していることになる。また第5の比較器15の閾値を4に固定することで、4の近傍に拘束していることになる。

【0033】

なおこの場合、前述の場合と同様に、初期状態のb1及び第1の更新動作後のb1’に対して、第2の更新動作後のb1’’は、

b1’’=(1−r)b1’

=(1−r)(b1+r・b2)

=b1+r(b2−b1)

となる。従って前述の場合と同様に、更新動作を繰り返していくことにより、b1がb2に等しくなる方向にb1の長さが変化していくことになる。その他の動作については、図1の場合と同様である。

【0034】

図5は、冗長な比較器を設けた場合の閾値設定方法を模式的に示す図である。図5において、第6の比較器16が冗長な比較器として設けられている。図1に示す例では、AD変換動作には、5つの比較器11乃至15が設けられている。このような回路では、全ての比較器11乃至15についての閾値設定動作が終了して初めて、エンコーダにより比較器11乃至15の出力をエンコードする実際のAD変換動作を開始することができる。即ち、AD変換動作を実行しながら閾値の更新を行なうことができない。

【0035】

それに対して図5に示す回路では、AD変換動作を行う5個以上の比較器の一例として、比較器11乃至16の6つの比較器を設ける。初期状態では、第5の比較器15以外の残りの複数の比較器11,12,13,14,16により入力電圧とそれぞれの閾値とを比較した結果をエンコーダに供給してAD変換動作を実行する。そしてAD変換動作を実行しながら、エンコーダから切り離した状態である第5の比較器15に対して閾値の更新作業を実行する。第5の比較器15の閾値を更新すると、第5の比較器15をエンコーダに接続するとともに、残りの複数の比較器11乃至15のうちから選択した所望の比較器をエンコーダから切り離して閾値の更新を行なってよい。具体的には、第4の比較器14をエンコーダから切り離して、閾値更新の対象としてよい。この閾値更新の間は、比較器11,12,13,15,16の5つの比較器により、AD変換動作を実行することになる。

【0036】

図5に示す例でも、図1と同様に、(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する更新動作を実行する。具体的には、まず第5の比較器15の閾値TH5に、(TH4−TH5)を1より小さい正の実数倍した値を加えることにより、第5の比較器15の閾値を更新する。この場合の掛算の係数である1より小さい正の実数は、図1の場合の掛算の係数をrとすれば、(1−r)となる。これは、図5に示されるように、第5の比較器15の閾値を更新すると、閾値更新後の第5の比較器15により、第4の比較器14を置き換えるからである。閾値3の近傍の比較動作を実行すべき比較器は、更新動作に関わらず図1の例では第4の比較器14である。それに対して、図5の例では、閾値3の近傍の比較動作を実行すべき比較器は初期状態で第4の比較器14であり、その後第5の比較器15に置き換わり、その後更に第4の比較器14に置き換わり、というように比較器14と15とに交互に置き換わる。図5において、点線で示す矢印が、各比較器の実際の閾値の変化を示す。実線で示す矢印は、所定の閾値近傍の比較動作を実行すべき比較器の置き換わりの推移を示す。

【0037】

第5の比較器15により置き換えられた第4の比較器14は、エンコーダから切り離され、閾値更新動作に供される。第4の比較器14の閾値更新が終了すると、閾値更新後の第4の比較器14により、第3の比較器13を置き換える。第4の比較器14により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。第3の比較器13の閾値更新が終了すると、閾値更新後の第3の比較器13により、第2の比較器12を置き換える。第2の比較器12は、エンコーダから切り離され、閾値更新動作に供される。この際、第2の比較器12の閾値TH2に、(TH1−TH2)を1より小さい正の実数倍した値を加えることにより、第2の比較器12の閾値を更新する。即ち、第2の比較器12の閾値を(1−r)・b1だけ減少させる(左に移動させる)ことにより、第2の比較器12の閾値を更新する。これにより、比較器11乃至16に対する一段の更新動作が終了する。なお両端の比較器11及び16については、それぞれ両端の閾値0及び4に固定しておいてよい。即ち、両端の閾値0及び4に拘束しておくことになる。また図5において、各段の更新処理開始時における冗長な比較器(エンコーダから切り離されている比較器)が黒丸で示されている。

【0038】

次の更新動作においては、図1と同様に、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する更新動作を実行する。具体的には、まず第2の比較器12の閾値TH2に、(TH3−TH2)を1より小さい正の実数倍した値を加えることにより、第2の比較器12の閾値を更新する。即ち、第2の比較器12の閾値を(1−r)・b2だけ増加させる(右に移動させる)ことにより、第2の比較器12の閾値を更新する。第2の比較器12の閾値更新が終了すると、閾値更新後の第2の比較器12により、第3の比較器13を置き換える。第2の比較器12により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。以降同様にして、順次、比較器13乃至15の閾値を更新していく。

【0039】

図5の場合も図1の場合と同様に、例えば実際に着目比較器で入力電圧と閾値との比較結果を求め、更に隣接する比較器により当該入力電圧と閾値との比較結果を求め、これらの比較結果を比較してよい。入力電圧を変えながら複数回比較して、着目比較器のコードを徐々に変化させていくことで、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断することができる。このときの着目比較器のコード入力と、着目比較器の元のコード入力との差分を求め、この差分を(1−r)倍した値を元のコード入力に加えるようにして、閾値を更新してよい。

【0040】

図6は、入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。図6に示す半導体集積回路は全並列型或いは直並列型のAD変換器であり、複数の比較器20−1乃至20−8、エンコーダ21、及び制御回路22を含む。第1乃至第8の比較器20−1乃至20−8は、制御回路22からのデジタルコード入力により対応する閾値が設定される。なお図6には、説明の便宜上、シングルエンドであるAD変換器を示すが、差動信号のAD変換を行なう差動構成のAD変換器であってよい。

【0041】

比較器20−1乃至20−8は、それぞれ制御回路22から印加されたコードに対応する閾値が設定されている。比較器20−1乃至20−8は、入力アナログ電位VINを受け取り、入力アナログ電位VINとそれぞれの閾値とを比較して、その比較結果を出力する。各比較器は、入力アナログ電位VINが内部設定された閾値よりも大きければ出力を1とし、入力アナログ電位VINが内部設定された閾値以下であれば出力を0とする。適切な閾値が設定されている状態では、比較器20−1乃至20−8の出力は、“00001111”のように下位の比較器出力が“1”であり、途中の比較器以降の出力が“0”となるサーモメータ(温度計)コードとなる。なお比較器20−1乃至20−8のうちの1つは前述の冗長な比較器であり、制御回路22によりエンコーダ21から切り離され、閾値更新動作に供される。残りの7つの比較器の出力に基づいて、エンコーダ21が符号化を実行し、3ビットのバイナリコードDoutとして出力する。なお図6に示す例では、説明の便宜上、AD変換結果が3ビットの場合を示すが、AD変換器の出力ビット数は3ビットに限定されるものではなく、任意のビット数であってよい。

【0042】

図7は、エンコーダ21の一例を示す図である。図7に示すエンコーダ21は、スイッチ回路31、2入力のうち一方が負論理入力の複数のORゲート32、ワイアードOR回路33、スイッチ回路34、及びフリップフロップ回路35を含む。スイッチ回路31は、7つの同一の構造のスイッチを含む。各スイッチは、比較器20−1乃至20−8のうちの隣接する2つの比較器の出力を受け取り、何れか一方の出力を選択して次段のORゲート32に供給する。この際、下位側のスイッチが隣接する2つの比較器の下位側の比較器の出力を選択し、上位側のスイッチが隣接する2つの比較器の上位側の比較器の出力を選択することで、境界部分にある比較器をエンコーダ21内部から切り離すことができる。図7に示す例では、比較器20−1乃至20−8のうち第3の比較器20−3がエンコーダ21内部から切り離されている。スイッチ回路31の接続状態を制御するスイッチ制御信号φselは、図6の制御回路22から供給される。

【0043】

ORゲート32は、2入力のうち下位側の比較器からの入力が反転されて入力される。従って、サーモメータコードの1と0との境界位置におけるORゲート32の出力が0となり、それ以外のORゲート32の出力は1となる。図7の例では、下位側から4番目のORゲート32の出力が0となり、サーモメータコードの1と0との境界位置を検出している。ワイアードOR回路33は、8つのORゲート32の8本の出力線とフリップフロップ回路35の3本の入力線との交点のうち、図7に示される位置に設けられる。ワイアードOR回路33は、対応するORゲート32の出力が0であれば、フリップフロップ回路35の対応する入力線をグランド電位に接続する。フリップフロップ回路35の一本の入力線に着目したとき、この入力線には4つのワイアードOR回路33が接続されている。従って、これら4つのワイアードOR回路33が交点となる位置の4つのORゲート32の出力の何れか1つでも0になれば、この入力線の電位はLOWとなる。この回路により、8つのORゲート32の8つの出力のうちで値が0である出力の位置を3ビットに符号化し、符号化データD0’、D1’、D3’をフリップフロップ回路35に格納する。フリップフロップ回路35に格納した3ビットのデータは、エンコード結果D0、D1、D2として出力される。なおスイッチ回路34は、エンコードタイミングにおいて開放状態となる。スイッチ回路34は、リセットタイミングにおいて導通状態となり、フリップフロップ回路35の入力をグランドに接続してリセットする。フリップフロップ回路35及びスイッチ回路34の動作タイミングを制御するエンコード制御信号φencは、図6の制御回路22から供給される。

【0044】

図8は、図7の比較器20−1乃至20−8及びエンコーダ21の動作のタイミングを示すタイミングチャートである。リセットタイミングResetにおいて、図6の制御回路22から比較器20−1乃至20−8に供給される比較器制御信号φcmpがHIGHとなり、比較器20−1乃至20−8がリセットされる。またこのリセットタイミングResetにおいて、エンコード制御信号φencがHIGHとなり、スイッチ回路34が導通してフリップフロップ回路35の入力がグランドに接続される。即ち、フリップフロップ回路35の入力であるデータDn’(図7に示すD0’、D1’、D3’)が0にリセットされる。次に比較動作タイミングCompにおいて、比較器20−1乃至20−8に供給される比較器制御信号φcmpがLOWとなり、比較器20−1乃至20−8が比較動作を実行する。これにより、比較器20−1乃至20−8の出力Cmp_outが有効となる。またエンコード制御信号φencがLOWとなり、スイッチ回路34が非導通状態となることにより、フリップフロップ回路35の入力であるデータDn’が有効状態となる。このエンコード制御信号φencはフリップフロップ回路35にも供給されており、フリップフロップ回路35は、エンコード制御信号φencの立ち上がりエッジで入力データDn’を取り込む(ラッチする)。

【0045】

図9は、制御回路22による冗長比較器の閾値更新を説明するための図である。図9に示されるように、制御回路22は、2入力のうち下位側が負論理入力の複数のNORゲート40、2入力のうち上位側が負論理入力の複数のNORゲート41、及び制御ロジック回路43を含む。1つのNORゲート40と1つのNORゲート41とで一対をなし、一対のNORゲートの各々は、2つの比較器20−1乃至20−8のうちの隣接する2つの比較器の出力を受け取る。比較器20−1乃至20−8のうちの隣接する2つの比較器の組み合わせは、7つあるので、7対のNORゲートが設けられることになる。図9には図示の便宜上、第3及び第4の比較器20−3及び20−4に対する一対のNORゲートと、第4及び第5の比較器20−4及び20−5に対する一対のNORゲートとだけが示される。

【0046】

各比較器20−1乃至20−8の出力はエンコーダ21に供給されると共に、並行して制御回路22にも供給される。隣接する2つの比較器に対して設けられた一対のNORゲートは、入力電圧VINがこれら2つの比較器の2つの閾値よりも大きいか、小さいか、或いはその中間にあるか、に関する判定を行なう。以下において、図7で示した例と同様に、第3の比較器20-3が冗長比較器であり、この閾値の更新を実行する場合について説明する。

【0047】

第3の比較器20-3の閾値及び第4の比較器20-4の閾値の何れよりも入力電圧VINが低い場合、対応するNORゲート40の出力J+とNORゲート41の出力J−は、双方共に0となる。また第3の比較器20-3の閾値及び第4の比較器20-4の閾値の何れよりも入力電圧VINが高い場合も、対応するNORゲート40の出力J+とNORゲート41の出力J−は、双方共に0となる。このように出力J+と出力J−とが双方共に0の場合、制御ロジック回路43は何も実行しない。

【0048】

第3の比較器20-3の閾値及び第4の比較器20-4の閾値との間に入力電圧VINが有る場合には、第3の比較器20-3の閾値TH3と第4の比較器20-4の閾値TH4との大小関係に応じて、対応するNORゲートの出力J+及び出力J−が変化する。TH3<TH4である場合、第3の比較器20-3及び第4の比較器20-4の出力はそれぞれ1及び0となるので、NORゲート40の出力J+とNORゲート41の出力J−はそれぞれ1及び0となる。このとき、制御ロジック回路43は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1増加させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ増加させる。これにより、TH3がTH4に近づくことになる。逆に、TH3>TH4である場合、第3の比較器20-3及び第4の比較器20-4の出力はそれぞれ0及び1となるので、NORゲート40の出力J+とNORゲート41の出力J−はそれぞれ0及び1となる。このとき、制御ロジック回路43は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1減少させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ増加させる。これにより、TH3がTH4に近づくことになる。このようにして、AD変換器に入力される入力アナログ電圧VINと閾値との比較動作を逐次実行し、その比較結果に応じて、第3の比較器20-3の閾値を変化させていく。

【0049】

TH3とTH4とが等しくなると、入力アナログ電圧VINの値に関わらず、NORゲート40の出力J+とNORゲート41の出力J−とは、共に0になる。例えば、入力アナログ電圧VINと各閾値の比較動作を1000回行なったときに、1000回の比較動作の全てにおいて出力J+と出力J−とが、双方共に0になる。如何なるデジタルコードDcnt(3)を設定してもTH3とTH4とが完全に一致することが無い場合、即ち、各比較器の最小分解能に応じた差が常に存在する場合には、多数回の比較動作のうちで出力J+と出力J−とが異なる値となる場合が常に発生する。従って、例えば、1000回の比較動作において所定の割合以上(例えば99.5%以上)において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH4とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。同様に、所定の回数以上連続して出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH4とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。ここで更新動作の実行とは、TH3とTH4とが実質的に等しくなったときのデジタルコードと最初の状態のデジタルコードとの差を1より小さい正の実数倍した値を、最初の状態のデジタルコードに加えることである。これにより、(TH4−TH3)を1より小さい正の実数倍した値をTH3に加えることにより、第3の比較器の閾値を更新する更新動作を実行したことになる。

【0050】

TH3の更新動作が完了すると、第3の比較器20-3をエンコーダ21に接続し、第4の比較器20-4をエンコーダ21から切り離す。そして、第4の比較器20-4を冗長比較器として、第4の比較器20-4の閾値の更新を実行する。

【0051】

図10は、比較器の閾値の更新動作のタイミングの一例を示すタイミングチャートである。図10に示す比較器制御信号φcmpは、図8で説明した比較器制御信号と同一であり、比較器20−1乃至20−8のリセットタイミングと比較動作タイミングとを制御する。比較器制御信号φcmpがLOWのときに、各比較器により比較動作が実行され、各比較器の出力が有効(Valid)となる。図10に示す例では、最初にn番目の比較器を冗長比較器として、閾値更新処理の対象としている。n番目の比較器の出力としてCnが示されている。図9を参照して説明したように、制御回路22の制御ロジック回路43は、出力J+と出力J−とに応じて、n番目の比較器に供給するデジタルコードDcnt(n)を+1又は−1することにより、n番目の比較器の閾値Vthを変更する。図10に示す例では、比較器制御信号φcmpをクロックとしてクロックサイクルを考えた場合、出力J+と出力J−とに応じた閾値Vthの変更に、3クロックサイクルかかっている。この閾値Vthの変更を、比較動作の結果に応じて逐次実行する。なお前述のように、出力J+と出力J−とが双方共に0であれば、閾値Vthを変更しないで現状維持とする。複数回の比較動作において所定の割合以上において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、n番目の比較器の閾値とn+1番目の比較器の閾値とが実質的に等しくなったと判断(即ち収束したと判断)してよい。これにより、図10に示すように、n番目の比較器のデジタルコードDcnt(n)を固定し、次のn+1番目の比較器のデジタルコードDcnt(n+1)の調整を開始する。

【0052】

図11は、AD変換器の複数の比較器の更新動作の流れを示すフローチャートである。図11の処理は、例えば図6に示す制御回路22により実行される。図11においては、AD変換器に設けられた比較器の全個数をmとしている。図6の場合で言えば、m=8となる。まずステップS1において、各比較器にデジタルコードを初期設定する。ここで、第1の比較器及び第mの比較器(即ち両端の比較器)については、例えば、それぞれ最小のデジタルコード及び最大のデジタルコードを設定してよい。それ以外の第2乃至第M−1の比較器については、デジタルコードの初期値は如何なる値でもよい。例えば、最小のデジタルコードから最大のデジタルコードまでの範囲を等間隔に分割するように、各デジタルコードの初期値を設定してよい。

【0053】

ステップS2において、変数Mを2に初期化する。この変数Mは、第M番目の比較器を指し示す変数である。ステップS3において、変数Mが比較器の全個数mに等しいか否かを判定する。等しくない場合には、ステップS4に進む。ステップS4において、図9を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。第M番目の比較器の閾値更新処理を完了すると、ステップS5において、変数M=M+1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS3に戻り、以降の処理を、次の比較器に対して実行する。

【0054】

ステップS3において、変数Mが比較器の全個数mに等しいと判定された場合、ステップS6に進む。ステップS6において、変数M=m−1とする。これは、端の比較器(第Mの比較器)については、閾値を固定としておくことに相当する。次にステップS7において、変数Mが1に等しいか否かを判定する。等しくない場合には、ステップS8に進む。ステップS8において、図9を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。第M番目の比較器の閾値更新処理を完了すると、ステップS9において、変数M=M−1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS7に戻り、以降の処理を、次の比較器に対して実行する。

【0055】

ステップS7において、変数Mが1に等しいと判定された場合、ステップS2に進む。ステップS2において、変数M=2とする。これは、端の比較器(第1の比較器)については、閾値を固定としておくことに相当する。以降、ステップS2乃至S9の処理を同様にして繰り返す。

【0056】

このようにして、第1の比較器乃至第mの比較器から1つの比較器を冗長比較器として順次選択し、閾値更新処理の対象とする。この処理をAD変換器のAD変換動作を実行しながらバックグラウンドで実行することにより、AD変換動作と並行して比較器の閾値更新処理を実行することができる。

【0057】

図9乃至図11に説明した例では、1つの比較器を冗長比較器として順次選択して閾値更新処理を実行しており、図5に示す閾値設定方法を行なっていることに相当する。図6のAD変換器の閾値設定動作としては、図5に示す閾値設定方法に限定されることなく、図1や図2に示す閾値設定方法を実行してもよい。例えば、実際のAD変換動作を開始する前段階として更正期間を設け、この更正期間において、冗長比較器を用いてバックグラウンドでの閾値更新処理を実行するのではなく、冗長比較器を用いずにフォアグランドで閾値更新処理を並行して実行してもよい。その際、更正期間において入力電圧を印加し、着目比較器とそれに隣接する比較器との両方において入力電圧と閾値との比較結果を求め、図9により、これらの比較結果を比較してよい。入力電圧を変えながら複数回比較して、着目比較器のコードを徐々に変化させていくことで、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断することができる。このときの着目比較器のコード入力と、着目比較器の元のコード入力との差分を求め、この差分をr倍した値を元のコード入力に加えるようにして、閾値を更新してよい。この際、着目比較器は、隣の比較器を置き換えるのではなく、図1又は図2に示すような閾値更新としてよい。またこの時、1つずつ着目比較器を選択して順次閾値更新してもよいし、或いは、複数の比較器(例えば図1の模式図の場合、第2の比較器12と第4の比較器14等)を同時に着目比較器として選択して隣接比較器との間で比較結果を比較してもよい。この際、例えば第2の比較器12と第4の比較器14については、デジタルコードの更新値を求めるだけで、制御回路22内のレジスタ等に求めたデジタルコードを格納しておき、実際に閾値更新することなく元のデジタルコードに戻してよい。その後、第3の比較器13についても着目比較器として選択して隣接比較器との間で比較結果を比較しデジタルコードの更新値を求め、最後に、纏めて第2乃至第4の比較器の閾値を更新してよい。

【0058】

図12は、比較器の一例を示す図である。図12に示す比較器は、NMOSトランジスタ51乃至54、PMOSトランジスタ55及び56、更にスイッチ回路57乃至59を含む。この比較器は、スイッチ回路57を導通し且つスイッチ回路58及び59を非導通とすることにより、比較動作を開始する。その際、スイッチ回路58及び59を非導通とするタイミングを互いにずらすことにより、差動入力段のNMOSトランジスタ53及び54のドレイン端の電圧Vm及びVpを上記タイミングに応じて制御し、比較動作の閾値を制御している。なお制御信号φ1がHIGHになると、スイッチ回路57が導通する。また制御信号φ1xpがLOWになるとスイッチ回路59が非導通となり、制御信号φ1xmがLOWになるとスイッチ回路58が非導通となる。

【0059】

図13は、制御信号を生成する回路の一例を示す図である。図13に示す回路は、信号遷移速度を制御信号CNTLにより制御可能なインバータ61及び62により、制御信号φ1から制御信号φ1xp及び制御信号φ1xmを生成している。

【0060】

図14は、信号遷移速度を制御信号により制御可能なインバータの一例を示す図である。図14(a)に示すインバータは、PMOSトランジスタ63及びNMOSトランジスタ64を含むインバータ回路に、可変抵抗65が設けられている。図14(b)に示すように、可変抵抗65は、複数のNMOSトランジスタを並列接続し、そのゲート端に印加する1又は0の制御信号により、所望の数のNMOSトランジスタを導通状態として、所望の抵抗値を実現する。

【0061】

図15は、信号遷移速度を制御信号により制御可能なインバータの別の一例を示す図である。図15(a)に示すインバータは、PMOSトランジスタ66及びNMOSトランジスタ67を含むインバータ回路に、可変容量68が設けられている。図15(b)に示すように、可変容量68は、複数の容量素子とスイッチ回路とを並列接続し、スイッチ回路に印加する1又は0の制御信号により、所望の数のスイッチ回路を導通状態として、所望の容量値を実現する。

【0062】

図16は、図12の比較器の動作の一例を示す図である。制御信号φ1がHIGHになると、スイッチ回路57が導通する。制御信号φ1xpがLOWになると、スイッチ回路59が非導通となる。また制御信号φ1xmがLOWになると、スイッチ回路58が非導通となる。図16に示す例では、制御信号φ1xpが先にLOWになり、その後に制御信号φ1xmがLOWになっている。このタイミング差は制御信号CNTL(図14(b)又は図15(b)に示す1又は0の信号)により制御される。制御信号φ1xpが先にLOWになり、その後に制御信号φ1xmがLOWになることにより、電圧Vpが電圧Vmよりも先に低下を始める。その結果、図16の比較器の入力Vi+とVi−とがVi+>Vth+Vi−のときにのみ、出力Vo+及びVo−はそれぞれHIGH及びLOWとなる。この電圧Vthが閾値である。仮に、制御信号φ1xpと制御信号φ1xmとがLOWになるタイミングが同一であれば、Vi+>Vi−であれば、出力Vo+及びVo−はそれぞれHIGH及びLOWとなる。図16に示す例のように、制御信号φ1xpと制御信号φ1xmとにタイミング差を設けることで、このタイミング差に応じた閾値Vthを設定することができる。

【0063】

図17は、比較器の別の一例を示す図である。図17に示す比較器は、NMOSトランジスタ71乃至74、PMOSトランジスタ75及び76、スイッチ回路77乃至79を含む。更にこの比較器は、閾値設定回路80、スイッチ回路81及び82、複数のNMOSトランジスタ83、複数のNMOSトランジスタ84、及びスイッチ回路85及び86を含む。この比較回路は、スイッチ回路77を導通し且つスイッチ回路78及び79を非導通とすることにより、比較動作を開始する。その際、スイッチ回路81及びNMOSトランジスタ83を介して電流を瞬間的に流すと共に、スイッチ回路82及びNMOSトランジスタ84を介して電流を瞬間的に流す。これらの電流量を、スイッチ回路81の導通スイッチ数とスイッチ回路82の導通スイッチ数とを調整することにより制御し、比較動作の閾値を制御している。これらのスイッチ回路81及び82の導通スイッチ数は、閾値設定回路80により制御される。なお制御信号φ1がLOWの場合、スイッチ回路77が非導通となり、スイッチ回路78、79、85、86が導通となる。制御信号φ1がHIGHになると、スイッチ回路77が導通し、スイッチ回路78、79、85、86が非導通となり、比較動作を開始する。

【0064】

図18は、図17の比較器の動作の一例を示す図である。制御信号φ1がLOWでリセット状態であり、制御信号φ1がHIGHになると比較動作が開始される。比較動作が開始されると、図17に示す差動入力段のNMOSトランジスタ73及び74のドレイン端の電圧DM及びDPがHIGHから降下していく。これら電圧DM及びDPがNMOSトランジスタ83及び84の閾値電圧より高い間は、スイッチ回路81及びNMOSトランジスタ83を介して電流が瞬間的に流れると共に、スイッチ回路82及びNMOSトランジスタ84を介して電流が瞬間的に流れる。その後、電圧DM及びDPがNMOSトランジスタ83及び84の閾値電圧より低くなり、これらの2つの電流は停止する。これらの電流は、比較器の出力OP及びOMをグランドに引っ張る方向に流れる。従って、スイッチ回路81の導通スイッチ数とスイッチ回路82の導通スイッチ数とを異ならせることにより、出力OP及びOMの何れか一方を他方よりも強くグランドに向けて引っ張ることができる。

【0065】

このようにして、スイッチ回路81の導通スイッチ数とスイッチ回路82の導通スイッチ数とを制御することで、例えば、比較器の入力VIPとVIMとがVIP>Vth+VIMのときにのみ、出力OP及びOMをそれぞれHIGH及びLOWとする。この電圧Vthが閾値である。仮に、スイッチ回路81とスイッチ回路82とで導通スイッチ数が同一であれば、VIP>VIMであれば、出力OP及びOMはそれぞれHIGH及びLOWとなる。スイッチ回路81の導通スイッチ数とスイッチ回路82の導通スイッチ数とを異ならせることで、この導通スイッチ数の差に応じた閾値Vthを設定することができる。

【0066】

図19は、通信装置の一例を示す図である。図19の通信装置100は、RF回路101、AD変換&DA変換部102、及びデジタル信号処理部103を含む。デジタル信号処理部103は、同期部、復調部、変調部、誤り訂正部、符号化部等の通信処理部を含む。RF回路101が、受信したRF信号を変調信号に変換する。AD変換&DA変換部102により、変調信号をデジタルからアナログへ変換した後に、デジタル信号処理部103により所定の処理を実行する。AD変換&DA変換部102に、前述のAD変換器を用いることができる。

【0067】

以下において、閾値が収束した後に誤差が発生しないような閾値設定方法について説明する。前述のように、図1又は図4の動作をするAD変換器においてrが例えば0.1である場合、各比較器の閾値が、隣接閾値との差の0.1倍程度の振幅で増減し続けることになる。この結果、各比較器の閾値が所望の閾値の近辺に収束した後であっても、隣接閾値との差の0.1倍程度の誤差が残ってしまうことになる。これは図5の動作をするAD変換器においてrが例えば0.9である場合にも同様である。rを例えば0.01のように小さな値に設定すれば、誤差は小さくなるが、収束するまでに時間がかかるという問題がある。

【0068】

以下の説明では、便宜上、前述の閾値設定方法と同様に、図4の例を用いて説明する。比較器11乃至15の両端の閾値、即ち比較器11の閾値と比較器15の閾値とは、両方ともに所定の閾値に固定されていてよい。

【0069】

まず、第1乃至第5の比較器11乃至15のうち、1<M<5である第Mの比較器(即ち両端以外の比較器)に着目し、この第Mの比較器の閾値をTHMとする。また第1乃至第5の比較器11乃至15の並び順において、M番目の位置の近傍にある第M−1の比較器の閾値をTHM−1とし、M番目の位置の近傍にある第M+1の比較器の閾値をTHM+1とする。このとき閾値更新動作により、第Mの比較器の更新後の閾値は、第M−1の比較器の閾値と第M+1の比較器の閾値との平均値に等しく設定される。即ち、第Mの比較器の更新後の閾値は、(THM−1+THM+1)/2に等しく設定される。同様の閾値更新動作を、比較器12乃至14の各々に対して実行する。これにより、1回の閾値更新動作が終了する。この閾値更新動作を繰り返し複数回実行することにより、各比較器12乃至14の閾値は、比較器11の閾値と及び比較器15の閾値との間を略等間隔に分割するように設定される。

【0070】

上記説明では、M番目の位置の前後2つの比較器である第M−1の比較器の閾値と第M+1の比較器の閾値との平均値を、第Mの比較器の更新後の閾値とした。しかし更新後の閾値は、この計算例に限定されることなく、第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定されてよい。例えば、M番目の位置の近傍にある第M−1の比較器、第Mの比較器、及び第M+1の比較器のそれぞれの比較器の平均値としてよい。即ち、第M−1の比較器の閾値をTHM−1とし、第Mの比較器の閾値をTHMとし、第M+1の比較器の閾値をTHM+1とする。このとき閾値更新動作により、第Mの比較器の更新後の閾値は、(THM−1+THM+THM+1)/3に等しく設定されてよい。

【0071】

また例えば、M番目の位置の近傍にある第M−2、第M−1、第M、第M+1、及び第M+2の5つの比較器の閾値の平均値を、第M番目の比較器の更新後の閾値としてよい。或いは例えば、M番目の位置の近傍にある第M−2、第M、及び第M+2の3つの比較器の閾値の平均値を、第M番目の比較器の更新後の閾値としてよい。或いは例えば、M番目の位置の近傍にある第M−2及び第M+2の2つの比較器の閾値の平均値を、第M番目の比較器の更新後の閾値としてよい。なおM番目の位置の近傍にある複数の比較器とは、例えば、第Mの比較器、第M−1の比較器、第M+1の比較器、・・・、第M−kの比較器、第M+kの比較器のうちの少なくとも2つの比較器である。M番目の位置の近傍にある何れの比較器を閾値平均化の対象とするかについては、特に限定されるものではない。近傍領域において比較的遠くにある比較器(上記のkが大きな比較器)を選ぶほど、比較的収束し難くなる傾向にある。しかしこの収束容易性の変化は連続的な変化であり、確実な収束の必要条件となる近傍領域の大きさが明確に規定されるものではない。

【0072】

このように、第Mの比較器の閾値を例えばその前後の比較器の閾値の平均値に等しく設定することで、第Mの比較器とその前後の比較器との間の閾値間距離が等しくなるように閾値が更新される。即ち更新動作により局所的に閾値間距離が等しくなるように変化し、その結果、各比較器の閾値の間の閾値間距離は、第1の比較器から第5の比較器まで一定値である方向に変化していく。最終的には、複数の閾値間距離が端から端まで一定の値である分布に近づいていく。即ち、比較器11乃至15の閾値が、下端閾値から上端閾値までの間に等間隔に並ぶような配置に近づいていく。

【0073】

なお複数の比較器の閾値の単なる平均値ではなく、複数の比較器の閾値の重み付け平均値であってよい。重み付け平均値であってよい理由は、以下に説明するように2つある。

【0074】

まず第1の理由について述べる。図1を用いて説明した閾値設定方法においては、第1の更新動作において、(THM+1−THM)のr倍をTHMに加えるように閾値更新をし、第2の更新動作において、(THM−1−THM)のr倍をTHMに加えるように閾値更新をする。この第1の更新動作は、

(THM+1−THM)r+THM=r・THM+1+(1−r)・THM

であり、更新後の閾値は、M番目の位置の近傍にある複数の比較器の閾値の重み付け平均値となっている。第2の更新動作も同様に、更新後の閾値は、M番目の位置の近傍にある複数の比較器の閾値の重み付け平均値となっている。これは、ここまで説明した全ての更新動作について同様である。即ち、ここまで説明した全ての閾値設定方法は、第Mの比較器の更新後の閾値をM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定するという技術的思想で統一される。なお単純な平均値を求める場合は、重み付け平均値を求める際の重みは平均化対象である各閾値に対して同一となる。

【0075】

次に第2の理由について述べる。またAD変換器のアプリケーションによっては、入力電圧と出力デジタルコードとの間の関係が線形特性ではなく、曲線的な特性となることが好ましい場合がある。例えば、後段の表示機器のガンマ特性を補正するために、このガンマ特性を補償するような曲線特性をAD変換器により実現することが考えられる。或いは前段のセンサの特性を補正するために、センサ特性を補償するような曲線特性をAD変換器により実現することが考えられる。そのような場合、閾値更新に例えば前後2つの比較器の閾値THM−1及びTHM+1を用いるとすると、第Mの比較器の更新後の閾値を平均値(THM−1+THM+1)/2とするのではなく、重み付け平均値r・THM−1+(1−r)・THM+1とすることが考えられる。ここで係数rは、0より大きく1より小さい値である。そしてこの重み付けの係数rを、各位置(M=2,3,4・・・)において異ならせることにより、収束後の閾値間距離を、各位置(M=2,3,4・・・)において異ならせることができる。即ち、第Mの比較器の更新後の閾値をM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定する際に、その重み付けを各位置において異ならせる。言葉を換えて言えば、重み付け平均値を求める際の平均化対象である各閾値の重みの比率(例えばr:(1−r))は、第1の値のM(例えば3番目)に対する第1の比率と、前記第1の値とは異なる第2の値のM(例えば4番目)に対する第2の比率とが異なる。これにより、AD変換器の入力電圧と出力デジタルコードとの間の関係を、線形特性ではなく曲線的な特性に設定することが可能となる。

【0076】

上記の閾値設定方法は、前述の図5に示した場合のように、冗長な比較器を設けた構成に対しても適用できる。冗長な比較器を設けた場合の閾値設定方法を、便宜上図5を用いて説明する。

【0077】

図5において、第6の比較器16が冗長な比較器として設けられている。この図5におけるAD変換動作と閾値更新動作とは、前述の場合と同様である。即ち、第5の比較器15の閾値を更新すると、第5の比較器15をエンコーダに接続するとともに、残りの複数の比較器11乃至15のうちから選択した所望の比較器をエンコーダから切り離して閾値の更新を行なってよい。具体的には、第4の比較器14をエンコーダから切り離して、閾値更新の対象としてよい。この閾値更新の間は、比較器11,12,13,15,16の5つの比較器により、AD変換動作を実行することになる。

【0078】

第Mの比較器の更新後の閾値は、M番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定される。例えば、第Mの比較器の更新後の閾値は、第Mの比較器の閾値と第M−2の比較器の閾値との平均値に等しく設定されてよい。即ち、第Mの比較器の更新後の閾値は、(THM−2+THM)/2に等しく設定されてよい。具体的には、まず第5の比較器15の更新後の閾値を、(TH3+TH5)/2とする。TH4とTH6との平均値ではなく、TH3とTH5との平均値を用いるのは、図5に示されるように、第5の比較器15の閾値を更新すると、閾値更新後の第5の比較器15により、第4の比較器14を置き換えるからである。但し見方を変えれば、第5の比較器15は、更新後にエンコーダに接続される置換後の第4番目の比較器となるのであり、この置換後の第4番目の比較器の更新後の閾値TH4が、その前後の閾値の平均値(TH3+TH5)/2であると考えることもできる。図5の例では、閾値3の近傍の比較動作を実行すべき比較器は初期状態で第4の比較器14であり、その後第5の比較器15に置き換わり、その後更に第4の比較器14に置き換わり、というように比較器14と15とに交互に置き換わる。図5において、点線で示す矢印が、各比較器の実際の閾値の変化を示す。実線で示す矢印は、所定の閾値近傍の比較動作を実行すべき比較器の置き換わりの推移を示す。

【0079】

第5の比較器15により置き換えられた第4の比較器14は、エンコーダから切り離され、閾値更新動作に供される。第4の比較器14の閾値更新が終了すると、閾値更新後の第4の比較器14により、第3の比較器13を置き換える。第4の比較器14により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。第3の比較器13の閾値更新が終了すると、閾値更新後の第3の比較器13により、第2の比較器12を置き換える。第2の比較器12は、エンコーダから切り離され、閾値更新動作に供される。この際、第2の比較器12の閾値TH2は、第1の比較器11の閾値TH1に等しい値に設定されてよい。以上で、比較器11乃至16に対する一段の閾値更新動作が終了する。なお両端の比較器11及び16については、それぞれ両端の閾値0及び4に固定しておいてよい。

【0080】

次の更新動作においては、第Mの比較器の更新後の閾値は、第Mの比較器の閾値と第M+2の比較器の閾値との平均値に等しく設定されてよい。即ち、第Mの比較器の更新後の閾値は、(THM+2+THM)/2に等しく設定されてよい。具体的には、まず第2の比較器12の更新後の閾値を、(TH4+TH2)/2とする。第2の比較器12の閾値更新が終了すると、閾値更新後の第2の比較器12により、第3の比較器13を置き換える。第2の比較器12により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。以降同様にして、順次、比較器13乃至15の閾値を更新していく。

【0081】

前述の場合と同様に、更新後の閾値は、上記の計算例に限定されることなく、例えば、M番目の位置の近傍にある第3つの比較器のそれぞれの比較器の平均値としてよい。また例えば、M番目の位置の近傍にある4つ又はそれ以上の数の比較器の閾値の平均値を、第M番目の比較器の更新後の閾値としてよい。また例えば連続する位置にある比較器ではなく、1つ又はそれ以上の比較器を間に挟んだ位置にある複数の比較器の閾値を、平均値をとる対象の閾値としてもよい。M番目の位置の近傍にある何れの比較器を閾値平均化の対象とするかについては、特に限定されるものではない。また曲線特性を得るために、単純な平均値ではなく重み付け平均値により更新するようにし、その重み係数の値を位置により異なる値に設定してもよい。

【0082】

上記説明した、第Mの比較器の更新後の閾値をM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定する方法は、前述の図6及び図7に示す半導体集積回路(AD変換回路)及びエンコーダにより実行することができる。但し、制御回路22については、閾値更新動作に用いる比較器の数及び位置に応じて、その構成を適宜変更する。

【0083】

図20は、制御回路22による冗長比較器の閾値更新を説明するための図である。図20では、第Mの比較器の更新後の閾値が(THM+2+THM)/2に等しく設定される例について、制御回路22の構成が示される。制御回路22は、2入力のうち下位側が負論理入力の複数のNORゲート90、2入力のうち上位側が負論理入力の複数のNORゲート91、及び制御ロジック回路93を含む。1つのNORゲート90と1つのNORゲート91とで一対をなし、一対のNORゲートの各々は、8つの比較器20−1乃至20−8のうちで、1つの比較器を間において並ぶ2つの比較器の出力を受け取る。比較器20−1乃至20−8のうちの1つの比較器を間において並ぶ2つの比較器の組み合わせは、6つあるので、6対のNORゲートが設けられることになる。図20には図示の便宜上、4対のNORゲートだけが示されている。

【0084】

各比較器20−1乃至20−8の出力はエンコーダ21に供給されると共に、並行して制御回路22にも供給される。1つの比較器を間において並ぶ2つの比較器に対して設けられた一対のNORゲートは、入力電圧VINがこれら2つの比較器の2つの閾値よりも大きいか、小さいか、或いはその中間にあるか、に関する判定を行なう。以下において、図7で示した例と同様に、第3の比較器20-3が冗長比較器であり、この閾値の更新を実行する場合について説明する。

【0085】

第3の比較器20-3の閾値及び第5の比較器20-5の閾値の何れよりも入力電圧VINが低い場合、対応するNORゲート90の出力J+とNORゲート91の出力J−は、双方共に0となる。また第3の比較器20-3の閾値及び第5の比較器20-5の閾値の何れよりも入力電圧VINが高い場合も、対応するNORゲート90の出力J+とNORゲート91の出力J−は、双方共に0となる。このように出力J+と出力J−とが双方共に0の場合、制御ロジック回路93は何も実行しない。

【0086】

第3の比較器20-3の閾値及び第5の比較器20-5の閾値との間に入力電圧VINが有る場合には、第3の比較器20-3の閾値TH3と第5の比較器20-5の閾値TH5との大小関係に応じて、対応するNORゲートの出力J+及び出力J−が変化する。TH3<TH5である場合、第3の比較器20-3及び第5の比較器20-5の出力はそれぞれ1及び0となるので、NORゲート90の出力J+とNORゲート91の出力J−はそれぞれ1及び0となる。このとき、制御ロジック回路93は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1増加させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ増加させる。これにより、TH3がTH5に近づくことになる。逆に、TH3>TH5である場合、第3の比較器20-3及び第5の比較器20-5の出力はそれぞれ0及び1となるので、NORゲート90の出力J+とNORゲート91の出力J−はそれぞれ0及び1となる。このとき、制御ロジック回路93は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1減少させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ減少させる。これにより、TH3がTH5に近づくことになる。このようにして、AD変換器に入力される入力アナログ電圧VINと閾値との比較動作を逐次実行し、その比較結果に応じて、第3の比較器20-3の閾値を変化させていく。

【0087】

TH3とTH5とが等しくなると、入力アナログ電圧VINの値に関わらず、NORゲート90の出力J+とNORゲート91の出力J−とは、共に0になる。例えば、入力アナログ電圧VINと各閾値の比較動作を1000回行なったときに、1000回の比較動作の全てにおいて出力J+と出力J−とが、双方共に0になる。如何なるデジタルコードDcnt(3)を設定してもTH3とTH5とが完全に一致することが無い場合、即ち、各比較器の最小分解能に応じた差が常に存在する場合には、多数回の比較動作のうちで出力J+と出力J−とが異なる値となる場合が常に発生する。従って、例えば、1000回の比較動作において所定の割合以上(例えば99.5%以上)において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH5とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。同様に、所定の回数以上連続して出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH5とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。ここで更新動作の実行とは、TH3とTH5とが実質的に等しくなったときのデジタルコードと最初の状態のデジタルコードとの差の0.5倍を、最初の状態のデジタルコードに加えることである。これにより、0.5(TH5−TH3)をTH3に加えることになり、第3の比較器の更新後の閾値は(TH5+TH3)/2となる。

【0088】

TH3の更新動作が完了すると、第3の比較器20-3をエンコーダ21に接続し、第4の比較器20-4をエンコーダ21から切り離す。そして、第4の比較器20-4を冗長比較器として、第4の比較器20-4の閾値の更新を実行する。以下同様である。なお、下側の比較器(例えば第3の比較器20−3)の閾値を参照して上側の比較器(例えば第5の比較器20−5)の閾値を更新する動作も、上記の説明と同様にして実行することができる。

【0089】

上記説明した図20に示すAD変換器の複数の比較器の更新動作は、前述の図11に示すフローチャートに示す通りの流れにより実行することができる。簡単に説明すると、ステップS1において、各比較器にデジタルコードを初期設定する。ステップS2において、変数Mを2に初期化する。ステップS3において、変数Mが比較器の全個数mに等しいか否かを判定する。等しくない場合には、ステップS4に進む。ステップS4において、図20を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。但し、端の1つ前の比較器(第m−1の比較器)の場合には、前述のように、更新後の閾値を端の閾値(第mの比較器の閾値)に等しくなるように設定する。第M番目の比較器の閾値更新処理を完了すると、ステップS5において、変数M=M+1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS3に戻り、以降の処理を、次の比較器に対して実行する。

【0090】

ステップS3において、変数Mが比較器の全個数mに等しいと判定された場合、ステップS6に進む。ステップS6において、変数M=m−1とする。次にステップS7において、変数Mが1に等しいか否かを判定する。等しくない場合には、ステップS8に進む。ステップS8において、図20を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。但し、端の1つ前の比較器(第2の比較器)の場合には、前述のように、更新後の閾値を端の閾値(第1の比較器の閾値)に等しくなるように設定する。第M番目の比較器の閾値更新処理を完了すると、ステップS9において、変数M=M−1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS7に戻り、以降の処理を、次の比較器に対して実行する。

【0091】

ステップS7において、変数Mが1に等しいと判定された場合、ステップS2に進む。ステップS2において、変数M=2とする。以降、ステップS2乃至S9の処理を同様にして繰り返す。

【0092】

なお上記の図20に示す例では、2つの閾値の平均値を求める場合が示されるが、3つの閾値の平均値を求める場合も同様の回路構成を用いることができる。即ち、第Mの比較器の更新後の閾値が(THM+2+THM+1+THM)/3に等しく設定される場合であれば、図9のNORゲート40及び41と図20のNORゲート90及び91とを両方とも備えた構成とすればよい。まず第3の比較器20-3の閾値TH3と第4の比較器20-4の閾値TH4とに着目し、上記と同様の処理により、NORゲート40及び41の出力に基づいて(TH4−TH3)に相当する第1のデジタルコード差を求める。また第3の比較器20-3の閾値TH3と第5の比較器20-5の閾値TH5とに着目し、NORゲート90及び91の出力に基づいて(TH5−TH3)に相当する第2のデジタルコード差を求める。その後、第1のデジタルコード差と第2のデジタルコード差との和の1/3を最初の状態のデジタルコードに加える。これにより、((TH4−TH3)+(TH5−TH3))/3をTH3に加えることになり、第3の比較器の更新後の閾値は(TH5+TH4+TH3)/2となる。

【0093】

図21は、閾値設定方法の計算機シミュレーションの結果を示す図である。この図21は、ある閾値更新動作では第Mの比較器の更新後の閾値を(THM−2+THM)/2に等しく設定し、次の閾値更新動作では第Mの比較器の更新後の閾値を(THM+2+THM)/2に等しく設定する場合の計算機シミュレーションの結果を示す。この場合、重み付け平均に用いる重み係数の値は、比較器の位置によらず一定の値0.5である。横軸は、比較器の番号を示し、第1の比較器から第16の比較器まで16個の比較器が設けられている。縦軸は、各比較器の閾値の値を示す。なお計算機シミュレーションでは、デジタルコードを介して各比較器の閾値を変化させるのではなく、直接に閾値を用いて閾値更新動作を行なっている。即ち、各比較器の閾値(例えば第Mの比較器の閾値THM)が分かっているものとして、複数の閾値の平均値計算を行なっている。複数の比較器の出力であるサーモメータコードをエンコーダによりエンコードしてAD変換後のデジタルコードが得られるので、比較器の番号を示す横軸はそのままデジタル値に対応すると考えることができる。従って、各比較器の番号と閾値との関係を示す図21は、AD変換器の入力電圧とデジタルコード出力との間の特性を示していると考えることができる。

【0094】

図21において、特性曲線101は初期状態での閾値分布を示すものである。第2乃至第15の比較器の閾値を順次更新していくことにより徐々に閾値が直線上に揃っていき、十分な回数の閾値更新動作を実行した後には、特性曲線102及び特性曲線103に示す閾値分布が得られる。この例では、1つ冗長な比較器を設け、冗長な比較器の閾値を更新した後に、閾値更新後の比較器で他の比較器を置き換えていく動作が実行される。従って、16個の比較器に対して、閾値分布は1.00〜15.00の範囲での分布となっている。従って、十分な回数の閾値更新動作を実行した後であっても、ある1つの比較器に着目すると、この比較器の閾値は略1.00の変化幅で増減を繰り返すことになる。即ち、例えば第10の比較器の閾値は、略9.00と略10.00との2つの値の間を行き来することになる。しかしマークAで示すように、第9の比較器の閾値と第10の比較器の閾値とは略9.00の値を交互にとっており、AD変換動作の為に必要な閾値としては略9.00の値が得られる。この場合、小数点以下4桁程度まで9.0に値が等しい閾値を、比較的迅速に得ることができる。即ち、更新の係数rが例えば0.1である場合のように隣接閾値との差の0.1倍程度の誤差が残ってしまうことがない。

【0095】

図22は、閾値設定方法の別の計算機シミュレーションの結果を示す図である。この図22は、第Mの比較器の更新後の閾値を重み付け平均値に等しく設定し、その重み付け係数の値を位置により変化させた場合の計算機シミュレーションの結果を示す。具体的には、ある閾値更新動作では第Mの比較器の更新後の閾値をr・THM−1+(1−r)THMに等しく設定し、次の閾値更新動作では第Mの比較器の更新後の閾値をr・THM+1+(1−r)THMに等しく設定する。重み付け係数rの値は、第2の比較器から第8の比較器に対してそれぞれ0.9、0.8、0.7、0.6、0.5、0.4、0.3であり、第9の比較器から第15の比較器に対してそれぞれ0.4、0.5、0.6、0.7、0.8、0.9、0.9である。このように、中心部で値が小さく、周辺部に向かい値が大きくなるように、重み付け係数が設定されている。

【0096】

図22において、特性曲線111は初期状態での閾値分布を示すものである。第2乃至第15の比較器の閾値を順次更新していくことにより徐々に閾値が直線上に揃っていき、十分な回数の閾値更新動作を実行した後には、特性曲線112及び特性曲線113に示す閾値分布が得られる。この例では、1つ冗長な比較器を設け、冗長な比較器の閾値を更新した後に、閾値更新後の比較器で他の比較器を置き換えていく動作が実行される。従って、16個の比較器に対して、閾値分布は1.00〜15.00の範囲での分布となっている。図22に示されるように、AD変換器の入力電圧とデジタルコード出力との間の特性に対応する特性曲線112及び113は、S字型の曲線の特性となっている。これは、中心部で値が小さく周辺部に向かい値が大きくなるような重み付け係数の設定に対応している。このように重み付け係数の値、即ち平均化対象の複数の閾値の重み付けの比率を、Mの値に応じて変化させることで所望の形の特性曲線を得ることができる。

【0097】

冒頭で説明したように、所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。従って、下端の閾値及び上端の閾値をそれぞれ適切な値に設定できるとは限らない。ここまでは、下端の閾値及び上端の閾値を適切な値に設定できると仮定して、その間を等分する場合について説明してきたが、以下においては、下端の閾値及び上端の閾値を適切な値に設定する方法について説明する。

【0098】

まず下端の閾値及び上端の閾値が適切な値に設定されない場合の問題点について説明する。図1、図4、及び図5に示す例において、例えば上端の閾値が3.6に設定され、下端の閾値が0.0に設定される場合を考える。この場合、ここまでに説明した閾値設定方法により各比較器の閾値を設定すると、0.0〜3.6の範囲を4等分することになり、1.0間隔の閾値設定ではなく0.9間隔の閾値設定しか得られないことになる。また例えば、図1、図4、及び図5に示す例において、例えば上端の閾値が4.3に設定され、入力アナログ電圧の上限は4.0(V)である場合を考える。前述の閾値設定方法では、着目比較器のコードを徐々に変化させながら、着目比較器の比較結果と隣接比較器の比較結果とを比較し、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断している。例えば図4の例において、比較器15の閾値が4.3に設定されている場合、比較器14の入力コードを徐々に増大させていきその閾値が少しでも4.0を超えると、その時点で比較器14の比較結果と比較器15の比較結果とは常に同一となってしまう。従って、比較器14に対して適切な閾値更新動作を実行することができない。以下においては、これらの問題点を解決するための両端(上端及び下端)の閾値設定方法について説明する。

【0099】

図23は、入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。図23において、図6と同一又は対応する構成要素は同一又は対応する番号で参照し、その説明は適宜省略する。

【0100】

図23に示す半導体集積回路は全並列型或いは直並列型のAD変換器であり、複数の比較器20−1乃至20−8、エンコーダ21、及び制御回路122を含む。第1乃至第8の比較器20−1乃至20−8は、制御回路122からの4ビットのデジタルコード入力により対応する閾値が設定される。エンコーダ21の構成は図7に示すものであってよい。なお図23には、説明の便宜上、シングルエンドであるAD変換器を示すが、差動信号のAD変換を行なう差動構成のAD変換器であってよい。

【0101】

比較器20−1乃至20−8は、それぞれ制御回路122から印加されたコードに対応する閾値が設定されている。比較器20−1乃至20−8は、入力アナログ電位VINを受け取り、入力アナログ電位VINとそれぞれの閾値とを比較して、その比較結果を出力する。比較器20−1乃至20−8のうちの1つは冗長な比較器であり、制御回路122によりエンコーダ21から切り離され、閾値更新動作に供される。残りの7つの比較器の出力に基づいて、エンコーダ21が符号化を実行し、3ビットのバイナリコードDoutとして出力する。

【0102】

図24は、制御回路122の構成の一例を示す図である。図24に示す制御回路122は、内部制御部131、選択部132、閾値コード決定部133、振幅検出部134、及び閾値コード保持部135を含む。振幅検出部134は、上限値検出部136及び下限値検出部137を含む。内部制御部131は、選択部132、閾値コード決定部133、振幅検出部134、及び閾値コード保持部135の動作を制御する。

【0103】

選択部132は、比較器20−1乃至20−8からそれぞれの比較結果を受け取る。選択部132は、内部制御部131の制御の下で、現在エンコーダ21から切り離され閾値更新動作に供されている冗長な比較器の出力とそれに隣接する比較対象の比較器の出力とを選択し、選択した2つの出力を閾値コード決定部133に供給する。閾値コード決定部133は、図9に示す構成と同様に、2入力のうち下位側が負論理入力の1個のNORゲート40、及び、2入力のうち上位側が負論理入力の1個のNORゲート41を含んでよい。これらNORゲート40及びNORゲート41の対により、選択部132から供給される冗長な比較器の出力と比較対象の比較器の出力との比較を行う。

【0104】

図9に示す制御ロジック回路43に相当する論理制御は、内部制御部131に設けられていてもよいし、或いは閾値コード決定部133に設けられていてもよい。閾値コード決定部133は、図9で説明した動作と同様にして、選択部132から供給される比較器の出力と比較対象の比較器の出力との比較を行い、冗長な比較器の閾値を更新する。即ち、NORゲート40の出力J+とNORゲート41の出力J−とに基づいて、冗長な比較器のデジタルコードを1ずつ増加又は減少させることにより、冗長な比較器の閾値を比較対象の比較器の閾値に近づけていく。そして例えば1000回の比較動作において所定の割合以上(例えば99.5%以上)において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、冗長な比較器の更新動作を実行してよい。これにより、閾値コード保持部135に保持される冗長な比較器の閾値を示すデジタルコードが更新後のデジタルコードに設定される。この更新後のデジタルコードを供給される冗長な比較器には、更新後の閾値が設定されることになる。

【0105】

図9の場合と同様に、図24に示す構成においても、冗長な比較器を順次選択して閾値更新処理を実行する図5に示す閾値設定方法に限定されることなく、図1や図4に示す閾値設定方法を実行してもよい。例えば、実際のAD変換動作を開始する前段階として更正期間を設け、この更正期間において、冗長比較器を用いずにフォアグランドで閾値更新処理を実行してもよい。

【0106】

振幅検出部134は、入力アナログ電圧の動作範囲(振幅)を検出することに相当する動作を実行し、検出結果に応じて第1の比較器20−1及び第8の比較器20−8の閾値を設定する。具体的には、振幅検出部134は、入力アナログ電圧の下限値及び上限値に応じて、第1の比較器20−1及び第8の比較器20−8の閾値を設定する閾値設定動作を実行する。この閾値設定動作により、第1及び第8の比較器20−1及び20−8の閾値は、第1及び第8の比較器20−1及び20−8による入力アナログ電圧と閾値との比較結果に応じて、それぞれ入力アナログ電圧の下限値近傍及び上限値近傍に設定される。より具体的には、下限値検出部137が、第1の比較器20−1による入力アナログ電圧と閾値との比較結果に応じて、入力アナログ電圧の下限値近傍に第1の比較器20−1の閾値を設定する。また上限値検出部136が、第8の比較器20−8による入力アナログ電圧と閾値との比較結果に応じて、入力アナログ電圧の上限値近傍に第8の比較器20−8の閾値を設定する。なお入力アナログ電圧の下限値近傍及び上限値近傍の位置とは、比較器20−1及び20−8の当該位置への閾値設定後、8つの比較器20−1乃至20−8の閾値が等間隔に調整されたときに、下限値から上限値までを略7等分に分割する第1の位置であってよい。また或いは、入力アナログ電圧の下限値近傍及び上限値近傍の位置とは、比較器20−1及び20−8の当該位置への閾値設定後、8つの比較器20−1乃至20−8の閾値が等間隔に調整されたときに、下限値から上限値までを略9等分に分割する第2の位置であってよい。第1の位置は、入力アナログ電圧の下限値及び上限値に略一致する位置であり、第2の位置は、入力アナログ電圧の下限値及び上限値から入力アナログ電圧の振幅幅の1/9だけそれぞれ内側に入り込んだ位置である。また或いは、入力アナログ電圧の下限値近傍及び上限値近傍の位置とは、上記第1の位置から上記第2の位置の間の位置であってよい。

【0107】

以下の説明においては、説明の便宜上、並列型のAD変換器の複数の比較器をC1乃至C6とし、これら6個の比較器C1乃至C6に対する閾値設定動作について説明する。

【0108】

図25は、初期設定処理としての閾値設定動作及びその後の設定処理としての閾値更新動作の一例を示す図である。初期設定ステップI0において、下端の閾値に対応する比較器C1の閾値設定動作を実行する。次に初期設定ステップI1において、上端の閾値に対応する比較器C6の閾値設定動作を実行する。その後、閾値更新ステップS0乃至S9において、両端以外の閾値に対応する比較器C2乃至C5の閾値を順次更新していく。これらの閾値更新動作は前述の通りである。なお図25に示す例では、比較器C2乃至C5の閾値更新動作だけでなく、両端の比較器C1及びC6の閾値設定動作も順次実行している。この閾値設定動作は、初期設定ステップI0及びI1における処理と同様である。冗長比較器を用いてバックグラウンドでの閾値更新処理を実行する場合に、両端の比較器C1及びC6の閾値設定動作も順次実行することにより、入力アナログ電圧の範囲の変動や比較器の特性の時間による変化等に対して動的に適応することが可能となる。

【0109】

図26は、下限値検出部137の構成の一例を示す図である。図26に示す下限値検出部137は、下限値検出部制御部141、出力値モニタ部142、比較器出力値保持部143、及び閾値更新部144を含む。下限値検出部制御部141は、図24の内部制御部131の制御の下で動作し、出力値モニタ部142及び閾値更新部144の動作を制御する。比較器出力値保持部143は、比較器C1の出力をサンプルし、サンプルしたC1出力を所定の期間保持する。なお比較器C1の出力は、入力アナログ電圧が比較器C1の閾値よりも低いときに0となり、入力アナログ電圧が比較器C1の閾値よりも高いときに1となる。出力値モニタ部142は、比較器出力値保持部143が保持する比較器C1の出力をモニタする。出力値モニタ部142によるモニタ結果に応じて、下限値検出部制御部141は、比較器C1の閾値更新処理を閾値更新部144に実行させる。具体的には、閾値更新部144は、閾値コード保持部135から比較器C1の閾値を受け取り、更新後の閾値を閾値コード保持部135に供給する。これらの動作により、比較器C1のコード入力を徐々に変化させながら、比較器C1による入力アナログ電圧と閾値との比較結果が0であるか1であるかを判定することにより、比較器C1の閾値を入力アナログ電圧の下限値近傍に設定する。

【0110】

図27は、比較器C1の閾値を設定する閾値設定動作の一例を示すフローチャートである。ステップS1で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS2で、モニタ期間として定めた一定期間中においてC1出力値が常に1であるか否かを出力値モニタ部142が判定する。判定結果がYesである場合、処理はステップS3に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(即ち閾値を1ステップ増加させる)。ステップS4で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS5で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS6で、モニタ期間として定めた一定期間中においてC1出力値が常に1であるか否かを出力値モニタ部142が判定する。判定結果がYesである場合、処理はステップS7に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(即ち閾値を1ステップ増加させる)。その後ステップS8で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新し、処理はステップS5に戻る。ステップS6での判定結果がNoである場合、即ち、モニタ期間として定めた一定期間中において0であるC1出力値が一度でも検出された場合、ステップS9に進みそのまま処理を終了する。

【0111】

図28は、以上のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。2つの○印が2つの比較器C1及びC2を表わし、○印の垂直方向の位置が各比較器に設定されている閾値の大きさTH1及びTH2を表わす。図28(a)から(c)へと時間が経過していき、閾値が変化していく様子が模式的に示されている。Lは、入力アナログ電圧の下限値の位置を示す。図28(a)の状態では、比較器C1の閾値TH1は、下限値Lよりも低い位置にあり、比較器C1の出力(比較結果)は常に1となる。従って、比較器C1の閾値のデジタルコードは順次+1されて、図28(b)に示されるように徐々に閾値TH1が大きく(高く)なっていく。その後閾値TH1が更に高くなり図28(c)の状態になると、比較器C1の閾値TH1は下限値Lよりも高い位置になり、比較器C1の出力(比較結果)が0になる場合が発生する。このように0であるC1出力値が検出された場合、処理を終了することにより、その時点でのTH1の位置(図28(c)に示す位置)が比較器C1の閾値の設定値となる。

【0112】

図27に戻り、ステップS2での判定結果がNoである場合、即ちモニタ期間として定めた一定期間中において0であるC1出力値が一度でも検出された場合、処理はステップS10に進む。ステップS10で、閾値更新部144が比較器C1の閾値のデジタルコードを−1する(即ち閾値を1ステップ減少させる)。ステップS11で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS12で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS13で、モニタ期間として定めた一定期間中においてC1出力値が常に1であるか否かを出力値モニタ部142が判定する。ステップS13での判定結果がNoである場合、即ちモニタ期間として定めた一定期間中において0であるC1出力値が一度でも検出された場合、処理はステップS14に進む。ステップS14で、閾値更新部144が比較器C1の閾値のデジタルコードを−1する(即ち閾値を1ステップ減少させる)。ステップS15で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。その後処理はステップS12に戻り、以降の処理を繰り返す。ステップS13での判定結果がYesである場合、処理はステップS16に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(即ち閾値を1ステップ増加させる)。その後ステップS17で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新し、ステップS18で処理を完了する。

【0113】

図29は、以上のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。図29の表記は図28の表記と同様である。図29(a)の状態では、比較器C1の閾値TH1は、下限値Lよりも高い位置にあり、比較器C1の出力(比較結果)は0になる場合がある。従って、比較器C1の閾値のデジタルコードは順次−1されて、図29(b)に示されるように徐々に閾値TH1が小さく(低く)なっていく。その後閾値TH1が更に低くなり図29(c)の状態になると、比較器C1の閾値TH1は下限値Lよりも低い位置になり、比較器C1の出力(比較結果)が常に1になる。このように比較器C1の出力が常に1になる状態となると、比較器C1の閾値のデジタルコードを+1することにより、図29(d)に示されるように閾値TH1を1ステップ上昇させる。この状態で処理を終了することにより、その時点でのTH1の位置(図29(d)に示す位置)が比較器C1の閾値の設定値となる。このように最後に閾値TH1を1ステップ上昇させて閾値設定することにより、図28(c)に示す状態と同様に、下限値Lより内側(上側)の位置に閾値TH1を設定することができる。

【0114】

図30は、上限値検出部136の構成の一例を示す図である。図30に示す上限値検出部136は、上限値検出部制御部151、出力値モニタ部152、比較器出力値保持部153、及び閾値更新部154を含む。上限値検出部制御部151は、図24の内部制御部131の制御の下で動作し、出力値モニタ部152及び閾値更新部154の動作を制御する。比較器出力値保持部153は、比較器C6の出力をサンプルし、サンプルしたC6出力を所定の期間保持する。なお比較器C6の出力は、入力アナログ電圧が比較器C6の閾値よりも低いときに0となり、入力アナログ電圧が比較器C6の閾値よりも高いときに1となる。出力値モニタ部152は、比較器出力値保持部153が保持する比較器C6の出力をモニタする。出力値モニタ部152によるモニタ結果に応じて、上限値検出部制御部151は、比較器C6の閾値更新処理を閾値更新部154に実行させる。具体的には、閾値更新部154は、閾値コード保持部135から比較器C6の閾値を受け取り、更新後の閾値を閾値コード保持部135に供給する。これらの動作により、比較器C6のコード入力を徐々に変化させながら、比較器C6による入力アナログ電圧と閾値との比較結果が0であるか1であるかを判定することにより、比較器C6の閾値を入力アナログ電圧の上限値近傍に設定する。

【0115】

図31は、比較器C6の閾値を設定する閾値設定動作の一例を示すフローチャートである。ステップS1で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS2で、モニタ期間として定めた一定期間中においてC6出力値が常に0であるか否かを出力値モニタ部152が判定する。判定結果がYesである場合、処理はステップS3に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−1する(即ち閾値を1ステップ減少させる)。ステップS4で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS5で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS6で、モニタ期間として定めた一定期間中においてC6出力値が常に0であるか否かを出力値モニタ部152が判定する。判定結果がYesである場合、処理はステップS7に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−1する(即ち閾値を1ステップ減少させる)。その後ステップS8で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新し、処理はステップS5に戻る。ステップS6での判定結果がNoである場合、即ち、モニタ期間として定めた一定期間中において1であるC6出力値が一度でも検出された場合、ステップS9に進みそのまま処理を終了する。

【0116】

図32は、以上のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。2つの○印が2つの比較器C6及びC5を表わし、○印の垂直方向の位置が各比較器に設定されている閾値の大きさTH6及びTH5を表わす。図32(a)から(c)へと時間が経過していき、閾値が変化していく様子が模式的に示されている。Uは、入力アナログ電圧の上限値の位置を示す。図32(a)の状態では、比較器C6の閾値TH6は、上限値Uよりも高い位置にあり、比較器C6の出力(比較結果)は常に0となる。従って、比較器C6の閾値のデジタルコードは順次−1されて、図32(b)に示されるように徐々に閾値TH6が小さく(低く)なっていく。その後閾値TH6が更に低くなり図32(c)の状態になると、比較器C6の閾値TH6は上限値Uよりも低い位置になり、比較器C6の出力(比較結果)が1になる場合が発生する。このように1であるC6出力値が検出された場合、処理を終了することにより、その時点でのTH6の位置(図32(c)に示す位置)が比較器C6の閾値の設定値となる。

【0117】

図31に戻り、ステップS2での判定結果がNoである場合、即ちモニタ期間として定めた一定期間中において1であるC6出力値が一度でも検出された場合、処理はステップS10に進む。ステップS10で、閾値更新部154が比較器C6の閾値のデジタルコードを+1する(即ち閾値を1ステップ増加させる)。ステップS11で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS12で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS13で、モニタ期間として定めた一定期間中においてC6出力値が常に0であるか否かを出力値モニタ部152が判定する。ステップS13での判定結果がNoである場合、即ちモニタ期間として定めた一定期間中において1であるC6出力値が一度でも検出された場合、処理はステップS14に進む。ステップS14で、閾値更新部154が比較器C6の閾値のデジタルコードを+1する(即ち閾値を1ステップ増加させる)。ステップS15で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。その後処理はステップS12に戻り、以降の処理を繰り返す。ステップS13での判定結果がYesである場合、処理はステップS16に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−1する(即ち閾値を1ステップ減少させる)。その後ステップS17で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新し、ステップS18で処理を完了する。

【0118】

図33は、以上のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。図33の表記は図32の表記と同様である。図33(a)の状態では、比較器C6の閾値TH6は、上限値Uよりも低い位置にあり、比較器C6の出力(比較結果)は1になる場合がある。従って、比較器C6の閾値のデジタルコードは順次+1されて、図33(b)に示されるように徐々に閾値TH6が大きく(高く)なっていく。その後閾値TH6が更に高くなり図33(c)の状態になると、比較器C6の閾値TH6は上限値Uよりも高い位置になり、比較器C6の出力(比較結果)が常に0になる。このように比較器C6の出力が常に0になる状態となると、比較器C6の閾値のデジタルコードを−1することにより、図33(d)に示されるように閾値TH6を1ステップ下降させる。この状態で処理を終了することにより、その時点でのTH6の位置(図33(d)に示す位置)が比較器C6の閾値の設定値となる。このように最後に閾値TH6を1ステップ下降させて閾値設定することにより、図32(c)に示す状態と同様に、上限値Uより内側(下側)の位置に閾値TH6を設定することができる。

【0119】

図34は、両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。図34において、6つの○印が6つの比較器C1乃至C6を表わし、○印の垂直方向の位置が各比較器に設定されている閾値の大きさを表わす。図面左から右に向かい時間が経過していき、閾値が変化していく様子が模式的に示されている。この例では、閾値L0〜L4の間を4等分して、冗長比較器を除く5つの比較器の閾値をそれぞれL0,L1,L2,L3,L4に設定する場合について示してある。即ち、図5に示した場合と同様に、冗長な比較器を設けた構成の場合の動作が示されている。なお図4に示す場合と同様に冗長な比較器を設けない構成の場合、或いは図1に示す場合と同様に両端の比較器の閾値を更新する場合に対しても、図27及び図31に示す下限及び上限の閾値設定動作を適用してよい。

【0120】

図35は、両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。図34は、両端の比較器の閾値の初期位置が入力アナログ電圧の振幅の範囲外にある場合を示すのに対して、図35は、両端の比較器の閾値の初期位置が入力アナログ電圧の振幅の範囲内にある場合を示している。このように両端の比較器の閾値の初期位置に関わらず、適切な閾値設定動作を実現することができる。

【0121】

図36A及び図36Bは、比較器C1の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。ステップS1で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS2で、状態Aであるか否かを出力値モニタ部142が判定する。ここで状態Aとは、モニタ期間として定めた一定期間中においてC1出力値が常に1である状態である。判定結果がYesである場合、処理はステップS3に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+8する(増加させる)。ステップS4で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS5で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS6で、状態Bであるか否かを出力値モニタ部142が判定する。ここで状態Bとは、モニタ期間として定めた一定期間中において0であるC1出力値が一度でも検出される状態である。判定結果がNoである場合、処理はステップS3に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS7に進み、閾値更新部144が比較器C1の閾値のデジタルコードを−4する(減少させる)。ステップS8で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS9で、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0122】

ステップS10で、状態Aであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS7に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS11に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+2する(増加させる)。ステップS12で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS13で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS14で、状態Bであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS11に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS15に進み、閾値更新部144が比較器C1の閾値のデジタルコードを−1する(減少させる)。ステップS16で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS17で、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0123】

ステップS18で、状態Aであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS15に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS19に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(増加させる)。ステップS20で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。以上で処理を完了する。

【0124】

また図36AのステップS2での判定結果がNoである場合、処理は図36BのステップS22に進み、閾値更新部144が比較器C1の閾値のデジタルコードを−8する(減少させる)。ステップS23で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS24で、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0125】

ステップS25で、状態Aであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS22に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS26に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+4する(増加させる)。ステップS27で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS28で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS29で、状態Bであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS26に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS30に進み、閾値更新部144が比較器C1の閾値のデジタルコードを−2する(減少させる)。ステップS31で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS32で、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0126】

ステップS33で、状態Aであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS30に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS34に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(増加させる)。ステップS35で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS36で、比較器C1の出力値を比較器出力値保持部143に取り込む。ステップS37で、状態Bであるか否かを出力値モニタ部142が判定する。判定結果がNoである場合、処理はステップS34に戻り、以降の処理を繰り返す。判定結果がYesである場合、ステップS38で処理を完了する。

【0127】

図37は、図36A及び図36Bに示す閾値設定動作の一例を模式的に示す図である。○印が比較器C1を表わし、○印の垂直方向の位置が比較器C1に設定されている閾値の大きさを表わす。図37の左から右へと時間がT1からT9まで経過していき、閾値が変化していく様子が模式的に示されている。Lは、入力アナログ電圧の下限値の位置を示す。時間T1における初期状態において比較器C1の閾値は入力アナログ電圧の下限値Lよりも低い位置にあるが、2回続けて閾値のデジタルコードを+8することにより、時間T3で閾値は下限値Lよりも高くなっている。その後、−4の変化を2回、+2の変化を2回、−1の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T9に示す位置に設定される。

【0128】

図38は、図36A及び図36Bに示す閾値設定動作の別の一例を模式的に示す図である。図38における表記は、図37における表記と同様である。時間T1における初期状態において比較器C1の閾値は入力アナログ電圧の下限値Lよりも高い位置にあるが、2回続けて閾値のデジタルコードを−8することにより、時間T3で閾値は下限値Lよりも低くなっている。その後、+4の変化を1回、−2の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T6に示す位置に設定される。

【0129】

図39A及び図39Bは、比較器C6の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。ステップS1で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS2で、状態Dであるか否かを出力値モニタ部152が判定する。ここで状態Dとは、モニタ期間として定めた一定期間中において1であるC6出力値が一度でも検出される状態である。判定結果がYesである場合、処理はステップS3に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+8する(増加させる)。ステップS4で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS5で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS6で、状態Cであるか否かを出力値モニタ部152が判定する。ここで状態Cとは、モニタ期間として定めた一定期間中においてC6出力値が常に0である状態である。判定結果がNoである場合、処理はステップS3に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS7に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−4する(減少させる)。ステップS8で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS9で、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0130】

ステップS10で、状態Dであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS7に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS11に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+2する(増加させる)。ステップS12で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS13で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS14で、状態Cであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS11に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS15に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−1する(減少させる)。ステップS16で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS17で、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0131】

ステップS18で、状態Dであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS15に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS19に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+1する(増加させる)。ステップS20で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。以上で処理を完了する。

【0132】

また図39AのステップS2での判定結果がNoである場合、処理は図39BのステップS22に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−8する(減少させる)。ステップS23で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS24で、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0133】

ステップS25で、状態Dであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS22に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS26に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+4する(増加させる)。ステップS27で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS28で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS29で、状態Cであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS26に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS30に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−2する(減少させる)。ステップS31で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS32で、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0134】

ステップS33で、状態Dであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS30に戻り、以降の処理を繰り返す。判定結果がYesである場合、処理はステップS34に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+1する(増加させる)。ステップS35で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS36で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS37で、状態Cであるか否かを出力値モニタ部152が判定する。判定結果がNoである場合、処理はステップS34に戻り、以降の処理を繰り返す。判定結果がYesである場合、ステップS38で処理を完了する。

【0135】

図40は、図39A及び図39Bに示す閾値設定動作の一例を模式的に示す図である。○印が比較器C6を表わし、○印の垂直方向の位置が比較器C6に設定されている閾値の大きさを表わす。図40の左から右へと時間がT1からT9まで経過していき、閾値が変化していく様子が模式的に示されている。Uは、入力アナログ電圧の上限値の位置を示す。時間T1における初期状態において比較器C6の閾値は入力アナログ電圧の上限値Uよりも低い位置にあるが、2回続けて閾値のデジタルコードを+8することにより、時間T3で閾値は上限値Uよりも高くなっている。その後、−4の変化を2回、+2の変化を2回、−1の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T9に示す位置に設定される。

【0136】

図41は、図39A及び図39Bに示す閾値設定動作の別の一例を模式的に示す図である。図41における表記は、図40における表記と同様である。時間T1における初期状態において比較器C6の閾値は入力アナログ電圧の上限値Uよりも高い位置にあるが、2回続けて閾値のデジタルコードを−8することにより、時間T3で閾値は上限値Uよりも低くなっている。その後、+4の変化を1回、−2の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T6に示す位置に設定される。

【0137】

図36A及び図36B並びに図39A及び図39Bに示す閾値設定動作では、閾値調整の初期段階では比較的大きな変化幅で閾値を変化させ、その後徐々に変化幅を小さくしていき、最終的に最も小さな変化幅で閾値を変化させて細かな調整を行う。これにより、常に最小の変化幅(デジタルコードの±1)で閾値を変化させる図27や図31に示す閾値設定動作の場合と比較して、高速に閾値設定処理を完了することができる。

【0138】

図42は、比較器C1の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。ステップS1で、変数nを0に設定して、処理がスタートする。ステップS2で、比較器C16の出力値を比較器出力値保持部143に取り込む。ステップS3で、状態Aであるか否かを出力値モニタ部142が判定する。ここで状態Aとは、モニタ期間として定めた一定期間中においてC1出力値が常に1である状態である。判定結果がYesである場合、処理はステップS4に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+8/(2n)する(増加させる)。ステップS5で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS6で、nが3に等しいか否かを判定する。判定結果がNoの場合、処理はステップS7に進み、n=n+1としてステップS2に戻る。ステップS6の判定結果がYesの場合、ステップS8で、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0139】

ステップS3での判定結果がNoである場合、処理はステップS9に進み、閾値更新部144が比較器C1の閾値のデジタルコードを−8/(2n)する(減少させる)。ステップS10で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C1の閾値のデジタルコードを更新する。ステップS11で、nが3に等しいか否かを判定する。判定結果がNoの場合、処理はステップS12に進み、n=n+1としてステップS2に戻る。ステップS11の判定結果がYesの場合、ステップS8に進み、比較器C1の出力値を比較器出力値保持部143に取り込む。

【0140】

ステップS8に続いてステップS13で、状態Aであるか否かを出力値モニタ部142が判定する。判定結果がYesである場合、処理はステップS14に進み、閾値更新部144が比較器C1の閾値のデジタルコードを+1する(増加させる)。その後、ステップS15で処理を終了する。またステップS13の判定結果がNoである場合、処理はステップS15に進み、そのまま処理を終了する。

【0141】

図43は、図42に示す閾値設定動作の一例を模式的に示す図である。○印が比較器C1を表わし、○印の垂直方向の位置が比較器C1に設定されている閾値の大きさを表わす。図43の左から右へと時間がT1からT5まで経過していき、閾値が変化していく様子が模式的に示されている。Lは、入力アナログ電圧の下限値の位置を示す。時間T1における初期状態において比較器C1の閾値は入力アナログ電圧の下限値Lよりも低い位置にある。その初期位置から開始して、+8の変化を1回、+4の変化を1回、−2の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T5に示す位置に設定される。

【0142】

図44は、図42に示す閾値設定動作の別の一例を模式的に示す図である。図44における表記は、図43における表記と同様である。時間T1における初期状態において比較器C1の閾値は入力アナログ電圧の下限値Lよりも高い位置にある。その初期位置から開始して、−8の変化を1回、−4の変化を1回、−2の変化を1回、+1の変化を1回行うことにより、閾値の位置は時間T5に示す位置に設定される。

【0143】

図45は、比較器C6の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。ステップS1で、変数nを0に設定して、処理がスタートする。ステップS2で、比較器C6の出力値を比較器出力値保持部153に取り込む。ステップS3で、状態Cであるか否かを出力値モニタ部152が判定する。ここで状態Cとは、モニタ期間として定めた一定期間中においてC6出力値が常に0である状態である。判定結果がYesである場合、処理はステップS4に進み、閾値更新部154が比較器C6の閾値のデジタルコードを−8/(2n)する(減少させる)。ステップS5で、減少させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS6で、nが3に等しいか否かを判定する。判定結果がNoの場合、処理はステップS7に進み、n=n+1としてステップS2に戻る。ステップS6の判定結果がYesの場合、ステップS8で、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0144】

ステップS3での判定結果がNoである場合、処理はステップS9に進み、閾値更新部154が比較器C6の閾値のデジタルコードを+8/(2n)する(増加させる)。ステップS10で、増加させた閾値のデジタルコードにより閾値コード保持部135が保持する比較器C6の閾値のデジタルコードを更新する。ステップS11で、nが3に等しいか否かを判定する。判定結果がNoの場合、処理はステップS12に進み、n=n+1としてステップS2に戻る。ステップS11の判定結果がYesの場合、ステップS8に進み、比較器C6の出力値を比較器出力値保持部153に取り込む。

【0145】

ステップS8に続いてステップS13で、状態Cであるか否かを出力値モニタ部152が判定する。判定結果がYesである場合、処理はステップS14に進み、閾値更新部144が比較器C6の閾値のデジタルコードを−1する(減少させる)。その後、ステップS15で処理を終了する。またステップS13の判定結果がNoである場合、処理はステップS15に進み、そのまま処理を終了する。

【0146】

図45に示す閾値設定動作により、比較器C6の閾値を入力アナログ電圧の上限近傍に設定することができる。即ち、図43及び図44に模式的に示した比較器C1の場合の閾値設定動作の例と同様に、閾値の変化幅を8,4,2,1と順次小さくしていきながら、比較器C6の閾値を入力アナログ電圧の上限近傍に設定することができる。

【0147】

図42及び図45に示す閾値設定動作では、閾値調整の初期段階では比較的大きな変化幅で閾値を変化させ、その後徐々に変化幅を小さくしていき、最終的に最も小さな変化幅で閾値を変化させて細かな調整を行う。これにより、常に最小の変化幅(デジタルコードの±1)で閾値を変化させる図27や図31に示す閾値設定動作の場合と比較して、高速に閾値設定処理を完了することができる。

【0148】

図46は、閾値設定動作及び閾値更新動作の実行の仕方の別の一例を示す図である。図25に示す例では、初期設定ステップにおいて下端及び上端の閾値に対する閾値設定動作を実行し、その後、両端以外の閾値に対応する比較器の閾値を順次更新している。図46に示す例では、ステップI0での比較器C1の閾値設定動作、ステップI1での比較器C6の閾値設定動作、及びステップS0乃至S7での比較器C2乃至C5の閾値更新動作を並行して実行する。即ち、比較器C2乃至C5の閾値更新動作とは独立して並行に、例えば図27及び図31に示す閾値設定動作を継続的に実行することにより、両端の比較器C1及びC6の閾値を常に入力アナログ電圧の両端近傍に位置させることができる。

【0149】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【符号の説明】

【0150】

11〜16 比較器

20−1〜20−8 比較器

21 エンコーダ

22 制御回路

122 制御回路

【技術分野】

【0001】

本願開示は、一般に半導体集積回路に関し、詳しくは閾値設定可能な比較器を含む半導体集積回路、閾値設定方法、及び通信装置に関する。

【背景技術】

【0002】

全並列型あるいは直並列型AD(analog-to-digital)変換器においては、それぞれ異なる閾値を設定した複数の比較器に入力アナログ電圧を印加し、各比較器において入力アナログ電圧と閾値との比較を行なう。複数の比較器の出力はサーモメータコードとなり、この出力をエンコーダによりエンコードすることにより、電圧値を表現したバイナリコードに変換する。一般に、複数の比較器のそれぞれの閾値に相当する比較基準電圧を抵抗ラダーにより発生させ、各比較器に印加していた(例えば非特許文献1)。

【0003】

アナログ信号と比較基準電圧との電位差を判定する比較器には、素子バラツキに起因するオフセットバラツキが存在する。AD変換器の高速化のためには、比較器のトランジスタに短チャネル長素子を使った方が有利であるが、短チャネル長素子を用いると素子バラツキが大きくなり、結果としてオフセットバラツキが大きくなってしまう。オフセットバラツキをキャンセルするための一手法として、AD変換動作を実行する前に、前処理としてオフセットキャンセルを行う手法が報告されている(例えば非特許文献2)。しかしながらこの手法では、閾値を調整するための期間は、AD変換動作を実行できない。そこで、AD変換に必要な所定個数の比較器に加え、冗長な比較器を設け、所定個数の比較器を用いてAD変換動作を実行する一方で、冗長分の比較器の閾値をバックグラウンドにて調整する技術が報告されている(例えば非特許文献3)。閾値を調整後の比較器をAD変換用に切り換えて使用し、AD変換に使用していた比較器を冗長分に切り換えて閾値調整に回すことで、常時閾値調整しながらAD変換動作を実行することができる。また、抵抗ラダーを設けることなく、閾値をデジタル的に制御する機能を比較器に備えることにより、閾値を与える手法も報告されている(例えば非特許文献4)。電流が流れる抵抗ラダーを取り除くことで、消費電力を削減することができる。

【0004】

閾値をデジタル的に制御する機能を比較器に設けた場合、適切なデジタルコードを各比較器に設定することで、各比較器に適切な閾値を設定する。しかしながら、デジタルコードと実際の閾値との関係は、理想的な線形関係になく、デジタルコードを等間隔に設定しても閾値は等間隔とならない、という問題がある。即ち、ある所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。例えば、上記非特許文献4に開示されるAD変換では、オフチップでの手動作業により閾値の制御を行なっている。

【0005】

また複数の比較器の閾値のうちで上端と下端との閾値についても、入力アナログ電圧の電圧範囲の上限と下限とに対応した閾値に設定することが好ましい。しかしながら、デジタルコードと実際の閾値との関係には誤差があるために、デジタルコードを所定値に設定しても閾値を所望値に設定することにはならない、という問題がある。従って、複数の比較器の閾値のうちで上端と下端との閾値を適切な値に設定することが難しい、という問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−18008号公報

【特許文献2】特開2002−33663号公報

【特許文献3】特開2008−160593号公報

【非特許文献】

【0007】

【非特許文献1】Yasuhiko Fujita,Eiji Masuda, Shigemi Sakamoto, Tatsuo Sakaue, Yasushi Sato; A bulk CMOS 20MS/s7b flash ADC, IEEE International Solid-State Circuits Conference, vol. XXVII,pp. 56 - 57, February 1984

【非特許文献2】Yuko Tamba, Kazuo Yamakido; A CMOS 6b 500MSample/s ADC for a harddisk drive read channel, IEEE International Solid-State Circuits Conference,vol. XLII, pp. 324 - 325, February 1999

【非特許文献3】Sanroku Tsukamoto, Ian Dedic, Toshiaki Endo, Kazu-yoshi Kikuta,Kunihiko Goto, Osamu Kobayashi; A CMOS 6-b, 200 Msample/s, 3 V-supply A/Dconverter for a PRML read channel LSI, IEEE Journal of Solid-State Circuits,vol. 31, pp. 1831 - 1836, November 1996

【非特許文献4】Geert Van der Plas, Stefaan Decoutere, Stephane Donnay; A 0.16pJ/conversion-step 2.5mW 1.25GS/s 4b ADC in a90nm digital CMOS process, IEEE International Solid-State Circuits Conference,vol. XLIX, pp. 566 - 567, February 2006

【発明の概要】

【発明が解決しようとする課題】

【0008】

以上を鑑みると、複数の比較器に対して両端の閾値を適切な値に設定すると共にその間の閾値を等間隔に設定可能である半導体集積回路、閾値設定方法、及び通信装置が望まれる。

【課題を解決するための手段】

【0009】

半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、前記第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、前記第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、前記閾値設定動作により、前記第1及び第Nの比較器の閾値は、前記第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、それぞれ前記入力電圧の下限値近傍及び上限値近傍に設定され、前記閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定されることを特徴とする。

【0010】

閾値設定方法は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器のうちで、第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、前記第1及び第Nの比較器の閾値をそれぞれ前記入力電圧の下限値近傍及び上限値近傍に設定する段階と、前記第1乃至第Nの比較器のうちで、1<M<Nである第Mの比較器の閾値を前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定する動作を、1<M<Nである全ての第Mの比較器に対して実行する第1の段階と、前記第1の段階を複数回繰り返す第2の段階とを含むことを特徴とする。

【0011】

通信処理部とAD変換器とを含む通信装置において、前記AD変換器は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、前記第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、前記第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、前記閾値設定動作により、前記第1及び第Nの比較器の閾値は、前記第1及び第Nの比較器による前記入力電圧と閾値との比較結果に応じて、それぞれ前記入力電圧の下限値近傍及び上限値近傍に設定され、前記閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、前記第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定されることを特徴とする。

【発明の効果】

【0012】

本願開示の少なくとも1つの実施例によれば、複数の比較器に対して両端の閾値を適切な値に設定すると共に、その間の閾値を等間隔に設定することができる。

【図面の簡単な説明】

【0013】

【図1】比較器の閾値を等間隔に設定する方法の一例を模式的に示す図である。

【図2】比較器の閾値が順番に並んでいない初期状態を模式的に示す図である。

【図3】複数の比較器の端の部分における閾値間距離の変化について説明するための図である。

【図4】比較器の両端の閾値を固定状態とした場合を示す図である。

【図5】冗長な比較器を設けた場合の閾値設定方法を模式的に示す図である。

【図6】入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。

【図7】エンコーダの一例を示す図である。

【図8】図7の比較器及びエンコーダの動作のタイミングを示すタイミングチャートである。

【図9】制御回路による冗長比較器の閾値更新を説明するための図である。

【図10】比較器の閾値の更新動作のタイミングの一例を示すタイミングチャートである。

【図11】AD変換器の複数の比較器の更新動作の流れを示すフローチャートである。

【図12】比較器の一例を示す図である。

【図13】制御信号を生成する回路の一例を示す図である。

【図14】信号遷移速度を制御信号により制御可能なインバータの一例を示す図である。

【図15】信号遷移速度を制御信号により制御可能なインバータの別の一例を示す図である。

【図16】図12の比較器の動作の一例を示す図である。

【図17】比較器の別の一例を示す図である。

【図18】図17の比較器の動作の一例を示す図である。

【図19】通信装置の一例を示す図である。

【図20】制御回路による冗長比較器の閾値更新を説明するための図である。

【図21】閾値設定方法の計算機シミュレーションの結果を示す図である。

【図22】閾値設定方法の別の計算機シミュレーションの結果を示す図である。

【図23】入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。

【図24】制御回路の構成の一例を示す図である。

【図25】初期設定処理としての閾値設定動作及びその後の設定処理としての閾値更新動作の一例を示す図である。

【図26】下限値検出部の構成の一例を示す図である。

【図27】比較器C1の閾値を設定する閾値設定動作の一例を示すフローチャートである。

【図28】図27のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。

【図29】図27のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。

【図30】上限値検出部の構成の一例を示す図である。

【図31】比較器C6の閾値を設定する閾値設定動作の一例を示すフローチャートである。

【図32】図31のステップS3乃至S9の処理による閾値設定動作を模式的に示す図である。

【図33】図31のステップS10乃至S18の処理による閾値設定動作を模式的に示す図である。

【図34】両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。

【図35】両端の比較器の閾値を設定すると共にその他の比較器の閾値を等間隔に設定する様子を模式的に示す図である。

【図36A】比較器C1の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図36B】比較器C1の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図37】図36A及び図36Bに示す閾値設定動作の一例を模式的に示す図である。

【図38】図36A及び図36Bに示す閾値設定動作の別の一例を模式的に示す図である。

【図39A】比較器C6の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図39B】比較器C6の閾値を設定する閾値設定動作の別の一例を示すフローチャートである。

【図40】図39A及び図39Bに示す閾値設定動作の一例を模式的に示す図である。

【図41】図39A及び図39Bに示す閾値設定動作の別の一例を模式的に示す図である。

【図42】比較器C1の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。

【図43】図42に示す閾値設定動作の一例を模式的に示す図である。

【図44】図42に示す閾値設定動作の別の一例を模式的に示す図である。

【図45】比較器C6の閾値を設定する閾値設定動作の更に別の一例を示すフローチャートである。

【図46】閾値設定動作及び閾値更新動作の実行の仕方の別の一例を示す図である。

【発明を実施するための形態】

【0014】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0015】

図1は、比較器の閾値を等間隔に設定する方法の一例を模式的に示す図である。図1において、5つの○印が5つの比較器11乃至15を表わし、○印の水平方向の位置が各比較器に設定されている閾値の大きさを表わす。図面上から下に向かい時間が経過していき、閾値が変化していく様子が模式的に示されている。この例では、閾値0〜4の間を4等分して、5つの比較器11乃至15の閾値をそれぞれ0,1,2,3,4に設定する場合について示してある。

【0016】

閾値の範囲及び閾値間の間隔は、説明を簡単にするための一例に過ぎず、これに限定されるものではない。閾値の下端は0以外の数値であってよく、上端は4以外の数値であってよい。また4等分以外の数に等分してもよい。なお所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。従って、下端の閾値及び上端の閾値をそれぞれ0及び4に設定できるとは限らない。以下において、取り敢えずは、下端の閾値及び上端の閾値を適切な値(図1の例であれば閾値0及び4)に設定できると仮定して、その間を等分(図1の例であれば4等分)する場合について説明を進める。このようにしてまずは下端の閾値と上端の閾値との間を等分する閾値を設定する方法について説明し、その後に、下端の閾値及び上端の閾値を適切な値に設定する方法について説明する。

【0017】

図1に示す閾値設定方法では、比較器11乃至15の閾値を所定の条件に従い増減を繰り返していくことにより、閾値を徐々に位置を移動させ、閾値間の間隔が略等間隔となるように調整する。まず、第1乃至第5の比較器11乃至15のうち、1<M<5である第Mの比較器(即ち両端以外の比較器)に着目し、この第Mの比較器の閾値をTHMとする。また第M+1の比較器の閾値をTHM+1とする。このとき、第M+1の比較器と第Mの比較器との間の閾値差はTHM+1−THMである。図1において、例えばM=3として、第4の比較器14と第3の比較器13との間の閾値差TH4−TH3は、図示する距離b3である。まずこの状態において、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する。例えば第3の比較器13の場合であれば、b3をr倍(0<r<1)した距離だけ、第3の比較器13の閾値を増加させる(右にずらす)ことで、閾値を更新する。同様の処理を、各比較器11乃至14に対して実行する。比較器15の閾値については、上端の閾値4に設定することにより、上端の閾値4に拘束する。この動作により、最初の状態において各比較器11乃至15間の閾値差(閾値間距離)がb1乃至b4であったのが、閾値差b1’乃至b4’に変化する。以上の動作を、第1の更新動作とする。

【0018】

この変化後の状態において、第M−1の比較器と第Mの比較器とに着目する。これらの比較器の閾値差はTHM−1−THMである。図1において、例えばM=3として、第2の比較器12と第3の比較器13との間の閾値差TH2−TH3の絶対値は、図示する距離b2’である。この状態において、負の値である(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する。第3の比較器13の場合であれば、b2’をr倍(0<r<1)した距離だけ、第3の比較器13の閾値を減少させる(左にずらす)ことで、閾値を更新する。同様の処理を、各比較器12乃至15に対して実行する。比較器11の閾値については、下端の閾値0に設定することにより、下端の閾値0に拘束する。以上の動作を、第2の更新動作とする。

【0019】

上記の第1の更新動作と第2の更新動作とを、交互に複数回実行する。この際、第1の比較器11の閾値は、1回おきに0に設定されるので、常に0近傍に拘束されることになる。また第5の比較器15の閾値は、1回おきに4に設定されるので、常に4近傍に拘束されることになる。なお最初に実行するのは第1の更新動作ではなく第2の更新動作であってもよい。また、図1の例では、初期状態において、比較器11乃至15の閾値が比較器の番号順に従って順番に並んでいるが、これに限定されることはない。即ち比較器11乃至15の閾値が順番に並んでおらず、初期状態において、例えば第3の比較器13の閾値が第4の比較器14の閾値よりも大きくてもよい。

【0020】

図2は、比較器11乃至15の閾値が順番に並んでいない初期状態を模式的に示す図である。図2では、図1の表現方式と異なり、横方向に比較器の番号をとり、縦方向に閾値の値をとっている。図2に示す例では、第3の比較器13の閾値が第4の比較器14の閾値よりも大きくなっている。この場合、第3の比較器13の閾値を基準点とした第4の比較器14の閾値との閾値差b3は、負の値となる。従って、r・b3を加えることにより、第3の比較器13の閾値は減少する方向に更新される。この時、他の比較器については、閾値が増加する方向に更新される。

【0021】

図1に戻り、第1の更新動作において、第1の比較器11の閾値はr・b1だけ増加し、第2の比較器12の閾値はr・b2だけ増加する。閾値間距離b1に着目すると、r・b1だけ狭まり、r・b2だけ広がることになる。即ち、b1はr(b2−b1)だけ変化する。同様にして、b2はr(b3−b2)だけ変化し、b3はr(b4−b3)だけ変化する。b4については、初期状態の第5の比較器15の閾値を4−r・INとすれば、r(IN−b3)だけ変化する。第2の更新動作において、第1の比較器11の閾値はr・b1となっているので、b1はr(b1−b1’)だけ変化する。またb2はr(b1’−b2’)だけ変化し、b3はr(b2’−b3’)だけ変化し、b4はr(b3’−b4’)だけ変化する。

【0022】

例えば、b2に着目した場合、第1の更新動作によりb2はr(b3−b2)だけ変化するので、b2>b3であれば、b2は狭まる。またb2>b1であり、この大小関係が第1の更新動作後も続くのであれば、第2の更新動作によりb2’はr(b1’−b2’)だけ変化するので、b2’は狭まる。従って、着目閾値間距離は、その両側の閾値間距離よりも長い状態である間は、更新動作により狭まっていくことになる。同様にして、着目閾値間距離は、その両側の閾値間距離よりも短い状態である間は、更新動作により広がっていくことになる。これらのことをまとめれば、着目閾値間距離は、その両側の閾値間距離よりも長い又は短い状態である間は、更新動作により両側の閾値間距離に近づくように更新される。

【0023】

またb1<b2<b3の大小関係が続く限りは、第1の更新動作によりb2はr(b3−b2)だけ変化し広くなり、第2の更新動作によりb2’はr(b1’−b2’)だけ変化して狭くなる。仮にb1とb3とが変化しないと仮定すると、安定状態ではr(b3−b2)とr(b1−b2)とが等しくなるので、b2はb3及びb1との平均値となる。実際にはb1とb3とが変化するが、この場合も、b2はb3及びb1との平均値に向かい近づくように更新されていく。

【0024】

上述のように着目閾値間距離は、その両側の閾値間距離よりも長い又は短い状態である間は、更新動作により両側の閾値間距離に近づくように更新される。そして更に、着目閾値間距離は、両側の閾値間距離の間にある状態では、更新動作により両側の閾値間距離の平均に近づくように更新される。これらの特徴により、閾値間距離は、端から端まで、直線上に増加する、直線上に減少する、又は一定値であるの何れかの形に近づく方向に変化していくことが分かる。

【0025】

図3は、複数の比較器の端の部分における閾値間距離の変化について説明するための図である。図3は、図1に示す模式図の左端を着目して示しており、左端の閾値間距離b1がb1’更にはb1’’へと更新されていく様子を示している。ここで、

b1’=b1+r(b2−b1)

である。従って、b1’’は、

b1’’=b1’+r(b1−b1’)

=(1−r)b1’+rb1

=(1−r){b1+r(b2−b1)}+rb1

=b1+(r−r2)(b2−b1)

となる。ここでrは1より小さいので、(r−r2)は正である。従って、b2>b1であるならば、第1の更新動作及び第2の更新動作によりb1は広がる。逆に、b2<b1であるならば、第1の更新動作及び第2の更新動作によりb1は狭まる。従って、更新動作を繰り返していくことにより、b1がb2に等しくなる方向にb1の長さが変化していくことになる。

【0026】

b1とb2とが略等しい状態になった後において、第2の更新動作では、b2の長さは変化せずに略一定である。第1の更新動作では、b2はr(b3−b2)だけ変化するので、b3>b2であるならばb2は広がる。逆に、b3<b2であるならばb2は狭まる。従って、更新動作を繰り返していくことにより、b2がb3に等しくなる方向に変化していくことになる。

【0027】

このようにして、閾値を拘束されている左端から各閾値間距離が等しくなろうとする方向へ閾値間距離が変化していく。右端でも同様であり、閾値を拘束されている右端から各閾値間距離が等しくなる方向へ閾値間距離が変化していく。また前述のように、閾値間距離は、端から端まで、直線上に増加する、直線上に減少する、又は一定値であるの何れかの形に近づく方向に変化していく。従って、これらの変化の傾向が組み合わさり、最終的には、複数の閾値間距離が端から端まで一定の値である分布に近づいていく。即ち、比較器11乃至15の閾値が、下端閾値0から上端閾値4までの間に等間隔に並ぶような配置に近づいていく。

【0028】

なお第1の更新動作において、(THM+1−THM)のr倍をTHMに加えるように閾値更新をし、第2の更新動作において、(THM−1−THM)のr倍をTHMに加えるように閾値更新をする。この際、所望の閾値を設定するためのデジタルコードは、大まかなコード値としては分かっているが正確なコード値は不明な状態である。このことから、隣接する比較器の閾値(THM+1やTHM+1)の値は正確には分からないし、着目比較器の閾値(THM)も正確には分からない。そこで例えば実際に着目比較器で入力電圧と閾値との比較結果を求め、更に隣接する比較器により当該入力電圧と閾値との比較結果を求め、これらの比較結果を比較してよい。入力電圧を変えながら複数回比較して、着目比較器のコードを徐々に変化させていくことで、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断することができる。このときの着目比較器のコード入力と、着目比較器の元のコード入力との差分を求め、この差分をr倍した値を元のコード入力に加えるようにして、閾値を更新してよい。

【0029】

なお上記の閾値設定方法は、厳密な数式解を求めるような性質のものではないので、若干のずれがあっても繰り返し動作により所望の閾値配置に収束する。従って、例えば2つのコードの差分をr倍しても閾値差を正確にr倍したことにはならないが、一般に0<r<1である条件であればrの値に関わらず収束するので、特に問題はない。同様に、図1の閾値調整において、時間の経過とともにrが変化したとしても、所望の閾値配置に問題なく収束する。即ち、rは必ずしも最初から最後まで同一値でなくともよい。但し、図1に示す模式図において、ある一段の更新動作(例えばb1乃至b4をb1’乃至b4’に更新する初段の更新動作)及びその直後の段の更新動作においては、rを各比較器11乃至15に対して同一値にしておくことが好ましい。また例えば、ある比較器に対して閾値更新を繰り返す途中で、一時的に閾値更新を停止してしまっても、その後再開すれば最終的には問題なく所望の閾値に収束する。

【0030】

0<r<1である条件であればrの値に関わらず収束するが、一般的には、例えばr=0.1程度の値が好ましい。例えばrが0.9等の大きい値では、各比較器11乃至15の閾値が0.9程度の振幅で増減し続けることになる。所望の閾値の近辺で各比較器の閾値が振動するのであるが、その振動幅が大きいので、あるタイミングで閾値更新動作を終了させたときに、0.9の誤差が存在することになる。それに対してrが0.1等の小さい値の場合、各比較器11乃至15の閾値が0.1程度の振幅で増減し続けることになる。所望の閾値の近辺で各比較器の閾値が振動し、その振動幅が小さいので、あるタイミングで閾値更新動作を終了させたときに、各比較器の閾値は所望の閾値に近い値となっている。一般にAD変換動作では、0.5LSB以下の誤差(微分非直線性誤差)が求められるので、0<r<0.5が一般的には許容できる範囲である。但し上述のように、0<r<1であれば収束する(即ち安定的な定位置での振動となる)。なおrが例えば0.01のように小さすぎると、収束するまで(即ち安定的な定位置での振動となるまで)に時間がかかる、即ち膨大な回数の閾値更新動作であってもよい。従って、所望の精度と収束時間とを勘案して、適切なrの値を採用すればよい。

【0031】

図4は、比較器11乃至15の両端の閾値を固定状態とした場合を示す図である。この場合であっても、図1の場合と同様の設定方法により、比較器11乃至15の閾値を略等間隔に設定することができる。

【0032】

即ち、まず例えば、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する第1の更新動作を実行する。更に、(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する第2の更新動作を実行する。これら第1の更新動作と第2の更新動作とを交互に複数回実行することで、比較器11乃至15の閾値が、下端閾値0から上端閾値4までの間に等間隔に並ぶような配置に近づいていく。この場合、第1の比較器11の閾値を0に固定することで、0の近傍に拘束していることになる。また第5の比較器15の閾値を4に固定することで、4の近傍に拘束していることになる。

【0033】

なおこの場合、前述の場合と同様に、初期状態のb1及び第1の更新動作後のb1’に対して、第2の更新動作後のb1’’は、

b1’’=(1−r)b1’

=(1−r)(b1+r・b2)

=b1+r(b2−b1)

となる。従って前述の場合と同様に、更新動作を繰り返していくことにより、b1がb2に等しくなる方向にb1の長さが変化していくことになる。その他の動作については、図1の場合と同様である。

【0034】

図5は、冗長な比較器を設けた場合の閾値設定方法を模式的に示す図である。図5において、第6の比較器16が冗長な比較器として設けられている。図1に示す例では、AD変換動作には、5つの比較器11乃至15が設けられている。このような回路では、全ての比較器11乃至15についての閾値設定動作が終了して初めて、エンコーダにより比較器11乃至15の出力をエンコードする実際のAD変換動作を開始することができる。即ち、AD変換動作を実行しながら閾値の更新を行なうことができない。

【0035】

それに対して図5に示す回路では、AD変換動作を行う5個以上の比較器の一例として、比較器11乃至16の6つの比較器を設ける。初期状態では、第5の比較器15以外の残りの複数の比較器11,12,13,14,16により入力電圧とそれぞれの閾値とを比較した結果をエンコーダに供給してAD変換動作を実行する。そしてAD変換動作を実行しながら、エンコーダから切り離した状態である第5の比較器15に対して閾値の更新作業を実行する。第5の比較器15の閾値を更新すると、第5の比較器15をエンコーダに接続するとともに、残りの複数の比較器11乃至15のうちから選択した所望の比較器をエンコーダから切り離して閾値の更新を行なってよい。具体的には、第4の比較器14をエンコーダから切り離して、閾値更新の対象としてよい。この閾値更新の間は、比較器11,12,13,15,16の5つの比較器により、AD変換動作を実行することになる。

【0036】

図5に示す例でも、図1と同様に、(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する更新動作を実行する。具体的には、まず第5の比較器15の閾値TH5に、(TH4−TH5)を1より小さい正の実数倍した値を加えることにより、第5の比較器15の閾値を更新する。この場合の掛算の係数である1より小さい正の実数は、図1の場合の掛算の係数をrとすれば、(1−r)となる。これは、図5に示されるように、第5の比較器15の閾値を更新すると、閾値更新後の第5の比較器15により、第4の比較器14を置き換えるからである。閾値3の近傍の比較動作を実行すべき比較器は、更新動作に関わらず図1の例では第4の比較器14である。それに対して、図5の例では、閾値3の近傍の比較動作を実行すべき比較器は初期状態で第4の比較器14であり、その後第5の比較器15に置き換わり、その後更に第4の比較器14に置き換わり、というように比較器14と15とに交互に置き換わる。図5において、点線で示す矢印が、各比較器の実際の閾値の変化を示す。実線で示す矢印は、所定の閾値近傍の比較動作を実行すべき比較器の置き換わりの推移を示す。

【0037】

第5の比較器15により置き換えられた第4の比較器14は、エンコーダから切り離され、閾値更新動作に供される。第4の比較器14の閾値更新が終了すると、閾値更新後の第4の比較器14により、第3の比較器13を置き換える。第4の比較器14により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。第3の比較器13の閾値更新が終了すると、閾値更新後の第3の比較器13により、第2の比較器12を置き換える。第2の比較器12は、エンコーダから切り離され、閾値更新動作に供される。この際、第2の比較器12の閾値TH2に、(TH1−TH2)を1より小さい正の実数倍した値を加えることにより、第2の比較器12の閾値を更新する。即ち、第2の比較器12の閾値を(1−r)・b1だけ減少させる(左に移動させる)ことにより、第2の比較器12の閾値を更新する。これにより、比較器11乃至16に対する一段の更新動作が終了する。なお両端の比較器11及び16については、それぞれ両端の閾値0及び4に固定しておいてよい。即ち、両端の閾値0及び4に拘束しておくことになる。また図5において、各段の更新処理開始時における冗長な比較器(エンコーダから切り離されている比較器)が黒丸で示されている。

【0038】

次の更新動作においては、図1と同様に、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより、第Mの比較器の閾値を更新する更新動作を実行する。具体的には、まず第2の比較器12の閾値TH2に、(TH3−TH2)を1より小さい正の実数倍した値を加えることにより、第2の比較器12の閾値を更新する。即ち、第2の比較器12の閾値を(1−r)・b2だけ増加させる(右に移動させる)ことにより、第2の比較器12の閾値を更新する。第2の比較器12の閾値更新が終了すると、閾値更新後の第2の比較器12により、第3の比較器13を置き換える。第2の比較器12により置き換えられた第3の比較器13は、エンコーダから切り離され、閾値更新動作に供される。以降同様にして、順次、比較器13乃至15の閾値を更新していく。

【0039】

図5の場合も図1の場合と同様に、例えば実際に着目比較器で入力電圧と閾値との比較結果を求め、更に隣接する比較器により当該入力電圧と閾値との比較結果を求め、これらの比較結果を比較してよい。入力電圧を変えながら複数回比較して、着目比較器のコードを徐々に変化させていくことで、両比較結果が所定の割合以上一致するときに、着目比較器と隣接比較器とで閾値が同一である、と判断することができる。このときの着目比較器のコード入力と、着目比較器の元のコード入力との差分を求め、この差分を(1−r)倍した値を元のコード入力に加えるようにして、閾値を更新してよい。

【0040】

図6は、入力電圧と閾値とをそれぞれ比較する複数の比較器を有する半導体集積回路の一例を示す図である。図6に示す半導体集積回路は全並列型或いは直並列型のAD変換器であり、複数の比較器20−1乃至20−8、エンコーダ21、及び制御回路22を含む。第1乃至第8の比較器20−1乃至20−8は、制御回路22からのデジタルコード入力により対応する閾値が設定される。なお図6には、説明の便宜上、シングルエンドであるAD変換器を示すが、差動信号のAD変換を行なう差動構成のAD変換器であってよい。

【0041】

比較器20−1乃至20−8は、それぞれ制御回路22から印加されたコードに対応する閾値が設定されている。比較器20−1乃至20−8は、入力アナログ電位VINを受け取り、入力アナログ電位VINとそれぞれの閾値とを比較して、その比較結果を出力する。各比較器は、入力アナログ電位VINが内部設定された閾値よりも大きければ出力を1とし、入力アナログ電位VINが内部設定された閾値以下であれば出力を0とする。適切な閾値が設定されている状態では、比較器20−1乃至20−8の出力は、“00001111”のように下位の比較器出力が“1”であり、途中の比較器以降の出力が“0”となるサーモメータ(温度計)コードとなる。なお比較器20−1乃至20−8のうちの1つは前述の冗長な比較器であり、制御回路22によりエンコーダ21から切り離され、閾値更新動作に供される。残りの7つの比較器の出力に基づいて、エンコーダ21が符号化を実行し、3ビットのバイナリコードDoutとして出力する。なお図6に示す例では、説明の便宜上、AD変換結果が3ビットの場合を示すが、AD変換器の出力ビット数は3ビットに限定されるものではなく、任意のビット数であってよい。

【0042】

図7は、エンコーダ21の一例を示す図である。図7に示すエンコーダ21は、スイッチ回路31、2入力のうち一方が負論理入力の複数のORゲート32、ワイアードOR回路33、スイッチ回路34、及びフリップフロップ回路35を含む。スイッチ回路31は、7つの同一の構造のスイッチを含む。各スイッチは、比較器20−1乃至20−8のうちの隣接する2つの比較器の出力を受け取り、何れか一方の出力を選択して次段のORゲート32に供給する。この際、下位側のスイッチが隣接する2つの比較器の下位側の比較器の出力を選択し、上位側のスイッチが隣接する2つの比較器の上位側の比較器の出力を選択することで、境界部分にある比較器をエンコーダ21内部から切り離すことができる。図7に示す例では、比較器20−1乃至20−8のうち第3の比較器20−3がエンコーダ21内部から切り離されている。スイッチ回路31の接続状態を制御するスイッチ制御信号φselは、図6の制御回路22から供給される。

【0043】

ORゲート32は、2入力のうち下位側の比較器からの入力が反転されて入力される。従って、サーモメータコードの1と0との境界位置におけるORゲート32の出力が0となり、それ以外のORゲート32の出力は1となる。図7の例では、下位側から4番目のORゲート32の出力が0となり、サーモメータコードの1と0との境界位置を検出している。ワイアードOR回路33は、8つのORゲート32の8本の出力線とフリップフロップ回路35の3本の入力線との交点のうち、図7に示される位置に設けられる。ワイアードOR回路33は、対応するORゲート32の出力が0であれば、フリップフロップ回路35の対応する入力線をグランド電位に接続する。フリップフロップ回路35の一本の入力線に着目したとき、この入力線には4つのワイアードOR回路33が接続されている。従って、これら4つのワイアードOR回路33が交点となる位置の4つのORゲート32の出力の何れか1つでも0になれば、この入力線の電位はLOWとなる。この回路により、8つのORゲート32の8つの出力のうちで値が0である出力の位置を3ビットに符号化し、符号化データD0’、D1’、D3’をフリップフロップ回路35に格納する。フリップフロップ回路35に格納した3ビットのデータは、エンコード結果D0、D1、D2として出力される。なおスイッチ回路34は、エンコードタイミングにおいて開放状態となる。スイッチ回路34は、リセットタイミングにおいて導通状態となり、フリップフロップ回路35の入力をグランドに接続してリセットする。フリップフロップ回路35及びスイッチ回路34の動作タイミングを制御するエンコード制御信号φencは、図6の制御回路22から供給される。

【0044】

図8は、図7の比較器20−1乃至20−8及びエンコーダ21の動作のタイミングを示すタイミングチャートである。リセットタイミングResetにおいて、図6の制御回路22から比較器20−1乃至20−8に供給される比較器制御信号φcmpがHIGHとなり、比較器20−1乃至20−8がリセットされる。またこのリセットタイミングResetにおいて、エンコード制御信号φencがHIGHとなり、スイッチ回路34が導通してフリップフロップ回路35の入力がグランドに接続される。即ち、フリップフロップ回路35の入力であるデータDn’(図7に示すD0’、D1’、D3’)が0にリセットされる。次に比較動作タイミングCompにおいて、比較器20−1乃至20−8に供給される比較器制御信号φcmpがLOWとなり、比較器20−1乃至20−8が比較動作を実行する。これにより、比較器20−1乃至20−8の出力Cmp_outが有効となる。またエンコード制御信号φencがLOWとなり、スイッチ回路34が非導通状態となることにより、フリップフロップ回路35の入力であるデータDn’が有効状態となる。このエンコード制御信号φencはフリップフロップ回路35にも供給されており、フリップフロップ回路35は、エンコード制御信号φencの立ち上がりエッジで入力データDn’を取り込む(ラッチする)。

【0045】

図9は、制御回路22による冗長比較器の閾値更新を説明するための図である。図9に示されるように、制御回路22は、2入力のうち下位側が負論理入力の複数のNORゲート40、2入力のうち上位側が負論理入力の複数のNORゲート41、及び制御ロジック回路43を含む。1つのNORゲート40と1つのNORゲート41とで一対をなし、一対のNORゲートの各々は、2つの比較器20−1乃至20−8のうちの隣接する2つの比較器の出力を受け取る。比較器20−1乃至20−8のうちの隣接する2つの比較器の組み合わせは、7つあるので、7対のNORゲートが設けられることになる。図9には図示の便宜上、第3及び第4の比較器20−3及び20−4に対する一対のNORゲートと、第4及び第5の比較器20−4及び20−5に対する一対のNORゲートとだけが示される。

【0046】

各比較器20−1乃至20−8の出力はエンコーダ21に供給されると共に、並行して制御回路22にも供給される。隣接する2つの比較器に対して設けられた一対のNORゲートは、入力電圧VINがこれら2つの比較器の2つの閾値よりも大きいか、小さいか、或いはその中間にあるか、に関する判定を行なう。以下において、図7で示した例と同様に、第3の比較器20-3が冗長比較器であり、この閾値の更新を実行する場合について説明する。

【0047】

第3の比較器20-3の閾値及び第4の比較器20-4の閾値の何れよりも入力電圧VINが低い場合、対応するNORゲート40の出力J+とNORゲート41の出力J−は、双方共に0となる。また第3の比較器20-3の閾値及び第4の比較器20-4の閾値の何れよりも入力電圧VINが高い場合も、対応するNORゲート40の出力J+とNORゲート41の出力J−は、双方共に0となる。このように出力J+と出力J−とが双方共に0の場合、制御ロジック回路43は何も実行しない。

【0048】

第3の比較器20-3の閾値及び第4の比較器20-4の閾値との間に入力電圧VINが有る場合には、第3の比較器20-3の閾値TH3と第4の比較器20-4の閾値TH4との大小関係に応じて、対応するNORゲートの出力J+及び出力J−が変化する。TH3<TH4である場合、第3の比較器20-3及び第4の比較器20-4の出力はそれぞれ1及び0となるので、NORゲート40の出力J+とNORゲート41の出力J−はそれぞれ1及び0となる。このとき、制御ロジック回路43は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1増加させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ増加させる。これにより、TH3がTH4に近づくことになる。逆に、TH3>TH4である場合、第3の比較器20-3及び第4の比較器20-4の出力はそれぞれ0及び1となるので、NORゲート40の出力J+とNORゲート41の出力J−はそれぞれ0及び1となる。このとき、制御ロジック回路43は、第3の比較器20-3に設定するデジタルコードDcnt(3)を1減少させることにより、第3の比較器20-3の閾値TH3を最小刻み幅だけ増加させる。これにより、TH3がTH4に近づくことになる。このようにして、AD変換器に入力される入力アナログ電圧VINと閾値との比較動作を逐次実行し、その比較結果に応じて、第3の比較器20-3の閾値を変化させていく。

【0049】

TH3とTH4とが等しくなると、入力アナログ電圧VINの値に関わらず、NORゲート40の出力J+とNORゲート41の出力J−とは、共に0になる。例えば、入力アナログ電圧VINと各閾値の比較動作を1000回行なったときに、1000回の比較動作の全てにおいて出力J+と出力J−とが、双方共に0になる。如何なるデジタルコードDcnt(3)を設定してもTH3とTH4とが完全に一致することが無い場合、即ち、各比較器の最小分解能に応じた差が常に存在する場合には、多数回の比較動作のうちで出力J+と出力J−とが異なる値となる場合が常に発生する。従って、例えば、1000回の比較動作において所定の割合以上(例えば99.5%以上)において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH4とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。同様に、所定の回数以上連続して出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、TH3とTH4とが実質的に等しくなったと判断して、TH3の更新動作を実行してよい。ここで更新動作の実行とは、TH3とTH4とが実質的に等しくなったときのデジタルコードと最初の状態のデジタルコードとの差を1より小さい正の実数倍した値を、最初の状態のデジタルコードに加えることである。これにより、(TH4−TH3)を1より小さい正の実数倍した値をTH3に加えることにより、第3の比較器の閾値を更新する更新動作を実行したことになる。

【0050】

TH3の更新動作が完了すると、第3の比較器20-3をエンコーダ21に接続し、第4の比較器20-4をエンコーダ21から切り離す。そして、第4の比較器20-4を冗長比較器として、第4の比較器20-4の閾値の更新を実行する。

【0051】

図10は、比較器の閾値の更新動作のタイミングの一例を示すタイミングチャートである。図10に示す比較器制御信号φcmpは、図8で説明した比較器制御信号と同一であり、比較器20−1乃至20−8のリセットタイミングと比較動作タイミングとを制御する。比較器制御信号φcmpがLOWのときに、各比較器により比較動作が実行され、各比較器の出力が有効(Valid)となる。図10に示す例では、最初にn番目の比較器を冗長比較器として、閾値更新処理の対象としている。n番目の比較器の出力としてCnが示されている。図9を参照して説明したように、制御回路22の制御ロジック回路43は、出力J+と出力J−とに応じて、n番目の比較器に供給するデジタルコードDcnt(n)を+1又は−1することにより、n番目の比較器の閾値Vthを変更する。図10に示す例では、比較器制御信号φcmpをクロックとしてクロックサイクルを考えた場合、出力J+と出力J−とに応じた閾値Vthの変更に、3クロックサイクルかかっている。この閾値Vthの変更を、比較動作の結果に応じて逐次実行する。なお前述のように、出力J+と出力J−とが双方共に0であれば、閾値Vthを変更しないで現状維持とする。複数回の比較動作において所定の割合以上において出力J+と出力J−とが0となる場合、即ち両比較結果が一致する場合に、n番目の比較器の閾値とn+1番目の比較器の閾値とが実質的に等しくなったと判断(即ち収束したと判断)してよい。これにより、図10に示すように、n番目の比較器のデジタルコードDcnt(n)を固定し、次のn+1番目の比較器のデジタルコードDcnt(n+1)の調整を開始する。

【0052】

図11は、AD変換器の複数の比較器の更新動作の流れを示すフローチャートである。図11の処理は、例えば図6に示す制御回路22により実行される。図11においては、AD変換器に設けられた比較器の全個数をmとしている。図6の場合で言えば、m=8となる。まずステップS1において、各比較器にデジタルコードを初期設定する。ここで、第1の比較器及び第mの比較器(即ち両端の比較器)については、例えば、それぞれ最小のデジタルコード及び最大のデジタルコードを設定してよい。それ以外の第2乃至第M−1の比較器については、デジタルコードの初期値は如何なる値でもよい。例えば、最小のデジタルコードから最大のデジタルコードまでの範囲を等間隔に分割するように、各デジタルコードの初期値を設定してよい。

【0053】

ステップS2において、変数Mを2に初期化する。この変数Mは、第M番目の比較器を指し示す変数である。ステップS3において、変数Mが比較器の全個数mに等しいか否かを判定する。等しくない場合には、ステップS4に進む。ステップS4において、図9を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。第M番目の比較器の閾値更新処理を完了すると、ステップS5において、変数M=M+1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS3に戻り、以降の処理を、次の比較器に対して実行する。

【0054】

ステップS3において、変数Mが比較器の全個数mに等しいと判定された場合、ステップS6に進む。ステップS6において、変数M=m−1とする。これは、端の比較器(第Mの比較器)については、閾値を固定としておくことに相当する。次にステップS7において、変数Mが1に等しいか否かを判定する。等しくない場合には、ステップS8に進む。ステップS8において、図9を参照して説明した閾値更新処理を第M番目の比較器に対して実行する。第M番目の比較器の閾値更新処理を完了すると、ステップS9において、変数M=M−1として、次の比較器を冗長比較器として閾値更新処理の対象とする。その後ステップS7に戻り、以降の処理を、次の比較器に対して実行する。

【0055】

ステップS7において、変数Mが1に等しいと判定された場合、ステップS2に進む。ステップS2において、変数M=2とする。これは、端の比較器(第1の比較器)については、閾値を固定としておくことに相当する。以降、ステップS2乃至S9の処理を同様にして繰り返す。

【0056】

このようにして、第1の比較器乃至第mの比較器から1つの比較器を冗長比較器として順次選択し、閾値更新処理の対象とする。この処理をAD変換器のAD変換動作を実行しながらバックグラウンドで実行することにより、AD変換動作と並行して比較器の閾値更新処理を実行することができる。

【0057】