半導体集積回路およびデータ漏洩防止方法

【課題】JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサにバス経由でメモリが接続されるケースにおいて、メモリに保持されたプログラムやデータの読み出し保護を行う。

【解決手段】制御部1(バス出力部142)は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、バス(アドレスバス15またはデータバス16)に対して所定のデータを出力し、この所定のデータと、メモリ(外付けフラッシュROM12または外付けRAM13)に保持されてバスに出力されるデータとが衝突することで、バスを伝搬するデータが破壊されて不定になる。

【解決手段】制御部1(バス出力部142)は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、バス(アドレスバス15またはデータバス16)に対して所定のデータを出力し、この所定のデータと、メモリ(外付けフラッシュROM12または外付けRAM13)に保持されてバスに出力されるデータとが衝突することで、バスを伝搬するデータが破壊されて不定になる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体集積回路およびデータ漏洩防止方法に係り、特に、パワーエレクトロニクス技術を応用した電力変換装置の制御装置等の組込みシステムにおいて、プログラムやデータ等の知的財産保護に用いて好適な技術に関する。

【背景技術】

【0002】

最近の電力変換装置の制御装置等、組込みシステムに使用されるマイクロプロセッサでは、JTAG(Joint Test Action Group)を使用したインタフェースをデバック機能として搭載することが主流になっている。

【0003】

ところで、PC(Personal Computer)等、汎用のコンピュータシステムは勿論のこと、組込みシステムにおいても知的財産であるプログラムやデータ等、ソフトウェアの保護は重要な設計事項になっている。しかしながら、上記したJTAGインタフェースを用いると、半導体集積回路に内蔵されたフラッシュROMや内蔵RAMに保持されるプログラムやデータを自由に読みだすことが出来る。

【0004】

図6に、マイクロプロセッサ100aに、外付けフラッシュROM120と外付けRAM130が、アドレスバス150とデータバス160経由で接続され、使用される、一般的な組込みシステム(制御装置100)の構成を示す図である。JTAG−ICE(In Circuit Emulator)等のデバッガ200は、JTAGポート110を介してマイクロプロセッサ100aに接続される。

【0005】

ソフトウェアの保護機能を持たない制御装置100の場合、外付けフラッシュROM120には、暗号化ソフトウェアと、この暗号化ソフトウェアを解読するための復号化ソフトウェアとが保持されている。この理由は、第三者がPt板に半田付けされた外付けフラッシュROM120をシステムから取り外し、不図示のフラッシュROMライタ等により保持されたこれらソフトウェアが読み出されることを防ぐためである。

【0006】

マイクロプロセッサ100aは、リセット解除後の初期化処理の過程で、外付けフラッシュROM120に保持された復号化ソフトウェアを使用して暗号化されたソフトウェアを暗号化前の元のソフトウェアに変換し、外付けRAM130に保持する処理を行う。マイクロプロセッサ100aは、上記した処理の後、外付けRAM130に保持された暗号化前のソフトウェアを使用して組込みシステムが持つ本来の処理を行う。

【0007】

従来、第三者によるJTAGインタフェースを介したプログラムやデータの読み出しが出来ないような仕組みが開発され、多数特許出願されている。例えば、特許文献1には、内蔵フラッシュROMにセキュリティビットを設け、このセキュリティビットをONすることでJTAGインタフェースの機能を禁止してフラッシュROMに保持されたプログラムの読出しが出来ない仕組みが開示されている。また、特許文献2には、JTAGインタフェースにICE等のデバッグ機器が接続されているときは、内蔵RAMのアクセスを禁止することで内蔵RAMに保持されたプログラムの読み出しが出来ない仕組みが開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−32267号公報

【特許文献2】特開2009−25907号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記した電力変換装置に使用される組込みシステムにおいても、最近ではソフトウェアの容量が大規模化し、マイクロプロセッサに外付けフラッシュROMや外付けRAM等を使用するケースが多くなって来ている。この組込みシステムにおいてもプログラムやデータの保護が重要になって来ているが、JTAGインタフェースからプログラムやデータの読み出しを防止する対象は、特許文献1や特許文献2に開示されているように、マイクロプロセッサに内蔵されたフラッシュROMやRAMに保持されたものであり、外付けフラッシュROMや外付けRAM等の外付けメモリに保持されたものではない。

【0010】

また、マイクロプロセッサに外付けメモリを接続して使用する場合、フラッシュROMを内蔵しないマイクロプロセッサを使用することも多い。そのようなマイクロプロセッサでもJTAGインタフェースが搭載されたものは多いが、JTAGインタフェースを介して外付けメモリに保持されたプログラムやデータの漏洩を防止する機能を持つものは存在しなかった。

【0011】

本発明は上記した課題を解決するためになされたものであり、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサにバス経由でメモリが接続されるケースにおいても、メモリに保持されたプログラムやデータの読み出し保護が可能な、半導体集積回路およびソフトウェア漏洩防止方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記した課題を解決するために本発明の第1の観点に係る半導体集積回路は、プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、を備えることを特徴とする。

【0013】

本発明の第1の観点に係る半導体集積回路によれば、バス出力部が、デバッガが接続されたことを示す接続検出信号と、マイクロプロセッサからのアクセス制御信号が共に有効である場合に、バスに対して所定のデータを出力する。このため、所定のデータと、メモリに保持されバスに出力されるデータとが衝突することでバスを伝搬するデータが破壊されて不定になるため、マイクロプロセッサにバス経由で接続されるメモリに保持されたプログラムやデータの読み出し保護が可能になる。

本発明の第1の観点に係る半導体集積回路において、前記バスは複数ビットで構成されるパラレルバスであり、前記ブレークデータは、隣接するビットが異なる値であることを特徴とする。

【0014】

本発明の第1の観点に係る半導体集積回路において、前記バスは、アドレスバス、もしくはデータバスであることを特徴とする。

本発明の第1の観点に係る半導体集積回路において、前記バス出力部は、電流抑制手段を介して前記バスに接続されることを特徴とする。

【0015】

本発明の第1の観点に係る半導体集積回路において、前記接続検出部または前記バス出力部は、所定の言語でプログラムされたプログラムブルロジックデバイスで構成されることを特徴とする。

【0016】

本発明の第1の観点に係る半導体集積回路において、前記バス出力部は、自らが選択されるセレクトポートと、前記アクセス制御信号を受信する制御ポートと、前記セレクトポートおよび前記アクセス制御信号の両方が有効になることにより前記ブレークデータを出力する出力ポートと、を有する記憶手段で構成され、前記接続検出信号を前記セレクトポートに接続し、前記制御信号を前記制御ポートに接続し、前記出力ポートを前記バスに接続することを特徴とする。

【0017】

本発明の第1の観点に係る半導体集積回路において、前記接続検出部は、前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持したコマンドに基づき前記接続検出信号をオフするコマンド受信手段を備えることを特徴とする。本発明によれば、所定のコマンドを受信するとバスへの所定のデータの出力を阻止することで、プログラムやデータの保護が、メーカの保守要員によるデバッグ作業の妨げになることを回避することができる。

【0018】

本発明の第1の観点に係る半導体集積回路において、前記コマンドは、第1コマンドと第2コマンドとからなり、前記コマンド受信手段は、前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする。本発明によれば、第三者による試行錯誤に基づくコマンド送信の偶然の一致によるバスへの所定のデータの出力阻止を制御することができる。

【0019】

本発明の第2の観点に係る半導体集積回路は、プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するバス出力部と、を備えることを特徴とする。

【0020】

本発明の第2の観点に係る半導体集積回路によれば、バス出力部が、デバッガが接続されたときに接続検出部により出力される接続検出信号がオンのとき、マイクロプロセッサから出力されるメモリへのアクセス制御信号がオンされることでマイクロプロセッサにリセット信号を供給する。このため、マイクロプロセッサは、リセット信号を受信する毎に初期化され、都度初期ルーチンから起動されるため、連続してプログラムが読み込まれることが無くなり、プログラム保護に有効な手段として提供することが出来る。

【0021】

本発明の第3の観点に係る半導体集積回路は、プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、を備えることを特徴とする。

【0022】

本発明の第3の観点に係る半導体集積回路によれば、バス出力部は、デバッガが接続されたときに接続検出部により出力される接続検出信号がオンのとき、マイクロプロセッサから出力される不揮発性メモリまたは揮発性メモリへのアクセス制御信号がオンされることでバスにブレークデータを出力し、このブレークデータとアクセス制御信号のオンに伴って不揮発性メモリまたは揮発性メモリがバスに出力するデータとを衝突させ、バスに伝搬するデータを不定にする。したがって、マイクロプロセッサにバス経由で接続される揮発性メモリに保持された不揮発性メモリの少なくとも一部写しであるプログラムやデータの保護が可能になる。

【0023】

本発明の第4の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩防止方法であって、前記接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にする第2のステップと、を有することを特徴とする。

【0024】

本発明の第4の観点に係るデータ漏洩防止方法において、前記第1のステップには、前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持されたコマンドに基づき前記接続検出信号をオフする第1のサブステップを含むことを特徴とする。

【0025】

本発明の第4の観点に係るデータ漏洩防止方法において、前記コマンドは、第1コマンドと第2コマンドとからなり、前記第1のサブステップにおいて、前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする。

【0026】

本発明の第5の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩方法であって、前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するステップと、を有することを特徴とする。

【0027】

本発明の第6の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路におけるデータ漏洩防止方法であって、前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするステップと、を有することを特徴とする。

【発明の効果】

【0028】

本発明によれば、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサにバス経由でメモリが接続され、使用するケースにおいても、メモリに保持されたプログラムやデータの読み出し保護が可能な、半導体集積回路およびソフトウェア漏洩防止方法を提供することができる。

【図面の簡単な説明】

【0029】

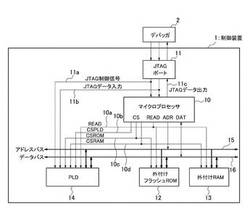

【図1】本発明の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】本発明の実施の形態に係る半導体集積回路のバス出力部の内部構成の一例を示すブロック図である。

【図3】本発明の実施の形態に係る半導体集積回路において、デバッガが接続されていない場合の動作を示すタイミング図である。

【図4】本発明の実施の形態に係る半導体集積回路において、デバッガが接続された場合の動作を示すタイミング図である。

【図5】本発明の実施の形態に係る半導体集積回路のバス出力部の内部構成の他の例を示すブロック図である。

【図6】一般的な組み込みシステムの構成を示すブロック図である。

【発明を実施するための形態】

【0030】

以下、添付図面を参照して本発明を実施するための実施の形態(以下、単に本実施形態という)について詳細に説明する。

(実施形態の構成)

図1は、本実施形態に係る半導体集積回路の構成を示すブロック図である。ここでは、半導体集積回路として、電力変換装置の制御装置1等の組み込みシステムを例示して説明する。

【0031】

図1に示されるように、制御装置1は、マイクロプロセッサ10と、JTAGポート11と、外付けフラッシュROMと、外付けRAM13と、PLD(Programmable Logic Device)14と、を含み構成される。PLD14を除けば、図6に示した一般的な組み込みシステムと同様の構成を有する。すなわち、マイクロプロセッサ10に、外付けフラッシュROM12と外付けRAM13が、アドレスバス15とデータバス16経由で接続されており、また、JTAG−ICE等のデバッガ2は、接続部(コネクタ)であるJTAGポート11を介してマイクロプロセッサ10に接続されている。

【0032】

PLD14は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号(READまたはWRITEであって、ここではメモリの読み出しを保護するためREADを対象とする)が共に有効である場合に、アドレスバス15またはデータバス16に対して所定のデータを出力する機能を有するプログラムロジックデバイスである。このため、所定のデータとして用いられるブレークデータと、メモリ(外付けフラッシュROM12、外付けRAM13)に保持され、バスに出力される出力データとが衝突することで、アドレスバス15またはデータバス16を伝搬する出力データが破壊されて不定になる。したがって、マイクロプロセッサ10にバス経由で接続される不揮発性フラッシュROM12や外付けRAM13に保持されたプログラムを含むデータの保護が可能になる。

【0033】

なお、ここで、デバッガ2を介してマイクロプロセッサ10による読出しを防止して保護する対象は、外付けRAM13に保持された暗号化前のプログラム、外付けフラッシュROM12に保持された暗号化プログラム、あるいは不図示のLSIが内蔵するレジスタ(揮発性メモリ)に保持されたデータを含むものとする。

【0034】

このため、PLD14は、マイクロプロセッサ10とは、アドレスバス15、データバス16経由で接続されると共に、マイクロプロセッサ10から、外付けフラッシュROM12または外付けRAM13のアクセス制御信号であるリード信号(READ)をライン10a経由で、自身のチップセレクト信号(CSPLD)をライン10b経由で、外付けフラッシュROM12のチップセレクト信号(CSROM)をライン10c経由で、外付けRAM13のチップセレクト信号(CSRAM)をライン10d経由でそれぞれ取得する。また、JTAGポート11から、JTAG制御信号、JTAGデータを、それぞれライン11a、11b経由で取得する。

【0035】

なお、ライン11a経由で取得されるJTAG制御信号は、ライン11b経由で取得されるJTAGデータ、およびマイクロプロセッサ10からJTAGポート11に出力されるJTAGデータと共に、IEEE1149.1で標準化されたJTAGインタフェースで定義された信号である。特に、JTAG制御信号の中には、TMS(Test Mode State)、TRST(Test Reset)等の信号が含まれ、PLD14は、それらの信号の状態や遷移から、JTAG−ICE等のデバッガ2の接続の有無を検出することができる。

【0036】

図2にPLD14の内部構成の一例が示されている。図2によれば、PLD14は、接続検出部141と、バス出力部142とを含み構成される。接続検出部141は、JTAGポート11から、ライン11a経由でJTAG制御信号を入力として得、ライン11b経由でJTAGデータを入力として得る。接続検出部141は、JTAGポート11にデバッガ2が接続されたことを検出すると、接続検出信号を有効にしてバス出力部142へ出力する。

【0037】

バス出力部142は、バス出力制御部142aと、アドレスバス出力部142bと、データバス出力部142cとを含み構成される。バス出力制御部142aは、マイクロプロセッサ10から、ライン10c経由でCSROM信号、ライン10b経由でCSRAM信号、ライン10a経由でアクセス制御信号であるREAD信号をそれぞれ取得し、READ信号がON(有効化)されたときに、同じく入力されるCSROM信号またはCSRAM信号に基づき、外付けフラッシュROM12または外付けRAM13を選択するように、アドレスバス出力部142b、およびデータバス出力部142cを制御するイネーブル信号を生成する。

【0038】

アドレスバス出力部142bは、ダンピング抵抗17aを介してアドレスバス15に接続されている。アドレスバス出力部142bは、ライン14b経由でバス出力制御部142aから出力されるイネーブル信号に基づき、選択された外付けフラッシュROM12、または外付けRAM13にアドレスデータを出力する。また、データバス出力部142cは、ダンピング抵抗17bを介してデータバス16に接続される。データバス出力部142cは、ライン14b経由でバス出力制御部142aから出力されるイネーブル信号に基づき、選択された外付けフラッシュROM12または外付けRAM13にデータを出力する。なお、ダンピング抵抗17a、17bは、ブレークデータと出力データとの衝突による電流を抑制し、不図示のドライバやレシーバ等、アドレスバス15やデータバス16周辺の素子の破損を防ぐために挿入される。

(実施形態の動作)

図3、図4は、本実施形態に係る半導体集積回路の動作を示すタイミング図であり、デバッガ2が未接続の場合、デバッガ2が接続された場合の、それぞれにおけるバス出力部142の動作を示す。図3、図4ともに、(a)はマイクロプロセッサ10から出力される外付けフラッシュROMのチップセレクト信号(CSROM)、(b)はマイクロプロセッサ10から外付けフラッシュROM12に対して出力されるアクセス制御信号(READ)、(c)はアドレスバス出力部142bの出力データ、(d)は、データバス出力部142cの出力データ、(e)はアドレスバス15を伝搬するアドレスデータ、(f)は、データバス16を伝搬するデータのそれぞれを示す。

【0039】

以下、図3、図4のタイミング図を参照しながら、図1、図2に示す本実施形態に係る半導体集積回路(制御装置1)の動作、特に、バス出力部142の動作について詳細に説明する。

【0040】

まず、図3のタイミング図を参照しながら、デバッガ2が未接続の場合の制御装置1の動作から説明する。この場合、接続検出部141から出力される接続検出信号はOFFになっているため、バス出力部142のバス出力制御部142aは、マイクロプロセッサ10からライン10a経由で取得されるREAD信号、ライン10c経由で取得されるCSROM信号、およびライン10b経由で取得されるCSRAM信号の状態に依存することなく、ライン14b経由でアドレスバス出力部142bとデータバス出力部142cに出力されるイネーブル信号をOFFにする。したがって、アドレスバス出力部142bとデータバス出力部142cは、ハイインピーダンス状態(Hi−Z)を維持する。

【0041】

この状態で、マイクロプロセッサ10が、外付けフラッシュROM12や外付けRAM13に対してREADアクセスを行った場合、アドレスバス15には、マイクロプロセッサ10が読み出したいアドレスデータが出力され、データバス16には、外付けフラッシュROM12や外付けRAM13の先のアドレスに該当するデータが出力される。このことにより、マイクロプロセッサ10が行うプログラムの読み出しやワーク変数の読出し等の読出し動作は正常に行われ、したがって、メーカの開発要員あるいは保守要員はデバッグによるソフトウェアの開発を行うことが出来る。

【0042】

一方、デバッガ2がJTAGポート11に接続された場合、接続検出部141から接続検出信号が出力される。このとき、バス出力部142のバス出力制御部142aは、外付けフラッシュROM12や外付けRAM13のデータ読出しが行われた場合、すなわち、マイクロプロセッサ10からリードアクセス信号であるREAD信号が出力され、且つ、CSROM信号またはCSRAM信号がONになった場合は、イネーブル信号を生成し、このイネーブル信号をアドレスバス出力部141bおよびデータバス出力部142cに供給する。イネーブル信号がONになると、アドレスバス出力部142bとデータバス出力部142cは、例えば、0x0000や、0xFFFF等の固定データからなるプレークデータ(所定のデータ)をアドレスバス15とデータバス16にそれぞれ出力する。

【0043】

一方、マイクロプロセッサ10が、読み出したいデータのアドレス値をアドレスバス15に出力すると、外付けフラッシュROM12、または外付けRAM13の該当データがデータバス16に出力される。この場合、出力データとブレークデータの2種類のデータ(信号)が衝突することになり、図4の(e)と(f)に示されるように、アドレスバス15、データバス16を伝搬するそれぞれアドレスデータ、および出力データの値は不定になる。したがって、マイクロプロセッサ10は正常な読出しを行うことが出来ない。このように、JTAG−ICE等のデバッカ2が、マイクロプロセッサ10の読出し機能を使用して、外付けフラッシュROM12、または外付けRAM13が保持したプログラムを含むデータを保護し、読み出しを防止することが出来る。

【0044】

なお、デバッガ2は、本来、マイクロプロセッサ10が持つデータの読出し機能を使用して、外付けフラッシュROM12または外付けRAM13が保持したデータを読み出してプログラム開発を支援するツールである。したがって、例えば、接続検出部141が、デバッガ2からJTAGポート11を介して所定のコマンドを受信し保持する構成(コマンド受信手段)を有することで、保持された所定のコマンドに基づきブレークデータの出力を阻止し、メーカの保守要員によるデバッグ作業の妨げにならないようにすることができる。

【0045】

この場合に使用される所定のコマンドとは、第三者が知りえない非公開のコマンドであり、予めコマンド受信手段(PLD14内)にプログラミングされ登録されている。コマンド受信手段は、この予め登録されたコマンドと前述JTAGポート11を介して受信したコマンドとが一致することで、コマンドを保持し、ブレークデータの出力を阻止するようバス出力部142に作用する。これについては、接続検出部141の接続検出信号14aをオフしても良いし、イネーブル信号14bが出力されないようにマスク信号をバス出力部142に与えても良い。

【0046】

また、コマンド受信手段にタイマーを設け、所定のコマンドを、第1コマンドと第2コマンドに区分して管理するような多段コマンド形態とし、接続検出部141が、第1コマンドを受信してから所定の時間以内に第2コマンドを受信することで所定のコマンドの保持を許可する構成をとることができる。このことにより、第三者による試行錯誤に基づくコマンド送信の偶然の一致による、アドレスバス15やデータバス16へのブレークデータの出力阻止を抑制することができる。第1コマンドと第2コマンドについては、両方とも同じコマンドでも良く、相違したコマンドにしても良い。両方とも同じコマンドとして管理する場合には、第1コマンドと前述コマンド受信手段に予め登録されたコマンドとの一致を検出してから、例えば10秒以内に第2コマンドを受信し、この受信された第2コマンドと前述コマンド受信手段に予め登録されたコマンドが一致することでコマンドを保持すればよい。バス出力部142への作用については前述と同様である。

【0047】

一方、第1コマンドと第2コマンドのそれぞれをコマンド受信手段(PLD14内)に予め登録する構成とすれば、第1コマンドと第2コマンドとを相違したコマンドとして管理することができる。この場合、受信手段に予め登録された第1コマンドとJTAGポート11を介して受信した第1コマンドとの一致を検出してから、例えば10秒以内に第2コマンドを受信し、この受信された第2コマンドと受信手段に予め登録された第2コマンドが一致することでコマンド(第1コマンドもしくは第2コマンド)を保持すればよい。バス出力部142への作用については前述と同様である。

【0048】

上記のように、ブレークデータの出力を多段コマンドの受信によって解除するように構成することで、第三者による試行錯誤に基づくコマンド送信の偶然の一致による、アドレスバス15やデータバス16へのブレークデータの出力阻止をさらに抑制することができる。

【0049】

また、図2に示す構成では、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、アドレスバス15またはデータバス16に対してブレークデータを出力するバス出力部142を、PLD14で構成するものとして説明したが、PLDに代わり、ROMやフラッシュメモリもしくはRAM等のメモリで代替することができる。この場合の、バス出力部142の内部構成例が図5に示されている。

【0050】

図5によれば、バス出力部142は、接続検出信号が入力されて自身が選択されるセレクトポート142dと、アクセス制御信号であるマイクロプロセッサ10からのREAD信号を受信する制御ポート142eと、セレクトポート142d、およびアクセス制御信号の両方がONすることでデータを出力する出力ポート142fとを有する記憶手段で構成される。この構成によっても、アドレスバス15またはデータバス16を伝搬するデータに関し、READにより出力されるデータにブレークデータを衝突させることで破壊させる仕組みを実現出来、デバッガ2が接続されたときに、外付けフラッシュROM12や外付けRAM13からのプログラムを含むデータの読み出しを阻止することができる。

(実施形態の変形例)

なお、上記した本実施形態に係る半導体集積回路では、PLD14は、デバッガ2がJTAGポート11に接続されることにより、接続検出部141で接続検出信号が出力され、バス出力部142でREAD信号がONになることで、アドレスバス15およびデータバス16に、固定データからなるプレークデータを出力するものとして説明したが、ブレークデータとして、任意の値を用いても良い。この場合、隣接するビットが異なる値であれば特に都合が良い。

【0051】

すなわち、マイクロプロセッサ10と、外付けフラッシュROM12あるいは外付けRAM13とを接続するアドレスバス15とデータバス16は、複数本のラインが並列に接続されるパラレルバス構成である。このため、パラレルバスを伝搬する複数のビットの内容が同時にスイッチングされると、これに起因して大きな電流の変化が生じる。このとき流れる高周波電流は、マイクロプロセッサ10を含む各種LSIの電源やグラウンドに集中し、電位変動を発生させる。この電位変動によってLSI等の電源電圧が変動すると、不図示のバスドライバの出力電流が変化してレシーバの信号立ち上がり時間が変化し、結果として信号送受信間の信号のタイミングがずれることになる。極端な場合には、閾値の変動により誤作動が発生する可能性がある。したがって、隣接ビットの値を異ならせることで同時にスイッチングが抑制され、誤作動を回避することができる。

【0052】

また、本実施形態によれば、バス出力制御部142aは、条件(接続検出信号とアクセス制御信号が共に両方がON)が成立したときに、アドレスバス出力部142bとデータバス出力部142cの両方にイネーブル信号を供給し、アドレスバス15とデータバス16の双方を有効にしているが、この場合、いずれか一方を有効にするだけで本発明を実現できる。

【0053】

また、本実施形態によれば、アドレスバス15とデータバス16に出力されたプログラムを含むデータをブレークデータと衝突させることで破壊し、不定値とするものとしたが、他に、同じ条件が成立したときにマイクロプロセッサ10にリセット信号を供給して初期化することで、JTAGインタフェース経由でプログラムを含むデータが読み込まれることを防止することができる。

【0054】

この場合、バス出力部142には、接続検出部141から出力される接続検出信号とマイクロプロセッサ10から外付けフラッシュROM12や外付けRAM13に対して出力されるアクセス制御信号(READ)とを受信し、接続検出信号とアクセス制御信号とがONすることで、マイクロプロセッサ10にリセット信号を供給するハードウェアが付加される。しかしながら、この場合でも、バスにロジックアナライザ等を接続してトレースすればバスに出力されたプログラムやデータが読まれることは否めない。但し、マイクロプロセッサ10がリセットされる毎にプログラムがイニシャルルーチンから起動されるため、連続してプログラムが読まれることは少なく、このため、プログラムの保護の観点からは有効に手段となる。

【0055】

また、本実施形態では、マイクロプロセッサ10に、アドレスバス15、データバス16経由で接続されるメモリとして、外付けフラッシュROM12、あるいは外付けRAM13を使用するものとして説明したが、その他LSIに内蔵されたレジスタ等の揮発性メモリについてもそれらに設定されるデータが保護対象になれば、それらLSIに対して出力されるチップセレクト信号をバス出力部142(バス出力制御部142a)へ供給することで、同様の効果が得られる。

【0056】

この場合も同様、バス出力部142は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号(READ)が共に有効である場合に、アドレスバス15およびデータバス16に対してブレークデータを出力する。このため、上記した揮発性メモリに保持されアドレスバス15やデータバス16に出力される出力データとブレークデータとが衝突することでアドレスバス15やデータバス16を伝搬するデータが破壊されて不定になる。したがって、マイクロプロセッサ10にアドレスバス15やデータバス16経由で接続される、揮発性メモリに保持された、不揮発性メモリの少なくとも一部写しであるプログラムやデータの保護が可能になる。なお、ここで使用される揮発性メモリとして上記したLSIが内蔵するレジスタの他に、SRAM等が実装されるキャッシュ等の高速メモリが含まれても良い。

(実施形態の効果)

以上説明のように本実施形態に係る半導体集積回路によれば、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサ10に、アドレスバス15およびデータバス16経由で、例えば、外付けフラッシュROM12や外付けRAM13が接続されるケースにおいても、外付けフラッシュROM12や外付けRAM13に保持されたプログラムを含むデータ、更にはマイクロプロセッサ10に内蔵されたレジスタに保持されたデータの読み出しを防止することができる。また、本実施形態に係る半導体集積回路を電力変換装置の制御装置1等の組み込みシステムに適用しても、マイクロプロセッサ10の動作クロックが高速化され、外付けフラッシュROM12や外付けRAM13対する信号の遅延に対する要求仕様も厳しいものになってきている昨今、外付けフラッシュROM12や外付けRAM13に入力される信号線の途中に遅延を増加させる素子を挿入することなくプログラムを含むデータ保護を実現するため、高性能な組み込みシステムを提供することができる。

(データ漏洩防止方法)

また、本実施形態に係るデータ漏洩防止方法は、例えば、図1に示されるように、プログラムを含むデータが保持されたメモリ(外付けフラッシュROM12と外付けRAM13)と、このメモリにバス(アドレスバス15とデータバス16)を介して接続され、前記プログラムを実行するマイクロプロセッサ10と、前記プログラムのデバッグを支援するデバッガ2が接続される接続部(JTAGポート11)と、を有する半導体集積回路におけるデータ漏洩防止方法である。

【0057】

そして、接続部にデバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、この接続検出信号がオンされているとき、マイクロプロセッサから出力されるメモリへのアクセス制御信号(READ)がオンされることでバスにブレークデータを出力し、このブレークデータとアクセス制御信号のオンに伴ってメモリがバスに出力するデータとを衝突させ、バスに伝搬するデータを不定にする第2のステップと、を有するものである。

【0058】

このように本実施形態に係るデータ漏洩防止方法によれば、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、バスに対してブレークデータを出力するため、このブレークデータと、メモリに保持されバスに出力される出力データとが衝突することでバスを伝搬するデータが破壊されて不定になる。したがって、マイクロプロセッサ10にバス経由で接続されるメモリに保持されたプログラムやデータの保護が可能になる。なお、バスに出力されるプレークデータとメモリからの出力データとを衝突させて不定値とする代わりに、同じ条件(デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効)が成立したときに、マイクロプロセッサ10にリセット信号を供給しても同じ効果が得られる。

【0059】

以上、本実施形態について説明したが、本発明の技術的範囲は上記実施形態に記載の範囲には限定されないことは言うまでもない。上記実施形態に、多様な変更又は改良を加えることが可能であることが当業者に明らかである。またそのような変更又は改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【符号の説明】

【0060】

1・・制御装置、2・・デバッガ(JTAG−ICE)、10・・マイクロプロセッサ、11・・JTAGポート(接続部)、12・・外付けフラッシュROM、13・・外付けRAM、14・・PLD(プログラムロジックデバイス)、15・・アドレスバス、16・・データバス、141・・接続検出部、142・・バス出力部、142a・・バス出力制御部、142b・・アドレスバス出力部、142c・・データバス出力部、142d・・セレクトポート、142e・・制御ポート、142f・・出力ポート

【技術分野】

【0001】

この発明は、半導体集積回路およびデータ漏洩防止方法に係り、特に、パワーエレクトロニクス技術を応用した電力変換装置の制御装置等の組込みシステムにおいて、プログラムやデータ等の知的財産保護に用いて好適な技術に関する。

【背景技術】

【0002】

最近の電力変換装置の制御装置等、組込みシステムに使用されるマイクロプロセッサでは、JTAG(Joint Test Action Group)を使用したインタフェースをデバック機能として搭載することが主流になっている。

【0003】

ところで、PC(Personal Computer)等、汎用のコンピュータシステムは勿論のこと、組込みシステムにおいても知的財産であるプログラムやデータ等、ソフトウェアの保護は重要な設計事項になっている。しかしながら、上記したJTAGインタフェースを用いると、半導体集積回路に内蔵されたフラッシュROMや内蔵RAMに保持されるプログラムやデータを自由に読みだすことが出来る。

【0004】

図6に、マイクロプロセッサ100aに、外付けフラッシュROM120と外付けRAM130が、アドレスバス150とデータバス160経由で接続され、使用される、一般的な組込みシステム(制御装置100)の構成を示す図である。JTAG−ICE(In Circuit Emulator)等のデバッガ200は、JTAGポート110を介してマイクロプロセッサ100aに接続される。

【0005】

ソフトウェアの保護機能を持たない制御装置100の場合、外付けフラッシュROM120には、暗号化ソフトウェアと、この暗号化ソフトウェアを解読するための復号化ソフトウェアとが保持されている。この理由は、第三者がPt板に半田付けされた外付けフラッシュROM120をシステムから取り外し、不図示のフラッシュROMライタ等により保持されたこれらソフトウェアが読み出されることを防ぐためである。

【0006】

マイクロプロセッサ100aは、リセット解除後の初期化処理の過程で、外付けフラッシュROM120に保持された復号化ソフトウェアを使用して暗号化されたソフトウェアを暗号化前の元のソフトウェアに変換し、外付けRAM130に保持する処理を行う。マイクロプロセッサ100aは、上記した処理の後、外付けRAM130に保持された暗号化前のソフトウェアを使用して組込みシステムが持つ本来の処理を行う。

【0007】

従来、第三者によるJTAGインタフェースを介したプログラムやデータの読み出しが出来ないような仕組みが開発され、多数特許出願されている。例えば、特許文献1には、内蔵フラッシュROMにセキュリティビットを設け、このセキュリティビットをONすることでJTAGインタフェースの機能を禁止してフラッシュROMに保持されたプログラムの読出しが出来ない仕組みが開示されている。また、特許文献2には、JTAGインタフェースにICE等のデバッグ機器が接続されているときは、内蔵RAMのアクセスを禁止することで内蔵RAMに保持されたプログラムの読み出しが出来ない仕組みが開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−32267号公報

【特許文献2】特開2009−25907号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記した電力変換装置に使用される組込みシステムにおいても、最近ではソフトウェアの容量が大規模化し、マイクロプロセッサに外付けフラッシュROMや外付けRAM等を使用するケースが多くなって来ている。この組込みシステムにおいてもプログラムやデータの保護が重要になって来ているが、JTAGインタフェースからプログラムやデータの読み出しを防止する対象は、特許文献1や特許文献2に開示されているように、マイクロプロセッサに内蔵されたフラッシュROMやRAMに保持されたものであり、外付けフラッシュROMや外付けRAM等の外付けメモリに保持されたものではない。

【0010】

また、マイクロプロセッサに外付けメモリを接続して使用する場合、フラッシュROMを内蔵しないマイクロプロセッサを使用することも多い。そのようなマイクロプロセッサでもJTAGインタフェースが搭載されたものは多いが、JTAGインタフェースを介して外付けメモリに保持されたプログラムやデータの漏洩を防止する機能を持つものは存在しなかった。

【0011】

本発明は上記した課題を解決するためになされたものであり、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサにバス経由でメモリが接続されるケースにおいても、メモリに保持されたプログラムやデータの読み出し保護が可能な、半導体集積回路およびソフトウェア漏洩防止方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記した課題を解決するために本発明の第1の観点に係る半導体集積回路は、プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、を備えることを特徴とする。

【0013】

本発明の第1の観点に係る半導体集積回路によれば、バス出力部が、デバッガが接続されたことを示す接続検出信号と、マイクロプロセッサからのアクセス制御信号が共に有効である場合に、バスに対して所定のデータを出力する。このため、所定のデータと、メモリに保持されバスに出力されるデータとが衝突することでバスを伝搬するデータが破壊されて不定になるため、マイクロプロセッサにバス経由で接続されるメモリに保持されたプログラムやデータの読み出し保護が可能になる。

本発明の第1の観点に係る半導体集積回路において、前記バスは複数ビットで構成されるパラレルバスであり、前記ブレークデータは、隣接するビットが異なる値であることを特徴とする。

【0014】

本発明の第1の観点に係る半導体集積回路において、前記バスは、アドレスバス、もしくはデータバスであることを特徴とする。

本発明の第1の観点に係る半導体集積回路において、前記バス出力部は、電流抑制手段を介して前記バスに接続されることを特徴とする。

【0015】

本発明の第1の観点に係る半導体集積回路において、前記接続検出部または前記バス出力部は、所定の言語でプログラムされたプログラムブルロジックデバイスで構成されることを特徴とする。

【0016】

本発明の第1の観点に係る半導体集積回路において、前記バス出力部は、自らが選択されるセレクトポートと、前記アクセス制御信号を受信する制御ポートと、前記セレクトポートおよび前記アクセス制御信号の両方が有効になることにより前記ブレークデータを出力する出力ポートと、を有する記憶手段で構成され、前記接続検出信号を前記セレクトポートに接続し、前記制御信号を前記制御ポートに接続し、前記出力ポートを前記バスに接続することを特徴とする。

【0017】

本発明の第1の観点に係る半導体集積回路において、前記接続検出部は、前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持したコマンドに基づき前記接続検出信号をオフするコマンド受信手段を備えることを特徴とする。本発明によれば、所定のコマンドを受信するとバスへの所定のデータの出力を阻止することで、プログラムやデータの保護が、メーカの保守要員によるデバッグ作業の妨げになることを回避することができる。

【0018】

本発明の第1の観点に係る半導体集積回路において、前記コマンドは、第1コマンドと第2コマンドとからなり、前記コマンド受信手段は、前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする。本発明によれば、第三者による試行錯誤に基づくコマンド送信の偶然の一致によるバスへの所定のデータの出力阻止を制御することができる。

【0019】

本発明の第2の観点に係る半導体集積回路は、プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するバス出力部と、を備えることを特徴とする。

【0020】

本発明の第2の観点に係る半導体集積回路によれば、バス出力部が、デバッガが接続されたときに接続検出部により出力される接続検出信号がオンのとき、マイクロプロセッサから出力されるメモリへのアクセス制御信号がオンされることでマイクロプロセッサにリセット信号を供給する。このため、マイクロプロセッサは、リセット信号を受信する毎に初期化され、都度初期ルーチンから起動されるため、連続してプログラムが読み込まれることが無くなり、プログラム保護に有効な手段として提供することが出来る。

【0021】

本発明の第3の観点に係る半導体集積回路は、プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路において、前記プログラムのデバッグを支援するデバッガが接続される接続部と、この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、この接続検出信号がオンのとき、前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、を備えることを特徴とする。

【0022】

本発明の第3の観点に係る半導体集積回路によれば、バス出力部は、デバッガが接続されたときに接続検出部により出力される接続検出信号がオンのとき、マイクロプロセッサから出力される不揮発性メモリまたは揮発性メモリへのアクセス制御信号がオンされることでバスにブレークデータを出力し、このブレークデータとアクセス制御信号のオンに伴って不揮発性メモリまたは揮発性メモリがバスに出力するデータとを衝突させ、バスに伝搬するデータを不定にする。したがって、マイクロプロセッサにバス経由で接続される揮発性メモリに保持された不揮発性メモリの少なくとも一部写しであるプログラムやデータの保護が可能になる。

【0023】

本発明の第4の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩防止方法であって、前記接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にする第2のステップと、を有することを特徴とする。

【0024】

本発明の第4の観点に係るデータ漏洩防止方法において、前記第1のステップには、前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持されたコマンドに基づき前記接続検出信号をオフする第1のサブステップを含むことを特徴とする。

【0025】

本発明の第4の観点に係るデータ漏洩防止方法において、前記コマンドは、第1コマンドと第2コマンドとからなり、前記第1のサブステップにおいて、前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする。

【0026】

本発明の第5の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩方法であって、前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するステップと、を有することを特徴とする。

【0027】

本発明の第6の観点に係るデータ漏洩防止方法は、プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路におけるデータ漏洩防止方法であって、前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、この接続検出信号がオンされているとき、前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするステップと、を有することを特徴とする。

【発明の効果】

【0028】

本発明によれば、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサにバス経由でメモリが接続され、使用するケースにおいても、メモリに保持されたプログラムやデータの読み出し保護が可能な、半導体集積回路およびソフトウェア漏洩防止方法を提供することができる。

【図面の簡単な説明】

【0029】

【図1】本発明の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】本発明の実施の形態に係る半導体集積回路のバス出力部の内部構成の一例を示すブロック図である。

【図3】本発明の実施の形態に係る半導体集積回路において、デバッガが接続されていない場合の動作を示すタイミング図である。

【図4】本発明の実施の形態に係る半導体集積回路において、デバッガが接続された場合の動作を示すタイミング図である。

【図5】本発明の実施の形態に係る半導体集積回路のバス出力部の内部構成の他の例を示すブロック図である。

【図6】一般的な組み込みシステムの構成を示すブロック図である。

【発明を実施するための形態】

【0030】

以下、添付図面を参照して本発明を実施するための実施の形態(以下、単に本実施形態という)について詳細に説明する。

(実施形態の構成)

図1は、本実施形態に係る半導体集積回路の構成を示すブロック図である。ここでは、半導体集積回路として、電力変換装置の制御装置1等の組み込みシステムを例示して説明する。

【0031】

図1に示されるように、制御装置1は、マイクロプロセッサ10と、JTAGポート11と、外付けフラッシュROMと、外付けRAM13と、PLD(Programmable Logic Device)14と、を含み構成される。PLD14を除けば、図6に示した一般的な組み込みシステムと同様の構成を有する。すなわち、マイクロプロセッサ10に、外付けフラッシュROM12と外付けRAM13が、アドレスバス15とデータバス16経由で接続されており、また、JTAG−ICE等のデバッガ2は、接続部(コネクタ)であるJTAGポート11を介してマイクロプロセッサ10に接続されている。

【0032】

PLD14は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号(READまたはWRITEであって、ここではメモリの読み出しを保護するためREADを対象とする)が共に有効である場合に、アドレスバス15またはデータバス16に対して所定のデータを出力する機能を有するプログラムロジックデバイスである。このため、所定のデータとして用いられるブレークデータと、メモリ(外付けフラッシュROM12、外付けRAM13)に保持され、バスに出力される出力データとが衝突することで、アドレスバス15またはデータバス16を伝搬する出力データが破壊されて不定になる。したがって、マイクロプロセッサ10にバス経由で接続される不揮発性フラッシュROM12や外付けRAM13に保持されたプログラムを含むデータの保護が可能になる。

【0033】

なお、ここで、デバッガ2を介してマイクロプロセッサ10による読出しを防止して保護する対象は、外付けRAM13に保持された暗号化前のプログラム、外付けフラッシュROM12に保持された暗号化プログラム、あるいは不図示のLSIが内蔵するレジスタ(揮発性メモリ)に保持されたデータを含むものとする。

【0034】

このため、PLD14は、マイクロプロセッサ10とは、アドレスバス15、データバス16経由で接続されると共に、マイクロプロセッサ10から、外付けフラッシュROM12または外付けRAM13のアクセス制御信号であるリード信号(READ)をライン10a経由で、自身のチップセレクト信号(CSPLD)をライン10b経由で、外付けフラッシュROM12のチップセレクト信号(CSROM)をライン10c経由で、外付けRAM13のチップセレクト信号(CSRAM)をライン10d経由でそれぞれ取得する。また、JTAGポート11から、JTAG制御信号、JTAGデータを、それぞれライン11a、11b経由で取得する。

【0035】

なお、ライン11a経由で取得されるJTAG制御信号は、ライン11b経由で取得されるJTAGデータ、およびマイクロプロセッサ10からJTAGポート11に出力されるJTAGデータと共に、IEEE1149.1で標準化されたJTAGインタフェースで定義された信号である。特に、JTAG制御信号の中には、TMS(Test Mode State)、TRST(Test Reset)等の信号が含まれ、PLD14は、それらの信号の状態や遷移から、JTAG−ICE等のデバッガ2の接続の有無を検出することができる。

【0036】

図2にPLD14の内部構成の一例が示されている。図2によれば、PLD14は、接続検出部141と、バス出力部142とを含み構成される。接続検出部141は、JTAGポート11から、ライン11a経由でJTAG制御信号を入力として得、ライン11b経由でJTAGデータを入力として得る。接続検出部141は、JTAGポート11にデバッガ2が接続されたことを検出すると、接続検出信号を有効にしてバス出力部142へ出力する。

【0037】

バス出力部142は、バス出力制御部142aと、アドレスバス出力部142bと、データバス出力部142cとを含み構成される。バス出力制御部142aは、マイクロプロセッサ10から、ライン10c経由でCSROM信号、ライン10b経由でCSRAM信号、ライン10a経由でアクセス制御信号であるREAD信号をそれぞれ取得し、READ信号がON(有効化)されたときに、同じく入力されるCSROM信号またはCSRAM信号に基づき、外付けフラッシュROM12または外付けRAM13を選択するように、アドレスバス出力部142b、およびデータバス出力部142cを制御するイネーブル信号を生成する。

【0038】

アドレスバス出力部142bは、ダンピング抵抗17aを介してアドレスバス15に接続されている。アドレスバス出力部142bは、ライン14b経由でバス出力制御部142aから出力されるイネーブル信号に基づき、選択された外付けフラッシュROM12、または外付けRAM13にアドレスデータを出力する。また、データバス出力部142cは、ダンピング抵抗17bを介してデータバス16に接続される。データバス出力部142cは、ライン14b経由でバス出力制御部142aから出力されるイネーブル信号に基づき、選択された外付けフラッシュROM12または外付けRAM13にデータを出力する。なお、ダンピング抵抗17a、17bは、ブレークデータと出力データとの衝突による電流を抑制し、不図示のドライバやレシーバ等、アドレスバス15やデータバス16周辺の素子の破損を防ぐために挿入される。

(実施形態の動作)

図3、図4は、本実施形態に係る半導体集積回路の動作を示すタイミング図であり、デバッガ2が未接続の場合、デバッガ2が接続された場合の、それぞれにおけるバス出力部142の動作を示す。図3、図4ともに、(a)はマイクロプロセッサ10から出力される外付けフラッシュROMのチップセレクト信号(CSROM)、(b)はマイクロプロセッサ10から外付けフラッシュROM12に対して出力されるアクセス制御信号(READ)、(c)はアドレスバス出力部142bの出力データ、(d)は、データバス出力部142cの出力データ、(e)はアドレスバス15を伝搬するアドレスデータ、(f)は、データバス16を伝搬するデータのそれぞれを示す。

【0039】

以下、図3、図4のタイミング図を参照しながら、図1、図2に示す本実施形態に係る半導体集積回路(制御装置1)の動作、特に、バス出力部142の動作について詳細に説明する。

【0040】

まず、図3のタイミング図を参照しながら、デバッガ2が未接続の場合の制御装置1の動作から説明する。この場合、接続検出部141から出力される接続検出信号はOFFになっているため、バス出力部142のバス出力制御部142aは、マイクロプロセッサ10からライン10a経由で取得されるREAD信号、ライン10c経由で取得されるCSROM信号、およびライン10b経由で取得されるCSRAM信号の状態に依存することなく、ライン14b経由でアドレスバス出力部142bとデータバス出力部142cに出力されるイネーブル信号をOFFにする。したがって、アドレスバス出力部142bとデータバス出力部142cは、ハイインピーダンス状態(Hi−Z)を維持する。

【0041】

この状態で、マイクロプロセッサ10が、外付けフラッシュROM12や外付けRAM13に対してREADアクセスを行った場合、アドレスバス15には、マイクロプロセッサ10が読み出したいアドレスデータが出力され、データバス16には、外付けフラッシュROM12や外付けRAM13の先のアドレスに該当するデータが出力される。このことにより、マイクロプロセッサ10が行うプログラムの読み出しやワーク変数の読出し等の読出し動作は正常に行われ、したがって、メーカの開発要員あるいは保守要員はデバッグによるソフトウェアの開発を行うことが出来る。

【0042】

一方、デバッガ2がJTAGポート11に接続された場合、接続検出部141から接続検出信号が出力される。このとき、バス出力部142のバス出力制御部142aは、外付けフラッシュROM12や外付けRAM13のデータ読出しが行われた場合、すなわち、マイクロプロセッサ10からリードアクセス信号であるREAD信号が出力され、且つ、CSROM信号またはCSRAM信号がONになった場合は、イネーブル信号を生成し、このイネーブル信号をアドレスバス出力部141bおよびデータバス出力部142cに供給する。イネーブル信号がONになると、アドレスバス出力部142bとデータバス出力部142cは、例えば、0x0000や、0xFFFF等の固定データからなるプレークデータ(所定のデータ)をアドレスバス15とデータバス16にそれぞれ出力する。

【0043】

一方、マイクロプロセッサ10が、読み出したいデータのアドレス値をアドレスバス15に出力すると、外付けフラッシュROM12、または外付けRAM13の該当データがデータバス16に出力される。この場合、出力データとブレークデータの2種類のデータ(信号)が衝突することになり、図4の(e)と(f)に示されるように、アドレスバス15、データバス16を伝搬するそれぞれアドレスデータ、および出力データの値は不定になる。したがって、マイクロプロセッサ10は正常な読出しを行うことが出来ない。このように、JTAG−ICE等のデバッカ2が、マイクロプロセッサ10の読出し機能を使用して、外付けフラッシュROM12、または外付けRAM13が保持したプログラムを含むデータを保護し、読み出しを防止することが出来る。

【0044】

なお、デバッガ2は、本来、マイクロプロセッサ10が持つデータの読出し機能を使用して、外付けフラッシュROM12または外付けRAM13が保持したデータを読み出してプログラム開発を支援するツールである。したがって、例えば、接続検出部141が、デバッガ2からJTAGポート11を介して所定のコマンドを受信し保持する構成(コマンド受信手段)を有することで、保持された所定のコマンドに基づきブレークデータの出力を阻止し、メーカの保守要員によるデバッグ作業の妨げにならないようにすることができる。

【0045】

この場合に使用される所定のコマンドとは、第三者が知りえない非公開のコマンドであり、予めコマンド受信手段(PLD14内)にプログラミングされ登録されている。コマンド受信手段は、この予め登録されたコマンドと前述JTAGポート11を介して受信したコマンドとが一致することで、コマンドを保持し、ブレークデータの出力を阻止するようバス出力部142に作用する。これについては、接続検出部141の接続検出信号14aをオフしても良いし、イネーブル信号14bが出力されないようにマスク信号をバス出力部142に与えても良い。

【0046】

また、コマンド受信手段にタイマーを設け、所定のコマンドを、第1コマンドと第2コマンドに区分して管理するような多段コマンド形態とし、接続検出部141が、第1コマンドを受信してから所定の時間以内に第2コマンドを受信することで所定のコマンドの保持を許可する構成をとることができる。このことにより、第三者による試行錯誤に基づくコマンド送信の偶然の一致による、アドレスバス15やデータバス16へのブレークデータの出力阻止を抑制することができる。第1コマンドと第2コマンドについては、両方とも同じコマンドでも良く、相違したコマンドにしても良い。両方とも同じコマンドとして管理する場合には、第1コマンドと前述コマンド受信手段に予め登録されたコマンドとの一致を検出してから、例えば10秒以内に第2コマンドを受信し、この受信された第2コマンドと前述コマンド受信手段に予め登録されたコマンドが一致することでコマンドを保持すればよい。バス出力部142への作用については前述と同様である。

【0047】

一方、第1コマンドと第2コマンドのそれぞれをコマンド受信手段(PLD14内)に予め登録する構成とすれば、第1コマンドと第2コマンドとを相違したコマンドとして管理することができる。この場合、受信手段に予め登録された第1コマンドとJTAGポート11を介して受信した第1コマンドとの一致を検出してから、例えば10秒以内に第2コマンドを受信し、この受信された第2コマンドと受信手段に予め登録された第2コマンドが一致することでコマンド(第1コマンドもしくは第2コマンド)を保持すればよい。バス出力部142への作用については前述と同様である。

【0048】

上記のように、ブレークデータの出力を多段コマンドの受信によって解除するように構成することで、第三者による試行錯誤に基づくコマンド送信の偶然の一致による、アドレスバス15やデータバス16へのブレークデータの出力阻止をさらに抑制することができる。

【0049】

また、図2に示す構成では、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、アドレスバス15またはデータバス16に対してブレークデータを出力するバス出力部142を、PLD14で構成するものとして説明したが、PLDに代わり、ROMやフラッシュメモリもしくはRAM等のメモリで代替することができる。この場合の、バス出力部142の内部構成例が図5に示されている。

【0050】

図5によれば、バス出力部142は、接続検出信号が入力されて自身が選択されるセレクトポート142dと、アクセス制御信号であるマイクロプロセッサ10からのREAD信号を受信する制御ポート142eと、セレクトポート142d、およびアクセス制御信号の両方がONすることでデータを出力する出力ポート142fとを有する記憶手段で構成される。この構成によっても、アドレスバス15またはデータバス16を伝搬するデータに関し、READにより出力されるデータにブレークデータを衝突させることで破壊させる仕組みを実現出来、デバッガ2が接続されたときに、外付けフラッシュROM12や外付けRAM13からのプログラムを含むデータの読み出しを阻止することができる。

(実施形態の変形例)

なお、上記した本実施形態に係る半導体集積回路では、PLD14は、デバッガ2がJTAGポート11に接続されることにより、接続検出部141で接続検出信号が出力され、バス出力部142でREAD信号がONになることで、アドレスバス15およびデータバス16に、固定データからなるプレークデータを出力するものとして説明したが、ブレークデータとして、任意の値を用いても良い。この場合、隣接するビットが異なる値であれば特に都合が良い。

【0051】

すなわち、マイクロプロセッサ10と、外付けフラッシュROM12あるいは外付けRAM13とを接続するアドレスバス15とデータバス16は、複数本のラインが並列に接続されるパラレルバス構成である。このため、パラレルバスを伝搬する複数のビットの内容が同時にスイッチングされると、これに起因して大きな電流の変化が生じる。このとき流れる高周波電流は、マイクロプロセッサ10を含む各種LSIの電源やグラウンドに集中し、電位変動を発生させる。この電位変動によってLSI等の電源電圧が変動すると、不図示のバスドライバの出力電流が変化してレシーバの信号立ち上がり時間が変化し、結果として信号送受信間の信号のタイミングがずれることになる。極端な場合には、閾値の変動により誤作動が発生する可能性がある。したがって、隣接ビットの値を異ならせることで同時にスイッチングが抑制され、誤作動を回避することができる。

【0052】

また、本実施形態によれば、バス出力制御部142aは、条件(接続検出信号とアクセス制御信号が共に両方がON)が成立したときに、アドレスバス出力部142bとデータバス出力部142cの両方にイネーブル信号を供給し、アドレスバス15とデータバス16の双方を有効にしているが、この場合、いずれか一方を有効にするだけで本発明を実現できる。

【0053】

また、本実施形態によれば、アドレスバス15とデータバス16に出力されたプログラムを含むデータをブレークデータと衝突させることで破壊し、不定値とするものとしたが、他に、同じ条件が成立したときにマイクロプロセッサ10にリセット信号を供給して初期化することで、JTAGインタフェース経由でプログラムを含むデータが読み込まれることを防止することができる。

【0054】

この場合、バス出力部142には、接続検出部141から出力される接続検出信号とマイクロプロセッサ10から外付けフラッシュROM12や外付けRAM13に対して出力されるアクセス制御信号(READ)とを受信し、接続検出信号とアクセス制御信号とがONすることで、マイクロプロセッサ10にリセット信号を供給するハードウェアが付加される。しかしながら、この場合でも、バスにロジックアナライザ等を接続してトレースすればバスに出力されたプログラムやデータが読まれることは否めない。但し、マイクロプロセッサ10がリセットされる毎にプログラムがイニシャルルーチンから起動されるため、連続してプログラムが読まれることは少なく、このため、プログラムの保護の観点からは有効に手段となる。

【0055】

また、本実施形態では、マイクロプロセッサ10に、アドレスバス15、データバス16経由で接続されるメモリとして、外付けフラッシュROM12、あるいは外付けRAM13を使用するものとして説明したが、その他LSIに内蔵されたレジスタ等の揮発性メモリについてもそれらに設定されるデータが保護対象になれば、それらLSIに対して出力されるチップセレクト信号をバス出力部142(バス出力制御部142a)へ供給することで、同様の効果が得られる。

【0056】

この場合も同様、バス出力部142は、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号(READ)が共に有効である場合に、アドレスバス15およびデータバス16に対してブレークデータを出力する。このため、上記した揮発性メモリに保持されアドレスバス15やデータバス16に出力される出力データとブレークデータとが衝突することでアドレスバス15やデータバス16を伝搬するデータが破壊されて不定になる。したがって、マイクロプロセッサ10にアドレスバス15やデータバス16経由で接続される、揮発性メモリに保持された、不揮発性メモリの少なくとも一部写しであるプログラムやデータの保護が可能になる。なお、ここで使用される揮発性メモリとして上記したLSIが内蔵するレジスタの他に、SRAM等が実装されるキャッシュ等の高速メモリが含まれても良い。

(実施形態の効果)

以上説明のように本実施形態に係る半導体集積回路によれば、JTAG等のデバッグインタフェースが搭載されたマイクロプロセッサ10に、アドレスバス15およびデータバス16経由で、例えば、外付けフラッシュROM12や外付けRAM13が接続されるケースにおいても、外付けフラッシュROM12や外付けRAM13に保持されたプログラムを含むデータ、更にはマイクロプロセッサ10に内蔵されたレジスタに保持されたデータの読み出しを防止することができる。また、本実施形態に係る半導体集積回路を電力変換装置の制御装置1等の組み込みシステムに適用しても、マイクロプロセッサ10の動作クロックが高速化され、外付けフラッシュROM12や外付けRAM13対する信号の遅延に対する要求仕様も厳しいものになってきている昨今、外付けフラッシュROM12や外付けRAM13に入力される信号線の途中に遅延を増加させる素子を挿入することなくプログラムを含むデータ保護を実現するため、高性能な組み込みシステムを提供することができる。

(データ漏洩防止方法)

また、本実施形態に係るデータ漏洩防止方法は、例えば、図1に示されるように、プログラムを含むデータが保持されたメモリ(外付けフラッシュROM12と外付けRAM13)と、このメモリにバス(アドレスバス15とデータバス16)を介して接続され、前記プログラムを実行するマイクロプロセッサ10と、前記プログラムのデバッグを支援するデバッガ2が接続される接続部(JTAGポート11)と、を有する半導体集積回路におけるデータ漏洩防止方法である。

【0057】

そして、接続部にデバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、この接続検出信号がオンされているとき、マイクロプロセッサから出力されるメモリへのアクセス制御信号(READ)がオンされることでバスにブレークデータを出力し、このブレークデータとアクセス制御信号のオンに伴ってメモリがバスに出力するデータとを衝突させ、バスに伝搬するデータを不定にする第2のステップと、を有するものである。

【0058】

このように本実施形態に係るデータ漏洩防止方法によれば、デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効である場合に、バスに対してブレークデータを出力するため、このブレークデータと、メモリに保持されバスに出力される出力データとが衝突することでバスを伝搬するデータが破壊されて不定になる。したがって、マイクロプロセッサ10にバス経由で接続されるメモリに保持されたプログラムやデータの保護が可能になる。なお、バスに出力されるプレークデータとメモリからの出力データとを衝突させて不定値とする代わりに、同じ条件(デバッガ2が接続されたことを示す接続検出信号と、マイクロプロセッサ10からのアクセス制御信号が共に有効)が成立したときに、マイクロプロセッサ10にリセット信号を供給しても同じ効果が得られる。

【0059】

以上、本実施形態について説明したが、本発明の技術的範囲は上記実施形態に記載の範囲には限定されないことは言うまでもない。上記実施形態に、多様な変更又は改良を加えることが可能であることが当業者に明らかである。またそのような変更又は改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【符号の説明】

【0060】

1・・制御装置、2・・デバッガ(JTAG−ICE)、10・・マイクロプロセッサ、11・・JTAGポート(接続部)、12・・外付けフラッシュROM、13・・外付けRAM、14・・PLD(プログラムロジックデバイス)、15・・アドレスバス、16・・データバス、141・・接続検出部、142・・バス出力部、142a・・バス出力制御部、142b・・アドレスバス出力部、142c・・データバス出力部、142d・・セレクトポート、142e・・制御ポート、142f・・出力ポート

【特許請求の範囲】

【請求項1】

プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項2】

請求項1記載の半導体集積回路において、

前記バスは複数ビットで構成されるパラレルバスであり、

前記ブレークデータは、隣接するビットが異なる値であることを特徴とする半導体集積回路。

【請求項3】

請求項1または請求項2記載の半導体集積回路において、

前記バスは、アドレスバス、もしくはデータバスであることを特徴とする半導体集積回路。

【請求項4】

請求項1〜請求項3のいずれか1項記載の半導体集積回路において

前記バス出力部は、

電流抑制手段を介して前記バスに接続されることを特徴とする半導体集積回路。

【請求項5】

請求項1〜請求項4のいずれか1項記載の半導体集積回路において、

前記接続検出部または前記バス出力部は、

所定の言語でプログラムされたプログラムブルロジックデバイスで構成されることを特徴とする半導体集積回路。

【請求項6】

請求項1〜請求項4のいずれか1項記載の半導体集積回路において、

前記バス出力部は、

自らが選択されるセレクトポートと、前記アクセス制御信号を受信する制御ポートと、前記セレクトポートおよび前記アクセス制御信号の両方が有効になることにより前記ブレークデータを出力する出力ポートと、を有する記憶手段で構成され、

前記接続検出信号を前記セレクトポートに接続し、前記制御信号を前記制御ポートに接続し、前記出力ポートを前記バスに接続することを特徴とする半導体集積回路。

【請求項7】

請求項1〜請求項5のいずれか1項記載の半導体集積回路において、

前記接続検出部は、

前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持したコマンドに基づき前記接続検出信号をオフするコマンド受信手段を備えることを特徴とする半導体集積回路。

【請求項8】

請求項7記載の半導体集積回路において、

前記コマンドは、第1コマンドと第2コマンドとからなり、

前記コマンド受信手段は、

前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする半導体集積回路。

【請求項9】

プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項10】

プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項11】

プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩防止方法であって、

前記接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にする第2のステップと、

を有することを特徴とするデータ漏洩防止方法。

【請求項12】

請求項11記載のデータ漏洩防止方法において、

前記第1のステップには、

前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持されたコマンドに基づき前記接続検出信号をオフする第1のサブステップを含むことを特徴とするデータ漏洩防止方法。

【請求項13】

請求項12記載のデータ漏洩防止方法において、

前記コマンドは、第1コマンドと第2コマンドとからなり、

前記第1のサブステップにおいて、

前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とするデータ漏洩防止方法。

【請求項14】

プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩方法であって、

前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するステップと、

を有することを特徴とするデータ漏洩防止方法。

【請求項15】

プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路におけるデータ漏洩防止方法であって、

前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするステップと、

を有することを特徴とするデータ漏洩防止方法。

【請求項1】

プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項2】

請求項1記載の半導体集積回路において、

前記バスは複数ビットで構成されるパラレルバスであり、

前記ブレークデータは、隣接するビットが異なる値であることを特徴とする半導体集積回路。

【請求項3】

請求項1または請求項2記載の半導体集積回路において、

前記バスは、アドレスバス、もしくはデータバスであることを特徴とする半導体集積回路。

【請求項4】

請求項1〜請求項3のいずれか1項記載の半導体集積回路において

前記バス出力部は、

電流抑制手段を介して前記バスに接続されることを特徴とする半導体集積回路。

【請求項5】

請求項1〜請求項4のいずれか1項記載の半導体集積回路において、

前記接続検出部または前記バス出力部は、

所定の言語でプログラムされたプログラムブルロジックデバイスで構成されることを特徴とする半導体集積回路。

【請求項6】

請求項1〜請求項4のいずれか1項記載の半導体集積回路において、

前記バス出力部は、

自らが選択されるセレクトポートと、前記アクセス制御信号を受信する制御ポートと、前記セレクトポートおよび前記アクセス制御信号の両方が有効になることにより前記ブレークデータを出力する出力ポートと、を有する記憶手段で構成され、

前記接続検出信号を前記セレクトポートに接続し、前記制御信号を前記制御ポートに接続し、前記出力ポートを前記バスに接続することを特徴とする半導体集積回路。

【請求項7】

請求項1〜請求項5のいずれか1項記載の半導体集積回路において、

前記接続検出部は、

前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持したコマンドに基づき前記接続検出信号をオフするコマンド受信手段を備えることを特徴とする半導体集積回路。

【請求項8】

請求項7記載の半導体集積回路において、

前記コマンドは、第1コマンドと第2コマンドとからなり、

前記コマンド受信手段は、

前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とする半導体集積回路。

【請求項9】

プログラムを含むデータが保持されたメモリとマイクロプロセッサとがバスを介して接続された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項10】

プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路において、

前記プログラムのデバッグを支援するデバッガが接続される接続部と、

この接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする接続検出部と、

この接続検出信号がオンのとき、

前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするバス出力部と、

を備えることを特徴とする半導体集積回路。

【請求項11】

プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩防止方法であって、

前記接続部に前記デバッガが接続されたことを検出すると接続検出信号をオンする第1のステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にする第2のステップと、

を有することを特徴とするデータ漏洩防止方法。

【請求項12】

請求項11記載のデータ漏洩防止方法において、

前記第1のステップには、

前記デバッガから前記接続部を介してコマンドを受信して保持し、該保持されたコマンドに基づき前記接続検出信号をオフする第1のサブステップを含むことを特徴とするデータ漏洩防止方法。

【請求項13】

請求項12記載のデータ漏洩防止方法において、

前記コマンドは、第1コマンドと第2コマンドとからなり、

前記第1のサブステップにおいて、

前記第1コマンドを受信してから所定の時間以内に前記第2コマンドを受信することで前記第1コマンドもしくは前記第2コマンドを前記コマンドとして保持することを特徴とするデータ漏洩防止方法。

【請求項14】

プログラムを含むデータが保持されたメモリと、このメモリにバスを介して接続され、前記プログラムを実行するマイクロプロセッサと、前記プログラムのデバッグを支援するデバッガが接続される接続部と、を有する半導体集積回路におけるデータ漏洩方法であって、

前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記メモリへのアクセス制御信号がオンされることで前記マイクロプロセッサにリセット信号を供給するステップと、

を有することを特徴とするデータ漏洩防止方法。

【請求項15】

プログラムを含むデータが保持された不揮発性メモリと、揮発性メモリと、マイクロプロセッサとがバスを介して接続され、前記揮発性メモリには、前記不揮発性メモリに保持された前記データの少なくとも一部写しが保持された半導体集積回路におけるデータ漏洩防止方法であって、

前記接続部に前記デバッガが接続されたことを検出し接続検出信号をオンするステップと、

この接続検出信号がオンされているとき、

前記マイクロプロセッサから出力される前記不揮発性メモリまたは前記揮発性メモリへのアクセス制御信号がオンされることで前記バスにブレークデータを出力し、このブレークデータと前記アクセス制御信号のオンに伴って前記不揮発性メモリまたは前記揮発性メモリが前記バスに出力する前記データとを衝突させ、前記バスに伝搬するデータを不定にするステップと、

を有することを特徴とするデータ漏洩防止方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−37654(P2013−37654A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−175637(P2011−175637)

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]