半導体集積回路の設計方法および設計用プログラム

【課題】電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出できる半導体集積回路の設計方法を提供する。

【解決手段】電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1とで決まる第1の共振周波数faと、電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1と抵抗付きデカップリングコンデンサ35の容量値C2とで決まる第2の共振周波数fbを算出し、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35のコンデンサ36のインピーダンスに等しい値を抵抗付きデカップリングコンデンサ35の抵抗素子37の最適抵抗値として算出する。

【解決手段】電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1とで決まる第1の共振周波数faと、電源配線の抵抗成分32A、32Bの合成抵抗値とインダクタ成分33A、33Bの合成インダクタンスと電源配線間の容量34の容量値C1と抵抗付きデカップリングコンデンサ35の容量値C2とで決まる第2の共振周波数fbを算出し、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35のコンデンサ36のインピーダンスに等しい値を抵抗付きデカップリングコンデンサ35の抵抗素子37の最適抵抗値として算出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧の異なる電源配線間に抵抗付きデカップリングコンデンサを接続する半導体集積回路を設計する場合に使用して好適な半導体集積回路の設計方法および設計用プログラムに関する。

【背景技術】

【0002】

半導体集積回路においては、その微細化に伴って、その大規模化・高速化が図られている。半導体集積回路が大規模化・高速化すると、その動作電流は高周波成分を多く含んだものとなる。この動作電流がインピーダンスを持つ電源配線を流れると、その電流振幅や周波数に応じて電源電圧の変動を引き起こす。

【0003】

内部回路の動作中に電源電圧が大きく変動すると、内部回路において遅延時間の変動や論理の誤認識が生じる場合があり、結果的に、そのような半導体集積回路は誤動作してしまうことになる。そこで、半導体集積回路においては、内部回路の動作中における電源電圧の変動を抑制する必要がある。

【0004】

ここに、半導体集積回路の電源配線系のインピーダンスを直流から高周波まで低くすることができれば、動作電流の高周波成分に起因する電源電圧の変動を小さくすることができる。そこで、電源配線系は、内部回路の動作状態によらず、低インピーダンスであることが望まれている。

【0005】

電源配線系の低インピーダンス化の手法の一つに、デカップリングコンデンサを用いる手法がある。デカップリングコンデンサとは、電圧の異なる電源配線間に電源電圧安定化の目的で挿入されるコンデンサのことであり、交流電流に対する電源配線系のインピーダンスを下げる働きがある。半導体集積回路内の電源配線の寄生容量もデカップリングコンデンサと同様の働きをする場合もある。

【0006】

ここで、コンデンサのインピーダンスZCは、コンデンサの容量値をC[F]、コンデンサに流れる電流の周波数をf[Hz]とすると、ZC=1/j2πfCで表される。したがって、デカップリングコンデンサを用いる場合には、電流の周波数が高いほど、電源配線系のインピーダンス低減効果は高くなる。

【0007】

多くの半導体集積回路のレイアウトでは、意図的に必要量のデカップリングコンデンサを事前に配置してから、残りの回路を配置したり、半導体集積回路のレイアウト後の空き領域にデカップリングコンデンサを配置したりして、電源配線系のインピーダンス低減化を図ることが行われている。

【0008】

電源配線系の低インピーダンス化のもう一つの手法に、電源配線の太幅化がある。この手法では、半導体集積回路の電源配線を多層化したり、メッシュ状にしたりすることにより、電源配線系のインピーダンスを小さく、かつ、均一にすることが行われる。更には、ダイにパッケージの電極と接続するための電極を複数個設け、パッケージの電極との接続に複数本のワイヤを用いることで、電源配線系のインピーダンスを下げることも行われている。

【0009】

ここで、インダクタのインピーダンスZLは、インダクタのインダクタンスをL、インダクタに流れる電流の周波数をfとすると、ZL=j2πfLで表される。したがって、電源配線の太幅化による電源配線系の低インピーダンス化は、直流電流に対する電源のインピーダンスを小さくするには十分な手法であるが、交流、特に、高周波成分を多く含む電流に対しては、電源配線のインダクタ成分が原因でインピーダンスが上がってしまうことになる。

【0010】

ところで、デカップリングコンデンサを用いる電源配線系の低インピーダンス化手法および電源配線の太幅化による電源配線系の低インピーダンス化手法は、半導体集積回路のレイアウトでは同時に用いられるのが一般的であるが、昨今の大規模かつ高速動作の半導体集積回路においては、これらの電源配線系の低インピーダンス化手法を用いても、半導体集積回路に誤動作が生じるケースが出てきた。

【0011】

これは、パッケージを含む電源配線(半導体集積回路内の電源配線、半導体集積回路とパッケージとの間のボンディングワイヤおよびパッケージを構成するインターポーザ中の電源配線)が持つ抵抗成分、インダクタ成分および寄生容量と、電源配線間に接続するデカップリングコンデンサとで構成されるRLC共振回路系による共振が原因で電源電圧が大きく変動してしまうことに起因するものである。このことを、図8を用いて、以下に説明する。

【0012】

図8はパッケージに組み込まれた半導体集積回路から見た電源配線系の等価回路図である。図8中、1は外部電源、2A、2Bはパッケージを含む電源配線の抵抗成分、3A、3Bはパッケージを含む電源配線のインダクタ成分、4は電源配線間の容量であり、電源配線間の容量4には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量とが含まれる。

【0013】

ここで、電源配線の抵抗成分2A、2Bの合成抵抗値をR、電源配線のインダクタ成分3A、3Bの合成インダクタンスをL、容量4の容量値をCとすると、図8に示す電源配線系は、fr=1/2π√LCで表される固有の共振周波数を持ち、共振時におけるQ値は、Q=2πfrL/Rとなるが、パッケージに組み込まれた半導体集積回路の電源配線系においては、Q値が高い値を持つ場合が多い。これは、半導体集積回路では、直流電流に対して電源配線系のインピーダンスは、特に小さくなるように設計されるからである。

【0014】

このように、直流電流に対して電源配線系のインピーダンスが小さくなるように設計される理由は、直流電流に対して電源配線系のインピーダンスが大きいと、電源配線での電圧降下が大きくなることから、半導体集積回路の外部電源の電圧と半導体集積回路に実際に印加される電圧が異なることになるばかりか、半導体集積回路の動作状態によって電源配線に流れる電流が変化するのにつれて半導体集積回路に実際に印加される電圧が変動してしまうことになり、半導体集積回路の誤動作を引き起こす要因となるからである。

【0015】

また、パッケージに組み込まれた半導体集積回路の電源配線系の共振対策として共振周波数をずらす手法がある。この手法は、半導体集積回路が持つ固有の動作電流の周波数および半導体集積回路の外部のプリント基板上の電源配線に重畳しているノイズ電流の周波数の付近でQ値が十分小さくなるようにパッケージに組み込まれた半導体集積回路の電源配線系の共振周波数を調整するというものである。具体的には、インダクタ成分3A、3Bの合成インダクタンスLや容量4の容量値Cを変化させることになる。

【0016】

しかしながら、この手法では、共振周波数をシフトした後の共振周波数におけるQ値が元の共振周波数におけるQ値よりも高くなってしまう場合がある。電源配線のインダクタ成分3A、3Bの合成インダクタンスLを大きくしたり、電源配線間の容量4の容量値Cを小さくしたりした場合である。

【0017】

逆に、電源配線のインダクタ成分3A、3Bの合成インダクタンスLを小さく、電源配線間の容量4の容量値Cを大きくすることができれば、共振周波数のシフトと共にQ値をある程度下げることができるが、Q値低減効果は小さい。例えば、Q値を半分にするためには、電源配線の抵抗成分2A、2Bの合成抵抗値Rおよびインダクタ成分3A、3Bの合成インダクタンスLを一定値とすると、電源配線間の容量4の容量値Cを元の値の4倍にしなくてはならない。このことは、半導体集積回路の面積の大幅な増加を意味しており、半導体集積回路のコスト面で現実的ではない。

【0018】

また、電源配線の抵抗成分2A、2Bの合成抵抗値Rおよび電源配線間の容量4の容量値Cを一定値にし、電源配線のインダクタ成分3A、3Bの合成インダクタンスLを小さくすることができれば、例えば、合成インダクタンスLを元の0.25倍にできれば、Q値を半分にすることができるが、電源配線を大幅に太くしたり、ボンディングワイヤの本数を増やしたり、インターポーザの配線の太幅化、多層化が必要となり、これもコスト面で現実的ではない。

【0019】

そこで、また、従来、パッケージに組み込まれた半導体集積回路の電源配線系のQ値を面積効率良く低減する手法として、抵抗付きデカップリングコンデンサを用いる方法が提案されている。例えば、特許文献1には、抵抗素子が直列接続されたデカップリングコンデンサ、いわゆる抵抗付きデカップリングコンデンサを用いた電源配線系のQ値低減回路が開示されている。

【0020】

図9は特許文献1が提案する電源配線系のQ値低減回路を示す図である。図9中、11は電源、12A、12Bは電源配線のインダクタ成分、13は抵抗素子が直列接続されていないデカップリングコンデンサ、いわゆる抵抗なしデカップリングコンデンサ、14は抵抗付きデカップリングコンデンサ、15は抵抗付きデカップリングコンデンサ14を構成するコンデンサ、16は抵抗付きデカップリングコンデンサ14を構成する抵抗素子、17は電子回路要素である。

【0021】

この電源配線系のQ値低減回路は、電圧の異なる電源配線間に抵抗付きデカップリングコンデンサ14を接続し、デカップリングコンデンサ14を構成する抵抗素子16をダンピング抵抗として機能させて電源配線系のQ値を低減するというものである。

【特許文献1】特開平6−132668号公報

【発明の開示】

【発明が解決しようとする課題】

【0022】

特許文献1によれば、抵抗素子16の抵抗値は、抵抗素子16を接続しない場合の電源配線系の共振ピークのインピーダンスよりも十分低い値になるように選ばれるとされているが、抵抗素子16の抵抗値の具体的な決定方法は示されていない。本発明者の知見によれば、抵抗素子16の抵抗値には最適値があり、抵抗素子16の抵抗値が高すぎても、低すぎても、電源配線系における十分なQ値低減効果を得ることができない。このことを、図10を用いて、以下に説明する。

【0023】

図10は電源配線間に挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を検討するために使用した電源配線系の等価回路を示す図であり、パッケージに組み込まれた半導体集積回路(電源配線間に抵抗付きデカップリングコンデンサを挿入した半導体集積回路)から見た電源配線系の等価回路を示している。

【0024】

図10中、21は外部電源、22A、22Bはパッケージを含む電源配線の抵抗成分、23A、23Bはパッケージを含む電源配線のインダクタ成分、24は電源配線間の容量であり、電源配線間の容量24には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量とが含まれる。25は電源配線間に挿入された抵抗付きデカップリングコンデンサであり、26は抵抗付きデカップリングコンデンサ25を構成するコンデンサ、27は抵抗付きデカップリングコンデンサ25を構成する抵抗素子である。

【0025】

図11は図10に示す電源配線系の共振周波数frとQ値との関係を示す図であり、回路シミュレータで求めたものである。本例では、抵抗成分22A、22Bの合成抵抗値を250mΩ、インダクタ成分23A、23Bの合成インダクタンスを10nH、容量24の容量値を0.8nF、コンデンサ26の容量値を0.2nFとし、抵抗素子27の抵抗値Rdを変化させた場合を示している。

【0026】

図11から分る通り、抵抗素子27の抵抗値Rdは、高すぎても、低すぎても、Q値低減効果が低い。本例では、抵抗素子27の抵抗値Rdとして、16Ω程度が最適値であり、この場合のQ値は、抵抗付きデカップリングコンデンサ25を用いず、抵抗なしデカップリングコンデンサを用いる場合、即ち、抵抗素子27の抵抗値Rdが0Ωの場合と比較すると、12.6から5.39にまで低減している。なお、この場合の共振周波数frは52.7MHzである。

【0027】

これと同じQ値低減効果を抵抗付きデカップリングコンデンサ25を用いずに、抵抗なしデカップリングコンデンサの増加だけで実現しようとすると、容量値として約5nFが必要となり、元の容量値(容量24の容量値+コンデンサ26の容量値)の5倍の容量が必要となってしまう。当然、これを実現するためには半導体集積回路の面積を大幅に大きくしなくてはならなくなる。

【0028】

以上のことから、抵抗付きデカップリングコンデンサを用いた半導体集積回路における電源配線系のQ値低減手法は、面積効率が良い手法といえるが、抵抗付きデカップリングコンデンサを構成する抵抗素子の抵抗値の決定においては最適値があるので、このことを十分に考慮して設計しなければならないことが分る。

【0029】

本発明は、かかる点に鑑み、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を自動算出することができる半導体集積回路の設計方法および設計用プログラムを提供することを目的とする。

【課題を解決するための手段】

【0030】

本発明中、第1の発明は、電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計方法であって、第1の算出手段が、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する工程と、第2の算出手段が、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する工程を含むものである。

【0031】

本発明中、第2の発明は、電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計用プログラムであって、コンピュータを、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する第1の算出手段、および、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する第2の算出手段として機能させるプログラムを含むものである。

【発明の効果】

【0032】

本発明によれば、第1の算出手段と、第2の算出手段とで、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出することができる。

【発明を実施するための最良の形態】

【0033】

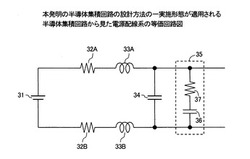

図1は本発明の半導体集積回路の設計方法の一実施形態が適用される半導体集積回路から見た電源配線系の等価回路図である。図1中、31は外部電源、32A、32Bはパッケージを含む電源配線(半導体集積回路内の電源配線、半導体集積回路とパッケージとの間のボンディングワイヤおよびパッケージを構成するインターポーザ中の電源配線)の抵抗成分、33A、33Bはパッケージを含む電源配線のインダクタ成分、34は電源配線間の容量であり、電源配線間の容量34には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量が含まれる。

【0034】

35は半導体集積回路内の電源配線間に挿入された抵抗付きデカップリングコンデンサであり、36は抵抗付きデカップリングコンデンサ35を構成するコンデンサ、37は抵抗付きデカップリングコンデンサ35を構成する抵抗素子である。本発明の半導体集積回路の設計方法の一実施形態は、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の抵抗値を自動算出する工程を含むものである。

【0035】

図2は本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの機能ブロック図である。図2中、41は第1の共振周波数算出手段、42は第2の共振周波数算出手段、43は共振周波数平均値算出手段、44は最適抵抗値算出手段、45は記憶手段である。

【0036】

記憶手段45には、図1に示す電源配線系の電源配線の抵抗成分32A、32Bの合成抵抗値R、電源配線のインダクタ成分33A、33Bの合成インダクタンスL、電源配線間の容量34の容量値C1、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2が記憶される。

【0037】

第1の共振周波数算出手段41は、図1に示す電源配線系について、抵抗付きデカップリングコンデンサ35を挿入しない場合の共振周波数、即ち、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1とで決まる第1の共振周波数faを算出するものであり、第1の共振周波数算出手段41が算出した第1の共振周波数faは記憶手段45に保存する。

【0038】

第2の共振周波数算出手段42は、図1に示す電源配線系について、抵抗素子37の抵抗値を0とした場合の共振周波数、即ち、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1と、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2とで決まる第2の共振周波数fbを算出するものであり、第2の共振周波数算出手段42が算出した第2の共振周波数fbは記憶手段45に保存される。

【0039】

共振周波数平均値算出手段43は、第1の共振周波数算出手段41が算出した第1の共振周波数faと、第2の共振周波数算出手段42が算出した第2の共振周波数fbとの平均値(fa+fb)/2を算出するものであり、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2は記憶手段45に保存される。

【0040】

最適抵抗値算出手段44は、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値を抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値として算出するものである。

【0041】

即ち、本発明の半導体集積回路の設計方法の一実施形態では、まず、第1の共振周波数算出手段41により、図1に示す電源配線系について、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1とで決まる第1の共振周波数faが算出される。

【0042】

次に、第2の共振周波数算出手段42により、図1に示す電源配線系について、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1と、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2とで決まる第2の共振周波数fbが算出される。

【0043】

次に、共振周波数平均値算出手段43により、第1の共振周波数算出手段41が算出した第1の共振周波数faと、第2の共振周波数算出手段42が算出した第2の共振周波数fbとの平均値(fa+fb)/2が算出される。

【0044】

次に、最適抵抗値算出手段44により、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値が、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値として算出される。

【0045】

ここで、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値が、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値となることを、図10および図11を使用して説明する。

【0046】

図11は、図10において、抵抗成分22A、22Bの合成抵抗値を250mΩ、インダクタ成分23A、23Bの合成インダクタンスを10nH、容量24の容量値を0.8nF、コンデンサ26の容量値を0.2nFとし、抵抗素子27の抵抗値Rdを変化させた場合の共振周波数frとQ値との関係のシミュレーション結果を示している。

【0047】

このシミュレーション結果によれば、抵抗素子27の抵抗値Rdを変化させた場合に、回路の共振によるQ値が最も低減されるのは、周波数が52.7MHzのときであり、このときの抵抗素子27の抵抗値Rdは16Ω程度となっている。

【0048】

本発明の半導体集積回路の設計方法の一実施形態により、抵抗素子27の最適抵抗値を算出する場合には、まず、第1の共振周波数算出手段41により、第1の共振周波数faを算出することになるが、fa=1/2π√(LC)=1/2π√(10[nH]×0.8[nF])=56.4MHzとなる。

【0049】

次に、第2の共振周波数算出手段42により、第2の共振周波数fbを算出することになるが、fb=1/2π√(LC)=1/2π√(10[nH]×1[nF])=50MHzとなる。

【0050】

次に、共振周波数平均値算出手段43により、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2を算出することになるが、(fa+fb)/2=(56.4MHz+50MHz)/2=53.2MHzとなる。

【0051】

次に、最適抵抗値算出手段44により、周波数(fa+fb)/2=53.2MHzにおけるコンデンサ26のインピーダンス|Zc|を算出することになるが、|Zc|=1/2πfC=1/2π×53.2[MHz]×0.2[nF]=15Ωとなる。

【0052】

このように、本発明の半導体集積回路の設計方法の一実施形態によれば、抵抗素子27の最適抵抗値は15Ωとなるが、これは、図11に示すシミュレーション結果による算出結果とかなり近い数字になっており、そのときのQ値は、シミュレーション結果との誤差も小さい。したがって、本発明の半導体集積回路の設計方法の一実施形態によれば、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37についても最適抵抗値を算出することができる。

【0053】

なお、本発明の半導体集積回路の設計方法の一実施形態では、第1の共振周波数算出手段41と第2の共振周波数算出手段42とで第1の算出手段が構成され、共振周波数平均値算出手段43と抵抗値算出手段44とで第2の算出手段が構成されている。但し、第1の共振周波数算出手段41による第1の共振周波数faの算出と、第2の共振周波数算出手段42による第2の共振周波数fbの算出は、どちらを先に実行しても良い。

【0054】

図3は本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの概略的構成図である。図3中、51はCPU(central processing unit)、52はROM(read only memory)、53はRAM(random access memory)、54はキーボードやマウス等の入力装置、55はディスプレイやプリンタ等の出力装置、56は外部装置との通信を行う通信装置、57はハードディスク装置(HDD)、58はハードディスク装置57により駆動されるハードディスクである。

【0055】

ハードディスク58には、本発明の半導体集積回路の設計用プログラムの一実施形態59や、図1に示す電源配線系の回路定数情報60(電源配線の抵抗成分32A、32Bの合成抵抗値R、電源配線のインダクタ成分33A、33Bの合成インダクタンスL、電源配線間の容量34の容量値C1、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2)などの格納に使用される。

【0056】

本発明の半導体集積回路の設計用プログラムの一実施形態59には、第1の共振周波数算出プログラム61、第2の共振周波数算出プログラム62、共振周波数平均値算出プログラム63、最適抵抗値算出プログラム64が含まれる。

【0057】

第1の共振周波数算出プログラム61は、CPU51を第1の共振周波数算出手段41として機能させるものである。第2の共振周波数算出プログラム62は、CPU52を第2の共振周波数算出手段42として機能させるものである。共振周波数平均値算出プログラム63は、CPU51を共振周波数平均値算出手段43として機能させるものである。最適抵抗値算出プログラム64は、CPU51を最適抵抗値算出手段44として機能させるものである。

【0058】

図4は本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の一例を説明するための概念図である。図4中、71は半導体集積回路のダイ、72はダイ71に配置された回路であり、他の回路とは電源が分離された回路である。通常、このような回路72は、マクロと呼ばれており、例えば、PLL(位相同期ループ)やAD(アナログ・デジタル)コンバータやDA(デジタル・アナログ)コンバータ等が該当する。73はパッケージのボンディングワイヤ、74はパッケージのインターポーザ中の電源配線である。

【0059】

本発明の半導体集積回路の設計方法の一実施形態は、マクロ72を設計する場合に使用することができる。なお、図4に示す例は、マクロ72の外側にデカップリングコンデンサ配置領域を有しない場合である。この場合、マクロ72内の電源配線、パッケージのボンディングワイヤ73およびパッケージのインターポーザ中の電源配線74が持つ抵抗成分、インダクタ成分、寄生容量と、マクロ72内に配置された抵抗なしデカップリングコンデンサとで共振回路が形成される。

【0060】

マクロ72には、その物理的なサイズの制限からQ値を小さくするのに十分な容量の抵抗なしデカップリングコンデンサを搭載できない場合が多く、この場合には、抵抗値を最適化した抵抗付きデカップリングコンデンサによるQ値低減手法の効果が高いと期待できる。具体的には、マクロ72内に配置されている抵抗なしデカップリングコンデンサのうち、マクロ72の動作に影響を与えない範囲で、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える。

【0061】

図5は本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の他の例を説明するための概念図である。図5中、81は半導体集積回路のダイ、82はダイ81に配置されたマクロ、83はパッケージのボンディングワイヤ、84はパッケージのインターポーザの配線、85はダイ81上に設けられたマクロ82のためのデカップリングコンデンサ配置領域である。デカップリングコンデンサ配置領域85に置かれたデカップリングコンデンサは全てマクロ82の電源配線に接続される。

【0062】

本発明の半導体集積回路の設計方法の一実施形態は、マクロ82を設計する場合に使用することができる。図5に示す例は、マクロ82の外側にデカップリングコンデンサ配置領域85を有する場合である。この場合、マクロ82の電源配線、パッケージのボンディングワイヤ83、パッケージのインターポーザの電源配線84が持つ抵抗成分、インダクタ成分、寄生容量と、デカップリングコンデンサ配置領域85に配置された抵抗なしデカップリングコンデンサとで共振回路が形成される。

【0063】

この例の場合、デカップリングコンデンサ配置領域85の物理的なサイズの制限からQ値を小さくするのに十分な容量の抵抗なしデカップリングコンデンサを搭載できない場合が多く、抵抗値を最適化した抵抗付きデカップリングコンデンサによるQ値低減手法の効果が高いと期待できる。具体的には、デカップリングコンデンサ配置領域85に配置されている抵抗なしデカップリングコンデンサのうち、マクロ82の動作に影響を与えない範囲で、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える。

【0064】

図6は本発明の半導体集積回路の設計方法の一実施形態の使用例を示すフローチャートであり、図4および図5に示すマクロ72、82を設計対象とする場合を示している。図6中、91は半導体集積回路レイアウト情報、92はパッケージ電気特性情報である。

【0065】

本例においては、まず、第1の共振周波数・Q値算出手段93により、半導体集積回路レイアウト情報91と、パッケージ電気特性情報92とを元に、マクロ72(又はマクロ82)について、抵抗付きデカップリングコンデンサを挿入しない状態で、パッケージを含む電源配線の抵抗成分の合成抵抗値、インダクタ成分の合成インピーダンス、電源配線間の容量の合成容量値を算出し、電源配線系の共振周波数とQ値とを算出する(ステップS1)。

【0066】

次に、マクロ72(又はマクロ82)の動作に影響を与えない範囲内において、電源配線間に接続された抵抗なしデカップリングコンデンサのうちで、抵抗付きデカップリングコンデンサに置き換え可能な抵抗なしデカップリングコンデンサの容量値の総和をデカップリングコンデンサ置き換え手段94に設定する(ステップS2)。この工程は、ユーザがコンピュータの表示画面上で、例えば、直接容量値を設定することにより行っても良いし、電源間容量の総和に対する割合を指定することにより行っても良い。

【0067】

次に、設定された抵抗付きデカップリングコンデンサに置き換え可能な抵抗なしデカップリングコンデンサの容量値の総和を元に、デカップリングコンデンサ置き換え手段94により、電源配線間に接続された抵抗なしデカップリングコンデンサのうちで、抵抗付きデカップリングコンデンサに置き換え可能なものについては、抵抗付きデカップリングコンデンサに置き換える(ステップS3)。

【0068】

次に、最適抵抗値算出手段95により、本発明の半導体集積回路の設計方法の一実施形態を実施して抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を算出する(ステップS4)。

【0069】

次に、第2の共振周波数・Q値算出手段96により、抵抗付きデカップリングコンデンサを挿入した状態での電源配線系の共振周波数とQ値を算出し(ステップS5)、これら共振周波数とQ値とを確認し(ステップS6)、Q値がマクロ72(又はマクロ82)のクライテリア(許容値)に対して高い場合は、ステップS2に戻り、再度、抵抗付きデカップリングコンデンサの割合を見直す。これに対して、Q値が適当な場合には、最適抵抗値決定工程を終了する。

【0070】

図7は本発明の半導体集積回路の設計方法の一実施形態の使用例を実施するためのコンピュータ・システムの概略的構成図である。図7に示すコンピュータ・システムは、図3に示すハードディスク58に半導体集積回路レイアウト情報91と、パッケージ電気特性情報92と、第1の共振周波数・Q値算出プログラム101と、デカップリングコンデンサ置き換えプログラム102と、第2の共振周波数・Q値算出プログラム103を格納するようにし、その他については、図3に示すコンピュータ・システムと同様に構成したものである。

【0071】

第1の共振周波数・Q値算出プログラム101は、CPU51を第1の共振周波数・Q値算出手段93として機能させるものである。デカップリングコンデンサ置き換えプログラム102は、CPU51をデカップリングコンデンサ置き換え手段94として機能させるものである。第2の共振周波数・Q値算出プログラム103は、CPU51を第2の共振周波数・Q値算出手段96として機能させるものである。また、本例では、本発明の半導体集積回路の設計方法の一実施形態59は、CPU51を最適抵抗値算出手段95として機能させる。

【0072】

以上のように、本発明の半導体集積回路の設計方法の一実施形態によれば、第1の共振周波数算出手段41と、第2の共振周波数算出手段42と、共振周波数平均値算出手段43と、最適抵抗値算出手段44とで、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出することができる。

【図面の簡単な説明】

【0073】

【図1】本発明の半導体集積回路の設計方法の一実施形態が適用される半導体集積回路から見た電源配線系の等価回路図である。

【図2】本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの機能ブロック図である。

【図3】本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの概略的構成図である。

【図4】本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の一例を説明するための概念図である。

【図5】本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の他の例を説明するための概念図である。

【図6】本発明の半導体集積回路の設計方法の一実施形態の使用例を示すフローチャートである。

【図7】本発明の半導体集積回路の設計方法の一実施形態の使用例を実施するためのコンピュータ・システムの概略的構成図である。

【図8】パッケージに組み込まれた半導体集積回路から見た電源配線系の等価回路図である。

【図9】特許文献1が提案する電源配線系のQ値低減回路を示す図である。

【図10】電源配線間に挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を検討するために使用した電源配線系の等価回路を示す図である。

【図11】図10に示す電源配線系の共振周波数とQ値との関係を示す図である。

【符号の説明】

【0074】

1…外部電源、2A、2B…電源配線の抵抗成分、3A、3B…電源配線のインダクタ成分、4…電源配線間の容量、11…電源、12A、12B…電源配線のインダクタ成分、13…抵抗なしデカップリングコンデンサ、14…抵抗付きデカップリングコンデンサ、15…コンデンサ、16…抵抗素子、17…電子回路要素、21…外部電源、22A、22B…電源配線の抵抗成分、23A、23B…電源配線のインダクタ成分、24…電源配線間の容量、25…抵抗付きデカップリングコンデンサ、26…コンデンサ、27…抵抗素子、31…外部電源、32A、32B…電源配線の抵抗成分、33A、33B…電源配線のインダクタ成分、34…電源配線間の容量、35…抵抗付きデカップリングコンデンサ、36…コンデンサ、37…抵抗素子、41…第1の共振周波数算出手段、42…第2の共振周波数算出手段、43…共振周波数平均値算出手段、44…最適抵抗値算出手段、45…記憶手段、51…CPU、52…ROM、53…RAM、54…入力装置、55…出力装置、56…通信装置、57…ハードディスク装置(HDD)、58…ハードディスク、59…本発明の半導体集積回路の設計用プログラムの一実施形態、60…回路定数情報、61…第1の共振周波数算出プログラム、62…第2の共振周波数算出プログラム、63…共振周波数平均値算出プログラム、64…最適抵抗値算出プログラム、71…ダイ、72…マクロ、73…ボンディングワイヤ、74…インターポーザの電源配線、81…ダイ、82…マクロ、83…ボンディングワイヤ、84…インターポーザの電源配線、85…デカップリングコンデンサ配置領域、91…半導体集積回路レイアウト情報、92…パッケージ電気特性情報、93…第1の共振周波数・Q値算出手段、94…デカップリングコンデンサ置き換え手段、95…最適抵抗値算出手段、96…第2の共振周波数・Q値算出手段、101…第1の共振周波数・Q値算出プログラム、102…デカップリングコンデンサ置き換えプログラム、103…第2の共振周波数・Q値算出プログラム

【技術分野】

【0001】

本発明は、電圧の異なる電源配線間に抵抗付きデカップリングコンデンサを接続する半導体集積回路を設計する場合に使用して好適な半導体集積回路の設計方法および設計用プログラムに関する。

【背景技術】

【0002】

半導体集積回路においては、その微細化に伴って、その大規模化・高速化が図られている。半導体集積回路が大規模化・高速化すると、その動作電流は高周波成分を多く含んだものとなる。この動作電流がインピーダンスを持つ電源配線を流れると、その電流振幅や周波数に応じて電源電圧の変動を引き起こす。

【0003】

内部回路の動作中に電源電圧が大きく変動すると、内部回路において遅延時間の変動や論理の誤認識が生じる場合があり、結果的に、そのような半導体集積回路は誤動作してしまうことになる。そこで、半導体集積回路においては、内部回路の動作中における電源電圧の変動を抑制する必要がある。

【0004】

ここに、半導体集積回路の電源配線系のインピーダンスを直流から高周波まで低くすることができれば、動作電流の高周波成分に起因する電源電圧の変動を小さくすることができる。そこで、電源配線系は、内部回路の動作状態によらず、低インピーダンスであることが望まれている。

【0005】

電源配線系の低インピーダンス化の手法の一つに、デカップリングコンデンサを用いる手法がある。デカップリングコンデンサとは、電圧の異なる電源配線間に電源電圧安定化の目的で挿入されるコンデンサのことであり、交流電流に対する電源配線系のインピーダンスを下げる働きがある。半導体集積回路内の電源配線の寄生容量もデカップリングコンデンサと同様の働きをする場合もある。

【0006】

ここで、コンデンサのインピーダンスZCは、コンデンサの容量値をC[F]、コンデンサに流れる電流の周波数をf[Hz]とすると、ZC=1/j2πfCで表される。したがって、デカップリングコンデンサを用いる場合には、電流の周波数が高いほど、電源配線系のインピーダンス低減効果は高くなる。

【0007】

多くの半導体集積回路のレイアウトでは、意図的に必要量のデカップリングコンデンサを事前に配置してから、残りの回路を配置したり、半導体集積回路のレイアウト後の空き領域にデカップリングコンデンサを配置したりして、電源配線系のインピーダンス低減化を図ることが行われている。

【0008】

電源配線系の低インピーダンス化のもう一つの手法に、電源配線の太幅化がある。この手法では、半導体集積回路の電源配線を多層化したり、メッシュ状にしたりすることにより、電源配線系のインピーダンスを小さく、かつ、均一にすることが行われる。更には、ダイにパッケージの電極と接続するための電極を複数個設け、パッケージの電極との接続に複数本のワイヤを用いることで、電源配線系のインピーダンスを下げることも行われている。

【0009】

ここで、インダクタのインピーダンスZLは、インダクタのインダクタンスをL、インダクタに流れる電流の周波数をfとすると、ZL=j2πfLで表される。したがって、電源配線の太幅化による電源配線系の低インピーダンス化は、直流電流に対する電源のインピーダンスを小さくするには十分な手法であるが、交流、特に、高周波成分を多く含む電流に対しては、電源配線のインダクタ成分が原因でインピーダンスが上がってしまうことになる。

【0010】

ところで、デカップリングコンデンサを用いる電源配線系の低インピーダンス化手法および電源配線の太幅化による電源配線系の低インピーダンス化手法は、半導体集積回路のレイアウトでは同時に用いられるのが一般的であるが、昨今の大規模かつ高速動作の半導体集積回路においては、これらの電源配線系の低インピーダンス化手法を用いても、半導体集積回路に誤動作が生じるケースが出てきた。

【0011】

これは、パッケージを含む電源配線(半導体集積回路内の電源配線、半導体集積回路とパッケージとの間のボンディングワイヤおよびパッケージを構成するインターポーザ中の電源配線)が持つ抵抗成分、インダクタ成分および寄生容量と、電源配線間に接続するデカップリングコンデンサとで構成されるRLC共振回路系による共振が原因で電源電圧が大きく変動してしまうことに起因するものである。このことを、図8を用いて、以下に説明する。

【0012】

図8はパッケージに組み込まれた半導体集積回路から見た電源配線系の等価回路図である。図8中、1は外部電源、2A、2Bはパッケージを含む電源配線の抵抗成分、3A、3Bはパッケージを含む電源配線のインダクタ成分、4は電源配線間の容量であり、電源配線間の容量4には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量とが含まれる。

【0013】

ここで、電源配線の抵抗成分2A、2Bの合成抵抗値をR、電源配線のインダクタ成分3A、3Bの合成インダクタンスをL、容量4の容量値をCとすると、図8に示す電源配線系は、fr=1/2π√LCで表される固有の共振周波数を持ち、共振時におけるQ値は、Q=2πfrL/Rとなるが、パッケージに組み込まれた半導体集積回路の電源配線系においては、Q値が高い値を持つ場合が多い。これは、半導体集積回路では、直流電流に対して電源配線系のインピーダンスは、特に小さくなるように設計されるからである。

【0014】

このように、直流電流に対して電源配線系のインピーダンスが小さくなるように設計される理由は、直流電流に対して電源配線系のインピーダンスが大きいと、電源配線での電圧降下が大きくなることから、半導体集積回路の外部電源の電圧と半導体集積回路に実際に印加される電圧が異なることになるばかりか、半導体集積回路の動作状態によって電源配線に流れる電流が変化するのにつれて半導体集積回路に実際に印加される電圧が変動してしまうことになり、半導体集積回路の誤動作を引き起こす要因となるからである。

【0015】

また、パッケージに組み込まれた半導体集積回路の電源配線系の共振対策として共振周波数をずらす手法がある。この手法は、半導体集積回路が持つ固有の動作電流の周波数および半導体集積回路の外部のプリント基板上の電源配線に重畳しているノイズ電流の周波数の付近でQ値が十分小さくなるようにパッケージに組み込まれた半導体集積回路の電源配線系の共振周波数を調整するというものである。具体的には、インダクタ成分3A、3Bの合成インダクタンスLや容量4の容量値Cを変化させることになる。

【0016】

しかしながら、この手法では、共振周波数をシフトした後の共振周波数におけるQ値が元の共振周波数におけるQ値よりも高くなってしまう場合がある。電源配線のインダクタ成分3A、3Bの合成インダクタンスLを大きくしたり、電源配線間の容量4の容量値Cを小さくしたりした場合である。

【0017】

逆に、電源配線のインダクタ成分3A、3Bの合成インダクタンスLを小さく、電源配線間の容量4の容量値Cを大きくすることができれば、共振周波数のシフトと共にQ値をある程度下げることができるが、Q値低減効果は小さい。例えば、Q値を半分にするためには、電源配線の抵抗成分2A、2Bの合成抵抗値Rおよびインダクタ成分3A、3Bの合成インダクタンスLを一定値とすると、電源配線間の容量4の容量値Cを元の値の4倍にしなくてはならない。このことは、半導体集積回路の面積の大幅な増加を意味しており、半導体集積回路のコスト面で現実的ではない。

【0018】

また、電源配線の抵抗成分2A、2Bの合成抵抗値Rおよび電源配線間の容量4の容量値Cを一定値にし、電源配線のインダクタ成分3A、3Bの合成インダクタンスLを小さくすることができれば、例えば、合成インダクタンスLを元の0.25倍にできれば、Q値を半分にすることができるが、電源配線を大幅に太くしたり、ボンディングワイヤの本数を増やしたり、インターポーザの配線の太幅化、多層化が必要となり、これもコスト面で現実的ではない。

【0019】

そこで、また、従来、パッケージに組み込まれた半導体集積回路の電源配線系のQ値を面積効率良く低減する手法として、抵抗付きデカップリングコンデンサを用いる方法が提案されている。例えば、特許文献1には、抵抗素子が直列接続されたデカップリングコンデンサ、いわゆる抵抗付きデカップリングコンデンサを用いた電源配線系のQ値低減回路が開示されている。

【0020】

図9は特許文献1が提案する電源配線系のQ値低減回路を示す図である。図9中、11は電源、12A、12Bは電源配線のインダクタ成分、13は抵抗素子が直列接続されていないデカップリングコンデンサ、いわゆる抵抗なしデカップリングコンデンサ、14は抵抗付きデカップリングコンデンサ、15は抵抗付きデカップリングコンデンサ14を構成するコンデンサ、16は抵抗付きデカップリングコンデンサ14を構成する抵抗素子、17は電子回路要素である。

【0021】

この電源配線系のQ値低減回路は、電圧の異なる電源配線間に抵抗付きデカップリングコンデンサ14を接続し、デカップリングコンデンサ14を構成する抵抗素子16をダンピング抵抗として機能させて電源配線系のQ値を低減するというものである。

【特許文献1】特開平6−132668号公報

【発明の開示】

【発明が解決しようとする課題】

【0022】

特許文献1によれば、抵抗素子16の抵抗値は、抵抗素子16を接続しない場合の電源配線系の共振ピークのインピーダンスよりも十分低い値になるように選ばれるとされているが、抵抗素子16の抵抗値の具体的な決定方法は示されていない。本発明者の知見によれば、抵抗素子16の抵抗値には最適値があり、抵抗素子16の抵抗値が高すぎても、低すぎても、電源配線系における十分なQ値低減効果を得ることができない。このことを、図10を用いて、以下に説明する。

【0023】

図10は電源配線間に挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を検討するために使用した電源配線系の等価回路を示す図であり、パッケージに組み込まれた半導体集積回路(電源配線間に抵抗付きデカップリングコンデンサを挿入した半導体集積回路)から見た電源配線系の等価回路を示している。

【0024】

図10中、21は外部電源、22A、22Bはパッケージを含む電源配線の抵抗成分、23A、23Bはパッケージを含む電源配線のインダクタ成分、24は電源配線間の容量であり、電源配線間の容量24には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量とが含まれる。25は電源配線間に挿入された抵抗付きデカップリングコンデンサであり、26は抵抗付きデカップリングコンデンサ25を構成するコンデンサ、27は抵抗付きデカップリングコンデンサ25を構成する抵抗素子である。

【0025】

図11は図10に示す電源配線系の共振周波数frとQ値との関係を示す図であり、回路シミュレータで求めたものである。本例では、抵抗成分22A、22Bの合成抵抗値を250mΩ、インダクタ成分23A、23Bの合成インダクタンスを10nH、容量24の容量値を0.8nF、コンデンサ26の容量値を0.2nFとし、抵抗素子27の抵抗値Rdを変化させた場合を示している。

【0026】

図11から分る通り、抵抗素子27の抵抗値Rdは、高すぎても、低すぎても、Q値低減効果が低い。本例では、抵抗素子27の抵抗値Rdとして、16Ω程度が最適値であり、この場合のQ値は、抵抗付きデカップリングコンデンサ25を用いず、抵抗なしデカップリングコンデンサを用いる場合、即ち、抵抗素子27の抵抗値Rdが0Ωの場合と比較すると、12.6から5.39にまで低減している。なお、この場合の共振周波数frは52.7MHzである。

【0027】

これと同じQ値低減効果を抵抗付きデカップリングコンデンサ25を用いずに、抵抗なしデカップリングコンデンサの増加だけで実現しようとすると、容量値として約5nFが必要となり、元の容量値(容量24の容量値+コンデンサ26の容量値)の5倍の容量が必要となってしまう。当然、これを実現するためには半導体集積回路の面積を大幅に大きくしなくてはならなくなる。

【0028】

以上のことから、抵抗付きデカップリングコンデンサを用いた半導体集積回路における電源配線系のQ値低減手法は、面積効率が良い手法といえるが、抵抗付きデカップリングコンデンサを構成する抵抗素子の抵抗値の決定においては最適値があるので、このことを十分に考慮して設計しなければならないことが分る。

【0029】

本発明は、かかる点に鑑み、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を自動算出することができる半導体集積回路の設計方法および設計用プログラムを提供することを目的とする。

【課題を解決するための手段】

【0030】

本発明中、第1の発明は、電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計方法であって、第1の算出手段が、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する工程と、第2の算出手段が、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する工程を含むものである。

【0031】

本発明中、第2の発明は、電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計用プログラムであって、コンピュータを、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する第1の算出手段、および、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する第2の算出手段として機能させるプログラムを含むものである。

【発明の効果】

【0032】

本発明によれば、第1の算出手段と、第2の算出手段とで、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出することができる。

【発明を実施するための最良の形態】

【0033】

図1は本発明の半導体集積回路の設計方法の一実施形態が適用される半導体集積回路から見た電源配線系の等価回路図である。図1中、31は外部電源、32A、32Bはパッケージを含む電源配線(半導体集積回路内の電源配線、半導体集積回路とパッケージとの間のボンディングワイヤおよびパッケージを構成するインターポーザ中の電源配線)の抵抗成分、33A、33Bはパッケージを含む電源配線のインダクタ成分、34は電源配線間の容量であり、電源配線間の容量34には、電源配線の寄生容量と電源配線間に意図的に挿入されたデカップリングコンデンサの容量が含まれる。

【0034】

35は半導体集積回路内の電源配線間に挿入された抵抗付きデカップリングコンデンサであり、36は抵抗付きデカップリングコンデンサ35を構成するコンデンサ、37は抵抗付きデカップリングコンデンサ35を構成する抵抗素子である。本発明の半導体集積回路の設計方法の一実施形態は、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の抵抗値を自動算出する工程を含むものである。

【0035】

図2は本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの機能ブロック図である。図2中、41は第1の共振周波数算出手段、42は第2の共振周波数算出手段、43は共振周波数平均値算出手段、44は最適抵抗値算出手段、45は記憶手段である。

【0036】

記憶手段45には、図1に示す電源配線系の電源配線の抵抗成分32A、32Bの合成抵抗値R、電源配線のインダクタ成分33A、33Bの合成インダクタンスL、電源配線間の容量34の容量値C1、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2が記憶される。

【0037】

第1の共振周波数算出手段41は、図1に示す電源配線系について、抵抗付きデカップリングコンデンサ35を挿入しない場合の共振周波数、即ち、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1とで決まる第1の共振周波数faを算出するものであり、第1の共振周波数算出手段41が算出した第1の共振周波数faは記憶手段45に保存する。

【0038】

第2の共振周波数算出手段42は、図1に示す電源配線系について、抵抗素子37の抵抗値を0とした場合の共振周波数、即ち、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1と、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2とで決まる第2の共振周波数fbを算出するものであり、第2の共振周波数算出手段42が算出した第2の共振周波数fbは記憶手段45に保存される。

【0039】

共振周波数平均値算出手段43は、第1の共振周波数算出手段41が算出した第1の共振周波数faと、第2の共振周波数算出手段42が算出した第2の共振周波数fbとの平均値(fa+fb)/2を算出するものであり、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2は記憶手段45に保存される。

【0040】

最適抵抗値算出手段44は、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値を抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値として算出するものである。

【0041】

即ち、本発明の半導体集積回路の設計方法の一実施形態では、まず、第1の共振周波数算出手段41により、図1に示す電源配線系について、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1とで決まる第1の共振周波数faが算出される。

【0042】

次に、第2の共振周波数算出手段42により、図1に示す電源配線系について、電源配線の抵抗成分32A、32Bの合成抵抗値Rと、電源配線のインダクタ成分33A、33Bの合成インダクタンスLと、電源配線間の容量34の容量値C1と、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2とで決まる第2の共振周波数fbが算出される。

【0043】

次に、共振周波数平均値算出手段43により、第1の共振周波数算出手段41が算出した第1の共振周波数faと、第2の共振周波数算出手段42が算出した第2の共振周波数fbとの平均値(fa+fb)/2が算出される。

【0044】

次に、最適抵抗値算出手段44により、共振周波数平均値算出手段43が算出した第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値が、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値として算出される。

【0045】

ここで、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2における抵抗付きデカップリングコンデンサ35を構成するコンデンサ36のインピーダンスに等しい値が、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37の最適抵抗値となることを、図10および図11を使用して説明する。

【0046】

図11は、図10において、抵抗成分22A、22Bの合成抵抗値を250mΩ、インダクタ成分23A、23Bの合成インダクタンスを10nH、容量24の容量値を0.8nF、コンデンサ26の容量値を0.2nFとし、抵抗素子27の抵抗値Rdを変化させた場合の共振周波数frとQ値との関係のシミュレーション結果を示している。

【0047】

このシミュレーション結果によれば、抵抗素子27の抵抗値Rdを変化させた場合に、回路の共振によるQ値が最も低減されるのは、周波数が52.7MHzのときであり、このときの抵抗素子27の抵抗値Rdは16Ω程度となっている。

【0048】

本発明の半導体集積回路の設計方法の一実施形態により、抵抗素子27の最適抵抗値を算出する場合には、まず、第1の共振周波数算出手段41により、第1の共振周波数faを算出することになるが、fa=1/2π√(LC)=1/2π√(10[nH]×0.8[nF])=56.4MHzとなる。

【0049】

次に、第2の共振周波数算出手段42により、第2の共振周波数fbを算出することになるが、fb=1/2π√(LC)=1/2π√(10[nH]×1[nF])=50MHzとなる。

【0050】

次に、共振周波数平均値算出手段43により、第1の共振周波数faと第2の共振周波数fbの平均値(fa+fb)/2を算出することになるが、(fa+fb)/2=(56.4MHz+50MHz)/2=53.2MHzとなる。

【0051】

次に、最適抵抗値算出手段44により、周波数(fa+fb)/2=53.2MHzにおけるコンデンサ26のインピーダンス|Zc|を算出することになるが、|Zc|=1/2πfC=1/2π×53.2[MHz]×0.2[nF]=15Ωとなる。

【0052】

このように、本発明の半導体集積回路の設計方法の一実施形態によれば、抵抗素子27の最適抵抗値は15Ωとなるが、これは、図11に示すシミュレーション結果による算出結果とかなり近い数字になっており、そのときのQ値は、シミュレーション結果との誤差も小さい。したがって、本発明の半導体集積回路の設計方法の一実施形態によれば、抵抗付きデカップリングコンデンサ35を構成する抵抗素子37についても最適抵抗値を算出することができる。

【0053】

なお、本発明の半導体集積回路の設計方法の一実施形態では、第1の共振周波数算出手段41と第2の共振周波数算出手段42とで第1の算出手段が構成され、共振周波数平均値算出手段43と抵抗値算出手段44とで第2の算出手段が構成されている。但し、第1の共振周波数算出手段41による第1の共振周波数faの算出と、第2の共振周波数算出手段42による第2の共振周波数fbの算出は、どちらを先に実行しても良い。

【0054】

図3は本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの概略的構成図である。図3中、51はCPU(central processing unit)、52はROM(read only memory)、53はRAM(random access memory)、54はキーボードやマウス等の入力装置、55はディスプレイやプリンタ等の出力装置、56は外部装置との通信を行う通信装置、57はハードディスク装置(HDD)、58はハードディスク装置57により駆動されるハードディスクである。

【0055】

ハードディスク58には、本発明の半導体集積回路の設計用プログラムの一実施形態59や、図1に示す電源配線系の回路定数情報60(電源配線の抵抗成分32A、32Bの合成抵抗値R、電源配線のインダクタ成分33A、33Bの合成インダクタンスL、電源配線間の容量34の容量値C1、抵抗付きデカップリングコンデンサ35を構成するコンデンサ36の容量値C2)などの格納に使用される。

【0056】

本発明の半導体集積回路の設計用プログラムの一実施形態59には、第1の共振周波数算出プログラム61、第2の共振周波数算出プログラム62、共振周波数平均値算出プログラム63、最適抵抗値算出プログラム64が含まれる。

【0057】

第1の共振周波数算出プログラム61は、CPU51を第1の共振周波数算出手段41として機能させるものである。第2の共振周波数算出プログラム62は、CPU52を第2の共振周波数算出手段42として機能させるものである。共振周波数平均値算出プログラム63は、CPU51を共振周波数平均値算出手段43として機能させるものである。最適抵抗値算出プログラム64は、CPU51を最適抵抗値算出手段44として機能させるものである。

【0058】

図4は本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の一例を説明するための概念図である。図4中、71は半導体集積回路のダイ、72はダイ71に配置された回路であり、他の回路とは電源が分離された回路である。通常、このような回路72は、マクロと呼ばれており、例えば、PLL(位相同期ループ)やAD(アナログ・デジタル)コンバータやDA(デジタル・アナログ)コンバータ等が該当する。73はパッケージのボンディングワイヤ、74はパッケージのインターポーザ中の電源配線である。

【0059】

本発明の半導体集積回路の設計方法の一実施形態は、マクロ72を設計する場合に使用することができる。なお、図4に示す例は、マクロ72の外側にデカップリングコンデンサ配置領域を有しない場合である。この場合、マクロ72内の電源配線、パッケージのボンディングワイヤ73およびパッケージのインターポーザ中の電源配線74が持つ抵抗成分、インダクタ成分、寄生容量と、マクロ72内に配置された抵抗なしデカップリングコンデンサとで共振回路が形成される。

【0060】

マクロ72には、その物理的なサイズの制限からQ値を小さくするのに十分な容量の抵抗なしデカップリングコンデンサを搭載できない場合が多く、この場合には、抵抗値を最適化した抵抗付きデカップリングコンデンサによるQ値低減手法の効果が高いと期待できる。具体的には、マクロ72内に配置されている抵抗なしデカップリングコンデンサのうち、マクロ72の動作に影響を与えない範囲で、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える。

【0061】

図5は本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の他の例を説明するための概念図である。図5中、81は半導体集積回路のダイ、82はダイ81に配置されたマクロ、83はパッケージのボンディングワイヤ、84はパッケージのインターポーザの配線、85はダイ81上に設けられたマクロ82のためのデカップリングコンデンサ配置領域である。デカップリングコンデンサ配置領域85に置かれたデカップリングコンデンサは全てマクロ82の電源配線に接続される。

【0062】

本発明の半導体集積回路の設計方法の一実施形態は、マクロ82を設計する場合に使用することができる。図5に示す例は、マクロ82の外側にデカップリングコンデンサ配置領域85を有する場合である。この場合、マクロ82の電源配線、パッケージのボンディングワイヤ83、パッケージのインターポーザの電源配線84が持つ抵抗成分、インダクタ成分、寄生容量と、デカップリングコンデンサ配置領域85に配置された抵抗なしデカップリングコンデンサとで共振回路が形成される。

【0063】

この例の場合、デカップリングコンデンサ配置領域85の物理的なサイズの制限からQ値を小さくするのに十分な容量の抵抗なしデカップリングコンデンサを搭載できない場合が多く、抵抗値を最適化した抵抗付きデカップリングコンデンサによるQ値低減手法の効果が高いと期待できる。具体的には、デカップリングコンデンサ配置領域85に配置されている抵抗なしデカップリングコンデンサのうち、マクロ82の動作に影響を与えない範囲で、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える。

【0064】

図6は本発明の半導体集積回路の設計方法の一実施形態の使用例を示すフローチャートであり、図4および図5に示すマクロ72、82を設計対象とする場合を示している。図6中、91は半導体集積回路レイアウト情報、92はパッケージ電気特性情報である。

【0065】

本例においては、まず、第1の共振周波数・Q値算出手段93により、半導体集積回路レイアウト情報91と、パッケージ電気特性情報92とを元に、マクロ72(又はマクロ82)について、抵抗付きデカップリングコンデンサを挿入しない状態で、パッケージを含む電源配線の抵抗成分の合成抵抗値、インダクタ成分の合成インピーダンス、電源配線間の容量の合成容量値を算出し、電源配線系の共振周波数とQ値とを算出する(ステップS1)。

【0066】

次に、マクロ72(又はマクロ82)の動作に影響を与えない範囲内において、電源配線間に接続された抵抗なしデカップリングコンデンサのうちで、抵抗付きデカップリングコンデンサに置き換え可能な抵抗なしデカップリングコンデンサの容量値の総和をデカップリングコンデンサ置き換え手段94に設定する(ステップS2)。この工程は、ユーザがコンピュータの表示画面上で、例えば、直接容量値を設定することにより行っても良いし、電源間容量の総和に対する割合を指定することにより行っても良い。

【0067】

次に、設定された抵抗付きデカップリングコンデンサに置き換え可能な抵抗なしデカップリングコンデンサの容量値の総和を元に、デカップリングコンデンサ置き換え手段94により、電源配線間に接続された抵抗なしデカップリングコンデンサのうちで、抵抗付きデカップリングコンデンサに置き換え可能なものについては、抵抗付きデカップリングコンデンサに置き換える(ステップS3)。

【0068】

次に、最適抵抗値算出手段95により、本発明の半導体集積回路の設計方法の一実施形態を実施して抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を算出する(ステップS4)。

【0069】

次に、第2の共振周波数・Q値算出手段96により、抵抗付きデカップリングコンデンサを挿入した状態での電源配線系の共振周波数とQ値を算出し(ステップS5)、これら共振周波数とQ値とを確認し(ステップS6)、Q値がマクロ72(又はマクロ82)のクライテリア(許容値)に対して高い場合は、ステップS2に戻り、再度、抵抗付きデカップリングコンデンサの割合を見直す。これに対して、Q値が適当な場合には、最適抵抗値決定工程を終了する。

【0070】

図7は本発明の半導体集積回路の設計方法の一実施形態の使用例を実施するためのコンピュータ・システムの概略的構成図である。図7に示すコンピュータ・システムは、図3に示すハードディスク58に半導体集積回路レイアウト情報91と、パッケージ電気特性情報92と、第1の共振周波数・Q値算出プログラム101と、デカップリングコンデンサ置き換えプログラム102と、第2の共振周波数・Q値算出プログラム103を格納するようにし、その他については、図3に示すコンピュータ・システムと同様に構成したものである。

【0071】

第1の共振周波数・Q値算出プログラム101は、CPU51を第1の共振周波数・Q値算出手段93として機能させるものである。デカップリングコンデンサ置き換えプログラム102は、CPU51をデカップリングコンデンサ置き換え手段94として機能させるものである。第2の共振周波数・Q値算出プログラム103は、CPU51を第2の共振周波数・Q値算出手段96として機能させるものである。また、本例では、本発明の半導体集積回路の設計方法の一実施形態59は、CPU51を最適抵抗値算出手段95として機能させる。

【0072】

以上のように、本発明の半導体集積回路の設計方法の一実施形態によれば、第1の共振周波数算出手段41と、第2の共振周波数算出手段42と、共振周波数平均値算出手段43と、最適抵抗値算出手段44とで、半導体集積回路内の電圧の異なる電源配線間に電源電圧安定化のために挿入する抵抗付きデカップリングコンデンサの抵抗素子の最適抵抗値を自動算出することができる。

【図面の簡単な説明】

【0073】

【図1】本発明の半導体集積回路の設計方法の一実施形態が適用される半導体集積回路から見た電源配線系の等価回路図である。

【図2】本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの機能ブロック図である。

【図3】本発明の半導体集積回路の設計方法の一実施形態を実施するためのコンピュータ・システムの概略的構成図である。

【図4】本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の一例を説明するための概念図である。

【図5】本発明の半導体集積回路の設計方法の一実施形態が使用される半導体集積回路の他の例を説明するための概念図である。

【図6】本発明の半導体集積回路の設計方法の一実施形態の使用例を示すフローチャートである。

【図7】本発明の半導体集積回路の設計方法の一実施形態の使用例を実施するためのコンピュータ・システムの概略的構成図である。

【図8】パッケージに組み込まれた半導体集積回路から見た電源配線系の等価回路図である。

【図9】特許文献1が提案する電源配線系のQ値低減回路を示す図である。

【図10】電源配線間に挿入する抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値を検討するために使用した電源配線系の等価回路を示す図である。

【図11】図10に示す電源配線系の共振周波数とQ値との関係を示す図である。

【符号の説明】

【0074】

1…外部電源、2A、2B…電源配線の抵抗成分、3A、3B…電源配線のインダクタ成分、4…電源配線間の容量、11…電源、12A、12B…電源配線のインダクタ成分、13…抵抗なしデカップリングコンデンサ、14…抵抗付きデカップリングコンデンサ、15…コンデンサ、16…抵抗素子、17…電子回路要素、21…外部電源、22A、22B…電源配線の抵抗成分、23A、23B…電源配線のインダクタ成分、24…電源配線間の容量、25…抵抗付きデカップリングコンデンサ、26…コンデンサ、27…抵抗素子、31…外部電源、32A、32B…電源配線の抵抗成分、33A、33B…電源配線のインダクタ成分、34…電源配線間の容量、35…抵抗付きデカップリングコンデンサ、36…コンデンサ、37…抵抗素子、41…第1の共振周波数算出手段、42…第2の共振周波数算出手段、43…共振周波数平均値算出手段、44…最適抵抗値算出手段、45…記憶手段、51…CPU、52…ROM、53…RAM、54…入力装置、55…出力装置、56…通信装置、57…ハードディスク装置(HDD)、58…ハードディスク、59…本発明の半導体集積回路の設計用プログラムの一実施形態、60…回路定数情報、61…第1の共振周波数算出プログラム、62…第2の共振周波数算出プログラム、63…共振周波数平均値算出プログラム、64…最適抵抗値算出プログラム、71…ダイ、72…マクロ、73…ボンディングワイヤ、74…インターポーザの電源配線、81…ダイ、82…マクロ、83…ボンディングワイヤ、84…インターポーザの電源配線、85…デカップリングコンデンサ配置領域、91…半導体集積回路レイアウト情報、92…パッケージ電気特性情報、93…第1の共振周波数・Q値算出手段、94…デカップリングコンデンサ置き換え手段、95…最適抵抗値算出手段、96…第2の共振周波数・Q値算出手段、101…第1の共振周波数・Q値算出プログラム、102…デカップリングコンデンサ置き換えプログラム、103…第2の共振周波数・Q値算出プログラム

【特許請求の範囲】

【請求項1】

電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計方法であって、

第1の算出手段が、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する工程と、

第2の算出手段が、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する工程を含む

ことを特徴とする半導体集積回路の設計方法。

【請求項2】

前記第1の共振周波数および前記第2の共振周波数を算出する前に、デカップリングコンデンサ置き換え手段が、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える工程を含む

ことを特徴とする請求項1に記載の半導体集積回路の設計方法。

【請求項3】

電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計用プログラムであって、

コンピュータを、

前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する第1の算出手段、および、

前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する第2の算出手段として機能させるプログラムを含む

ことを特徴とする半導体集積回路の設計用プログラム。

【請求項4】

前記第1の共振周波数および前記第2の共振周波数を算出する前に、前記コンピュータを、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換えるデカップリングコンデンサ置き換え手段として機能させるプログラムを含む

ことを特徴とする請求項3に記載の半導体集積回路の設計用プログラム。

【請求項1】

電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計方法であって、

第1の算出手段が、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する工程と、

第2の算出手段が、前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する工程を含む

ことを特徴とする半導体集積回路の設計方法。

【請求項2】

前記第1の共振周波数および前記第2の共振周波数を算出する前に、デカップリングコンデンサ置き換え手段が、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換える工程を含む

ことを特徴とする請求項1に記載の半導体集積回路の設計方法。

【請求項3】

電源配線間に抵抗なしデカップリングコンデンサと抵抗付きデカップリングコンデンサを接続する半導体集積回路の設計用プログラムであって、

コンピュータを、

前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサとで決まる第1の共振周波数と、前記電源配線の抵抗成分、インダクタ成分および寄生容量と、前記抵抗なしデカップリングコンデンサおよび前記抵抗付きデカップリングコンデンサを構成するコンデンサとで決まる第2の共振周波数を算出する第1の算出手段、および、

前記第1の共振周波数と前記第2の共振周波数との平均値を算出し、該平均値における前記抵抗付きデカップリングコンデンサを構成するコンデンサのインピーダンスに等しい値を前記抵抗付きデカップリングコンデンサを構成する抵抗素子の最適抵抗値として算出する第2の算出手段として機能させるプログラムを含む

ことを特徴とする半導体集積回路の設計用プログラム。

【請求項4】

前記第1の共振周波数および前記第2の共振周波数を算出する前に、前記コンピュータを、抵抗なしデカップリングコンデンサの一部又は全部を抵抗付きデカップリングコンデンサに置き換えるデカップリングコンデンサ置き換え手段として機能させるプログラムを含む

ことを特徴とする請求項3に記載の半導体集積回路の設計用プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2008−251571(P2008−251571A)

【公開日】平成20年10月16日(2008.10.16)

【国際特許分類】

【出願番号】特願2007−87165(P2007−87165)

【出願日】平成19年3月29日(2007.3.29)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

【公開日】平成20年10月16日(2008.10.16)

【国際特許分類】

【出願日】平成19年3月29日(2007.3.29)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]