半導体集積回路の設計方法

【構成】 スタンダードセルの自動設計方法において、仮想配線容量による論理シミュレーションを行う以前に、各信号の容量値に合わせて機能は同じだが駆動能力の異なる別セルに置換する。

【効果】 論理設計の最適化を計る。

【効果】 論理設計の最適化を計る。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は半導体集積回路の設計方法に係り、特にスタンダードセル方式を用いた自動設計方法に関する。

【0002】

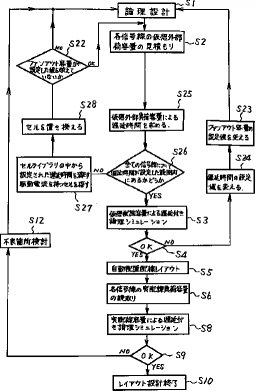

【従来の技術】近年、汎用品等の大量生産主体の集積回路の他に、ユーザーからの要求に応じて設計されるセミカスタム方式の集積回路、いわゆるASICの要求が高くなっている。スタンダードセル方式やゲートアレイ方式は、ASICの設計・製造に用いられる代表的な手法である。なかでもスタンダードセル方式はゲートアレイ方式に対してセル使用率が高く、しかも未使用の配線トラックがない等の利点を持つ。図3にはスタンダードセル方式を用いた半導体集積回路の自動設計方法に関するフローチャートが示されている。

【0003】最初、論理設計を行い(ステップS1)、次にファンイン,ファンアウト数及び仮想配線容量から仮想外部負荷容量を見積り(ステップS2)、この仮想配置線容量による遅延付き論理シミュレーションを行い(ステップS3)、論理の誤り,タイミングの誤り等があるか設計の検証を行う(ステップS4)。

【0004】誤りが検出されたら不良箇所を検討し(ステップS11)、論理設計(ステップS1)に戻り、誤りがなくなるまで上述したステップ(S1〜S4,S11)をくり返す。

【0005】仮想配線容量による遅延付き論理シミュレーション(ステップS3)で誤りが検出されなければステップS5に飛び、自動配置配線によるレイアウト設計を行う。次にレイアウトの結果から各信号線の実配線負荷容量を読み取り(ステップS6)、この実配線容量による遅延付き論理シミュレーションを行い(ステップS8)、論理の誤り、タイミング等の誤りがないか検証を行う(ステップS9)。誤りがなければステップS10に飛び、レイアウト設計が終了する。もし誤りがあれば不良箇所を検討し(ステップS12)、論理設計(ステップS1)に戻り誤りがなくなるまで上述したステップ(S1〜S12)をくり返す。

【0006】遅延付き論理シミュレーションは、配線容量による遅延時間を考慮して行うが、配線容量は実際にレイアウトしてみないと値が定まらないため、最初にシステム設計する場合には上述の如く仮配線容量を用いて行う。この場合、自動配置配線によりレイアウト設計を行った(ステップS5)後に、実際の配線容量と仮想配線容量が一致すれば問題ないが、大規模ASICではしばしば大きな不一致が生じ、シミュレーションで所望の回路動作が実現されなかった場合には、最初の論理設計にもどって設計をやり直さなければならない(S1〜S12)。そこで、論理設計からレイアウト設計終了までの期間、すなわち、設計TAT(TurnAnd Time)が長くなってしまうのを避けるために、仮想配線容量をマージンをとって大きく見積り、論理検証で誤りが検出される率を低くしようとした。しかし、信号線を駆動する電流も大きくなるのでFETサイズ及び消費電力が増大する傾向にある。仮想配線容量による論理シミュレーションの結果はそのまま次のレイアウト以降に反映されるので最適解よりも、レイアウト面積が大きく、消費電力が大きいチップになりやすいという問題があった。

【0007】上述の問題は、特にGaAs集積回路を設計する場合に生じやすい。それは、GaAs集積回路の負荷駆動能力はSi集積回路のそれより小さいので、同じ配線長でもGaAs集積回路の方がSi集積回路よりも信号の遅延時間が長くなり、信号のタイミングずれが大きくなって正常な回路動作をしなくなる率が高くなるためSi集積回路の場合に比べ、駆動電流を大きくして設計しなければならないからである。そのため、FETサイズが大きくなるのでレイアウト面積が大きくなり、実配線長が長いためGaAs集積回路の高速性を活かすことができなくなってしまう。また、消費電力も増大する。

【0008】

【発明が解決しようとする課題】これまでスタンダードセル方式を用いた集積回路の設計は、その集積度がさほど高くなかったので仮想配線容量と実配線容量とが大きく異なることはなかった。したがって信号遅延が回路の電気的特性に大きい影響を及ぼすことはなかった。しかしながら最近、大規模なシステムを集積化することが増え、しばしば実配線容量と仮配線容量とに大きな不一致が生じるようになった。その結果、設計検証で誤りが検出され、論理設計に戻り設計を再検討する必要が生じ、設計・開発に多大の時間がかかるという問題があった。そこで仮想配線容量をマージンを大きくとって見積り、論理シミュレーションによる検証で誤りが検出される率を低くしようとする傾向があった。しかし、このために、駆動電流が大きくなり、最適解よりもレイアウト面積及び消費電力の大きいチップになりやすいという問題があった。

【0009】本発明は上記事情を考慮してなされたもので、その目的とするところは論理設計からレイアウト設計終了までの期間を短縮しながら、より高集積で高速、低消費電力の半導体集積回路の設計方法を提供することにある。

【0010】

【課題を解決するための手段】上記の目的を達成するために、本発明は、標準セルを用いた半導体集積回路の設計方法において、論理設計するステップと、前記論理設計の後に各信号線の仮想配線容量による遅延時間を求め、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計をやり直すステップと、前記各信号線の遅延時間が全て所定の時間以内に収まる論理設計が決定された後、仮想線容量による遅延付き論理シミュレーションによる設計検証を行うステップと前記仮想配線容量による遅延付き論理シミュレーションによる設計検証の後、配置配線するステップとを有するステップで半導体集積回路を設計することを特徴とする。

【0011】

【作用】本発明によれば、全ての信号線についてその遅延時間が所定範囲内に収まるまで論理設計の修正を行うので、仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証に合格しやすくなる。

【0012】また、遅延時間が所定範囲にない信号線が検出された場合、この信号線を出力段に有するセルをこのセルと機能が同じで駆動能力が異なるセルに置換することにより容易に設計修正することができる。

【0013】さらに、仮想外部負荷容量に対し、最適な駆動能力を持つセルを選定するため最適設計を計ることができ、またその結果は、仮想配線容量による論理検証以降の配置配線や実配線容量による論理検証に反映されるため、より高集積で高速、低消費電力の集積回路を実現することができる。

【0014】

【実施例】以下、図面を参照しながら実施例を説明する。図1には本発明の一実施例に係る半導体論理集積回路の自動設計方法に関するフローチャートが示されている。

【0015】最初に論理設計(ステップS1)を行い、ファンイン、ファンアウト数及び仮想配線容量から各信号線の仮想外部負荷容量を見積る(ステップS2)。外部負荷の容量は、次段のセルとの接続に用いた仮想配線容量とファンアウト容量の和として求める。次に各信号線の外部負荷容量による遅延時間を式(1)より求める(ステップS25)。

(外部負荷の容量による遅延時間)

=α(外部負荷の容量)/(セルの駆動電流)…(1)

なお、αは比例定数である。次に全ての信号線について、外部負荷の容量による遅延時間が設定した範囲内にあるかどうかを判断する(ステップS26)。

【0016】遅延時間が設定した範囲内にない信号線があった場合には、その信号線のセルを、セルライブラリの中からその信号線のセルと機能は同じであるが出力段の駆動電流が異なるセルと置き換え、信号遅延を設定した範囲に収める(ステップS27,S28)。セルの選定は、例えば、外部負荷容量と駆動電流との関係が第2図に示される直線a,bで表される場合、直線a,bのそれぞれの傾きtanθa,tanθbは遅延時間を意味しているので、外部負荷容量がCoで、遅延時間の設定がtanθa〜tanθbの時には、駆動電流がIa〜Ibであるセルをセルライブラリの中から選べば良い。

【0017】駆動電流の異なるセルに置き換えるとセルサイズ、トランジスタサイズが変化するので配線容量,ファンアウト容量も変化する。そこでレイアウト設計を最適化するために各セルについてファンアウト容量が設定した値を越えているかどうかを判断し(ステップS22)、各セルの外部負荷容量による遅延時間が設定した範囲内になるように論理設計(ステップS1)を行い、ステップS1,S2,S22,S25〜S28をくり返す。遅延時間が設定した範囲内にある場合には、ステップS3に進み仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証を行う。

【0018】誤りが検出されなければレイアウト設計に飛ぶ(ステップS5)が、誤りが検出された場合にはステップS24に飛び、外部負荷容量による遅延時間の設定範囲を変えるか、ステップS23に進みファンアウト容量の設定値を変えてもう一度論理設計(ステップS1)を行い、所望の結果が得られるまでステップS1,S2,S3,S22〜S28を繰り返す。

【0019】仮想配線容量による遅延付き論理シミュレーション(ステップS3)で誤りが検出されなければステップS5に飛び、自動配置配線によるレイアウト設計を行う。次にレイアウトの結果から各信号線の実配線負荷容量を読み取り(ステップS6)、この実配線容量による遅延付き論理シミュレーションを行い(ステップS8)、論理の誤り、タイミング等の誤りがないか検証を行う(ステップS9)。誤りがなければステップS10に飛び、レイアウト設計が終了する。もし誤りがあれば不良箇所を検討し(ステップS12)、論理設計(ステップS1)に戻り誤りがなくなるまで上述したステップ(S1〜S12,S22〜S28)をくり返す。

【0020】本発明者等は約3KゲートのGaAs論理集積回路の設計を従来の方法と本実施例の方法とで行って比較してみた。その結果、従来の方法では設計に約4ヵ月間かかった。これに対して本実施例の方法では設計期間を約3ヵ月間に短縮することができた。また、消費電力を比較してみたところ本実施例の方法で設計されたGaAs論理集積回路の方が低いことが分かった。これは本実施例の方法で選定されたセルの方が外部負荷容量に対しより最適な駆動電流を持つからである。これより消費電力の最適化を効率良く行うことが可能になる。そして最適な駆動電流を持つセルが用いられているのでセルサイズも同時に最適化され、集積密度の高いGaAs論理集積回路が得られた。かくして本発明をGaAs論理集積回路の設計に適用することで、設計TAT,レイアウト面積,消費電力の改善が図れる。

【0021】

【発明の効果】以上述べたように本発明によれば、各信号線の遅延時間を全て所定範囲に収めた後に、仮想配線容量を用いた遅延付き論理シミュレーションにより設計検証を行うので時間のかかる設計修正を行う率が低くなるので設計TATの大幅な短縮を図ることができる。また本発明では遅延時間が所定範囲に収まらない信号線が検出された場合に不良箇所のセルを最適な駆動能力を持つセルに置き換えるので設計修正が容易に行われる。また、本発明によれば最適な駆動能力を持つセルを選定できるので、回路の最適化を計ることができる。

【図面の簡単な説明】

【図1】 本発明の一実施例に係る半導体集積回路の自動設計方法に関するフローチャートを示す図。

【図2】 外部負荷の容量と駆動電流との関係を示す図。

【図3】 従来例の自動設計方法に関するフローチャートを示す図。

【符号の説明】

S1…論理設計 S22…ファンアウト容量の判断 S5…自動配線レイアウトS2…仮想外部負荷容量の見積り S25…遅延時間の算出S26…各信号線の遅延時間の合否判定 S27…セルの選定 S28…セルの置き換え S29…論理シミュレーション S24…遅延時間の設定 23…ファンアウト容量の設定

【0001】

【産業上の利用分野】本発明は半導体集積回路の設計方法に係り、特にスタンダードセル方式を用いた自動設計方法に関する。

【0002】

【従来の技術】近年、汎用品等の大量生産主体の集積回路の他に、ユーザーからの要求に応じて設計されるセミカスタム方式の集積回路、いわゆるASICの要求が高くなっている。スタンダードセル方式やゲートアレイ方式は、ASICの設計・製造に用いられる代表的な手法である。なかでもスタンダードセル方式はゲートアレイ方式に対してセル使用率が高く、しかも未使用の配線トラックがない等の利点を持つ。図3にはスタンダードセル方式を用いた半導体集積回路の自動設計方法に関するフローチャートが示されている。

【0003】最初、論理設計を行い(ステップS1)、次にファンイン,ファンアウト数及び仮想配線容量から仮想外部負荷容量を見積り(ステップS2)、この仮想配置線容量による遅延付き論理シミュレーションを行い(ステップS3)、論理の誤り,タイミングの誤り等があるか設計の検証を行う(ステップS4)。

【0004】誤りが検出されたら不良箇所を検討し(ステップS11)、論理設計(ステップS1)に戻り、誤りがなくなるまで上述したステップ(S1〜S4,S11)をくり返す。

【0005】仮想配線容量による遅延付き論理シミュレーション(ステップS3)で誤りが検出されなければステップS5に飛び、自動配置配線によるレイアウト設計を行う。次にレイアウトの結果から各信号線の実配線負荷容量を読み取り(ステップS6)、この実配線容量による遅延付き論理シミュレーションを行い(ステップS8)、論理の誤り、タイミング等の誤りがないか検証を行う(ステップS9)。誤りがなければステップS10に飛び、レイアウト設計が終了する。もし誤りがあれば不良箇所を検討し(ステップS12)、論理設計(ステップS1)に戻り誤りがなくなるまで上述したステップ(S1〜S12)をくり返す。

【0006】遅延付き論理シミュレーションは、配線容量による遅延時間を考慮して行うが、配線容量は実際にレイアウトしてみないと値が定まらないため、最初にシステム設計する場合には上述の如く仮配線容量を用いて行う。この場合、自動配置配線によりレイアウト設計を行った(ステップS5)後に、実際の配線容量と仮想配線容量が一致すれば問題ないが、大規模ASICではしばしば大きな不一致が生じ、シミュレーションで所望の回路動作が実現されなかった場合には、最初の論理設計にもどって設計をやり直さなければならない(S1〜S12)。そこで、論理設計からレイアウト設計終了までの期間、すなわち、設計TAT(TurnAnd Time)が長くなってしまうのを避けるために、仮想配線容量をマージンをとって大きく見積り、論理検証で誤りが検出される率を低くしようとした。しかし、信号線を駆動する電流も大きくなるのでFETサイズ及び消費電力が増大する傾向にある。仮想配線容量による論理シミュレーションの結果はそのまま次のレイアウト以降に反映されるので最適解よりも、レイアウト面積が大きく、消費電力が大きいチップになりやすいという問題があった。

【0007】上述の問題は、特にGaAs集積回路を設計する場合に生じやすい。それは、GaAs集積回路の負荷駆動能力はSi集積回路のそれより小さいので、同じ配線長でもGaAs集積回路の方がSi集積回路よりも信号の遅延時間が長くなり、信号のタイミングずれが大きくなって正常な回路動作をしなくなる率が高くなるためSi集積回路の場合に比べ、駆動電流を大きくして設計しなければならないからである。そのため、FETサイズが大きくなるのでレイアウト面積が大きくなり、実配線長が長いためGaAs集積回路の高速性を活かすことができなくなってしまう。また、消費電力も増大する。

【0008】

【発明が解決しようとする課題】これまでスタンダードセル方式を用いた集積回路の設計は、その集積度がさほど高くなかったので仮想配線容量と実配線容量とが大きく異なることはなかった。したがって信号遅延が回路の電気的特性に大きい影響を及ぼすことはなかった。しかしながら最近、大規模なシステムを集積化することが増え、しばしば実配線容量と仮配線容量とに大きな不一致が生じるようになった。その結果、設計検証で誤りが検出され、論理設計に戻り設計を再検討する必要が生じ、設計・開発に多大の時間がかかるという問題があった。そこで仮想配線容量をマージンを大きくとって見積り、論理シミュレーションによる検証で誤りが検出される率を低くしようとする傾向があった。しかし、このために、駆動電流が大きくなり、最適解よりもレイアウト面積及び消費電力の大きいチップになりやすいという問題があった。

【0009】本発明は上記事情を考慮してなされたもので、その目的とするところは論理設計からレイアウト設計終了までの期間を短縮しながら、より高集積で高速、低消費電力の半導体集積回路の設計方法を提供することにある。

【0010】

【課題を解決するための手段】上記の目的を達成するために、本発明は、標準セルを用いた半導体集積回路の設計方法において、論理設計するステップと、前記論理設計の後に各信号線の仮想配線容量による遅延時間を求め、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計をやり直すステップと、前記各信号線の遅延時間が全て所定の時間以内に収まる論理設計が決定された後、仮想線容量による遅延付き論理シミュレーションによる設計検証を行うステップと前記仮想配線容量による遅延付き論理シミュレーションによる設計検証の後、配置配線するステップとを有するステップで半導体集積回路を設計することを特徴とする。

【0011】

【作用】本発明によれば、全ての信号線についてその遅延時間が所定範囲内に収まるまで論理設計の修正を行うので、仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証に合格しやすくなる。

【0012】また、遅延時間が所定範囲にない信号線が検出された場合、この信号線を出力段に有するセルをこのセルと機能が同じで駆動能力が異なるセルに置換することにより容易に設計修正することができる。

【0013】さらに、仮想外部負荷容量に対し、最適な駆動能力を持つセルを選定するため最適設計を計ることができ、またその結果は、仮想配線容量による論理検証以降の配置配線や実配線容量による論理検証に反映されるため、より高集積で高速、低消費電力の集積回路を実現することができる。

【0014】

【実施例】以下、図面を参照しながら実施例を説明する。図1には本発明の一実施例に係る半導体論理集積回路の自動設計方法に関するフローチャートが示されている。

【0015】最初に論理設計(ステップS1)を行い、ファンイン、ファンアウト数及び仮想配線容量から各信号線の仮想外部負荷容量を見積る(ステップS2)。外部負荷の容量は、次段のセルとの接続に用いた仮想配線容量とファンアウト容量の和として求める。次に各信号線の外部負荷容量による遅延時間を式(1)より求める(ステップS25)。

(外部負荷の容量による遅延時間)

=α(外部負荷の容量)/(セルの駆動電流)…(1)

なお、αは比例定数である。次に全ての信号線について、外部負荷の容量による遅延時間が設定した範囲内にあるかどうかを判断する(ステップS26)。

【0016】遅延時間が設定した範囲内にない信号線があった場合には、その信号線のセルを、セルライブラリの中からその信号線のセルと機能は同じであるが出力段の駆動電流が異なるセルと置き換え、信号遅延を設定した範囲に収める(ステップS27,S28)。セルの選定は、例えば、外部負荷容量と駆動電流との関係が第2図に示される直線a,bで表される場合、直線a,bのそれぞれの傾きtanθa,tanθbは遅延時間を意味しているので、外部負荷容量がCoで、遅延時間の設定がtanθa〜tanθbの時には、駆動電流がIa〜Ibであるセルをセルライブラリの中から選べば良い。

【0017】駆動電流の異なるセルに置き換えるとセルサイズ、トランジスタサイズが変化するので配線容量,ファンアウト容量も変化する。そこでレイアウト設計を最適化するために各セルについてファンアウト容量が設定した値を越えているかどうかを判断し(ステップS22)、各セルの外部負荷容量による遅延時間が設定した範囲内になるように論理設計(ステップS1)を行い、ステップS1,S2,S22,S25〜S28をくり返す。遅延時間が設定した範囲内にある場合には、ステップS3に進み仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証を行う。

【0018】誤りが検出されなければレイアウト設計に飛ぶ(ステップS5)が、誤りが検出された場合にはステップS24に飛び、外部負荷容量による遅延時間の設定範囲を変えるか、ステップS23に進みファンアウト容量の設定値を変えてもう一度論理設計(ステップS1)を行い、所望の結果が得られるまでステップS1,S2,S3,S22〜S28を繰り返す。

【0019】仮想配線容量による遅延付き論理シミュレーション(ステップS3)で誤りが検出されなければステップS5に飛び、自動配置配線によるレイアウト設計を行う。次にレイアウトの結果から各信号線の実配線負荷容量を読み取り(ステップS6)、この実配線容量による遅延付き論理シミュレーションを行い(ステップS8)、論理の誤り、タイミング等の誤りがないか検証を行う(ステップS9)。誤りがなければステップS10に飛び、レイアウト設計が終了する。もし誤りがあれば不良箇所を検討し(ステップS12)、論理設計(ステップS1)に戻り誤りがなくなるまで上述したステップ(S1〜S12,S22〜S28)をくり返す。

【0020】本発明者等は約3KゲートのGaAs論理集積回路の設計を従来の方法と本実施例の方法とで行って比較してみた。その結果、従来の方法では設計に約4ヵ月間かかった。これに対して本実施例の方法では設計期間を約3ヵ月間に短縮することができた。また、消費電力を比較してみたところ本実施例の方法で設計されたGaAs論理集積回路の方が低いことが分かった。これは本実施例の方法で選定されたセルの方が外部負荷容量に対しより最適な駆動電流を持つからである。これより消費電力の最適化を効率良く行うことが可能になる。そして最適な駆動電流を持つセルが用いられているのでセルサイズも同時に最適化され、集積密度の高いGaAs論理集積回路が得られた。かくして本発明をGaAs論理集積回路の設計に適用することで、設計TAT,レイアウト面積,消費電力の改善が図れる。

【0021】

【発明の効果】以上述べたように本発明によれば、各信号線の遅延時間を全て所定範囲に収めた後に、仮想配線容量を用いた遅延付き論理シミュレーションにより設計検証を行うので時間のかかる設計修正を行う率が低くなるので設計TATの大幅な短縮を図ることができる。また本発明では遅延時間が所定範囲に収まらない信号線が検出された場合に不良箇所のセルを最適な駆動能力を持つセルに置き換えるので設計修正が容易に行われる。また、本発明によれば最適な駆動能力を持つセルを選定できるので、回路の最適化を計ることができる。

【図面の簡単な説明】

【図1】 本発明の一実施例に係る半導体集積回路の自動設計方法に関するフローチャートを示す図。

【図2】 外部負荷の容量と駆動電流との関係を示す図。

【図3】 従来例の自動設計方法に関するフローチャートを示す図。

【符号の説明】

S1…論理設計 S22…ファンアウト容量の判断 S5…自動配線レイアウトS2…仮想外部負荷容量の見積り S25…遅延時間の算出S26…各信号線の遅延時間の合否判定 S27…セルの選定 S28…セルの置き換え S29…論理シミュレーション S24…遅延時間の設定 23…ファンアウト容量の設定

【特許請求の範囲】

【請求項1】 標準セルを用いた半導体集積回路の設計方法において、理論設計するステップと、前記論理設計の後に各信号線の仮想配線容量を見積るステップと、前記仮想配線容量から各信号線の遅延時間を求め、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計の修正を行うステップと、前記各信号線の遅延時間が全て所定の時間以内に収まる論理設計が決定された後、仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証を行うステップと、前記仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証の後、配置配線を行うステップとを有することを特徴とする半導体集積回路の設計方法。

【請求項2】 前記遅延時間の結果から所定の時間以内に収まらない信号線が見つかった場合、前記信号線を出力段に有するセルをこのセルと機能が同じで駆動能力が異なるセルに置換し、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計の修正を行うことを特徴とする請求項1記載の半導体集積回路の設計方法。

【請求項1】 標準セルを用いた半導体集積回路の設計方法において、理論設計するステップと、前記論理設計の後に各信号線の仮想配線容量を見積るステップと、前記仮想配線容量から各信号線の遅延時間を求め、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計の修正を行うステップと、前記各信号線の遅延時間が全て所定の時間以内に収まる論理設計が決定された後、仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証を行うステップと、前記仮想配線容量を用いた遅延付き論理シミュレーションによる設計検証の後、配置配線を行うステップとを有することを特徴とする半導体集積回路の設計方法。

【請求項2】 前記遅延時間の結果から所定の時間以内に収まらない信号線が見つかった場合、前記信号線を出力段に有するセルをこのセルと機能が同じで駆動能力が異なるセルに置換し、前記各信号線の遅延時間が全て所定の時間以内に収めるべく論理設計の修正を行うことを特徴とする請求項1記載の半導体集積回路の設計方法。

【図2】

【図1】

【図3】

【図1】

【図3】

【公開番号】特開平5−102306

【公開日】平成5年(1993)4月23日

【国際特許分類】

【出願番号】特願平3−258804

【出願日】平成3年(1991)10月7日

【出願人】(000003078)株式会社東芝 (54,554)

【公開日】平成5年(1993)4月23日

【国際特許分類】

【出願日】平成3年(1991)10月7日

【出願人】(000003078)株式会社東芝 (54,554)

[ Back to top ]