半導体集積回路の試験方法及び試験装置

【課題】半導体集積回路の製造(検査に要する時間を含む)に要する時間を短縮できる半導体集積回路の試験方法及び試験装置を提供する。

【解決手段】同一ウエハ20上の半導体チップA,Bにそれぞれプローブピンを接触させる。その後、試験装置本体からプローブピンを介して半導体チップAに仕様で定められた条件で電源電圧と第1のテスト信号とを供給し、選別試験を実施する。これと同時に、半導体チップBに仕様で定められた条件よりも過酷な条件で電源電圧とテスト信号とを供給し、バーンイン試験を行う。次の回では、バーンイン試験した半導体チップに対し選別試験を実施し、未試験の半導体チップに対しバーンイン試験を実施する。

【解決手段】同一ウエハ20上の半導体チップA,Bにそれぞれプローブピンを接触させる。その後、試験装置本体からプローブピンを介して半導体チップAに仕様で定められた条件で電源電圧と第1のテスト信号とを供給し、選別試験を実施する。これと同時に、半導体チップBに仕様で定められた条件よりも過酷な条件で電源電圧とテスト信号とを供給し、バーンイン試験を行う。次の回では、バーンイン試験した半導体チップに対し選別試験を実施し、未試験の半導体チップに対しバーンイン試験を実施する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ウエハ上に形成された半導体チップにテスト信号を供給し、半導体チップから出力される信号を調べて半導体チップの良否を判定する半導体集積回路の試験方法及び試験装置に関する。

【背景技術】

【0002】

半導体集積回路(LSI:Large Scale Integrated circuit)の検査の一つに、ウエハ上に形成された半導体チップに電気信号を供給して電気特性の良否を判定する選別試験(プロービング試験)がある。

【0003】

選別試験では、試験対象の半導体チップにプローブピンを接触させ、試験装置(LSIテスター)からプローブピンを介して半導体チップに所定の信号を供給して半導体チップから出力される信号を調べ、その結果に基づいて良否の判定を行う。良と判定された半導体チップは、ウエハを各半導体チップ毎に分離する工程(スクライブ工程)の後にパッケージングされ、製品(半導体集積回路)として出荷される。

【0004】

一方、出荷前の半導体集積回路に対し、バーンイン試験を実施することもある。バーンイン試験は加速試験の一種であり、半導体集積回路を加熱した状態で動作させて潜在する欠陥を顕在化し、良否を判定するものである。バーンイン試験は通常パッケージングされた半導体集積回路に対し行われるが、ウエハ上に形成された半導体チップに対し過剰な負荷を電気的に与えて簡易的にバーンイン試験を行うこともある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平6−53299号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

選別試験とバーンイン試験とは個別に実施される。このため、半導体集積回路の製造に要する時間(検査に要する時間を含む)が長くなり、その結果半導体集積回路の製造コストが上昇する。

【0007】

以上から、半導体集積回路の製造(検査に要する時間を含む)に要する時間を短縮できる半導体集積回路の試験方法及び試験装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

一観点によれば、同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程とを有する半導体集積回路の試験方法が提供される。

【発明の効果】

【0009】

上記一観点によれば、第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給して第1の半導体チップの良否を判定する選別試験と、第2の半導体チップに仕様よりも過酷な条件で電源電圧と第2のテスト信号を供給する加速試験(簡易的バーンイン試験)とを同時に実施する。これにより、試験に要する時間を短縮できて、半導体集積回路の製造(検査に要する時間を含む)に要する時間を短縮できる。

【図面の簡単な説明】

【0010】

【図1】図1は、選別試験に使用する試験装置の構成を示すブロック図である。

【図2】図2(a)は実施形態において使用するプローブカードの上面図、図2(b)は同じくその側面図である。

【図3】図3は、実施形態に係る試験方法を示すフローチャートである。

【図4】図4(a)は半導体チップの電極とプローブピンとの接続状態を示す模式図、図4(b)はウエハ上に形成された半導体チップを示す模式図である。

【図5】図5(a),(b)はその他の実施形態(その1)を示す模式図である。

【図6】図6(a),(b)はその他の実施形態(その2)を示す模式図である。

【図7】図7(a),(b)はその他の実施形態(その3)を示す模式図である。

【発明を実施するための形態】

【0011】

以下、実施形態について、添付の部面を参照して説明する。

【0012】

図1は、選別試験に使用する試験装置の構成を示すブロック図である。この図1に示すように、選別試験に使用する試験装置は、試験装置本体10と、ステージ駆動部15と、ステージ16と、プローブカード20とを有している。ステージ16の上には、複数の半導体チップ(半導体集積回路)が形成されたウエハが載置される。試験装置本体10とプローブカード20との間は、ケーブル等を介して電気的に接続される。

【0013】

試験装置本体10は、制御部11と、パターンジェネレータ12と、電源電圧出力部13と、ドライバ回路部14とを有している。パターンジェネレータ12には、試験対象となる半導体チップ(半導体集積回路)に応じたテストパターン(テスト用データ)が記憶される。また、電源電圧出力部13には、制御部11からの信号に応じた所定の電源電圧を出力可能な電源回路が設けられている。

【0014】

ドライバ回路部14には、制御部11からの信号に応じてハイレベル(以下、“H”レベルと記載する)及びロウレベル(以下、“L”レベルと記載する)に変化する信号を出力する多数のドライバが設けられている。なお、ドライバからプローブカード20側に出力される“H”レベル及び“L”レベルの電圧は、テストパターンに応じて設定することができる。

【0015】

ステージ駆動部15は、制御部11からの信号に基づき、ウエハが載置されたステージ16を相互に直交する3軸(X軸、Y軸、Z軸)方向に移動したり、ステージ16を所望の方向に傾ける等の動作を行う。

【0016】

プローブカード20には、ステージ16上に載置された半導体チップの電極に接触する多数のプローブピンが設けられている。選別試験では、プローブカード20のプローブピンをウエハに形成された半導体チップの外部接続用電極(電源供給電極、信号入力電極及び信号出力電極)に接触させる。

【0017】

選別試験が開始されると、試験装置本体10の制御部11は、パターンジェネレータ12からテストパターンを読み出し、電源電圧出力部13及びドライバ回路部14を制御して、テストパターンに応じた電源電圧及びテスト信号を発生させる。これらの電源電圧及びテスト信号は、プローブカード20を介して半導体チップの電源供給電極及び信号入力電極に供給される。

【0018】

一方、半導体チップの信号出力電極からは、入力されたテスト信号に応じた信号が出力される。この半導体チップから出力された信号は、プローブカード20及びドライバ回路部14に内蔵されたコンパレータを介して試験装置本体10の制御部11に伝達される。

【0019】

制御部11は、半導体チップに入力されたテスト信号と、半導体チップから出力された信号との関係を調べて、その結果に基づいて半導体チップの良否を判定する。すなわち、入力信号に応じて半導体チップから出力された信号が仕様(半導体集積回路の仕様:以下、同じ)で定められた範囲内であれば良と判定し、仕様で定められた範囲から外れていれば不良と判定する。

【0020】

一般的に、選別試験に使用する試験装置本体11のドライバ回路部14には、種々の半導体集積回路に対応するために多数のドライバが設けられている。しかし、一度に選別試験できる半導体チップの数は限られているため、選別試験において全てのドライバが使用されることは殆どない。従って、殆どの場合、選別試験時には半導体チップに接続されないドライバが少なからず存在し、無駄となっている。

【0021】

そこで、本実施形態においては、選別試験時に使用されていないドライバを用いて、選別試験を行う前の半導体チップに対し加速試験を実施する。なお、以下の説明においても図1を随時参照する。また、本実施形態で行う加速試験は簡易的なバーンイン試験であって完全なバーンイン試験ではないが、以下の説明では便宜上バーンイン試験と呼んでいる。

【0022】

図2(a)は、本実施形態において使用するプローブカードの上面図、図2(b)は同じくその側面図である。これらの図2(a),(b)に示すように、本実施形態で使用するプローブカード20は円盤状に形成されており、試験する半導体チップに対応する大きさの穴21が設けられている。そして、穴21の周囲から斜め下方に向けて多数のプローブピン22が突き出しており、それらのプローブピン22の先端が半導体チップに設けられた電極に接触するようになっている。

【0023】

本実施形態においては、一つの半導体チップに対し選別試験を実施しながら、他の一つの半導体チップに対してバーンイン試験(加速試験)を行うので、プローブカード20にはそれらの試験に必要なプローブピン22が設けられている。

【0024】

すなわち、プローブカード20には半導体チップ2個分に対応する大きさの穴21が設けられている。そして、プローブカード20のうち選別試験を行う半導体チップに対応する領域にはプローブピン22が一定のピッチで配置されており、半導体チップの全ての外部接続用電極(電源供給電極、信号入力電極及び信号出力電極)にプローブピン22が接触するようになっている。

【0025】

一方、プローブカード20のうちバーンイン試験を行う半導体チップに対応する領域には、半導体チップの電源供給電極と主要な信号入力電極とに接触するプローブピン22しか設けられてなく、信号出力電極に接触するプローブピンはない。

【0026】

プローブカード20の上側の面には多数の端子23が配列している。これらの端子23は、プローブカード20に設けられた配線及びスルーホールを介して各プローブピン22とそれぞれ電気的に接続されている。プローブカード20の上には各端子23に電気的に接続する導電体が設けられたコンタクトリング(図示せず)が配置され、各プローブピン22はコンタクトリング及びケーブルを介して試験装置本体10に電気的に接続される。

【0027】

図3は、本実施形態に係る試験方法を示すフローチャートである。また、図4(a)は半導体チップの電極とプローブピンとの接続状態を示す模式図、図4(b)はウエハ上に形成された半導体チップを示す模式図である。

【0028】

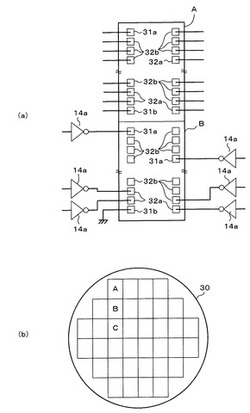

本実施形態では、例えば図4(a),(b)に示すように、半導体チップAに対し選別試験を行うと同時に、半導体チップAの下隣りに配置された半導体チップBに対しバーンイン試験を行う。1回の試験が終了すると、ステージ16が移動してプローブカード20がウエハ30に対し半導体チップ1つ分だけずれて配置される。そして、次の回では半導体チップBに対し選別試験が実施され、半導体チップBの下隣りに配置された半導体チップCに対しバーンイン試験が実施される。ここでは、予め試験装置には図2(a),(b)に示すプローブカード20、すなわち選別試験とバーンイン試験とを同時に実施可能なプローブカードが取り付けられているものとする。

【0029】

まず、ステップS11において、装置外部から試験装置本体10にテストパターンが供給され、パターンジェネレータ12に記憶される。このテストパターンはウエハ30上に形成された半導体チップ(半導体集積回路)に応じたものであり、選別試験用テストパターンとバーンイン試験(加速試験)用テストパターンとが含まれる。

【0030】

次に、ステップS12において、試験装置本体10の制御部11は、選別試験用テストパターンに応じて選別試験に使用するドライバを決定する。例えば試験装置本体10のドライバ回路部14には256個のドライバが設けられているとする。また、制御部11は、選別試験用テストパターンを調べて選別試験には20個のドライバが必要であると判断したものとする。この場合、制御部11は、256個のドライバのうち20個のドライバを選別試験用に割り振る。

【0031】

次に、ステップS13において、試験装置本体10の制御部11は、バーンイン試験用テストパターンに応じてバーンイン試験に使用するドライバを決定する。ここでは、バーンイン試験用テストパターンを調べてバーンイン試験に10個のドライバが必要であると判断したものとする。上述したようにドライバ回路部14に設けられた256個のドライバのうち20個を選別試験用に設定した場合、制御部11は残りの236個ドライバから10個のドライバをバーンイン試験用に割り振る。

【0032】

次に、ステップS14において、ウエハ30をステージ16の上に載置する。そして、試験装置本体10に試験の開始を指示する。そうすると、ステップS15に移行し、制御部11はステージ駆動部15を介してステージ16を駆動し、プローブカード20のプローブピン22を所定の半導体チップ(半導体チップA,B)の電極に接触させる。その後、ステップS16に移行し、選別試験及びバーンイン試験を実行する。

【0033】

以下、図4(a)を参照して、選別試験及びバーンイン試験についてより詳細に説明する。図4(a)において、31aは高電位側電源供給電極、31bは低電位側電源供給電極、32aは信号入力電極、32bは信号出力電極を示している。また、図4(a)において、14aはバーンイン試験する半導体チップBに割り振られたドライバを示している。なお、ここでは説明を簡単にするために、半導体チップAにはバーンイン試験がすでに終了しているものとしている。

【0034】

プローブピン22が半導体チップA,Bの所定の電極に接続されると、試験装置本体10内の制御部11は、パターンジェネレータ12から選別試験用テストパターン及びバーンイン試験用テストパターンを読み出す。そして、制御部11は、電源電圧出力部13及びドライバ回路部14を制御して、半導体チップA,Bに所定の電源電圧及びテスト信号を供給する。

【0035】

すなわち、半導体チップAの電源供給電極31a,31bに仕様に定められた範囲の電源電圧を供給するとともに、信号入力電極32aに経時的に状態(レベル)が変化する所定の選別試験用テスト信号を供給する。このテスト信号の“H”レベル及び“L”レベルの電圧値も、仕様に定められた範囲の電圧値である。そして、制御部11は、半導体チップAの信号出力電極32bから出力される信号をプローブカード20及びドライバ回路部14に内蔵されたコンパレータを介して入力し、半導体チップAから出力される信号が仕様で定められた範囲内か否かを判定する。

【0036】

この選別試験と同時に、制御部11は、半導体チップBの電源供給電極31aに、例えば仕様で定められた電源電圧の上限値よりも10%高い電圧を供給するとともに、信号入力電極32aに所定のバーンイン試験用テスト信号を供給する。なお、図4(a)ではドライバ14aから半導体チップBの電源供給電極31aに電源電圧を供給している。しかし、電源電圧出力部13から上述の電圧(仕様で定められた電源電圧の上限値よりも10%高い電圧)の電源電圧を供給できる場合は、電源電圧出力部13から半導体チップBの電源供給電極31aに電源電圧を供給してもよい。

【0037】

半導体チップBに供給するテスト信号は、仕様で定められた範囲の信号としてもよく、仕様の範囲を外れる信号を供給してもよい。このバーンイン試験では、半導体チップBから出力される信号を調べていないので、半導体チップBの良否を判定することはできない。しかし、バーンイン試験では、仕様で定められた条件よりも過酷な条件で半導体チップBを駆動するので、半導体チップBに欠陥が潜在する場合は欠陥が顕在化される。このため、次に行う選別試験では欠陥が検出されて不良と判定される。

【0038】

なお、半導体チップBの信号入力電極32aにテスト信号としてレベルが変化しない信号を供給した場合は、いわゆるスタティックバーンイン試験となる。また、半導体チップBの信号入力電極32aにテスト信号としてレベルが変化する信号を供給した場合は、いわゆるダイナミックバーンイン試験となる。

【0039】

このようにして選別試験及びバーンイン試験を実施した後、ステップS17に移行する。ステップS17では、ウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了したか否かを判定する。ウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了していないと判定したとき(NOのとき)は、ステップS15に戻り、制御部11はステージ駆動部15を制御してステージ16を移動させ、次の検査対象の半導体チップにプローブピンを接触させる。その後、ステップS16に移行して選別試験及びバーンイン試験を実施する。

【0040】

このようにしてウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了すると、ステップS17でYESと判定され、当該ウエハの試験を終了する。

【0041】

上述したように、本実施形態においては、1つの半導体チップに対し選別試験を実施しながら、他の1つの半導体チップに対しバーンイン試験を実施する。このため、半導体チップの検査に要する時間を短縮でき、その結果半導体集積回路装置の製造に要する時間が短縮される。また、本実施形態においてはバーンイン試験を実施した半導体チップに対し選別試験を実施するので、欠陥が潜在する半導体チップを発見でき、初期不良となるおそれのある半導体チップ(半導体集積回路)が製品として出荷されることを防止できる。これにより、製品として出荷される半導体集積回路の信頼性が向上する。

【0042】

なお、上記実施形態では選別試験及びバーンイン試験を常温で行うものとしているが、ウエハを加熱しながら選別試験及びバーンイン試験を行ってもよい。例えばウエハを100℃又はそれ以上の温度に加熱しながら上述した選別試験及びバーンイン試験を行うことにより、欠陥が潜在する半導体チップをより確実に排除することができる。

【0043】

(その他の実施形態)

上述の実施形態では選別試験する半導体チップの下隣りに配置された半導体チップに対しバーンイン試験を行うものとしたが、選別試験する半導体チップとバーンイン試験する半導体チップとは離れていてもよい。図5(a),(b)及び図6(a),(b)は、選別試験する半導体チップAとバーンイン試験する半導体チップBとが離れている場合の例を示している。また、図7(a),(b)は、2つの半導体チップAに対し選別試験すると同時に、2つの半導体チップBに対しバーンイン試験する場合の例を示している。

【0044】

これらの図5〜図7に示すように、選別試験する半導体チップとバーンイン試験する半導体チップとの位置関係や、選別試験する半導体チップの数及びバーンイン試験する半導体チップの数は適宜設定することができる。

【0045】

以下、本発明の諸態様を、付記としてまとめて記載する。

【0046】

(付記1)同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、

試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程と

を有することを特徴とする半導体集積回路の試験方法。

【0047】

(付記2)前記第2の工程を終了した後、前記第2の半導体チップを新たに第1の半導体チップとし、未試験の半導体チップを第2の半導体チップとして、前記第1の工程及び前記第2の工程を繰り返すことを特徴とする付記1に記載の半導体集積回路の試験方法。

【0048】

(付記3)前記第2の半導体チップには、前記仕様で定められた電源電圧の上限値よりも高い電圧を供給することを特徴とする付記1又は2に記載の半導体集積回路の試験方法。

【0049】

(付記4)前記第2の半導体チップには、前記第2のテスト信号として、前記仕様で定められた条件と異なるレベルの信号を入力することを特徴とする付記1乃至3のいずれか1項に記載の半導体集積回路の試験方法。

【0050】

(付記5)前記第1の半導体チップの全ての外部接続用電極に前記プローブピンを接触させ、前記第2の半導体チップの外部接続用電極のうち信号出力端子には前記プローブピンを接触させないことを特徴とする付記1乃至4のいずれか1項に記載の半導体集積回路の試験方法。

【0051】

(付記6)前記第2の工程では、前記ウエハを加熱することを特徴とする付記1乃至5のいずれか1項に記載の半導体集積回路の試験方法。

【0052】

(付記7)ウエハに形成された第1の半導体チップに対し選別試験を行うと同時に前記ウエハに形成された第2の半導体チップに加速試験を行う際に使用するプローブカードであって、

前記プローブカードは、

前記第1の半導体チップの全ての外部接続用電極にそれぞれ個別に接続するように一定のピッチで配列したプローブピンと、

前記第2の半導体チップの外部接続用電極うち電源電圧供給電極及び信号入力電極にそれぞれ個別に接続するように選択的に配置されたプローブピンとを有することを特徴とするプローブカード。

【0053】

(付記8)複数の半導体チップが形成されたウエハが載置されるステージと、

選別試験用テストパターン及び加速試験用テストパターンを記憶するパターンジェネレータと、

電源電圧を出力する電源電圧出力部と、

複数のドライバを有するドライバ回路部と、

前記ステージを駆動するステージ駆動部と、

前記パターンジェネレータ、前記電源電圧出力部、前記ドライバ回路部及び前記ステージ駆動部を制御する制御部とを有し、

前記制御部は、

前記選別試験用テストパターンに応じて前記ドライバ回路部のドライバから選別試験に使用するドライバを振り分け、

前記加速試験用テストパターンに応じて前記ドライバ回路部の残りのドライバから加速試験に使用するドライバを振り分け、

前記電源電圧出力部及び前記ドライバ回路部を制御して、前記選別試験用テストパターンに応じて前記ウエハの第1の半導体チップに対し仕様で定められた電源電圧を供給しながら選別試験用テスト信号を供給するとともに、前記加速試験用テストパターンに応じて前記第2の半導体チップに前記仕様よりも過酷な条件で電源電圧及び加速試験用テスト信号を供給し、前記第1の半導体チップから出力される信号に基づいて前記第1の半導体チップの良否を判定することを特徴とする試験装置。

【符号の説明】

【0054】

10…試験装置本体、11…制御部、12…パターンジェネレータ、13…電源電圧出力部、14…ドライバ回路部、14a…ドライバ、15…ステージ駆動部、16…ステージ、20…プローブカード、22…プローブピン、23…端子、30…ウエハ、31a,31b…電源供給電極、32a…信号入力電極、32b…信号出力電極。

【技術分野】

【0001】

本発明は、ウエハ上に形成された半導体チップにテスト信号を供給し、半導体チップから出力される信号を調べて半導体チップの良否を判定する半導体集積回路の試験方法及び試験装置に関する。

【背景技術】

【0002】

半導体集積回路(LSI:Large Scale Integrated circuit)の検査の一つに、ウエハ上に形成された半導体チップに電気信号を供給して電気特性の良否を判定する選別試験(プロービング試験)がある。

【0003】

選別試験では、試験対象の半導体チップにプローブピンを接触させ、試験装置(LSIテスター)からプローブピンを介して半導体チップに所定の信号を供給して半導体チップから出力される信号を調べ、その結果に基づいて良否の判定を行う。良と判定された半導体チップは、ウエハを各半導体チップ毎に分離する工程(スクライブ工程)の後にパッケージングされ、製品(半導体集積回路)として出荷される。

【0004】

一方、出荷前の半導体集積回路に対し、バーンイン試験を実施することもある。バーンイン試験は加速試験の一種であり、半導体集積回路を加熱した状態で動作させて潜在する欠陥を顕在化し、良否を判定するものである。バーンイン試験は通常パッケージングされた半導体集積回路に対し行われるが、ウエハ上に形成された半導体チップに対し過剰な負荷を電気的に与えて簡易的にバーンイン試験を行うこともある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平6−53299号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

選別試験とバーンイン試験とは個別に実施される。このため、半導体集積回路の製造に要する時間(検査に要する時間を含む)が長くなり、その結果半導体集積回路の製造コストが上昇する。

【0007】

以上から、半導体集積回路の製造(検査に要する時間を含む)に要する時間を短縮できる半導体集積回路の試験方法及び試験装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

一観点によれば、同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程とを有する半導体集積回路の試験方法が提供される。

【発明の効果】

【0009】

上記一観点によれば、第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給して第1の半導体チップの良否を判定する選別試験と、第2の半導体チップに仕様よりも過酷な条件で電源電圧と第2のテスト信号を供給する加速試験(簡易的バーンイン試験)とを同時に実施する。これにより、試験に要する時間を短縮できて、半導体集積回路の製造(検査に要する時間を含む)に要する時間を短縮できる。

【図面の簡単な説明】

【0010】

【図1】図1は、選別試験に使用する試験装置の構成を示すブロック図である。

【図2】図2(a)は実施形態において使用するプローブカードの上面図、図2(b)は同じくその側面図である。

【図3】図3は、実施形態に係る試験方法を示すフローチャートである。

【図4】図4(a)は半導体チップの電極とプローブピンとの接続状態を示す模式図、図4(b)はウエハ上に形成された半導体チップを示す模式図である。

【図5】図5(a),(b)はその他の実施形態(その1)を示す模式図である。

【図6】図6(a),(b)はその他の実施形態(その2)を示す模式図である。

【図7】図7(a),(b)はその他の実施形態(その3)を示す模式図である。

【発明を実施するための形態】

【0011】

以下、実施形態について、添付の部面を参照して説明する。

【0012】

図1は、選別試験に使用する試験装置の構成を示すブロック図である。この図1に示すように、選別試験に使用する試験装置は、試験装置本体10と、ステージ駆動部15と、ステージ16と、プローブカード20とを有している。ステージ16の上には、複数の半導体チップ(半導体集積回路)が形成されたウエハが載置される。試験装置本体10とプローブカード20との間は、ケーブル等を介して電気的に接続される。

【0013】

試験装置本体10は、制御部11と、パターンジェネレータ12と、電源電圧出力部13と、ドライバ回路部14とを有している。パターンジェネレータ12には、試験対象となる半導体チップ(半導体集積回路)に応じたテストパターン(テスト用データ)が記憶される。また、電源電圧出力部13には、制御部11からの信号に応じた所定の電源電圧を出力可能な電源回路が設けられている。

【0014】

ドライバ回路部14には、制御部11からの信号に応じてハイレベル(以下、“H”レベルと記載する)及びロウレベル(以下、“L”レベルと記載する)に変化する信号を出力する多数のドライバが設けられている。なお、ドライバからプローブカード20側に出力される“H”レベル及び“L”レベルの電圧は、テストパターンに応じて設定することができる。

【0015】

ステージ駆動部15は、制御部11からの信号に基づき、ウエハが載置されたステージ16を相互に直交する3軸(X軸、Y軸、Z軸)方向に移動したり、ステージ16を所望の方向に傾ける等の動作を行う。

【0016】

プローブカード20には、ステージ16上に載置された半導体チップの電極に接触する多数のプローブピンが設けられている。選別試験では、プローブカード20のプローブピンをウエハに形成された半導体チップの外部接続用電極(電源供給電極、信号入力電極及び信号出力電極)に接触させる。

【0017】

選別試験が開始されると、試験装置本体10の制御部11は、パターンジェネレータ12からテストパターンを読み出し、電源電圧出力部13及びドライバ回路部14を制御して、テストパターンに応じた電源電圧及びテスト信号を発生させる。これらの電源電圧及びテスト信号は、プローブカード20を介して半導体チップの電源供給電極及び信号入力電極に供給される。

【0018】

一方、半導体チップの信号出力電極からは、入力されたテスト信号に応じた信号が出力される。この半導体チップから出力された信号は、プローブカード20及びドライバ回路部14に内蔵されたコンパレータを介して試験装置本体10の制御部11に伝達される。

【0019】

制御部11は、半導体チップに入力されたテスト信号と、半導体チップから出力された信号との関係を調べて、その結果に基づいて半導体チップの良否を判定する。すなわち、入力信号に応じて半導体チップから出力された信号が仕様(半導体集積回路の仕様:以下、同じ)で定められた範囲内であれば良と判定し、仕様で定められた範囲から外れていれば不良と判定する。

【0020】

一般的に、選別試験に使用する試験装置本体11のドライバ回路部14には、種々の半導体集積回路に対応するために多数のドライバが設けられている。しかし、一度に選別試験できる半導体チップの数は限られているため、選別試験において全てのドライバが使用されることは殆どない。従って、殆どの場合、選別試験時には半導体チップに接続されないドライバが少なからず存在し、無駄となっている。

【0021】

そこで、本実施形態においては、選別試験時に使用されていないドライバを用いて、選別試験を行う前の半導体チップに対し加速試験を実施する。なお、以下の説明においても図1を随時参照する。また、本実施形態で行う加速試験は簡易的なバーンイン試験であって完全なバーンイン試験ではないが、以下の説明では便宜上バーンイン試験と呼んでいる。

【0022】

図2(a)は、本実施形態において使用するプローブカードの上面図、図2(b)は同じくその側面図である。これらの図2(a),(b)に示すように、本実施形態で使用するプローブカード20は円盤状に形成されており、試験する半導体チップに対応する大きさの穴21が設けられている。そして、穴21の周囲から斜め下方に向けて多数のプローブピン22が突き出しており、それらのプローブピン22の先端が半導体チップに設けられた電極に接触するようになっている。

【0023】

本実施形態においては、一つの半導体チップに対し選別試験を実施しながら、他の一つの半導体チップに対してバーンイン試験(加速試験)を行うので、プローブカード20にはそれらの試験に必要なプローブピン22が設けられている。

【0024】

すなわち、プローブカード20には半導体チップ2個分に対応する大きさの穴21が設けられている。そして、プローブカード20のうち選別試験を行う半導体チップに対応する領域にはプローブピン22が一定のピッチで配置されており、半導体チップの全ての外部接続用電極(電源供給電極、信号入力電極及び信号出力電極)にプローブピン22が接触するようになっている。

【0025】

一方、プローブカード20のうちバーンイン試験を行う半導体チップに対応する領域には、半導体チップの電源供給電極と主要な信号入力電極とに接触するプローブピン22しか設けられてなく、信号出力電極に接触するプローブピンはない。

【0026】

プローブカード20の上側の面には多数の端子23が配列している。これらの端子23は、プローブカード20に設けられた配線及びスルーホールを介して各プローブピン22とそれぞれ電気的に接続されている。プローブカード20の上には各端子23に電気的に接続する導電体が設けられたコンタクトリング(図示せず)が配置され、各プローブピン22はコンタクトリング及びケーブルを介して試験装置本体10に電気的に接続される。

【0027】

図3は、本実施形態に係る試験方法を示すフローチャートである。また、図4(a)は半導体チップの電極とプローブピンとの接続状態を示す模式図、図4(b)はウエハ上に形成された半導体チップを示す模式図である。

【0028】

本実施形態では、例えば図4(a),(b)に示すように、半導体チップAに対し選別試験を行うと同時に、半導体チップAの下隣りに配置された半導体チップBに対しバーンイン試験を行う。1回の試験が終了すると、ステージ16が移動してプローブカード20がウエハ30に対し半導体チップ1つ分だけずれて配置される。そして、次の回では半導体チップBに対し選別試験が実施され、半導体チップBの下隣りに配置された半導体チップCに対しバーンイン試験が実施される。ここでは、予め試験装置には図2(a),(b)に示すプローブカード20、すなわち選別試験とバーンイン試験とを同時に実施可能なプローブカードが取り付けられているものとする。

【0029】

まず、ステップS11において、装置外部から試験装置本体10にテストパターンが供給され、パターンジェネレータ12に記憶される。このテストパターンはウエハ30上に形成された半導体チップ(半導体集積回路)に応じたものであり、選別試験用テストパターンとバーンイン試験(加速試験)用テストパターンとが含まれる。

【0030】

次に、ステップS12において、試験装置本体10の制御部11は、選別試験用テストパターンに応じて選別試験に使用するドライバを決定する。例えば試験装置本体10のドライバ回路部14には256個のドライバが設けられているとする。また、制御部11は、選別試験用テストパターンを調べて選別試験には20個のドライバが必要であると判断したものとする。この場合、制御部11は、256個のドライバのうち20個のドライバを選別試験用に割り振る。

【0031】

次に、ステップS13において、試験装置本体10の制御部11は、バーンイン試験用テストパターンに応じてバーンイン試験に使用するドライバを決定する。ここでは、バーンイン試験用テストパターンを調べてバーンイン試験に10個のドライバが必要であると判断したものとする。上述したようにドライバ回路部14に設けられた256個のドライバのうち20個を選別試験用に設定した場合、制御部11は残りの236個ドライバから10個のドライバをバーンイン試験用に割り振る。

【0032】

次に、ステップS14において、ウエハ30をステージ16の上に載置する。そして、試験装置本体10に試験の開始を指示する。そうすると、ステップS15に移行し、制御部11はステージ駆動部15を介してステージ16を駆動し、プローブカード20のプローブピン22を所定の半導体チップ(半導体チップA,B)の電極に接触させる。その後、ステップS16に移行し、選別試験及びバーンイン試験を実行する。

【0033】

以下、図4(a)を参照して、選別試験及びバーンイン試験についてより詳細に説明する。図4(a)において、31aは高電位側電源供給電極、31bは低電位側電源供給電極、32aは信号入力電極、32bは信号出力電極を示している。また、図4(a)において、14aはバーンイン試験する半導体チップBに割り振られたドライバを示している。なお、ここでは説明を簡単にするために、半導体チップAにはバーンイン試験がすでに終了しているものとしている。

【0034】

プローブピン22が半導体チップA,Bの所定の電極に接続されると、試験装置本体10内の制御部11は、パターンジェネレータ12から選別試験用テストパターン及びバーンイン試験用テストパターンを読み出す。そして、制御部11は、電源電圧出力部13及びドライバ回路部14を制御して、半導体チップA,Bに所定の電源電圧及びテスト信号を供給する。

【0035】

すなわち、半導体チップAの電源供給電極31a,31bに仕様に定められた範囲の電源電圧を供給するとともに、信号入力電極32aに経時的に状態(レベル)が変化する所定の選別試験用テスト信号を供給する。このテスト信号の“H”レベル及び“L”レベルの電圧値も、仕様に定められた範囲の電圧値である。そして、制御部11は、半導体チップAの信号出力電極32bから出力される信号をプローブカード20及びドライバ回路部14に内蔵されたコンパレータを介して入力し、半導体チップAから出力される信号が仕様で定められた範囲内か否かを判定する。

【0036】

この選別試験と同時に、制御部11は、半導体チップBの電源供給電極31aに、例えば仕様で定められた電源電圧の上限値よりも10%高い電圧を供給するとともに、信号入力電極32aに所定のバーンイン試験用テスト信号を供給する。なお、図4(a)ではドライバ14aから半導体チップBの電源供給電極31aに電源電圧を供給している。しかし、電源電圧出力部13から上述の電圧(仕様で定められた電源電圧の上限値よりも10%高い電圧)の電源電圧を供給できる場合は、電源電圧出力部13から半導体チップBの電源供給電極31aに電源電圧を供給してもよい。

【0037】

半導体チップBに供給するテスト信号は、仕様で定められた範囲の信号としてもよく、仕様の範囲を外れる信号を供給してもよい。このバーンイン試験では、半導体チップBから出力される信号を調べていないので、半導体チップBの良否を判定することはできない。しかし、バーンイン試験では、仕様で定められた条件よりも過酷な条件で半導体チップBを駆動するので、半導体チップBに欠陥が潜在する場合は欠陥が顕在化される。このため、次に行う選別試験では欠陥が検出されて不良と判定される。

【0038】

なお、半導体チップBの信号入力電極32aにテスト信号としてレベルが変化しない信号を供給した場合は、いわゆるスタティックバーンイン試験となる。また、半導体チップBの信号入力電極32aにテスト信号としてレベルが変化する信号を供給した場合は、いわゆるダイナミックバーンイン試験となる。

【0039】

このようにして選別試験及びバーンイン試験を実施した後、ステップS17に移行する。ステップS17では、ウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了したか否かを判定する。ウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了していないと判定したとき(NOのとき)は、ステップS15に戻り、制御部11はステージ駆動部15を制御してステージ16を移動させ、次の検査対象の半導体チップにプローブピンを接触させる。その後、ステップS16に移行して選別試験及びバーンイン試験を実施する。

【0040】

このようにしてウエハ30上の全ての半導体チップに対し選別試験及びバーンイン試験が終了すると、ステップS17でYESと判定され、当該ウエハの試験を終了する。

【0041】

上述したように、本実施形態においては、1つの半導体チップに対し選別試験を実施しながら、他の1つの半導体チップに対しバーンイン試験を実施する。このため、半導体チップの検査に要する時間を短縮でき、その結果半導体集積回路装置の製造に要する時間が短縮される。また、本実施形態においてはバーンイン試験を実施した半導体チップに対し選別試験を実施するので、欠陥が潜在する半導体チップを発見でき、初期不良となるおそれのある半導体チップ(半導体集積回路)が製品として出荷されることを防止できる。これにより、製品として出荷される半導体集積回路の信頼性が向上する。

【0042】

なお、上記実施形態では選別試験及びバーンイン試験を常温で行うものとしているが、ウエハを加熱しながら選別試験及びバーンイン試験を行ってもよい。例えばウエハを100℃又はそれ以上の温度に加熱しながら上述した選別試験及びバーンイン試験を行うことにより、欠陥が潜在する半導体チップをより確実に排除することができる。

【0043】

(その他の実施形態)

上述の実施形態では選別試験する半導体チップの下隣りに配置された半導体チップに対しバーンイン試験を行うものとしたが、選別試験する半導体チップとバーンイン試験する半導体チップとは離れていてもよい。図5(a),(b)及び図6(a),(b)は、選別試験する半導体チップAとバーンイン試験する半導体チップBとが離れている場合の例を示している。また、図7(a),(b)は、2つの半導体チップAに対し選別試験すると同時に、2つの半導体チップBに対しバーンイン試験する場合の例を示している。

【0044】

これらの図5〜図7に示すように、選別試験する半導体チップとバーンイン試験する半導体チップとの位置関係や、選別試験する半導体チップの数及びバーンイン試験する半導体チップの数は適宜設定することができる。

【0045】

以下、本発明の諸態様を、付記としてまとめて記載する。

【0046】

(付記1)同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、

試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程と

を有することを特徴とする半導体集積回路の試験方法。

【0047】

(付記2)前記第2の工程を終了した後、前記第2の半導体チップを新たに第1の半導体チップとし、未試験の半導体チップを第2の半導体チップとして、前記第1の工程及び前記第2の工程を繰り返すことを特徴とする付記1に記載の半導体集積回路の試験方法。

【0048】

(付記3)前記第2の半導体チップには、前記仕様で定められた電源電圧の上限値よりも高い電圧を供給することを特徴とする付記1又は2に記載の半導体集積回路の試験方法。

【0049】

(付記4)前記第2の半導体チップには、前記第2のテスト信号として、前記仕様で定められた条件と異なるレベルの信号を入力することを特徴とする付記1乃至3のいずれか1項に記載の半導体集積回路の試験方法。

【0050】

(付記5)前記第1の半導体チップの全ての外部接続用電極に前記プローブピンを接触させ、前記第2の半導体チップの外部接続用電極のうち信号出力端子には前記プローブピンを接触させないことを特徴とする付記1乃至4のいずれか1項に記載の半導体集積回路の試験方法。

【0051】

(付記6)前記第2の工程では、前記ウエハを加熱することを特徴とする付記1乃至5のいずれか1項に記載の半導体集積回路の試験方法。

【0052】

(付記7)ウエハに形成された第1の半導体チップに対し選別試験を行うと同時に前記ウエハに形成された第2の半導体チップに加速試験を行う際に使用するプローブカードであって、

前記プローブカードは、

前記第1の半導体チップの全ての外部接続用電極にそれぞれ個別に接続するように一定のピッチで配列したプローブピンと、

前記第2の半導体チップの外部接続用電極うち電源電圧供給電極及び信号入力電極にそれぞれ個別に接続するように選択的に配置されたプローブピンとを有することを特徴とするプローブカード。

【0053】

(付記8)複数の半導体チップが形成されたウエハが載置されるステージと、

選別試験用テストパターン及び加速試験用テストパターンを記憶するパターンジェネレータと、

電源電圧を出力する電源電圧出力部と、

複数のドライバを有するドライバ回路部と、

前記ステージを駆動するステージ駆動部と、

前記パターンジェネレータ、前記電源電圧出力部、前記ドライバ回路部及び前記ステージ駆動部を制御する制御部とを有し、

前記制御部は、

前記選別試験用テストパターンに応じて前記ドライバ回路部のドライバから選別試験に使用するドライバを振り分け、

前記加速試験用テストパターンに応じて前記ドライバ回路部の残りのドライバから加速試験に使用するドライバを振り分け、

前記電源電圧出力部及び前記ドライバ回路部を制御して、前記選別試験用テストパターンに応じて前記ウエハの第1の半導体チップに対し仕様で定められた電源電圧を供給しながら選別試験用テスト信号を供給するとともに、前記加速試験用テストパターンに応じて前記第2の半導体チップに前記仕様よりも過酷な条件で電源電圧及び加速試験用テスト信号を供給し、前記第1の半導体チップから出力される信号に基づいて前記第1の半導体チップの良否を判定することを特徴とする試験装置。

【符号の説明】

【0054】

10…試験装置本体、11…制御部、12…パターンジェネレータ、13…電源電圧出力部、14…ドライバ回路部、14a…ドライバ、15…ステージ駆動部、16…ステージ、20…プローブカード、22…プローブピン、23…端子、30…ウエハ、31a,31b…電源供給電極、32a…信号入力電極、32b…信号出力電極。

【特許請求の範囲】

【請求項1】

同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、

試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程と

を有することを特徴とする半導体集積回路の試験方法。

【請求項2】

前記第2の工程を終了した後、前記第2の半導体チップを新たに第1の半導体チップとし、未試験の半導体チップを第2の半導体チップとして、前記第1の工程及び前記第2の工程を繰り返すことを特徴とする請求項1に記載の半導体集積回路の試験方法。

【請求項3】

前記第2の工程では、前記ウエハを加熱することを特徴とする請求項1又は2に記載の半導体集積回路の試験方法。

【請求項4】

ウエハに形成された第1の半導体チップに対し選別試験を行うと同時に前記ウエハに形成された第2の半導体チップに加速試験を行う際に使用するプローブカードであって、

前記プローブカードは、

前記第1の半導体チップの全ての外部接続用電極にそれぞれ個別に接続するように一定のピッチで配列したプローブピンと、

前記第2の半導体チップの外部接続用電極うち電源電圧供給電極及び信号入力電極にそれぞれ個別に接続するように選択的に配置されたプローブピンとを有することを特徴とするプローブカード。

【請求項5】

複数の半導体チップが形成されたウエハが載置されるステージと、

選別試験用テストパターン及び加速試験用テストパターンを記憶するパターンジェネレータと、

電源電圧を出力する電源電圧出力部と、

複数のドライバを有するドライバ回路部と、

前記ステージを駆動するステージ駆動部と、

前記パターンジェネレータ、前記電源電圧出力部、前記ドライバ回路部及び前記ステージ駆動部を制御する制御部とを有し、

前記制御部は、

前記選別試験用テストパターンに応じて前記ドライバ回路部のドライバから選別試験に使用するドライバを振り分け、

前記加速試験用テストパターンに応じて前記ドライバ回路部の残りのドライバから加速試験に使用するドライバを振り分け、

前記電源電圧出力部及び前記ドライバ回路部を制御して、前記選別試験用テストパターンに応じて前記ウエハの第1の半導体チップに対し仕様で定められた電源電圧を供給しながら選別試験用テスト信号を供給するとともに、前記加速試験用テストパターンに応じて前記第2の半導体チップに前記仕様よりも過酷な条件で電源電圧及び加速試験用テスト信号を供給し、前記第1の半導体チップから出力される信号に基づいて前記第1の半導体チップの良否を判定することを特徴とする試験装置。

【請求項1】

同一ウエハ上の第1の半導体チップ及び第2の半導体チップにそれぞれプローブピンを接触させる第1の工程と、

試験装置本体から前記プローブピンを介して前記第1の半導体チップに仕様で定められた条件で電源電圧と第1のテスト信号とを供給するとともに、前記第2の半導体チップに前記仕様で定められた条件よりも過酷な条件で電源電圧と第2のテスト信号とを供給し、前記第1の半導体チップから出力される信号を調べて前記第1の半導体チップの良否を判定する第2の工程と

を有することを特徴とする半導体集積回路の試験方法。

【請求項2】

前記第2の工程を終了した後、前記第2の半導体チップを新たに第1の半導体チップとし、未試験の半導体チップを第2の半導体チップとして、前記第1の工程及び前記第2の工程を繰り返すことを特徴とする請求項1に記載の半導体集積回路の試験方法。

【請求項3】

前記第2の工程では、前記ウエハを加熱することを特徴とする請求項1又は2に記載の半導体集積回路の試験方法。

【請求項4】

ウエハに形成された第1の半導体チップに対し選別試験を行うと同時に前記ウエハに形成された第2の半導体チップに加速試験を行う際に使用するプローブカードであって、

前記プローブカードは、

前記第1の半導体チップの全ての外部接続用電極にそれぞれ個別に接続するように一定のピッチで配列したプローブピンと、

前記第2の半導体チップの外部接続用電極うち電源電圧供給電極及び信号入力電極にそれぞれ個別に接続するように選択的に配置されたプローブピンとを有することを特徴とするプローブカード。

【請求項5】

複数の半導体チップが形成されたウエハが載置されるステージと、

選別試験用テストパターン及び加速試験用テストパターンを記憶するパターンジェネレータと、

電源電圧を出力する電源電圧出力部と、

複数のドライバを有するドライバ回路部と、

前記ステージを駆動するステージ駆動部と、

前記パターンジェネレータ、前記電源電圧出力部、前記ドライバ回路部及び前記ステージ駆動部を制御する制御部とを有し、

前記制御部は、

前記選別試験用テストパターンに応じて前記ドライバ回路部のドライバから選別試験に使用するドライバを振り分け、

前記加速試験用テストパターンに応じて前記ドライバ回路部の残りのドライバから加速試験に使用するドライバを振り分け、

前記電源電圧出力部及び前記ドライバ回路部を制御して、前記選別試験用テストパターンに応じて前記ウエハの第1の半導体チップに対し仕様で定められた電源電圧を供給しながら選別試験用テスト信号を供給するとともに、前記加速試験用テストパターンに応じて前記第2の半導体チップに前記仕様よりも過酷な条件で電源電圧及び加速試験用テスト信号を供給し、前記第1の半導体チップから出力される信号に基づいて前記第1の半導体チップの良否を判定することを特徴とする試験装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−29512(P2011−29512A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2009−175713(P2009−175713)

【出願日】平成21年7月28日(2009.7.28)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成21年7月28日(2009.7.28)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]