半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体集積回路及びその設計方法に関するものである。

【背景技術】

【0002】

半導体集積回路、例えばロジック混載LSIの回路設計では、高集積化と動作周波数速度の向上に伴い、アナログ回路の設計が非常に大きなウエイトを占めている。特に、位相同期回路(PLL:Phase-Locked Loop)などは、ホワイトノイズジッタ(white noise jitter)、perodic jitter 等のジッタの精度がロジック回路(メモリを含む)の動作特性に影響を及ぼす。また、レギュレータにより昇圧あるいは降圧する回路の出力のノイズ特性が、LSI動作に影響を与えてしまう。

【0003】

これらアナログ回路の問題を解決するためには、バッファ能力の増加、キャパシタの容量の増加が必須となる。しかし、バッファ能力やキャパシタの容量を増加すると、チップサイズが増大してしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−121730号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【課題を解決するための手段】

【0006】

一実施態様の半導体集積回路は、半導体基板上にメインブロックとロジック回路を含む周辺ブロックとが混載された半導体集積回路において、前記半導体基板上の前記メインブロックに形成され、第1のトレンチキャパシタを有するメイン回路と、前記半導体基板上の前記周辺ブロックに形成され、第2のトレンチキャパシタを有するアナログ回路とを具備することを特徴とする。

【図面の簡単な説明】

【0007】

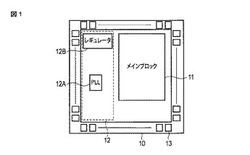

【図1】第1実施形態のメモリ/ロジック混載LSIのレイアウトを示す平面図である。

【図2】第1実施形態のメモリ/ロジック混載LSIにおけるPLLの回路図である。

【図3】第1実施形態のメモリ/ロジック混載LSIにおけるレギュレータの回路図である。

【図4】第1実施形態におけるDRAM及びアナログ回路が含むトレンチキャパシタの断面図である。

【図5】第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの回路図である。

【図6】(a)は第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの平面図であり、(b)はCMOSイメージセンサの断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して実施形態の半導体集積回路について説明する。ここでは、半導体集積回路として、ロジック混載LSI(メモリ/ロジック混載LSI、センサ/ロジック混載LSI)を例に取る。なお、以下の説明において、同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0009】

[第1実施形態]

第1実施形態のメモリ/ロジック混載LSIについて説明する。メモリ/ロジック混載LSIは、メインブロックと周辺ブロックとを有する。メインブロックには、メモリ回路が形成される。周辺ブロックには、ロジック回路及びアナログ回路が形成される。

【0010】

メモリ/ロジック混載LSIは、メモリ回路(例えば、DRAM)のメモリセルにおいて電荷を蓄積するためのトレンチキャパシタを使用している。トレンチキャパシタの製造工程では、トレンチキャパシタを形成するために半導体基板の表面をエッチングしてトレンチが形成される。このとき、トレンチの開口率(占有率)は、製造上問題が生じない所定値に設定する必要がある。その後、トレンチ内には絶縁膜と導電膜が埋め込まれ、トレンチキャパシタが形成される。開口率は、半導体基板の主面に対するトレンチ(またはトレンチキャパシタ)の割合を指す。

【0011】

所定の開口率で形成されたトレンチキャパシタは、DRAMで使用され、従来の場合、残りはダミートレンチキャパシタとして使用されていた。本実施形態では、ダミートレンチキャパシタの少なくとも一部を、アナログ回路(例えば、PLL、レギュレータ)のキャパシタとして使用する。なお、トレンチキャパシタの詳細については後述する。

【0012】

前述した設計の手順(設計方法)を列記すると次のようになる。

【0013】

(1)半導体基板(半導体チップ)に形成するトレンチキャパシタの半導体基板の主面に対する開口率(第1の占有率)を決定する。

【0014】

(2)第1の占有率で形成されるトレンチキャパシタのうち、メモリ回路(DRAM)を含むメインブロックに用いるトレンチキャパシタの第2の占有率を決定する。

【0015】

(3)第1占有率から第2占有率を減算した第3の占有率で形成されるトレンチキャパシタのうち少なくとも1つを、アナログ回路を含む周辺ブロックに用いる。すなわち、半導体基板に形成するトレンチキャパシタのうち、メモリ回路で使用されないトレンチキャパシタをアナログ回路内のキャパシタとして使用する。

【0016】

以下に、前述した設計方法にて設計され形成されたメモリ/ロジック混載LSIについて説明する。

【0017】

図1は、第1実施形態のメモリ/ロジック混載LSIのレイアウトを示す平面図である。

【0018】

図示するように、半導体基板(半導体チップ)10上には、メインブロック11及び周辺ブロック12が配置されている。メインブロック11には、メモリ回路、例えば、DRAMが形成される。周辺ブロック12には、ロジック回路及びアナログ回路、例えば、PLL12A、レギュレータ12Bが形成される。さらに、半導体基板10の端部の周辺領域には、外部接続用のパッド13が配置されている。

【0019】

次に、メモリ/ロジック混載LSIにおけるPLLとレギュレータの回路構成を説明する。

【0020】

図2は、第1実施形態のメモリ/ロジック混載LSIにおけるPLLの回路図である。

【0021】

図示するように、PLLは、位相比較器21、電圧制御発振器(VCO:voltage controlled oscillator)22、増幅器23、ダイオードD1〜D4、抵抗R1、及びトレンチキャパシタC1、C2を含む。

【0022】

位相比較器21の出力部には、電圧制御発振器22の入力部が接続されている。位相比較器21の出力部と電圧制御発振器22の入力部との間には、抵抗とトレンチキャパシタC1を介して電源電圧端VDDが接続されている。トレンチキャパシタC1の両端には、ダイオードD1、D2がそれぞれ接続されている。さらに、位相比較器21の出力部と電圧制御発振器22の入力部との間には、トレンチキャパシタC2を介して電源電圧端VDDが接続されている。トレンチキャパシタC2の両端には、ダイオードD3、D4がそれぞれ接続されている。トレンチキャパシタC1、C2は、半導体基板に形成されたトレンチ内に、絶縁膜及び金属層が埋め込まれて形成されたディープトレンチキャパシタから構成されている。トレンチキャパシタC1、C2の詳細については後述する。

【0023】

図3は、第1実施形態のメモリ/ロジック混載LSIにおけるレギュレータの回路図である。

【0024】

図示するように、レギュレータは、メイン増幅器24、サブ増幅器25、トランジスタT1、T2、抵抗R2、R3、及びトレンチキャパシタC3を含む。

【0025】

入力電圧としての電源電圧VDDは、トランジスタT1のソースに入力される。トランジスタT1のドレインには、トレンチキャパシタC3、抵抗R2が接続されている。抵抗R2は抵抗R3を介して基準電位(例えば、接地電位)に接続されている。また、電源電圧VDDは、メイン増幅器24及びサブ増幅器25の正端子にそれぞれ入力される。メイン増幅器24の負端子はサブ増幅器25の負端子に接続されている。メイン増幅器24の出力端子はトランジスタT1のゲートに接続され、サブ増幅器25の出力端子はトランジスタT2のゲートに接続されている。トレンチキャパシタC3は、半導体基板に形成されたトレンチ内に、絶縁膜及び金属層が埋め込まれて形成されたディープトレンチキャパシタから構成されている。

【0026】

前述したトレンチキャパシタは、メインブロック11に配置されるDRAM内にも形成されている。以下に、トレンチキャパシタについて詳述する。

【0027】

図4は、第1実施形態におけるDRAM及びアナログ回路が含むトレンチキャパシタの断面図である。

【0028】

DRAMが含むトレンチキャパシタは以下のような構造を持つ。

【0029】

図4に示すように、半導体基板30上には、n型ウェル領域31が形成されている。n型ウェル領域31上には、p型ウェル領域32、n型ウェル領域33が形成されている。p型ウェル領域32の表面領域には、n+型拡散層32N、p型拡散層32Pが形成される。n型ウェル領域33の表面領域には、n型拡散層33Nが形成されている。さらに、n型ウェル領域31下の半導体基板30内には、n+型領域30Nが形成されている。

【0030】

p型ウェル領域32、n型ウェル領域31、及びn+型領域30Nには深いトレンチが掘られている。トレンチは、p型ウェル領域32の表面からn型ウェル領域31を通り、n+型領域30Nまで達している。トレンチの側面及び底面には絶縁膜(図示せず)が形成され、トレンチ内の絶縁膜上には金属層34Mが埋め込まれている。これにより、n+型領域30Nと金属層34Mとの間に絶縁膜が配置されてなるトレンチキャパシタ34が形成されている。

【0031】

トレンチキャパシタ34はn+型拡散層32Nに接続され、n+型拡散層32Nは、例えば電源電圧端VDDに接続される。p型拡散層32Pは、例えば接地電位GNDに接続され、n型拡散層33Nはトレンチキャパシタ34が接続されるべきノードに接続される。

【0032】

ロジック回路(PLL、レギュレータ)が含むトレンチキャパシタは以下のような構造を持つ。

【0033】

図4に示すように、半導体基板30上には、n型ウェル領域31が形成されている。n型ウェル領域31上には、p型ウェル領域32、n型ウェル領域33が形成されている。p型ウェル領域32の表面領域には、n+型拡散層32N、p型拡散層32Pが形成される。n型ウェル領域33の表面領域には、n型拡散層33Nが形成されている。n型ウェル領域31下の半導体基板30内には、n+型領域30Nが形成されている。さらに、DRAMとロジック回路のウェル領域間には、p型ウェル領域35が形成されている。

【0034】

p型ウェル領域32、n型ウェル領域31、及びn+型領域30Nには深いトレンチが掘られている。トレンチは、p型ウェル領域32の表面からn型ウェル領域31を通り、n+型領域30Nまで達している。トレンチの側面及び底面には絶縁膜(図示せず)が形成され、トレンチ内の絶縁膜上には金属層34Mが埋め込まれている。これにより、n+型領域30Nと金属層34Mとの間に絶縁膜が配置されてなるトレンチキャパシタC1(またはC2、C3)が形成されている。

【0035】

トレンチキャパシタC1はn+型拡散層32Nに接続され、n+型拡散層32Nは、例えば電源電圧端VDDに接続される。p型拡散層32Pは、例えば接地電位GNDに接続され、n型拡散層33NはトレンチキャパシタC1が接続されるべきノードに接続される。

【0036】

第1実施形態では、PLL内のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。さらに、トレンチキャパシタは容量を大きくすることができるため、PLLの出力(例えば、クロック信号等)を安定させることができる。同様に、レギュレータ内のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。さらに、トレンチキャパシタは容量を大きくすることができるため、レギュレータの出力(例えば、電源)の安定化を図ることができる。

【0037】

前述したように第1実施形態では、アナログ回路内のキャパシタにトレンチキャパシタを用いているため、アナログ回路内のキャパシタが占める占有面積を低減することができる。さらに、トレンチキャパシタを用いることで、キャパシタの容量を増やすことができる。

【0038】

以上説明したように第1実施形態によれば、チップサイズを増大することなく、キャパシタの容量を増やすことが可能である。

【0039】

[第2実施形態]

第2実施形態のセンサ/ロジック混載LSI(固体撮像装置)について説明する。センサ/ロジック混載LSIは、図1に示したように、メインブロック11と周辺ブロック12とを有する。メインブロック11には、イメージセンサ(例えば、CMOSイメージセンサ)が形成される。周辺ブロックには、ロジック回路及びアナログ回路が形成される。その他のレイアウト構成は図1に示した構成と同様である。

【0040】

図5は、第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの回路図である。

【0041】

図示するように、CMOSイメージセンサは、フォトダイオードPD、リードトランジスタT3、リセットトランジスタT4、アドレストランジスタT5、アンプトランジスタT6、リセットトランジスタT7、及びトレンチキャパシタC4を含む。

【0042】

フォトダイオードPDは、リードトランジスタT3を介してフローティングディフュージョンFDに接続されている。フローティングディフュージョンFDには、トレンチキャパシタC4が接続されている。フォトダイオードPDにて光電変換された電荷は、フローティングディフュージョンFDに接続されたトレンチキャパシタC4に蓄積される。

【0043】

フローティングディフュージョンFDには、リセットトランジスタT4を介して電源線が接続される共に、アンプトランジスタT6のゲートが接続されている。アンプトランジスタT6の電流通路の一端は、リセットトランジスタT7を介して基準電位(例えば、接地電位)に接続されている。アンプトランジスタT6の電流通路の他端には、アドレストランジスタT5を介して電源線が接続されている。そして、アンプトランジスタT6の電流通路の一端から、フォトダイオードPDにより検出された信号Vsigが出力される。

【0044】

図6(a)は第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの平面図であり、図6(b)はCMOSイメージセンサの断面図である。なお、これら図6(a)及び図6(b)はCMOSイメージセンサの一部を示すものである。

【0045】

半導体基板40には、フォトダイオードPD、バリア層41、及びトレンチキャパシタC4が形成されている。フォトダイオードPDはn型領域を有し、バリア層41はp型領域から成る。トレンチキャパシタC4は、半導体基板40に掘られた深いトレンチ内に、絶縁膜42と金属層43が埋め込まれて形成されている。すなわち、半導体基板40と金属層43との間に絶縁膜42が配置されてトレンチキャパシタC4が形成されている。

【0046】

半導体基板40上にはゲート絶縁膜44が形成され、ゲート絶縁膜44上にはゲート電極45が形成されている。前記リードトランジスタT3はゲート絶縁膜44及びゲート電極45を有する。同様に、半導体基板40上にはゲート絶縁膜46が形成され、ゲート絶縁膜46上にはゲート電極47が形成されている。前記アンプトランジスタT6はゲート絶縁膜46及びゲート電極47を有する。

【0047】

半導体基板40上には、層間絶縁膜48が形成されている。層間絶縁膜48上には、配線49が形成されている。さらに、層間絶縁膜48内には、半導体基板40に形成された拡散層(図示せず)と配線49とを接続するコンタクトプラグ50が形成されている。

【0048】

第2実施形態では、CMOSイメージセンサ内の画素電圧変換回路のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。すなわち、図5に示したように、1画素辺りの電圧変換回路におけるフローティングディフュージョンFDのキャパシタC4をトレンチキャパシタにする。例えば、5メガ画素を持つCMOSセンサの場合は、5メガ個のトレンチキャパシタをCMOSセンサに形成する。これにより、通常のキャパシタを用いたCMOSセンサと比べて、キャパシタの形成に必要な面積を大幅に削減することができる。

【0049】

また、PLL内のキャパシタにトレンチキャパシタを用いることにより、チップ面積を小さくすることができる。さらに、トレンチキャパシタは容量を大きくすることができるため、PLLの出力(例えば、クロック信号等)を安定させることができる。

【0050】

同様に、レギュレータ内のキャパシタにトレンチキャパシタを用いることにより、チップ面積を小さくすることができる。さらに、トレンチキャパシタは容量を大きくすることができるため、レギュレータの出力(例えば、電源等)の安定化を図ることができる。

【0051】

前述したように第2実施形態では、イメージセンサ内及びアナログ回路内のキャパシタにトレンチキャパシタを用いているため、イメージセンサ内及びロジック回路内のキャパシタが占める占有面積を低減することができる。さらに、トレンチキャパシタを用いることで、キャパシタの容量を増やすことができる。

【0052】

以上説明したように第2実施形態によれば、チップサイズを増大することなく、キャパシタの容量を増やすことができる。

【0053】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0054】

10…半導体基板(半導体チップ)、11…メインブロック、12…周辺ブロック、12A…PLL、12B…レギュレータ、13…パッド、21…位相比較器、22…電圧制御発振器(VCO)、23…増幅器、24…メイン増幅器、25…サブ増幅器、30…半導体基板、31…n型ウェル領域、32…p型ウェル領域、33…n型ウェル領域、32N…n+型拡散層、32P…p型拡散層、33…n型ウェル領域、33N…n型拡散層、30N…n+型領域、34M…金属層、34…トレンチキャパシタ、40…半導体基板、41…バリア層、42…絶縁膜、43…金属層、44…ゲート絶縁膜、45…ゲート電極、46…ゲート絶縁膜、47…ゲート電極、48…層間絶縁膜、49…配線、50…コンタクトプラグ、C1,C2,C3,C4…トレンチキャパシタ、D1〜D4…ダイオード、PD…フォトダイオード、FD…フローティングディフュージョン、R1,R2,R3…抵抗、T1,T2…トランジスタ、T3…リードトランジスタ、T4…リセットトランジスタ、T5…アドレストランジスタ、T6…アンプトランジスタ、T7…リセットトランジスタ。

【技術分野】

【0001】

本発明の実施形態は、半導体集積回路及びその設計方法に関するものである。

【背景技術】

【0002】

半導体集積回路、例えばロジック混載LSIの回路設計では、高集積化と動作周波数速度の向上に伴い、アナログ回路の設計が非常に大きなウエイトを占めている。特に、位相同期回路(PLL:Phase-Locked Loop)などは、ホワイトノイズジッタ(white noise jitter)、perodic jitter 等のジッタの精度がロジック回路(メモリを含む)の動作特性に影響を及ぼす。また、レギュレータにより昇圧あるいは降圧する回路の出力のノイズ特性が、LSI動作に影響を与えてしまう。

【0003】

これらアナログ回路の問題を解決するためには、バッファ能力の増加、キャパシタの容量の増加が必須となる。しかし、バッファ能力やキャパシタの容量を増加すると、チップサイズが増大してしまう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−121730号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【課題を解決するための手段】

【0006】

一実施態様の半導体集積回路は、半導体基板上にメインブロックとロジック回路を含む周辺ブロックとが混載された半導体集積回路において、前記半導体基板上の前記メインブロックに形成され、第1のトレンチキャパシタを有するメイン回路と、前記半導体基板上の前記周辺ブロックに形成され、第2のトレンチキャパシタを有するアナログ回路とを具備することを特徴とする。

【図面の簡単な説明】

【0007】

【図1】第1実施形態のメモリ/ロジック混載LSIのレイアウトを示す平面図である。

【図2】第1実施形態のメモリ/ロジック混載LSIにおけるPLLの回路図である。

【図3】第1実施形態のメモリ/ロジック混載LSIにおけるレギュレータの回路図である。

【図4】第1実施形態におけるDRAM及びアナログ回路が含むトレンチキャパシタの断面図である。

【図5】第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの回路図である。

【図6】(a)は第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの平面図であり、(b)はCMOSイメージセンサの断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して実施形態の半導体集積回路について説明する。ここでは、半導体集積回路として、ロジック混載LSI(メモリ/ロジック混載LSI、センサ/ロジック混載LSI)を例に取る。なお、以下の説明において、同一の機能及び構成を有する構成要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0009】

[第1実施形態]

第1実施形態のメモリ/ロジック混載LSIについて説明する。メモリ/ロジック混載LSIは、メインブロックと周辺ブロックとを有する。メインブロックには、メモリ回路が形成される。周辺ブロックには、ロジック回路及びアナログ回路が形成される。

【0010】

メモリ/ロジック混載LSIは、メモリ回路(例えば、DRAM)のメモリセルにおいて電荷を蓄積するためのトレンチキャパシタを使用している。トレンチキャパシタの製造工程では、トレンチキャパシタを形成するために半導体基板の表面をエッチングしてトレンチが形成される。このとき、トレンチの開口率(占有率)は、製造上問題が生じない所定値に設定する必要がある。その後、トレンチ内には絶縁膜と導電膜が埋め込まれ、トレンチキャパシタが形成される。開口率は、半導体基板の主面に対するトレンチ(またはトレンチキャパシタ)の割合を指す。

【0011】

所定の開口率で形成されたトレンチキャパシタは、DRAMで使用され、従来の場合、残りはダミートレンチキャパシタとして使用されていた。本実施形態では、ダミートレンチキャパシタの少なくとも一部を、アナログ回路(例えば、PLL、レギュレータ)のキャパシタとして使用する。なお、トレンチキャパシタの詳細については後述する。

【0012】

前述した設計の手順(設計方法)を列記すると次のようになる。

【0013】

(1)半導体基板(半導体チップ)に形成するトレンチキャパシタの半導体基板の主面に対する開口率(第1の占有率)を決定する。

【0014】

(2)第1の占有率で形成されるトレンチキャパシタのうち、メモリ回路(DRAM)を含むメインブロックに用いるトレンチキャパシタの第2の占有率を決定する。

【0015】

(3)第1占有率から第2占有率を減算した第3の占有率で形成されるトレンチキャパシタのうち少なくとも1つを、アナログ回路を含む周辺ブロックに用いる。すなわち、半導体基板に形成するトレンチキャパシタのうち、メモリ回路で使用されないトレンチキャパシタをアナログ回路内のキャパシタとして使用する。

【0016】

以下に、前述した設計方法にて設計され形成されたメモリ/ロジック混載LSIについて説明する。

【0017】

図1は、第1実施形態のメモリ/ロジック混載LSIのレイアウトを示す平面図である。

【0018】

図示するように、半導体基板(半導体チップ)10上には、メインブロック11及び周辺ブロック12が配置されている。メインブロック11には、メモリ回路、例えば、DRAMが形成される。周辺ブロック12には、ロジック回路及びアナログ回路、例えば、PLL12A、レギュレータ12Bが形成される。さらに、半導体基板10の端部の周辺領域には、外部接続用のパッド13が配置されている。

【0019】

次に、メモリ/ロジック混載LSIにおけるPLLとレギュレータの回路構成を説明する。

【0020】

図2は、第1実施形態のメモリ/ロジック混載LSIにおけるPLLの回路図である。

【0021】

図示するように、PLLは、位相比較器21、電圧制御発振器(VCO:voltage controlled oscillator)22、増幅器23、ダイオードD1〜D4、抵抗R1、及びトレンチキャパシタC1、C2を含む。

【0022】

位相比較器21の出力部には、電圧制御発振器22の入力部が接続されている。位相比較器21の出力部と電圧制御発振器22の入力部との間には、抵抗とトレンチキャパシタC1を介して電源電圧端VDDが接続されている。トレンチキャパシタC1の両端には、ダイオードD1、D2がそれぞれ接続されている。さらに、位相比較器21の出力部と電圧制御発振器22の入力部との間には、トレンチキャパシタC2を介して電源電圧端VDDが接続されている。トレンチキャパシタC2の両端には、ダイオードD3、D4がそれぞれ接続されている。トレンチキャパシタC1、C2は、半導体基板に形成されたトレンチ内に、絶縁膜及び金属層が埋め込まれて形成されたディープトレンチキャパシタから構成されている。トレンチキャパシタC1、C2の詳細については後述する。

【0023】

図3は、第1実施形態のメモリ/ロジック混載LSIにおけるレギュレータの回路図である。

【0024】

図示するように、レギュレータは、メイン増幅器24、サブ増幅器25、トランジスタT1、T2、抵抗R2、R3、及びトレンチキャパシタC3を含む。

【0025】

入力電圧としての電源電圧VDDは、トランジスタT1のソースに入力される。トランジスタT1のドレインには、トレンチキャパシタC3、抵抗R2が接続されている。抵抗R2は抵抗R3を介して基準電位(例えば、接地電位)に接続されている。また、電源電圧VDDは、メイン増幅器24及びサブ増幅器25の正端子にそれぞれ入力される。メイン増幅器24の負端子はサブ増幅器25の負端子に接続されている。メイン増幅器24の出力端子はトランジスタT1のゲートに接続され、サブ増幅器25の出力端子はトランジスタT2のゲートに接続されている。トレンチキャパシタC3は、半導体基板に形成されたトレンチ内に、絶縁膜及び金属層が埋め込まれて形成されたディープトレンチキャパシタから構成されている。

【0026】

前述したトレンチキャパシタは、メインブロック11に配置されるDRAM内にも形成されている。以下に、トレンチキャパシタについて詳述する。

【0027】

図4は、第1実施形態におけるDRAM及びアナログ回路が含むトレンチキャパシタの断面図である。

【0028】

DRAMが含むトレンチキャパシタは以下のような構造を持つ。

【0029】

図4に示すように、半導体基板30上には、n型ウェル領域31が形成されている。n型ウェル領域31上には、p型ウェル領域32、n型ウェル領域33が形成されている。p型ウェル領域32の表面領域には、n+型拡散層32N、p型拡散層32Pが形成される。n型ウェル領域33の表面領域には、n型拡散層33Nが形成されている。さらに、n型ウェル領域31下の半導体基板30内には、n+型領域30Nが形成されている。

【0030】

p型ウェル領域32、n型ウェル領域31、及びn+型領域30Nには深いトレンチが掘られている。トレンチは、p型ウェル領域32の表面からn型ウェル領域31を通り、n+型領域30Nまで達している。トレンチの側面及び底面には絶縁膜(図示せず)が形成され、トレンチ内の絶縁膜上には金属層34Mが埋め込まれている。これにより、n+型領域30Nと金属層34Mとの間に絶縁膜が配置されてなるトレンチキャパシタ34が形成されている。

【0031】

トレンチキャパシタ34はn+型拡散層32Nに接続され、n+型拡散層32Nは、例えば電源電圧端VDDに接続される。p型拡散層32Pは、例えば接地電位GNDに接続され、n型拡散層33Nはトレンチキャパシタ34が接続されるべきノードに接続される。

【0032】

ロジック回路(PLL、レギュレータ)が含むトレンチキャパシタは以下のような構造を持つ。

【0033】

図4に示すように、半導体基板30上には、n型ウェル領域31が形成されている。n型ウェル領域31上には、p型ウェル領域32、n型ウェル領域33が形成されている。p型ウェル領域32の表面領域には、n+型拡散層32N、p型拡散層32Pが形成される。n型ウェル領域33の表面領域には、n型拡散層33Nが形成されている。n型ウェル領域31下の半導体基板30内には、n+型領域30Nが形成されている。さらに、DRAMとロジック回路のウェル領域間には、p型ウェル領域35が形成されている。

【0034】

p型ウェル領域32、n型ウェル領域31、及びn+型領域30Nには深いトレンチが掘られている。トレンチは、p型ウェル領域32の表面からn型ウェル領域31を通り、n+型領域30Nまで達している。トレンチの側面及び底面には絶縁膜(図示せず)が形成され、トレンチ内の絶縁膜上には金属層34Mが埋め込まれている。これにより、n+型領域30Nと金属層34Mとの間に絶縁膜が配置されてなるトレンチキャパシタC1(またはC2、C3)が形成されている。

【0035】

トレンチキャパシタC1はn+型拡散層32Nに接続され、n+型拡散層32Nは、例えば電源電圧端VDDに接続される。p型拡散層32Pは、例えば接地電位GNDに接続され、n型拡散層33NはトレンチキャパシタC1が接続されるべきノードに接続される。

【0036】

第1実施形態では、PLL内のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。さらに、トレンチキャパシタは容量を大きくすることができるため、PLLの出力(例えば、クロック信号等)を安定させることができる。同様に、レギュレータ内のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。さらに、トレンチキャパシタは容量を大きくすることができるため、レギュレータの出力(例えば、電源)の安定化を図ることができる。

【0037】

前述したように第1実施形態では、アナログ回路内のキャパシタにトレンチキャパシタを用いているため、アナログ回路内のキャパシタが占める占有面積を低減することができる。さらに、トレンチキャパシタを用いることで、キャパシタの容量を増やすことができる。

【0038】

以上説明したように第1実施形態によれば、チップサイズを増大することなく、キャパシタの容量を増やすことが可能である。

【0039】

[第2実施形態]

第2実施形態のセンサ/ロジック混載LSI(固体撮像装置)について説明する。センサ/ロジック混載LSIは、図1に示したように、メインブロック11と周辺ブロック12とを有する。メインブロック11には、イメージセンサ(例えば、CMOSイメージセンサ)が形成される。周辺ブロックには、ロジック回路及びアナログ回路が形成される。その他のレイアウト構成は図1に示した構成と同様である。

【0040】

図5は、第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの回路図である。

【0041】

図示するように、CMOSイメージセンサは、フォトダイオードPD、リードトランジスタT3、リセットトランジスタT4、アドレストランジスタT5、アンプトランジスタT6、リセットトランジスタT7、及びトレンチキャパシタC4を含む。

【0042】

フォトダイオードPDは、リードトランジスタT3を介してフローティングディフュージョンFDに接続されている。フローティングディフュージョンFDには、トレンチキャパシタC4が接続されている。フォトダイオードPDにて光電変換された電荷は、フローティングディフュージョンFDに接続されたトレンチキャパシタC4に蓄積される。

【0043】

フローティングディフュージョンFDには、リセットトランジスタT4を介して電源線が接続される共に、アンプトランジスタT6のゲートが接続されている。アンプトランジスタT6の電流通路の一端は、リセットトランジスタT7を介して基準電位(例えば、接地電位)に接続されている。アンプトランジスタT6の電流通路の他端には、アドレストランジスタT5を介して電源線が接続されている。そして、アンプトランジスタT6の電流通路の一端から、フォトダイオードPDにより検出された信号Vsigが出力される。

【0044】

図6(a)は第2実施形態のセンサ/ロジック混載LSIにおけるCMOSイメージセンサの平面図であり、図6(b)はCMOSイメージセンサの断面図である。なお、これら図6(a)及び図6(b)はCMOSイメージセンサの一部を示すものである。

【0045】

半導体基板40には、フォトダイオードPD、バリア層41、及びトレンチキャパシタC4が形成されている。フォトダイオードPDはn型領域を有し、バリア層41はp型領域から成る。トレンチキャパシタC4は、半導体基板40に掘られた深いトレンチ内に、絶縁膜42と金属層43が埋め込まれて形成されている。すなわち、半導体基板40と金属層43との間に絶縁膜42が配置されてトレンチキャパシタC4が形成されている。

【0046】

半導体基板40上にはゲート絶縁膜44が形成され、ゲート絶縁膜44上にはゲート電極45が形成されている。前記リードトランジスタT3はゲート絶縁膜44及びゲート電極45を有する。同様に、半導体基板40上にはゲート絶縁膜46が形成され、ゲート絶縁膜46上にはゲート電極47が形成されている。前記アンプトランジスタT6はゲート絶縁膜46及びゲート電極47を有する。

【0047】

半導体基板40上には、層間絶縁膜48が形成されている。層間絶縁膜48上には、配線49が形成されている。さらに、層間絶縁膜48内には、半導体基板40に形成された拡散層(図示せず)と配線49とを接続するコンタクトプラグ50が形成されている。

【0048】

第2実施形態では、CMOSイメージセンサ内の画素電圧変換回路のキャパシタにトレンチキャパシタを用いることにより、キャパシタの占有面積を小さくできる。これにより、チップ面積を低減することができる。すなわち、図5に示したように、1画素辺りの電圧変換回路におけるフローティングディフュージョンFDのキャパシタC4をトレンチキャパシタにする。例えば、5メガ画素を持つCMOSセンサの場合は、5メガ個のトレンチキャパシタをCMOSセンサに形成する。これにより、通常のキャパシタを用いたCMOSセンサと比べて、キャパシタの形成に必要な面積を大幅に削減することができる。

【0049】

また、PLL内のキャパシタにトレンチキャパシタを用いることにより、チップ面積を小さくすることができる。さらに、トレンチキャパシタは容量を大きくすることができるため、PLLの出力(例えば、クロック信号等)を安定させることができる。

【0050】

同様に、レギュレータ内のキャパシタにトレンチキャパシタを用いることにより、チップ面積を小さくすることができる。さらに、トレンチキャパシタは容量を大きくすることができるため、レギュレータの出力(例えば、電源等)の安定化を図ることができる。

【0051】

前述したように第2実施形態では、イメージセンサ内及びアナログ回路内のキャパシタにトレンチキャパシタを用いているため、イメージセンサ内及びロジック回路内のキャパシタが占める占有面積を低減することができる。さらに、トレンチキャパシタを用いることで、キャパシタの容量を増やすことができる。

【0052】

以上説明したように第2実施形態によれば、チップサイズを増大することなく、キャパシタの容量を増やすことができる。

【0053】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0054】

10…半導体基板(半導体チップ)、11…メインブロック、12…周辺ブロック、12A…PLL、12B…レギュレータ、13…パッド、21…位相比較器、22…電圧制御発振器(VCO)、23…増幅器、24…メイン増幅器、25…サブ増幅器、30…半導体基板、31…n型ウェル領域、32…p型ウェル領域、33…n型ウェル領域、32N…n+型拡散層、32P…p型拡散層、33…n型ウェル領域、33N…n型拡散層、30N…n+型領域、34M…金属層、34…トレンチキャパシタ、40…半導体基板、41…バリア層、42…絶縁膜、43…金属層、44…ゲート絶縁膜、45…ゲート電極、46…ゲート絶縁膜、47…ゲート電極、48…層間絶縁膜、49…配線、50…コンタクトプラグ、C1,C2,C3,C4…トレンチキャパシタ、D1〜D4…ダイオード、PD…フォトダイオード、FD…フローティングディフュージョン、R1,R2,R3…抵抗、T1,T2…トランジスタ、T3…リードトランジスタ、T4…リセットトランジスタ、T5…アドレストランジスタ、T6…アンプトランジスタ、T7…リセットトランジスタ。

【特許請求の範囲】

【請求項1】

半導体基板上にメインブロックとロジック回路を含む周辺ブロックとが混載された半導体集積回路において、

前記半導体基板上の前記メインブロックに形成され、第1のトレンチキャパシタを有するメイン回路と、

前記半導体基板上の前記周辺ブロックに形成され、第2のトレンチキャパシタを有するアナログ回路と、

を具備することを特徴とする半導体集積回路。

【請求項2】

前記メイン回路は、メモリ回路またはイメージセンサ回路のいずれかを含むことを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記アナログ回路は、位相同期回路(PLL)またはレギュレータの少なくともいずれかを含むことを特徴とする請求項1または2に記載の半導体集積回路。

【請求項4】

前記メモリ回路はDRAMを含むことを特徴とする請求項2に記載の半導体集積回路。

【請求項5】

半導体基板の主面上にメインブロックとロジック回路を含む周辺ブロックとが混載される半導体集積回路の設計方法において、

前記半導体基板に形成するトレンチキャパシタの前記半導体基板の主面に対する第1の占有率を決定するステップと、

前記第1の占有率で形成されるトレンチキャパシタのうち、前記メインブロックに用いる前記トレンチキャパシタの第2の占有率を決定するステップと、

前記第1占有率から前記第2占有率を減算した第3の占有率で形成されるトレンチキャパシタのうち少なくとも1つを前記周辺ブロックに用いるステップと、

を具備することを特徴とする半導体集積回路の設計方法。

【請求項1】

半導体基板上にメインブロックとロジック回路を含む周辺ブロックとが混載された半導体集積回路において、

前記半導体基板上の前記メインブロックに形成され、第1のトレンチキャパシタを有するメイン回路と、

前記半導体基板上の前記周辺ブロックに形成され、第2のトレンチキャパシタを有するアナログ回路と、

を具備することを特徴とする半導体集積回路。

【請求項2】

前記メイン回路は、メモリ回路またはイメージセンサ回路のいずれかを含むことを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記アナログ回路は、位相同期回路(PLL)またはレギュレータの少なくともいずれかを含むことを特徴とする請求項1または2に記載の半導体集積回路。

【請求項4】

前記メモリ回路はDRAMを含むことを特徴とする請求項2に記載の半導体集積回路。

【請求項5】

半導体基板の主面上にメインブロックとロジック回路を含む周辺ブロックとが混載される半導体集積回路の設計方法において、

前記半導体基板に形成するトレンチキャパシタの前記半導体基板の主面に対する第1の占有率を決定するステップと、

前記第1の占有率で形成されるトレンチキャパシタのうち、前記メインブロックに用いる前記トレンチキャパシタの第2の占有率を決定するステップと、

前記第1占有率から前記第2占有率を減算した第3の占有率で形成されるトレンチキャパシタのうち少なくとも1つを前記周辺ブロックに用いるステップと、

を具備することを特徴とする半導体集積回路の設計方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−110254(P2013−110254A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253804(P2011−253804)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]