半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体拡散プロセスにより製造された半導体集積回路及びそれを内包した半導体装置又は電子機器に関する。

【背景技術】

【0002】

近年、情報通信機器又は事務用電子機器の小型化及び高機能化が進展するのに伴って、これらの機器に搭載される半導体集積回路についても、小型化及び高集積化が要求されている。そのため、端子配置がペリフェラル配置からエリアアレイ配置に移行することにより、端子数の増大が図られている。しかし、従来のエリアアレイ配置は、ハイエンド製品に適用されており小型化への要求が強くはなかったが、近年の民生分野へのエリアアレイ配置の採用により、小型化への要求が非常に強くなってきている。

【0003】

このような要求を実現させる目的で、半導体チップ周辺部の縮小による小型化が検討されるようになってきている。

【0004】

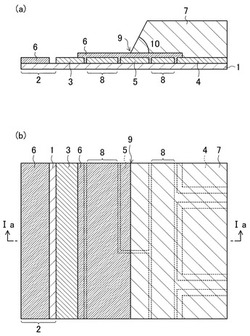

図6(a)及び(b)は、従来の半導体集積回路における半導体チップ周辺部を示しており、図6(a)はその断面図であって図6(b)のVIa-VIa線に対応するものであり、図6(b)はその平面図を示している。

【0005】

図6(a)及び(b)に示すように、半導体チップ101上には、半導体チップ101周辺部のスクライブ領域102の近傍にシールリング103が設けられており、該シールリング103よりも内側にパッド104が設けられている。また、半導体チップ101上には、シールリング103とパッド104との間に位置するように、配線105が形成されている。また、スクライブ領域102の一部を覆うと共に、シールリング103の一部からパッド104の一部までを覆うように無機物又は有機物からなる保護膜106が形成されており、保護膜106の一部からパッド104までを覆うように有機物からなる保護膜107が形成されている。保護膜107の終端縁109は、図6(a)及び(b)に示すようにシールリング103とパッド104の間に位置しているが、シールリング103よりも外側に位置したり、パッド104よりも内側に位置することもある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−287906号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述したような従来の構造では、保護膜107の終端縁9をシールリング103よりも外側に配置する場合には、ダイシング時にブレードが保護膜107に接触しないようスクライブ領域102を広く設定する必要がある。一方で、保護膜107の終端縁109をパッド104よりも内側に配置する場合には、パッド104と内部のバンプとの距離を広く設定する必要があり、且つ、パッド104が露出することによる腐食の懸念が発生する。また、保護膜107の終端縁109をシールリング103とパッド104との間に配置する場合には、保護膜107の位置精度を考慮する必要がある。さらに、保護膜107の終端縁109の下部に凹凸が存在すると剥離の懸念があるため、配線105などが保護膜107の終端縁109の下部に位置する可能性がないよう、シールリング103とパッド104との間を広げるなどの考慮が必要である。以上のように、保護膜107の終端縁109の配置制約が存在することにより、半導体チップの小型化が妨げられていた。

【0008】

前記に鑑み、本発明の目的は、保護膜の終端縁がシールリングとパッドとの間に配置される構造を有する半導体集積回路及びそれを備えた半導体装置、電子機器において、半導体チップ周辺部の拡大を抑制できる構造を提供することである。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、本発明の一形態の半導体集積回路は、半導体チップ上に、半導体チップの外周部に形成されたシールリングと、半導体チップ上に、シールリングよりも半導体チップの中央部側に形成されたパッドと、半導体チップ上に、シールリングとパッドとの間に形成された配線と、半導体チップ上に、シールリングと配線との間に形成されていると共に、配線とパッドとの間に形成されているダミーパターンと、シールリングの一部からパッドの一部までの間を覆うように形成された第1の保護膜と、第1の保護膜の一部及びパッドを覆うよう形成された第2の保護膜とを備えている。

【0010】

本発明の一形態の半導体装置において、第2の保護膜の終端縁は、シールリングとパッドとの間に位置していてもよい。

【0011】

本発明の一形態の半導体装置において、前記第2の保護膜の終端縁は、前記配線上に位置していてもよい。

【0012】

本発明の一形態の半導体装置において、ダミーパターンにおける配線を挟んで互いに向かい合う部分の端部が、第2の保護膜の終端縁を中心に半導体チップの周縁部側及び中央部側方向に5μmの間隔以内に位置していてもよい。

【0013】

本発明の一形態の半導体集積回路によると、第2の保護膜の終端縁の位置精度範囲内に、配線と同一層で形成され、配線を挟んで互いに向かい合うダミーパターンの部分の端部が配置されていることにより、第2の保護膜の終端縁の下部に凹凸が形成されても1μm以内の凹凸に設定できる。その結果、第2の保護膜の剥離の懸念を小さくすることができると共に、第2の保護膜の密着性を確保することができる。さらに、ダミーパターンの存在により、従来の半導体集積回路のような配線などが保護膜の終端の下部に位置する可能性がないようシールリングとパッドとの間を広げるという検討が本形態では不要となって、シールリングとパッドとの距離を第2の保護膜の位置精度のみで規定することができ、半導体チップ周辺部の拡大を抑制してその縮小化が可能となる。

【0014】

本発明の一形態の半導体集積回路において、ダミーパターンは、第2の保護膜の終端縁に対して垂直方向に伸びるように形成された複数の直方体からなってもよい。

【0015】

本発明の一形態の半導体集積回路において、ダミーパターンは、複数の四角柱からなってもよい。

【0016】

本発明の一形態の半導体装置において、前記複数の四角柱からダミーパターンは、表面の四角形の最大辺が5μm以下であってもよい。

【0017】

本発明の一形態の半導体集積回路において、ダミーパターンは、複数の六角柱からなってもよい。

【0018】

本発明の一形態の半導体装置において、前記複数の六角柱からなるダミーパターンは、表面の六角形の最大対角線が5μm以下であってもよい。

【0019】

本発明の一形態の半導体集積回路において、ダミーパターン同士の間、ダミーパターンとシールリングとの間、ダミーパターンと配線との間、ダミーパターンとパッドとの間に存在するギャップの幅が5μm以下であってもよい。

【0020】

本発明の一形態の半導体集積回路において、第1の保護膜の表面の平坦度が1μm以下であってもよい。

【0021】

本発明の一形態の半導体集積回路において、第1の保護膜に対する第2の保護膜の終端縁の接触角は、90°未満であってもよい。

【0022】

本発明の一形態の半導体集積回路において、第2の保護膜の終端縁の面内での角部は鈍角であってもよい。

【0023】

本発明の一形態の半導体装置は、上記半導体集積回路を備えた半導体装置である。

【0024】

本発明の一形態の電子機器は、上記半導体装置を備えた電子機器である。

【発明の効果】

【0025】

本発明の一側面の半導体集積回路によると、半導体集積回路及びそれを備えた電子機器において、半導体チップ周辺部の拡大を抑制できる構造を実現できる。その結果、半導体集積回路及びそれを備えた電子機器の小型化を実現できる。

【図面の簡単な説明】

【0026】

【図1】図1(a)及び(b)は、本実施形態の半導体集積回路における半導体チップ周辺部を示しており、図1(a)はその断面図であって図1(b)のIa-Ia線に対応するものであり、図1(b)はその平面図を示している。

【図2】図2(a)及び(b)は、本実施形態の半導体集積回路の第1の変形例における半導体チップ周辺部を示しており、図2(a)はその断面図であって図2(b)のIIa-IIa線に対応するものであり、図2(b)はその平面図を示している。

【図3】図3(a)及び(b)は、本実施形態の半導体集積回路の第2の変形例における半導体チップ周辺部を示しており、図3(a)はその断面図であって図3(b)のIIIa-IIIa線に対応するものであり、図3(b)はその平面図を示している。

【図4】図4(a)及び(b)は、本実施形態の半導体集積回路の第3の変形例における半導体チップ周辺部を示しており、図4(a)はその断面図であって図4(b)のIVa-IVa線に対応するものであり、図4(b)はその平面図を示している。

【図5】図5(a)及び(b)は、本実施形態の半導体集積回路の第7の変形例における半導体チップ周辺部を示しており、図5(a)はその断面図であって図5(b)のVa-Va線に対応するものであり、図5(b)はその平面図を示している。

【図6】図6(a)及び(b)は、従来の半導体集積回路における半導体チップ周辺部を示しており、図6(a)はその断面図であって図6(b)のVIa-VIa線に対応するものであり、図6(b)はその平面図を示している。

【発明を実施するための形態】

【0027】

以下、本発明の一実施形態に係る半導体集積回路及びそれを備えた電子機器について、図面を参照しながら説明する。

【0028】

図1(a)及び(b)は、本実施形態の半導体集積回路における半導体チップ周辺部を示しており、図1(a)はその断面図であって図1(b)のIa-Ia線に対応するものであり、図1(b)はその平面図を示している。

【0029】

図1(a)及び(b)に示すように、例えばシリコンからなる半導体チップ(半導体基板)1上には、半導体チップの回路形成面の周辺部におけるスクライブ領域2の近傍に例えばアルミニウム(Al)からなるリング状のシールリング3が設けられており、該シールリング3よりも半導体チップ1の中央側(内側)に例えばアルミニウム(Al)からなるパッド4が設けられている。また、半導体チップ1上には、シールリング3とパッド4との間に位置するように、例えばアルミニウム(Al)からなる配線5が形成されている。また、配線5とシールリング3との間、及び、配線5とパッド4との間の各々には、例えば配線5と同一層からなる単一の構造体からなるダミーパターン8が設けられている。また、スクライブ領域2の一部を覆うと共に、シールリング103の一部からダミーパターン8及び配線5を含んでパッド4の一部までを覆うように、無機物又は有機物からなり、例えばここではシリコンナイトライド(SiN)からなる保護膜6が形成されている。なお、保護膜6は、スクライブ領域2上の一部又は全部を覆うように形成されていてもよい。

【0030】

また、保護膜6の一部からパッド4までを覆うように、有機物からなり、例えばここではポリイミド又はPBOからなる保護膜7が形成されている。保護膜7の終端縁(底面における半導体チップ外側方向の縁部)9は、図1(a)及び(b)に示すようにシールリング3とパッド4との間のいずれかの位置に配置されており、ここでは配線5及びダミーパターン8上に配置されている。このように、保護膜7の終端縁9は、シールリング3よりも半導体チップ1の周縁部側に(外側に)位置しないため、ダイシング時にブレードが保護膜7に接触しないようスクライブ領域2を広く設定する必要がない。また、パッド4よりも半導体チップ1の中央側に(内側に)位置しないため、パッド4と内部のバンプ(図示せず)の距離を広く設定する必要がなく、且つ、パッド4が露出することによる腐食の懸念がなくなる。

【0031】

また、ダミーパターン8と保護膜7の終端縁9との配置関係については、保護膜7の形成位置の精度を考慮して、ダミーパターン8は、配線5を挟んで互いに向かい合う部分の端部が、該保護膜7の終端縁9を中心に半導体チップ1の周縁部側(外側)及び中央部側(内側)方向に5μmの間隔以内に位置するように配置されている。なお、ここで、外側及び内側とは、上記の通り、半導体チップにおける中央部側方向が内側であり、半導体チップにおける周縁部側方向が外側である。

【0032】

上記本実施形態に係る半導体集積回路によると、保護膜7の終端縁9の位置精度範囲内に、配線5と同一層で形成され、配線5を挟んで互いに向かい合うダミーパターン8の部分の端部が配置されていることにより、保護膜7の終端縁9の下部に凹凸が形成されても1μm以内の凹凸に設定できる。その結果、保護膜7の剥離の懸念を小さくすることができると共に、保護膜7の密着性を確保することができる。さらに、ダミーパターン8の存在により、従来の半導体集積回路のような配線などが保護膜の終端の下部に位置する可能性がないようシールリング3とパッド4との間を広げるという検討が本実施形態では不要となって、シールリング3とパッド4との距離を保護膜7の位置精度のみで規定することができ、半導体チップ周辺部の拡大を抑制してその縮小化が可能となる。

【0033】

−第1の変形例−

図2(a)及び(b)は、本実施形態の半導体集積回路の第1の変形例における半導体チップ周辺部を示しており、図2(a)はその断面図であって図2(b)のIIa-IIa線に対応するものであり、図2(b)はその平面図を示している。

【0034】

図2(a)及び(b)に示す第1の変形例における半導体チップ周辺部の構造では、ダミーパターン8aが、保護膜7の終端縁9(終端縁9が伸びる方向)に対して垂直方向に伸びるように形成された複数の直方体からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0035】

本実施形態の第1の変形例によると、複数の四角柱からなるダミーパターン8bを設けることにより、図1(a)及び(b)に示したダミーパターン8のような単一の構造体からなるベタパターンを配置する必要がないと共に、保護膜7のズレによる終端縁9の位置の高さバラツキを抑制することができため、保護膜7の終端縁9の密着性をより確保することができる。

【0036】

−第2の変形例−

図3(a)及び(b)は、本実施形態の半導体集積回路の第2の変形例における半導体チップ周辺部を示しており、図3(a)はその断面図であって図3(b)のIIIa-IIIa線に対応するものであり、図3(b)はその平面図を示している。

【0037】

図3(a)及び(b)に示す第2の変形例における半導体チップ周辺部の構造では、ダミーパターン8bが、表面の四角形の最大辺が5μm以下となる複数の四角柱からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0038】

本実施形態の第2の変形例によると、複数の四角柱からなるダミーパターン8bを設けることにより、上記第1及び第2の変形例と比較して、ダミーパターンの配置の自由度を向上させることができる。

【0039】

−第3の変形例−

図4(a)及び(b)は、本実施形態の半導体集積回路の第3の変形例における半導体チップ周辺部を示しており、図4(a)はその断面図であって図4(b)のIVa-IVa線に対応するものであり、図4(b)はその平面図を示している。

【0040】

図4(a)及び(b)に示す第3の変形例における半導体チップ周辺部の構造では、ダミーパターン8cが、六角形の対角に位置する頂点同士間(対角線)の距離が最大5μm以下となる複数の六角柱からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0041】

本実施形態の第3の変形例によると、複数の六角柱からなるダミーパターン8cを設けることにより、上記第2及び第3の変形例と比較して、ダミーパターンをより細密に配置することができるため、保護膜7の平面性及び密着性を向上させることができる。

【0042】

−第4の変形例−

本実施形態の半導体集積回路の第4の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、単一又は複数の構造体からなるダミーパターン(8、8a、8b)とシールリング3、パッド4及び配線5との間に存在するギャップの幅、並びに、複数の構造体からなるダミーパターン(8a、8b、8c)における各構造体間に存在するギャップの幅が5μm以下となる構造を有している。

【0043】

本実施形態の第4の変形例によると、上記各ギャップの幅が5μm以下であることにより、それらの上に形成され得る保護膜7の表面の高低差を小さくし、表面の平坦性をより確保することができる。

【0044】

−第5の変形例−

本実施形態の半導体集積回路の第5の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、保護膜6の表面を研磨することでその平坦度を1μm以下とした構造を有している。

【0045】

本実施形態の第5の変形例によると、保護膜6の表面の平坦度が向上することにより、その上に形成される保護膜7の表面の平坦度をより向上させることができる。

【0046】

−第6の変形例−

本実施形態の半導体集積回路の第6の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、保護膜6に対する保護膜7の終端縁の接触角(立ち上がり角度)(図1〜図4の符号10参照)が90°未満である構造を有している。

【0047】

本実施形態の第6の変形例によると、曲げなどの外力が加わる際に保護膜6と保護膜7とを引き剥がす方向の応力が発生した場合においても、保護膜6と保護膜7との隙間の亀裂又は剥離が発生しにくい構造となるため、保護膜7の終端縁9の密着性をより確保することができる。

【0048】

−第7の変形例−

図5(a)及び(b)は、本実施形態の半導体集積回路の第7の変形例における半導体チップ周辺部を示しており、図5(a)はその断面図であって図5(b)のVa-Va線に対応するものであり、図5(b)はその平面図を示している。

【0049】

図5(a)及び(b)に示す第7の変形例における半導体チップ周辺部の構造では、保護膜7の終端縁9の面内での角部がいずれも鈍角αとなっている構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0050】

本実施形態の第7の変形例によると、保護膜7の局所的に小さな密着面積となる配置を防ぐことができるため、保護膜7の終端縁9の密着性をより確保することができる。

【0051】

なお、以上の第1〜第7の変形例を含む一実施形態で説明した半導体集積回路は、半導体装置に搭載することができる。さらに、当該半導体装置は、例えば、撮像ユニットとして携帯電話等の通信機器、デジタルカメラ、又はデジタルテレビ等の電子機器などに搭載することができる。

【0052】

また、以上の第1〜第7の変形例を含む一実施形態で説明した半導体集積回路において、ダミーパターン8は適宜分割して、単一の連続体と図2〜図4に示した複数の構造体との組み合わせからなる構造としてもよい。その他、第1〜第7の変形例を含む一実施形態で説明した半導体集積回路の構造は、上述した発明の趣旨を逸脱しない範囲で適宜組み合わせることができる。

【産業上の利用可能性】

【0053】

本発明は、撮像ユニットとして携帯電話等の通信機器、デジタルカメラ、又はデジタルテレビ等の各種電子機器などにとって有用である。

【符号の説明】

【0054】

1 半導体チップ

2 スクライブ領域

3 シールリング

4 パッド

5 配線

6 保護膜

7 保護膜

8、8a、8b、8c ダミーパターン

9 保護膜の終端縁

10 接触角(立ち上がり角度)

【技術分野】

【0001】

本発明は、半導体拡散プロセスにより製造された半導体集積回路及びそれを内包した半導体装置又は電子機器に関する。

【背景技術】

【0002】

近年、情報通信機器又は事務用電子機器の小型化及び高機能化が進展するのに伴って、これらの機器に搭載される半導体集積回路についても、小型化及び高集積化が要求されている。そのため、端子配置がペリフェラル配置からエリアアレイ配置に移行することにより、端子数の増大が図られている。しかし、従来のエリアアレイ配置は、ハイエンド製品に適用されており小型化への要求が強くはなかったが、近年の民生分野へのエリアアレイ配置の採用により、小型化への要求が非常に強くなってきている。

【0003】

このような要求を実現させる目的で、半導体チップ周辺部の縮小による小型化が検討されるようになってきている。

【0004】

図6(a)及び(b)は、従来の半導体集積回路における半導体チップ周辺部を示しており、図6(a)はその断面図であって図6(b)のVIa-VIa線に対応するものであり、図6(b)はその平面図を示している。

【0005】

図6(a)及び(b)に示すように、半導体チップ101上には、半導体チップ101周辺部のスクライブ領域102の近傍にシールリング103が設けられており、該シールリング103よりも内側にパッド104が設けられている。また、半導体チップ101上には、シールリング103とパッド104との間に位置するように、配線105が形成されている。また、スクライブ領域102の一部を覆うと共に、シールリング103の一部からパッド104の一部までを覆うように無機物又は有機物からなる保護膜106が形成されており、保護膜106の一部からパッド104までを覆うように有機物からなる保護膜107が形成されている。保護膜107の終端縁109は、図6(a)及び(b)に示すようにシールリング103とパッド104の間に位置しているが、シールリング103よりも外側に位置したり、パッド104よりも内側に位置することもある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−287906号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述したような従来の構造では、保護膜107の終端縁9をシールリング103よりも外側に配置する場合には、ダイシング時にブレードが保護膜107に接触しないようスクライブ領域102を広く設定する必要がある。一方で、保護膜107の終端縁109をパッド104よりも内側に配置する場合には、パッド104と内部のバンプとの距離を広く設定する必要があり、且つ、パッド104が露出することによる腐食の懸念が発生する。また、保護膜107の終端縁109をシールリング103とパッド104との間に配置する場合には、保護膜107の位置精度を考慮する必要がある。さらに、保護膜107の終端縁109の下部に凹凸が存在すると剥離の懸念があるため、配線105などが保護膜107の終端縁109の下部に位置する可能性がないよう、シールリング103とパッド104との間を広げるなどの考慮が必要である。以上のように、保護膜107の終端縁109の配置制約が存在することにより、半導体チップの小型化が妨げられていた。

【0008】

前記に鑑み、本発明の目的は、保護膜の終端縁がシールリングとパッドとの間に配置される構造を有する半導体集積回路及びそれを備えた半導体装置、電子機器において、半導体チップ周辺部の拡大を抑制できる構造を提供することである。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、本発明の一形態の半導体集積回路は、半導体チップ上に、半導体チップの外周部に形成されたシールリングと、半導体チップ上に、シールリングよりも半導体チップの中央部側に形成されたパッドと、半導体チップ上に、シールリングとパッドとの間に形成された配線と、半導体チップ上に、シールリングと配線との間に形成されていると共に、配線とパッドとの間に形成されているダミーパターンと、シールリングの一部からパッドの一部までの間を覆うように形成された第1の保護膜と、第1の保護膜の一部及びパッドを覆うよう形成された第2の保護膜とを備えている。

【0010】

本発明の一形態の半導体装置において、第2の保護膜の終端縁は、シールリングとパッドとの間に位置していてもよい。

【0011】

本発明の一形態の半導体装置において、前記第2の保護膜の終端縁は、前記配線上に位置していてもよい。

【0012】

本発明の一形態の半導体装置において、ダミーパターンにおける配線を挟んで互いに向かい合う部分の端部が、第2の保護膜の終端縁を中心に半導体チップの周縁部側及び中央部側方向に5μmの間隔以内に位置していてもよい。

【0013】

本発明の一形態の半導体集積回路によると、第2の保護膜の終端縁の位置精度範囲内に、配線と同一層で形成され、配線を挟んで互いに向かい合うダミーパターンの部分の端部が配置されていることにより、第2の保護膜の終端縁の下部に凹凸が形成されても1μm以内の凹凸に設定できる。その結果、第2の保護膜の剥離の懸念を小さくすることができると共に、第2の保護膜の密着性を確保することができる。さらに、ダミーパターンの存在により、従来の半導体集積回路のような配線などが保護膜の終端の下部に位置する可能性がないようシールリングとパッドとの間を広げるという検討が本形態では不要となって、シールリングとパッドとの距離を第2の保護膜の位置精度のみで規定することができ、半導体チップ周辺部の拡大を抑制してその縮小化が可能となる。

【0014】

本発明の一形態の半導体集積回路において、ダミーパターンは、第2の保護膜の終端縁に対して垂直方向に伸びるように形成された複数の直方体からなってもよい。

【0015】

本発明の一形態の半導体集積回路において、ダミーパターンは、複数の四角柱からなってもよい。

【0016】

本発明の一形態の半導体装置において、前記複数の四角柱からダミーパターンは、表面の四角形の最大辺が5μm以下であってもよい。

【0017】

本発明の一形態の半導体集積回路において、ダミーパターンは、複数の六角柱からなってもよい。

【0018】

本発明の一形態の半導体装置において、前記複数の六角柱からなるダミーパターンは、表面の六角形の最大対角線が5μm以下であってもよい。

【0019】

本発明の一形態の半導体集積回路において、ダミーパターン同士の間、ダミーパターンとシールリングとの間、ダミーパターンと配線との間、ダミーパターンとパッドとの間に存在するギャップの幅が5μm以下であってもよい。

【0020】

本発明の一形態の半導体集積回路において、第1の保護膜の表面の平坦度が1μm以下であってもよい。

【0021】

本発明の一形態の半導体集積回路において、第1の保護膜に対する第2の保護膜の終端縁の接触角は、90°未満であってもよい。

【0022】

本発明の一形態の半導体集積回路において、第2の保護膜の終端縁の面内での角部は鈍角であってもよい。

【0023】

本発明の一形態の半導体装置は、上記半導体集積回路を備えた半導体装置である。

【0024】

本発明の一形態の電子機器は、上記半導体装置を備えた電子機器である。

【発明の効果】

【0025】

本発明の一側面の半導体集積回路によると、半導体集積回路及びそれを備えた電子機器において、半導体チップ周辺部の拡大を抑制できる構造を実現できる。その結果、半導体集積回路及びそれを備えた電子機器の小型化を実現できる。

【図面の簡単な説明】

【0026】

【図1】図1(a)及び(b)は、本実施形態の半導体集積回路における半導体チップ周辺部を示しており、図1(a)はその断面図であって図1(b)のIa-Ia線に対応するものであり、図1(b)はその平面図を示している。

【図2】図2(a)及び(b)は、本実施形態の半導体集積回路の第1の変形例における半導体チップ周辺部を示しており、図2(a)はその断面図であって図2(b)のIIa-IIa線に対応するものであり、図2(b)はその平面図を示している。

【図3】図3(a)及び(b)は、本実施形態の半導体集積回路の第2の変形例における半導体チップ周辺部を示しており、図3(a)はその断面図であって図3(b)のIIIa-IIIa線に対応するものであり、図3(b)はその平面図を示している。

【図4】図4(a)及び(b)は、本実施形態の半導体集積回路の第3の変形例における半導体チップ周辺部を示しており、図4(a)はその断面図であって図4(b)のIVa-IVa線に対応するものであり、図4(b)はその平面図を示している。

【図5】図5(a)及び(b)は、本実施形態の半導体集積回路の第7の変形例における半導体チップ周辺部を示しており、図5(a)はその断面図であって図5(b)のVa-Va線に対応するものであり、図5(b)はその平面図を示している。

【図6】図6(a)及び(b)は、従来の半導体集積回路における半導体チップ周辺部を示しており、図6(a)はその断面図であって図6(b)のVIa-VIa線に対応するものであり、図6(b)はその平面図を示している。

【発明を実施するための形態】

【0027】

以下、本発明の一実施形態に係る半導体集積回路及びそれを備えた電子機器について、図面を参照しながら説明する。

【0028】

図1(a)及び(b)は、本実施形態の半導体集積回路における半導体チップ周辺部を示しており、図1(a)はその断面図であって図1(b)のIa-Ia線に対応するものであり、図1(b)はその平面図を示している。

【0029】

図1(a)及び(b)に示すように、例えばシリコンからなる半導体チップ(半導体基板)1上には、半導体チップの回路形成面の周辺部におけるスクライブ領域2の近傍に例えばアルミニウム(Al)からなるリング状のシールリング3が設けられており、該シールリング3よりも半導体チップ1の中央側(内側)に例えばアルミニウム(Al)からなるパッド4が設けられている。また、半導体チップ1上には、シールリング3とパッド4との間に位置するように、例えばアルミニウム(Al)からなる配線5が形成されている。また、配線5とシールリング3との間、及び、配線5とパッド4との間の各々には、例えば配線5と同一層からなる単一の構造体からなるダミーパターン8が設けられている。また、スクライブ領域2の一部を覆うと共に、シールリング103の一部からダミーパターン8及び配線5を含んでパッド4の一部までを覆うように、無機物又は有機物からなり、例えばここではシリコンナイトライド(SiN)からなる保護膜6が形成されている。なお、保護膜6は、スクライブ領域2上の一部又は全部を覆うように形成されていてもよい。

【0030】

また、保護膜6の一部からパッド4までを覆うように、有機物からなり、例えばここではポリイミド又はPBOからなる保護膜7が形成されている。保護膜7の終端縁(底面における半導体チップ外側方向の縁部)9は、図1(a)及び(b)に示すようにシールリング3とパッド4との間のいずれかの位置に配置されており、ここでは配線5及びダミーパターン8上に配置されている。このように、保護膜7の終端縁9は、シールリング3よりも半導体チップ1の周縁部側に(外側に)位置しないため、ダイシング時にブレードが保護膜7に接触しないようスクライブ領域2を広く設定する必要がない。また、パッド4よりも半導体チップ1の中央側に(内側に)位置しないため、パッド4と内部のバンプ(図示せず)の距離を広く設定する必要がなく、且つ、パッド4が露出することによる腐食の懸念がなくなる。

【0031】

また、ダミーパターン8と保護膜7の終端縁9との配置関係については、保護膜7の形成位置の精度を考慮して、ダミーパターン8は、配線5を挟んで互いに向かい合う部分の端部が、該保護膜7の終端縁9を中心に半導体チップ1の周縁部側(外側)及び中央部側(内側)方向に5μmの間隔以内に位置するように配置されている。なお、ここで、外側及び内側とは、上記の通り、半導体チップにおける中央部側方向が内側であり、半導体チップにおける周縁部側方向が外側である。

【0032】

上記本実施形態に係る半導体集積回路によると、保護膜7の終端縁9の位置精度範囲内に、配線5と同一層で形成され、配線5を挟んで互いに向かい合うダミーパターン8の部分の端部が配置されていることにより、保護膜7の終端縁9の下部に凹凸が形成されても1μm以内の凹凸に設定できる。その結果、保護膜7の剥離の懸念を小さくすることができると共に、保護膜7の密着性を確保することができる。さらに、ダミーパターン8の存在により、従来の半導体集積回路のような配線などが保護膜の終端の下部に位置する可能性がないようシールリング3とパッド4との間を広げるという検討が本実施形態では不要となって、シールリング3とパッド4との距離を保護膜7の位置精度のみで規定することができ、半導体チップ周辺部の拡大を抑制してその縮小化が可能となる。

【0033】

−第1の変形例−

図2(a)及び(b)は、本実施形態の半導体集積回路の第1の変形例における半導体チップ周辺部を示しており、図2(a)はその断面図であって図2(b)のIIa-IIa線に対応するものであり、図2(b)はその平面図を示している。

【0034】

図2(a)及び(b)に示す第1の変形例における半導体チップ周辺部の構造では、ダミーパターン8aが、保護膜7の終端縁9(終端縁9が伸びる方向)に対して垂直方向に伸びるように形成された複数の直方体からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0035】

本実施形態の第1の変形例によると、複数の四角柱からなるダミーパターン8bを設けることにより、図1(a)及び(b)に示したダミーパターン8のような単一の構造体からなるベタパターンを配置する必要がないと共に、保護膜7のズレによる終端縁9の位置の高さバラツキを抑制することができため、保護膜7の終端縁9の密着性をより確保することができる。

【0036】

−第2の変形例−

図3(a)及び(b)は、本実施形態の半導体集積回路の第2の変形例における半導体チップ周辺部を示しており、図3(a)はその断面図であって図3(b)のIIIa-IIIa線に対応するものであり、図3(b)はその平面図を示している。

【0037】

図3(a)及び(b)に示す第2の変形例における半導体チップ周辺部の構造では、ダミーパターン8bが、表面の四角形の最大辺が5μm以下となる複数の四角柱からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0038】

本実施形態の第2の変形例によると、複数の四角柱からなるダミーパターン8bを設けることにより、上記第1及び第2の変形例と比較して、ダミーパターンの配置の自由度を向上させることができる。

【0039】

−第3の変形例−

図4(a)及び(b)は、本実施形態の半導体集積回路の第3の変形例における半導体チップ周辺部を示しており、図4(a)はその断面図であって図4(b)のIVa-IVa線に対応するものであり、図4(b)はその平面図を示している。

【0040】

図4(a)及び(b)に示す第3の変形例における半導体チップ周辺部の構造では、ダミーパターン8cが、六角形の対角に位置する頂点同士間(対角線)の距離が最大5μm以下となる複数の六角柱からなる構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0041】

本実施形態の第3の変形例によると、複数の六角柱からなるダミーパターン8cを設けることにより、上記第2及び第3の変形例と比較して、ダミーパターンをより細密に配置することができるため、保護膜7の平面性及び密着性を向上させることができる。

【0042】

−第4の変形例−

本実施形態の半導体集積回路の第4の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、単一又は複数の構造体からなるダミーパターン(8、8a、8b)とシールリング3、パッド4及び配線5との間に存在するギャップの幅、並びに、複数の構造体からなるダミーパターン(8a、8b、8c)における各構造体間に存在するギャップの幅が5μm以下となる構造を有している。

【0043】

本実施形態の第4の変形例によると、上記各ギャップの幅が5μm以下であることにより、それらの上に形成され得る保護膜7の表面の高低差を小さくし、表面の平坦性をより確保することができる。

【0044】

−第5の変形例−

本実施形態の半導体集積回路の第5の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、保護膜6の表面を研磨することでその平坦度を1μm以下とした構造を有している。

【0045】

本実施形態の第5の変形例によると、保護膜6の表面の平坦度が向上することにより、その上に形成される保護膜7の表面の平坦度をより向上させることができる。

【0046】

−第6の変形例−

本実施形態の半導体集積回路の第6の変形例における半導体チップ周辺部の構造では、上記図1〜図4に示した構造において、保護膜6に対する保護膜7の終端縁の接触角(立ち上がり角度)(図1〜図4の符号10参照)が90°未満である構造を有している。

【0047】

本実施形態の第6の変形例によると、曲げなどの外力が加わる際に保護膜6と保護膜7とを引き剥がす方向の応力が発生した場合においても、保護膜6と保護膜7との隙間の亀裂又は剥離が発生しにくい構造となるため、保護膜7の終端縁9の密着性をより確保することができる。

【0048】

−第7の変形例−

図5(a)及び(b)は、本実施形態の半導体集積回路の第7の変形例における半導体チップ周辺部を示しており、図5(a)はその断面図であって図5(b)のVa-Va線に対応するものであり、図5(b)はその平面図を示している。

【0049】

図5(a)及び(b)に示す第7の変形例における半導体チップ周辺部の構造では、保護膜7の終端縁9の面内での角部がいずれも鈍角αとなっている構造を有している。なお、その他の構造等は、上記図1(a)及び(b)に示した半導体集積回路の構造及び対応する説明と同様である。

【0050】

本実施形態の第7の変形例によると、保護膜7の局所的に小さな密着面積となる配置を防ぐことができるため、保護膜7の終端縁9の密着性をより確保することができる。

【0051】

なお、以上の第1〜第7の変形例を含む一実施形態で説明した半導体集積回路は、半導体装置に搭載することができる。さらに、当該半導体装置は、例えば、撮像ユニットとして携帯電話等の通信機器、デジタルカメラ、又はデジタルテレビ等の電子機器などに搭載することができる。

【0052】

また、以上の第1〜第7の変形例を含む一実施形態で説明した半導体集積回路において、ダミーパターン8は適宜分割して、単一の連続体と図2〜図4に示した複数の構造体との組み合わせからなる構造としてもよい。その他、第1〜第7の変形例を含む一実施形態で説明した半導体集積回路の構造は、上述した発明の趣旨を逸脱しない範囲で適宜組み合わせることができる。

【産業上の利用可能性】

【0053】

本発明は、撮像ユニットとして携帯電話等の通信機器、デジタルカメラ、又はデジタルテレビ等の各種電子機器などにとって有用である。

【符号の説明】

【0054】

1 半導体チップ

2 スクライブ領域

3 シールリング

4 パッド

5 配線

6 保護膜

7 保護膜

8、8a、8b、8c ダミーパターン

9 保護膜の終端縁

10 接触角(立ち上がり角度)

【特許請求の範囲】

【請求項1】

半導体チップ上に、前記半導体チップの外周部に形成されたシールリングと、

前記半導体チップ上に、前記シールリングよりも前記半導体チップの中央部側に形成されたパッドと、

前記半導体チップ上に、前記シールリングと前記パッドとの間に形成された配線と、

前記半導体チップ上に、前記シールリングと前記配線との間に形成されていると共に、前記配線と前記パッドとの間に形成されているダミーパターンと、

前記シールリングの一部から前記パッドの一部までの間を覆うように形成された第1の保護膜と、

前記第1の保護膜の一部及び前記パッドを覆うよう形成された第2の保護膜とを備えていることを特徴とする半導体集積回路。

【請求項2】

前記第2の保護膜の終端縁は、前記シールリングと前記パッドとの間に位置していることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記第2の保護膜の終端縁は、前記配線上に位置していることを特徴とする請求項2に記載の半導体集積回路。

【請求項4】

前記ダミーパターンにおける前記配線を挟んで互いに向かい合う部分の端部が、前記第2の保護膜の終端縁を中心に前記半導体チップの周縁部側及び中央部側方向に5μmの間隔以内に位置していることを特徴とする請求項3に記載の半導体集積回路。

【請求項5】

前記ダミーパターンは、前記第2の保護膜の終端縁に対して垂直方向に伸びるように形成された複数の直方体からなることを特徴とする請求項1に記載の半導体集積回路。

【請求項6】

前記ダミーパターンは、複数の四角柱からなることを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記複数の四角柱からなるダミーパターンは、表面の四角形の最大辺が5μm以下であることを特徴とする請求項6に記載の半導体集積回路。

【請求項8】

前記ダミーパターンは、複数の六角柱からなることを特徴とする請求項1に記載の半導体装置。

【請求項9】

前記複数の六角柱からなるダミーパターンは、表面の六角形の最大対角線が5μm以下であることを特徴とする請求項8に記載の半導体集積回路。

【請求項10】

前記ダミーパターン同士の間、前記ダミーパターンと前記シールリングとの間、前記ダミーパターンと前記配線との間、前記ダミーパターンと前記パッドとの間に存在するギャップの幅が5μm以下である、請求項1〜9のうちのいずれか1項に記載の半導体集積回路。

【請求項11】

前記第1の保護膜の表面の平坦度が1μm以下である、請求項1〜10のうちのいずれか1項に記載の半導体集積回路。

【請求項12】

前記第1の保護膜に対する前記第2の保護膜の終端縁の接触角は、90°未満である、請求項1〜10のうちのいずれか1項に記載の半導体集積回路。

【請求項13】

前記第2の保護膜の終端縁の面内での角部は鈍角である、請求項1〜12のうちのいずれか1項に記載の半導体集積回路。

【請求項14】

請求項1〜13のうちのいずれか1項に記載の半導体集積回路を備えた半導体装置。

【請求項15】

請求項14に記載の半導体装置を備えた電子機器。

【請求項1】

半導体チップ上に、前記半導体チップの外周部に形成されたシールリングと、

前記半導体チップ上に、前記シールリングよりも前記半導体チップの中央部側に形成されたパッドと、

前記半導体チップ上に、前記シールリングと前記パッドとの間に形成された配線と、

前記半導体チップ上に、前記シールリングと前記配線との間に形成されていると共に、前記配線と前記パッドとの間に形成されているダミーパターンと、

前記シールリングの一部から前記パッドの一部までの間を覆うように形成された第1の保護膜と、

前記第1の保護膜の一部及び前記パッドを覆うよう形成された第2の保護膜とを備えていることを特徴とする半導体集積回路。

【請求項2】

前記第2の保護膜の終端縁は、前記シールリングと前記パッドとの間に位置していることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記第2の保護膜の終端縁は、前記配線上に位置していることを特徴とする請求項2に記載の半導体集積回路。

【請求項4】

前記ダミーパターンにおける前記配線を挟んで互いに向かい合う部分の端部が、前記第2の保護膜の終端縁を中心に前記半導体チップの周縁部側及び中央部側方向に5μmの間隔以内に位置していることを特徴とする請求項3に記載の半導体集積回路。

【請求項5】

前記ダミーパターンは、前記第2の保護膜の終端縁に対して垂直方向に伸びるように形成された複数の直方体からなることを特徴とする請求項1に記載の半導体集積回路。

【請求項6】

前記ダミーパターンは、複数の四角柱からなることを特徴とする請求項1に記載の半導体装置。

【請求項7】

前記複数の四角柱からなるダミーパターンは、表面の四角形の最大辺が5μm以下であることを特徴とする請求項6に記載の半導体集積回路。

【請求項8】

前記ダミーパターンは、複数の六角柱からなることを特徴とする請求項1に記載の半導体装置。

【請求項9】

前記複数の六角柱からなるダミーパターンは、表面の六角形の最大対角線が5μm以下であることを特徴とする請求項8に記載の半導体集積回路。

【請求項10】

前記ダミーパターン同士の間、前記ダミーパターンと前記シールリングとの間、前記ダミーパターンと前記配線との間、前記ダミーパターンと前記パッドとの間に存在するギャップの幅が5μm以下である、請求項1〜9のうちのいずれか1項に記載の半導体集積回路。

【請求項11】

前記第1の保護膜の表面の平坦度が1μm以下である、請求項1〜10のうちのいずれか1項に記載の半導体集積回路。

【請求項12】

前記第1の保護膜に対する前記第2の保護膜の終端縁の接触角は、90°未満である、請求項1〜10のうちのいずれか1項に記載の半導体集積回路。

【請求項13】

前記第2の保護膜の終端縁の面内での角部は鈍角である、請求項1〜12のうちのいずれか1項に記載の半導体集積回路。

【請求項14】

請求項1〜13のうちのいずれか1項に記載の半導体集積回路を備えた半導体装置。

【請求項15】

請求項14に記載の半導体装置を備えた電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−33775(P2013−33775A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2009−275268(P2009−275268)

【出願日】平成21年12月3日(2009.12.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成21年12月3日(2009.12.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]