半導体集積回路及びそれを用いたDC−DCコンバータ

【課題】2次側に同期整流回路を用いる場合、出力電圧検出信号を1次側にフィードバックさせる手段を含め、1次−2次間を絶縁した状態で信号を伝達させる手段が少なくとも2つ必要になり、回路構成が複雑になるという問題がある。

【解決手段】外部信号との送受信が可能で、絶縁型であれば1次側と2次側に同じハードウェア構成のICを2つ使用することができ、かつ非絶縁型にも適用可能な、電源装置に利用できる半導体集積回路を用いる。

【解決手段】外部信号との送受信が可能で、絶縁型であれば1次側と2次側に同じハードウェア構成のICを2つ使用することができ、かつ非絶縁型にも適用可能な、電源装置に利用できる半導体集積回路を用いる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フルブリッジ構成のスイッチング回路を備え、外部信号との送受信が可能で、絶縁型/非絶縁型に関わらず電源装置に利用できる半導体集積回路と、それを用いたDC−DCコンバータに関するものである。

【背景技術】

【0002】

絶縁型DC−DCコンバータでは、1次回路と2次回路とで異なるグランド電位に対応したり、安全規格を満たすために、トランスで1次−2次間を絶縁する。2次側の出力電圧や出力電流を制御する場合、それらを検出して1次側にフィードバックし、1次側のスイッチング回路を制御することになるが、このフィードバック回路にも1次−2次間の絶縁が求められる。

【0003】

また、2次側に同期整流回路を採用する場合、メインスイッチと転流側同期整流器が共にオン状態となって貫通電流が流れるのを防ぐために、メインスイッチのターンオン直前に、2次側同期整流回路の転流側同期整流器をターンオフさせる動作が必要となり、メインスイッチのターンオン直前のタイミングを示す信号を1次側から2次側に伝送し、2次側同期整流器のスイッチングタイミングを制御する必要がある。(特許文献1参照)

ここで特許文献1に示されている絶縁型DC−DCコンバータの基本的な構成を図1に示す。

【0004】

図1において、メインスイッチ2は、1次側制御回路5から出力される制御信号に応じてスイッチング制御される。1次側制御回路5は、出力電圧Voを絶縁回路10を介して検出し、これに基づいてメインスイッチ2のデューティ比を制御する信号C1を出力する。さらに制御信号C1は、駆動回路7、8及びトランス9を介して2次側にも伝達されて制御信号C2となり、かかる制御信号C2は2次側制御回路21に供給される。2次側制御回路21に供給された制御信号C2は、駆動回路13の入力端及びトランジスタ15のゲート電極に印加され、これによって整流側同期整流器3はメインスイッチ2と同相に駆動され、転流側同期整流器4はメインスイッチ2と逆相に駆動される。

【0005】

ここで、駆動回路7、8及びトランス9が介在することによって生じる制御信号C1と制御信号C2との間のタイミングのズレ、及び転流側同期整流器を構成するMOSFETのターンオフ遅延時間は、メインスイッチのターンオンタイミングを遅延させる遅延回路11によって調整されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−272097号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1に示されているように、2次側に同期整流回路を用いる場合、出力電圧検出信号を1次側にフィードバックさせる手段を含め、1次−2次間を絶縁した状態で信号を伝達させる手段が少なくとも2つ必要になり、回路構成が複雑になるという問題がある。

【0008】

また、別の問題としては、近年、制御回路にはICが用いられるが、1次側制御回路と2次側制御回路で固有の設計とした場合、2種類の特定用途向けIC(ASIC)を製造せねばならず、生産性・経済性が悪いという問題があった。

【0009】

そこで、この発明の目的は、フルブリッジ構成のスイッチング回路を備え、外部信号との送受信が可能で、絶縁型であれば1次側と2次側に同じハードウェア構成のICを2つ使用することができ、かつ非絶縁型にも適用可能な、電源装置に利用できる半導体集積回路と、それを用いたDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0010】

本発明の絶縁型DC−DCコンバータは、所定の直流電圧が印加される第1の直流電圧部と、第2の直流電圧部と、基準電位に接続されるGND端子と、第1のスイッチ回路S1と第2のスイッチ回路S2とからなる第1の直列回路と、第3のスイッチ回路S3と第4のスイッチ回路S4とからなる第2の直列回路と、該第1〜第4のスイッチ回路のオン/オフ動作を制御する制御部と、前記第1のスイッチ回路S1と前記第2のスイッチ回路S2との接続点を外部に引き出すための第1の出力端子と、前記第3のスイッチ回路S3と前記第4のスイッチ回路S4の接続点を外部に引き出すための第2の出力端子と、を含む半導体集積回路であって、前記第1の直列回路の一端は前記第1の直流電圧部Vdr1に接続され、前記第2の直列回路の一端は前記第2の直流電圧部Vdr2に接続され、前記第1の直列回路の他端と、前記第2の直列回路の他端が共に前記GND端子に対して接続され、前記第1の出力端子と前記第2の出力端子との間にリアクタンス素子が接続され、前記リアクタンス素子の両端電圧の変化を検出する巻線電圧検出手段(Vdet)と、少なくとも前記第1のスイッチ回路S1がオン状態、かつ前記第2のスイッチ回路S2及び前記第3のスイッチ回路S3が共にオフ状態である時に、前記リアクタンス素子に正極性の電圧を印加し、もしくは前記第2のスイッチ回路(S2)がオン状態、かつ前記第1のスイッチ回路(S1)及び前記第4のスイッチ回路(S4)が共にオフ状態である時に、前記リアクタンス素子に負極性の電圧を印加することで、前記リアクタンス素子に励磁電流を流してパルス電圧を発生させ、該パルス電圧をエッジ信号として外部に送信すると共に、少なくとも前記第1のスイッチ回路S1及び前記第2のスイッチ回路S2が共にオフ状態である時に、前記リアクタンス素子に生じるパルス電圧を、前記巻線電圧検出端子によって検出することにより、外部からのエッジ信号を受信できるようにしたことを特徴とする。

【0011】

さらには、前記半導体集積回路はさらに、前記第1の直流電圧部から入力される電圧を出力する第3の出力端子と、該第3の出力端子に、電圧を出力するか否かを制御するサブドライバ回路と、を備え、前記サブドライバ回路のターンオン及びターンオフ動作は前記制御部によって制御され、前記制御部は、前記第2の出力端子に生じる方形波電圧と、前記第3の出力端子に生じる方形波電圧が、共に低レベルである期間を挟んで互いに相補的な関係になるように前記第1〜第4のスイッチ回路及び前記サブドライバ回路を制御することを特徴とする。

【0012】

さらには、前記半導体集積回路が1次側制御回路及び2次側制御回路にそれぞれ用いられた絶縁型スイッチング電源装置であって、直流電源と、少なくとも1組の1次巻線及び2次巻線を有するトランスと、前記直流電源から供給される直流電圧を前記1次巻線に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、前記2次巻線に接続される少なくとも1つの同期整流回路を含む整流回路と、該整流回路の出力を平滑する出力フィルタ回路と、を少なくとも備え、少なくとも1次巻線と2次巻線を有し、1次側に配置された前記半導体集積回路に該1次巻線を、2次側に配置された前記半導体集積回路に該2次巻線が接続された信号伝送トランスをリアクタンス素子として用いて、前記1次側に配置された半導体集積回路と、前記2次側に配置された半導体集積回路との間で、パルス信号を双方向に伝送し、前記電力スイッチ素子及び前記同期整流器の駆動タイミングを制御することを特徴とする。

【0013】

さらには、請求項1、もしくは請求項2に記載の半導体集積回路を制御回路に用い、直流電源と、少なくとも1つのインダクタンス素子と、前記直流電源から供給される直流電圧を該インダクタンス素子に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、少なくとも1つの同期整流器を含む整流回路と、整流回路の出力を平滑する出力フィルタ回路と、を備える非絶縁型スイッチング電源装置であって、前記電力スイッチ素子、もしくは前記同期整流器は電界効果トランジスタで構成されており、該電界効果トランジスタのソース端子が該制御回路のグランド電位からフローティングされていて、該電界効果トランジスタのゲート−ソース間にエッジ信号から方形波信号への変換回路が接続され、前記半導体集積回路からトランスを介して送信されるエッジ信号を前記変換回路にて変換された方形波信号で、該電界効果トランジスタが駆動されることを特徴とする。

【発明の効果】

【0014】

本発明は、

(a)パワー半導体素子の駆動を制御するとともに、双方向信号伝送機能を有するプログラマブルな半導体素子を提供できる。

(b)絶縁型/非絶縁型を問わず、様々なトポロジーの電源装置の制御回路として応用出来る。

(c)絶縁型DC−DCコンバータに利用した場合は、1次側と2次側に同じハードウェアの半導体素子を使用でき、制御ICの開発コストの低減、製造コストの削減に貢献できる。

【図面の簡単な説明】

【0015】

【図1】特許文献1に示されている絶縁型DC−DCコンバータの基本的な構成を示す図である。

【図2】第1の実施形態に係る制御IC101の内部ブロック図である。

【図3】第1の実施形態に係る制御ICを用いた絶縁型DC−DCコンバータの回路例である。

【図4】スイッチング周期あたりの各部の波形図である。

【図5】時間t0〜t1区間における制御IC内部の動作説明図である。

【図6】時間t1における制御IC内部の動作説明図である。

【図7】時間t1〜t2区間における制御IC内部の動作説明図である。

【図8】時間t2における制御IC内部の動作説明図である。

【図9】時間t2〜t3区間における制御IC内部の動作説明図である。

【図10】時間t3〜t4区間における制御IC内部の動作説明図である。

【図11】時間t4〜t5区間における制御IC内部の動作説明図である。

【図12】時間t5における制御IC内部の動作説明図である。

【図13】時間t5〜t6区間における制御IC内部の動作説明図である。

【図14】時間t6における制御IC内部の動作説明図である。

【図15】時間t6〜t7区間における制御IC内部の動作説明図である。

【図16】時間t7〜t8区間における制御IC内部の動作説明図である。

【図17】第2の実施形態に係る制御IC101の内部ブロック図である。

【図18】第1の実施形態に係る制御ICを用いた非絶縁型降圧DC−DCコンバータの回路例である。

【図19】第1の実施形態に係る制御ICを用いた非絶縁型昇圧DC−DCコンバータの回路例である。

【図20】第1の実施形態に係る制御ICを用いた非絶縁型SEPICコンバータの回路例である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

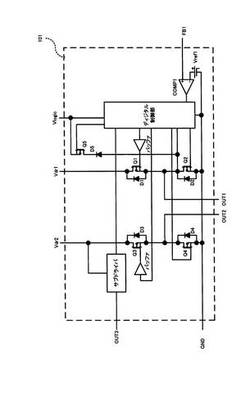

図2は第1の実施形態に係る絶縁型DC−DCコンバータの制御に用いられる半導体集積回路(以下、制御ICと呼ぶ)101の内部ブロック図である。制御IC101は、少なくとも第1のスイッチング素子Q1と第1のダイオードD1の並列回路からなる第1のスイッチ回路S1、及び少なくとも第2のスイッチング素子Q2と第2のダイオードの並列回路からなる第2のスイッチ回路S2、とからなる直列回路と、少なくとも第3のスイッチング素子Q3と第3のダイオードD3の並列回路からなる第3のスイッチ回路S3、及び少なくとも第4のスイッチング素子Q4と第4のダイオードD4の並列回路からなる第4のスイッチ回路S4とからなる直列回路と、を備え、各スイッチ回路S1〜S4のターンオン及びターンオフを制御する制御信号を出力するディジタル制御部を備える。

【0017】

第1のスイッチ回路S1と第2のスイッチ回路S2の接続点と、第3のスイッチ回路S3と第4のスイッチ回路S4の接続点には、両者間にインダクタンス素子を接続するための第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2が設けられている。また、第1のスイッチ回路S1及び第2のスイッチ回路S2とからなる直列回路と、第3のスイッチ回路S3及び第4のスイッチ回路S4とからなる直列回路は、それぞれの一端が共通接続されて接地端子GNDに接続され他端はそれぞれ第1の直流電圧部Vdr1及び第2の直流電圧部Vdr2に接続されている。すなわち、各スイッチ回路S1〜S4はフルブリッジ型を形成することとなるので、ハイサイド側スイッチとなる第1のスイッチ回路S1及び第3のスイッチ回路S3は、ハイサイドドライバとしてのバッファを介してディジタル制御部からの制御信号が伝達される。

【0018】

さらに、第3のスイッチ回路S3と第4のスイッチ回路S4の接続点には、該接続点の電位を検出するためのパルス電圧信号検出端子Vdetが設けられ、ディジタル制御部に入力されるように構成されている。

【0019】

さらに、例えば第2の直流電圧部Vdr2から電力を得て、ディジタル制御部から出力される信号により第2のドライブ信号を出力するためのサブドライバと、該第2のドライブ信号が出力される第3の信号出力端子OUT3を備えている。

【0020】

さらに、第1の比較器COMP1、該第1の比較器COMP1に入力される第1の基準電圧源Vref1を備え、該第1の比較器の出力信号がディジタル制御部に入力される構成になっている。

【0021】

さらに、第1のスイッチ回路S1と第2のスイッチ回路S2の接続点と、該ディジタル制御部の駆動電源端子Vlogicとの間が、第9のダイオードD9と第9のスイッチ回路S9を介して接続されており、第9のスイッチ回路S9は該ディジタル制御部によって制御される。

【0022】

図3に図2で示した制御ICを用いた絶縁型DC−DCコンバータの第1の実施形態に係る回路図を示す。

【0023】

直流入力電源Vinの両端に対して、トランスTの1次巻線Np1と、第11のスイッチング素子Q11と第1の抵抗R1とからなる直列回路が接続されており、該第11のスイッチング素子Q11に対して、第1のキャパシタC1とPチャネルMOSFETで形成された第12のスイッチング素子Q12とからなる直列回路が並列に接続されている。

【0024】

トランスTの2次巻線Ns1の両端に対しては、整流用同期整流器として機能する第13のスイッチング素子Q13及び転流用同期整流器として機能する第14のスイッチング素子Q14とからなる同期整流回路が接続され、第1のインダクタL1及び第4のキャパシタC4とからなる平滑回路を介して直流電圧が出力端子Voutに出力される。

【0025】

1次側制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第11のスイッチング素子Q11を制御するために、第11のスイッチング素子Q11の制御端子と第2の信号出力端子OUT2とが接続され、第12のスイッチング素子Q12を制御するために、第12のスイッチング素子Q12の制御端子と第3の信号出力端子OUT3とが第3のキャパシタC3及び第13のダイオードD13とからなるレベルシフト回路を介して接続され、第1の抵抗R1を電流検出抵抗として第11のスイッチング素子Q11に流れる電流を検出するために、第11のスイッチング素子Q11と第1の抵抗R1との接続点が帰還信号入力端子FB1に接続され、第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2には、パルストランスPTの1次巻線Np2の両端が接続されている。また、接地端子GNDがGNDラインに接続されている。

【0026】

2次側制御IC102は、トランスTの2次巻線Ns1に生じる電圧を整流平滑した出力電圧から駆動電源端子Vdd、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第13のスイッチング素子Q13を制御するために、第13のスイッチング素子Q13の制御端子と第2の信号出力端子OUT2とが接続され、第14のスイッチング素子Q14を制御するために、第14のスイッチング素子Q14の制御端子と第3の信号出力端子OUT3とが接続され、出力電圧を第4の抵抗R4と第5の抵抗R5とで分圧したものと、第2の抵抗R2、第3の抵抗R3、第4のキャパシタC4、及び第5のキャパシタC5とからなるランプ波形成回路103からのランプ波信号とを合成したものが帰還信号入力端子FB1に入力されるように接続され、第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2には、パルストランスPTの2次巻線Ns2の両端が接続されている。なお、第6のキャパシタC6は平滑コンデンサとして機能する。

【0027】

少なくとも第1のスイッチ回路S1〜第8のスイッチ回路S8の各スイッチ回路は、MOSFETで構成することによって、第1のダイオードD1〜第8のダイオードD8をMOSFETのボディダイオードで代替させることができる。特にパワー半導体素子である第11のスイッチング素子Q11〜第14のスイッチング素子Q14に関しては、MOSFETに限らず、BJT(バイポーラジャンクショントランジスタ)やIGBT(絶縁ゲートバイポーラトランジスタ)等も適用できる。なお、図3においては、第12のスイッチング素子Q12にのみPチャネル型FETが用いられ、他のスイッチング素子にはNチャネル型FETが用いられているが、必要に応じて適宜使い分ければよい。

【0028】

なお、詳細は後述するが、1次側制御IC101及び2次側制御IC102には同一のハードウェアのICを利用することができる。

【0029】

図4に、第11のスイッチング素子Q11の1スイッチング周期における、第11のスイッチング素子Q11のドレイン−ソース間電圧、第1のスイッチング素子Q1〜第4のスイッチング素子Q4のゲート−ソース間電圧、及びパルストランスPTの1次巻線Np2の両端電圧の各波形図を示す。

【0030】

第11のスイッチング素子Q11の1スイッチング周期をt0〜t8の計10区間に分けて各部の動作を説明する。

[時間t0〜t1区間における動作]

図5に、この区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。1次側制御IC101及び2次側制御IC102のディジタル制御部の駆動電源端子Vlogicには、図2に示すように、第9のスイッチ回路S9と第9のダイオードD9を介して、第1のスイッチ回路S1と第2のスイッチ回路S2との接続点に接続されているので、このようになる。

【0031】

この時、第1のスイッチ回路S1、第2のスイッチ回路S2、及び第3のスイッチ回路S3はオフ、第4のスイッチ回路S4はオン状態となっている。これにより、1次側制御IC101における第2の信号出力端子OUT2に接続されている第11のスイッチング素子Q11のゲート−ソース間は第4のスイッチ回路S4がオンしていることによりショート状態となり、第11のスイッチング素子Q11の入力容量Cissには電荷が蓄積されていない。すなわち第11のスイッチング素子Q11はオフ状態である。

【0032】

この時、Pチャネル型FETである第12のスイッチング素子Q12のソース−ゲート間電圧は負電位になっているので、オン状態である。

【0033】

2次側制御IC102内においても同様で、第5のスイッチ回路S5、第6のスイッチ回路S6及び第7のスイッチ回路S7はオフ、第8のスイッチ回路S8はオン状態となっている。これにより、2次側制御IC102における第2の信号出力端子OUT2に接続されている第13のスイッチング素子Q13のゲート−ソース間は第8のスイッチ回路S8がオンしていることによりショート状態となり、第13のスイッチング素子Q13の入力容量Cissには電荷が蓄積されていない。すなわち整流側同期整流器として機能する第13のスイッチング素子Q13はオフ状態である。

【0034】

なお、転流側同期整流器として機能する第14のスイッチング素子Q14は、第13のスイッチング素子Q13とはデッドタイムを挟んで相補的に動作するため、オン状態である。

[時間t1における動作]

図6に、時間t1における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0035】

時間t1において、1次側制御IC101内の第1のスイッチ回路S1をターンオンさせる。すると、第1の直流電圧部Vdr1から供給される電流が第1のスイッチ回路S1、パルストランスPTの1次巻線Np2、第4のスイッチ回路S4を介して流れる。パルストランスPTの1次巻線Np2が励磁されることによって、パルストランスPTの2次巻線Ns2には電圧が生じるので、2次側制御IC102において、これを第5のスイッチ回路S5と第6のスイッチ回路S6の接続点に位置する巻線電圧検出端子Vdetにて検出する。

[時間t1〜t2区間における動作]

図7に、時間t1〜t2区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0036】

2次側制御IC102内のディジタル制御部は、巻線電圧検出端子Vdetに電圧が入力されたことに応じて、第5のスイッチ回路S5をターンオンさせる。この動作により、2次側制御IC102においても、第2の直流電圧部Vdr2から供給される電流が、第5のスイッチ回路S5、パルストランスPTの2次巻線Ns2、第8のスイッチ回路S8を介して流れる。

[時間t2における動作]

図8に、時間t2における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0037】

時間t2において、1次側制御IC101内のディジタル制御部は、第4のスイッチ回路S4を、また2次側制御IC102内のディジタル制御部は、第8のスイッチ回路S8を、それぞれターンオフさせる。この動作により、1次側制御IC101内においては、第1の直流電圧部Vdr1から供給される電流が、第11のスイッチング素子Q11の入力容量Cissに流れて電荷が充電され、第11のスイッチング素子Q11がターンオンする。同時に2次側制御IC102内においては、第2の直流電圧部Vdr2から供給される電流が、第13のスイッチング素子Q13の入力容量Cissに流れて電荷が充電され、第13のスイッチング素子Q13がターンオンする。

[時間t2〜t3区間における動作]

図9に、時間t2〜t3区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0038】

時間t2〜t3において、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のターンオンが終了すると、1次側制御IC101内において第1の直流電圧部Vdr1から供給される電流は、第1のスイッチ回路S1、パルストランスPTの1次巻線Np2、第3のダイオードD3を介して第1の直流電圧部Vdr1に還流する。また、2次側制御IC102内においても同様に、第2の直流電圧部Vdr2から供給される電流は、第5のスイッチ回路S5、パルストランスPTの2次巻線Ns2、第7のダイオードD7を介して還流する。

[時間t3〜t4区間における動作]

図10に、時間t3〜t4区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0039】

時間t3において、1次側制御IC101においては第1のスイッチ回路S1が、2次側制御IC102においては第5のスイッチ回路S5がそれぞれターンオフする。この動作によって時間t3〜t4の間、パルストランスPTの1次巻線Np2及び2次巻線Ns2にそれぞれ流れる電流は減少しながら、1次側制御IC101においては第2のダイオードD2、パルストランスPTの1次巻線Np2、第3のダイオードD3を介して流れ、2次側制御IC102においては第6のダイオードD6、パルストランスPTの2次巻線Ns2、第7のダイオードD7を介して流れ、パルストランスPT1に蓄積された電磁エネルギーが回生される。

[時間t4〜t5区間における動作]

図11に、時間t4〜t5区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0040】

その後、時間t4において、パルストランスPTの1次巻線Np2及び2次巻線Ns2に流れる電流がゼロに近づき、1次側制御IC101における第2のダイオードD2、及び第3のダイオードD3と、2次側制御IC102における第6のダイオードD6、及び第7のダイオードD7のそれぞれに順方向電流が流れなくなると、1次側制御IC101における第3のスイッチ回路S3及び2次側制御IC102における第7のスイッチ回路S7をそれぞれターンオンさせる。この動作により、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のゲート電位は、第2の直流電圧部Vdr2(=第1の直流電圧部Vdr1)から供給される電圧値に維持されることとなり、常にオン状態が維持されることになる。

[時間t5における動作]

図12に、時間t5における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0041】

時間t5において、2次側制御IC102内の第6のスイッチ回路S6をターンオンさせる。すると、第1の直流電圧部Vdr1から供給される電流が第7のスイッチ回路S7、パルストランスPTの2次巻線Ns2、第6のスイッチ回路S6を介して流れる。パルストランスPTの2次巻線Ns2が励磁されることによって、パルストランスPTの1次巻線Np2には電圧が生じるので、1次側制御IC101において、これを第1のスイッチ回路S1と第2のスイッチ回路S2の接続点に位置する巻線電圧検出端子Vdetにて検出する。

[時間t5〜t6区間における動作]

図13に、時間t5〜t6区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0042】

1次側制御IC101内のディジタル制御部は、巻線電圧検出端子Vdetに電圧が入力されたことに応じて、第2のスイッチ回路S2をターンオンさせる。この動作により、1次側制御IC101においても、第2の直流電圧部Vdr2から供給される電流が、第3のスイッチ回路S3、パルストランスPTの1次巻線Np2、第2のスイッチ回路S2を介して流れる。

【0043】

この期間の途中で、第9のスイッチ回路S9及び第10のスイッチ回路S10もターンオンさせる。t5〜t6区間の時間長さを調整するとパルストランスPTに蓄える電磁エネルギーの量を変更できる。従ってt5〜t6区間の時間長さの制御によって1次側制御IC101内、及び2次側制御IC102内のディジタル制御部に与える駆動電圧を制御できる。

[時間t6における動作]

図14に、時間t6における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

時間t6において、1次側制御IC101内のディジタル制御部は、第3のスイッチ回路S3を、また2次側制御IC102内のディジタル制御部は、第7のスイッチ回路S7を、それぞれターンオフさせる。この動作により、1次側制御IC101内においては、第11のスイッチング素子Q11の入力容量Cissに蓄積されていた電荷が放電され、第11のスイッチング素子Q11がターンオフする。同時に2次側制御IC内においては、第13のスイッチング素子Q13の入力容量Cissに蓄積されていた電荷が放電され、第13のスイッチング素子Q13がターンオフする。

[時間t6〜t7区間における動作]

図15に、時間t6〜t7区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0044】

時間t6〜t7において、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のゲート−ソース間電圧が0Vに到達すると、1次側制御IC101内において、第4のダイオードD4、パルストランスPTの1次巻線Np2、第2のスイッチ回路S2を介してGNDに向かって電流が流れる。また、2次側制御IC102内においても同様に、第8のダイオードD8、パルストランスPTの2次巻線Ns2、第6のスイッチ回路S6を介してGNDに向かって電流が流れる。

[時間t7〜t8区間における動作]

図16に、時間t7〜t8区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

時間t7において、1次側制御IC101においては第4のスイッチ回路S4が、2次側制御IC102においては第8のスイッチ回路S8がそれぞれターンオンすると同時に、第2のスイッチ回路S2と第6のスイッチ回路S6がターンオフする。この動作によって時間t7〜t8の間、パルストランスPTの1次巻線Np2及び2次巻線Ns2にそれぞれ流れる電流は減少しながら、1次側制御IC101においては第4のダイオードD4、パルストランスPTの1次巻線Np2、第9のダイオードD9を介して第7のキャパシタC7を充電するように流れ、2次側制御IC102においては第8のダイオードD8、パルストランスPTの2次巻線Ns2、第10のダイオードD10を介して第8のキャパシタC8を充電するように流れる。

【0045】

上述した動作によって、第11のスイッチング素子Q11、第13のスイッチング素子Q13の駆動エネルギーを、1次側制御IC101、2次側制御IC102のディジタル制御回路を駆動する電力として回生させることができる。なお、この期間の途中で第9のスイッチ回路S9及び第10のスイッチ回路S10をターンオフすれば第7のキャパシタC7及び第8のキャパシタC8を充電するエネルギーを制限する事ができる。その後、第9のスイッチ回路S9及び第10のスイッチ回路S10のターンオフ時点でまだ回生されていないパルストランスPTの電磁エネルギーは第1のダイオードD1及び第5のダイオードD5を介して第1の直流電圧部Vdr1に回生される。この方法でもディジタル制御部の駆動電源端子Vlogicの電圧を目標値に安定化するよう制御できる。

[時間t8以降における動作]

時間t8以降時間t1までの区間における動作は、上記[時間t0〜t1区間における動作]と同一の動作になる。

【0046】

上述した動作により、1次側制御ICから出力される、1次側のメインスイッチに相当する第11のスイッチング素子Q11をターンオンさせる直前のタイミングを示す信号を、パルストランスPTを介して2次側に伝送し、2次側の同期整流回路における整流側同期整流器に相当する第13のスイッチング素子Q13をターンオンさせるためのタイミング信号として利用するとともに、2次側制御ICから出力される、2次側の同期整流回路における転流側同期整流器をターンオフさせる。メインスイッチのターンオン直前のタイミングで転流側同期整流器がターンオフされる事で、メインスイッチと転流側同期整流器の同時オンによる貫通電流の発生が防止される。整流側同期整流器に相当する第13のスイッチング素子Q13をターンオフさせる直前のタイミングを示す信号を、パルストランスPTを介して1次側に伝送し、1次側のメインスイッチに相当する第11のスイッチング素子Q11をターンオフさせるためのタイミング信号として利用できる。また、前述の例とは逆にメインスイッチのターンオン直前のタイミングを示す信号を2次側から1次側に伝送する事もできるし、メインスイッチのターンオフ直前のタイミングを示す信号を1次側から2次側に伝送する事もできる。1次側と2次側の内、先に送出された信号が優先して実行される。すなわち、1つのパルストランスPTを用いた完全な双方向通信が可能となる。さらに、回生するエネルギーを制御IC内のディジタル制御部の駆動電圧源として利用することができる。すなわち、例えば第11のスイッチング素子Q11、第12のスイッチング素子Q12、第13のスイッチング素子Q13、および第14のスイッチング素子Q14のゲート駆動電圧が10V程度であって、1次側制御IC101及び2次側制御IC102のディジタル制御部の駆動電圧が1.8V程度である場合などに、パルストランスPTの励磁インダクタンスをエネルギー蓄積素子として利用することで、リニアレギュレータによる降圧ではなく、スイッチングレギュレータとして任意の電圧を生成することができ、回路効率を高めることができる。また、1次−2次間の信号伝送に用いるパルストランスPTをエネルギー蓄積素子としても兼用しているので、別個にスイッチングレギュレータを構成するより簡略な回路構成となる。

【0047】

なお、時間t0〜t2の区間及び時間t4〜t6の区間における動作は、第11のスイッチング素子Q11と第12のスイッチング素子Q12が共にオフである期間(デッドタイム)、及び第13のスイッチング素子Q13と第14のスイッチング素子Q14が共にオフである期間(デッドタイム)を作るための動作であるが、デッドタイムを作る手段を別に設ければ、第3のスイッチ回路S3と第4のスイッチ回路S4、及び第7のスイッチ回路S7と第8のスイッチ回路S8は常にオフ、すなわち単なるダイオードに置き換えてもよい。

【0048】

第1の実施形態に係る発明は、上述した(a)、(b)、(c)の効果を有する。

《第2の実施形態》

また、図17に、第2の直流電圧部Vdr2を駆動電圧源に接続せず、1次側制御IC101では第9のキャパシタC9、2次側制御IC102では第10のキャパシタC10に接続した場合の、1次側制御IC101及び2次側制御IC102の内部ブロック図を示す。1次側制御IC101を例に取ると、第1のスイッチ回路S1がオン状態である期間中に、第4のスイッチ回路S4のオン時間を可変させるとすると、第1の直流電圧部Vdr1からパルストランスPTの励磁インダクタンス、第4のスイッチ回路S4、第3のスイッチ回路S3、及び第9のキャパシタC9からなる回路は、昇圧チョッパ型コンバータになることが分かる。すなわち、第1の直流電圧部Vdr1から供給される電圧が変動の大きな直流電圧であった場合でも、第4のスイッチ回路S4のオン時間を制御することによって、第2の信号出力端子OUT2に印加される電圧値を一定に制御することができる。なお、これは2次側制御IC102にも適用できることは言うまでもない。

【0049】

第2の実施形態に係る発明は、上述した(a)、(b)、(c)の効果を有する。

《非絶縁型降圧コンバータに適用した場合》

図18に図2で示した制御ICを用いた非絶縁型降圧DC−DCコンバータの実施形態に係る回路図を示す。

【0050】

直流入力電源Vinの両端に対して、電力スイッチ素子として機能する第15のスイッチング素子Q15と、同期整流器として機能する第16のスイッチング素子Q16とからなる直列回路が接続されており、前記第15のスイッチング素子Q15と前記第16のスイッチング素子Q16の接続点から、第3のインダクタL3及び第16のキャパシタC16とからなる平滑回路を介して直流電圧が出力端子Voutに出力される。

【0051】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第15のスイッチング素子Q15を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第14のダイオードD14、第15のダイオードD15、第16のダイオードD16、第6の抵抗R6、第7の抵抗R7、第1のツェナーダイオードZD1、第12のキャパシタC12、第17のスイッチング素子Q17及び第18のスイッチング素子Q18からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第15のスイッチング素子Q15の制御端子に接続されている。また、第2の信号出力端子OUT2には第13のキャパシタC13が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第15のスイッチング素子Q15をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第15のスイッチング素子Q15をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。また、第16のスイッチング素子Q16を制御するために、第16のスイッチング素子Q16の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。

【0052】

また、出力電圧を第10の抵抗R10と第11の抵抗R11とで分圧したものと、第8の抵抗R8、第9の抵抗R9、第14のキャパシタC14、及び第15のキャパシタC15とからなるランプ波形成回路104からのランプ波信号とを合成したものが帰還信号入力端子FB1に入力されるように接続されており、これが第15のスイッチング素子Q15及び第16のスイッチング素子Q16の駆動タイミングを決めるための帰還信号の役割を果たしている。

【0053】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

《非絶縁型昇圧コンバータに適用した場合》

図19に図2で示した制御ICを用いた非絶縁型昇圧DC−DCコンバータの実施形態に係る回路図を示す。

【0054】

直流入力電源Vinの両端に対して、第4のインダクタL4と電力スイッチ素子として機能する第19のスイッチング素子Q19とからなる直列回路が接続され、第19のスイッチング素子Q19の両端に対して、同期整流器として機能する第20のスイッチング素子Q20と第20のキャパシタC20とからなる直列回路が接続されており、第20のキャパシタC20の両端を出力として、直流電圧が出力端子Voutに出力される。

【0055】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第19のスイッチング素子Q19を制御するために、第19のスイッチング素子Q19の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。また、第20のスイッチング素子Q20を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第17のダイオードD17、第18のダイオードD18、第19のダイオードD19、第12の抵抗R12、第13の抵抗R13、第2のツェナーダイオードZD2、第19のキャパシタC19、第21のスイッチング素子Q21及び第22のスイッチング素子Q22からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第20のスイッチング素子Q20の制御端子に接続されている。また、第2の信号出力端子OUT2には第18のキャパシタC18が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第20のスイッチング素子Q20をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第20のスイッチング素子Q20をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。

【0056】

また、図19では省略しているが、第19のスイッチング素子Q19がオン状態の時に増加し、オフ状態の時に減少するようなランプ波を形成する回路が設けられ、帰還信号端子FB1に入力される帰還信号に重畳されている。

【0057】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

《非絶縁型SEPICコンバータに適用した場合》

図20に図2で示した制御ICを用いた非絶縁型SEPIC(Single Ended Primary Inductance Converter)DC−DCコンバータの実施形態に係る回路図を示す。

【0058】

直流入力電源Vinの両端に対して、第5のインダクタL5と電力スイッチ素子として機能する第23のスイッチング素子Q23とからなる直列回路が接続され、同期整流器として機能する第24のスイッチング素子Q24とからなる直列回路が接続されており、前記第23のスイッチング素子Q23の両端に対して、第22のキャパシタC22と第6のインダクタL6とからなる直列回路が接続され、第6のインダクタL6の両端に対して、第24のスイッチング素子Q24と第25のキャパシタC25とからなる直列回路が接続され、第25のキャパシタC25の両端を出力として、直流電圧が出力端子Voutに出力される。第5のインダクタL5と第6のインダクタL6は磁気結合しているように図示されているが、磁気結合していなくても動作する。

【0059】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第24のスイッチング素子Q24を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第20のダイオードD20、第21のダイオードD21、第22のダイオードD22、第16の抵抗R16、第17の抵抗R17、第3のツェナーダイオードZD3、第24のキャパシタC24、第25のスイッチング素子Q25及び第26のスイッチング素子Q26からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第24のスイッチング素子Q24の制御端子に接続されている。また、第2の信号出力端子OUT2には第23のキャパシタC23が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第24のスイッチング素子Q24をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第24のスイッチング素子Q24をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。また、第23のスイッチング素子Q23を制御するために、第23のスイッチング素子Q23の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。

【0060】

また、図20では省略しているが、第23のスイッチング素子Q23がオン状態の時に増加し、オフ状態の時に減少するようなランプ波を形成する回路が設けられ、帰還信号端子FB1に入力される帰還信号に重畳されている。

【0061】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

【符号の説明】

【0062】

101、102…制御IC

103、104…ランプ波形成回路

L1…第1のインダクタ

L2…第2のインダクタ

L3…第3のインダクタ

L4…第4のインダクタ

L5…第5のインダクタ

L6…第6のインダクタ

C1…第1のキャパシタ

C2…第2のキャパシタ

C3…第3のキャパシタ

C4…第4のキャパシタ

C5…第5のキャパシタ

C6…第6のキャパシタ

C7…第7のキャパシタ

C8…第8のキャパシタ

C9…第9のキャパシタ

C10…第10のキャパシタ

C11…第11のキャパシタ

C12…第12のキャパシタ

C13…第13のキャパシタ

C14…第14のキャパシタ

C15…第15のキャパシタ

C16…第16のキャパシタ

C17…第17のキャパシタ

C18…第18のキャパシタ

C19…第19のキャパシタ

C20…第20のキャパシタ

C21…第21のキャパシタ

C22…第22のキャパシタ

C23…第23のキャパシタ

C24…第24のキャパシタ

C25…第25のキャパシタ

Ciss…スイッチング素子のゲート−ソース間容量

D1…第1のダイオード

D2…第2のダイオード

D3…第3のダイオード

D4…第4のダイオード

D5…第5のダイオード

D6…第6のダイオード

D7…第7のダイオード

D8…第8のダイオード

D9…第9のダイオード

D10…第10のダイオード

D11…第11のダイオード

D12…第12のダイオード

D13…第13のダイオード

D14…第14のダイオード

D15…第15のダイオード

D16…第16のダイオード

D17…第17のダイオード

D18…第18のダイオード

D19…第19のダイオード

D20…第20のダイオード

D21…第21のダイオード

D22…第22のダイオード

ZD1…第1のツェナーダイオード

ZD2…第2のツェナーダイオード

ZD3…第3のツェナーダイオード

Q1…第1のスイッチング素子

Q2…第2のスイッチング素子

Q3…第3のスイッチング素子

Q4…第4のスイッチング素子

Q5…第5のスイッチング素子

Q6…第6のスイッチング素子

Q7…第7のスイッチング素子

Q8…第8のスイッチング素子

Q9…第9のスイッチング素子

Q10…第10のスイッチング素子

Q11…第11のスイッチング素子

Q12…第12のスイッチング素子

Q13…第13のスイッチング素子

Q14…第14のスイッチング素子

Q15…第15のスイッチング素子

Q16…第16のスイッチング素子

Q17…第17のスイッチング素子

Q18…第18のスイッチング素子

Q19…第19のスイッチング素子

Q20…第20のスイッチング素子

Q21…第21のスイッチング素子

Q22…第22のスイッチング素子

Q23…第23のスイッチング素子

Q24…第24のスイッチング素子

Q25…第25のスイッチング素子

Q26…第26のスイッチング素子

S1…第1のスイッチ回路

S2…第2のスイッチ回路

S3…第3のスイッチ回路

S4…第4のスイッチ回路

S5…第5のスイッチ回路

S6…第6のスイッチ回路

S7…第7のスイッチ回路

S8…第8のスイッチ回路

S9…第9のスイッチ回路

S10…第10のスイッチ回路

R1…第1の抵抗

R2…第2の抵抗

R3…第3の抵抗

R4…第4の抵抗

R5…第5の抵抗

R6…第6の抵抗

R7…第7の抵抗

R8…第8の抵抗

R9…第9の抵抗

R10…第10の抵抗

R11…第11の抵抗

R12…第12の抵抗

R13…第13の抵抗

R14…第14の抵抗

R15…第15の抵抗

R16…第16の抵抗

R17…第17の抵抗

R18…第18の抵抗

R19…第19の抵抗

T…トランス

PT…パルストランス

Np1…第1の1次巻線

Np2…第2の1次巻線

Np3…第3の1次巻線

Ns1…第1の2次巻線

Ns2…第2の2次巻線

Vin…入力電圧

Vdet…巻線電圧検出端子

Vdr1…第1の直流電圧部

Vdr2…第2の直流電圧部

Vout…出力端子

Vref1…リファレンス電圧

OUT1…第1の出力信号端子

OUT2…第2の信号出力端子

OUT3…第3の信号出力端子

FB1…帰還信号入力端子

COMP1…コンパレータ

GND…グランド端子

【技術分野】

【0001】

本発明は、フルブリッジ構成のスイッチング回路を備え、外部信号との送受信が可能で、絶縁型/非絶縁型に関わらず電源装置に利用できる半導体集積回路と、それを用いたDC−DCコンバータに関するものである。

【背景技術】

【0002】

絶縁型DC−DCコンバータでは、1次回路と2次回路とで異なるグランド電位に対応したり、安全規格を満たすために、トランスで1次−2次間を絶縁する。2次側の出力電圧や出力電流を制御する場合、それらを検出して1次側にフィードバックし、1次側のスイッチング回路を制御することになるが、このフィードバック回路にも1次−2次間の絶縁が求められる。

【0003】

また、2次側に同期整流回路を採用する場合、メインスイッチと転流側同期整流器が共にオン状態となって貫通電流が流れるのを防ぐために、メインスイッチのターンオン直前に、2次側同期整流回路の転流側同期整流器をターンオフさせる動作が必要となり、メインスイッチのターンオン直前のタイミングを示す信号を1次側から2次側に伝送し、2次側同期整流器のスイッチングタイミングを制御する必要がある。(特許文献1参照)

ここで特許文献1に示されている絶縁型DC−DCコンバータの基本的な構成を図1に示す。

【0004】

図1において、メインスイッチ2は、1次側制御回路5から出力される制御信号に応じてスイッチング制御される。1次側制御回路5は、出力電圧Voを絶縁回路10を介して検出し、これに基づいてメインスイッチ2のデューティ比を制御する信号C1を出力する。さらに制御信号C1は、駆動回路7、8及びトランス9を介して2次側にも伝達されて制御信号C2となり、かかる制御信号C2は2次側制御回路21に供給される。2次側制御回路21に供給された制御信号C2は、駆動回路13の入力端及びトランジスタ15のゲート電極に印加され、これによって整流側同期整流器3はメインスイッチ2と同相に駆動され、転流側同期整流器4はメインスイッチ2と逆相に駆動される。

【0005】

ここで、駆動回路7、8及びトランス9が介在することによって生じる制御信号C1と制御信号C2との間のタイミングのズレ、及び転流側同期整流器を構成するMOSFETのターンオフ遅延時間は、メインスイッチのターンオンタイミングを遅延させる遅延回路11によって調整されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−272097号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

図1に示されているように、2次側に同期整流回路を用いる場合、出力電圧検出信号を1次側にフィードバックさせる手段を含め、1次−2次間を絶縁した状態で信号を伝達させる手段が少なくとも2つ必要になり、回路構成が複雑になるという問題がある。

【0008】

また、別の問題としては、近年、制御回路にはICが用いられるが、1次側制御回路と2次側制御回路で固有の設計とした場合、2種類の特定用途向けIC(ASIC)を製造せねばならず、生産性・経済性が悪いという問題があった。

【0009】

そこで、この発明の目的は、フルブリッジ構成のスイッチング回路を備え、外部信号との送受信が可能で、絶縁型であれば1次側と2次側に同じハードウェア構成のICを2つ使用することができ、かつ非絶縁型にも適用可能な、電源装置に利用できる半導体集積回路と、それを用いたDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0010】

本発明の絶縁型DC−DCコンバータは、所定の直流電圧が印加される第1の直流電圧部と、第2の直流電圧部と、基準電位に接続されるGND端子と、第1のスイッチ回路S1と第2のスイッチ回路S2とからなる第1の直列回路と、第3のスイッチ回路S3と第4のスイッチ回路S4とからなる第2の直列回路と、該第1〜第4のスイッチ回路のオン/オフ動作を制御する制御部と、前記第1のスイッチ回路S1と前記第2のスイッチ回路S2との接続点を外部に引き出すための第1の出力端子と、前記第3のスイッチ回路S3と前記第4のスイッチ回路S4の接続点を外部に引き出すための第2の出力端子と、を含む半導体集積回路であって、前記第1の直列回路の一端は前記第1の直流電圧部Vdr1に接続され、前記第2の直列回路の一端は前記第2の直流電圧部Vdr2に接続され、前記第1の直列回路の他端と、前記第2の直列回路の他端が共に前記GND端子に対して接続され、前記第1の出力端子と前記第2の出力端子との間にリアクタンス素子が接続され、前記リアクタンス素子の両端電圧の変化を検出する巻線電圧検出手段(Vdet)と、少なくとも前記第1のスイッチ回路S1がオン状態、かつ前記第2のスイッチ回路S2及び前記第3のスイッチ回路S3が共にオフ状態である時に、前記リアクタンス素子に正極性の電圧を印加し、もしくは前記第2のスイッチ回路(S2)がオン状態、かつ前記第1のスイッチ回路(S1)及び前記第4のスイッチ回路(S4)が共にオフ状態である時に、前記リアクタンス素子に負極性の電圧を印加することで、前記リアクタンス素子に励磁電流を流してパルス電圧を発生させ、該パルス電圧をエッジ信号として外部に送信すると共に、少なくとも前記第1のスイッチ回路S1及び前記第2のスイッチ回路S2が共にオフ状態である時に、前記リアクタンス素子に生じるパルス電圧を、前記巻線電圧検出端子によって検出することにより、外部からのエッジ信号を受信できるようにしたことを特徴とする。

【0011】

さらには、前記半導体集積回路はさらに、前記第1の直流電圧部から入力される電圧を出力する第3の出力端子と、該第3の出力端子に、電圧を出力するか否かを制御するサブドライバ回路と、を備え、前記サブドライバ回路のターンオン及びターンオフ動作は前記制御部によって制御され、前記制御部は、前記第2の出力端子に生じる方形波電圧と、前記第3の出力端子に生じる方形波電圧が、共に低レベルである期間を挟んで互いに相補的な関係になるように前記第1〜第4のスイッチ回路及び前記サブドライバ回路を制御することを特徴とする。

【0012】

さらには、前記半導体集積回路が1次側制御回路及び2次側制御回路にそれぞれ用いられた絶縁型スイッチング電源装置であって、直流電源と、少なくとも1組の1次巻線及び2次巻線を有するトランスと、前記直流電源から供給される直流電圧を前記1次巻線に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、前記2次巻線に接続される少なくとも1つの同期整流回路を含む整流回路と、該整流回路の出力を平滑する出力フィルタ回路と、を少なくとも備え、少なくとも1次巻線と2次巻線を有し、1次側に配置された前記半導体集積回路に該1次巻線を、2次側に配置された前記半導体集積回路に該2次巻線が接続された信号伝送トランスをリアクタンス素子として用いて、前記1次側に配置された半導体集積回路と、前記2次側に配置された半導体集積回路との間で、パルス信号を双方向に伝送し、前記電力スイッチ素子及び前記同期整流器の駆動タイミングを制御することを特徴とする。

【0013】

さらには、請求項1、もしくは請求項2に記載の半導体集積回路を制御回路に用い、直流電源と、少なくとも1つのインダクタンス素子と、前記直流電源から供給される直流電圧を該インダクタンス素子に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、少なくとも1つの同期整流器を含む整流回路と、整流回路の出力を平滑する出力フィルタ回路と、を備える非絶縁型スイッチング電源装置であって、前記電力スイッチ素子、もしくは前記同期整流器は電界効果トランジスタで構成されており、該電界効果トランジスタのソース端子が該制御回路のグランド電位からフローティングされていて、該電界効果トランジスタのゲート−ソース間にエッジ信号から方形波信号への変換回路が接続され、前記半導体集積回路からトランスを介して送信されるエッジ信号を前記変換回路にて変換された方形波信号で、該電界効果トランジスタが駆動されることを特徴とする。

【発明の効果】

【0014】

本発明は、

(a)パワー半導体素子の駆動を制御するとともに、双方向信号伝送機能を有するプログラマブルな半導体素子を提供できる。

(b)絶縁型/非絶縁型を問わず、様々なトポロジーの電源装置の制御回路として応用出来る。

(c)絶縁型DC−DCコンバータに利用した場合は、1次側と2次側に同じハードウェアの半導体素子を使用でき、制御ICの開発コストの低減、製造コストの削減に貢献できる。

【図面の簡単な説明】

【0015】

【図1】特許文献1に示されている絶縁型DC−DCコンバータの基本的な構成を示す図である。

【図2】第1の実施形態に係る制御IC101の内部ブロック図である。

【図3】第1の実施形態に係る制御ICを用いた絶縁型DC−DCコンバータの回路例である。

【図4】スイッチング周期あたりの各部の波形図である。

【図5】時間t0〜t1区間における制御IC内部の動作説明図である。

【図6】時間t1における制御IC内部の動作説明図である。

【図7】時間t1〜t2区間における制御IC内部の動作説明図である。

【図8】時間t2における制御IC内部の動作説明図である。

【図9】時間t2〜t3区間における制御IC内部の動作説明図である。

【図10】時間t3〜t4区間における制御IC内部の動作説明図である。

【図11】時間t4〜t5区間における制御IC内部の動作説明図である。

【図12】時間t5における制御IC内部の動作説明図である。

【図13】時間t5〜t6区間における制御IC内部の動作説明図である。

【図14】時間t6における制御IC内部の動作説明図である。

【図15】時間t6〜t7区間における制御IC内部の動作説明図である。

【図16】時間t7〜t8区間における制御IC内部の動作説明図である。

【図17】第2の実施形態に係る制御IC101の内部ブロック図である。

【図18】第1の実施形態に係る制御ICを用いた非絶縁型降圧DC−DCコンバータの回路例である。

【図19】第1の実施形態に係る制御ICを用いた非絶縁型昇圧DC−DCコンバータの回路例である。

【図20】第1の実施形態に係る制御ICを用いた非絶縁型SEPICコンバータの回路例である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

図2は第1の実施形態に係る絶縁型DC−DCコンバータの制御に用いられる半導体集積回路(以下、制御ICと呼ぶ)101の内部ブロック図である。制御IC101は、少なくとも第1のスイッチング素子Q1と第1のダイオードD1の並列回路からなる第1のスイッチ回路S1、及び少なくとも第2のスイッチング素子Q2と第2のダイオードの並列回路からなる第2のスイッチ回路S2、とからなる直列回路と、少なくとも第3のスイッチング素子Q3と第3のダイオードD3の並列回路からなる第3のスイッチ回路S3、及び少なくとも第4のスイッチング素子Q4と第4のダイオードD4の並列回路からなる第4のスイッチ回路S4とからなる直列回路と、を備え、各スイッチ回路S1〜S4のターンオン及びターンオフを制御する制御信号を出力するディジタル制御部を備える。

【0017】

第1のスイッチ回路S1と第2のスイッチ回路S2の接続点と、第3のスイッチ回路S3と第4のスイッチ回路S4の接続点には、両者間にインダクタンス素子を接続するための第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2が設けられている。また、第1のスイッチ回路S1及び第2のスイッチ回路S2とからなる直列回路と、第3のスイッチ回路S3及び第4のスイッチ回路S4とからなる直列回路は、それぞれの一端が共通接続されて接地端子GNDに接続され他端はそれぞれ第1の直流電圧部Vdr1及び第2の直流電圧部Vdr2に接続されている。すなわち、各スイッチ回路S1〜S4はフルブリッジ型を形成することとなるので、ハイサイド側スイッチとなる第1のスイッチ回路S1及び第3のスイッチ回路S3は、ハイサイドドライバとしてのバッファを介してディジタル制御部からの制御信号が伝達される。

【0018】

さらに、第3のスイッチ回路S3と第4のスイッチ回路S4の接続点には、該接続点の電位を検出するためのパルス電圧信号検出端子Vdetが設けられ、ディジタル制御部に入力されるように構成されている。

【0019】

さらに、例えば第2の直流電圧部Vdr2から電力を得て、ディジタル制御部から出力される信号により第2のドライブ信号を出力するためのサブドライバと、該第2のドライブ信号が出力される第3の信号出力端子OUT3を備えている。

【0020】

さらに、第1の比較器COMP1、該第1の比較器COMP1に入力される第1の基準電圧源Vref1を備え、該第1の比較器の出力信号がディジタル制御部に入力される構成になっている。

【0021】

さらに、第1のスイッチ回路S1と第2のスイッチ回路S2の接続点と、該ディジタル制御部の駆動電源端子Vlogicとの間が、第9のダイオードD9と第9のスイッチ回路S9を介して接続されており、第9のスイッチ回路S9は該ディジタル制御部によって制御される。

【0022】

図3に図2で示した制御ICを用いた絶縁型DC−DCコンバータの第1の実施形態に係る回路図を示す。

【0023】

直流入力電源Vinの両端に対して、トランスTの1次巻線Np1と、第11のスイッチング素子Q11と第1の抵抗R1とからなる直列回路が接続されており、該第11のスイッチング素子Q11に対して、第1のキャパシタC1とPチャネルMOSFETで形成された第12のスイッチング素子Q12とからなる直列回路が並列に接続されている。

【0024】

トランスTの2次巻線Ns1の両端に対しては、整流用同期整流器として機能する第13のスイッチング素子Q13及び転流用同期整流器として機能する第14のスイッチング素子Q14とからなる同期整流回路が接続され、第1のインダクタL1及び第4のキャパシタC4とからなる平滑回路を介して直流電圧が出力端子Voutに出力される。

【0025】

1次側制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第11のスイッチング素子Q11を制御するために、第11のスイッチング素子Q11の制御端子と第2の信号出力端子OUT2とが接続され、第12のスイッチング素子Q12を制御するために、第12のスイッチング素子Q12の制御端子と第3の信号出力端子OUT3とが第3のキャパシタC3及び第13のダイオードD13とからなるレベルシフト回路を介して接続され、第1の抵抗R1を電流検出抵抗として第11のスイッチング素子Q11に流れる電流を検出するために、第11のスイッチング素子Q11と第1の抵抗R1との接続点が帰還信号入力端子FB1に接続され、第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2には、パルストランスPTの1次巻線Np2の両端が接続されている。また、接地端子GNDがGNDラインに接続されている。

【0026】

2次側制御IC102は、トランスTの2次巻線Ns1に生じる電圧を整流平滑した出力電圧から駆動電源端子Vdd、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第13のスイッチング素子Q13を制御するために、第13のスイッチング素子Q13の制御端子と第2の信号出力端子OUT2とが接続され、第14のスイッチング素子Q14を制御するために、第14のスイッチング素子Q14の制御端子と第3の信号出力端子OUT3とが接続され、出力電圧を第4の抵抗R4と第5の抵抗R5とで分圧したものと、第2の抵抗R2、第3の抵抗R3、第4のキャパシタC4、及び第5のキャパシタC5とからなるランプ波形成回路103からのランプ波信号とを合成したものが帰還信号入力端子FB1に入力されるように接続され、第1のパルス信号端子OUT1及び第2のパルス信号端子OUT2には、パルストランスPTの2次巻線Ns2の両端が接続されている。なお、第6のキャパシタC6は平滑コンデンサとして機能する。

【0027】

少なくとも第1のスイッチ回路S1〜第8のスイッチ回路S8の各スイッチ回路は、MOSFETで構成することによって、第1のダイオードD1〜第8のダイオードD8をMOSFETのボディダイオードで代替させることができる。特にパワー半導体素子である第11のスイッチング素子Q11〜第14のスイッチング素子Q14に関しては、MOSFETに限らず、BJT(バイポーラジャンクショントランジスタ)やIGBT(絶縁ゲートバイポーラトランジスタ)等も適用できる。なお、図3においては、第12のスイッチング素子Q12にのみPチャネル型FETが用いられ、他のスイッチング素子にはNチャネル型FETが用いられているが、必要に応じて適宜使い分ければよい。

【0028】

なお、詳細は後述するが、1次側制御IC101及び2次側制御IC102には同一のハードウェアのICを利用することができる。

【0029】

図4に、第11のスイッチング素子Q11の1スイッチング周期における、第11のスイッチング素子Q11のドレイン−ソース間電圧、第1のスイッチング素子Q1〜第4のスイッチング素子Q4のゲート−ソース間電圧、及びパルストランスPTの1次巻線Np2の両端電圧の各波形図を示す。

【0030】

第11のスイッチング素子Q11の1スイッチング周期をt0〜t8の計10区間に分けて各部の動作を説明する。

[時間t0〜t1区間における動作]

図5に、この区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。1次側制御IC101及び2次側制御IC102のディジタル制御部の駆動電源端子Vlogicには、図2に示すように、第9のスイッチ回路S9と第9のダイオードD9を介して、第1のスイッチ回路S1と第2のスイッチ回路S2との接続点に接続されているので、このようになる。

【0031】

この時、第1のスイッチ回路S1、第2のスイッチ回路S2、及び第3のスイッチ回路S3はオフ、第4のスイッチ回路S4はオン状態となっている。これにより、1次側制御IC101における第2の信号出力端子OUT2に接続されている第11のスイッチング素子Q11のゲート−ソース間は第4のスイッチ回路S4がオンしていることによりショート状態となり、第11のスイッチング素子Q11の入力容量Cissには電荷が蓄積されていない。すなわち第11のスイッチング素子Q11はオフ状態である。

【0032】

この時、Pチャネル型FETである第12のスイッチング素子Q12のソース−ゲート間電圧は負電位になっているので、オン状態である。

【0033】

2次側制御IC102内においても同様で、第5のスイッチ回路S5、第6のスイッチ回路S6及び第7のスイッチ回路S7はオフ、第8のスイッチ回路S8はオン状態となっている。これにより、2次側制御IC102における第2の信号出力端子OUT2に接続されている第13のスイッチング素子Q13のゲート−ソース間は第8のスイッチ回路S8がオンしていることによりショート状態となり、第13のスイッチング素子Q13の入力容量Cissには電荷が蓄積されていない。すなわち整流側同期整流器として機能する第13のスイッチング素子Q13はオフ状態である。

【0034】

なお、転流側同期整流器として機能する第14のスイッチング素子Q14は、第13のスイッチング素子Q13とはデッドタイムを挟んで相補的に動作するため、オン状態である。

[時間t1における動作]

図6に、時間t1における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0035】

時間t1において、1次側制御IC101内の第1のスイッチ回路S1をターンオンさせる。すると、第1の直流電圧部Vdr1から供給される電流が第1のスイッチ回路S1、パルストランスPTの1次巻線Np2、第4のスイッチ回路S4を介して流れる。パルストランスPTの1次巻線Np2が励磁されることによって、パルストランスPTの2次巻線Ns2には電圧が生じるので、2次側制御IC102において、これを第5のスイッチ回路S5と第6のスイッチ回路S6の接続点に位置する巻線電圧検出端子Vdetにて検出する。

[時間t1〜t2区間における動作]

図7に、時間t1〜t2区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0036】

2次側制御IC102内のディジタル制御部は、巻線電圧検出端子Vdetに電圧が入力されたことに応じて、第5のスイッチ回路S5をターンオンさせる。この動作により、2次側制御IC102においても、第2の直流電圧部Vdr2から供給される電流が、第5のスイッチ回路S5、パルストランスPTの2次巻線Ns2、第8のスイッチ回路S8を介して流れる。

[時間t2における動作]

図8に、時間t2における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0037】

時間t2において、1次側制御IC101内のディジタル制御部は、第4のスイッチ回路S4を、また2次側制御IC102内のディジタル制御部は、第8のスイッチ回路S8を、それぞれターンオフさせる。この動作により、1次側制御IC101内においては、第1の直流電圧部Vdr1から供給される電流が、第11のスイッチング素子Q11の入力容量Cissに流れて電荷が充電され、第11のスイッチング素子Q11がターンオンする。同時に2次側制御IC102内においては、第2の直流電圧部Vdr2から供給される電流が、第13のスイッチング素子Q13の入力容量Cissに流れて電荷が充電され、第13のスイッチング素子Q13がターンオンする。

[時間t2〜t3区間における動作]

図9に、時間t2〜t3区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0038】

時間t2〜t3において、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のターンオンが終了すると、1次側制御IC101内において第1の直流電圧部Vdr1から供給される電流は、第1のスイッチ回路S1、パルストランスPTの1次巻線Np2、第3のダイオードD3を介して第1の直流電圧部Vdr1に還流する。また、2次側制御IC102内においても同様に、第2の直流電圧部Vdr2から供給される電流は、第5のスイッチ回路S5、パルストランスPTの2次巻線Ns2、第7のダイオードD7を介して還流する。

[時間t3〜t4区間における動作]

図10に、時間t3〜t4区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0039】

時間t3において、1次側制御IC101においては第1のスイッチ回路S1が、2次側制御IC102においては第5のスイッチ回路S5がそれぞれターンオフする。この動作によって時間t3〜t4の間、パルストランスPTの1次巻線Np2及び2次巻線Ns2にそれぞれ流れる電流は減少しながら、1次側制御IC101においては第2のダイオードD2、パルストランスPTの1次巻線Np2、第3のダイオードD3を介して流れ、2次側制御IC102においては第6のダイオードD6、パルストランスPTの2次巻線Ns2、第7のダイオードD7を介して流れ、パルストランスPT1に蓄積された電磁エネルギーが回生される。

[時間t4〜t5区間における動作]

図11に、時間t4〜t5区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0040】

その後、時間t4において、パルストランスPTの1次巻線Np2及び2次巻線Ns2に流れる電流がゼロに近づき、1次側制御IC101における第2のダイオードD2、及び第3のダイオードD3と、2次側制御IC102における第6のダイオードD6、及び第7のダイオードD7のそれぞれに順方向電流が流れなくなると、1次側制御IC101における第3のスイッチ回路S3及び2次側制御IC102における第7のスイッチ回路S7をそれぞれターンオンさせる。この動作により、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のゲート電位は、第2の直流電圧部Vdr2(=第1の直流電圧部Vdr1)から供給される電圧値に維持されることとなり、常にオン状態が維持されることになる。

[時間t5における動作]

図12に、時間t5における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0041】

時間t5において、2次側制御IC102内の第6のスイッチ回路S6をターンオンさせる。すると、第1の直流電圧部Vdr1から供給される電流が第7のスイッチ回路S7、パルストランスPTの2次巻線Ns2、第6のスイッチ回路S6を介して流れる。パルストランスPTの2次巻線Ns2が励磁されることによって、パルストランスPTの1次巻線Np2には電圧が生じるので、1次側制御IC101において、これを第1のスイッチ回路S1と第2のスイッチ回路S2の接続点に位置する巻線電圧検出端子Vdetにて検出する。

[時間t5〜t6区間における動作]

図13に、時間t5〜t6区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0042】

1次側制御IC101内のディジタル制御部は、巻線電圧検出端子Vdetに電圧が入力されたことに応じて、第2のスイッチ回路S2をターンオンさせる。この動作により、1次側制御IC101においても、第2の直流電圧部Vdr2から供給される電流が、第3のスイッチ回路S3、パルストランスPTの1次巻線Np2、第2のスイッチ回路S2を介して流れる。

【0043】

この期間の途中で、第9のスイッチ回路S9及び第10のスイッチ回路S10もターンオンさせる。t5〜t6区間の時間長さを調整するとパルストランスPTに蓄える電磁エネルギーの量を変更できる。従ってt5〜t6区間の時間長さの制御によって1次側制御IC101内、及び2次側制御IC102内のディジタル制御部に与える駆動電圧を制御できる。

[時間t6における動作]

図14に、時間t6における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

時間t6において、1次側制御IC101内のディジタル制御部は、第3のスイッチ回路S3を、また2次側制御IC102内のディジタル制御部は、第7のスイッチ回路S7を、それぞれターンオフさせる。この動作により、1次側制御IC101内においては、第11のスイッチング素子Q11の入力容量Cissに蓄積されていた電荷が放電され、第11のスイッチング素子Q11がターンオフする。同時に2次側制御IC内においては、第13のスイッチング素子Q13の入力容量Cissに蓄積されていた電荷が放電され、第13のスイッチング素子Q13がターンオフする。

[時間t6〜t7区間における動作]

図15に、時間t6〜t7区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

【0044】

時間t6〜t7において、第11のスイッチング素子Q11及び第13のスイッチング素子Q13のゲート−ソース間電圧が0Vに到達すると、1次側制御IC101内において、第4のダイオードD4、パルストランスPTの1次巻線Np2、第2のスイッチ回路S2を介してGNDに向かって電流が流れる。また、2次側制御IC102内においても同様に、第8のダイオードD8、パルストランスPTの2次巻線Ns2、第6のスイッチ回路S6を介してGNDに向かって電流が流れる。

[時間t7〜t8区間における動作]

図16に、時間t7〜t8区間における1次側制御IC101及び2次側制御IC102内の簡略化した回路ブロック図を示す。

時間t7において、1次側制御IC101においては第4のスイッチ回路S4が、2次側制御IC102においては第8のスイッチ回路S8がそれぞれターンオンすると同時に、第2のスイッチ回路S2と第6のスイッチ回路S6がターンオフする。この動作によって時間t7〜t8の間、パルストランスPTの1次巻線Np2及び2次巻線Ns2にそれぞれ流れる電流は減少しながら、1次側制御IC101においては第4のダイオードD4、パルストランスPTの1次巻線Np2、第9のダイオードD9を介して第7のキャパシタC7を充電するように流れ、2次側制御IC102においては第8のダイオードD8、パルストランスPTの2次巻線Ns2、第10のダイオードD10を介して第8のキャパシタC8を充電するように流れる。

【0045】

上述した動作によって、第11のスイッチング素子Q11、第13のスイッチング素子Q13の駆動エネルギーを、1次側制御IC101、2次側制御IC102のディジタル制御回路を駆動する電力として回生させることができる。なお、この期間の途中で第9のスイッチ回路S9及び第10のスイッチ回路S10をターンオフすれば第7のキャパシタC7及び第8のキャパシタC8を充電するエネルギーを制限する事ができる。その後、第9のスイッチ回路S9及び第10のスイッチ回路S10のターンオフ時点でまだ回生されていないパルストランスPTの電磁エネルギーは第1のダイオードD1及び第5のダイオードD5を介して第1の直流電圧部Vdr1に回生される。この方法でもディジタル制御部の駆動電源端子Vlogicの電圧を目標値に安定化するよう制御できる。

[時間t8以降における動作]

時間t8以降時間t1までの区間における動作は、上記[時間t0〜t1区間における動作]と同一の動作になる。

【0046】

上述した動作により、1次側制御ICから出力される、1次側のメインスイッチに相当する第11のスイッチング素子Q11をターンオンさせる直前のタイミングを示す信号を、パルストランスPTを介して2次側に伝送し、2次側の同期整流回路における整流側同期整流器に相当する第13のスイッチング素子Q13をターンオンさせるためのタイミング信号として利用するとともに、2次側制御ICから出力される、2次側の同期整流回路における転流側同期整流器をターンオフさせる。メインスイッチのターンオン直前のタイミングで転流側同期整流器がターンオフされる事で、メインスイッチと転流側同期整流器の同時オンによる貫通電流の発生が防止される。整流側同期整流器に相当する第13のスイッチング素子Q13をターンオフさせる直前のタイミングを示す信号を、パルストランスPTを介して1次側に伝送し、1次側のメインスイッチに相当する第11のスイッチング素子Q11をターンオフさせるためのタイミング信号として利用できる。また、前述の例とは逆にメインスイッチのターンオン直前のタイミングを示す信号を2次側から1次側に伝送する事もできるし、メインスイッチのターンオフ直前のタイミングを示す信号を1次側から2次側に伝送する事もできる。1次側と2次側の内、先に送出された信号が優先して実行される。すなわち、1つのパルストランスPTを用いた完全な双方向通信が可能となる。さらに、回生するエネルギーを制御IC内のディジタル制御部の駆動電圧源として利用することができる。すなわち、例えば第11のスイッチング素子Q11、第12のスイッチング素子Q12、第13のスイッチング素子Q13、および第14のスイッチング素子Q14のゲート駆動電圧が10V程度であって、1次側制御IC101及び2次側制御IC102のディジタル制御部の駆動電圧が1.8V程度である場合などに、パルストランスPTの励磁インダクタンスをエネルギー蓄積素子として利用することで、リニアレギュレータによる降圧ではなく、スイッチングレギュレータとして任意の電圧を生成することができ、回路効率を高めることができる。また、1次−2次間の信号伝送に用いるパルストランスPTをエネルギー蓄積素子としても兼用しているので、別個にスイッチングレギュレータを構成するより簡略な回路構成となる。

【0047】

なお、時間t0〜t2の区間及び時間t4〜t6の区間における動作は、第11のスイッチング素子Q11と第12のスイッチング素子Q12が共にオフである期間(デッドタイム)、及び第13のスイッチング素子Q13と第14のスイッチング素子Q14が共にオフである期間(デッドタイム)を作るための動作であるが、デッドタイムを作る手段を別に設ければ、第3のスイッチ回路S3と第4のスイッチ回路S4、及び第7のスイッチ回路S7と第8のスイッチ回路S8は常にオフ、すなわち単なるダイオードに置き換えてもよい。

【0048】

第1の実施形態に係る発明は、上述した(a)、(b)、(c)の効果を有する。

《第2の実施形態》

また、図17に、第2の直流電圧部Vdr2を駆動電圧源に接続せず、1次側制御IC101では第9のキャパシタC9、2次側制御IC102では第10のキャパシタC10に接続した場合の、1次側制御IC101及び2次側制御IC102の内部ブロック図を示す。1次側制御IC101を例に取ると、第1のスイッチ回路S1がオン状態である期間中に、第4のスイッチ回路S4のオン時間を可変させるとすると、第1の直流電圧部Vdr1からパルストランスPTの励磁インダクタンス、第4のスイッチ回路S4、第3のスイッチ回路S3、及び第9のキャパシタC9からなる回路は、昇圧チョッパ型コンバータになることが分かる。すなわち、第1の直流電圧部Vdr1から供給される電圧が変動の大きな直流電圧であった場合でも、第4のスイッチ回路S4のオン時間を制御することによって、第2の信号出力端子OUT2に印加される電圧値を一定に制御することができる。なお、これは2次側制御IC102にも適用できることは言うまでもない。

【0049】

第2の実施形態に係る発明は、上述した(a)、(b)、(c)の効果を有する。

《非絶縁型降圧コンバータに適用した場合》

図18に図2で示した制御ICを用いた非絶縁型降圧DC−DCコンバータの実施形態に係る回路図を示す。

【0050】

直流入力電源Vinの両端に対して、電力スイッチ素子として機能する第15のスイッチング素子Q15と、同期整流器として機能する第16のスイッチング素子Q16とからなる直列回路が接続されており、前記第15のスイッチング素子Q15と前記第16のスイッチング素子Q16の接続点から、第3のインダクタL3及び第16のキャパシタC16とからなる平滑回路を介して直流電圧が出力端子Voutに出力される。

【0051】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第15のスイッチング素子Q15を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第14のダイオードD14、第15のダイオードD15、第16のダイオードD16、第6の抵抗R6、第7の抵抗R7、第1のツェナーダイオードZD1、第12のキャパシタC12、第17のスイッチング素子Q17及び第18のスイッチング素子Q18からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第15のスイッチング素子Q15の制御端子に接続されている。また、第2の信号出力端子OUT2には第13のキャパシタC13が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第15のスイッチング素子Q15をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第15のスイッチング素子Q15をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。また、第16のスイッチング素子Q16を制御するために、第16のスイッチング素子Q16の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。

【0052】

また、出力電圧を第10の抵抗R10と第11の抵抗R11とで分圧したものと、第8の抵抗R8、第9の抵抗R9、第14のキャパシタC14、及び第15のキャパシタC15とからなるランプ波形成回路104からのランプ波信号とを合成したものが帰還信号入力端子FB1に入力されるように接続されており、これが第15のスイッチング素子Q15及び第16のスイッチング素子Q16の駆動タイミングを決めるための帰還信号の役割を果たしている。

【0053】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

《非絶縁型昇圧コンバータに適用した場合》

図19に図2で示した制御ICを用いた非絶縁型昇圧DC−DCコンバータの実施形態に係る回路図を示す。

【0054】

直流入力電源Vinの両端に対して、第4のインダクタL4と電力スイッチ素子として機能する第19のスイッチング素子Q19とからなる直列回路が接続され、第19のスイッチング素子Q19の両端に対して、同期整流器として機能する第20のスイッチング素子Q20と第20のキャパシタC20とからなる直列回路が接続されており、第20のキャパシタC20の両端を出力として、直流電圧が出力端子Voutに出力される。

【0055】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第19のスイッチング素子Q19を制御するために、第19のスイッチング素子Q19の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。また、第20のスイッチング素子Q20を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第17のダイオードD17、第18のダイオードD18、第19のダイオードD19、第12の抵抗R12、第13の抵抗R13、第2のツェナーダイオードZD2、第19のキャパシタC19、第21のスイッチング素子Q21及び第22のスイッチング素子Q22からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第20のスイッチング素子Q20の制御端子に接続されている。また、第2の信号出力端子OUT2には第18のキャパシタC18が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第20のスイッチング素子Q20をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第20のスイッチング素子Q20をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。

【0056】

また、図19では省略しているが、第19のスイッチング素子Q19がオン状態の時に増加し、オフ状態の時に減少するようなランプ波を形成する回路が設けられ、帰還信号端子FB1に入力される帰還信号に重畳されている。

【0057】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

《非絶縁型SEPICコンバータに適用した場合》

図20に図2で示した制御ICを用いた非絶縁型SEPIC(Single Ended Primary Inductance Converter)DC−DCコンバータの実施形態に係る回路図を示す。

【0058】

直流入力電源Vinの両端に対して、第5のインダクタL5と電力スイッチ素子として機能する第23のスイッチング素子Q23とからなる直列回路が接続され、同期整流器として機能する第24のスイッチング素子Q24とからなる直列回路が接続されており、前記第23のスイッチング素子Q23の両端に対して、第22のキャパシタC22と第6のインダクタL6とからなる直列回路が接続され、第6のインダクタL6の両端に対して、第24のスイッチング素子Q24と第25のキャパシタC25とからなる直列回路が接続され、第25のキャパシタC25の両端を出力として、直流電圧が出力端子Voutに出力される。第5のインダクタL5と第6のインダクタL6は磁気結合しているように図示されているが、磁気結合していなくても動作する。

【0059】

制御IC101は、第1の直流電圧部Vdr1、第2の直流電圧部Vdr2に駆動電圧を得て、第24のスイッチング素子Q24を制御するために、第1の信号出力端子OUT1と第2の信号出力端子OUT2との間に、パルストランスPTの1次巻線が接続され、パルストランスPTの2次巻線は、第20のダイオードD20、第21のダイオードD21、第22のダイオードD22、第16の抵抗R16、第17の抵抗R17、第3のツェナーダイオードZD3、第24のキャパシタC24、第25のスイッチング素子Q25及び第26のスイッチング素子Q26からなる、巻線に生じるエッジ信号を方形波に変換するための回路を介して第24のスイッチング素子Q24の制御端子に接続されている。また、第2の信号出力端子OUT2には第23のキャパシタC23が接続されている。この構成によって、制御IC101の第1のスイッチ回路S1及び第4のスイッチ回路S4がオン状態かつ第2のスイッチ回路S2及び第3のスイッチ回路S3がオフ状態になった時に、パルストランスPTにパルス信号を発生させることによって、第24のスイッチング素子Q24をターンオンさせることができ、第2のスイッチ回路S2及び第3のスイッチ回路S3がオン状態かつ第1のスイッチ回路S1及び第4のスイッチ回路S4がオフ状態になった時に、第24のスイッチング素子Q24をターンオフさせることができる。すなわち、パルストランスPTをハイサイドドライバとして利用することが可能となる。また、第23のスイッチング素子Q23を制御するために、第23のスイッチング素子Q23の制御端子と第3の信号出力端子OUT3とが接続され、接地端子GNDがGNDラインに接続されている。

【0060】

また、図20では省略しているが、第23のスイッチング素子Q23がオン状態の時に増加し、オフ状態の時に減少するようなランプ波を形成する回路が設けられ、帰還信号端子FB1に入力される帰還信号に重畳されている。

【0061】

この実施形態に係る発明は、上述した(a)、(b)の効果を有する。

【符号の説明】

【0062】

101、102…制御IC

103、104…ランプ波形成回路

L1…第1のインダクタ

L2…第2のインダクタ

L3…第3のインダクタ

L4…第4のインダクタ

L5…第5のインダクタ

L6…第6のインダクタ

C1…第1のキャパシタ

C2…第2のキャパシタ

C3…第3のキャパシタ

C4…第4のキャパシタ

C5…第5のキャパシタ

C6…第6のキャパシタ

C7…第7のキャパシタ

C8…第8のキャパシタ

C9…第9のキャパシタ

C10…第10のキャパシタ

C11…第11のキャパシタ

C12…第12のキャパシタ

C13…第13のキャパシタ

C14…第14のキャパシタ

C15…第15のキャパシタ

C16…第16のキャパシタ

C17…第17のキャパシタ

C18…第18のキャパシタ

C19…第19のキャパシタ

C20…第20のキャパシタ

C21…第21のキャパシタ

C22…第22のキャパシタ

C23…第23のキャパシタ

C24…第24のキャパシタ

C25…第25のキャパシタ

Ciss…スイッチング素子のゲート−ソース間容量

D1…第1のダイオード

D2…第2のダイオード

D3…第3のダイオード

D4…第4のダイオード

D5…第5のダイオード

D6…第6のダイオード

D7…第7のダイオード

D8…第8のダイオード

D9…第9のダイオード

D10…第10のダイオード

D11…第11のダイオード

D12…第12のダイオード

D13…第13のダイオード

D14…第14のダイオード

D15…第15のダイオード

D16…第16のダイオード

D17…第17のダイオード

D18…第18のダイオード

D19…第19のダイオード

D20…第20のダイオード

D21…第21のダイオード

D22…第22のダイオード

ZD1…第1のツェナーダイオード

ZD2…第2のツェナーダイオード

ZD3…第3のツェナーダイオード

Q1…第1のスイッチング素子

Q2…第2のスイッチング素子

Q3…第3のスイッチング素子

Q4…第4のスイッチング素子

Q5…第5のスイッチング素子

Q6…第6のスイッチング素子

Q7…第7のスイッチング素子

Q8…第8のスイッチング素子

Q9…第9のスイッチング素子

Q10…第10のスイッチング素子

Q11…第11のスイッチング素子

Q12…第12のスイッチング素子

Q13…第13のスイッチング素子

Q14…第14のスイッチング素子

Q15…第15のスイッチング素子

Q16…第16のスイッチング素子

Q17…第17のスイッチング素子

Q18…第18のスイッチング素子

Q19…第19のスイッチング素子

Q20…第20のスイッチング素子

Q21…第21のスイッチング素子

Q22…第22のスイッチング素子

Q23…第23のスイッチング素子

Q24…第24のスイッチング素子

Q25…第25のスイッチング素子

Q26…第26のスイッチング素子

S1…第1のスイッチ回路

S2…第2のスイッチ回路

S3…第3のスイッチ回路

S4…第4のスイッチ回路

S5…第5のスイッチ回路

S6…第6のスイッチ回路

S7…第7のスイッチ回路

S8…第8のスイッチ回路

S9…第9のスイッチ回路

S10…第10のスイッチ回路

R1…第1の抵抗

R2…第2の抵抗

R3…第3の抵抗

R4…第4の抵抗

R5…第5の抵抗

R6…第6の抵抗

R7…第7の抵抗

R8…第8の抵抗

R9…第9の抵抗

R10…第10の抵抗

R11…第11の抵抗

R12…第12の抵抗

R13…第13の抵抗

R14…第14の抵抗

R15…第15の抵抗

R16…第16の抵抗

R17…第17の抵抗

R18…第18の抵抗

R19…第19の抵抗

T…トランス

PT…パルストランス

Np1…第1の1次巻線

Np2…第2の1次巻線

Np3…第3の1次巻線

Ns1…第1の2次巻線

Ns2…第2の2次巻線

Vin…入力電圧

Vdet…巻線電圧検出端子

Vdr1…第1の直流電圧部

Vdr2…第2の直流電圧部

Vout…出力端子

Vref1…リファレンス電圧

OUT1…第1の出力信号端子

OUT2…第2の信号出力端子

OUT3…第3の信号出力端子

FB1…帰還信号入力端子

COMP1…コンパレータ

GND…グランド端子

【特許請求の範囲】

【請求項1】

所定の直流電圧が印加される第1の直流電圧部と、

第2の直流電圧部と、

基準電位に接続されるGND端子と、

第1のスイッチ回路S1と第2のスイッチ回路S2とからなる第1の直列回路と、

第3のスイッチ回路S3と第4のスイッチ回路S4とからなる第2の直列回路と、

該第1〜第4のスイッチ回路のオン/オフ動作を制御する制御部と、

前記第1のスイッチ回路S1と前記第2のスイッチ回路S2との接続点を外部に引き出すための第1の出力端子と、前記第3のスイッチ回路S3と前記第4のスイッチ回路S4の接続点を外部に引き出すための第2の出力端子と、を含む半導体集積回路であって、

前記第1の直列回路の一端は前記第1の直流電圧部Vdr1に接続され、

前記第2の直列回路の一端は前記第2の直流電圧部Vdr2に接続され、

前記第1の直列回路の他端と、前記第2の直列回路の他端が共に前記GND端子に対して接続され、

前記第1の出力端子と前記第2の出力端子との間にリアクタンス素子が接続され、

前記リアクタンス素子の両端電圧の変化を検出する巻線電圧検出手段(Vdet)と、

少なくとも前記第1のスイッチ回路S1がオン状態、かつ前記第2のスイッチ回路S2及び前記第3のスイッチ回路S3が共にオフ状態である時に、前記リアクタンス素子に正極性の電圧を印加し、もしくは前記第2のスイッチ回路(S2)がオン状態、かつ前記第1のスイッチ回路(S1)及び前記第4のスイッチ回路(S4)が共にオフ状態である時に、前記リアクタンス素子に負極性の電圧を印加することで、前記リアクタンス素子に励磁電流を流してパルス電圧を発生させ、該パルス電圧をエッジ信号として外部に送信すると共に、少なくとも前記第1のスイッチ回路S1及び前記第2のスイッチ回路S2が共にオフ状態である時に、前記リアクタンス素子に生じるパルス電圧を、前記巻線電圧検出端子によって検出することにより、外部からのエッジ信号を受信できるようにしたことを特徴とする半導体集積回路。

【請求項2】

前記半導体集積回路はさらに、前記第1の直流電圧部から入力される電圧を出力する第3の出力端子と、

該第3の出力端子に、電圧を出力するか否かを制御するサブドライバ回路と、を備え、

前記サブドライバ回路のターンオン及びターンオフ動作は前記制御部によって制御され、

前記制御部は、前記第2の出力端子に生じる方形波電圧と、前記第3の出力端子に生じる方形波電圧が、共に低レベルである期間を挟んで互いに相補的な関係になるように前記第1〜第4のスイッチ回路及び前記サブドライバ回路を制御することを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記半導体集積回路が1次側制御回路及び2次側制御回路にそれぞれ用いられた絶縁型スイッチング電源装置であって、

直流電源と、

少なくとも1組の1次巻線及び2次巻線を有するトランスと、

前記直流電源から供給される直流電圧を前記1次巻線に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、

前記2次巻線に接続される少なくとも1つの同期整流回路を含む整流回路と、該整流回路の出力を平滑する出力フィルタ回路と、を少なくとも備え、

少なくとも1次巻線と2次巻線を有し、1次側に配置された前記半導体集積回路に該1次巻線を、2次側に配置された前記半導体集積回路に該2次巻線が接続された信号伝送トランスをリアクタンス素子として用いて、

前記1次側に配置された半導体集積回路と、前記2次側に配置された半導体集積回路との間で、パルス信号を双方向に伝送し、前記電力スイッチ素子及び前記同期整流器の駆動タイミングを制御することを特徴とする絶縁型スイッチング電源装置。

【請求項4】

請求項1、もしくは請求項2に記載の半導体集積回路を制御回路に用い、

直流電源と、

少なくとも1つのインダクタンス素子と、

前記直流電源から供給される直流電圧を該インダクタンス素子に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、

少なくとも1つの同期整流器を含む整流回路と、

整流回路の出力を平滑する出力フィルタ回路と、を備える非絶縁型スイッチング電源装置であって、

前記電力スイッチ素子、もしくは前記同期整流器は電界効果トランジスタで構成されており、

該電界効果トランジスタのソース端子が該制御回路のグランド電位からフローティングされていて、該電界効果トランジスタのゲート−ソース間にエッジ信号から方形波信号への変換回路が接続され、

前記半導体集積回路からトランスを介して送信されるエッジ信号を前記変換回路にて変換された方形波信号で、該電界効果トランジスタが駆動されることを特徴とする非絶縁型スイッチング電源装置。

【請求項1】

所定の直流電圧が印加される第1の直流電圧部と、

第2の直流電圧部と、

基準電位に接続されるGND端子と、

第1のスイッチ回路S1と第2のスイッチ回路S2とからなる第1の直列回路と、

第3のスイッチ回路S3と第4のスイッチ回路S4とからなる第2の直列回路と、

該第1〜第4のスイッチ回路のオン/オフ動作を制御する制御部と、

前記第1のスイッチ回路S1と前記第2のスイッチ回路S2との接続点を外部に引き出すための第1の出力端子と、前記第3のスイッチ回路S3と前記第4のスイッチ回路S4の接続点を外部に引き出すための第2の出力端子と、を含む半導体集積回路であって、

前記第1の直列回路の一端は前記第1の直流電圧部Vdr1に接続され、

前記第2の直列回路の一端は前記第2の直流電圧部Vdr2に接続され、

前記第1の直列回路の他端と、前記第2の直列回路の他端が共に前記GND端子に対して接続され、

前記第1の出力端子と前記第2の出力端子との間にリアクタンス素子が接続され、

前記リアクタンス素子の両端電圧の変化を検出する巻線電圧検出手段(Vdet)と、

少なくとも前記第1のスイッチ回路S1がオン状態、かつ前記第2のスイッチ回路S2及び前記第3のスイッチ回路S3が共にオフ状態である時に、前記リアクタンス素子に正極性の電圧を印加し、もしくは前記第2のスイッチ回路(S2)がオン状態、かつ前記第1のスイッチ回路(S1)及び前記第4のスイッチ回路(S4)が共にオフ状態である時に、前記リアクタンス素子に負極性の電圧を印加することで、前記リアクタンス素子に励磁電流を流してパルス電圧を発生させ、該パルス電圧をエッジ信号として外部に送信すると共に、少なくとも前記第1のスイッチ回路S1及び前記第2のスイッチ回路S2が共にオフ状態である時に、前記リアクタンス素子に生じるパルス電圧を、前記巻線電圧検出端子によって検出することにより、外部からのエッジ信号を受信できるようにしたことを特徴とする半導体集積回路。

【請求項2】

前記半導体集積回路はさらに、前記第1の直流電圧部から入力される電圧を出力する第3の出力端子と、

該第3の出力端子に、電圧を出力するか否かを制御するサブドライバ回路と、を備え、

前記サブドライバ回路のターンオン及びターンオフ動作は前記制御部によって制御され、

前記制御部は、前記第2の出力端子に生じる方形波電圧と、前記第3の出力端子に生じる方形波電圧が、共に低レベルである期間を挟んで互いに相補的な関係になるように前記第1〜第4のスイッチ回路及び前記サブドライバ回路を制御することを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記半導体集積回路が1次側制御回路及び2次側制御回路にそれぞれ用いられた絶縁型スイッチング電源装置であって、

直流電源と、

少なくとも1組の1次巻線及び2次巻線を有するトランスと、

前記直流電源から供給される直流電圧を前記1次巻線に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、

前記2次巻線に接続される少なくとも1つの同期整流回路を含む整流回路と、該整流回路の出力を平滑する出力フィルタ回路と、を少なくとも備え、

少なくとも1次巻線と2次巻線を有し、1次側に配置された前記半導体集積回路に該1次巻線を、2次側に配置された前記半導体集積回路に該2次巻線が接続された信号伝送トランスをリアクタンス素子として用いて、

前記1次側に配置された半導体集積回路と、前記2次側に配置された半導体集積回路との間で、パルス信号を双方向に伝送し、前記電力スイッチ素子及び前記同期整流器の駆動タイミングを制御することを特徴とする絶縁型スイッチング電源装置。

【請求項4】

請求項1、もしくは請求項2に記載の半導体集積回路を制御回路に用い、

直流電源と、

少なくとも1つのインダクタンス素子と、

前記直流電源から供給される直流電圧を該インダクタンス素子に印加させるか否かを制御する少なくとも1つの電力スイッチ素子と、

少なくとも1つの同期整流器を含む整流回路と、

整流回路の出力を平滑する出力フィルタ回路と、を備える非絶縁型スイッチング電源装置であって、

前記電力スイッチ素子、もしくは前記同期整流器は電界効果トランジスタで構成されており、

該電界効果トランジスタのソース端子が該制御回路のグランド電位からフローティングされていて、該電界効果トランジスタのゲート−ソース間にエッジ信号から方形波信号への変換回路が接続され、

前記半導体集積回路からトランスを介して送信されるエッジ信号を前記変換回路にて変換された方形波信号で、該電界効果トランジスタが駆動されることを特徴とする非絶縁型スイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2011−223726(P2011−223726A)

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願番号】特願2010−89578(P2010−89578)

【出願日】平成22年4月8日(2010.4.8)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願日】平成22年4月8日(2010.4.8)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]