半導体集積回路装置、制御記憶装置の制御方法及びプログラム

【課題】ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にする。

【解決手段】エラー検出部22は、読み出し制御部21が通常の運用時における制御装置3の動作を規定する通常運用データを冗長メモリ11,12から読み出す前に、通常運用データを格納するブロックに対してチェック処理を行う。当該チェック処理によるエラー情報はエラー情報保持部13に保持させる。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、エラーが検出されたブロックに冗長構成的に対応する健全なブロックが存在するか否かを判定し、健全なブロックが存在する場合には、通常運用データの読み出しを行う。

【解決手段】エラー検出部22は、読み出し制御部21が通常の運用時における制御装置3の動作を規定する通常運用データを冗長メモリ11,12から読み出す前に、通常運用データを格納するブロックに対してチェック処理を行う。当該チェック処理によるエラー情報はエラー情報保持部13に保持させる。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、エラーが検出されたブロックに冗長構成的に対応する健全なブロックが存在するか否かを判定し、健全なブロックが存在する場合には、通常運用データの読み出しを行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロコード等を格納する制御記憶装置を備える半導体集積回路装置に関し、特に冗長化された制御記憶装置の制御に関するものである。

【背景技術】

【0002】

図4は、従来の制御記憶装置101の構成及び動作を模式的に示している。制御記憶装置101は、冗長メモリA201及び冗長メモリB202を備えている。両冗長メモリ201,202には、プロセッサの一部を構成する制御装置を制御するファームウェア等が格納される。両冗長メモリ201,202の記憶領域は、複数のブロックから構成され、上記ファームウェア等のデータは、各ブロックに分割された状態で格納される。

【0003】

図中、データエントリA1〜An〜,B1〜Bn〜は、各ブロックに付された識別情報である。両冗長メモリ201,202は、同一のブロック構成を有している。本例においては、データエントリA1,A2,〜,An,〜とデータエントリB1,B2,〜,Bn,〜とが、それぞれ冗長構成的に対応している。

【0004】

冗長メモリA201及び冗長メモリB202に格納されるファームウェアには、制御装置の通常の運用時における動作を規定するデータ(通常運用データ)、起動時の動作のみを規定するデータ等、様々なものが含まれる。このような冗長メモリ201,202に格納されるデータは、通常、制御装置に読み出される前にその有効性がチェックされ、エラーのあるデータは制御装置に読み出されないようになされている。

【0005】

上記チェック処理は、ハードウェア(制御記憶装置101)自身がチェック機構を持たない場合には、ファームフェアにより制御装置を介して行われる。このファームウェアによるチェック処理としては、通常運用データの読み出しを開始する前に、一度だけチェックサムにより行う方法等がある。両冗長メモリ201,202に使用される記憶媒体は、通常、アクセス速度が遅い不揮発性メモリであるため、常時チェックや演算負荷の大きいチェック処理は不向きである。

【0006】

図5は、上記のような制御記憶装置101の動作を例示している。先ず、冗長メモリA201の各ブロックを昇順にチェックし(S101)、エラーがあるか否かを判定する(S102)。ステップS102において、エラーがないと判定された場合(N)には、当該チェック処理の対象となった冗長メモリA201を使用可能と判定し(S105)、通常の運用(通常運用データの読み出し等)を開始する(S106)。

【0007】

一方、ステップS102において、エラーがあると判定された場合(Y)には、当該チェック処理の対象を冗長メモリB202に切り替え(S103)、エラーがあるか否かを判定する(S104)。ステップS104において、エラーがないと判定された場合(N)には、当該チェック処理の対象となった冗長メモリB202を使用可能と判定し(S105)、通常の運用を開始する(S106)。一方、ステップS104において、エラーがあると判定された場合(Y)には、冗長メモリA201及び冗長メモリB202を共に使用不可能と判定し(S107)、運用を中止する(S108)。

【0008】

また、他の先行技術として、下記特許文献1及び特許文献2が開示されている。特許文献1に開示される記憶部の冗長化方法は、記憶部への書き込みを制御する制御部に異常が生じた場合でも両系の記憶部(0系記憶部と1系記憶部)の既存データ(正常データ)が同時に破壊されないようにすることを課題とするものであり、ブロック単位で冗長化された両記憶部に交互にデータを書き込むことにより、両系記憶部に対して同一のタイミングでデータが書き込まれないようにするものである。当該方法においては、各ブロックにユーザデータを書き込む際に、CRC(Cyclic Redundancy Check)等の検査が行われ、ブロック毎にデータの正常性を示す誤り検出情報が書き込まれる(同文献段落0033−0036等参照)。

【0009】

特許文献2に係るディスクアレイ装置は、データを格納する複数のディスク装置、冗長情報として例えばパリティを格納する1台のディスク装置、及び予備機として待機状態にある少なくとも1台のディスク装置を備えるものである。データ記録用又はパリティ記録用のディスク装置に故障が生ずると、予備のディスク装置が故障したディスク装置の代わりに割り当てられてデータの修復が行われ、予備のディスク装置が本来のデータ記録用ディスク装置として運用される。これにより、故障が修復した段階で予備のディスク装置からデータを書き戻す必要がなくなり、予備のディスク装置に対するデータ修復が完了した段階で通常の処理に戻ることができるとされている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平9−263026号公報

【特許文献2】特開平6−119125号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上記図4,5に係る制御記憶装置101においては、上記チェック処理により例えば冗長メモリA201のデータエントリA1と冗長メモリB202のデータエントリBnとにエラーが検出された場合には、両冗長メモリ201,202が使用不可能となる(S107)。しかしながら、両冗長メモリ201,202のブロック構成においては、データエントリA1とデータエントリB1とが対応し、データエントリAnとデータエントリBnとが対応している。従って、データエントリA1に替わってデータエントリB1を利用すると共に、データエントリBnに替わってデータエントリAnを利用することにより、通常の運用を行うことが可能である。このように、上記のような制御記憶装置101は、自らが備える冗長機能を十分に発揮できないものであった。

【0012】

また、特許文献1に係る方法においては、CRC等のチェック処理がユーザデータの書き込みの際に行われる。しかしながら、上記のような通常運用データの読み出しに先立って行われるチェック処理については、如何なる手段を講じるのか不明である。従って、制御記憶装置自体にエラーチェック機構を備えることが必須になるものと予想される。

【0013】

そこで、本発明は、ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にすることを課題とする。

【課題を解決するための手段】

【0014】

本発明の第1の態様は、ファームウェアを格納する制御記憶装置と、前記ファームウェアにより制御される制御装置とを備える半導体集積回路装置であって、前記制御記憶装置は、前記ファームウェアを複数のブロックに分割して格納し、前記ブロック単位の冗長性を有する複数の冗長メモリと、前記各ブロックに格納されたデータの有効性を示すエラー情報を前記ブロック毎に保持するエラー情報保持手段とを備え、前記制御装置は、前記各ブロックに格納されたデータの読み出しを制御する読み出し制御手段と、前記各ブロックに格納されたデータの有効性を判定し、前記エラー情報を生成するチェック処理を行うエラー検出手段とを備え、前記エラー検出手段は、前記読み出し制御手段が通常の運用時における前記制御装置の動作を規定する通常運用データを読み出す前に、前記通常運用データを格納する前記ブロックに対して前記チェック処理を行い、当該チェック処理により取得された前記エラー情報を前記エラー情報保持手段に保持させ、前記読み出し制御手段は、前記エラー情報保持手段に保持された前記エラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出しを行うものである。

【0015】

本発明の第2の態様は、ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御方法であって、通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出すステップと、前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定するステップと、前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持するステップと、前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行うステップとを備えるものである。

【0016】

本発明の第3の態様は、ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御プログラムであって、前記制御装置に、通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出す処理と、前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定する処理と、前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持する処理と、前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行う処理とを実行させるものである。

【発明の効果】

【0017】

本発明によれば、冗長メモリから通常運用データが読み出される前に、当該通常運用データを格納する冗長メモリの各ブロックに対してチェック処理が行われ、当該チェック処理の結果がブロック毎に設けられたエラー情報保持部に保持され、当該保持されたエラー情報に応じて通常運用データの読み出しが行われる。これにより、複数の冗長メモリにそれぞれエラーブロックが存在する場合であっても、ブロック単位で読み取り先の転換が可能な状況であれば、運用を続行することが可能となる。

【0018】

また、上記エラー情報保持部に保持されたエラー情報は、通常運用データの読み出し動作を実行するファームウェアにより読み取られるため、上記のようなエラーブロックの転換処理を当該ファームウェアにより行うことが可能となる。これにより、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても、制御装置を制御するファームウェアの調整により対処が可能となる。

【図面の簡単な説明】

【0019】

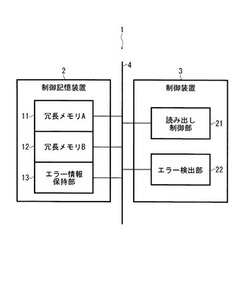

【図1】本発明の実施の形態1に係る半導体集積回路装置の機能的な構成を示す図である。

【図2】実施の形態1に係る制御記憶装置の構成及び動作を模式的に示す図である。

【図3】実施の形態1に係る制御記憶装置における処理の流れを示すフローチャートである。

【図4】従来の制御記憶装置の構成及び動作を模式的に示す図である。

【図5】従来の制御記憶装置における処理の流れを示すフローチャートである。

【発明を実施するための形態】

【0020】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。図1は、実施の形態1に係る半導体集積回路装置1の機能的な構成を示している。半導体集積回路装置1は、制御記憶装置2及び制御装置3を有し、いわゆるプロセッサ等に相当するものである。制御記憶装置2、制御装置3、入出力装置(図示せず)等は、バス4を介して接続されている。

【0021】

制御記憶装置2は、マスクROM、フラッシュメモリ等の不揮発性メモリにより構成され、冗長メモリA11、冗長メモリB12、及びエラー情報保持部13を有する。両冗長メモリ11,12は、制御装置3の動作を規定する各種データ(マイクロコードからなるファームウェア)を格納する。両冗長メモリ11,12の記憶領域は、複数のブロックに分割され、上記データは各ブロックに分割されて格納される。両冗長メモリ11,12のブロック構成は同一である。即ち、両冗長メモリ11,12は、ブロック単位で冗長化されている。

【0022】

エラー情報保持部13は、各ブロックに対応して設けられた記憶領域であり、各ブロック内のデータが有効であるか否かを示すエラー情報を保持する。

【0023】

制御装置3は、ファームウェアに基づいて各種演算処理を実行するハードウェアであり、読み出し制御部21及びエラー検出部22として機能する。

【0024】

読み出し制御部21は、冗長メモリA11又は冗長メモリB12から、制御装置3が通常の運用時に行う動作を規定するデータ(通常運用データ)の読み出しを制御する。当該読み出し動作は、通常運用データとは異なる(関連するものを含む)ファームウェアにより実行される。

【0025】

エラー検出部22は、冗長メモリA11及び冗長メモリB12に格納されているデータについて、ブロック毎にエラーの存否を検出するチェック処理を実行する。チェック処理としては、チェックサム等が好適である。チェック処理は、読み出し制御部21が通常運用データの読み出しを開始する前に実行される。チェック処理により取得されたエラー情報は、エラー情報保持部13に保持される。エラー情報保持部13に保持されたエラー情報は、通常運用データの読み出しを行うファームウェアにより読み取り可能なものである。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、通常運用データの読み出し方を決定する。

【0026】

図2は、制御記憶装置2の構成及び動作を模式的に示している。冗長メモリA11及び冗長メモリB12の記憶領域は、複数のブロック31に分割されている。図中、データエントリA1〜An〜,B1〜Bn〜は、各ブロック31に付された識別情報である。両冗長メモリ11,12は、同一のブロック構成を有している(又は含んでいる)。即ち、データエントリA1,A2,〜,An,〜とデータエントリB1,B2,〜,Bn,〜とが、それぞれ冗長構成的に対応している。

【0027】

図2中、矢印51は、エラー検出部22(図1参照)による各ブロック31に対するチェック処理を概念的に示している。当該チェック処理は、冗長メモリA11の先頭のデータエントリA1から昇順に最後のデータエントリまで行われた後、冗長メモリB12の先頭のデータエントリB1から昇順に最後のデータエントリまで行われる。この時、途中でエラーが検出されたか否かに関わらず、上記矢印51で示す流れが保たれる。本例では、データエントリA1とデータエントリBnとでエラーが検出されている。

【0028】

各ブロック31には、上記エラー情報保持部13(図1参照)としてのエラービットフィールド41が設けられている。エラービットフィールド41には、対応するブロック31(データエントリ)にエラーが検出された場合には1、エラーが検出されなかった場合には0が入力される。これらのエラービットフィールド41に保持される情報は、通常運用データの読み出しを行うファームウェアにより読み取り可能である。本例においては、データエントリA1,Bnにエラーが検出されているため、これらに対応するエラービットフィールド41に1が入力され、その他のエラービットフィールド41には0が入力されている。

【0029】

上記チェック処理及びエラービットフィールド41への書き込みは、読み出し制御部21(図1参照)が通常運用データの読み出しを開始する前に行われる。読み出し制御部21は、エラービットフィールド41を参照して通常運用データの読み出し方を決定する。本例においては、データエントリA1,Bnのエラービットフィールド41に1が記載され、データエントリA1に対応するデータエントリB1のエラービットフィールド41には0が記載され、データエントリBnに対応するデータエントリAnのエラービットフィールド41には0が記載されている。従って、読み出し制御部21は、矢印52が示すように、データエントリA1に替えてデータエントリB1からデータを読み出すと共に、矢印53が示すように、データエントリBnに替えてデータエントリAnからデータを読み出す。これにより、冗長メモリA11及び冗長メモリB12の両方にエラーブロックがある場合であっても、エラーブロックに対応するブロックにエラーがなければ、正常な運用が可能となる。

【0030】

図3は、上記制御記憶装置2における処理の流れを示している。読み出し制御部21による通常運用データの読み出しに先立ち、エラー検出部22による冗長メモリA11及び冗長メモリB12のチェックが行われる。

【0031】

先ず、冗長メモリA11の各データエントリに対して上述のように昇順にチェックを行い(S1)、エラーの有無を判定する(S2)。ステップS2において、エラーが発生したと判定された場合(Y)には、対応するエラービットフィールドに1をセットする(S3)。その後、冗長メモリA11の全てのデータエントリについてチェックが終了したか否かを判定し(S4)、終了していない場合(N)には、ステップS1に戻る。また、ステップS2において、エラーが発生していないと判定された場合(N)には、ステップS4へ移行する。

【0032】

ステップS4において、冗長メモリA11の全てのデータエントリについてチェックが終了したと判定された場合(Y)には、冗長メモリB12のチェックを開始し(S5)、各データエントリについてエラーの有無を判定する(S6)。ステップS6において、エラーが発生したと判定された場合(Y)には、対応するエラービットフィールド41に1をセットする(S7)。その後、冗長メモリB12の全てのデータエントリについてチェックが終了したか否かを判定し(S8)、終了していない場合(N)には、ステップS5に戻る。また、ステップS6において、エラーが発生していないと判定された場合(N)には、ステップS8へ移行する。

【0033】

ステップS8において、冗長メモリB12の全てのデータエントリについてチェックが終了したと判定された場合(Y)には、読み出し制御部21は、全てのエラービットフィールド41の中に1が存在するか否かを判定し(S9)、1が存在しない場合(N)には、いずれの冗長メモリ11,12も使用可能であると判定し(S10)、任意の冗長メモリ(通常は冗長メモリA11)により通常運用データの読み出しを開始する(S11)。

【0034】

一方、ステップS9において、エラービットフィールド41に1が存在すると判定された場合(Y)には、当該1がセットされたデータエントリに対応するデータエントリのエラービットが1であるか否かを判定する(S12)。ステップS12において、当該対応するエラービットが1でない場合(N)には、当該エラービットが1でないデータエントリをデータの読み出し先に転換し(図2中矢印52,53参照)(S13)、読み出し先を両方の冗長メモリ11,12の間で適宜切り替えることにより使用可能であると判定し(S10)、通常運用データの読み出しを開始する(S11)。

【0035】

一方、ステップS12において、1がセットされたデータエントリに対応するデータエントリのエラービット1である場合(Y)には、いずれの冗長メモリ11,12も使用不可能と判定し(S14)、運用を中止する(S15)。

【0036】

以上のように、本実施の形態に係る半導体集積回路装置1においては、冗長メモリ11,12から通常運用データが読み出される前に、冗長メモリ11,12の各ブロック31に対してチェック処理が行われ、当該チェック処理の結果がブロック31毎に保持され、当該保持されたエラー情報に応じて通常運用データの読み出しが行われる。これにより、両冗長メモリ11,12にそれぞれエラーブロックが存在する場合であっても、ブロック(データエントリ)単位で読み取り先の転換が可能な状況であれば、運用を続行することができる。

【0037】

また、上記エラービットフィールド41に保持されたエラー情報は、通常運用データの読み出し動作を実行するファームウェアにより読み取られるため、上記のようなエラーブロックの転換処理を当該ファームウェアにより行うことが可能となる。従って、制御記憶装置2自体にエラーチェック機構が備えられていない場合であっても、制御装置3を制御するファームウェアの調整により対処することが可能となる。

【0038】

尚、本発明は上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。例えば、上記実施の形態においては、冗長メモリの数が2つである場合を示したが、3つ以上であっても、本願発明の趣旨に基づいて同様の効果を有する半導体集積回路装置を構成することが可能である。

【符号の説明】

【0039】

1 半導体集積回路装置

2 制御記憶装置

3 制御装置

4 バス

11 冗長メモリA

12 冗長メモリB

13 エラー情報保持部

21 読み出し制御部

22 エラー検出部

31 ブロック

41 エラービットフィールド(エラー情報保持部)

【技術分野】

【0001】

本発明は、マイクロコード等を格納する制御記憶装置を備える半導体集積回路装置に関し、特に冗長化された制御記憶装置の制御に関するものである。

【背景技術】

【0002】

図4は、従来の制御記憶装置101の構成及び動作を模式的に示している。制御記憶装置101は、冗長メモリA201及び冗長メモリB202を備えている。両冗長メモリ201,202には、プロセッサの一部を構成する制御装置を制御するファームウェア等が格納される。両冗長メモリ201,202の記憶領域は、複数のブロックから構成され、上記ファームウェア等のデータは、各ブロックに分割された状態で格納される。

【0003】

図中、データエントリA1〜An〜,B1〜Bn〜は、各ブロックに付された識別情報である。両冗長メモリ201,202は、同一のブロック構成を有している。本例においては、データエントリA1,A2,〜,An,〜とデータエントリB1,B2,〜,Bn,〜とが、それぞれ冗長構成的に対応している。

【0004】

冗長メモリA201及び冗長メモリB202に格納されるファームウェアには、制御装置の通常の運用時における動作を規定するデータ(通常運用データ)、起動時の動作のみを規定するデータ等、様々なものが含まれる。このような冗長メモリ201,202に格納されるデータは、通常、制御装置に読み出される前にその有効性がチェックされ、エラーのあるデータは制御装置に読み出されないようになされている。

【0005】

上記チェック処理は、ハードウェア(制御記憶装置101)自身がチェック機構を持たない場合には、ファームフェアにより制御装置を介して行われる。このファームウェアによるチェック処理としては、通常運用データの読み出しを開始する前に、一度だけチェックサムにより行う方法等がある。両冗長メモリ201,202に使用される記憶媒体は、通常、アクセス速度が遅い不揮発性メモリであるため、常時チェックや演算負荷の大きいチェック処理は不向きである。

【0006】

図5は、上記のような制御記憶装置101の動作を例示している。先ず、冗長メモリA201の各ブロックを昇順にチェックし(S101)、エラーがあるか否かを判定する(S102)。ステップS102において、エラーがないと判定された場合(N)には、当該チェック処理の対象となった冗長メモリA201を使用可能と判定し(S105)、通常の運用(通常運用データの読み出し等)を開始する(S106)。

【0007】

一方、ステップS102において、エラーがあると判定された場合(Y)には、当該チェック処理の対象を冗長メモリB202に切り替え(S103)、エラーがあるか否かを判定する(S104)。ステップS104において、エラーがないと判定された場合(N)には、当該チェック処理の対象となった冗長メモリB202を使用可能と判定し(S105)、通常の運用を開始する(S106)。一方、ステップS104において、エラーがあると判定された場合(Y)には、冗長メモリA201及び冗長メモリB202を共に使用不可能と判定し(S107)、運用を中止する(S108)。

【0008】

また、他の先行技術として、下記特許文献1及び特許文献2が開示されている。特許文献1に開示される記憶部の冗長化方法は、記憶部への書き込みを制御する制御部に異常が生じた場合でも両系の記憶部(0系記憶部と1系記憶部)の既存データ(正常データ)が同時に破壊されないようにすることを課題とするものであり、ブロック単位で冗長化された両記憶部に交互にデータを書き込むことにより、両系記憶部に対して同一のタイミングでデータが書き込まれないようにするものである。当該方法においては、各ブロックにユーザデータを書き込む際に、CRC(Cyclic Redundancy Check)等の検査が行われ、ブロック毎にデータの正常性を示す誤り検出情報が書き込まれる(同文献段落0033−0036等参照)。

【0009】

特許文献2に係るディスクアレイ装置は、データを格納する複数のディスク装置、冗長情報として例えばパリティを格納する1台のディスク装置、及び予備機として待機状態にある少なくとも1台のディスク装置を備えるものである。データ記録用又はパリティ記録用のディスク装置に故障が生ずると、予備のディスク装置が故障したディスク装置の代わりに割り当てられてデータの修復が行われ、予備のディスク装置が本来のデータ記録用ディスク装置として運用される。これにより、故障が修復した段階で予備のディスク装置からデータを書き戻す必要がなくなり、予備のディスク装置に対するデータ修復が完了した段階で通常の処理に戻ることができるとされている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平9−263026号公報

【特許文献2】特開平6−119125号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上記図4,5に係る制御記憶装置101においては、上記チェック処理により例えば冗長メモリA201のデータエントリA1と冗長メモリB202のデータエントリBnとにエラーが検出された場合には、両冗長メモリ201,202が使用不可能となる(S107)。しかしながら、両冗長メモリ201,202のブロック構成においては、データエントリA1とデータエントリB1とが対応し、データエントリAnとデータエントリBnとが対応している。従って、データエントリA1に替わってデータエントリB1を利用すると共に、データエントリBnに替わってデータエントリAnを利用することにより、通常の運用を行うことが可能である。このように、上記のような制御記憶装置101は、自らが備える冗長機能を十分に発揮できないものであった。

【0012】

また、特許文献1に係る方法においては、CRC等のチェック処理がユーザデータの書き込みの際に行われる。しかしながら、上記のような通常運用データの読み出しに先立って行われるチェック処理については、如何なる手段を講じるのか不明である。従って、制御記憶装置自体にエラーチェック機構を備えることが必須になるものと予想される。

【0013】

そこで、本発明は、ブロック単位で構築された冗長構成の利点を最大限利用すると共に、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても対処可能にすることを課題とする。

【課題を解決するための手段】

【0014】

本発明の第1の態様は、ファームウェアを格納する制御記憶装置と、前記ファームウェアにより制御される制御装置とを備える半導体集積回路装置であって、前記制御記憶装置は、前記ファームウェアを複数のブロックに分割して格納し、前記ブロック単位の冗長性を有する複数の冗長メモリと、前記各ブロックに格納されたデータの有効性を示すエラー情報を前記ブロック毎に保持するエラー情報保持手段とを備え、前記制御装置は、前記各ブロックに格納されたデータの読み出しを制御する読み出し制御手段と、前記各ブロックに格納されたデータの有効性を判定し、前記エラー情報を生成するチェック処理を行うエラー検出手段とを備え、前記エラー検出手段は、前記読み出し制御手段が通常の運用時における前記制御装置の動作を規定する通常運用データを読み出す前に、前記通常運用データを格納する前記ブロックに対して前記チェック処理を行い、当該チェック処理により取得された前記エラー情報を前記エラー情報保持手段に保持させ、前記読み出し制御手段は、前記エラー情報保持手段に保持された前記エラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出しを行うものである。

【0015】

本発明の第2の態様は、ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御方法であって、通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出すステップと、前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定するステップと、前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持するステップと、前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行うステップとを備えるものである。

【0016】

本発明の第3の態様は、ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御プログラムであって、前記制御装置に、通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出す処理と、前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定する処理と、前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持する処理と、前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行う処理とを実行させるものである。

【発明の効果】

【0017】

本発明によれば、冗長メモリから通常運用データが読み出される前に、当該通常運用データを格納する冗長メモリの各ブロックに対してチェック処理が行われ、当該チェック処理の結果がブロック毎に設けられたエラー情報保持部に保持され、当該保持されたエラー情報に応じて通常運用データの読み出しが行われる。これにより、複数の冗長メモリにそれぞれエラーブロックが存在する場合であっても、ブロック単位で読み取り先の転換が可能な状況であれば、運用を続行することが可能となる。

【0018】

また、上記エラー情報保持部に保持されたエラー情報は、通常運用データの読み出し動作を実行するファームウェアにより読み取られるため、上記のようなエラーブロックの転換処理を当該ファームウェアにより行うことが可能となる。これにより、制御記憶装置自体にエラーチェック機構が備えられていない場合であっても、制御装置を制御するファームウェアの調整により対処が可能となる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1に係る半導体集積回路装置の機能的な構成を示す図である。

【図2】実施の形態1に係る制御記憶装置の構成及び動作を模式的に示す図である。

【図3】実施の形態1に係る制御記憶装置における処理の流れを示すフローチャートである。

【図4】従来の制御記憶装置の構成及び動作を模式的に示す図である。

【図5】従来の制御記憶装置における処理の流れを示すフローチャートである。

【発明を実施するための形態】

【0020】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。図1は、実施の形態1に係る半導体集積回路装置1の機能的な構成を示している。半導体集積回路装置1は、制御記憶装置2及び制御装置3を有し、いわゆるプロセッサ等に相当するものである。制御記憶装置2、制御装置3、入出力装置(図示せず)等は、バス4を介して接続されている。

【0021】

制御記憶装置2は、マスクROM、フラッシュメモリ等の不揮発性メモリにより構成され、冗長メモリA11、冗長メモリB12、及びエラー情報保持部13を有する。両冗長メモリ11,12は、制御装置3の動作を規定する各種データ(マイクロコードからなるファームウェア)を格納する。両冗長メモリ11,12の記憶領域は、複数のブロックに分割され、上記データは各ブロックに分割されて格納される。両冗長メモリ11,12のブロック構成は同一である。即ち、両冗長メモリ11,12は、ブロック単位で冗長化されている。

【0022】

エラー情報保持部13は、各ブロックに対応して設けられた記憶領域であり、各ブロック内のデータが有効であるか否かを示すエラー情報を保持する。

【0023】

制御装置3は、ファームウェアに基づいて各種演算処理を実行するハードウェアであり、読み出し制御部21及びエラー検出部22として機能する。

【0024】

読み出し制御部21は、冗長メモリA11又は冗長メモリB12から、制御装置3が通常の運用時に行う動作を規定するデータ(通常運用データ)の読み出しを制御する。当該読み出し動作は、通常運用データとは異なる(関連するものを含む)ファームウェアにより実行される。

【0025】

エラー検出部22は、冗長メモリA11及び冗長メモリB12に格納されているデータについて、ブロック毎にエラーの存否を検出するチェック処理を実行する。チェック処理としては、チェックサム等が好適である。チェック処理は、読み出し制御部21が通常運用データの読み出しを開始する前に実行される。チェック処理により取得されたエラー情報は、エラー情報保持部13に保持される。エラー情報保持部13に保持されたエラー情報は、通常運用データの読み出しを行うファームウェアにより読み取り可能なものである。読み出し制御部21は、エラー情報保持部13に保持されたエラー情報に基づいて、通常運用データの読み出し方を決定する。

【0026】

図2は、制御記憶装置2の構成及び動作を模式的に示している。冗長メモリA11及び冗長メモリB12の記憶領域は、複数のブロック31に分割されている。図中、データエントリA1〜An〜,B1〜Bn〜は、各ブロック31に付された識別情報である。両冗長メモリ11,12は、同一のブロック構成を有している(又は含んでいる)。即ち、データエントリA1,A2,〜,An,〜とデータエントリB1,B2,〜,Bn,〜とが、それぞれ冗長構成的に対応している。

【0027】

図2中、矢印51は、エラー検出部22(図1参照)による各ブロック31に対するチェック処理を概念的に示している。当該チェック処理は、冗長メモリA11の先頭のデータエントリA1から昇順に最後のデータエントリまで行われた後、冗長メモリB12の先頭のデータエントリB1から昇順に最後のデータエントリまで行われる。この時、途中でエラーが検出されたか否かに関わらず、上記矢印51で示す流れが保たれる。本例では、データエントリA1とデータエントリBnとでエラーが検出されている。

【0028】

各ブロック31には、上記エラー情報保持部13(図1参照)としてのエラービットフィールド41が設けられている。エラービットフィールド41には、対応するブロック31(データエントリ)にエラーが検出された場合には1、エラーが検出されなかった場合には0が入力される。これらのエラービットフィールド41に保持される情報は、通常運用データの読み出しを行うファームウェアにより読み取り可能である。本例においては、データエントリA1,Bnにエラーが検出されているため、これらに対応するエラービットフィールド41に1が入力され、その他のエラービットフィールド41には0が入力されている。

【0029】

上記チェック処理及びエラービットフィールド41への書き込みは、読み出し制御部21(図1参照)が通常運用データの読み出しを開始する前に行われる。読み出し制御部21は、エラービットフィールド41を参照して通常運用データの読み出し方を決定する。本例においては、データエントリA1,Bnのエラービットフィールド41に1が記載され、データエントリA1に対応するデータエントリB1のエラービットフィールド41には0が記載され、データエントリBnに対応するデータエントリAnのエラービットフィールド41には0が記載されている。従って、読み出し制御部21は、矢印52が示すように、データエントリA1に替えてデータエントリB1からデータを読み出すと共に、矢印53が示すように、データエントリBnに替えてデータエントリAnからデータを読み出す。これにより、冗長メモリA11及び冗長メモリB12の両方にエラーブロックがある場合であっても、エラーブロックに対応するブロックにエラーがなければ、正常な運用が可能となる。

【0030】

図3は、上記制御記憶装置2における処理の流れを示している。読み出し制御部21による通常運用データの読み出しに先立ち、エラー検出部22による冗長メモリA11及び冗長メモリB12のチェックが行われる。

【0031】

先ず、冗長メモリA11の各データエントリに対して上述のように昇順にチェックを行い(S1)、エラーの有無を判定する(S2)。ステップS2において、エラーが発生したと判定された場合(Y)には、対応するエラービットフィールドに1をセットする(S3)。その後、冗長メモリA11の全てのデータエントリについてチェックが終了したか否かを判定し(S4)、終了していない場合(N)には、ステップS1に戻る。また、ステップS2において、エラーが発生していないと判定された場合(N)には、ステップS4へ移行する。

【0032】

ステップS4において、冗長メモリA11の全てのデータエントリについてチェックが終了したと判定された場合(Y)には、冗長メモリB12のチェックを開始し(S5)、各データエントリについてエラーの有無を判定する(S6)。ステップS6において、エラーが発生したと判定された場合(Y)には、対応するエラービットフィールド41に1をセットする(S7)。その後、冗長メモリB12の全てのデータエントリについてチェックが終了したか否かを判定し(S8)、終了していない場合(N)には、ステップS5に戻る。また、ステップS6において、エラーが発生していないと判定された場合(N)には、ステップS8へ移行する。

【0033】

ステップS8において、冗長メモリB12の全てのデータエントリについてチェックが終了したと判定された場合(Y)には、読み出し制御部21は、全てのエラービットフィールド41の中に1が存在するか否かを判定し(S9)、1が存在しない場合(N)には、いずれの冗長メモリ11,12も使用可能であると判定し(S10)、任意の冗長メモリ(通常は冗長メモリA11)により通常運用データの読み出しを開始する(S11)。

【0034】

一方、ステップS9において、エラービットフィールド41に1が存在すると判定された場合(Y)には、当該1がセットされたデータエントリに対応するデータエントリのエラービットが1であるか否かを判定する(S12)。ステップS12において、当該対応するエラービットが1でない場合(N)には、当該エラービットが1でないデータエントリをデータの読み出し先に転換し(図2中矢印52,53参照)(S13)、読み出し先を両方の冗長メモリ11,12の間で適宜切り替えることにより使用可能であると判定し(S10)、通常運用データの読み出しを開始する(S11)。

【0035】

一方、ステップS12において、1がセットされたデータエントリに対応するデータエントリのエラービット1である場合(Y)には、いずれの冗長メモリ11,12も使用不可能と判定し(S14)、運用を中止する(S15)。

【0036】

以上のように、本実施の形態に係る半導体集積回路装置1においては、冗長メモリ11,12から通常運用データが読み出される前に、冗長メモリ11,12の各ブロック31に対してチェック処理が行われ、当該チェック処理の結果がブロック31毎に保持され、当該保持されたエラー情報に応じて通常運用データの読み出しが行われる。これにより、両冗長メモリ11,12にそれぞれエラーブロックが存在する場合であっても、ブロック(データエントリ)単位で読み取り先の転換が可能な状況であれば、運用を続行することができる。

【0037】

また、上記エラービットフィールド41に保持されたエラー情報は、通常運用データの読み出し動作を実行するファームウェアにより読み取られるため、上記のようなエラーブロックの転換処理を当該ファームウェアにより行うことが可能となる。従って、制御記憶装置2自体にエラーチェック機構が備えられていない場合であっても、制御装置3を制御するファームウェアの調整により対処することが可能となる。

【0038】

尚、本発明は上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。例えば、上記実施の形態においては、冗長メモリの数が2つである場合を示したが、3つ以上であっても、本願発明の趣旨に基づいて同様の効果を有する半導体集積回路装置を構成することが可能である。

【符号の説明】

【0039】

1 半導体集積回路装置

2 制御記憶装置

3 制御装置

4 バス

11 冗長メモリA

12 冗長メモリB

13 エラー情報保持部

21 読み出し制御部

22 エラー検出部

31 ブロック

41 エラービットフィールド(エラー情報保持部)

【特許請求の範囲】

【請求項1】

ファームウェアを格納する制御記憶装置と、前記ファームウェアにより制御される制御装置とを備える半導体集積回路装置であって、

前記制御記憶装置は、

前記ファームウェアを複数のブロックに分割して格納し、前記ブロック単位の冗長性を有する複数の冗長メモリと、

前記各ブロックに格納されたデータの有効性を示すエラー情報を前記ブロック毎に保持するエラー情報保持手段と、

を備え、

前記制御装置は、

前記各ブロックに格納されたデータの読み出しを制御する読み出し制御手段と、

前記各ブロックに格納されたデータの有効性を判定し、前記エラー情報を生成するチェック処理を行うエラー検出手段と、

を備え、

前記エラー検出手段は、前記読み出し制御手段が通常の運用時における前記制御装置の動作を規定する通常運用データを読み出す前に、前記通常運用データを格納する前記ブロックに対して前記チェック処理を行い、当該チェック処理により取得された前記エラー情報を前記エラー情報保持手段に保持させ、

前記読み出し制御手段は、前記エラー情報保持手段に保持された前記エラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出しを行う、

半導体集積回路装置。

【請求項2】

前記通常運用データを読み出す前に行われる前記チェック処理は、当該処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項1に記載の半導体集積回路。

【請求項3】

ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御方法であって、

通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出すステップと、

前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定するステップと、

前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持するステップと、

前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行うステップと、

を備える制御記憶装置の制御方法。

【請求項4】

前記通常運用データを読み出す前に行われる前記有効性の判定は、当該判定処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項3に記載の制御記憶装置の制御方法。

【請求項5】

ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御プログラムであって、

前記制御装置に、

通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出す処理と、

前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定する処理と、

前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持する処理と、

前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行う処理と、

を実行させる制御記憶装置の制御プログラム。

【請求項6】

前記通常運用データを読み出す前に行われる前記有効性の判定は、当該判定処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項5に記載の制御記憶装置の制御プログラム。

【請求項1】

ファームウェアを格納する制御記憶装置と、前記ファームウェアにより制御される制御装置とを備える半導体集積回路装置であって、

前記制御記憶装置は、

前記ファームウェアを複数のブロックに分割して格納し、前記ブロック単位の冗長性を有する複数の冗長メモリと、

前記各ブロックに格納されたデータの有効性を示すエラー情報を前記ブロック毎に保持するエラー情報保持手段と、

を備え、

前記制御装置は、

前記各ブロックに格納されたデータの読み出しを制御する読み出し制御手段と、

前記各ブロックに格納されたデータの有効性を判定し、前記エラー情報を生成するチェック処理を行うエラー検出手段と、

を備え、

前記エラー検出手段は、前記読み出し制御手段が通常の運用時における前記制御装置の動作を規定する通常運用データを読み出す前に、前記通常運用データを格納する前記ブロックに対して前記チェック処理を行い、当該チェック処理により取得された前記エラー情報を前記エラー情報保持手段に保持させ、

前記読み出し制御手段は、前記エラー情報保持手段に保持された前記エラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出しを行う、

半導体集積回路装置。

【請求項2】

前記通常運用データを読み出す前に行われる前記チェック処理は、当該処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項1に記載の半導体集積回路。

【請求項3】

ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御方法であって、

通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出すステップと、

前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定するステップと、

前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持するステップと、

前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行うステップと、

を備える制御記憶装置の制御方法。

【請求項4】

前記通常運用データを読み出す前に行われる前記有効性の判定は、当該判定処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項3に記載の制御記憶装置の制御方法。

【請求項5】

ブロック単位の冗長性を有する複数の冗長メモリを備え、制御装置を制御するファームウェアを前記各ブロックに分割して格納する制御記憶装置の制御プログラムであって、

前記制御装置に、

通常の運用時における前記制御装置の動作を規定する通常運用データを、前記ブロックから前記制御装置へ読み出す処理と、

前記通常運用データを読み出す前に、前記ブロックに格納された前記通常運用データの有効性を判定する処理と、

前記有効性の判定結果を示す前記エラー情報を前記ブロック毎に保持する処理と、

前記保持されたエラー情報に基づいて、エラーが検出された前記ブロックに冗長構成的に対応する健全な前記ブロックが存在するか否かを判定し、当該健全なブロックが存在する場合には、前記通常運用データの読み出し行う処理と、

を実行させる制御記憶装置の制御プログラム。

【請求項6】

前記通常運用データを読み出す前に行われる前記有効性の判定は、当該判定処理の過程においてエラーが検出されるか否かに関わらず、全ての前記冗長メモリの前記ブロックに対して連続的に行われる、

請求項5に記載の制御記憶装置の制御プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−113783(P2012−113783A)

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願番号】特願2010−262152(P2010−262152)

【出願日】平成22年11月25日(2010.11.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願日】平成22年11月25日(2010.11.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]