半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はマルチレートのシリアルデータを受信するクロックデータ復元回路に関する物で、特にシリアライザ−デシリアライザ回路(Serdes)に好適なクロックデータ復元回路に関する。

【背景技術】

【0002】

近年、シリアルデータ転送は図1に示すような光通信(PON; Passive Optical Network)を始め、パーソナルコンピュータ(PC)やサーバのバックプレーン転送など様々な場所に使用されており、また扱われる情報量の増加に伴い更なる高速化が求められている。この高速シリアルデータ転送を実現するために、送られてくるシリアルデータから位相情報を抽出し、データに同期したクロックを生成するクロックデータ復元回路(CDR)が必要である。また、高速シリアルデータ転送に使われる規格は用途の違いなどから、GPONなど様々あり、それぞれ決められた転送レートがある。またEthernet(Ethernetは、富士ゼロックス株式会社の登録商標である。)を始め同様のプロトコルでも複数の転送レートをもつ規格もあり、規格をひとつのLSIで準拠する為には、マルチレートに対応したクロックデータ復元回路が必要である。

【0003】

特許文献1はクロックデータ復元回路を含むシリアライザ−デシリアライザ回路(Serdes)について示されている。この回路は基本的なクロックデータ復元回路を持ち、パラレル−シリアル変換回路、シリアル−パラレル変換回路、ファストイン ファストアウト回路(FIFO; First In First Out)を一体化することで、小面積、低消費電力を実現している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−36869号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図6は、特許文献1の図7に示されるシリアライザ−デシリアライザ回路(Serdes)に含まれるクロックデータ復元回路(CDR)を抜粋したものである。図6には、位相同期回路6101(PLL)、分周回路6103、インターポレータ回路6102(IP)、サンプリング回路6104(Spl)、クロックデータ復元回路コントロール回路6106(CDRctrl; CDR control)が含まれる。

【0006】

位相同期回路6101(PLL)で生成されたクロックを分周回路6103(DIV)で分周多相クロックに変換する。その多相クロックを使いインターポレータ回路6102(IP)でリカバリクロックを生成する。サンプリング回路6104(Spl)で入力データとリカバリクロックの比較を行う。その比較結果を受けCDRコントロール回路6106がインターポレータ回路6102の位相制御を行うことで入力データに対して最適なリカバリクロックを生成する。

【0007】

図6では、位相同期回路6101(PLL)とインターポレータ回路6102(IP)の間にある分周回路6103(DIV)の分周比を変更することでマルチレートに対応する。しかし、この方法ではインターポレータ回路6102(IP)の動作速度を入力データの転送レートに合わせて切り変える必要があり、非常に広い帯域を前記インターポレータ回路6102(IP)に持たせる必要がある。ところが、インターポレータ回路などのアナログ回路は帯域を広くすると、ジッタの増加や、回路面積の増大などといった問題を生じる。

【0008】

以上の点に鑑み、本発明では、インターポレータ回路の広帯域化をせずに、マルチレートのデータに対応したクロックデータ復元回路の実現することを課題とする。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。すなわち、位相同期回路(PLL)などのクロック源(PLL)から供給される多相クロックを元にインターポレータ回路(IP)で合成されたクロック(Compclk)を送られてくるデータの転送レートに合わせて分周回路(DIV)で分周し、入力データの取り込みに最適な周波数のリカバリクロック(Rclk)を生成する。このリカバリクロック(Rclk)と入力データの位相を位相比較回路(PhC)で位相比較し、シリアルデータの位相に対してクロックが遅れているか、進んでいるかを判定する。その位相判定結果(Sig1)をフィルタ回路(Fil)で最適化し、その結果を基にポインタ回路(Pt)がインターポレータ回路(IP)に生成クロックの位相を進ませるもしくは、遅らせる制御信号(Sig3)を送る。その制御信号(Sig3)を受けて、インターポレータ回路は生成クロックの位相を進めたり、遅らせたりすることで、マルチレートに対応したクロックデータ復元回路(CDR)を実現する。また、位相比較回路(PhC)、フィルタ回路(Fil)、ポインタ回路(Pt)に供給するクロックをそれぞれ別系統にし、(1)インターポレータ回路の合成クロック、(2)リカバリクロック、(3)インターポレータ回路の合成クロックの分周クロック、(4)リカバリクロックの分周クロックのいずれかを使うことでクロックデータ復元回路の追従特性を制御することができる。

【発明の効果】

【0010】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すると、以下のようである。すなわち、インターポレータ回路の広帯域化をせずに、マルチレートのデータに対応したクロックデータ復元回路の実現が可能となる。

【図面の簡単な説明】

【0011】

【図1】高速シリアル転送システムの例である。(a)光通信システムPON, (b)PC内部のCPU-HDD間を示した図。

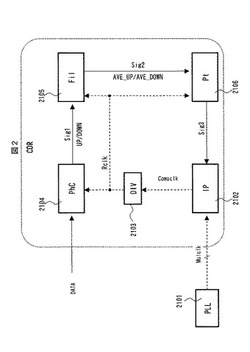

【図2】マルチレート対応クロックデータ復元回路の一例である。

【図3】マルチレート対応クロックデータ復元回路の一例である。

【図4】マルチレート対応クロックデータ復元回路の一例である。

【図5】マルチレート対応クロックデータ復元回路の一例である。

【図6】特許文献1の図7に示されるSerdes回路からクロックデータ復元回路を示したブロック図である。

【図7】マルチレート対応クロックデータ復元回路の入力データとリカバリクロックの波形を示した図である。(a) 入力データレート最速の時の波形, (b) 1/N動作時の波形(補正量T/Sの時), (c) 1/N動作時の波形(補正量N×T/Sの時), (d) 1/N動作時の期待値の波形。

【発明を実施するための形態】

【0012】

図1は、高速シリアル転送システムの例を示したものである。図1(a)は光通信ネットワークシステムであるパッシブオプティカルネットワーク(PON; Passive Optical Network)を示した図である。

【0013】

PONは複数の端末側送受信機であるONU1001〜1003(Optical Network Unit)と基地局側送受信機であるオプティカル ライン ターミナル1004(OLT; Optical Line Terminal)とそれらを繋ぐ光ファイバーで構成される。

【0014】

ONUは例えば各家庭にあるパーソナルコンピュータ(PC)に接続されOLTとのデータの送受信を行う通信装置である。

【0015】

OLTはインターネット供給会社等の基地局に配置され複数のONUと光ファイバーで接続されインターネットとONUとの間でデータの送受信を行う通信装置である。ONU-OLT間の通信ではギガビットポン(GPON)やギガビットイーサネットポン(イーサネットは、富士ゼロックス株式会社の登録商標である。)などの規格があり、それぞれ転送速度が異なっている。

【0016】

図1(b)はPC内部の中央演算処理装置(CPU)とハードディスクドライブ(HDD)間の通信を示した図である。中央演算処理装置(CPU)は記憶装置であるハードディスクドライブに蓄積したデータを必要に応じて読み出し、使用者の命令に従い演算処理を行い、演算結果を必要に応じてハードディスクドライブに書き込む半導体装置である。ハードディスクドライブ(HDD)は、PC等のデジタル機器に内蔵され、不揮発性の磁気記録ディスク、データの読み書きを行う磁気記録ヘッド、外部とデータのやり取りを行い磁気記録ヘッドを制御する制御回路から構成され、大容量のデータを保持する事ができる記憶装置である。CPU−HDD間の通信は所定の規格が適用されている。この規格ではジェネレーション1(G1)とジェネレーション2(G2)がありそれぞれ規定される転送レートが異なっているが、互換性が必要なため送受信回路はそれぞれジェネレーション1,2のデータを送受信する必要がある。

【0017】

図1(a),(b)に示した通信はいずれも高速シリアル転送であり、受信機内部には受信用の大規模集積回路(LSI)もしくは集積回路(IC)が組み込まれており、そのLSIやIC内部には必ず受信データに同期したクロック(リカバリクロック)を生成するクロックデータ復元回路(CDR)が組み込まれている。

【0018】

図2は、図1に示したクロックデータ復元回路(CDR)の詳細を示すブロック図である。図2の回路は位相同期回路2101(PLL)、インターポレータ回路2102(IP)、分周回路2103(DIV)、位相比較回路2104(PhC)、フィルタ回路2105(Fil)、ポインタ回路2106(Pt)からなる。

【0019】

位相同期回路2101(PLL)は例えば入力データが“1”の時“0”を出力する反転回路(インバータ)を複数個、輪のように接続した発信器(リングオシレータ)を備え、その複数の反転回路の出力をクロックとして取り出すことで周波数が等しく、位相の異なる多相クロック(Mulclk)を生成する。

【0020】

インターポレータ回路2102(IP)は位相同期回路2101(PLL)から供給される周波数が等しく位相が異なる複数の多相クロックをそれぞれ重み付けして足し合わせることで多相クロック間の位相を補間するクロックである合成クロック(Compclk)を合成する。合成クロックは重み付け量を切り替える事で、位相を1/S周期(Sは回路に求められる位相精度により決まる、正の整数)間隔でずらすことが出来る。インターポレータ2102(IP)は外部からの制御により重み付けを変えることで、任意の位相(1相〜S相)のクロックを生成することができる。

【0021】

分周回路2103(DIV)は入力されるクロックを1/Nの周波数に変換(分周)し、リカバリクロック(Rclk)を生成する。分周比Nは、外部の制御によりを任意に切り替えることができる。

【0022】

位相比較回路2104(PhC)は入力データと回路内部で生成したクロックの位相(切り替わりエッジ)を比較し、入力データに対してクロックが進んでいるか、送れているかを判定し、位相比較結果を出力する。

【0023】

フィルタ回路2105(Fil)は位相比較回路2104(PhC)が出力する位相比較結果を複数サイクルに渡り蓄積し平均化、閾値比較し、最終的にインターポレータ回路2102(IP)の位相を進めるか、遅らせるかを決定して位相更新信号を出力する。また、フィルタ回路2105(Fil)は位相比較結果を蓄積するサイクル(位相更新サイクル)を制御することで、入力データに対するリカバリクロックの位相制御の応答速度を制御することができ、クロックデータ復元回路全体の帯域を制御する。

【0024】

ポインタ回路2106(Pt)は、フィルタ回路2105(Fil)の位相更新信号に従い、インターポレータの合成クロックが取るべき相(1相〜S相)に対応付けされた情報を更新し、インターポレータの合成クロックの取り得る相(1相〜S相)に対応付けされたTAP信号(TAP1〜TAPS)のいずれかを選択することでインターポレータ回路2102(IP)の合成クロックの位相を制御する。

【0025】

また、クロックデータ復元回路ではデータ受信中にデータ受信用クロック(リカバリクロック)の位相が大きく動くとデータの受信に失敗する場合があるためポインタ回路2106(Pt)はインターポレータ回路2102(IP)の合成クロックの位相を1段階ずつ進めるもしくは遅らせる形でインクリメンタルに制御する。

【0026】

なお、位相比較回路2104(PhC)、フィルタ回路2105(Fil)、ポインタ回路2106(Pt)は、リカバリクロックを動作クロックとして動作する。なお、この「リカバリクロックを動作クロックとして動作する」とは、その回路内のフリップフロップがリカバリクロックに同期して動作することを意味する。

【0027】

理解を容易にするため、次に示す条件におけるクロックデータ復元回路(CDR)の動作原理について説明する。

・最大の入力データ転送レートとリカバリクロックのレートが同じ(例えば、データレートが1Giga bit/secの時リカバリクロックは1GHz)であるフルレート方式のクロックデータ復元回路(CDR)とする。

・入力されるデータの転送レートとインターポレータ回路の合成するクロックが同じ場合に最適となるように設定される。

・入力データは最大の転送レートを1として、転送レートが1/N(0<N<無限大)とする。

【0028】

インターポレータ回路2102(IP)は位相同期回路2101(PLL; Phase-locked loop)から供給される多相クロックを使い、周波数が等しく位相のずれた合成クロックを生成する。また、この合成クロックの位相はポインタ回路2106(Pt)からの制御信号で周期の1/S(Sは回路に求められる位相精度により決まる、正の整数)間隔でインクリメンタルに進めたり、遅らせたりすることができる。

【0029】

インターポレータ回路2102(IP)は、入力データの最速の転送レートに合わせて動作させ、入力データの転送レートが切り替わっても常に同じ周期Tのクロックを出力する。そのため、入力データの転送レートが1/Nの時は、分周回路2103で合成クロックを1/Nに分周してリカバリクロックを供給する。位相比較回路2104(PhC)は入力データとリカバリクロックの位相比較を行い、位相比較結果信号(Sig1)を出力する。入力データに対してリカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号(UP信号)を位相比較結果信号(Sig1)として出力する。逆に、入力データに対してリカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号(DOWN信号)を位相比較結果信号(Sig1)として出力する。

【0030】

フィルタ回路2105(Fil)は、位相遅れ信号/位相進み信号(UP/DOWN)のアサートされる回数を複数サイクルに渡りカウンタにカウントし、位相遅れ信号/位相進み信号(UP/DOWN)それぞれのカウント値の差(UP−DOWN)をあらかじめ設定された閾値と比較し、差が正の値であり且つ正の閾値より大きければ位相進める信号(AVE_UP)を位相更新信号(Sig2)として出力する。カウント値の差と閾値との比較を行い、差が負の値であり且つ負の閾値より小さければ位相遅らせる信号(AVE_DOWN)を位相更新信号(Sig2)として出力する。

【0031】

ポインタ回路2106(Pt)は位相更新信号(Sig2)を受け、インターポレータ回路2102(Pt)に位相を進める信号、又は、位相を遅らせる位相制御信号(Sig3)を出力して、インターポレータ回路2102(Pt)の合成クロックの位相を制御する。

【0032】

この一連の動作を繰り返すことでマルチレートの入力データを取り込むのに最適な周波数と位相のリカバリクロックを生成する。また、このクロックデータ復元回路は、帯域制限のあるインターポレータ回路は常に同じ速度で動作し、出力する合成クロックを分周回路が分周することで最適な周波数のリカバリクロックを生成するため、インターポレータ回路の動作速度以下の転送レートに関して帯域制限がなく何れの規格のデータでも受信可能であり、あらゆる転送レートを持つシリアルデータをひとつのLSIで受信することが可能である。

【0033】

図3は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図2に対して、フィルタ回路3105(Fil)とポインタ回路3106(Pt)に供給されるリカバリクロックを別系統にし個別の分周回路3116(DIV2)、分周回路3117(DIV3)で分周したクロックをそれぞれに供給することで、クロックデータ復元回路(CDR)の入力データに対するリカバリクロックの位相追従性を向上させることができる。

【0034】

図7にデータレートが1/Nの時の入力データとリカバリクロックの波形を示す。インターポレータ回路3102(IP)は入力データの転送レートによらず同じ速度で動作しているため、データレートが最速の時も1/Nの時も一回の制御信号で進めるもしくは遅らせることのできる位相補正量はT/Sである(図7(a,b)参照)。ところが、図7(d)にあるようにデータレート1/Nの時はリカバリクロックの周期が合成クロックのN倍であり、1回の位相更新サイクルで期待される位相補正量は N×T/S である。つまり回路全体をリカバリクロックで動作させてしまうと、1/N動作時はリカバリクロックの入力データに対する追従能力(位相追従性)が1/Nになってしまう。そこで、ポインタ回路3106とフィルタ回路3105に供給されるクロックをそれぞれ個別の分周クロックとし、フィルタ回路3105には1/P(但し0<N<P)に分周したリカバリクロック、ポインタ回路3106にはN/Pに分周したリカバリクロックを供給しポインタ回路3106をフィルタ回路3105のN倍の速さで動作させ、フィルタ回路3105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路3102に送ることとする。そうすることで、図7(c)にあるように1回の位相更新サイクルで位相補正される位相補正量がN×T/Sとなり、0<N<Pの範囲でデータレートによらず、同じ位相追従性を持ったマルチレート対応のクロックデータリカバリ回路を実現することができる。

【0035】

図4は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図2に対して、ポインタ回路4106に分周回路4103で分周する前の合成クロックを供給することにより、クロックデータ復元回路の入力データに対するリカバリクロックの位相追従性が向上させることができる。

【0036】

データレートが1/N時、フィルタ回路4105は分周回路4103により1/Nに分周された合成クロック(リカバリクロック)で動作し、ポインタ回路4106は分周前の合成クロックを使い動作することで、図3の回路と同様にフィルタ回路4105に対し、N倍の速さでポインタ回路4106を動作させ、フィルタ回路4105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路4102に送る。そうすることで、1回の位相更新サイクルで位相補正される位相補正量がN×T/Sとなり、データレートによらず、同じ位相追従性を持ったマルチレート対応のクロックデータ復元回路を実現することができる。

【0037】

図5は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図4の回路へフィルタ回路5105(Fil)、ポインタ回路5106(Pt)それぞれに供給されるクロックに分周回路5116(DIV4)、分周回路5117(DIV5)を追加することにより、クロックデータ復元回路(CDR)の帯域を制御しながら、位相追従能力を向上させることができる。

【0038】

フィルタ回路5105(Fil)には1/P(但しP>0)に分周したリカバリクロック(インターポレータ回路の合成クロックに対して1/(N×P)に分周したクロック)、ポインタ回路5106(Pt)には1/Pに分周したインターポレータ回路の合成クロックを供給する。フィルタ回路5105(Fil)はPの値を切り替えることで位相更新サイクルを切り替えることができ、クロックデータ復元回路(CDR)の帯域制御ができる。またポインタ回路5106(Pt)は常にフィルタ回路5105(Fil)のN倍の速さで動作でき、図4の回路と同様にフィルタ回路5105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路5102に送ることができ、データレートによらず同じ位相追従性を持ったマルチレート対応のクロックデータ復元回路を実現することができる。

【0039】

以上、本実施の形態を用いることで、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路の実現が可能となる。また、本発明者によってなされた発明を実施の形態に基づき説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。例えば、任意の分周比で動作する分周回路の代わりに、1つ以上の固定分周比を選択できる分周器と、インターポレータ回路の帯域を変更する必要がない範囲にて多相クロックの周波数を変更するような組み合わせでも良い。また、例えば位相比較回路をハーフレート方式にすれば入力データに対して速度1/2の周波数(データレートが1Giga bit/secの時クロックは500MHz)の合成クロックでマルチレート対応のクロックデータ復元回路を実現することができる。

【産業上の利用可能性】

【0040】

本発明のクロックデータ復元回路は、たとえばPONのような複数の転送レートをもつシリアル転送システムに対して広く適用可能である。

(付記)

1.位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定することを特徴とする半導体集積回路装置。

2.上記1記載の半導体集積回路装置において、

前記位相比較回路、前記ポインタ回路は、前記リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

3.上記1記載の半導体集積回路装置において、

フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

4.上記1記載の半導体集積回路装置において、

フィルタ回路を有し、

前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

5.上記1記載の半導体集積回路装置において、

フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

6.上記1記載の半導体集積回路装置において、

フィルタ回路を有し、

前記フィルタ回路は、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントし、位相遅れ信号と位相進み信号がアサートされた回数の差と閾値との比較を行い、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力し、前記差が負の閾値より小さければ位相遅らせる信号を出力することを特徴とする半導体集積回路装置。

7.位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定することを特徴とするクロックデータ復元方法。

8.上記7記載のクロックデータ復元方法において、

前記位相比較回路、前記ポインタ回路は、前記リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

9.上記7記載のクロックデータ復元方法において、

第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

10.上記7記載のクロックデータ復元方法において、

前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

11.上記7記載のクロックデータ復元方法において、

第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

12.上記7記載のクロックデータ復元方法において、

フィルタ回路により、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントさせ、位相遅れ信号と位相進み信号がアサートされた回数の差と閾値との比較を行わせ、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力させ、前記差が負の閾値より小さければ位相遅らせる信号を出力させることを特徴とするクロックデータ復元方法。

【符号の説明】

【0041】

1001、1002、1003……ONU(Optical Network Unit)

1004……OLT(Optical Line Terminal)

2101、3101、4101、5101、6101……位相同期回路(PLL; Phase−locked loop)

2102、3102、4102、5102、6102……インターポレータ回路(IP; Interpolator)

2103、3103、4103、5103、6103……分周回路(DIV; Divider)

2104、3104、4104、5104、……位相比較回路(PhC; Phase Comparator)

6104……サンプリング回路(Spy)

2105、3105、4105、5105……フィルタ回路(Fil; Filter)

2106、3106、4106、5106……ポインタ回路(Pt; Pointer)

3116、5116……フィルタ回路用分周回路

3117、5117……ポインタ回路用分周回路

6106……CDR制御回路(CDRctrl; CDR controller)

DATA……入力データ(Input data)

Rclk……リカバリクロック (Recovery clock)

Mulclk……多相クロック(Multi phase clock)

Compclk……合成クロック(Composite clock)

Sig1……位相比較結果信号

Sig2……位相更新信号

Sig3……位相制御信号

【技術分野】

【0001】

本発明はマルチレートのシリアルデータを受信するクロックデータ復元回路に関する物で、特にシリアライザ−デシリアライザ回路(Serdes)に好適なクロックデータ復元回路に関する。

【背景技術】

【0002】

近年、シリアルデータ転送は図1に示すような光通信(PON; Passive Optical Network)を始め、パーソナルコンピュータ(PC)やサーバのバックプレーン転送など様々な場所に使用されており、また扱われる情報量の増加に伴い更なる高速化が求められている。この高速シリアルデータ転送を実現するために、送られてくるシリアルデータから位相情報を抽出し、データに同期したクロックを生成するクロックデータ復元回路(CDR)が必要である。また、高速シリアルデータ転送に使われる規格は用途の違いなどから、GPONなど様々あり、それぞれ決められた転送レートがある。またEthernet(Ethernetは、富士ゼロックス株式会社の登録商標である。)を始め同様のプロトコルでも複数の転送レートをもつ規格もあり、規格をひとつのLSIで準拠する為には、マルチレートに対応したクロックデータ復元回路が必要である。

【0003】

特許文献1はクロックデータ復元回路を含むシリアライザ−デシリアライザ回路(Serdes)について示されている。この回路は基本的なクロックデータ復元回路を持ち、パラレル−シリアル変換回路、シリアル−パラレル変換回路、ファストイン ファストアウト回路(FIFO; First In First Out)を一体化することで、小面積、低消費電力を実現している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−36869号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図6は、特許文献1の図7に示されるシリアライザ−デシリアライザ回路(Serdes)に含まれるクロックデータ復元回路(CDR)を抜粋したものである。図6には、位相同期回路6101(PLL)、分周回路6103、インターポレータ回路6102(IP)、サンプリング回路6104(Spl)、クロックデータ復元回路コントロール回路6106(CDRctrl; CDR control)が含まれる。

【0006】

位相同期回路6101(PLL)で生成されたクロックを分周回路6103(DIV)で分周多相クロックに変換する。その多相クロックを使いインターポレータ回路6102(IP)でリカバリクロックを生成する。サンプリング回路6104(Spl)で入力データとリカバリクロックの比較を行う。その比較結果を受けCDRコントロール回路6106がインターポレータ回路6102の位相制御を行うことで入力データに対して最適なリカバリクロックを生成する。

【0007】

図6では、位相同期回路6101(PLL)とインターポレータ回路6102(IP)の間にある分周回路6103(DIV)の分周比を変更することでマルチレートに対応する。しかし、この方法ではインターポレータ回路6102(IP)の動作速度を入力データの転送レートに合わせて切り変える必要があり、非常に広い帯域を前記インターポレータ回路6102(IP)に持たせる必要がある。ところが、インターポレータ回路などのアナログ回路は帯域を広くすると、ジッタの増加や、回路面積の増大などといった問題を生じる。

【0008】

以上の点に鑑み、本発明では、インターポレータ回路の広帯域化をせずに、マルチレートのデータに対応したクロックデータ復元回路の実現することを課題とする。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。すなわち、位相同期回路(PLL)などのクロック源(PLL)から供給される多相クロックを元にインターポレータ回路(IP)で合成されたクロック(Compclk)を送られてくるデータの転送レートに合わせて分周回路(DIV)で分周し、入力データの取り込みに最適な周波数のリカバリクロック(Rclk)を生成する。このリカバリクロック(Rclk)と入力データの位相を位相比較回路(PhC)で位相比較し、シリアルデータの位相に対してクロックが遅れているか、進んでいるかを判定する。その位相判定結果(Sig1)をフィルタ回路(Fil)で最適化し、その結果を基にポインタ回路(Pt)がインターポレータ回路(IP)に生成クロックの位相を進ませるもしくは、遅らせる制御信号(Sig3)を送る。その制御信号(Sig3)を受けて、インターポレータ回路は生成クロックの位相を進めたり、遅らせたりすることで、マルチレートに対応したクロックデータ復元回路(CDR)を実現する。また、位相比較回路(PhC)、フィルタ回路(Fil)、ポインタ回路(Pt)に供給するクロックをそれぞれ別系統にし、(1)インターポレータ回路の合成クロック、(2)リカバリクロック、(3)インターポレータ回路の合成クロックの分周クロック、(4)リカバリクロックの分周クロックのいずれかを使うことでクロックデータ復元回路の追従特性を制御することができる。

【発明の効果】

【0010】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すると、以下のようである。すなわち、インターポレータ回路の広帯域化をせずに、マルチレートのデータに対応したクロックデータ復元回路の実現が可能となる。

【図面の簡単な説明】

【0011】

【図1】高速シリアル転送システムの例である。(a)光通信システムPON, (b)PC内部のCPU-HDD間を示した図。

【図2】マルチレート対応クロックデータ復元回路の一例である。

【図3】マルチレート対応クロックデータ復元回路の一例である。

【図4】マルチレート対応クロックデータ復元回路の一例である。

【図5】マルチレート対応クロックデータ復元回路の一例である。

【図6】特許文献1の図7に示されるSerdes回路からクロックデータ復元回路を示したブロック図である。

【図7】マルチレート対応クロックデータ復元回路の入力データとリカバリクロックの波形を示した図である。(a) 入力データレート最速の時の波形, (b) 1/N動作時の波形(補正量T/Sの時), (c) 1/N動作時の波形(補正量N×T/Sの時), (d) 1/N動作時の期待値の波形。

【発明を実施するための形態】

【0012】

図1は、高速シリアル転送システムの例を示したものである。図1(a)は光通信ネットワークシステムであるパッシブオプティカルネットワーク(PON; Passive Optical Network)を示した図である。

【0013】

PONは複数の端末側送受信機であるONU1001〜1003(Optical Network Unit)と基地局側送受信機であるオプティカル ライン ターミナル1004(OLT; Optical Line Terminal)とそれらを繋ぐ光ファイバーで構成される。

【0014】

ONUは例えば各家庭にあるパーソナルコンピュータ(PC)に接続されOLTとのデータの送受信を行う通信装置である。

【0015】

OLTはインターネット供給会社等の基地局に配置され複数のONUと光ファイバーで接続されインターネットとONUとの間でデータの送受信を行う通信装置である。ONU-OLT間の通信ではギガビットポン(GPON)やギガビットイーサネットポン(イーサネットは、富士ゼロックス株式会社の登録商標である。)などの規格があり、それぞれ転送速度が異なっている。

【0016】

図1(b)はPC内部の中央演算処理装置(CPU)とハードディスクドライブ(HDD)間の通信を示した図である。中央演算処理装置(CPU)は記憶装置であるハードディスクドライブに蓄積したデータを必要に応じて読み出し、使用者の命令に従い演算処理を行い、演算結果を必要に応じてハードディスクドライブに書き込む半導体装置である。ハードディスクドライブ(HDD)は、PC等のデジタル機器に内蔵され、不揮発性の磁気記録ディスク、データの読み書きを行う磁気記録ヘッド、外部とデータのやり取りを行い磁気記録ヘッドを制御する制御回路から構成され、大容量のデータを保持する事ができる記憶装置である。CPU−HDD間の通信は所定の規格が適用されている。この規格ではジェネレーション1(G1)とジェネレーション2(G2)がありそれぞれ規定される転送レートが異なっているが、互換性が必要なため送受信回路はそれぞれジェネレーション1,2のデータを送受信する必要がある。

【0017】

図1(a),(b)に示した通信はいずれも高速シリアル転送であり、受信機内部には受信用の大規模集積回路(LSI)もしくは集積回路(IC)が組み込まれており、そのLSIやIC内部には必ず受信データに同期したクロック(リカバリクロック)を生成するクロックデータ復元回路(CDR)が組み込まれている。

【0018】

図2は、図1に示したクロックデータ復元回路(CDR)の詳細を示すブロック図である。図2の回路は位相同期回路2101(PLL)、インターポレータ回路2102(IP)、分周回路2103(DIV)、位相比較回路2104(PhC)、フィルタ回路2105(Fil)、ポインタ回路2106(Pt)からなる。

【0019】

位相同期回路2101(PLL)は例えば入力データが“1”の時“0”を出力する反転回路(インバータ)を複数個、輪のように接続した発信器(リングオシレータ)を備え、その複数の反転回路の出力をクロックとして取り出すことで周波数が等しく、位相の異なる多相クロック(Mulclk)を生成する。

【0020】

インターポレータ回路2102(IP)は位相同期回路2101(PLL)から供給される周波数が等しく位相が異なる複数の多相クロックをそれぞれ重み付けして足し合わせることで多相クロック間の位相を補間するクロックである合成クロック(Compclk)を合成する。合成クロックは重み付け量を切り替える事で、位相を1/S周期(Sは回路に求められる位相精度により決まる、正の整数)間隔でずらすことが出来る。インターポレータ2102(IP)は外部からの制御により重み付けを変えることで、任意の位相(1相〜S相)のクロックを生成することができる。

【0021】

分周回路2103(DIV)は入力されるクロックを1/Nの周波数に変換(分周)し、リカバリクロック(Rclk)を生成する。分周比Nは、外部の制御によりを任意に切り替えることができる。

【0022】

位相比較回路2104(PhC)は入力データと回路内部で生成したクロックの位相(切り替わりエッジ)を比較し、入力データに対してクロックが進んでいるか、送れているかを判定し、位相比較結果を出力する。

【0023】

フィルタ回路2105(Fil)は位相比較回路2104(PhC)が出力する位相比較結果を複数サイクルに渡り蓄積し平均化、閾値比較し、最終的にインターポレータ回路2102(IP)の位相を進めるか、遅らせるかを決定して位相更新信号を出力する。また、フィルタ回路2105(Fil)は位相比較結果を蓄積するサイクル(位相更新サイクル)を制御することで、入力データに対するリカバリクロックの位相制御の応答速度を制御することができ、クロックデータ復元回路全体の帯域を制御する。

【0024】

ポインタ回路2106(Pt)は、フィルタ回路2105(Fil)の位相更新信号に従い、インターポレータの合成クロックが取るべき相(1相〜S相)に対応付けされた情報を更新し、インターポレータの合成クロックの取り得る相(1相〜S相)に対応付けされたTAP信号(TAP1〜TAPS)のいずれかを選択することでインターポレータ回路2102(IP)の合成クロックの位相を制御する。

【0025】

また、クロックデータ復元回路ではデータ受信中にデータ受信用クロック(リカバリクロック)の位相が大きく動くとデータの受信に失敗する場合があるためポインタ回路2106(Pt)はインターポレータ回路2102(IP)の合成クロックの位相を1段階ずつ進めるもしくは遅らせる形でインクリメンタルに制御する。

【0026】

なお、位相比較回路2104(PhC)、フィルタ回路2105(Fil)、ポインタ回路2106(Pt)は、リカバリクロックを動作クロックとして動作する。なお、この「リカバリクロックを動作クロックとして動作する」とは、その回路内のフリップフロップがリカバリクロックに同期して動作することを意味する。

【0027】

理解を容易にするため、次に示す条件におけるクロックデータ復元回路(CDR)の動作原理について説明する。

・最大の入力データ転送レートとリカバリクロックのレートが同じ(例えば、データレートが1Giga bit/secの時リカバリクロックは1GHz)であるフルレート方式のクロックデータ復元回路(CDR)とする。

・入力されるデータの転送レートとインターポレータ回路の合成するクロックが同じ場合に最適となるように設定される。

・入力データは最大の転送レートを1として、転送レートが1/N(0<N<無限大)とする。

【0028】

インターポレータ回路2102(IP)は位相同期回路2101(PLL; Phase-locked loop)から供給される多相クロックを使い、周波数が等しく位相のずれた合成クロックを生成する。また、この合成クロックの位相はポインタ回路2106(Pt)からの制御信号で周期の1/S(Sは回路に求められる位相精度により決まる、正の整数)間隔でインクリメンタルに進めたり、遅らせたりすることができる。

【0029】

インターポレータ回路2102(IP)は、入力データの最速の転送レートに合わせて動作させ、入力データの転送レートが切り替わっても常に同じ周期Tのクロックを出力する。そのため、入力データの転送レートが1/Nの時は、分周回路2103で合成クロックを1/Nに分周してリカバリクロックを供給する。位相比較回路2104(PhC)は入力データとリカバリクロックの位相比較を行い、位相比較結果信号(Sig1)を出力する。入力データに対してリカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号(UP信号)を位相比較結果信号(Sig1)として出力する。逆に、入力データに対してリカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号(DOWN信号)を位相比較結果信号(Sig1)として出力する。

【0030】

フィルタ回路2105(Fil)は、位相遅れ信号/位相進み信号(UP/DOWN)のアサートされる回数を複数サイクルに渡りカウンタにカウントし、位相遅れ信号/位相進み信号(UP/DOWN)それぞれのカウント値の差(UP−DOWN)をあらかじめ設定された閾値と比較し、差が正の値であり且つ正の閾値より大きければ位相進める信号(AVE_UP)を位相更新信号(Sig2)として出力する。カウント値の差と閾値との比較を行い、差が負の値であり且つ負の閾値より小さければ位相遅らせる信号(AVE_DOWN)を位相更新信号(Sig2)として出力する。

【0031】

ポインタ回路2106(Pt)は位相更新信号(Sig2)を受け、インターポレータ回路2102(Pt)に位相を進める信号、又は、位相を遅らせる位相制御信号(Sig3)を出力して、インターポレータ回路2102(Pt)の合成クロックの位相を制御する。

【0032】

この一連の動作を繰り返すことでマルチレートの入力データを取り込むのに最適な周波数と位相のリカバリクロックを生成する。また、このクロックデータ復元回路は、帯域制限のあるインターポレータ回路は常に同じ速度で動作し、出力する合成クロックを分周回路が分周することで最適な周波数のリカバリクロックを生成するため、インターポレータ回路の動作速度以下の転送レートに関して帯域制限がなく何れの規格のデータでも受信可能であり、あらゆる転送レートを持つシリアルデータをひとつのLSIで受信することが可能である。

【0033】

図3は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図2に対して、フィルタ回路3105(Fil)とポインタ回路3106(Pt)に供給されるリカバリクロックを別系統にし個別の分周回路3116(DIV2)、分周回路3117(DIV3)で分周したクロックをそれぞれに供給することで、クロックデータ復元回路(CDR)の入力データに対するリカバリクロックの位相追従性を向上させることができる。

【0034】

図7にデータレートが1/Nの時の入力データとリカバリクロックの波形を示す。インターポレータ回路3102(IP)は入力データの転送レートによらず同じ速度で動作しているため、データレートが最速の時も1/Nの時も一回の制御信号で進めるもしくは遅らせることのできる位相補正量はT/Sである(図7(a,b)参照)。ところが、図7(d)にあるようにデータレート1/Nの時はリカバリクロックの周期が合成クロックのN倍であり、1回の位相更新サイクルで期待される位相補正量は N×T/S である。つまり回路全体をリカバリクロックで動作させてしまうと、1/N動作時はリカバリクロックの入力データに対する追従能力(位相追従性)が1/Nになってしまう。そこで、ポインタ回路3106とフィルタ回路3105に供給されるクロックをそれぞれ個別の分周クロックとし、フィルタ回路3105には1/P(但し0<N<P)に分周したリカバリクロック、ポインタ回路3106にはN/Pに分周したリカバリクロックを供給しポインタ回路3106をフィルタ回路3105のN倍の速さで動作させ、フィルタ回路3105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路3102に送ることとする。そうすることで、図7(c)にあるように1回の位相更新サイクルで位相補正される位相補正量がN×T/Sとなり、0<N<Pの範囲でデータレートによらず、同じ位相追従性を持ったマルチレート対応のクロックデータリカバリ回路を実現することができる。

【0035】

図4は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図2に対して、ポインタ回路4106に分周回路4103で分周する前の合成クロックを供給することにより、クロックデータ復元回路の入力データに対するリカバリクロックの位相追従性が向上させることができる。

【0036】

データレートが1/N時、フィルタ回路4105は分周回路4103により1/Nに分周された合成クロック(リカバリクロック)で動作し、ポインタ回路4106は分周前の合成クロックを使い動作することで、図3の回路と同様にフィルタ回路4105に対し、N倍の速さでポインタ回路4106を動作させ、フィルタ回路4105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路4102に送る。そうすることで、1回の位相更新サイクルで位相補正される位相補正量がN×T/Sとなり、データレートによらず、同じ位相追従性を持ったマルチレート対応のクロックデータ復元回路を実現することができる。

【0037】

図5は、クロックデータ復元回路(CDR)の他の例を示すブロック図である。図4の回路へフィルタ回路5105(Fil)、ポインタ回路5106(Pt)それぞれに供給されるクロックに分周回路5116(DIV4)、分周回路5117(DIV5)を追加することにより、クロックデータ復元回路(CDR)の帯域を制御しながら、位相追従能力を向上させることができる。

【0038】

フィルタ回路5105(Fil)には1/P(但しP>0)に分周したリカバリクロック(インターポレータ回路の合成クロックに対して1/(N×P)に分周したクロック)、ポインタ回路5106(Pt)には1/Pに分周したインターポレータ回路の合成クロックを供給する。フィルタ回路5105(Fil)はPの値を切り替えることで位相更新サイクルを切り替えることができ、クロックデータ復元回路(CDR)の帯域制御ができる。またポインタ回路5106(Pt)は常にフィルタ回路5105(Fil)のN倍の速さで動作でき、図4の回路と同様にフィルタ回路5105から送られる1回の位相更新信号に対してN回制御信号をインターポレータ回路5102に送ることができ、データレートによらず同じ位相追従性を持ったマルチレート対応のクロックデータ復元回路を実現することができる。

【0039】

以上、本実施の形態を用いることで、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路の実現が可能となる。また、本発明者によってなされた発明を実施の形態に基づき説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。例えば、任意の分周比で動作する分周回路の代わりに、1つ以上の固定分周比を選択できる分周器と、インターポレータ回路の帯域を変更する必要がない範囲にて多相クロックの周波数を変更するような組み合わせでも良い。また、例えば位相比較回路をハーフレート方式にすれば入力データに対して速度1/2の周波数(データレートが1Giga bit/secの時クロックは500MHz)の合成クロックでマルチレート対応のクロックデータ復元回路を実現することができる。

【産業上の利用可能性】

【0040】

本発明のクロックデータ復元回路は、たとえばPONのような複数の転送レートをもつシリアル転送システムに対して広く適用可能である。

(付記)

1.位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定することを特徴とする半導体集積回路装置。

2.上記1記載の半導体集積回路装置において、

前記位相比較回路、前記ポインタ回路は、前記リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

3.上記1記載の半導体集積回路装置において、

フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

4.上記1記載の半導体集積回路装置において、

フィルタ回路を有し、

前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

5.上記1記載の半導体集積回路装置において、

フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

6.上記1記載の半導体集積回路装置において、

フィルタ回路を有し、

前記フィルタ回路は、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントし、位相遅れ信号と位相進み信号がアサートされた回数の差と閾値との比較を行い、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力し、前記差が負の閾値より小さければ位相遅らせる信号を出力することを特徴とする半導体集積回路装置。

7.位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定することを特徴とするクロックデータ復元方法。

8.上記7記載のクロックデータ復元方法において、

前記位相比較回路、前記ポインタ回路は、前記リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

9.上記7記載のクロックデータ復元方法において、

第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

10.上記7記載のクロックデータ復元方法において、

前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

11.上記7記載のクロックデータ復元方法において、

第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

12.上記7記載のクロックデータ復元方法において、

フィルタ回路により、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントさせ、位相遅れ信号と位相進み信号がアサートされた回数の差と閾値との比較を行わせ、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力させ、前記差が負の閾値より小さければ位相遅らせる信号を出力させることを特徴とするクロックデータ復元方法。

【符号の説明】

【0041】

1001、1002、1003……ONU(Optical Network Unit)

1004……OLT(Optical Line Terminal)

2101、3101、4101、5101、6101……位相同期回路(PLL; Phase−locked loop)

2102、3102、4102、5102、6102……インターポレータ回路(IP; Interpolator)

2103、3103、4103、5103、6103……分周回路(DIV; Divider)

2104、3104、4104、5104、……位相比較回路(PhC; Phase Comparator)

6104……サンプリング回路(Spy)

2105、3105、4105、5105……フィルタ回路(Fil; Filter)

2106、3106、4106、5106……ポインタ回路(Pt; Pointer)

3116、5116……フィルタ回路用分周回路

3117、5117……ポインタ回路用分周回路

6106……CDR制御回路(CDRctrl; CDR controller)

DATA……入力データ(Input data)

Rclk……リカバリクロック (Recovery clock)

Mulclk……多相クロック(Multi phase clock)

Compclk……合成クロック(Composite clock)

Sig1……位相比較結果信号

Sig2……位相更新信号

Sig3……位相制御信号

【特許請求の範囲】

【請求項1】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路を有し、

前記位相比較回路および前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項2】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項3】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項4】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路を有し、

前記フィルタ回路は、複数サイクルに渡り前記位相遅れ信号と前記位相進み信号がアサートされた回数をそれぞれカウントし、前記位相遅れ信号と前記位相進み信号がアサートされた回数の差と閾値との比較を行い、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力し、前記差が負の閾値より小さければ位相遅らせる信号を出力することを特徴とする半導体集積回路装置。

【請求項5】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項6】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項7】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項8】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路により、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントさせ、前記位相遅れ信号と前記位相進み信号がアサートされた回数の差と閾値との比較を行わせ、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力させ、前記差が負の閾値より小さければ位相遅らせる信号を出力させることを特徴とするクロックデータ復元方法。

【請求項1】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路を有し、

前記位相比較回路および前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項2】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項3】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路と、

第2分周回路と、

第3分周回路とを有し、

前記第2分周回路は、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成し、

前記第3分周回路は、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成し、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とする半導体集積回路装置。

【請求項4】

位相同期回路と、

インターポレータ回路と、

第1分周回路と、

ポインタ回路と、

位相比較回路とを有し、

前記位相同期回路は、周波数が同じで、位相がそれぞれ異なる多相クロックを生成し、

前記インターポレータ回路は、前記多相クロックを合成することにより、前記ポインタ回路が指定する位相の合成クロックを生成し、

前記第1分周回路は、前記合成クロックを所定の第1分周比で分周することにより、第1リカバリクロックを生成し、

前記位相比較回路は、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力し、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路を有し、

前記フィルタ回路は、複数サイクルに渡り前記位相遅れ信号と前記位相進み信号がアサートされた回数をそれぞれカウントし、前記位相遅れ信号と前記位相進み信号がアサートされた回数の差と閾値との比較を行い、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力し、前記差が負の閾値より小さければ位相遅らせる信号を出力することを特徴とする半導体集積回路装置。

【請求項5】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記第1リカバリクロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項6】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、前記位相比較回路、前記フィルタ回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記合成クロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項7】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、第2分周回路により、前記第1リカバリクロックを所定の第2分周比で分周することにより、第2リカバリクロックを生成させ、

第3分周回路により、前記合成クロックを所定の第3分周比で分周することにより、第3リカバリクロックを生成させ、

前記位相比較回路は、前記第1リカバリクロックを動作クロックとして動作し、

前記フィルタ回路は、前記第2リカバリクロックを動作クロックとして動作し、

前記ポインタ回路は、前記第3リカバリクロックを動作クロックとして動作することを特徴とするクロックデータ復元方法。

【請求項8】

位相同期回路により、周波数が同じで、位相がそれぞれ異なる多相クロックを生成させ、

インターポレータ回路により、前記多相クロックを合成し、ポインタ回路が指定する位相の合成クロックを生成させ、

第1分周回路により、前記合成クロックを所定の第1分周比で分周し、第1リカバリクロックを生成させ、

位相比較回路により、入力データと前記第1リカバリクロックの位相を比較し、前記入力データに対して前記第1リカバリクロックが遅れている場合には、位相が遅れていることを示す位相遅れ信号を出力し、前記入力データに対して前記第1リカバリクロックが進んでいる場合には、位相が進んでいることを示す位相進み信号を出力させ、

前記ポインタ回路は、前記位相遅れ信号または前記位相進み信号により保持する位相を更新し、前記更新された位相を前記インターポレータ回路へ指定するものであり、

さらに、フィルタ回路により、複数サイクルに渡り前記位相遅れ信号と位相進み信号がアサートされた回数をそれぞれカウントさせ、前記位相遅れ信号と前記位相進み信号がアサートされた回数の差と閾値との比較を行わせ、前記差が正の閾値より大きければ位相進める信号を前記ポインタ回路へ出力させ、前記差が負の閾値より小さければ位相遅らせる信号を出力させることを特徴とするクロックデータ復元方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−9389(P2013−9389A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2012−172504(P2012−172504)

【出願日】平成24年8月3日(2012.8.3)

【分割の表示】特願2008−85174(P2008−85174)の分割

【原出願日】平成20年3月28日(2008.3.28)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成24年8月3日(2012.8.3)

【分割の表示】特願2008−85174(P2008−85174)の分割

【原出願日】平成20年3月28日(2008.3.28)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]