半導体集積回路装置および出力バッファ遅延変動検出方法

【課題】I/Oバッファの実際の配置場所及び実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出し、オーバーマージンな設計を回避できるようにした半導体集積回路装置を提供する。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、外部装置とのインタフェースをなす入出力バッファ(以下、I/Oバッファという)を備える半導体集積回路装置、および、このような半導体集積回路装置におけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための出力バッファ遅延変動検出方法に関する。

【背景技術】

【0002】

半導体集積回路装置においては、I/Oバッファが同時にスイッチングすると、I/Oバッファの電源電圧および接地電圧に急激な変動が発生する。これらI/Oバッファの電源電圧および接地電圧の急激な変動の大きさは、同時にスイッチングするI/Oバッファの個数や外部負荷条件などに依拠する。なお、I/Oバッファにおいては、出力バッファがスイッチングすると、入力バッファもまた出力バッファの出力信号によりスイッチングする。

【0003】

半導体集積回路装置におけるI/Oバッファの同時スイッチングによる電源電圧変動および接地電圧変動は、半導体集積回路装置の安定動作を阻害するものであり、一般に、同時スイッチングノイズ(SSN[Simultaneous Switching Noise])と呼ばれている。類義語として、SSOノイズ(Simultaneous Switching Output Noise)や、SSIノイズ(Simultaneous Switching Input Noise)がある。

【0004】

半導体集積回路装置の設計においては、SSOノイズ検証が非常に面倒な作業となる。I/Oバッファの同時スイッチングによるI/Oバッファの電源電圧変動および接地電圧変動は、半導体集積回路装置の内部の電源線網および接地線網を伝わって伝搬する。これは、空間的な広がりとして、隣接するI/Oバッファの電源電圧および接地電圧を揺らすことになる。

【0005】

SSOノイズを時間軸方向で捉えると、或るI/Oバッファがスイッチングして電源電圧変動および接地電圧変動を引き起こし、これらが時間的に収まらないうちに、隣接するI/Oバッファがスイッチングして電源電圧変動および接地電圧変動を引き起こした場合、これら2個のI/Oバッファのスイッチングによる電源電圧変動および接地電圧変動が助長する方向で重なれば、電源電圧変動および接地電圧変動は大きく成長し、抑制する方向で重なれば、電源電圧変動および接地電圧変動は減衰することになる。

【0006】

したがって、電源線網および接地線網を空間的に忠実にモデリングすることができたとしても、問題になるのが、時間軸方向のスイッチングステミラスの定義方法となる。ここで、I/Oバッファを構成する出力バッファの出力端子電圧を半導体集積回路装置が動作する製品寿命の生涯に渡って超高速に過渡解析することができるのであれば、I/Oバッファがスイッチングする瞬間瞬間の電源電圧変動および接地電圧変動を高精度に解析することができる。

【0007】

しかしながら、半導体集積回路装置の実際の設計においては、半導体集積回路装置に搭載されているインタフェースごとに、たとえば、SDRAMインタフェースやPCIインタフェースごとにI/Oバッファのスイッチング確率を求め、同時にスイッチングする可能性があるI/Oバッファは、同時にスイッチングするとみなすことになる。更に、インタフェース信号のプロトコルが不確かな信号の場合には、同時にスイッチングするという仮定を用いることになり、電源電圧変動および接地電圧変動は、ワースト目に解析することになる。

【0008】

たとえば、特許文献1〜3には、出力バッファの同時スイッチングによる電源電圧変動および接地電圧変動を抑制する技術が開示されている。特許文献1には、出力バッファに接続した逆相電圧生成回路で、出力バッファの電源電圧および接地電圧を検出し、電源電圧および接地電圧を安定化させる方向に電流を流し込む技術が開示されている。

【0009】

特許文献2には、出力バッファの電源電圧変動および接地電圧変動を検出する回路と、他の出力バッファの同時スイッチングを制御する回路を備える構成が開示されている。特許文献3には、SSOノイズを検出し、SSOノイズを抑制するように、出力バッファを駆動するフリップフロップへのクロック供給を調整する技術が開示されている。

【0010】

半導体集積回路装置の設計においては、SSOノイズ検証モデルを用いて過渡解析された電源電圧変動および接地電圧変動は、そのままでは、使いものにならない。電源電圧変動および接地電圧変動を、時間軸方向の変動、即ち、SSOノイズによる出力バッファの遅延変動に焼きなおす必要がある。

【0011】

図7は従来の半導体集積回路装置の一例の一部分の概略的レイアウト図である。図1中、1、2は外部電源電圧VDE(たとえば、3.5V)が印加されるVDE電源パッド、3、4は外部接地電圧VSSが印加されるVSS電源パッド、5〜14は信号パッドである。

【0012】

15、16はVDE電源セルであり、VDE電源セル15はVDE電源パッド1に接続され、VDE電源セル16はVDE電源パッド2に接続されている。17、18はVSS電源セルであり、電源セル17はVSS電源パッド3に接続され、VSS電源セル18はVSS電源パッド4に接続されている。

【0013】

19〜28は同一構成のI/Oバッファ、19A〜28AはI/Oバッファ19〜28を構成する出力バッファであり、I/Oバッファ19〜28を構成している入力バッファは図示を省略している。29はVDE電源線、30はVSS電源線である。

【0014】

出力バッファ19A〜28AのVDE電源端子はVDE電源線29に接続され、VDE電源線29はVDE電源セル15、16に接続されている。また、出力バッファ19A〜28AのVSS電源端子はVSS電源線30に接続され、VSS電源線30はVSS電源セル17、18に接続されている。

【0015】

図7に示す従来の半導体集積回路装置においては、VDE電源セル15とVSS電源セル17は隣接して配置され、VDE電源セル16とVSS電源セル18は隣接して配置されている。そして、I/Oバッファ20〜27は、VDE電源セル15とVSS電源セル17からなるVDE/VSS電源セル部と、VDE電源セル16とVSS電源セル18からなるVDE/VSS電源セル部との間に配置されている。これらI/Oバッファ20〜27はSSOグループとされ、SSOノイズ解析を行う場合の単位とされる。

【0016】

図8は出力バッファ20A〜27Aに同時に入力信号を与えてI/Oバッファ20〜27を同時スイッチングさせた場合の電圧波形図であり、出力バッファ20Aにおける入力端子電圧波形41と、VDE電源端子電圧波形42と、VSS電源端子電圧波形43と、出力端子電圧波形44を示している。

【0017】

チップの面積が許すのであれば、I/Oバッファ1つに1個のVDE/VSS電源セル部を配置し、電源電圧変動および接地電圧変動に強い半導体集積回路装置を形成することが可能であるが、現実的には、4〜8個のI/Oバッファに1組のVDE/VSS電源セル部を配置するに留まっている。

【0018】

ここで、VDE電源セルおよびVSS電源セルに流れる電流は、VDE/VSS電源セル部間に配置されたSSOグループのI/Oバッファ数に比例するが、電源電圧変動および接地電圧変動は、VDE電源セルおよびVSS電源セル、VDE電源セルおよびVSS電源セルに繋がるI/Oバッファ、VDE電源パッドおよびVSS電源パッド、ボンディングワイヤ、リードフレームおよび半田ボールを経由してプリント基板に至る電源経路および接地経路のネットワークの全体で決まることになる。

【0019】

そこで、SSOノイズ低減方法として、SSOグループ単位で、(1)I/Oバッファ数の削減、(2)VDE電源セル、VSS電源セルおよび半田ボールの増設、(3)VDE電源線およびVSS電源線のインダクタンスの削減、(4)外部負荷条件の見直しによる外部負荷容量の低減(たとえば、プリント基板上の配線分岐枝の見直しや、外部デバイスの接続個数の削減)、(5)出力バッファの駆動能力の低下などの措置が採られることになる。

【0020】

図9は図7に示す出力バッファ20A〜27Aに同時に入力信号を与えてI/Oバッファ20〜27を同時スイッチングさせた場合の電圧波形図であり、図9中、45は出力バッファ20A〜27Aの入力端子電圧波形、46は出力バッファ20AのVDE電源端子電圧波形、47は出力バッファ21AのVDE電源端子電圧波形、48は出力バッファ22AのVDE電源端子電圧波形、49は出力バッファ23AのVDE電源端子電圧波形である。

【0021】

また、50は出力バッファ20AのVSS電源端子電圧波形、51は出力バッファ21AのVSS電源端子電圧波形、52は出力バッファ22AのVSS電源端子電圧波形、53は出力バッファ23AのVSS電源端子電圧波形、54は出力バッファ20Aの出力端子電圧波形、55は出力バッファ21Aの出力端子電圧波形、56は出力バッファ22Aの出力端子電圧波形、57は出力バッファ23Aの出力端子電圧波形を示している。

【0022】

図9から分るように、出力バッファ20A〜23Aにおいては、VDE電源セル15およびVSS電源セル16から遠くなるほど、VDE変動およびVSS変動が大きくなっている。その結果、出力バッファ20A〜23Aの遅延変動は、VDE電源セル15およびVSS電源セル16から遠くなる方が大きくなる。

【0023】

図10はI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための回路モデルを示す図である。図10中、61はI/Oバッファ、62は出力バッファであり、入力バッファは図示を省略している。

【0024】

63はI/Oバッファ61の入力端子(出力バッファ62の入力端子)、64はI/Oバッファ61のVDE電源端子、65はI/Oバッファ61のVSS電源端子、66はI/Oバッファ61の入出力端子(出力バッファ62の出力端子)、67はI/Oバッファ61のVDE電源端子64に与えるVDE変動波形を出力するVDE変動波形出力手段、68はI/Oバッファ61のVSS電源端子65に与えるVSS変動波形を出力するVSS変動波形出力手段である。

【0025】

VDE変動波形出力手段67は、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合にVDE電源端子64に生じるVDE変動波形を出力するものである。VSS変動波形出力手段68は、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合にVSS電源端子65に生じるVSS変動波形を出力するものである。

【0026】

図10に示す回路モデルは、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合に生じるI/Oバッファ61のVDE電源端子電圧の揺れおよびVSS電源端子電圧の揺れをそれぞれ折れ線でモデル化したものであり、出力バッファ62に入力する入力信号INをスイープすることで、出力バッファ62の遅延がどのように変化するかを調査する場合に使用される。

【0027】

即ち、SSOノイズによるVDE変動およびVSS変動が時間とI/Oバッファの配置位置によって変化することは前述したが、実際の出力バッファの遅延を解析する上では、それぞれのI/OバッファのVDE電源端子、VSS電源端子の揺れを折れ線でモデル化し、出力バッファに与える入力信号INをスイープすることにより、出力バッファの遅延がどのように変化するかが調査される。

【0028】

この場合、入力信号INをスイープする範囲が問題であり、狭すぎるとVDE電源端子電圧およびVSS電源端子電圧の大きな変動を見逃すことになる。反対に広くすると、本来動作しないスイッチングタイミングまで見てしまうことになる。したがって、入力信号INをスイープする範囲の決め方が、SSOノイズによる出力バッファの遅延変動の解析における問題となる。

【0029】

図11は図10に示す回路モデルのシミュレーション結果を示す電圧波形図である。図11中、70は入力信号INの電圧波形、71はVDE電源端子64の電圧波形、72はVSS電源端子65の電圧波形、73は出力信号OUTの電圧波形(入出力端子66の電圧波形)である。

【0030】

70A1〜70E1は入力信号INの立ち下がりエッジであり、70A1は入力信号INの基準点T0から入力信号INが最初に遷移するタイミングまでの時間差、いわゆるスキューを1.0nsecとした場合、70B1はスキューを1.5nsecとした場合、70C1はスキューを2.0nsecとした場合、70D1はスキューを2.5nsecとした場合、70E1はスキューを3.0nsecとした場合である。

【0031】

70A2〜70E2は入力信号INの立ち上がりエッジであり、70A2はスキューを1.0nsecとした場合、70B2はスキューを1.5nsecとした場合、70C2はスキューを2.0nsecとした場合、70D2はスキューを2.5nsecとした場合、70E2はスキューを3.0nsecとした場合である。

【0032】

73A1〜73E1は出力信号OUTの立ち下がりエッジであり、73A1は入力信号INのスキューが1.0nsecの場合、73B1は入力信号INのスキューが1.5nsecの場合、73C1は入力信号INのスキューが2.0nsecの場合、73D1は入力信号INのスキューが2.5nsecの場合、73E1は入力信号INのスキューが3.0nsecの場合である。

【0033】

73A2〜73E2は出力信号OUTの立ち上がりエッジであり、73A2は入力信号INのスキューが1.0nsecの場合、73B2は入力信号INのスキューが1.5nsecの場合、73C2は入力信号INのスキューが2.0nsecの場合、73D2は入力信号INのスキューが2.5nsecの場合、73E2は入力信号INのスキューが3.0nsecの場合である。

【0034】

図12は図11に示すシミュレーション結果を別の視点から示す図であり、横軸に入力信号INのスキュー、左縦軸に出力バッファ62の遅延時間、右縦軸にVDE電源端子64の電圧およびVSS電源端子65の電圧を取った場合を示している。

【0035】

図12中、75はVDE電源端子64の電圧波形、76はVSS電源端子65の電圧波形、77は出力バッファ62の立ち上がり遅延(入力信号INの立ち上がりエッジに対する出力信号OUTの立ち上がりエッジの遅延時間)、78は出力バッファ62の立ち下がり遅延(入力信号INの立ち下がりエッジに対する出力信号OUTの立ち下がりエッジの遅延時間)を示している。

【0036】

図13は図11に示すシミュレーション結果を更に別の視点から示す図であり、横軸に入力信号INのスキュー、左縦軸に出力バッファ62の遅延変動“ΔDelay”、即ち、出力バッファ62のVDE/VSS変動波形下での遅延と電圧変動のない理想電源下での遅延との差、右縦軸にVDE電源端子64の電圧とVSS電源端子65との差電圧“VDE−VSS”を取った場合を示している。

【0037】

図13中、80はVDE電源端子64の電圧とVSS電源端子65の電圧との差“VDE−VSS”の電圧波形、81は出力バッファ62の立ち上がり遅延変動“ΔDelay”、即ち、「(出力バッファ62のVDE/VSS変動波形下での立ち上がり遅延)−(電圧変動のない理想電源下での立ち上がり遅延)」、82は出力バッファ62の立ち下がりエッジ遅延変動“ΔDelay”、即ち、「(出力バッファ62のVDE/VSS変動波形下での立ち下がり遅延)−(電圧変動のない理想電源下の立ち下がり遅延)」を示している。

【0038】

ここで、図11は出力バッファ62の遅延とVDE変動およびVSS変動の相関性を示しているが、入力信号INをスイープしながら出力バッファ62の立ち上がり遅延および立ち下がり遅延を見たものが図12である。本例では、VDE変動波形出力手段67およびVSS変動波形出力手段68は、入力信号INのスキューが2nsecの場合に変動が最も大きくなるVDE変動波形およびVSS変動波形を出力しているので、入力信号が2nsecのスキューで動作したときの出力バッファ62の遅延が最も大きくなる。

【0039】

これは、図13に示すように、右縦軸にVDE電源端子64の電圧とVSS電源端子65との差電圧“VDE−VSS”を取った場合の出力バッファ62の遅延変動ΔDelayを示した方が分り易く、図13によれば、「VDE−VSS」が落ち込んだところで、出力バッファ62の遅延変動が最も大きくなる(遅れている)ことが読み取れる。

【特許文献1】特開平5−335927号公報

【特許文献2】特開昭61−82454号公報

【特許文献3】特開2006−14065号公報

【発明の開示】

【発明が解決しようとする課題】

【0040】

ところで、今まで述べたI/Oバッファの同時スイッチングによる出力バッファの遅延変動の解析は、非常に悲観的な方法と言わざるを得ない。なぜなら、空間的視点からは、I/Oバッファの置かれた位置による電源線網および接地線網の強度が問題となり、時間的視点からは、VDE変動波形およびVSS変動波形を与え、入力信号をスイープさせる範囲が問題となり、出力バッファの遅延変動算出問題からは、理想電源下の出力バッファ遅延と比べることが問題となるからである。

【0041】

これらの問題を解決し、半導体集積回路装置のオーバーマージンな設計を回避するためには、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出することが必要である。

【0042】

本発明は、かかる点に鑑み、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができるようにした半導体集積回路装置および出力バッファ遅延変動検出方法を提供することを目的とする。

【課題を解決するための手段】

【0043】

本発明中、第1の発明は、複数のI/Oバッファを備える半導体集積回路装置であって、各I/Oバッファを構成する出力バッファ毎に、前記出力バッファの電源端子電圧、接地端子電圧および出力端子電圧と基準電圧とから、前記複数のI/Oバッファの同時スイッチングによる前記出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成する出力バッファ遅延変動検出用信号生成回路を備えるものである。

【0044】

本発明中、第2の発明は、第1の発明において、前記出力バッファ遅延変動検出用信号生成回路は、前記接地端子電圧と前記出力端子電圧との電圧差を検出する第1の差動アンプと、前記出力端子電圧と前記電源端子電圧との電圧差を検出する第2の差動アンプと、前記基準電圧と前記出力端子電圧との電圧差を検出する第3の差動アンプとを備えるものである。

【0045】

本発明中、第3の発明は、第2の発明において、前記第1の差動アンプ、前記第2の差動アンプおよび前記第3の差動アンプの接地端子は、前記出力バッファの接地端子と分離されているものである。

【0046】

本発明中、第4の発明は、第2の発明又は第3の発明の半導体集積回路装置における前記複数のI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出する出力バッファ遅延変動検出方法であって、前記出力バッファの入力信号に対して、前記第1の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と、前記出力バッファの入力信号に対して、前記第2の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程とを含むものである。

【発明の効果】

【0047】

本発明中、第1の発明によれば、出力バッファ遅延変動検出用信号生成回路で、複数のI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成することができる。したがって、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【0048】

本発明中、第2の発明は、第1の差動アンプの出力信号、第2の差動アンプの出力信号および第3の差動アンプの出力信号を出力バッファ遅延変動検出用信号として得るとするものである。

【0049】

ここで、出力バッファの入力信号に対して、第1の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出することにより、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファの遅延変動“ΔDelay”を検出することができる。

【0050】

また、出力バッファの入力信号に対して、第2の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出することにより、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の遅延変動“−ΔDelay”を検出することができる。

【0051】

本発明中、第3の発明によれば、第1の差動アンプ、第2の差動アンプおよび第3の差動アンプの接地端子は、出力バッファの接地端子と分離されているので、出力バッファ遅延変動検出信号として、波形の良好な出力バッファ遅延変動検出用信号を得ることができる。

【0052】

本発明中、第4の発明によれば、出力バッファの入力信号に対して、第1の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程により、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファの遅延変動“ΔDelay”を検出することができる。

【0053】

また、出力バッファの入力信号に対して、第2の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程により、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の遅延変動“−ΔDelay”を検出することができる。

【0054】

したがって、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【発明を実施するための最良の形態】

【0055】

以下、図1〜図6を参照して、本発明の半導体集積回路装置の一実施形態について、本発明の出力バッファ遅延変動検出方法の一実施形態を含めて説明する。

【0056】

図1は本発明の半導体集積回路装置の一実施形態の一部分の概略的レイアウト図である。図1中、101は外部電源電圧VDE(たとえば、3.5V)が印加されるVDE電源パッド、102は外部接地電圧VSSが印加されるVSS電源パッド、103〜107は信号パッド、108は電圧値をVDE/2とする外部基準電圧VREFが印加されるVREF電源パッド、109は後述する出力バッファ遅延変動検出用信号生成回路を構成する差動アンプ専用の外部接地電圧VSSが印加される差動アンプ専用VSS電源パッドである。

【0057】

110はVDE電源セルであり、VDE電源パッド101に接続されている。111はVSS電源セルであり、VSS電源パッド102に接続されている。112〜116は同一構成のI/Oバッファセルであり、117〜121は同一構成のI/Oバッファ、122〜126は同一構成の出力バッファ遅延変動検出用信号生成回路、127はVREF電源セルであり、VREF電源パッド108に接続されている。128は差動アンプ専用VSS電源セルであり、差動アンプ専用VSS電源パッド109に接続されている。

【0058】

129はI/Oバッファ117〜121の内部の出力バッファのハイボルテージトランジスタ(高電圧トランジスタ)回路部に外部電源電圧VDEを供給するVDE電源線、130はI/Oバッファ117〜121の内部の出力バッファのハイボルテージトランジスタ回路部に外部接地電圧VSSを供給するVSS電源線である。

【0059】

131はI/Oバッファ117〜121の内部の出力バッファのロウボルテージトランジスタ(低電圧トランジスタ)回路部および入力バッファに外部電源電圧VDEよりも低電圧の電源電圧VDDを供給するVDD電源線、132はI/Oバッファ117〜121の内部の出力バッファのロウボルテージトランジスタ回路部および入力バッファに接地電圧VSSを供給するVSS電源線である。

【0060】

133は出力バッファ遅延変動検出用信号生成回路122〜126に外部基準電圧VREFを供給するためのVREF電源線であり、VREF電源パッド108に接続されている。134は出力バッファ遅延変動検出用信号生成回路122の内部の差動アンプに差動アンプ専用の接地電圧VSSを供給するための差動アンプ専用VSS電源線であり、差動アンプ専用VSS電源パッド109に接続されている。

【0061】

本例では、出力バッファ遅延変動検出用信号生成回路122〜126をI/Oバッファセル112〜116内に配置しており、既存のレイアウトフローに影響を与えないようにしている。また、隣接して配置されたVDE電源セルおよびVSS電源セルからなるVDE/VSS電源セル部間に配置された複数個のI/OバッファのグループをSSOグループと呼ぶことは前述したが、本例では、更に、SSOグループをスイッチングタイミングが等しい機能ごとに細分化し、VDE電源セル、VSS電源セル、VREF電源セルおよび差動アンプ専用VSS電源セルを配置する単位としてのSSO単位を形成している。

【0062】

SSO単位に属するI/Oバッファは2〜4個が望ましいが、信号パッドネックになる可能性を避けるために、SSOノイズが問題にならないような低速のインタフェースにおいては、SSO単位に属するI/Oバッファを4〜8個あるいは8〜16個と大きくして設計する。いずれにせよ、SSO単位ごとに、VDE電源セル、VSS電源セル、VREF電源セルおよび差動アンプ専用VSS電源セルを配置する。本例では、I/Oバッファ117〜121でSSO単位を形成している。

【0063】

図2は信号パッド103およびI/Oバッファセル112の部分の概略的レイアウト図であり、I/Oバッファセル113〜116も同様に構成されている。図2中、135はI/Oバッファ117内の出力バッファに与える入力信号IN用の入力端子である。

【0064】

136は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP1用の出力端子、137は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP2用の出力端子、138は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP3用の出力端子である。

【0065】

139はVDE電源線129を構成するVDE電源端子であり、I/Oバッファ117内の出力バッファのハイボルテージトランジスタ回路部のVDE電源端子に接続されている。140はVSS電源線130を構成するVSS電源端子であり、I/Oバッファ117内の出力バッファのハイボルテージトランジスタ回路部のVSS電源端子に接続されている。

【0066】

141はVDD電源線131を構成するVDD電源端子であり、I/Oバッファ117内の出力バッファのロウボルテージトランジスタ回路部および入力バッファのVDD電源端子に接続されている。142はVSS電源線132を構成するVSS電源端子であり、I/Oバッファ117内の出力バッファのロウボルテージトランジスタ回路部および入力バッファのVSS電源端子に接続されている。143は入出力端子であり、出力バッファの出力端子及び入力バッファの入力端子に接続されている。

【0067】

出力バッファ遅延変動検出用信号生成回路122は、I/Oバッファ117を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117の遅延を解析するために使用する3個の出力バッファ遅延変動検出用信号SAMP1〜SAMP3を生成するものである。

【0068】

出力バッファ遅延変動検出用信号生成回路122において、144はI/Oバッファ117のVDE電源端子139の電圧を入力するための入力端子であり、I/Oバッファ117のVDE電源端子139に接続されている。145はI/Oバッファ117のVSS電源端子140の電圧を入力するための入力端子であり、I/Oバッファ117のVSS電源端子140に接続されている。

【0069】

146はI/Oバッファ117の入出力端子143の電圧を入力するための入力端子であり、I/Oバッファ117の入出力端子143に接続されている。147は外部基準電圧VREFを入力するためのVREF電源端子であり、VREF電源線133に接続されている。148は差動アンプ専用VSS電源線134を構成する差動アンプ専用VSS電源端子である。

【0070】

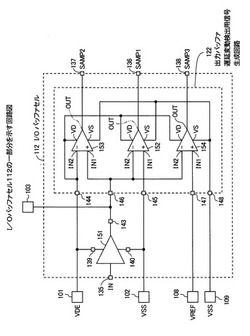

図3はI/Oバッファセル112の一部分を示す回路図であり、I/Oバッファセル113〜116も同様に構成されている。図3中、151はI/Oバッファ117を構成する出力バッファであり、I/Oバッファ117を構成する入力バッファは、図示を省略している。152〜154は出力バッファ遅延変動検出用信号生成回路122を構成する差動アンプである。

【0071】

差動アンプ152は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動を受けている入出力端子143の電圧からVSS電源端子140の電圧変動分をキャンセルし、VDE電源端子139の電圧変動が乗った状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として検出するものである。

【0072】

この差動アンプ152は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をI/Oバッファ117のVSS電源端子電圧入力用の入力端子145に接続し、その反転入力端子IN2をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続し、その出力端子OUTを出力バッファ遅延変動検出用信号SAMP1用の出力端子136に接続している。

【0073】

差動アンプ153は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動を受けている入出力端子143の電圧からVDE電源端子139の電圧変動分をキャンセルし、VSS電源端子140の電圧変動が乗った状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として検出するものである。

【0074】

この差動アンプ153は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続し、その反転入力端子IN2をI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その出力端子OUTを出力バッファ遅延変動検出用信号SAMP2用の出力端子137に接続している。

【0075】

差動アンプ154は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として検出するものである。

【0076】

この差動アンプ154は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をVREF電源入力端子147に接続し、その反転入力端子IN2をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続している。

【0077】

なお、差動アンプ152〜154の電源端子VDをI/Oバッファ117のVDE電源端子139に接続しても問題はないが、差動アンプ152〜154の接地端子VSをI/Oバッファ117のVSS電源端子140に接続してしまうと、良好な電圧波形の出力バッファ遅延変動検出用信号SAMP1〜SAMP3を得ることができない場合がある。

【0078】

そこで、本例では、差動アンプ専用VSS電源パッド109と、差動アンプ専用VSS電源線134を設け、差動アンプ152〜154の接地端子VSを差動アンプ専用VSS電源線134に接続し、差動アンプ152〜154がSSOノイズの影響を受けないようにしている。また、差動アンプ154の非反転入力端子IN1に与える基準電圧VREFもSSOノイズの影響を受けないように、VREF電源パッド108と、VREF電源線133を設け、外部基準電圧VREFを差動アンプ154の非反転入力端子IN1に与えるようにしている。

【0079】

図4は差動アンプ152の回路図であり、差動アンプ153、154も同様に構成されている。図4中、161は差動増幅部、162は差動増幅部161に流れる電流を設定する電流設定部である。差動増幅部161において、163、164は駆動素子であるNMOSトランジスタ、165、166は負荷素子であるPMOSトランジスタ、167は定電流源を構成するNMOSトランジスタである。

【0080】

PMOSトランジスタ165は、ソースを電源端子VDに接続し、ゲートをドレインに接続し、ドレインをNMOSトランジスタ163のドレインに接続している。PMOSトランジスタ166は、ソースを電源端子VDに接続し、ゲートをPMOSトランジスタ165のゲートに接続し、ドレインを出力端子136およびNMOSトランジスタ164のドレインに接続している。

【0081】

NMOSトランジスタ163は、ゲートを非反転入力端子IN1に接続し、ソースをNMOSトランジスタ167のドレインに接続している。NMOSトランジスタ164は、ゲートを反転入力端子IN2に接続し、ドレインをNMOSトランジスタ167のドレインに接続している。NMOSトランジスタ167は、ソースを接地端子VSに接続している。

【0082】

電流設定部162において、168はPMOSトランジスタ、169はNMOSトランジスタである。PMOSトランジスタ168は、ゲートをソースに接続し、ソースを電源端子VDに接続し、ドレインをNMOSトランジスタ169のドレインに接続している。NMOSトランジスタ169は、ゲートをソースに接続し、ソースを接地端子VSに接続している。そして、PMOSトランジスタ168のドレインとNMOSトランジスタ169のドレインとの接続点をNMOSトランジスタ167のゲートに接続している。

【0083】

電流設定部162は、PMOSトランジスタ168のオフ抵抗とNMOSトランジスタ169のオフ抵抗とで構成される分圧回路を利用し、差動増幅部161の定電流源をなすNMOSトランジスタ167のゲートバイアス電圧を生成している。なお、差動アンプ152〜154を構成するMOSトランジスタは、出力バッファのハイボルテージトランジスタ回路部のハイボルテージトランジスタと同様にハイボルテージトランジスタで構成する。

【0084】

図5は出力バッファ遅延変動検出用信号生成回路122の動作を示す電圧波形図であり、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INと、I/Oバッファ117のVDE電源端子139の電圧波形171と、I/Oバッファ117のVSS電源端子140の電圧波形172と、I/Oバッファ117の入出力端子143(出力バッファ151の出力端子)の電圧波形173と、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を示している。

【0085】

ここで、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INに対して、出力バッファ遅延変動検出用信号SAMP1が任意の基準電位をクロスしてから、出力バッファ遅延変動検出用信号SAMP3が任意の基準電位をクロスするまでの時間を測定することにより、出力バッファ151の遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファ151の遅延変動“ΔDelay”を検出することができる。

【0086】

また、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INに対して、出力バッファ遅延変動検出用信号SAMP2が任意の基準電位をクロスしてから、出力バッファ遅延変動検出用信号SAMP3が任意の基準電位をクロスするまでの時間を測定することにより、出力バッファ151の遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の出力バッファ151の遅延変動“−ΔDelay”を検出することができる。

【0087】

本例では、出力バッファ151の遅延変動“ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP1の任意の基準電位をHレベル/Lレベル判定基準電位とし、このHレベル/Lレベル判定基準電位を差動アンプ152の出力レベルの概ね半分の電位(0.5V付近)としている。

【0088】

また、出力バッファ151の遅延変動“−ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP2の任意の基準電位を出力バッファ遅延変動検出用信号SAMP2のHレベル/Lレベル判定基準電位とし、このHレベル/Lレベル判定基準電位を差動アンプ153の出力レベルの概ね半分の電位(1.25V付近)としている。

【0089】

また、出力バッファ151の遅延変動“ΔDelay”、“−ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP3の任意の基準電位を出力バッファ遅延変動検出用信号SAMP2のHレベル/Lベル判定基準電位とし、このHレベル/Lレベル判定基準電位を概ね差動アンプ154の出力レベルの概ね半分の電位(1.75V付近)としている。

【0090】

即ち、本例では、差動アンプ152〜154の入力レベル差(非反転端子IN1・反転端子IN2間のレベル差)がまちまちとなるため、出力バッファ遅延変動検出用信号SAMP1〜SAMP3のHレベルがまちまちとなる。そこで、出力バッファ遅延変動検出用信号SAMP1〜SAMP3のそれぞれについてHレベル/Lレベル判定基準電位を決めている。

【0091】

図6は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP1〜SAMP3の他の例を反転信号/SAMP1〜/SAMP3で示す電圧波形図であり、I/Oバッファ117と同様のI/Oバッファについて、外部基準電圧VREFを0Vとし、かつ、差動アンプ152〜154の駆動能力を高くし、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を電源電圧VDEと接地電圧VSSとの間でフルスイングできるようにした場合の反転出力バッファ遅延変動検出用信号/SAMP1〜/SAMP3を数値計算で求めた場合を示している。

【0092】

この場合には、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を電源電圧VDEと接地電圧VSSとの間でフルスイングできるようにしているので、反転出力バッファ遅延変動検出用信号/SAMP1〜/SAMP3のHレベル/Lレベル判定基準電位を概ねVDE/2(1.75V付近)とし、出力バッファ151の遅延変動“ΔDelay、−ΔDelay”を検出するようにする。

【0093】

以上のように、本発明の半導体集積回路装置の一実施形態によれば、I/Oバッファ117〜121に対応して出力バッファ遅延変動検出用信号生成回路122〜126を備えているので、I/Oバッファ117〜121を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117〜121内の出力バッファの遅延変動を解析するために必要な出力バッファ遅延変動検出用信号SAMP1〜SAMP3を得ることができる。

【0094】

したがって、I/Oバッファ117〜121の実際の配置場所および実際の動作タイミングにおけるI/Oバッファ117〜121を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117〜121内の出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【図面の簡単な説明】

【0095】

【図1】本発明の半導体集積回路装置の一実施形態の一部分の概略的レイアウト図である。

【図2】図1の一部分(1組の信号パッドおよびI/Oバッファセル)の部分の概略的レイアウト図である。

【図3】本発明の半導体集積回路装置の一実施形態が備えるI/Oバッファセルの一部分を示す回路図である。

【図4】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路を構成する差動アンプの回路図である。

【図5】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路の動作を示す電圧波形図である。

【図6】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路が出力する出力バッファ遅延変動検出用信号の他の例を反転信号で示す電圧波形図である。

【図7】従来の半導体集積回路装置の一例の一部分の概略的レイアウト図である。

【図8】図7に示す従来の半導体集積回路装置において、I/Oバッファ内の出力バッファに同時に入力信号を与えてI/Oバッファを同時スイッチングさせた場合の電圧波形図である。

【図9】図7に示す従来の半導体集積回路装置において、I/Oバッファ内の出力バッファに同時に入力信号を与えてI/Oバッファを同時スイッチングさせた場合の電圧波形図である。

【図10】I/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための回路モデルを示す図である。

【図11】図10に示す回路モデルのシミュレーション結果を示す電圧波形図である。

【図12】図11に示すシミュレーション結果を別の視点から示す図である。

【図13】図11に示すシミュレーション結果を更に別の視点から示す図である。

【符号の説明】

【0096】

(図7)

1、2…VDE電源パッド、3、4…VSS電源パッド、5〜14…信号パッド、15、16…VDE電源セル、17、18…VSS電源セル、19〜28…I/Oバッファ、19A〜28A…出力バッファ、29…VDD電源線、30…VSS電源線

(図8)

41…出力バッファの入力端子電圧波形、42…出力バッファのVDE電源端子電圧波形、43…出力バッファのVSS電源端子電圧波形、44…出力バッファの出力端子電圧波形

(図9)

45…出力バッファの入力端子電圧波形、46〜49…出力バッファのVDE電源端子電圧波形、50〜53…出力バッファのVSS電源端子電圧波形、54〜57…出力バッファの出力端子電圧波形

(図10)

61…I/Oバッファ、62…出力バッファ、63…I/Oバッファの入力端子、64…I/OバッファのVDE電源端子、65…I/OバッファのVSS電源端子、66…I/Oバッファの入出力端子、67…VDE変動波形出力手段、68…VSS変動波形出力手段

(図11)

70…入力信号INの電圧波形、71…VDE電源端子の電圧波形、72…VSS電源端子の電圧波形、73…出力信号の電圧波形(入出力端子の電圧波形)、70A1〜70E1…入力信号の立ち下がりエッジ、70A2〜70E2…入力信号の立ち上がりエッジ、73A1〜73E1…出力信号の立ち下がりエッジ、73A2〜73E2…出力信号の立ち上がりエッジ

(図12)

75…VDE電源端子電圧、76…VSS電源端子電圧、77…出力バッファの出力信号の立ち上がり遅延、78…出力バッファの出力信号の立ち下がり遅延

(図13)

80…VDE−VSS、81…出力バッファの出力信号の立ち上がり遅延変動、82…出力バッファの出力信号の立ち下がり遅延変動

(図1〜図3)

101…VDE電源パッド、102…VSS電源パッド、103〜107…信号パッド、108…VREF電源パッド、109…差動アンプ専用VSS電源パッド、110…VDE電源セル、111…VSS電源セル、112〜116…I/Oバッファセル、117〜121…I/Oバッファ、122〜126…出力バッファ遅延変動検出用信号生成回路、127…VREF電源セル、128…差動アンプ専用VSSセル、129…VDE電源線、130…VSS電源線、131…VDD電源線、132…VSS電源線、133…VREF電源線、134…差動アンプ専用VSS電源線、135…I/Oバッファセルの入力端子、136〜138…出力バッファ遅延変動検出用信号用の出力端子、139…I/OバッファのVDE電源端子、140…I/OバッファのVSS電源端子、141…I/OバッファのVDD電源端子、142…I/OバッファのVSS電源端子、143…I/Oバッファの入出力端子、144〜146…入力端子、147…VREF電源端子、148…差動アンプ専用VSS電源端子、151…出力バッファ、152〜154…差動アンプ

(図4)

161…差動増幅部、162…電流設定部、163、164…NMOSトランジスタ、165、166…PMOSトランジスタ、167…NMOSトランジスタ、168…PMOSトランジスタ、169…NMOSトランジスタ

(図5)

171…I/OバッファのVDE電源端子の電圧波形、172…I/OバッファのVSS電源端子の電圧波形、173…I/Oバッファの入出力端子の電圧波形

【技術分野】

【0001】

本発明は、外部装置とのインタフェースをなす入出力バッファ(以下、I/Oバッファという)を備える半導体集積回路装置、および、このような半導体集積回路装置におけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための出力バッファ遅延変動検出方法に関する。

【背景技術】

【0002】

半導体集積回路装置においては、I/Oバッファが同時にスイッチングすると、I/Oバッファの電源電圧および接地電圧に急激な変動が発生する。これらI/Oバッファの電源電圧および接地電圧の急激な変動の大きさは、同時にスイッチングするI/Oバッファの個数や外部負荷条件などに依拠する。なお、I/Oバッファにおいては、出力バッファがスイッチングすると、入力バッファもまた出力バッファの出力信号によりスイッチングする。

【0003】

半導体集積回路装置におけるI/Oバッファの同時スイッチングによる電源電圧変動および接地電圧変動は、半導体集積回路装置の安定動作を阻害するものであり、一般に、同時スイッチングノイズ(SSN[Simultaneous Switching Noise])と呼ばれている。類義語として、SSOノイズ(Simultaneous Switching Output Noise)や、SSIノイズ(Simultaneous Switching Input Noise)がある。

【0004】

半導体集積回路装置の設計においては、SSOノイズ検証が非常に面倒な作業となる。I/Oバッファの同時スイッチングによるI/Oバッファの電源電圧変動および接地電圧変動は、半導体集積回路装置の内部の電源線網および接地線網を伝わって伝搬する。これは、空間的な広がりとして、隣接するI/Oバッファの電源電圧および接地電圧を揺らすことになる。

【0005】

SSOノイズを時間軸方向で捉えると、或るI/Oバッファがスイッチングして電源電圧変動および接地電圧変動を引き起こし、これらが時間的に収まらないうちに、隣接するI/Oバッファがスイッチングして電源電圧変動および接地電圧変動を引き起こした場合、これら2個のI/Oバッファのスイッチングによる電源電圧変動および接地電圧変動が助長する方向で重なれば、電源電圧変動および接地電圧変動は大きく成長し、抑制する方向で重なれば、電源電圧変動および接地電圧変動は減衰することになる。

【0006】

したがって、電源線網および接地線網を空間的に忠実にモデリングすることができたとしても、問題になるのが、時間軸方向のスイッチングステミラスの定義方法となる。ここで、I/Oバッファを構成する出力バッファの出力端子電圧を半導体集積回路装置が動作する製品寿命の生涯に渡って超高速に過渡解析することができるのであれば、I/Oバッファがスイッチングする瞬間瞬間の電源電圧変動および接地電圧変動を高精度に解析することができる。

【0007】

しかしながら、半導体集積回路装置の実際の設計においては、半導体集積回路装置に搭載されているインタフェースごとに、たとえば、SDRAMインタフェースやPCIインタフェースごとにI/Oバッファのスイッチング確率を求め、同時にスイッチングする可能性があるI/Oバッファは、同時にスイッチングするとみなすことになる。更に、インタフェース信号のプロトコルが不確かな信号の場合には、同時にスイッチングするという仮定を用いることになり、電源電圧変動および接地電圧変動は、ワースト目に解析することになる。

【0008】

たとえば、特許文献1〜3には、出力バッファの同時スイッチングによる電源電圧変動および接地電圧変動を抑制する技術が開示されている。特許文献1には、出力バッファに接続した逆相電圧生成回路で、出力バッファの電源電圧および接地電圧を検出し、電源電圧および接地電圧を安定化させる方向に電流を流し込む技術が開示されている。

【0009】

特許文献2には、出力バッファの電源電圧変動および接地電圧変動を検出する回路と、他の出力バッファの同時スイッチングを制御する回路を備える構成が開示されている。特許文献3には、SSOノイズを検出し、SSOノイズを抑制するように、出力バッファを駆動するフリップフロップへのクロック供給を調整する技術が開示されている。

【0010】

半導体集積回路装置の設計においては、SSOノイズ検証モデルを用いて過渡解析された電源電圧変動および接地電圧変動は、そのままでは、使いものにならない。電源電圧変動および接地電圧変動を、時間軸方向の変動、即ち、SSOノイズによる出力バッファの遅延変動に焼きなおす必要がある。

【0011】

図7は従来の半導体集積回路装置の一例の一部分の概略的レイアウト図である。図1中、1、2は外部電源電圧VDE(たとえば、3.5V)が印加されるVDE電源パッド、3、4は外部接地電圧VSSが印加されるVSS電源パッド、5〜14は信号パッドである。

【0012】

15、16はVDE電源セルであり、VDE電源セル15はVDE電源パッド1に接続され、VDE電源セル16はVDE電源パッド2に接続されている。17、18はVSS電源セルであり、電源セル17はVSS電源パッド3に接続され、VSS電源セル18はVSS電源パッド4に接続されている。

【0013】

19〜28は同一構成のI/Oバッファ、19A〜28AはI/Oバッファ19〜28を構成する出力バッファであり、I/Oバッファ19〜28を構成している入力バッファは図示を省略している。29はVDE電源線、30はVSS電源線である。

【0014】

出力バッファ19A〜28AのVDE電源端子はVDE電源線29に接続され、VDE電源線29はVDE電源セル15、16に接続されている。また、出力バッファ19A〜28AのVSS電源端子はVSS電源線30に接続され、VSS電源線30はVSS電源セル17、18に接続されている。

【0015】

図7に示す従来の半導体集積回路装置においては、VDE電源セル15とVSS電源セル17は隣接して配置され、VDE電源セル16とVSS電源セル18は隣接して配置されている。そして、I/Oバッファ20〜27は、VDE電源セル15とVSS電源セル17からなるVDE/VSS電源セル部と、VDE電源セル16とVSS電源セル18からなるVDE/VSS電源セル部との間に配置されている。これらI/Oバッファ20〜27はSSOグループとされ、SSOノイズ解析を行う場合の単位とされる。

【0016】

図8は出力バッファ20A〜27Aに同時に入力信号を与えてI/Oバッファ20〜27を同時スイッチングさせた場合の電圧波形図であり、出力バッファ20Aにおける入力端子電圧波形41と、VDE電源端子電圧波形42と、VSS電源端子電圧波形43と、出力端子電圧波形44を示している。

【0017】

チップの面積が許すのであれば、I/Oバッファ1つに1個のVDE/VSS電源セル部を配置し、電源電圧変動および接地電圧変動に強い半導体集積回路装置を形成することが可能であるが、現実的には、4〜8個のI/Oバッファに1組のVDE/VSS電源セル部を配置するに留まっている。

【0018】

ここで、VDE電源セルおよびVSS電源セルに流れる電流は、VDE/VSS電源セル部間に配置されたSSOグループのI/Oバッファ数に比例するが、電源電圧変動および接地電圧変動は、VDE電源セルおよびVSS電源セル、VDE電源セルおよびVSS電源セルに繋がるI/Oバッファ、VDE電源パッドおよびVSS電源パッド、ボンディングワイヤ、リードフレームおよび半田ボールを経由してプリント基板に至る電源経路および接地経路のネットワークの全体で決まることになる。

【0019】

そこで、SSOノイズ低減方法として、SSOグループ単位で、(1)I/Oバッファ数の削減、(2)VDE電源セル、VSS電源セルおよび半田ボールの増設、(3)VDE電源線およびVSS電源線のインダクタンスの削減、(4)外部負荷条件の見直しによる外部負荷容量の低減(たとえば、プリント基板上の配線分岐枝の見直しや、外部デバイスの接続個数の削減)、(5)出力バッファの駆動能力の低下などの措置が採られることになる。

【0020】

図9は図7に示す出力バッファ20A〜27Aに同時に入力信号を与えてI/Oバッファ20〜27を同時スイッチングさせた場合の電圧波形図であり、図9中、45は出力バッファ20A〜27Aの入力端子電圧波形、46は出力バッファ20AのVDE電源端子電圧波形、47は出力バッファ21AのVDE電源端子電圧波形、48は出力バッファ22AのVDE電源端子電圧波形、49は出力バッファ23AのVDE電源端子電圧波形である。

【0021】

また、50は出力バッファ20AのVSS電源端子電圧波形、51は出力バッファ21AのVSS電源端子電圧波形、52は出力バッファ22AのVSS電源端子電圧波形、53は出力バッファ23AのVSS電源端子電圧波形、54は出力バッファ20Aの出力端子電圧波形、55は出力バッファ21Aの出力端子電圧波形、56は出力バッファ22Aの出力端子電圧波形、57は出力バッファ23Aの出力端子電圧波形を示している。

【0022】

図9から分るように、出力バッファ20A〜23Aにおいては、VDE電源セル15およびVSS電源セル16から遠くなるほど、VDE変動およびVSS変動が大きくなっている。その結果、出力バッファ20A〜23Aの遅延変動は、VDE電源セル15およびVSS電源セル16から遠くなる方が大きくなる。

【0023】

図10はI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための回路モデルを示す図である。図10中、61はI/Oバッファ、62は出力バッファであり、入力バッファは図示を省略している。

【0024】

63はI/Oバッファ61の入力端子(出力バッファ62の入力端子)、64はI/Oバッファ61のVDE電源端子、65はI/Oバッファ61のVSS電源端子、66はI/Oバッファ61の入出力端子(出力バッファ62の出力端子)、67はI/Oバッファ61のVDE電源端子64に与えるVDE変動波形を出力するVDE変動波形出力手段、68はI/Oバッファ61のVSS電源端子65に与えるVSS変動波形を出力するVSS変動波形出力手段である。

【0025】

VDE変動波形出力手段67は、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合にVDE電源端子64に生じるVDE変動波形を出力するものである。VSS変動波形出力手段68は、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合にVSS電源端子65に生じるVSS変動波形を出力するものである。

【0026】

図10に示す回路モデルは、I/Oバッファ61を含むSSOグループのI/Oバッファを同時スイッチングさせた場合に生じるI/Oバッファ61のVDE電源端子電圧の揺れおよびVSS電源端子電圧の揺れをそれぞれ折れ線でモデル化したものであり、出力バッファ62に入力する入力信号INをスイープすることで、出力バッファ62の遅延がどのように変化するかを調査する場合に使用される。

【0027】

即ち、SSOノイズによるVDE変動およびVSS変動が時間とI/Oバッファの配置位置によって変化することは前述したが、実際の出力バッファの遅延を解析する上では、それぞれのI/OバッファのVDE電源端子、VSS電源端子の揺れを折れ線でモデル化し、出力バッファに与える入力信号INをスイープすることにより、出力バッファの遅延がどのように変化するかが調査される。

【0028】

この場合、入力信号INをスイープする範囲が問題であり、狭すぎるとVDE電源端子電圧およびVSS電源端子電圧の大きな変動を見逃すことになる。反対に広くすると、本来動作しないスイッチングタイミングまで見てしまうことになる。したがって、入力信号INをスイープする範囲の決め方が、SSOノイズによる出力バッファの遅延変動の解析における問題となる。

【0029】

図11は図10に示す回路モデルのシミュレーション結果を示す電圧波形図である。図11中、70は入力信号INの電圧波形、71はVDE電源端子64の電圧波形、72はVSS電源端子65の電圧波形、73は出力信号OUTの電圧波形(入出力端子66の電圧波形)である。

【0030】

70A1〜70E1は入力信号INの立ち下がりエッジであり、70A1は入力信号INの基準点T0から入力信号INが最初に遷移するタイミングまでの時間差、いわゆるスキューを1.0nsecとした場合、70B1はスキューを1.5nsecとした場合、70C1はスキューを2.0nsecとした場合、70D1はスキューを2.5nsecとした場合、70E1はスキューを3.0nsecとした場合である。

【0031】

70A2〜70E2は入力信号INの立ち上がりエッジであり、70A2はスキューを1.0nsecとした場合、70B2はスキューを1.5nsecとした場合、70C2はスキューを2.0nsecとした場合、70D2はスキューを2.5nsecとした場合、70E2はスキューを3.0nsecとした場合である。

【0032】

73A1〜73E1は出力信号OUTの立ち下がりエッジであり、73A1は入力信号INのスキューが1.0nsecの場合、73B1は入力信号INのスキューが1.5nsecの場合、73C1は入力信号INのスキューが2.0nsecの場合、73D1は入力信号INのスキューが2.5nsecの場合、73E1は入力信号INのスキューが3.0nsecの場合である。

【0033】

73A2〜73E2は出力信号OUTの立ち上がりエッジであり、73A2は入力信号INのスキューが1.0nsecの場合、73B2は入力信号INのスキューが1.5nsecの場合、73C2は入力信号INのスキューが2.0nsecの場合、73D2は入力信号INのスキューが2.5nsecの場合、73E2は入力信号INのスキューが3.0nsecの場合である。

【0034】

図12は図11に示すシミュレーション結果を別の視点から示す図であり、横軸に入力信号INのスキュー、左縦軸に出力バッファ62の遅延時間、右縦軸にVDE電源端子64の電圧およびVSS電源端子65の電圧を取った場合を示している。

【0035】

図12中、75はVDE電源端子64の電圧波形、76はVSS電源端子65の電圧波形、77は出力バッファ62の立ち上がり遅延(入力信号INの立ち上がりエッジに対する出力信号OUTの立ち上がりエッジの遅延時間)、78は出力バッファ62の立ち下がり遅延(入力信号INの立ち下がりエッジに対する出力信号OUTの立ち下がりエッジの遅延時間)を示している。

【0036】

図13は図11に示すシミュレーション結果を更に別の視点から示す図であり、横軸に入力信号INのスキュー、左縦軸に出力バッファ62の遅延変動“ΔDelay”、即ち、出力バッファ62のVDE/VSS変動波形下での遅延と電圧変動のない理想電源下での遅延との差、右縦軸にVDE電源端子64の電圧とVSS電源端子65との差電圧“VDE−VSS”を取った場合を示している。

【0037】

図13中、80はVDE電源端子64の電圧とVSS電源端子65の電圧との差“VDE−VSS”の電圧波形、81は出力バッファ62の立ち上がり遅延変動“ΔDelay”、即ち、「(出力バッファ62のVDE/VSS変動波形下での立ち上がり遅延)−(電圧変動のない理想電源下での立ち上がり遅延)」、82は出力バッファ62の立ち下がりエッジ遅延変動“ΔDelay”、即ち、「(出力バッファ62のVDE/VSS変動波形下での立ち下がり遅延)−(電圧変動のない理想電源下の立ち下がり遅延)」を示している。

【0038】

ここで、図11は出力バッファ62の遅延とVDE変動およびVSS変動の相関性を示しているが、入力信号INをスイープしながら出力バッファ62の立ち上がり遅延および立ち下がり遅延を見たものが図12である。本例では、VDE変動波形出力手段67およびVSS変動波形出力手段68は、入力信号INのスキューが2nsecの場合に変動が最も大きくなるVDE変動波形およびVSS変動波形を出力しているので、入力信号が2nsecのスキューで動作したときの出力バッファ62の遅延が最も大きくなる。

【0039】

これは、図13に示すように、右縦軸にVDE電源端子64の電圧とVSS電源端子65との差電圧“VDE−VSS”を取った場合の出力バッファ62の遅延変動ΔDelayを示した方が分り易く、図13によれば、「VDE−VSS」が落ち込んだところで、出力バッファ62の遅延変動が最も大きくなる(遅れている)ことが読み取れる。

【特許文献1】特開平5−335927号公報

【特許文献2】特開昭61−82454号公報

【特許文献3】特開2006−14065号公報

【発明の開示】

【発明が解決しようとする課題】

【0040】

ところで、今まで述べたI/Oバッファの同時スイッチングによる出力バッファの遅延変動の解析は、非常に悲観的な方法と言わざるを得ない。なぜなら、空間的視点からは、I/Oバッファの置かれた位置による電源線網および接地線網の強度が問題となり、時間的視点からは、VDE変動波形およびVSS変動波形を与え、入力信号をスイープさせる範囲が問題となり、出力バッファの遅延変動算出問題からは、理想電源下の出力バッファ遅延と比べることが問題となるからである。

【0041】

これらの問題を解決し、半導体集積回路装置のオーバーマージンな設計を回避するためには、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出することが必要である。

【0042】

本発明は、かかる点に鑑み、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができるようにした半導体集積回路装置および出力バッファ遅延変動検出方法を提供することを目的とする。

【課題を解決するための手段】

【0043】

本発明中、第1の発明は、複数のI/Oバッファを備える半導体集積回路装置であって、各I/Oバッファを構成する出力バッファ毎に、前記出力バッファの電源端子電圧、接地端子電圧および出力端子電圧と基準電圧とから、前記複数のI/Oバッファの同時スイッチングによる前記出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成する出力バッファ遅延変動検出用信号生成回路を備えるものである。

【0044】

本発明中、第2の発明は、第1の発明において、前記出力バッファ遅延変動検出用信号生成回路は、前記接地端子電圧と前記出力端子電圧との電圧差を検出する第1の差動アンプと、前記出力端子電圧と前記電源端子電圧との電圧差を検出する第2の差動アンプと、前記基準電圧と前記出力端子電圧との電圧差を検出する第3の差動アンプとを備えるものである。

【0045】

本発明中、第3の発明は、第2の発明において、前記第1の差動アンプ、前記第2の差動アンプおよび前記第3の差動アンプの接地端子は、前記出力バッファの接地端子と分離されているものである。

【0046】

本発明中、第4の発明は、第2の発明又は第3の発明の半導体集積回路装置における前記複数のI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出する出力バッファ遅延変動検出方法であって、前記出力バッファの入力信号に対して、前記第1の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と、前記出力バッファの入力信号に対して、前記第2の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程とを含むものである。

【発明の効果】

【0047】

本発明中、第1の発明によれば、出力バッファ遅延変動検出用信号生成回路で、複数のI/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成することができる。したがって、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【0048】

本発明中、第2の発明は、第1の差動アンプの出力信号、第2の差動アンプの出力信号および第3の差動アンプの出力信号を出力バッファ遅延変動検出用信号として得るとするものである。

【0049】

ここで、出力バッファの入力信号に対して、第1の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出することにより、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファの遅延変動“ΔDelay”を検出することができる。

【0050】

また、出力バッファの入力信号に対して、第2の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出することにより、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の遅延変動“−ΔDelay”を検出することができる。

【0051】

本発明中、第3の発明によれば、第1の差動アンプ、第2の差動アンプおよび第3の差動アンプの接地端子は、出力バッファの接地端子と分離されているので、出力バッファ遅延変動検出信号として、波形の良好な出力バッファ遅延変動検出用信号を得ることができる。

【0052】

本発明中、第4の発明によれば、出力バッファの入力信号に対して、第1の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程により、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファの遅延変動“ΔDelay”を検出することができる。

【0053】

また、出力バッファの入力信号に対して、第2の差動アンプの出力信号が任意の基準電位になる時点と、第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程により、出力バッファの遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の遅延変動“−ΔDelay”を検出することができる。

【0054】

したがって、I/Oバッファの実際の配置場所および実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【発明を実施するための最良の形態】

【0055】

以下、図1〜図6を参照して、本発明の半導体集積回路装置の一実施形態について、本発明の出力バッファ遅延変動検出方法の一実施形態を含めて説明する。

【0056】

図1は本発明の半導体集積回路装置の一実施形態の一部分の概略的レイアウト図である。図1中、101は外部電源電圧VDE(たとえば、3.5V)が印加されるVDE電源パッド、102は外部接地電圧VSSが印加されるVSS電源パッド、103〜107は信号パッド、108は電圧値をVDE/2とする外部基準電圧VREFが印加されるVREF電源パッド、109は後述する出力バッファ遅延変動検出用信号生成回路を構成する差動アンプ専用の外部接地電圧VSSが印加される差動アンプ専用VSS電源パッドである。

【0057】

110はVDE電源セルであり、VDE電源パッド101に接続されている。111はVSS電源セルであり、VSS電源パッド102に接続されている。112〜116は同一構成のI/Oバッファセルであり、117〜121は同一構成のI/Oバッファ、122〜126は同一構成の出力バッファ遅延変動検出用信号生成回路、127はVREF電源セルであり、VREF電源パッド108に接続されている。128は差動アンプ専用VSS電源セルであり、差動アンプ専用VSS電源パッド109に接続されている。

【0058】

129はI/Oバッファ117〜121の内部の出力バッファのハイボルテージトランジスタ(高電圧トランジスタ)回路部に外部電源電圧VDEを供給するVDE電源線、130はI/Oバッファ117〜121の内部の出力バッファのハイボルテージトランジスタ回路部に外部接地電圧VSSを供給するVSS電源線である。

【0059】

131はI/Oバッファ117〜121の内部の出力バッファのロウボルテージトランジスタ(低電圧トランジスタ)回路部および入力バッファに外部電源電圧VDEよりも低電圧の電源電圧VDDを供給するVDD電源線、132はI/Oバッファ117〜121の内部の出力バッファのロウボルテージトランジスタ回路部および入力バッファに接地電圧VSSを供給するVSS電源線である。

【0060】

133は出力バッファ遅延変動検出用信号生成回路122〜126に外部基準電圧VREFを供給するためのVREF電源線であり、VREF電源パッド108に接続されている。134は出力バッファ遅延変動検出用信号生成回路122の内部の差動アンプに差動アンプ専用の接地電圧VSSを供給するための差動アンプ専用VSS電源線であり、差動アンプ専用VSS電源パッド109に接続されている。

【0061】

本例では、出力バッファ遅延変動検出用信号生成回路122〜126をI/Oバッファセル112〜116内に配置しており、既存のレイアウトフローに影響を与えないようにしている。また、隣接して配置されたVDE電源セルおよびVSS電源セルからなるVDE/VSS電源セル部間に配置された複数個のI/OバッファのグループをSSOグループと呼ぶことは前述したが、本例では、更に、SSOグループをスイッチングタイミングが等しい機能ごとに細分化し、VDE電源セル、VSS電源セル、VREF電源セルおよび差動アンプ専用VSS電源セルを配置する単位としてのSSO単位を形成している。

【0062】

SSO単位に属するI/Oバッファは2〜4個が望ましいが、信号パッドネックになる可能性を避けるために、SSOノイズが問題にならないような低速のインタフェースにおいては、SSO単位に属するI/Oバッファを4〜8個あるいは8〜16個と大きくして設計する。いずれにせよ、SSO単位ごとに、VDE電源セル、VSS電源セル、VREF電源セルおよび差動アンプ専用VSS電源セルを配置する。本例では、I/Oバッファ117〜121でSSO単位を形成している。

【0063】

図2は信号パッド103およびI/Oバッファセル112の部分の概略的レイアウト図であり、I/Oバッファセル113〜116も同様に構成されている。図2中、135はI/Oバッファ117内の出力バッファに与える入力信号IN用の入力端子である。

【0064】

136は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP1用の出力端子、137は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP2用の出力端子、138は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP3用の出力端子である。

【0065】

139はVDE電源線129を構成するVDE電源端子であり、I/Oバッファ117内の出力バッファのハイボルテージトランジスタ回路部のVDE電源端子に接続されている。140はVSS電源線130を構成するVSS電源端子であり、I/Oバッファ117内の出力バッファのハイボルテージトランジスタ回路部のVSS電源端子に接続されている。

【0066】

141はVDD電源線131を構成するVDD電源端子であり、I/Oバッファ117内の出力バッファのロウボルテージトランジスタ回路部および入力バッファのVDD電源端子に接続されている。142はVSS電源線132を構成するVSS電源端子であり、I/Oバッファ117内の出力バッファのロウボルテージトランジスタ回路部および入力バッファのVSS電源端子に接続されている。143は入出力端子であり、出力バッファの出力端子及び入力バッファの入力端子に接続されている。

【0067】

出力バッファ遅延変動検出用信号生成回路122は、I/Oバッファ117を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117の遅延を解析するために使用する3個の出力バッファ遅延変動検出用信号SAMP1〜SAMP3を生成するものである。

【0068】

出力バッファ遅延変動検出用信号生成回路122において、144はI/Oバッファ117のVDE電源端子139の電圧を入力するための入力端子であり、I/Oバッファ117のVDE電源端子139に接続されている。145はI/Oバッファ117のVSS電源端子140の電圧を入力するための入力端子であり、I/Oバッファ117のVSS電源端子140に接続されている。

【0069】

146はI/Oバッファ117の入出力端子143の電圧を入力するための入力端子であり、I/Oバッファ117の入出力端子143に接続されている。147は外部基準電圧VREFを入力するためのVREF電源端子であり、VREF電源線133に接続されている。148は差動アンプ専用VSS電源線134を構成する差動アンプ専用VSS電源端子である。

【0070】

図3はI/Oバッファセル112の一部分を示す回路図であり、I/Oバッファセル113〜116も同様に構成されている。図3中、151はI/Oバッファ117を構成する出力バッファであり、I/Oバッファ117を構成する入力バッファは、図示を省略している。152〜154は出力バッファ遅延変動検出用信号生成回路122を構成する差動アンプである。

【0071】

差動アンプ152は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動を受けている入出力端子143の電圧からVSS電源端子140の電圧変動分をキャンセルし、VDE電源端子139の電圧変動が乗った状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として検出するものである。

【0072】

この差動アンプ152は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をI/Oバッファ117のVSS電源端子電圧入力用の入力端子145に接続し、その反転入力端子IN2をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続し、その出力端子OUTを出力バッファ遅延変動検出用信号SAMP1用の出力端子136に接続している。

【0073】

差動アンプ153は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動を受けている入出力端子143の電圧からVDE電源端子139の電圧変動分をキャンセルし、VSS電源端子140の電圧変動が乗った状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として検出するものである。

【0074】

この差動アンプ153は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続し、その反転入力端子IN2をI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その出力端子OUTを出力バッファ遅延変動検出用信号SAMP2用の出力端子137に接続している。

【0075】

差動アンプ154は、I/Oバッファ117のVDE電源端子139の電圧変動およびVSS電源端子140の電圧変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として検出するものである。

【0076】

この差動アンプ154は、その電源端子VDをI/Oバッファ117のVDE電源端子電圧入力用の入力端子144に接続し、その接地端子VSを差動アンプ専用VSS電源端子148に接続し、その非反転入力端子IN1をVREF電源入力端子147に接続し、その反転入力端子IN2をI/Oバッファ117の入出力端子電圧入力用の入力端子146に接続している。

【0077】

なお、差動アンプ152〜154の電源端子VDをI/Oバッファ117のVDE電源端子139に接続しても問題はないが、差動アンプ152〜154の接地端子VSをI/Oバッファ117のVSS電源端子140に接続してしまうと、良好な電圧波形の出力バッファ遅延変動検出用信号SAMP1〜SAMP3を得ることができない場合がある。

【0078】

そこで、本例では、差動アンプ専用VSS電源パッド109と、差動アンプ専用VSS電源線134を設け、差動アンプ152〜154の接地端子VSを差動アンプ専用VSS電源線134に接続し、差動アンプ152〜154がSSOノイズの影響を受けないようにしている。また、差動アンプ154の非反転入力端子IN1に与える基準電圧VREFもSSOノイズの影響を受けないように、VREF電源パッド108と、VREF電源線133を設け、外部基準電圧VREFを差動アンプ154の非反転入力端子IN1に与えるようにしている。

【0079】

図4は差動アンプ152の回路図であり、差動アンプ153、154も同様に構成されている。図4中、161は差動増幅部、162は差動増幅部161に流れる電流を設定する電流設定部である。差動増幅部161において、163、164は駆動素子であるNMOSトランジスタ、165、166は負荷素子であるPMOSトランジスタ、167は定電流源を構成するNMOSトランジスタである。

【0080】

PMOSトランジスタ165は、ソースを電源端子VDに接続し、ゲートをドレインに接続し、ドレインをNMOSトランジスタ163のドレインに接続している。PMOSトランジスタ166は、ソースを電源端子VDに接続し、ゲートをPMOSトランジスタ165のゲートに接続し、ドレインを出力端子136およびNMOSトランジスタ164のドレインに接続している。

【0081】

NMOSトランジスタ163は、ゲートを非反転入力端子IN1に接続し、ソースをNMOSトランジスタ167のドレインに接続している。NMOSトランジスタ164は、ゲートを反転入力端子IN2に接続し、ドレインをNMOSトランジスタ167のドレインに接続している。NMOSトランジスタ167は、ソースを接地端子VSに接続している。

【0082】

電流設定部162において、168はPMOSトランジスタ、169はNMOSトランジスタである。PMOSトランジスタ168は、ゲートをソースに接続し、ソースを電源端子VDに接続し、ドレインをNMOSトランジスタ169のドレインに接続している。NMOSトランジスタ169は、ゲートをソースに接続し、ソースを接地端子VSに接続している。そして、PMOSトランジスタ168のドレインとNMOSトランジスタ169のドレインとの接続点をNMOSトランジスタ167のゲートに接続している。

【0083】

電流設定部162は、PMOSトランジスタ168のオフ抵抗とNMOSトランジスタ169のオフ抵抗とで構成される分圧回路を利用し、差動増幅部161の定電流源をなすNMOSトランジスタ167のゲートバイアス電圧を生成している。なお、差動アンプ152〜154を構成するMOSトランジスタは、出力バッファのハイボルテージトランジスタ回路部のハイボルテージトランジスタと同様にハイボルテージトランジスタで構成する。

【0084】

図5は出力バッファ遅延変動検出用信号生成回路122の動作を示す電圧波形図であり、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INと、I/Oバッファ117のVDE電源端子139の電圧波形171と、I/Oバッファ117のVSS電源端子140の電圧波形172と、I/Oバッファ117の入出力端子143(出力バッファ151の出力端子)の電圧波形173と、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を示している。

【0085】

ここで、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INに対して、出力バッファ遅延変動検出用信号SAMP1が任意の基準電位をクロスしてから、出力バッファ遅延変動検出用信号SAMP3が任意の基準電位をクロスするまでの時間を測定することにより、出力バッファ151の遅延が電圧変動のない理想電源下での遅延よりも大きくなる方向の出力バッファ151の遅延変動“ΔDelay”を検出することができる。

【0086】

また、I/Oバッファ117を含むSSOグループの出力バッファに入力信号INを与えてI/Oバッファ117を含むSSOグループのI/Oバッファを同時スイッチングさせた場合の入力信号INに対して、出力バッファ遅延変動検出用信号SAMP2が任意の基準電位をクロスしてから、出力バッファ遅延変動検出用信号SAMP3が任意の基準電位をクロスするまでの時間を測定することにより、出力バッファ151の遅延が電圧変動のない理想電源下での遅延よりも小さくなる方向の出力バッファ151の遅延変動“−ΔDelay”を検出することができる。

【0087】

本例では、出力バッファ151の遅延変動“ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP1の任意の基準電位をHレベル/Lレベル判定基準電位とし、このHレベル/Lレベル判定基準電位を差動アンプ152の出力レベルの概ね半分の電位(0.5V付近)としている。

【0088】

また、出力バッファ151の遅延変動“−ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP2の任意の基準電位を出力バッファ遅延変動検出用信号SAMP2のHレベル/Lレベル判定基準電位とし、このHレベル/Lレベル判定基準電位を差動アンプ153の出力レベルの概ね半分の電位(1.25V付近)としている。

【0089】

また、出力バッファ151の遅延変動“ΔDelay”、“−ΔDelay”を検出する場合の出力バッファ遅延変動検出用信号SAMP3の任意の基準電位を出力バッファ遅延変動検出用信号SAMP2のHレベル/Lベル判定基準電位とし、このHレベル/Lレベル判定基準電位を概ね差動アンプ154の出力レベルの概ね半分の電位(1.75V付近)としている。

【0090】

即ち、本例では、差動アンプ152〜154の入力レベル差(非反転端子IN1・反転端子IN2間のレベル差)がまちまちとなるため、出力バッファ遅延変動検出用信号SAMP1〜SAMP3のHレベルがまちまちとなる。そこで、出力バッファ遅延変動検出用信号SAMP1〜SAMP3のそれぞれについてHレベル/Lレベル判定基準電位を決めている。

【0091】

図6は出力バッファ遅延変動検出用信号生成回路122が出力する出力バッファ遅延変動検出用信号SAMP1〜SAMP3の他の例を反転信号/SAMP1〜/SAMP3で示す電圧波形図であり、I/Oバッファ117と同様のI/Oバッファについて、外部基準電圧VREFを0Vとし、かつ、差動アンプ152〜154の駆動能力を高くし、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を電源電圧VDEと接地電圧VSSとの間でフルスイングできるようにした場合の反転出力バッファ遅延変動検出用信号/SAMP1〜/SAMP3を数値計算で求めた場合を示している。

【0092】

この場合には、出力バッファ遅延変動検出用信号SAMP1〜SAMP3を電源電圧VDEと接地電圧VSSとの間でフルスイングできるようにしているので、反転出力バッファ遅延変動検出用信号/SAMP1〜/SAMP3のHレベル/Lレベル判定基準電位を概ねVDE/2(1.75V付近)とし、出力バッファ151の遅延変動“ΔDelay、−ΔDelay”を検出するようにする。

【0093】

以上のように、本発明の半導体集積回路装置の一実施形態によれば、I/Oバッファ117〜121に対応して出力バッファ遅延変動検出用信号生成回路122〜126を備えているので、I/Oバッファ117〜121を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117〜121内の出力バッファの遅延変動を解析するために必要な出力バッファ遅延変動検出用信号SAMP1〜SAMP3を得ることができる。

【0094】

したがって、I/Oバッファ117〜121の実際の配置場所および実際の動作タイミングにおけるI/Oバッファ117〜121を含むSSOグループのI/Oバッファの同時スイッチングによるI/Oバッファ117〜121内の出力バッファの遅延変動を容易に検出することができ、オーバーマージンな設計を回避することができる。

【図面の簡単な説明】

【0095】

【図1】本発明の半導体集積回路装置の一実施形態の一部分の概略的レイアウト図である。

【図2】図1の一部分(1組の信号パッドおよびI/Oバッファセル)の部分の概略的レイアウト図である。

【図3】本発明の半導体集積回路装置の一実施形態が備えるI/Oバッファセルの一部分を示す回路図である。

【図4】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路を構成する差動アンプの回路図である。

【図5】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路の動作を示す電圧波形図である。

【図6】本発明の半導体集積回路装置の一実施形態が備える出力バッファ遅延変動検出用信号生成回路が出力する出力バッファ遅延変動検出用信号の他の例を反転信号で示す電圧波形図である。

【図7】従来の半導体集積回路装置の一例の一部分の概略的レイアウト図である。

【図8】図7に示す従来の半導体集積回路装置において、I/Oバッファ内の出力バッファに同時に入力信号を与えてI/Oバッファを同時スイッチングさせた場合の電圧波形図である。

【図9】図7に示す従来の半導体集積回路装置において、I/Oバッファ内の出力バッファに同時に入力信号を与えてI/Oバッファを同時スイッチングさせた場合の電圧波形図である。

【図10】I/Oバッファの同時スイッチングによる出力バッファの遅延変動を検出するための回路モデルを示す図である。

【図11】図10に示す回路モデルのシミュレーション結果を示す電圧波形図である。

【図12】図11に示すシミュレーション結果を別の視点から示す図である。

【図13】図11に示すシミュレーション結果を更に別の視点から示す図である。

【符号の説明】

【0096】

(図7)

1、2…VDE電源パッド、3、4…VSS電源パッド、5〜14…信号パッド、15、16…VDE電源セル、17、18…VSS電源セル、19〜28…I/Oバッファ、19A〜28A…出力バッファ、29…VDD電源線、30…VSS電源線

(図8)

41…出力バッファの入力端子電圧波形、42…出力バッファのVDE電源端子電圧波形、43…出力バッファのVSS電源端子電圧波形、44…出力バッファの出力端子電圧波形

(図9)

45…出力バッファの入力端子電圧波形、46〜49…出力バッファのVDE電源端子電圧波形、50〜53…出力バッファのVSS電源端子電圧波形、54〜57…出力バッファの出力端子電圧波形

(図10)

61…I/Oバッファ、62…出力バッファ、63…I/Oバッファの入力端子、64…I/OバッファのVDE電源端子、65…I/OバッファのVSS電源端子、66…I/Oバッファの入出力端子、67…VDE変動波形出力手段、68…VSS変動波形出力手段

(図11)

70…入力信号INの電圧波形、71…VDE電源端子の電圧波形、72…VSS電源端子の電圧波形、73…出力信号の電圧波形(入出力端子の電圧波形)、70A1〜70E1…入力信号の立ち下がりエッジ、70A2〜70E2…入力信号の立ち上がりエッジ、73A1〜73E1…出力信号の立ち下がりエッジ、73A2〜73E2…出力信号の立ち上がりエッジ

(図12)

75…VDE電源端子電圧、76…VSS電源端子電圧、77…出力バッファの出力信号の立ち上がり遅延、78…出力バッファの出力信号の立ち下がり遅延

(図13)

80…VDE−VSS、81…出力バッファの出力信号の立ち上がり遅延変動、82…出力バッファの出力信号の立ち下がり遅延変動

(図1〜図3)

101…VDE電源パッド、102…VSS電源パッド、103〜107…信号パッド、108…VREF電源パッド、109…差動アンプ専用VSS電源パッド、110…VDE電源セル、111…VSS電源セル、112〜116…I/Oバッファセル、117〜121…I/Oバッファ、122〜126…出力バッファ遅延変動検出用信号生成回路、127…VREF電源セル、128…差動アンプ専用VSSセル、129…VDE電源線、130…VSS電源線、131…VDD電源線、132…VSS電源線、133…VREF電源線、134…差動アンプ専用VSS電源線、135…I/Oバッファセルの入力端子、136〜138…出力バッファ遅延変動検出用信号用の出力端子、139…I/OバッファのVDE電源端子、140…I/OバッファのVSS電源端子、141…I/OバッファのVDD電源端子、142…I/OバッファのVSS電源端子、143…I/Oバッファの入出力端子、144〜146…入力端子、147…VREF電源端子、148…差動アンプ専用VSS電源端子、151…出力バッファ、152〜154…差動アンプ

(図4)

161…差動増幅部、162…電流設定部、163、164…NMOSトランジスタ、165、166…PMOSトランジスタ、167…NMOSトランジスタ、168…PMOSトランジスタ、169…NMOSトランジスタ

(図5)

171…I/OバッファのVDE電源端子の電圧波形、172…I/OバッファのVSS電源端子の電圧波形、173…I/Oバッファの入出力端子の電圧波形

【特許請求の範囲】

【請求項1】

複数の入出力バッファを備える半導体集積回路装置であって、

各入出力バッファを構成する出力バッファ毎に、前記出力バッファの電源端子電圧、接地端子電圧および出力端子電圧と基準電圧とから、前記複数の入出力バッファの同時スイッチングによる前記出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成する出力バッファ遅延変動検出用信号生成回路を備える

ことを特徴とする半導体集積回路装置。

【請求項2】

前記出力バッファ遅延変動検出用信号生成回路は、

前記接地端子電圧と前記出力端子電圧との電圧差を検出する第1の差動アンプと、

前記出力端子電圧と前記電源端子電圧との電圧差を検出する第2の差動アンプと、

前記基準電圧と前記出力端子電圧との電圧差を検出する第3の差動アンプと

を備えることを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記第1の差動アンプ、前記第2の差動アンプおよび前記第3の差動アンプの接地端子は、前記出力バッファの接地端子と分離されている

ことを特徴とする請求項2に記載の半導体集積回路装置。

【請求項4】

請求項2又は3に記載の半導体集積回路装置における前記複数の入出力バッファの同時スイッチングによる出力バッファの遅延変動を検出する出力バッファ遅延変動検出方法であって、

前記出力バッファの入力信号に対して、前記第1の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と、

前記出力バッファの入力信号に対して、前記第2の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と

を含むことを特徴とする出力バッファ遅延変動検出方法。

【請求項1】

複数の入出力バッファを備える半導体集積回路装置であって、

各入出力バッファを構成する出力バッファ毎に、前記出力バッファの電源端子電圧、接地端子電圧および出力端子電圧と基準電圧とから、前記複数の入出力バッファの同時スイッチングによる前記出力バッファの遅延変動を検出するための出力バッファ遅延変動検出用信号を生成する出力バッファ遅延変動検出用信号生成回路を備える

ことを特徴とする半導体集積回路装置。

【請求項2】

前記出力バッファ遅延変動検出用信号生成回路は、

前記接地端子電圧と前記出力端子電圧との電圧差を検出する第1の差動アンプと、

前記出力端子電圧と前記電源端子電圧との電圧差を検出する第2の差動アンプと、

前記基準電圧と前記出力端子電圧との電圧差を検出する第3の差動アンプと

を備えることを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記第1の差動アンプ、前記第2の差動アンプおよび前記第3の差動アンプの接地端子は、前記出力バッファの接地端子と分離されている

ことを特徴とする請求項2に記載の半導体集積回路装置。

【請求項4】

請求項2又は3に記載の半導体集積回路装置における前記複数の入出力バッファの同時スイッチングによる出力バッファの遅延変動を検出する出力バッファ遅延変動検出方法であって、

前記出力バッファの入力信号に対して、前記第1の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と、

前記出力バッファの入力信号に対して、前記第2の差動アンプの出力信号が任意の基準電位になる時点と、前記第3の差動アンプの出力信号が任意の基準電位になる時点との時間差を検出する工程と

を含むことを特徴とする出力バッファ遅延変動検出方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2008−244920(P2008−244920A)

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願番号】特願2007−83316(P2007−83316)

【出願日】平成19年3月28日(2007.3.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願日】平成19年3月28日(2007.3.28)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]