半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置および半導体集積回路装置の製造方法に関し、特に、複数のスタンダードセルを配列して構成されるセルアレイを含む機能装置を備えた半導体集積回路装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

従来、半導体集積回路装置のレイアウト設計にあたり、給電用の拡散層を一方向に延在させ、その間に所望の回路を構成するMOSトランジスタを配置することで、それらをセルとして認識している。このようなセルのレイアウトの一例については、例えば特開2006−253375号公報(特許文献1)に記載されている。また、一方向に延在するように形成された給電用の拡散層を、「タップ」と称することもある。

【0003】

また、特開2006−228982号公報(特許文献2)には、回路を形成するための回路用拡散層を有するスタンダードセルを複数配列する半導体集積回路において、隣接するスタンダードセル同士の回路用拡散層が予め定められた拡散層間隔で配置されるとともに位相シフトによって互いに異なる位相で形成される場合に、その隣接する回路用拡散層の近傍において電源電位または接地電位をとるためのタップ用拡散層を非連続的に形成する技術が開示されている。それにより、パターンの解像度を低下させることなく、位相矛盾等の不具合なく比較的容易にパターンを高集積化している。

【特許文献1】特開2006−253375号公報

【特許文献2】特開2006−228982号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

セルライブラリに登録されているスタンダードセルをアルゴリズムによってセルの高さ方向またはセルの幅方向に配置および配線することによりセルアレイが形成される。

【0005】

本発明者が使用している従来のアルゴリズムでは、セルの高さ方向の結線に2層目の配線または3層目の配線を用いている。しかし、この配線方法では、通り抜け配線を通過させる座標(配線チャンネル)が失われてしまい、半導体集積回路装置の集積度の向上の妨げとなる場合がある。

【0006】

図11は、本発明者が検討したセルの高さ方向に配置された2つのスタンダードセルの配置の一例を示す説明図である。図11(a)はスタンダードセルを回路記号で表した図、図11(b)はスタンダードセルをパターンで表した図である。セルrow上段には2入力NAND回路が配置され、セルrow下段にはインバータ回路が配置されている。

【0007】

セルrow上段の2入力NAND回路6aのゲート電極7N2,7P2とセルrow下段のインバータ回路1aの出力とを接続する場合は、タップ2(Vdd)上に配置される1層目の配線M1とのショートを避けるために2層目の配線M2を用いる。しかし、2層目の配線M2を用いることで、この座標には2層目の配線M2からなる通り抜け配線を配置することができない。そのため、例えば2層目の配線M2が密集した場合には、スタンダードセルの面積を広げるまたはその座標を迂回させて2層目の配線M2を配置するなどの方法によって2入力NAND回路6aとインバータ回路1aとを結線しなくてはならない。その結果、セルアレイの微細化が難しくなり、半導体集積回路装置の集積度の向上の妨げとなっている。

【0008】

また、図11(b)における左右のゲート電極4P,4Nの間には、ゲート電極4N,4Pと同層のダミーゲート電極DGが形成されている。このダミーゲート電極DGは、MISFET上に形成される層間絶縁膜の平坦性を向上させる目的で形成されている。すなわち、ゲート電極4P,4Nの間隔が広すぎる領域に設けられている。このダミーゲート電極DGにより、各ゲート電極の間隔がほぼ一定となり、層間絶縁膜の下地となるゲート電極の疎密差が少なくなる。その結果、層間絶縁膜の厚さの均一性が保たれるので、半導体装置の信頼性が増すことになる。また、このダミーゲート電極DGは、いずれのMISFETとも接続しておらず、インバータを構成する回路に寄与していない。

【0009】

また、本発明者が使用している従来のアルゴリズムでは、セルの幅はスタンダードセル内に部品の全てが収まることを前提に定義されており、スタンダードセル内で基本論理回路または基本機能回路が完結していることが前提となる。

【0010】

図12は、本発明者が検討したセルの幅方向に配置された2つのスタンダードセルの配置の一例を示す説明図であり、スタンダードセルをパターンで表した図である。ここでは、スタンダードセルとしてフリップフロップ回路を例示している。

【0011】

2つのフリップフロップ回路21aはオーバーラップせずに配置されている。そのため、2つのフリップフロップ回路21aをセルの幅方向に並べた場合には、セルの幅×2の面積を必要とする。フリップフロップ回路21aの左側はフリップフロップ回路21aの内部で反転信号を形成するインバータであり、その左端にはタップ22に繋がる電源用(ソース用)の拡散層が配置されている。この電源用の拡散層は他の回路においても電源用の拡散層として活用することが可能ではある。しかし、スタンダードセルの境界条件が複雑となるため、電源用の拡散層の共有化は行われていない。すなわち、スタンダードセルは枠を単位として設計しているために、共有化できる部分があったとしても、その部分は隣接して配列されたスタンダードセル間において互いに分離して扱われている。また、スタンダードセルの境界部分には、ダミーゲート電極DGが形成されている。ダミーゲート電極DGは、図12の左端、中央および右端に図示されている。ダミーゲート電極DGは、いずれのMISFETとも接続しておらず、フリップフロップを構成する回路に寄与していない。従って、デザインルールの変更などがない限り、セルの幅方向のスタンダードセルの微細化は難しく、スタンダードセルを他のスタンダードセルと共有化ができない枠として扱うこの方法では、半導体集積回路装置の集積度の向上を図ることができない。

【0012】

本発明の目的は、半導体集積回路装置の集積度の向上を図ることのできる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0015】

この実施の形態は、複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置である。セルの高さ方向に隣接して上下段に配置される2つのスタンダードセルは、1層目の配線よりも下層の導電体膜を用いて電気的に接続され、セルの高さ方向に1つ以上のスタンダードセルを挟んで上下段に配置される2つのスタンダードセルは、2層目以上の配線を用いて電気的に接続されている。

【0016】

また、この実施の形態は、複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置である。セルの横方向に隣接して左右段に配置される2つのスタンダードセルはミラー配置され、かつ、一方のスタンダードセルを右側に1ピッチずらし、他方のスタンダードセルを左側に1ピッチずらして重ねたオーバーラップ配置されている。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

半導体集積回路装置の集積度の向上を図ることができる。

【発明を実施するための最良の形態】

【0019】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0020】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態においては、電界効果トランジスタを代表するMISFET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型MISFETをpMISと略し、nチャネル型MISFETをnMISと略す。また、以下の実施の形態において説明する1層目の配線および2層目以上の配線は、タングステン膜、アルミニウム合金膜または銅膜などの金属膜によって形成されており、MISFETのゲート電極は、多結晶シリコン膜または多結晶シリコン膜とシリサイド膜との積層膜によって形成されている。

【0022】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0023】

(実施の形態1)

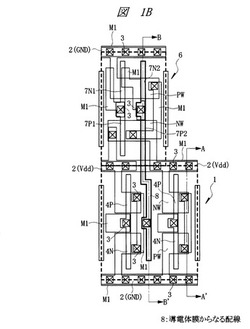

本実施の形態1によるスタンダードセルの配置の一例を図1Aおよび図1Bを用いて説明する。図1Aはスタンダードセルを回路記号で表した図、図1Bはスタンダードセルをパターンで表した図である。この論理回路では、2入力NAND回路(セルrow上段)とインバータ回路(セルrow下段)の2つのスタンダードセルがセルの高さ方向に隣接して配列されている。

【0024】

半導体集積回路装置の設計で使用するスタンダードセルの種類は数十種である。これらの機能、特性および形状などの幾何学的情報は予めセルライブラリに登録されている。半導体集積回路装置を構成する機能ブロックのレイアウト設計では、セルライブラリに登録されたスタンダードセルを部品として使用して、スタンダードセルの配置とスタンダードセルの相互間の配線とによって論理が構成される。従って、同一のデザインルールや製造プロセスのもとでは、同一のスタンダードセルを使用して設計が行われる。

【0025】

本実施の形態1において例示する2入力NAND回路およびインバータ回路はそれぞれ1つのスタンダードセルとして前述したセルライブラリに登録されている。図1Bの一点破線で枠取りした部分の縦横(セルの高さとセルの幅)の寸法及び端子の座標などが、セルライブラリに登録される幾何学的情報である。

【0026】

なお、本実施の形態1においては、一方向に延在するように形成された給電用の拡散層を、「タップ2」と称する。また、上下のタップ2間に複数のMISFETを配置している。これら複数のMISFETは、所望の回路の一部を構成する。上述のスタンダードセルとは、所望の回路を構成するために、これら複数のMISFETが1層目の配線M1によって結線されたものを指す。例えば、図1Aおよび図1Bに示す2入力NAND回路のスタンダードセルは、上下に配置されたタップ2と、各ゲート電極7N1,7P1,7N2,7P2と、各ソース領域と、各ドレイン領域とを有する4つのMISFETと、各MISFETとを結線する1層目の配線M1によって構成されている。ここで、各MISFETを結線する配線には、必要であれば2層目の配線M2や、さらに上層の配線層を使用してもよい。なお、セルの高さ方向にスタンダードセルが隣接する場合、タップ2は上下に隣接するセルで共通となり、2つのタップ2が隣接して配置されることはない。

【0027】

また、本実施の形態1で言うセルの高さは、タップ2と直行する方向のセルの長さであり、1つのセルの一端のタップ2の中心から、そのセルの他端のタップ2の中心までの距離のことである。言い換えれば、一端のタップ2に配置されたコンタクトホール3の中心から、他端のタップ2に配置されたコンタクトホール3の中心までの距離である。

【0028】

また、本実施の形態1では、セルの例として7ピッチセルを挙げる。この7ピッチセルは、上下に配置されたタップ2間を6本の2層目の配線M2が通過可能である。これに、片方のタップ2上の2層目の配線M2を加えて、7本の2層目の配線M2が通過可能なセルとしている。

【0029】

図8には、図1BのA−A’線に沿った要部断面図が示されている。p型半導体基板p−subには、n型半導体領域NiSOが形成されており、n型半導体領域NiSOによって、各半導体素子が形成されるウェル領域が分離されている。n型半導体領域NiSOには、n型ウェル領域NWとp型ウェル領域PWとが形成されている。

【0030】

p型半導体基板p−subには、素子分離領域9が形成されており、これにより主に半導体素子が形成される活性領域が区画されている。素子分離領域9は、p型半導体基板p−subに形成された溝内に、酸化シリコン膜等の絶縁膜が埋め込まれて形成されている。図1Bでは、活性領域を示す領域として、p型ウェル領域PW、n型ウェル領域NWおよびタップ2を示している。

【0031】

n型ウェル領域NWには、複数のpチャネル型電界効果トランジスタ(pMIS)が形成されており、p型ウェル領域PWには、複数のnチャネル型電界効果トランジスタ(nMIS)が形成されている。pMISおよびnMISは、それぞれp型半導体基板p−sub上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、p型半導体基板p−sub内に形成されたソース領域およびドレイン領域とを有する。ゲート絶縁膜は、例えば、酸化シリコン膜で形成されている。ゲート電極は、例えば、多結晶シリコン膜で形成されている。

【0032】

pMISのソース領域またはドレイン領域は、n型ウェル領域NWに形成された低濃度p型半導体領域と高濃度p型半導体領域p+とからなる。本実施の形態1では、説明簡略化のため、pMISのゲート長方向の図示を行っておらず、低濃度p型半導体領域は図示していない。図1BのA−A’線に沿った断面図である図8において、pMISのドレイン領域である高濃度p型半導体領域p+を示している。また、電源電位Vddのタップ2の表面は、n型ウェル領域NWに形成された高濃度n型半導体領域n+が形成されている。この領域は、nMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ2はpMISが形成されるn型ウェル領域NWに電源電位Vddを供給し、一定の電位に固定するように構成されている。これらの高濃度p型半導体領域p+、高濃度n型半導体領域n+およびpMISのゲート電極表面には、シリサイド膜10が形成されている。このシリサイド膜10は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜11が形成され、層間絶縁膜11内にコンタクトホール3が形成され、コンタクトホール3内にプラグ12が形成される。プラグ12は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0033】

nMISのソース領域またはドレイン領域は、p型ウェル領域PWに形成された低濃度n型半導体領域と高濃度n型半導体領域n+とからなる。本実施の形態1では、説明簡略化のため、nMISのゲート長方向の図示を行っておらず、低濃度n型半導体領域は図示していない。図1BのA−A’線に沿った断面図である図8において、nMISのドレイン領域である高濃度n型半導体領域n+を示している。また、基準電位Vssのタップ2の表面は、p型ウェル領域PWに形成された高濃度p型半導体領域p+が形成されている。この領域は、pMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ2はnMISが形成されるp型ウェル領域PWに基準電位Vssを供給し、一定の電位に固定するように構成されている。これらの高濃度n型半導体領域n+、高濃度p型半導体領域p+およびnMISのゲート電極表面には、シリサイド膜10が形成されている。このシリサイド膜10は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜11が形成され、層間絶縁膜11内にコンタクトホール3が形成され、コンタクトホール3内にプラグ12が形成される。プラグ12は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0034】

また、図1Bでは、pMISのソース領域を電源電位Vddのタップ2まで延在し、nMISのソース領域を基準電位Vssのタップ2まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddまたは基準電位Vssを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。

【0035】

また、nMISの駆動電流を増加させる目的で、図1Bの上下方向(A−A’方向)において、p型ウェル領域PWの幅をn型ウェル領域NWの幅よりも広くしても良い。

【0036】

また、1層目の配線M1は、層間絶縁膜13に形成された溝内に、バリアメタル膜および銅を主体とする導電性膜が埋め込まれて形成されている。バリアメタル膜は、タンタル、窒化タンタルまたはそれらの積層膜からなる。また、2層目の配線以降についても、同様の構成である。また、本実施の形態1では、配線とプラグとを別々に形成しているが、先にコンタクトホールと配線用の溝を形成し、その後、バリアメタル膜および銅を主体とする導電性膜を埋め込むことで、一体化して形成しても良い。

【0037】

インバータ回路1は、電源電位や接地電位をとるための拡散層であるタップ2をスタンダードセルの高さ方向の上下にそれぞれ備えている。タップ2はセルの幅方向に沿って形成されており、一方のタップ2に電源電位Vddが供給され、他方のタップ2に基準電位Vss(GND)が供給される。このタップ2上には電源電位用または接地電位用の1層目の配線M1が形成されており、コンタクトホール3を通してタップ2と電気的に接続されている。

【0038】

インバータ回路1は1入力1出力の基本論理回路であり、入力の反転を出力する。本実施の形態1によるインバータ回路1はnMISおよびpMISから構成されるCMISインバータを例示している。nMISのゲート電極4NとpMISのゲート電極4Pとは、これらゲート電極4N,4Pと同一層の導電体膜によって接続されており、インバータ回路1の入力端子となる。すなわち、ゲート電極4N,4Pは一体化して形成されている。この入力端子にはコンタクトホール3を通して1層目の配線M1が接続されている。

【0039】

ゲート電極4N,4Pを構成する導電体膜は、例えば多結晶シリコン膜である。ゲート電極4Nには燐または砒素などのn型導電性の不純物が導入されており、ゲート電極4Pにはボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。また、nMISのドレインとpMISのドレインとはコンタクトホール3を通して、1層目の配線M1によって接続されており、インバータ回路1の出力端子となる。このように、インバータ回路1は、2層目以上の配線を用いずに1層目の配線M1のみで回路形成されている。

【0040】

2入力NAND回路6も同様に、タップ2をセルの高さ方向の上下にそれぞれ備えており、一方のタップ2に電源電位Vddが供給され、他方のタップ2に基準電位Vss(GND)が供給される。また、このタップ2上には電源電位用または基準電位用の1層目の配線M1が形成されており、コンタクトホール3を通してタップ2と電気的に接続されている。セルの高さ方向に配列された2入力NAND回路6とインバータ回路1とは、電源電位Vddを供給するタップ2を共有している。

【0041】

2入力NAND回路6は多入力1出力の基本論理回路であり、すべての入力端子に「1」が入力されたときのみ「0」を出力する。2入力NAND回路6は、CMISインバータのnMIS側に同じnMISを直列に接続し、pMIS側に同じpMISを並列に接続し、そのCMISインバータに追加したnMISのゲート電極とpMISのゲート電極とを接続してもう1つの入力端子としている。nMISのゲート電極7N1とpMISのゲート電極7P1とは、これらゲート電極7N1,7P1と同一層の導電体膜によって接続されており、2入力NAND回路6の1つの入力端子となる。すなわち、ゲート電極7N1,7P1は一体化して形成されている。同様に、nMISのゲート電極7N2とpMISのゲート電極7P2とは、これらゲート電極7N2,7P2と同一層の導電体膜によって接続されており、2入力NAND回路6のもう1つの入力端子となる。すなわち、ゲート電極7N2,7P2は一体化して形成されている。

【0042】

ゲート電極7N1,7N2,7P1,7P2を構成する導電体膜は、例えば多結晶シリコン膜である。ゲート電極7N1,7N2には、燐または砒素などのn型導電性の不純物が導入されており、ゲート電極7P1,7P2には、ボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。2つの入力端子にはコンタクトホール3を通して、それぞれ1層目の配線M1が接続されている。また一方のnMISのドレインとpMISのドレインとの接続には1層目の配線M1を用いる。このように、2入力NAND回路6は、2層目以上の配線を用いずに1層目の配線M1のみで回路形成されている。

【0043】

インバータ回路1の出力端子と2入力NAND回路6の一方の入力端子との接続には、2層目以上の配線を用いずに、nMISのゲート電極4N,7N1,7N2またはpMISのゲート電極4P,7P1,7P2と同一層の導電体膜を用いる。すなわち、インバータ回路1のスタンダードセル内に、インバータ回路1を構成するnMISのゲート電極4NまたはpMISのゲート電極4Pと同一層の導電体膜からなる配線(以下、単に導電体膜からなる配線と記す)8を配置する。この導電体膜からなる配線8に、インバータ回路1の出力端子(nMISのドレインとpMISのドレイン)に接続された1層目の配線M1をコンタクトホール3を通して接続し、さらに、2入力NAND回路6の一方の入力端子(nMISのゲート電極7N2とpMISのゲート電極7P2)を接続する。すなわち、配線8とゲート電極7N2,7P2とは一体化して形成されている。従って、インバータ回路1の出力端子と2入力NAND回路6の入力端子との接続に2層目の配線を用いないことから、その座標に2層目の配線からなる通り抜け配線を配置することができる。また、通り抜け配線が配置できることから、迂回する余分な2層目の配線を形成する必要がなくなり、2層目の配線の使用頻度を7%程度少なくすることが可能となる。

【0044】

これにより、例えば2層目の配線が密集した場合においても、スタンダードセルの面積を広くすることなくまたはその座標を迂回させることなく2層目の配線を配置することができるので、半導体集積回路装置の集積度を向上させることができる。また、2層目の配線の迂回による配線容量の増大を防ぐことができるので、半導体集積回路装置の動作電力の削減または動作速度の向上を図ることができる。ここでの説明は省略しているが、セルの幅方向に配置された2つのスタンダードセルは1層目の配線M1を用いて電気的に接続される。

【0045】

図9は、図1BのB−B’線に沿った断面図である。前述したように、配線8とゲート電極7N2,7P2とは一体化して形成されている。この一体化したゲート電極は、タップ2(Vdd)を横断するように設けられている。一体化したゲート電極のうち、配線8にあたる部分は、タップ2(Vdd)より下の領域に設けられており、素子分離領域9上に位置している。また、配線8は、図1Bの左右のゲート電極4P,4Nの間に位置している。

【0046】

この配線8は、MISFET上に形成される層間絶縁膜の平坦性を向上させる目的で形成されている。すなわち、ゲート電極4P,4Nの間隔が広すぎる領域に設けられており、ダミーゲート電極として機能している。このダミーゲート電極により、各ゲート電極の間隔がほぼ一定となり、層間絶縁膜の下地となるゲート電極の疎密差が少なくなる。その結果、層間絶縁膜の厚さの均一性が保たれるので、半導体装置の信頼性が増すことになる。

【0047】

しかし、本実施の形態1における配線8は、図11(b)の課題に示したダミーゲート電極DGとは異なり、他のMISFETと接続するための配線の役割も担っている。図9に示すように、配線8上にはコンタクトホール3およびプラグ12が設けられており、1層目の配線M1と接続している。

【0048】

また、本実施の形態1では、配線8はゲート電極7P2側に形成されているので、ゲート電極7P2と同様に、p型の導電性の不純物が導入されている。また、配線8の表面にはシリサイド膜が形成されている。一体化されたゲート電極の場合、n型不純物とp型不純物との境界部分において、シリサイド膜の凝集が起こりやすくなる場合があり、シリサイド膜が断線する場合がある。従って、一体化されたゲート電極では、出来る限りn型不純物とp型不純物の境界部分を作らないことが好ましい。よって、本実施の形態1では、一体化されたゲート電極のうち、配線8とゲート電極7P2とを同一の導電型としている。

【0049】

つまり、何も考慮しなければ、n型ウェル領域NW上の配線8には、ゲート電極4Pと同様にp型の不純物が導入され、p型ウェル領域PW上の配線8には、ゲート電極4Nと同様にn型の不純物が導入されることになる。そうすると、配線8にn型の不純物とp型の不純物との境界部分が形成されることになるので、上記のシリサイド膜の凝集の問題が発生する確率が高まることとなる。以上より、配線8は、ゲート電極7P2と同一の導電型の不純物で構成されていることがより好ましい。また、これらのゲート電極の導電型は、ゲート電極へのイオン注入と、ソース領域およびドレイン領域を形成する際のイオン注入によって導入される不純物で決定されるが、できるだけ、ゲート電極7P2と同様となることが好ましい。すなわち、配線8には、低濃度p型半導体領域および高濃度p型半導体領域p+を形成する際の不純物のみを導入し、低濃度n型半導体領域および高濃度n型半導体領域n+を形成する際の不純物は導入しないようにすることが好ましい。

【0050】

ところで、インバータ回路1の出力端子と2入力NAND回路6の入力端子との接続に導電体膜からなる配線8を用いた場合、インバータ回路1と2入力NAND回路6とが共有するタップ2を導電体膜からなる配線8が跨ぐことになる。タップ2はウェルと同じ導電型の拡散層から形成されていることから、この交差領域にMISFETが形成されてしまう。しかし、このMISFETが半導体集積回路装置の動作に影響を及ぼすことはないと考えられることから、タップ2上に導電体膜からなる配線8を配置したままでもよい。本実施の形態1では、図1Bおよび図8に示すように、タップ2(Vdd)は、n型ウェル領域NWと高濃度n型半導体領域n+とから形成されている。従って、タップ2を横断する配線8が形成されても、ディプレッション型のMISFETとなるため、タップ2(Vdd)は導通が確保される。しかし、配線8に供給される電位が強く、その影響が懸念される場合には、図1に示したように、上記交差領域のタップ2を削除した方が好ましい。

【0051】

タップ2の削除方法の一例を図2に示す模式図を用いて説明する。まず、2つのスタンダードセルをセルrow上段とセルrow下段に隣接して配置する。例えばセルrow上段が2入力NAND回路6、セルrow下段がインバータ回路1の場合であれば、2入力NAND回路6の一方の入力端子とインバータ回路1の出力端子とは、導電体膜からなる配線8により接続されてタップ2上に導電体膜からなる配線8が配置される。次に、タップ2上のMISFETを図形認識させる。タップ2上にMISFETが図面認識されると、図形認識されたMISFET下のタップ2を構成する拡散層が消去される。このような簡易な図形処理により、タップ2と導電体膜からなる配線8との交差領域のタップ2を削除することができる。

【0052】

なお、導電体膜からなる配線8に多結晶シリコン膜を用いる場合、その抵抗は金属膜からなる2層目の配線よりも抵抗が高くなる。そのため、図3の模式図に示すように、セルの高さ方向に隣接して配置されるスタンダードセル間の結線には導電体膜からなる配線8を用い、セルの高さ方向に1つ以上のスタンダードセルを挟んで配置されるスタンダードセル間の結線には2層目の配線M2または3層目以上の配線を用いることが好ましい。

【0053】

(実施の形態2)

本実施の形態2によるスタンダードセルの配置の一例を図4を用いて説明する。図4は、セルの幅方向に配置された2つのフリップフロップ回路の配置を示す説明図であり、フリップフロップ回路をパターンで表した図である。

【0054】

図4に示すように、フリップフロップ回路21は、電源電位や接地電位をとるための拡散層であるタップ22をセルの高さ方向の上下にそれぞれ備えている。タップ22は、前述の実施の形態1で示したタップ2と同様の構成であり、セルの幅方向(セルの高さ方向と直交する方向)に沿って形成されている。一方のタップ22には電源電位Vddが供給され、他方のタップ22には基準電位Vss(GND)が供給される。このタップ22上には1層目の配線M1が形成されており、コンタクトホール23を通してタップ22と電気的に接続されている。

【0055】

また、図4に示すように、セルの幅方向に配置された2つのフリップフロップ回路21は、一方のセルを左右対称に折り返すように配置している。すなわち、一方のセルを、セルの幅方向に反転させるように配置している。そして、一方のフリップフロップ回路21を右側に1ピッチずらし、他方のフリップフロップ回路21を左側に1ピッチずらして重ねたオーバーラップ配置されている。すなわち、一方のフリップフロップ回路21の端部に配置されたMISFETのソース領域と、他方のフリップフロップ回路21の端部に配置されたMISFETのソース領域とを共通にしている。図4では、共通のソース領域として、拡散層25Vと拡散層25Gとを図示している。また、これにより、前述の図12に示した中央部のダミーゲート電極DGも配置する必要が無くなる。

【0056】

また、図10は図4のC−C’線に沿った断面図を示しており、インバータ24A,24Bのソース領域を共通化した際の、ソース領域の断面図を示している。拡散層25Vは電源電位Vddのタップ22まで延在し、拡散層25Gは基準電位Vss(GND)のタップ22まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddまたは基準電位Vssを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。

【0057】

このようにして、図4に示した本実施の形態2によるオーバーラップ配置を採用した2つのフリップフロップ回路21の配置例は、前述の図12に示した従来のオーバーラップ配置を採用しない2つのフリップフロップ回路21aの配置例と比較すると、セルの幅方向の長さを2ピッチ短くすることができる。例えばオーバーラップ配置を採用しない2つのフリップフロップ回路21aのセルの幅方向のピッチが42ピッチであり、オーバーラップ配置を採用することにより2つのフリップフロップ回路21のセルの幅方向のピッチが40ピッチとなった場合は、セルの幅方向の長さは4%程度縮小する。

【0058】

オーバーラップさせる領域は、セルの幅方向の左側または右側に配置されるスタンダードセルの電源部分が望ましい。すなわち、フリップフロップ回路21を構成するMISFETのソース領域を共通化させることが望ましい。本実施の形態2によるオーバーラップ配置された2つのフリップフロップ回路21では、セルの幅方向の左側または右側に配置された電源電位Vddに接続される電源用の拡散層および基準電位Vss(GND)に接続される接地用の拡散層をオーバーラップさせている。

【0059】

図4に示すように、2つのフリップフロップ回路21が接する部分(紙面上左に配置された第1フリップフロップ回路21Aでは右側、紙面上右に配置された第2フリップフロップ回路21Bでは左側)には、フリップフロップ回路21の内部で反転信号を形成するインバータが配置されている。紙面上左に配置された第1フリップフロップ回路21Aの右側に配置された第1インバータ24Aの右端には電源用の拡散層25Vと接地用の拡散層25Gとが配置されており、紙面上右に配置された第2フリップフロップ回路21Bの左側に配置された第2インバータ24Bの左端には電源用の拡散層25Vと接地用の拡散層25Gとが配置されている。第1インバータ24Aの電源用の拡散層25Vと第2インバータ24Bの電源用の拡散層25Vとはオーバーラップして形成されており、電源電位Vddが供給されるタップ22に接続している。同様に、第1インバータ24Aの接地用の拡散層25Gと第2インバータ24Bの接地用の拡散層25Gとはオーバーラップして形成されており、基準電位Vss(GND)が供給されるタップ22に接続している。

【0060】

本実施の形態2によるスタンダードセルの配置の他の例を図5(a)および(b)を用いて説明する。図5(a)は、本実施の形態2によるオーバーラップ配置を採用したセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図であり、図5(b)は、従来のオーバーラップ配置を採用しないセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図である。両図ともに、インバータ回路およびフリップフロップ回路をパターンで表している。

【0061】

前述の図4に示した2つのフリップフロップ回路21の配置と同様に、本実施の形態2によるインバータ回路26とフリップフロップ回路27とはミラー配置され、かつ、互いに1ピッチずつずらして重ねられたオーバーラップ配置されている。従って、図5(a)に示した本実施の形態2によるオーバーラップ配置を採用したインバータ回路26およびフリップフロップ回路27の配置例は、図5(b)に示した従来のオーバーラップ配置を採用しないインバータ回路26aおよびフリップフロップ回路27aの配置例と比較すると、セルの幅方向の長さを2ピッチ短くすることができる。例えばオーバーラップ配置を採用しないインバータ回路26aおよびフリップフロップ回路27aのセルの幅方向のピッチが24ピッチであり、オーバーラップ配置を採用することによりインバータ回路26aおよびフリップフロップ回路27aのセルの幅方向のピッチが22ピッチとなった場合は、セルの幅方向の長さは4%程度縮小する。

【0062】

本実施の形態2によるオーバーラップ配置されたインバータ回路26およびフリップフロップ回路27では、セルの幅方向の左側または右側に配置された電源電位Vddに接続される電源用の拡散層および基準電位Vss(GND)に接続される接地用の拡散層をオーバーラップさせている。

【0063】

図5(a)に示すように、インバータ回路26と接する側のフリップフロップ回路27には、反転信号を形成するインバータが配置されている。このインバータの左端(インバータ回路26と接する側)には電源用の拡散層28Vと接地用の拡散層28Gとが配置されている。インバータ回路26の電源用の拡散層28Vとフリップフロップ回路27のインバータの電源用の拡散層28Vとはオーバーラップして形成されており、電源電位Vddが供給されるタップ22に接続している。同様に、インバータ回路26の接地用の拡散層28Gとフリップフロップ回路27のインバータの接地用の拡散層28Gとはオーバーラップして形成されており、基準電位Vss(GND)が供給されるタップ22に接続している。

【0064】

次に、本実施の形態2による自動レイアウトによるスタンダードセルのオーバーラップ配置の方法について図6および図7を用いて説明する。図6は、本実施の形態2によるスタンダードセルの配置方法の流れを模式的に示した説明図、図7はフリップフロップ回路の一例を示すパターン図である。

【0065】

まず、スタンダードセルの設計データを持つ第1枠F1を用意し、電源部分が共有化できるスタンダードセルの設計データを持つ第2枠F2を用意し、これらをセルライブラリに登録する(図6(a))。第2枠F2に設計される基本論理回路や機能回路では、その右端部または左端部に共有化に適した電源部分のパターンが形成されており、第2枠F2にはオーバーラップ配置の可能性情報が保持されている。第2枠F2のセルの幅方向のピッチは、第1枠F1のセルの幅方向のピッチよりも1ピッチ短く設計されている。

【0066】

例えば図7に示すフリップフロップ回路では、第1枠F1内にはフリップフロップ回路が全て収まっており、第1枠F1内でフリップフロップ回路が完結している。これに対して、第2枠F2内ではフリップフロップ回路が完結せず、紙面上左側に設けられたインバータの電源用の拡散層および接地用の拡散層に、共有化に適した電源部分のパターンが形成されている。

【0067】

次に、第1枠F1のみをセルライブラリから取り出し、配置プログラムに従って適切に配置することによって機能ブロックを構成する(図6(b))。次に、セルの幅方向に隣接する2つの第1枠F1のうち、2つの第2枠F2に置き換えることが可能なセルを選択し、第1枠F1を第2枠F2へ置き換える(図6(c))。第2枠F2に置き換えられない第1枠F1は、置き換えられることなく、そのまま配置される。次に、第2枠F2の配置を補正することにより隣接する第2枠F2を接近させて配置し、第1枠F1を第2枠F2へ置き換えることによって生じた隙間を埋める(図6(d))。これにより、機能ブロック内の第1枠F1および第2枠F2の配置が完成する。

【0068】

その後、第1枠F1内の設計データまたは第2枠F2内の設計データを基に、配線プログラムに従って機能ブロック内のスタンダードセルの相互配線、機能ブロックの入出力端子、電源配線および接地配線などを適切に行い、機能ブロックの配置および配線を完成させる。

【0069】

なお、オーバーラップ配置を採用する基本論理回路または機能回路としては、特に限定されるものではないが、前述したフリップフロップ回路、インバータ回路の他に、AND回路、OR回路、NAND回路、NOR回路、XOR回路またはXNOR回路などの比較的使用頻度が高い基本論理回路とすることが望ましい。これは、オーバーラップ配置を採用する基本論理回路または機能回路の種類を増やすことにより、配置の混乱が生じることが懸念されるためである。オーバーラップ配置を採用する基本論理回路または機能回路を限定したとしても、比較的使用頻度が高い基本論理回路に適用することにより、確実に半導体集積回路装置の面積を縮小することができる。

【0070】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0071】

例えば、前記実施の形態1および2を組み合わせて実施することも可能である。その場合、タップ2の延在方向におけるセル面積の縮小を、さらに効果的に行うことができる。

【0072】

また、前記実施の形態1および2では、スタンダードセルとして7ピッチセルを例に説明したが、これに限定されるものではなく、9ピッチセル、8ピッチセル、6ピッチセルまたは5ピッチセルとしても良く、同様の効果を得ることができる。

【0073】

また、前記実施の形態1および2では、pMISおよびnMISのゲート電極を多結晶シリコン膜で形成する例を示したが、これに限られるものではなく、例えば金属膜で形成してもよい。そのような金属膜としては、Ti、TiN、PtまたはAl等が挙げられる。

【0074】

また、前記実施の形態1および2では、ゲート絶縁膜を酸化シリコン膜で形成した例を示したが、これに限られるものではなく、例えば窒化シリコン膜よりも高い誘電率を有する膜で形成してもよい。そのような高誘電率膜としては、HfO、HfAlO、HfSiAlO、HfSiO、ZrO、ZrAlO、ZrSiO、LaO、LaSiO、TaOまたはTiO等が挙げられる。

【産業上の利用可能性】

【0075】

本発明の半導体集積回路装置は、小型化の進んだスタンダードセルから形成された集積回路を有する半導体集積回路装置に適用することができる。

【図面の簡単な説明】

【0076】

【図1A】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、スタンダードセルを回路記号で表した図である。

【図1B】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、スタンダードセルをパターンで表した要部平面図である。

【図1C】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、図1Bにおける活性領域およびゲート電極のみを示す簡略図である。

【図2】本発明の実施の形態1によるタップの削除方法の一例を説明する模式図である。

【図3】本発明の実施の形態1による2層目の配線と導電体膜からなる配線との使用例を示した模式図である。

【図4】本発明の実施の形態2によるスタンダードセルの配置の一例の説明図であり、スタンダードセルをパターンで表した図である。

【図5】本実施の形態2によるスタンダードセルの配置の他の例の説明図であり、(a)は、本実施の形態2によるオーバーラップ配置を採用したセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図、(b)は、従来のオーバーラップ配置を採用しないセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図である。

【図6】本実施の形態2によるスタンダードセルの配置方法の流れを模式的に示した説明図である。

【図7】本実施の形態2によるフリップフロップ回路の一例を示すパターン図である。

【図8】図1BのA−A’線に沿った断面図である。

【図9】図1BのB−B’線に沿った断面図である。

【図10】図4のC−C’線に沿った断面図である。

【図11】本発明者が検討したスタンダードセルの配置の一例を示す説明図であり、(a)はスタンダードセルを回路記号で表した図、(b)はスタンダードセルをパターンで表した図である。

【図12】本発明者が検討したスタンダードセルの配置の一例を示す説明図であり、スタンダードセルをパターンで表した図である。

【符号の説明】

【0077】

1,1a インバータ回路

2 タップ

3 コンタクトホール

4N,4P ゲート電極

6,6a 2入力NAND回路

7N1,7N2 ゲート電極

7P1,7P2 ゲート電極

8 導電体膜からなる配線(ダミーゲート電極)

9 素子分離領域

10 シリサイド膜

11 層間絶縁膜

12 プラグ

13 層間絶縁膜

21,21a フリップフロップ回路

21A 第1フリップフロップ回路

21B 第2フリップフロップ回路

22 タップ

23 コンタクトホール

24A 第1インバータ

24B 第2インバータ

25V 電源用の拡散層

25G 接地用の拡散層

26,26a インバータ回路

27,27a フリップフロップ回路

28V 電源用の拡散層

28G 接地用の拡散層

DG ダミーゲート電極

F1 第1枠

F2 第2枠

M1 1層目の配線

M2 2層目の配線

n+ 高濃度n型半導体領域

NiSO n型半導体領域

NW n型ウェル領域

p−sub p型半導体基板

p+ 高濃度p型半導体領域

PW p型ウェル領域

Vdd 電源電位

Vss(GND) 基準電位

【技術分野】

【0001】

本発明は、半導体集積回路装置および半導体集積回路装置の製造方法に関し、特に、複数のスタンダードセルを配列して構成されるセルアレイを含む機能装置を備えた半導体集積回路装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

従来、半導体集積回路装置のレイアウト設計にあたり、給電用の拡散層を一方向に延在させ、その間に所望の回路を構成するMOSトランジスタを配置することで、それらをセルとして認識している。このようなセルのレイアウトの一例については、例えば特開2006−253375号公報(特許文献1)に記載されている。また、一方向に延在するように形成された給電用の拡散層を、「タップ」と称することもある。

【0003】

また、特開2006−228982号公報(特許文献2)には、回路を形成するための回路用拡散層を有するスタンダードセルを複数配列する半導体集積回路において、隣接するスタンダードセル同士の回路用拡散層が予め定められた拡散層間隔で配置されるとともに位相シフトによって互いに異なる位相で形成される場合に、その隣接する回路用拡散層の近傍において電源電位または接地電位をとるためのタップ用拡散層を非連続的に形成する技術が開示されている。それにより、パターンの解像度を低下させることなく、位相矛盾等の不具合なく比較的容易にパターンを高集積化している。

【特許文献1】特開2006−253375号公報

【特許文献2】特開2006−228982号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

セルライブラリに登録されているスタンダードセルをアルゴリズムによってセルの高さ方向またはセルの幅方向に配置および配線することによりセルアレイが形成される。

【0005】

本発明者が使用している従来のアルゴリズムでは、セルの高さ方向の結線に2層目の配線または3層目の配線を用いている。しかし、この配線方法では、通り抜け配線を通過させる座標(配線チャンネル)が失われてしまい、半導体集積回路装置の集積度の向上の妨げとなる場合がある。

【0006】

図11は、本発明者が検討したセルの高さ方向に配置された2つのスタンダードセルの配置の一例を示す説明図である。図11(a)はスタンダードセルを回路記号で表した図、図11(b)はスタンダードセルをパターンで表した図である。セルrow上段には2入力NAND回路が配置され、セルrow下段にはインバータ回路が配置されている。

【0007】

セルrow上段の2入力NAND回路6aのゲート電極7N2,7P2とセルrow下段のインバータ回路1aの出力とを接続する場合は、タップ2(Vdd)上に配置される1層目の配線M1とのショートを避けるために2層目の配線M2を用いる。しかし、2層目の配線M2を用いることで、この座標には2層目の配線M2からなる通り抜け配線を配置することができない。そのため、例えば2層目の配線M2が密集した場合には、スタンダードセルの面積を広げるまたはその座標を迂回させて2層目の配線M2を配置するなどの方法によって2入力NAND回路6aとインバータ回路1aとを結線しなくてはならない。その結果、セルアレイの微細化が難しくなり、半導体集積回路装置の集積度の向上の妨げとなっている。

【0008】

また、図11(b)における左右のゲート電極4P,4Nの間には、ゲート電極4N,4Pと同層のダミーゲート電極DGが形成されている。このダミーゲート電極DGは、MISFET上に形成される層間絶縁膜の平坦性を向上させる目的で形成されている。すなわち、ゲート電極4P,4Nの間隔が広すぎる領域に設けられている。このダミーゲート電極DGにより、各ゲート電極の間隔がほぼ一定となり、層間絶縁膜の下地となるゲート電極の疎密差が少なくなる。その結果、層間絶縁膜の厚さの均一性が保たれるので、半導体装置の信頼性が増すことになる。また、このダミーゲート電極DGは、いずれのMISFETとも接続しておらず、インバータを構成する回路に寄与していない。

【0009】

また、本発明者が使用している従来のアルゴリズムでは、セルの幅はスタンダードセル内に部品の全てが収まることを前提に定義されており、スタンダードセル内で基本論理回路または基本機能回路が完結していることが前提となる。

【0010】

図12は、本発明者が検討したセルの幅方向に配置された2つのスタンダードセルの配置の一例を示す説明図であり、スタンダードセルをパターンで表した図である。ここでは、スタンダードセルとしてフリップフロップ回路を例示している。

【0011】

2つのフリップフロップ回路21aはオーバーラップせずに配置されている。そのため、2つのフリップフロップ回路21aをセルの幅方向に並べた場合には、セルの幅×2の面積を必要とする。フリップフロップ回路21aの左側はフリップフロップ回路21aの内部で反転信号を形成するインバータであり、その左端にはタップ22に繋がる電源用(ソース用)の拡散層が配置されている。この電源用の拡散層は他の回路においても電源用の拡散層として活用することが可能ではある。しかし、スタンダードセルの境界条件が複雑となるため、電源用の拡散層の共有化は行われていない。すなわち、スタンダードセルは枠を単位として設計しているために、共有化できる部分があったとしても、その部分は隣接して配列されたスタンダードセル間において互いに分離して扱われている。また、スタンダードセルの境界部分には、ダミーゲート電極DGが形成されている。ダミーゲート電極DGは、図12の左端、中央および右端に図示されている。ダミーゲート電極DGは、いずれのMISFETとも接続しておらず、フリップフロップを構成する回路に寄与していない。従って、デザインルールの変更などがない限り、セルの幅方向のスタンダードセルの微細化は難しく、スタンダードセルを他のスタンダードセルと共有化ができない枠として扱うこの方法では、半導体集積回路装置の集積度の向上を図ることができない。

【0012】

本発明の目的は、半導体集積回路装置の集積度の向上を図ることのできる技術を提供することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0015】

この実施の形態は、複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置である。セルの高さ方向に隣接して上下段に配置される2つのスタンダードセルは、1層目の配線よりも下層の導電体膜を用いて電気的に接続され、セルの高さ方向に1つ以上のスタンダードセルを挟んで上下段に配置される2つのスタンダードセルは、2層目以上の配線を用いて電気的に接続されている。

【0016】

また、この実施の形態は、複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置である。セルの横方向に隣接して左右段に配置される2つのスタンダードセルはミラー配置され、かつ、一方のスタンダードセルを右側に1ピッチずらし、他方のスタンダードセルを左側に1ピッチずらして重ねたオーバーラップ配置されている。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

半導体集積回路装置の集積度の向上を図ることができる。

【発明を実施するための最良の形態】

【0019】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0020】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態においては、電界効果トランジスタを代表するMISFET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型MISFETをpMISと略し、nチャネル型MISFETをnMISと略す。また、以下の実施の形態において説明する1層目の配線および2層目以上の配線は、タングステン膜、アルミニウム合金膜または銅膜などの金属膜によって形成されており、MISFETのゲート電極は、多結晶シリコン膜または多結晶シリコン膜とシリサイド膜との積層膜によって形成されている。

【0022】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0023】

(実施の形態1)

本実施の形態1によるスタンダードセルの配置の一例を図1Aおよび図1Bを用いて説明する。図1Aはスタンダードセルを回路記号で表した図、図1Bはスタンダードセルをパターンで表した図である。この論理回路では、2入力NAND回路(セルrow上段)とインバータ回路(セルrow下段)の2つのスタンダードセルがセルの高さ方向に隣接して配列されている。

【0024】

半導体集積回路装置の設計で使用するスタンダードセルの種類は数十種である。これらの機能、特性および形状などの幾何学的情報は予めセルライブラリに登録されている。半導体集積回路装置を構成する機能ブロックのレイアウト設計では、セルライブラリに登録されたスタンダードセルを部品として使用して、スタンダードセルの配置とスタンダードセルの相互間の配線とによって論理が構成される。従って、同一のデザインルールや製造プロセスのもとでは、同一のスタンダードセルを使用して設計が行われる。

【0025】

本実施の形態1において例示する2入力NAND回路およびインバータ回路はそれぞれ1つのスタンダードセルとして前述したセルライブラリに登録されている。図1Bの一点破線で枠取りした部分の縦横(セルの高さとセルの幅)の寸法及び端子の座標などが、セルライブラリに登録される幾何学的情報である。

【0026】

なお、本実施の形態1においては、一方向に延在するように形成された給電用の拡散層を、「タップ2」と称する。また、上下のタップ2間に複数のMISFETを配置している。これら複数のMISFETは、所望の回路の一部を構成する。上述のスタンダードセルとは、所望の回路を構成するために、これら複数のMISFETが1層目の配線M1によって結線されたものを指す。例えば、図1Aおよび図1Bに示す2入力NAND回路のスタンダードセルは、上下に配置されたタップ2と、各ゲート電極7N1,7P1,7N2,7P2と、各ソース領域と、各ドレイン領域とを有する4つのMISFETと、各MISFETとを結線する1層目の配線M1によって構成されている。ここで、各MISFETを結線する配線には、必要であれば2層目の配線M2や、さらに上層の配線層を使用してもよい。なお、セルの高さ方向にスタンダードセルが隣接する場合、タップ2は上下に隣接するセルで共通となり、2つのタップ2が隣接して配置されることはない。

【0027】

また、本実施の形態1で言うセルの高さは、タップ2と直行する方向のセルの長さであり、1つのセルの一端のタップ2の中心から、そのセルの他端のタップ2の中心までの距離のことである。言い換えれば、一端のタップ2に配置されたコンタクトホール3の中心から、他端のタップ2に配置されたコンタクトホール3の中心までの距離である。

【0028】

また、本実施の形態1では、セルの例として7ピッチセルを挙げる。この7ピッチセルは、上下に配置されたタップ2間を6本の2層目の配線M2が通過可能である。これに、片方のタップ2上の2層目の配線M2を加えて、7本の2層目の配線M2が通過可能なセルとしている。

【0029】

図8には、図1BのA−A’線に沿った要部断面図が示されている。p型半導体基板p−subには、n型半導体領域NiSOが形成されており、n型半導体領域NiSOによって、各半導体素子が形成されるウェル領域が分離されている。n型半導体領域NiSOには、n型ウェル領域NWとp型ウェル領域PWとが形成されている。

【0030】

p型半導体基板p−subには、素子分離領域9が形成されており、これにより主に半導体素子が形成される活性領域が区画されている。素子分離領域9は、p型半導体基板p−subに形成された溝内に、酸化シリコン膜等の絶縁膜が埋め込まれて形成されている。図1Bでは、活性領域を示す領域として、p型ウェル領域PW、n型ウェル領域NWおよびタップ2を示している。

【0031】

n型ウェル領域NWには、複数のpチャネル型電界効果トランジスタ(pMIS)が形成されており、p型ウェル領域PWには、複数のnチャネル型電界効果トランジスタ(nMIS)が形成されている。pMISおよびnMISは、それぞれp型半導体基板p−sub上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、p型半導体基板p−sub内に形成されたソース領域およびドレイン領域とを有する。ゲート絶縁膜は、例えば、酸化シリコン膜で形成されている。ゲート電極は、例えば、多結晶シリコン膜で形成されている。

【0032】

pMISのソース領域またはドレイン領域は、n型ウェル領域NWに形成された低濃度p型半導体領域と高濃度p型半導体領域p+とからなる。本実施の形態1では、説明簡略化のため、pMISのゲート長方向の図示を行っておらず、低濃度p型半導体領域は図示していない。図1BのA−A’線に沿った断面図である図8において、pMISのドレイン領域である高濃度p型半導体領域p+を示している。また、電源電位Vddのタップ2の表面は、n型ウェル領域NWに形成された高濃度n型半導体領域n+が形成されている。この領域は、nMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ2はpMISが形成されるn型ウェル領域NWに電源電位Vddを供給し、一定の電位に固定するように構成されている。これらの高濃度p型半導体領域p+、高濃度n型半導体領域n+およびpMISのゲート電極表面には、シリサイド膜10が形成されている。このシリサイド膜10は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜11が形成され、層間絶縁膜11内にコンタクトホール3が形成され、コンタクトホール3内にプラグ12が形成される。プラグ12は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0033】

nMISのソース領域またはドレイン領域は、p型ウェル領域PWに形成された低濃度n型半導体領域と高濃度n型半導体領域n+とからなる。本実施の形態1では、説明簡略化のため、nMISのゲート長方向の図示を行っておらず、低濃度n型半導体領域は図示していない。図1BのA−A’線に沿った断面図である図8において、nMISのドレイン領域である高濃度n型半導体領域n+を示している。また、基準電位Vssのタップ2の表面は、p型ウェル領域PWに形成された高濃度p型半導体領域p+が形成されている。この領域は、pMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ2はnMISが形成されるp型ウェル領域PWに基準電位Vssを供給し、一定の電位に固定するように構成されている。これらの高濃度n型半導体領域n+、高濃度p型半導体領域p+およびnMISのゲート電極表面には、シリサイド膜10が形成されている。このシリサイド膜10は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜11が形成され、層間絶縁膜11内にコンタクトホール3が形成され、コンタクトホール3内にプラグ12が形成される。プラグ12は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0034】

また、図1Bでは、pMISのソース領域を電源電位Vddのタップ2まで延在し、nMISのソース領域を基準電位Vssのタップ2まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddまたは基準電位Vssを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。

【0035】

また、nMISの駆動電流を増加させる目的で、図1Bの上下方向(A−A’方向)において、p型ウェル領域PWの幅をn型ウェル領域NWの幅よりも広くしても良い。

【0036】

また、1層目の配線M1は、層間絶縁膜13に形成された溝内に、バリアメタル膜および銅を主体とする導電性膜が埋め込まれて形成されている。バリアメタル膜は、タンタル、窒化タンタルまたはそれらの積層膜からなる。また、2層目の配線以降についても、同様の構成である。また、本実施の形態1では、配線とプラグとを別々に形成しているが、先にコンタクトホールと配線用の溝を形成し、その後、バリアメタル膜および銅を主体とする導電性膜を埋め込むことで、一体化して形成しても良い。

【0037】

インバータ回路1は、電源電位や接地電位をとるための拡散層であるタップ2をスタンダードセルの高さ方向の上下にそれぞれ備えている。タップ2はセルの幅方向に沿って形成されており、一方のタップ2に電源電位Vddが供給され、他方のタップ2に基準電位Vss(GND)が供給される。このタップ2上には電源電位用または接地電位用の1層目の配線M1が形成されており、コンタクトホール3を通してタップ2と電気的に接続されている。

【0038】

インバータ回路1は1入力1出力の基本論理回路であり、入力の反転を出力する。本実施の形態1によるインバータ回路1はnMISおよびpMISから構成されるCMISインバータを例示している。nMISのゲート電極4NとpMISのゲート電極4Pとは、これらゲート電極4N,4Pと同一層の導電体膜によって接続されており、インバータ回路1の入力端子となる。すなわち、ゲート電極4N,4Pは一体化して形成されている。この入力端子にはコンタクトホール3を通して1層目の配線M1が接続されている。

【0039】

ゲート電極4N,4Pを構成する導電体膜は、例えば多結晶シリコン膜である。ゲート電極4Nには燐または砒素などのn型導電性の不純物が導入されており、ゲート電極4Pにはボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。また、nMISのドレインとpMISのドレインとはコンタクトホール3を通して、1層目の配線M1によって接続されており、インバータ回路1の出力端子となる。このように、インバータ回路1は、2層目以上の配線を用いずに1層目の配線M1のみで回路形成されている。

【0040】

2入力NAND回路6も同様に、タップ2をセルの高さ方向の上下にそれぞれ備えており、一方のタップ2に電源電位Vddが供給され、他方のタップ2に基準電位Vss(GND)が供給される。また、このタップ2上には電源電位用または基準電位用の1層目の配線M1が形成されており、コンタクトホール3を通してタップ2と電気的に接続されている。セルの高さ方向に配列された2入力NAND回路6とインバータ回路1とは、電源電位Vddを供給するタップ2を共有している。

【0041】

2入力NAND回路6は多入力1出力の基本論理回路であり、すべての入力端子に「1」が入力されたときのみ「0」を出力する。2入力NAND回路6は、CMISインバータのnMIS側に同じnMISを直列に接続し、pMIS側に同じpMISを並列に接続し、そのCMISインバータに追加したnMISのゲート電極とpMISのゲート電極とを接続してもう1つの入力端子としている。nMISのゲート電極7N1とpMISのゲート電極7P1とは、これらゲート電極7N1,7P1と同一層の導電体膜によって接続されており、2入力NAND回路6の1つの入力端子となる。すなわち、ゲート電極7N1,7P1は一体化して形成されている。同様に、nMISのゲート電極7N2とpMISのゲート電極7P2とは、これらゲート電極7N2,7P2と同一層の導電体膜によって接続されており、2入力NAND回路6のもう1つの入力端子となる。すなわち、ゲート電極7N2,7P2は一体化して形成されている。

【0042】

ゲート電極7N1,7N2,7P1,7P2を構成する導電体膜は、例えば多結晶シリコン膜である。ゲート電極7N1,7N2には、燐または砒素などのn型導電性の不純物が導入されており、ゲート電極7P1,7P2には、ボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。2つの入力端子にはコンタクトホール3を通して、それぞれ1層目の配線M1が接続されている。また一方のnMISのドレインとpMISのドレインとの接続には1層目の配線M1を用いる。このように、2入力NAND回路6は、2層目以上の配線を用いずに1層目の配線M1のみで回路形成されている。

【0043】

インバータ回路1の出力端子と2入力NAND回路6の一方の入力端子との接続には、2層目以上の配線を用いずに、nMISのゲート電極4N,7N1,7N2またはpMISのゲート電極4P,7P1,7P2と同一層の導電体膜を用いる。すなわち、インバータ回路1のスタンダードセル内に、インバータ回路1を構成するnMISのゲート電極4NまたはpMISのゲート電極4Pと同一層の導電体膜からなる配線(以下、単に導電体膜からなる配線と記す)8を配置する。この導電体膜からなる配線8に、インバータ回路1の出力端子(nMISのドレインとpMISのドレイン)に接続された1層目の配線M1をコンタクトホール3を通して接続し、さらに、2入力NAND回路6の一方の入力端子(nMISのゲート電極7N2とpMISのゲート電極7P2)を接続する。すなわち、配線8とゲート電極7N2,7P2とは一体化して形成されている。従って、インバータ回路1の出力端子と2入力NAND回路6の入力端子との接続に2層目の配線を用いないことから、その座標に2層目の配線からなる通り抜け配線を配置することができる。また、通り抜け配線が配置できることから、迂回する余分な2層目の配線を形成する必要がなくなり、2層目の配線の使用頻度を7%程度少なくすることが可能となる。

【0044】

これにより、例えば2層目の配線が密集した場合においても、スタンダードセルの面積を広くすることなくまたはその座標を迂回させることなく2層目の配線を配置することができるので、半導体集積回路装置の集積度を向上させることができる。また、2層目の配線の迂回による配線容量の増大を防ぐことができるので、半導体集積回路装置の動作電力の削減または動作速度の向上を図ることができる。ここでの説明は省略しているが、セルの幅方向に配置された2つのスタンダードセルは1層目の配線M1を用いて電気的に接続される。

【0045】

図9は、図1BのB−B’線に沿った断面図である。前述したように、配線8とゲート電極7N2,7P2とは一体化して形成されている。この一体化したゲート電極は、タップ2(Vdd)を横断するように設けられている。一体化したゲート電極のうち、配線8にあたる部分は、タップ2(Vdd)より下の領域に設けられており、素子分離領域9上に位置している。また、配線8は、図1Bの左右のゲート電極4P,4Nの間に位置している。

【0046】

この配線8は、MISFET上に形成される層間絶縁膜の平坦性を向上させる目的で形成されている。すなわち、ゲート電極4P,4Nの間隔が広すぎる領域に設けられており、ダミーゲート電極として機能している。このダミーゲート電極により、各ゲート電極の間隔がほぼ一定となり、層間絶縁膜の下地となるゲート電極の疎密差が少なくなる。その結果、層間絶縁膜の厚さの均一性が保たれるので、半導体装置の信頼性が増すことになる。

【0047】

しかし、本実施の形態1における配線8は、図11(b)の課題に示したダミーゲート電極DGとは異なり、他のMISFETと接続するための配線の役割も担っている。図9に示すように、配線8上にはコンタクトホール3およびプラグ12が設けられており、1層目の配線M1と接続している。

【0048】

また、本実施の形態1では、配線8はゲート電極7P2側に形成されているので、ゲート電極7P2と同様に、p型の導電性の不純物が導入されている。また、配線8の表面にはシリサイド膜が形成されている。一体化されたゲート電極の場合、n型不純物とp型不純物との境界部分において、シリサイド膜の凝集が起こりやすくなる場合があり、シリサイド膜が断線する場合がある。従って、一体化されたゲート電極では、出来る限りn型不純物とp型不純物の境界部分を作らないことが好ましい。よって、本実施の形態1では、一体化されたゲート電極のうち、配線8とゲート電極7P2とを同一の導電型としている。

【0049】

つまり、何も考慮しなければ、n型ウェル領域NW上の配線8には、ゲート電極4Pと同様にp型の不純物が導入され、p型ウェル領域PW上の配線8には、ゲート電極4Nと同様にn型の不純物が導入されることになる。そうすると、配線8にn型の不純物とp型の不純物との境界部分が形成されることになるので、上記のシリサイド膜の凝集の問題が発生する確率が高まることとなる。以上より、配線8は、ゲート電極7P2と同一の導電型の不純物で構成されていることがより好ましい。また、これらのゲート電極の導電型は、ゲート電極へのイオン注入と、ソース領域およびドレイン領域を形成する際のイオン注入によって導入される不純物で決定されるが、できるだけ、ゲート電極7P2と同様となることが好ましい。すなわち、配線8には、低濃度p型半導体領域および高濃度p型半導体領域p+を形成する際の不純物のみを導入し、低濃度n型半導体領域および高濃度n型半導体領域n+を形成する際の不純物は導入しないようにすることが好ましい。

【0050】

ところで、インバータ回路1の出力端子と2入力NAND回路6の入力端子との接続に導電体膜からなる配線8を用いた場合、インバータ回路1と2入力NAND回路6とが共有するタップ2を導電体膜からなる配線8が跨ぐことになる。タップ2はウェルと同じ導電型の拡散層から形成されていることから、この交差領域にMISFETが形成されてしまう。しかし、このMISFETが半導体集積回路装置の動作に影響を及ぼすことはないと考えられることから、タップ2上に導電体膜からなる配線8を配置したままでもよい。本実施の形態1では、図1Bおよび図8に示すように、タップ2(Vdd)は、n型ウェル領域NWと高濃度n型半導体領域n+とから形成されている。従って、タップ2を横断する配線8が形成されても、ディプレッション型のMISFETとなるため、タップ2(Vdd)は導通が確保される。しかし、配線8に供給される電位が強く、その影響が懸念される場合には、図1に示したように、上記交差領域のタップ2を削除した方が好ましい。

【0051】

タップ2の削除方法の一例を図2に示す模式図を用いて説明する。まず、2つのスタンダードセルをセルrow上段とセルrow下段に隣接して配置する。例えばセルrow上段が2入力NAND回路6、セルrow下段がインバータ回路1の場合であれば、2入力NAND回路6の一方の入力端子とインバータ回路1の出力端子とは、導電体膜からなる配線8により接続されてタップ2上に導電体膜からなる配線8が配置される。次に、タップ2上のMISFETを図形認識させる。タップ2上にMISFETが図面認識されると、図形認識されたMISFET下のタップ2を構成する拡散層が消去される。このような簡易な図形処理により、タップ2と導電体膜からなる配線8との交差領域のタップ2を削除することができる。

【0052】

なお、導電体膜からなる配線8に多結晶シリコン膜を用いる場合、その抵抗は金属膜からなる2層目の配線よりも抵抗が高くなる。そのため、図3の模式図に示すように、セルの高さ方向に隣接して配置されるスタンダードセル間の結線には導電体膜からなる配線8を用い、セルの高さ方向に1つ以上のスタンダードセルを挟んで配置されるスタンダードセル間の結線には2層目の配線M2または3層目以上の配線を用いることが好ましい。

【0053】

(実施の形態2)

本実施の形態2によるスタンダードセルの配置の一例を図4を用いて説明する。図4は、セルの幅方向に配置された2つのフリップフロップ回路の配置を示す説明図であり、フリップフロップ回路をパターンで表した図である。

【0054】

図4に示すように、フリップフロップ回路21は、電源電位や接地電位をとるための拡散層であるタップ22をセルの高さ方向の上下にそれぞれ備えている。タップ22は、前述の実施の形態1で示したタップ2と同様の構成であり、セルの幅方向(セルの高さ方向と直交する方向)に沿って形成されている。一方のタップ22には電源電位Vddが供給され、他方のタップ22には基準電位Vss(GND)が供給される。このタップ22上には1層目の配線M1が形成されており、コンタクトホール23を通してタップ22と電気的に接続されている。

【0055】

また、図4に示すように、セルの幅方向に配置された2つのフリップフロップ回路21は、一方のセルを左右対称に折り返すように配置している。すなわち、一方のセルを、セルの幅方向に反転させるように配置している。そして、一方のフリップフロップ回路21を右側に1ピッチずらし、他方のフリップフロップ回路21を左側に1ピッチずらして重ねたオーバーラップ配置されている。すなわち、一方のフリップフロップ回路21の端部に配置されたMISFETのソース領域と、他方のフリップフロップ回路21の端部に配置されたMISFETのソース領域とを共通にしている。図4では、共通のソース領域として、拡散層25Vと拡散層25Gとを図示している。また、これにより、前述の図12に示した中央部のダミーゲート電極DGも配置する必要が無くなる。

【0056】

また、図10は図4のC−C’線に沿った断面図を示しており、インバータ24A,24Bのソース領域を共通化した際の、ソース領域の断面図を示している。拡散層25Vは電源電位Vddのタップ22まで延在し、拡散層25Gは基準電位Vss(GND)のタップ22まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddまたは基準電位Vssを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。

【0057】

このようにして、図4に示した本実施の形態2によるオーバーラップ配置を採用した2つのフリップフロップ回路21の配置例は、前述の図12に示した従来のオーバーラップ配置を採用しない2つのフリップフロップ回路21aの配置例と比較すると、セルの幅方向の長さを2ピッチ短くすることができる。例えばオーバーラップ配置を採用しない2つのフリップフロップ回路21aのセルの幅方向のピッチが42ピッチであり、オーバーラップ配置を採用することにより2つのフリップフロップ回路21のセルの幅方向のピッチが40ピッチとなった場合は、セルの幅方向の長さは4%程度縮小する。

【0058】

オーバーラップさせる領域は、セルの幅方向の左側または右側に配置されるスタンダードセルの電源部分が望ましい。すなわち、フリップフロップ回路21を構成するMISFETのソース領域を共通化させることが望ましい。本実施の形態2によるオーバーラップ配置された2つのフリップフロップ回路21では、セルの幅方向の左側または右側に配置された電源電位Vddに接続される電源用の拡散層および基準電位Vss(GND)に接続される接地用の拡散層をオーバーラップさせている。

【0059】

図4に示すように、2つのフリップフロップ回路21が接する部分(紙面上左に配置された第1フリップフロップ回路21Aでは右側、紙面上右に配置された第2フリップフロップ回路21Bでは左側)には、フリップフロップ回路21の内部で反転信号を形成するインバータが配置されている。紙面上左に配置された第1フリップフロップ回路21Aの右側に配置された第1インバータ24Aの右端には電源用の拡散層25Vと接地用の拡散層25Gとが配置されており、紙面上右に配置された第2フリップフロップ回路21Bの左側に配置された第2インバータ24Bの左端には電源用の拡散層25Vと接地用の拡散層25Gとが配置されている。第1インバータ24Aの電源用の拡散層25Vと第2インバータ24Bの電源用の拡散層25Vとはオーバーラップして形成されており、電源電位Vddが供給されるタップ22に接続している。同様に、第1インバータ24Aの接地用の拡散層25Gと第2インバータ24Bの接地用の拡散層25Gとはオーバーラップして形成されており、基準電位Vss(GND)が供給されるタップ22に接続している。

【0060】

本実施の形態2によるスタンダードセルの配置の他の例を図5(a)および(b)を用いて説明する。図5(a)は、本実施の形態2によるオーバーラップ配置を採用したセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図であり、図5(b)は、従来のオーバーラップ配置を採用しないセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図である。両図ともに、インバータ回路およびフリップフロップ回路をパターンで表している。

【0061】

前述の図4に示した2つのフリップフロップ回路21の配置と同様に、本実施の形態2によるインバータ回路26とフリップフロップ回路27とはミラー配置され、かつ、互いに1ピッチずつずらして重ねられたオーバーラップ配置されている。従って、図5(a)に示した本実施の形態2によるオーバーラップ配置を採用したインバータ回路26およびフリップフロップ回路27の配置例は、図5(b)に示した従来のオーバーラップ配置を採用しないインバータ回路26aおよびフリップフロップ回路27aの配置例と比較すると、セルの幅方向の長さを2ピッチ短くすることができる。例えばオーバーラップ配置を採用しないインバータ回路26aおよびフリップフロップ回路27aのセルの幅方向のピッチが24ピッチであり、オーバーラップ配置を採用することによりインバータ回路26aおよびフリップフロップ回路27aのセルの幅方向のピッチが22ピッチとなった場合は、セルの幅方向の長さは4%程度縮小する。

【0062】

本実施の形態2によるオーバーラップ配置されたインバータ回路26およびフリップフロップ回路27では、セルの幅方向の左側または右側に配置された電源電位Vddに接続される電源用の拡散層および基準電位Vss(GND)に接続される接地用の拡散層をオーバーラップさせている。

【0063】

図5(a)に示すように、インバータ回路26と接する側のフリップフロップ回路27には、反転信号を形成するインバータが配置されている。このインバータの左端(インバータ回路26と接する側)には電源用の拡散層28Vと接地用の拡散層28Gとが配置されている。インバータ回路26の電源用の拡散層28Vとフリップフロップ回路27のインバータの電源用の拡散層28Vとはオーバーラップして形成されており、電源電位Vddが供給されるタップ22に接続している。同様に、インバータ回路26の接地用の拡散層28Gとフリップフロップ回路27のインバータの接地用の拡散層28Gとはオーバーラップして形成されており、基準電位Vss(GND)が供給されるタップ22に接続している。

【0064】

次に、本実施の形態2による自動レイアウトによるスタンダードセルのオーバーラップ配置の方法について図6および図7を用いて説明する。図6は、本実施の形態2によるスタンダードセルの配置方法の流れを模式的に示した説明図、図7はフリップフロップ回路の一例を示すパターン図である。

【0065】

まず、スタンダードセルの設計データを持つ第1枠F1を用意し、電源部分が共有化できるスタンダードセルの設計データを持つ第2枠F2を用意し、これらをセルライブラリに登録する(図6(a))。第2枠F2に設計される基本論理回路や機能回路では、その右端部または左端部に共有化に適した電源部分のパターンが形成されており、第2枠F2にはオーバーラップ配置の可能性情報が保持されている。第2枠F2のセルの幅方向のピッチは、第1枠F1のセルの幅方向のピッチよりも1ピッチ短く設計されている。

【0066】

例えば図7に示すフリップフロップ回路では、第1枠F1内にはフリップフロップ回路が全て収まっており、第1枠F1内でフリップフロップ回路が完結している。これに対して、第2枠F2内ではフリップフロップ回路が完結せず、紙面上左側に設けられたインバータの電源用の拡散層および接地用の拡散層に、共有化に適した電源部分のパターンが形成されている。

【0067】

次に、第1枠F1のみをセルライブラリから取り出し、配置プログラムに従って適切に配置することによって機能ブロックを構成する(図6(b))。次に、セルの幅方向に隣接する2つの第1枠F1のうち、2つの第2枠F2に置き換えることが可能なセルを選択し、第1枠F1を第2枠F2へ置き換える(図6(c))。第2枠F2に置き換えられない第1枠F1は、置き換えられることなく、そのまま配置される。次に、第2枠F2の配置を補正することにより隣接する第2枠F2を接近させて配置し、第1枠F1を第2枠F2へ置き換えることによって生じた隙間を埋める(図6(d))。これにより、機能ブロック内の第1枠F1および第2枠F2の配置が完成する。

【0068】

その後、第1枠F1内の設計データまたは第2枠F2内の設計データを基に、配線プログラムに従って機能ブロック内のスタンダードセルの相互配線、機能ブロックの入出力端子、電源配線および接地配線などを適切に行い、機能ブロックの配置および配線を完成させる。

【0069】

なお、オーバーラップ配置を採用する基本論理回路または機能回路としては、特に限定されるものではないが、前述したフリップフロップ回路、インバータ回路の他に、AND回路、OR回路、NAND回路、NOR回路、XOR回路またはXNOR回路などの比較的使用頻度が高い基本論理回路とすることが望ましい。これは、オーバーラップ配置を採用する基本論理回路または機能回路の種類を増やすことにより、配置の混乱が生じることが懸念されるためである。オーバーラップ配置を採用する基本論理回路または機能回路を限定したとしても、比較的使用頻度が高い基本論理回路に適用することにより、確実に半導体集積回路装置の面積を縮小することができる。

【0070】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0071】

例えば、前記実施の形態1および2を組み合わせて実施することも可能である。その場合、タップ2の延在方向におけるセル面積の縮小を、さらに効果的に行うことができる。

【0072】

また、前記実施の形態1および2では、スタンダードセルとして7ピッチセルを例に説明したが、これに限定されるものではなく、9ピッチセル、8ピッチセル、6ピッチセルまたは5ピッチセルとしても良く、同様の効果を得ることができる。

【0073】

また、前記実施の形態1および2では、pMISおよびnMISのゲート電極を多結晶シリコン膜で形成する例を示したが、これに限られるものではなく、例えば金属膜で形成してもよい。そのような金属膜としては、Ti、TiN、PtまたはAl等が挙げられる。

【0074】

また、前記実施の形態1および2では、ゲート絶縁膜を酸化シリコン膜で形成した例を示したが、これに限られるものではなく、例えば窒化シリコン膜よりも高い誘電率を有する膜で形成してもよい。そのような高誘電率膜としては、HfO、HfAlO、HfSiAlO、HfSiO、ZrO、ZrAlO、ZrSiO、LaO、LaSiO、TaOまたはTiO等が挙げられる。

【産業上の利用可能性】

【0075】

本発明の半導体集積回路装置は、小型化の進んだスタンダードセルから形成された集積回路を有する半導体集積回路装置に適用することができる。

【図面の簡単な説明】

【0076】

【図1A】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、スタンダードセルを回路記号で表した図である。

【図1B】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、スタンダードセルをパターンで表した要部平面図である。

【図1C】本発明の実施の形態1によるスタンダードセルの配置の一例の説明図であり、図1Bにおける活性領域およびゲート電極のみを示す簡略図である。

【図2】本発明の実施の形態1によるタップの削除方法の一例を説明する模式図である。

【図3】本発明の実施の形態1による2層目の配線と導電体膜からなる配線との使用例を示した模式図である。

【図4】本発明の実施の形態2によるスタンダードセルの配置の一例の説明図であり、スタンダードセルをパターンで表した図である。

【図5】本実施の形態2によるスタンダードセルの配置の他の例の説明図であり、(a)は、本実施の形態2によるオーバーラップ配置を採用したセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図、(b)は、従来のオーバーラップ配置を採用しないセルの幅方向に配置された1つのインバータ回路と1つのフリップフロップ回路の配置を示す説明図である。

【図6】本実施の形態2によるスタンダードセルの配置方法の流れを模式的に示した説明図である。

【図7】本実施の形態2によるフリップフロップ回路の一例を示すパターン図である。

【図8】図1BのA−A’線に沿った断面図である。

【図9】図1BのB−B’線に沿った断面図である。

【図10】図4のC−C’線に沿った断面図である。

【図11】本発明者が検討したスタンダードセルの配置の一例を示す説明図であり、(a)はスタンダードセルを回路記号で表した図、(b)はスタンダードセルをパターンで表した図である。

【図12】本発明者が検討したスタンダードセルの配置の一例を示す説明図であり、スタンダードセルをパターンで表した図である。

【符号の説明】

【0077】

1,1a インバータ回路

2 タップ

3 コンタクトホール

4N,4P ゲート電極

6,6a 2入力NAND回路

7N1,7N2 ゲート電極

7P1,7P2 ゲート電極

8 導電体膜からなる配線(ダミーゲート電極)

9 素子分離領域

10 シリサイド膜

11 層間絶縁膜

12 プラグ

13 層間絶縁膜

21,21a フリップフロップ回路

21A 第1フリップフロップ回路

21B 第2フリップフロップ回路

22 タップ

23 コンタクトホール

24A 第1インバータ

24B 第2インバータ

25V 電源用の拡散層

25G 接地用の拡散層

26,26a インバータ回路

27,27a フリップフロップ回路

28V 電源用の拡散層

28G 接地用の拡散層

DG ダミーゲート電極

F1 第1枠

F2 第2枠

M1 1層目の配線

M2 2層目の配線

n+ 高濃度n型半導体領域

NiSO n型半導体領域

NW n型ウェル領域

p−sub p型半導体基板

p+ 高濃度p型半導体領域

PW p型ウェル領域

Vdd 電源電位

Vss(GND) 基準電位

【特許請求の範囲】

【請求項1】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置であって、

セルの高さ方向に隣接して上下段に配置される2つのスタンダードセルは、1層目の配線よりも下層の導電体膜を用いて電気的に接続され、

セルの高さ方向に1つ以上のスタンダードセルを挟んで上下段に配置される2つのスタンダードセルは、2層目以上の配線を用いて電気的に接続されることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、前記1層目の配線よりも下層の前記導電体膜は、スタンダードセル内に形成されるMISFETのゲート電極を構成する導電体膜と同層であることを特徴とする半導体集積回路装置。

【請求項3】

請求項1記載の半導体集積回路装置において、前記1層目の配線よりも下層の前記導電体膜は多結晶シリコン膜であることを特徴とする半導体集積回路装置。

【請求項4】

請求項1記載の半導体集積回路装置において、前記1層目の配線および2層目以上の配線は金属膜であることを特徴とする半導体集積回路装置。

【請求項5】

請求項1記載の半導体集積回路装置において、セルの高さ方向に隣接して上下段に配置される前記2つのスタンダードセルの接する領域に、前記2つのスタンダードセルが共有し、セルの幅方向に延在する拡散層からなり、かつ、電源電位または基準電位が供給されるタップを有しており、

前記1層目の配線よりも下層の前記導電体膜と前記タップとが交差する領域では、前記1層目の配線よりも下層の前記導電体膜の下の前記タップが削除されていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1記載の半導体集積回路装置において、セルの幅方向に隣接して左右段に配置される2つのスタンダードセルは、前記1層目の配線を用いて電気的に接続されることを特徴とする半導体集積回路装置。

【請求項7】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置であって、

セルの横方向に隣接して左右段に配置される2つのスタンダードセルは、一方のスタンダードセルが、セルの高さ方向と直交するセルの幅方向に反転させるように配置され、かつ、一方のスタンダードセルを右側に1ピッチずらし、他方のスタンダードセルを左側に1ピッチずらして重ねたオーバーラップ配置されていることを特徴とする半導体集積回路装置。

【請求項8】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域に、前記2つのスタンダードセルに共通の電源用の拡散層が形成されていることを特徴とする半導体集積回路装置。

【請求項9】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域に、前記2つのスタンダードセルに共通の電源用の拡散層が形成されており、

前記2つのスタンダードセルを挟んでセルの高さ方向の上下にそれぞれタップが形成されて、前記電源用の拡散層は一方の前記タップに電気的に接続されていることを特徴とする半導体集積回路装置。

【請求項10】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域の右側および左側に、それぞれCMISインバータが形成されており、右側のCMISインバータのnチャネル型MISFETの電源用の拡散層と左側のCMISインバータのnチャネル型MISFETの電源用の拡散層とを共有化し、右側のCMISインバータのpチャネル型MISFETの電源用の拡散層と左側のCMISインバータのpチャネル型MISFETの電源用の拡散層とを共有化していることを特徴とする半導体集積回路装置。

【請求項11】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域の右側および左側に、それぞれCMISインバータが形成されて、右側のCMISインバータのnチャネル型MISFETの電源用の拡散層と左側のCMISインバータのnチャネル型MISFETの電源用の拡散層とを共有化し、右側のCMISインバータのpチャネル型MISFETの電源用の拡散層と左側のCMISインバータのpチャネル型MISFETの電源用の拡散層とを共有化しており、

前記2つのスタンダードセルを挟んでセルの高さ方向の上下にそれぞれタップが形成されて、前記右側のCMISインバータのpチャネル型MISFETと前記左側のCMISインバータのpチャネル型MISFETとが共有する電源用の拡散層は一方の前記タップに電気的に接続され、前記右側のCMISインバータのnチャネル型MISFETと前記左側のCMISインバータのnチャネル型MISFETとが共有する電源用の拡散層は他方の前記タップに電気的に接続されていることを特徴とする半導体集積回路装置。

【請求項12】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルを構成する回路は、インバータ回路、フリップフロップ回路、AND回路、OR回路、NAND回路、NOR回路、XOR回路またはXNOR回路であることを特徴とする半導体集積回路装置。

【請求項13】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置の製造方法であって、

(a)第1スタンダードセルの設計データを持つ第1枠を用意する工程と、

(b)前記第1スタンダードセルをセルの幅方向に隣接して反転させて配置したときに、電源部分を共有化できる第2スタンダードセルの設計データを持つ第2枠を用意する工程と、

(c)前記第1枠のみを配置プログラムに従って配置する工程と、

(d)前記第2枠に置き換えることが可能なセルの幅方向に隣接する2つの第1枠を選択し、前記隣接する2つの第1枠を、電源部分を共有化するように配置された隣接する2つの第2枠へ置き換える工程と、

(e)前記隣接する2つの第2枠を移動させて、前記隣接する2つの第1枠を前記隣接する2つの第2枠へ置き換えることによって生じた隙間を埋める工程と、

を有することを特徴とする半導体集積回路装置の製造方法。

【請求項14】

請求項13記載の半導体集積回路装置の製造方法において、(e)工程の後、さらに以下の工程を含むことを特徴とする半導体集積回路装置の製造方法;

(f)配線プログラムに従ってスタンダードセルの相互間の配線を行う工程。

【請求項15】

請求項13記載の半導体集積回路装置の製造方法において、前記隣接する2つの第2枠のセルの幅方向の長さは、前記隣接する2つの第1枠のセルの幅方向の長さよりも1ピッチ短いことを特徴とする半導体集積回路装置の製造方法。

【請求項16】

請求項13記載の半導体集積回路装置の製造方法において、前記第1枠内では論理回路が完結していることを特徴とする半導体集積回路装置の製造方法。

【請求項1】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置であって、

セルの高さ方向に隣接して上下段に配置される2つのスタンダードセルは、1層目の配線よりも下層の導電体膜を用いて電気的に接続され、

セルの高さ方向に1つ以上のスタンダードセルを挟んで上下段に配置される2つのスタンダードセルは、2層目以上の配線を用いて電気的に接続されることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、前記1層目の配線よりも下層の前記導電体膜は、スタンダードセル内に形成されるMISFETのゲート電極を構成する導電体膜と同層であることを特徴とする半導体集積回路装置。

【請求項3】

請求項1記載の半導体集積回路装置において、前記1層目の配線よりも下層の前記導電体膜は多結晶シリコン膜であることを特徴とする半導体集積回路装置。

【請求項4】

請求項1記載の半導体集積回路装置において、前記1層目の配線および2層目以上の配線は金属膜であることを特徴とする半導体集積回路装置。

【請求項5】

請求項1記載の半導体集積回路装置において、セルの高さ方向に隣接して上下段に配置される前記2つのスタンダードセルの接する領域に、前記2つのスタンダードセルが共有し、セルの幅方向に延在する拡散層からなり、かつ、電源電位または基準電位が供給されるタップを有しており、

前記1層目の配線よりも下層の前記導電体膜と前記タップとが交差する領域では、前記1層目の配線よりも下層の前記導電体膜の下の前記タップが削除されていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1記載の半導体集積回路装置において、セルの幅方向に隣接して左右段に配置される2つのスタンダードセルは、前記1層目の配線を用いて電気的に接続されることを特徴とする半導体集積回路装置。

【請求項7】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置であって、

セルの横方向に隣接して左右段に配置される2つのスタンダードセルは、一方のスタンダードセルが、セルの高さ方向と直交するセルの幅方向に反転させるように配置され、かつ、一方のスタンダードセルを右側に1ピッチずらし、他方のスタンダードセルを左側に1ピッチずらして重ねたオーバーラップ配置されていることを特徴とする半導体集積回路装置。

【請求項8】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域に、前記2つのスタンダードセルに共通の電源用の拡散層が形成されていることを特徴とする半導体集積回路装置。

【請求項9】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域に、前記2つのスタンダードセルに共通の電源用の拡散層が形成されており、

前記2つのスタンダードセルを挟んでセルの高さ方向の上下にそれぞれタップが形成されて、前記電源用の拡散層は一方の前記タップに電気的に接続されていることを特徴とする半導体集積回路装置。

【請求項10】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域の右側および左側に、それぞれCMISインバータが形成されており、右側のCMISインバータのnチャネル型MISFETの電源用の拡散層と左側のCMISインバータのnチャネル型MISFETの電源用の拡散層とを共有化し、右側のCMISインバータのpチャネル型MISFETの電源用の拡散層と左側のCMISインバータのpチャネル型MISFETの電源用の拡散層とを共有化していることを特徴とする半導体集積回路装置。

【請求項11】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルがオーバーラップ配置された領域の右側および左側に、それぞれCMISインバータが形成されて、右側のCMISインバータのnチャネル型MISFETの電源用の拡散層と左側のCMISインバータのnチャネル型MISFETの電源用の拡散層とを共有化し、右側のCMISインバータのpチャネル型MISFETの電源用の拡散層と左側のCMISインバータのpチャネル型MISFETの電源用の拡散層とを共有化しており、

前記2つのスタンダードセルを挟んでセルの高さ方向の上下にそれぞれタップが形成されて、前記右側のCMISインバータのpチャネル型MISFETと前記左側のCMISインバータのpチャネル型MISFETとが共有する電源用の拡散層は一方の前記タップに電気的に接続され、前記右側のCMISインバータのnチャネル型MISFETと前記左側のCMISインバータのnチャネル型MISFETとが共有する電源用の拡散層は他方の前記タップに電気的に接続されていることを特徴とする半導体集積回路装置。

【請求項12】

請求項7記載の半導体集積回路装置において、前記2つのスタンダードセルを構成する回路は、インバータ回路、フリップフロップ回路、AND回路、OR回路、NAND回路、NOR回路、XOR回路またはXNOR回路であることを特徴とする半導体集積回路装置。

【請求項13】

複数のスタンダードセルを配列したセルアレイを含む半導体集積回路装置の製造方法であって、

(a)第1スタンダードセルの設計データを持つ第1枠を用意する工程と、

(b)前記第1スタンダードセルをセルの幅方向に隣接して反転させて配置したときに、電源部分を共有化できる第2スタンダードセルの設計データを持つ第2枠を用意する工程と、

(c)前記第1枠のみを配置プログラムに従って配置する工程と、

(d)前記第2枠に置き換えることが可能なセルの幅方向に隣接する2つの第1枠を選択し、前記隣接する2つの第1枠を、電源部分を共有化するように配置された隣接する2つの第2枠へ置き換える工程と、

(e)前記隣接する2つの第2枠を移動させて、前記隣接する2つの第1枠を前記隣接する2つの第2枠へ置き換えることによって生じた隙間を埋める工程と、

を有することを特徴とする半導体集積回路装置の製造方法。

【請求項14】

請求項13記載の半導体集積回路装置の製造方法において、(e)工程の後、さらに以下の工程を含むことを特徴とする半導体集積回路装置の製造方法;

(f)配線プログラムに従ってスタンダードセルの相互間の配線を行う工程。

【請求項15】

請求項13記載の半導体集積回路装置の製造方法において、前記隣接する2つの第2枠のセルの幅方向の長さは、前記隣接する2つの第1枠のセルの幅方向の長さよりも1ピッチ短いことを特徴とする半導体集積回路装置の製造方法。

【請求項16】

請求項13記載の半導体集積回路装置の製造方法において、前記第1枠内では論理回路が完結していることを特徴とする半導体集積回路装置の製造方法。

【図1A】

【図1B】

【図1C】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図1B】

【図1C】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2010−141047(P2010−141047A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−314818(P2008−314818)

【出願日】平成20年12月10日(2008.12.10)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月10日(2008.12.10)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]