半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいては、一般にバンプ電極による外部接続が主要な構造である。一方、このようなデバイスにおいても、ワイヤ・ボンディングにより外部接続をとりたいというニーズが広く存在する。そこで、無電界メッキによる積層金属再配線上に更に無電界メッキによってボンディング用の金メッキ表面膜を設け、そこにワイヤをボンディングする技術が考えられている。しかし、このような無電界メッキ・ベースの技術では、耐拡散性および耐衝撃性等を十分に確保することができず、高信頼性のデバイス及びプロセスを提供することが困難である。

【解決手段】本願発明は半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するものである。

【解決手段】本願発明は半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)のデバイス構造および半導体集積回路装置(または半導体装置)の製造方法における外部接続技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2007−73611号公報(特許文献1)には、半導体チップ上のアルミニウム系ボンディング・パッド上方の再配線最上層である無電界メッキによるニッケル膜上に、無電界メッキによる金層を形成し、そこにボンディング・ワイヤを接続する技術が開示されている。

【0003】

【特許文献1】特開2007−73611号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいては、一般にバンプ電極による外部接続が主要な構造である。一方、このようなデバイスにおいても、ワイヤ・ボンディングにより外部接続をとりたいというニーズが広く存在する。そこで、日本特開2007−73611号公報(特許文献1)に開示されたように、無電界メッキによる積層金属再配線上に更に無電界メッキによってボンディング用の金メッキ表面膜を設け、そこにワイヤをボンディングする技術が考えられている。

【0005】

しかし、このような無電界メッキ・ベースの技術では、耐拡散性および耐衝撃性等を十分に確保することができず、高信頼性のデバイス及びプロセスを提供することが困難である。

【0006】

本願発明は、これらの課題を解決するためになされたものである。

【0007】

本発明の目的は、高信頼性の半導体集積回路装置または半導体集積回路装置の製造プロセスを提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、本願発明は半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するものである。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するので、膜質が良好で十分に厚いパッド膜とすることができる。

【発明を実施するための最良の形態】

【0013】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0014】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハのデバイス面上の多層配線層上に、第1のパッド電極を形成する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記デバイス面側を第1の絶縁膜で被覆する工程;

(c)前記工程(b)の後、前記第1のパッド電極上の前記第1の絶縁膜にパッド開口を形成する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記デバイス面側にシード・メタル層を形成する工程;

(e)前記工程(d)の後、前記シード・メタル層上に、前記パッド開口を内部に含む第1のレジスト膜開口を有する第1のレジスト膜パターンを形成する工程;

(f)前記工程(e)の後、前記シード・メタル層上の前記第1のレジスト膜開口内に、電解メッキにより、再配線金属層を形成する工程;

(g)前記工程(f)の後、前記再配線金属層上に第2のレジスト膜開口を有する第2のレジスト膜パターンを、前記シード・メタル層および前記再配線金属層上に、形成する工程;

(h)前記工程(g)の後、前記再配線金属層上の前記第2のレジスト膜開口内に、電解メッキにより、金を主要な成分とする第2のパッド電極を形成する工程;

(i)前記工程(h)の後、前記第2のレジスト膜パターンを除去する工程。

【0015】

2.前記1項の半導体集積回路装置の製造方法において、更に以下の工程を含む:

(j)前記工程(i)の後、前記半導体ウエハを半導体チップに分割する工程;

(k)前記工程(j)の後、前記半導体チップの裏面を配線基板上に固定する工程;

(l)前記工程(k)の後、前記半導体チップの前記第2のパッド電極と前記半導体チップの外部の電極間を金を主要な成分とするボンディング・ワイヤで接続する工程。

【0016】

3.前記1または2項の半導体集積回路装置の製造方法において、前記再配線金属層は、銅を主要な成分とする第1の再配線金属膜を有する。

【0017】

4.前記3項の半導体集積回路装置の製造方法において、前記再配線金属層は、前記第1の再配線金属膜上に、ニッケルを主要な成分とする第2の再配線金属膜を有する。

【0018】

5.前記1から4項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内に電解メッキにより形成されたパッド下地膜がある。

【0019】

6.前記1から5項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【0020】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記シード・メタル層は、以下を含む:

(1)スパッタリングにより形成された下層の拡散バリア・メタル膜;

(2)スパッタリングにより形成された上層の銅シード膜。

【0021】

8.前記7項の半導体集積回路装置の製造方法において、前記下層の拡散バリア・メタル膜は、クロムを主要な成分とする。

【0022】

9.前記1から3および6から8項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内の前記第1の再配線金属膜上に直接、電解メッキにより形成されたパッド下地膜がある。

【0023】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の絶縁膜よりも上には、他の絶縁膜が実質的に存在しない。

【0024】

11.前記1から10項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の絶縁膜は以下を含む:

(1)下層の無機系絶縁膜;

(2)上層の有機系絶縁膜。

【0025】

12.前記11項の半導体集積回路装置の製造方法において、前記下層の無機系絶縁膜は、窒化シリコンを主要な成分とする膜を含む。

【0026】

13.前記11または12項の半導体集積回路装置の製造方法において、前記上層の有機系絶縁膜は、ポリイミドを主要な成分とする膜を含む。

【0027】

14.以下を含む半導体集積回路装置:

(a)デバイス面を有する半導体基板;

(b)前記デバイス面上の多層配線層;

(c)前記多層配線層上の第1のパッド電極;

(d)前記多層配線層および前記第1のパッド電極上のファイナル・パッシベーション膜;

(e)前記ファイナル・パッシベーション膜の前記第1のパッド電極上のパッド開口;

(f)前記パッド開口を通して、前記第1のパッド電極に接続された再配線金属層;

(g)前記再配線金属層の上面の一部に設けられた電解メッキによる金を主要な成分とする第2のパッド電極。

【0028】

15.前記14項の半導体集積回路装置において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【0029】

16.前記14または15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜;

(2)前記第1の再配線金属膜上に設けられた、ニッケルを主要な成分とする第2の再配線金属膜。

【0030】

17.前記16項の半導体集積回路装置において、前記第2の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【0031】

18.前記14または15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜。

【0032】

19.前記18項の半導体集積回路装置において、前記第1の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【0033】

20.前記14から19項のいずれか一つの半導体集積回路装置において、前記ファイナル・パッシベーション膜上には、他の絶縁膜がない。

【0034】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。

【0036】

たとえば、「アルミニウム」、「銅」、「ニッケル」、「金」、「クロム」等といっても、これらの単独の純粋なメタル材料を意味するものではなく、当該材料成分を主要な構成成分とし、必要に応じて他の副次的成分を配合又は添加して合金を形成したものも含むことは言うまでもない。

【0037】

更に、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0038】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0039】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0040】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0041】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0042】

1.本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド形成から再配線等のウエハ・プロセスの説明(主に図1から図16)

以下では、図1から図16に基づいて、主に半導体集積回路装置のウエハ・プロセスにおけるアルミニウム系パッド(銅系パッドその他でもよい)形成工程周辺以降を説明する。アルミニウム系パッド層より下層には、通常、銅系ダマシン多層配線層またはアルミニウム系通常多層配線層(一般に3層から10層程度)がある。以下の説明する図面では、ウエハについて説明する際も、簡潔性を確保するために、原則として単位チップ領域のみを表示する。

【0043】

図1に示すように、半導体ウエハ1(チップ領域1c)のデバイス面1a(裏面1bに対向する主面)には、多数のアルミニウム系ボンディング・パッド2(第1のパッド電極)が形成されている。パッド周辺部CのX−X’断面を図2に示す。以下に平面構造とともに製造プロセスを説明する。

【0044】

図2に示すように、ボンディング・パッド2下の多層配線層を含む半導体基板1p(本来の基板部分は通常、たとえば300ファイのp型の単結晶シリコン・ウエハである)のデバイス面1a側には、ファイナル・パッシベーション膜4が形成されている。ボンディング・パッド2を構成するアルミニウム系パッド層は、最上層配線層を兼ねてもよい。ボンディング・パッド2およびファイナル・パッシベーション膜4の形成については、以下のように形成する。まず、多層配線層上にスパッタリングにより、アルミニウム系メタル膜(通常、中間のアルミニウムを主要な成分とし、銅その他を数パーセント程度添加した主配線金属層の上下にTiN等の薄膜を有する)を成膜する。通常のリソグラフィにより、アルミニウム系メタル膜をパターニングし、ボンディング・パッド2を形成する。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の無機ファイナル・パッシベーション膜となる酸化シリコン系絶縁膜をプラズマCVD法により成膜する。続いて、その上に、たとえば、上層の無機ファイナル・パッシベーション膜となる窒化シリコン系絶縁膜をプラズマCVD法により成膜する。次に、この2層からなる無機ファイナル・パッシベーション膜に通常のリソグラフィにより、パッド開口3を形成する。この後、一般に主配線金属層上のTiN等が自己整合的にエッチング除去される。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、有機ファイナル・パッシベーション膜となるポリイミド膜を塗布する。続いて、先とほぼ同じ開口位置に再び通常のリソグラフィにより、パッド開口3を形成する。従って、最終的なファイナル・パッシベーション膜4(第1の絶縁膜)は、下層から酸化シリコン膜、窒化シリコン膜、およびポリイミド膜の三層重ね膜となる。これで、図2のような断面形態となる。このように、再配線パターン16上に、第2のポリイミド膜等の別のパッシベーション膜がないので、簡易な構造とすることができる。また、製造プロセスは大幅に簡素化される。このような簡素化が可能な理由は、最上層が膜質の良好な非腐食性の電解メッキによる金パッド膜15と成っているからである。

【0045】

次に、図3に示すように、半導体ウエハ1のデバイス面1a側のほぼ全面に、スパッタリングにより、拡散バリア・メタル膜5(たとえば75nm程度の厚さのクロム膜)を成膜する。バリア・メタルとしては、他にチタン、窒化チタン、および窒化タングステン等を主要な成分とするものが好適なものとして例示できる。

【0046】

その上に、図4に示すように、銅の電解メッキのためのシード膜6(たとえば250nm程度の厚さの銅膜)をスパッタリングにより、成膜する。

【0047】

次に、図5に示すように、半導体ウエハ1のデバイス面1a側のほぼ全面に、レジスト膜7(たとえば厚さ12マイクロ・メートル程度)を形成する。続いて、レジスト膜7を通常のリソグラフィにより、パターニングすることにより、第1のレジスト膜開口10を有する第1のレジスト膜パターン7を形成する。

【0048】

次に、図6に示すように、電解メッキにより、第1のレジスト膜開口10内に、選択的に第1の再配線金属膜8(たとえば、厚さ7.5マイクロ・メートル程度の銅メッキ膜)を形成する。

【0049】

更に、その上に、図7に示すように、電解メッキにより、第1のレジスト膜開口10内に、選択的に第2の再配線金属膜9(たとえば、厚さ2.3マイクロ・メートル程度のニッケル・メッキ膜)を形成する。この膜は、必須ではないが、付加することでデバイスの信頼性を向上させることができる。拡散または反応バリア膜として作用する。この第1の再配線金属膜8と第2の再配線金属膜9で再配線金属層16を構成している。

【0050】

次に、図8および図9に示すように、レジスト膜7(第1のレジスト膜パターン)を有する半導体ウエハ1のデバイス面1a側のほぼ全面に、レジスト膜11(たとえば厚さ12マイクロ・メートル程度)を形成する。続いて、レジスト膜11を通常のリソグラフィにより、パターニングすることにより、第2のレジスト膜開口12を有する第2のレジスト膜パターン11を形成する。

【0051】

次に、図10に示すように、電解メッキにより、第2のレジスト膜開口12内に、選択的にパッド下地膜14(たとえば、厚さ0.7マイクロ・メートル程度のニッケル・メッキ膜)を形成する。この膜は必須ではないが、付加することで、後の金メッキの膜質を良好にするメリットがある。

【0052】

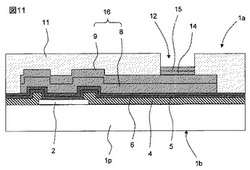

更に、その上に、図11に示すように、電解メッキにより、第2のレジスト膜開口12内に、選択的に第2のパッド電極15(たとえば、厚さ1.0マイクロ・メートル程度の金メッキ膜)を形成する。メッキ液としては、たとえば、亜硫酸金ナトリウム系のメッキ液等が好適なものとして例示できる。

【0053】

次に、図12に示すように、不要になった第2のレジスト膜パターン11を除去溶剤・アッシング等により除去する。

【0054】

更に、図13に示すように、再配線金属層16の直下以外のシード・メタル層21(下層のクロム膜5および上層の銅シード膜6)を、たとえばウエット・エッチングにより除去する。まず、上層の銅シード膜6を自己整合的に、除去し(処理としては、たとえば、摂氏25度程度の過酸化水素水による10秒程度のウエット・エッチング処理を例示することができる)、続いて、下層のクロム膜5を除去する(処理としては、たとえば、摂氏25度程度の過マンガン酸カリウムとメタケイ酸ナトリウムの混合液等による20分程度のウエット・エッチング処理を例示することができる)。なお、以下の工程では、シード・メタル層21も含めて再配線金属層または再配線パターン等ということがある。

【0055】

以上により、図14に示すように、ここで、半導体ウエハ1のデバイス面1a側に、分離した再配線金属層または再配線パターン16が形成される。図15に図14のパッド周辺部Cの拡大平面図を示す。図16は、図15のX−X’断面でカットしたデバイスの斜視図である。

【0056】

2.本願の一実施の形態の半導体集積回路装置の製造方法における実装プロセスの説明(主に図17および図18)

ここでは、セクション1で説明したプロセスの、その後のプロセス(実装プロセス)を説明する。

【0057】

図17に示すように、ダイシング等により、個々のチップ1cに分割する。次に、チップ1cを配線基板17上にダイ・ボンディングする。その後、金を主要な成分とするボンディング・ワイヤ19を用いて、キャピラリを用いたボール・ボンディング(たとえばサーモ・ソニック・ボンディング)により、チップ1c上の金パッド15(第2のパッド電極)とチップ1c外の電極(たとえば配線基板17上の外部リード18)間を接続する。図18に図17の破線部分の斜視図(図16に続く)を示す。

【0058】

なお、この場合、いずれの電極にボールを配置してもよい。

【0059】

3.図1から図18について説明した半導体集積回路装置およびその製造方法に対する変形例の説明(主に図19)

この例は、セクション1および2に説明したプロセスにおいて、図7で説明した電解メッキ・ニッケル再配線層9(第2の再配線金属膜)の形成を省略したものである。これにより、再配線構造の簡略化が可能となる。電解メッキ・ニッケル再配線層9がなくとも、ニッケル・パッド膜14がバリア・メタル膜として作用するので、特性上の問題は比較的少ないと考えられる。

【0060】

4.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0061】

例えば、前記実施の形態においては、主に銅層とニッケル層の重ね膜を再配線の主要な構成部分とする例について、具体的に説明したが、本願発明はそれに限定されるものではなく、銅層単層を再配線の主要な構成部分とするもの等にも適用できることは言うまでもない。

【図面の簡単な説明】

【0062】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法におけるパッド開口工程以降のプロセスの流れを示すための半導体ウエハの単位チップ領域の上面図(パッド開口工程完了時点)である。

【図2】図1の破線部分CのX−X’に対応するデバイス断面図(パッド開口工程完了時点)である。

【図3】図1の破線部分CのX−X’に対応するデバイス断面図(クロム膜スパッタ工程完了時点)である。

【図4】図1の破線部分CのX−X’に対応するデバイス断面図(銅シード膜スパッタ工程完了時点)である。

【図5】図1の破線部分CのX−X’に対応するデバイス断面図(第1のレジスト膜パターン形成工程完了時点)である。

【図6】図1の破線部分CのX−X’に対応するデバイス断面図(銅再配線電解メッキ工程完了時点)である。

【図7】図1の破線部分CのX−X’に対応するデバイス断面図(ニッケル再配線電解メッキ工程完了時点)である。

【図8】図1の破線部分Cに対応するデバイス上面図(第2のレジスト膜パターン形成工程完了時点)である。

【図9】図1または図8の破線部分CのX−X’に対応するデバイス断面図(第2のレジスト膜パターン形成工程完了時点)である。

【図10】図1の破線部分CのX−X’に対応するデバイス断面図(ニッケル・パッド電解メッキ工程完了時点)である。

【図11】図1の破線部分CのX−X’に対応するデバイス断面図(金パッド電解メッキ工程完了時点)である。

【図12】図1の破線部分CのX−X’に対応するデバイス断面図(第2のレジスト膜パターン除去工程完了時点)である。

【図13】図1の破線部分CのX−X’に対応するデバイス断面図(パッド上シード&バリア・メタル層除去工程完了時点)である。

【図14】本願の一実施の形態の半導体集積回路装置の製造方法における金パッド形成工程以降のプロセスの流れを示すための半導体ウエハの単位チップ領域の上面図(金パッド形成工程完了時点)である。

【図15】図14の破線部分Cの拡大上面図(金パッド形成工程完了時点)である。

【図16】図15に対応するデバイス斜視図(金パッド形成工程完了時点)である。

【図17】図14および15の破線部分CのX−X’に対応するデバイス断面図(ワイヤ・ボンディング工程完了時点)である。

【図18】図17に対応するデバイス斜視図(ワイヤ・ボンディング工程完了時点)である。

【図19】図1から図18(特に図17)に対応するデバイスまたは同プロセスに対する変形例(図7の工程が省略されている)を示すデバイス断面図(ワイヤ・ボンディング工程完了時点)である。

【符号の説明】

【0063】

1 半導体基板(半導体ウエハまたは半導体チップ)

1a 半導体基板の表主面(デバイス面または第1の主面)

1b 半導体基板の裏面(第2の主面)

1c チップ領域または半導体チップ

1p ボンディング・パッド下の配線層を含む半導体基板

2 アルミニウム系または銅系ボンディング・パッド(第1のパッド電極)

3 パッド開口

4 ファイナル・パッシベーション膜または第1の絶縁膜(下層から酸化シリコン膜、窒化シリコン膜、ポリイミド膜)

5 アルミニウム系パッド上バリア・メタル膜または下層の拡散バリア・メタル膜(クロム膜)

6 銅シード膜(上層の銅シード膜)

7 レジスト膜(第1のレジスト膜パターン)

8 電解メッキ銅再配線層(第1の再配線金属膜)

9 電解メッキ・ニッケル再配線層(第2の再配線金属膜)

10 レジスト膜の開口(第1のレジスト膜開口)

11 レジスト膜(第2のレジスト膜パターン)

12 レジスト膜の開口(第2のレジスト膜開口)

14 ニッケル・パッド膜(パッド下地膜)

15 金パッドまたは金パッド膜(第2のパッド電極)

16 再配線金属層または再配線パターン(下層銅、上層ニッケル)

17 配線基板

18 外部リード

19 ボンディング・ワイヤ

21 パッド上シード&バリア・メタル層(シード・メタル層)

C パッド周辺部

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)のデバイス構造および半導体集積回路装置(または半導体装置)の製造方法における外部接続技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2007−73611号公報(特許文献1)には、半導体チップ上のアルミニウム系ボンディング・パッド上方の再配線最上層である無電界メッキによるニッケル膜上に、無電界メッキによる金層を形成し、そこにボンディング・ワイヤを接続する技術が開示されている。

【0003】

【特許文献1】特開2007−73611号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいては、一般にバンプ電極による外部接続が主要な構造である。一方、このようなデバイスにおいても、ワイヤ・ボンディングにより外部接続をとりたいというニーズが広く存在する。そこで、日本特開2007−73611号公報(特許文献1)に開示されたように、無電界メッキによる積層金属再配線上に更に無電界メッキによってボンディング用の金メッキ表面膜を設け、そこにワイヤをボンディングする技術が考えられている。

【0005】

しかし、このような無電界メッキ・ベースの技術では、耐拡散性および耐衝撃性等を十分に確保することができず、高信頼性のデバイス及びプロセスを提供することが困難である。

【0006】

本願発明は、これらの課題を解決するためになされたものである。

【0007】

本発明の目的は、高信頼性の半導体集積回路装置または半導体集積回路装置の製造プロセスを提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、本願発明は半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するものである。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、半導体チップ上のアルミニウム系等のボンディング・パッド上方に再配線構造を有するデバイスにおいて、再配線上に電解メッキによるワイヤ・ボンディング用の金パッド層を形成するので、膜質が良好で十分に厚いパッド膜とすることができる。

【発明を実施するための最良の形態】

【0013】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0014】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハのデバイス面上の多層配線層上に、第1のパッド電極を形成する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記デバイス面側を第1の絶縁膜で被覆する工程;

(c)前記工程(b)の後、前記第1のパッド電極上の前記第1の絶縁膜にパッド開口を形成する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記デバイス面側にシード・メタル層を形成する工程;

(e)前記工程(d)の後、前記シード・メタル層上に、前記パッド開口を内部に含む第1のレジスト膜開口を有する第1のレジスト膜パターンを形成する工程;

(f)前記工程(e)の後、前記シード・メタル層上の前記第1のレジスト膜開口内に、電解メッキにより、再配線金属層を形成する工程;

(g)前記工程(f)の後、前記再配線金属層上に第2のレジスト膜開口を有する第2のレジスト膜パターンを、前記シード・メタル層および前記再配線金属層上に、形成する工程;

(h)前記工程(g)の後、前記再配線金属層上の前記第2のレジスト膜開口内に、電解メッキにより、金を主要な成分とする第2のパッド電極を形成する工程;

(i)前記工程(h)の後、前記第2のレジスト膜パターンを除去する工程。

【0015】

2.前記1項の半導体集積回路装置の製造方法において、更に以下の工程を含む:

(j)前記工程(i)の後、前記半導体ウエハを半導体チップに分割する工程;

(k)前記工程(j)の後、前記半導体チップの裏面を配線基板上に固定する工程;

(l)前記工程(k)の後、前記半導体チップの前記第2のパッド電極と前記半導体チップの外部の電極間を金を主要な成分とするボンディング・ワイヤで接続する工程。

【0016】

3.前記1または2項の半導体集積回路装置の製造方法において、前記再配線金属層は、銅を主要な成分とする第1の再配線金属膜を有する。

【0017】

4.前記3項の半導体集積回路装置の製造方法において、前記再配線金属層は、前記第1の再配線金属膜上に、ニッケルを主要な成分とする第2の再配線金属膜を有する。

【0018】

5.前記1から4項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内に電解メッキにより形成されたパッド下地膜がある。

【0019】

6.前記1から5項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【0020】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記シード・メタル層は、以下を含む:

(1)スパッタリングにより形成された下層の拡散バリア・メタル膜;

(2)スパッタリングにより形成された上層の銅シード膜。

【0021】

8.前記7項の半導体集積回路装置の製造方法において、前記下層の拡散バリア・メタル膜は、クロムを主要な成分とする。

【0022】

9.前記1から3および6から8項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内の前記第1の再配線金属膜上に直接、電解メッキにより形成されたパッド下地膜がある。

【0023】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の絶縁膜よりも上には、他の絶縁膜が実質的に存在しない。

【0024】

11.前記1から10項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の絶縁膜は以下を含む:

(1)下層の無機系絶縁膜;

(2)上層の有機系絶縁膜。

【0025】

12.前記11項の半導体集積回路装置の製造方法において、前記下層の無機系絶縁膜は、窒化シリコンを主要な成分とする膜を含む。

【0026】

13.前記11または12項の半導体集積回路装置の製造方法において、前記上層の有機系絶縁膜は、ポリイミドを主要な成分とする膜を含む。

【0027】

14.以下を含む半導体集積回路装置:

(a)デバイス面を有する半導体基板;

(b)前記デバイス面上の多層配線層;

(c)前記多層配線層上の第1のパッド電極;

(d)前記多層配線層および前記第1のパッド電極上のファイナル・パッシベーション膜;

(e)前記ファイナル・パッシベーション膜の前記第1のパッド電極上のパッド開口;

(f)前記パッド開口を通して、前記第1のパッド電極に接続された再配線金属層;

(g)前記再配線金属層の上面の一部に設けられた電解メッキによる金を主要な成分とする第2のパッド電極。

【0028】

15.前記14項の半導体集積回路装置において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【0029】

16.前記14または15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜;

(2)前記第1の再配線金属膜上に設けられた、ニッケルを主要な成分とする第2の再配線金属膜。

【0030】

17.前記16項の半導体集積回路装置において、前記第2の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【0031】

18.前記14または15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜。

【0032】

19.前記18項の半導体集積回路装置において、前記第1の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【0033】

20.前記14から19項のいずれか一つの半導体集積回路装置において、前記ファイナル・パッシベーション膜上には、他の絶縁膜がない。

【0034】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。

【0036】

たとえば、「アルミニウム」、「銅」、「ニッケル」、「金」、「クロム」等といっても、これらの単独の純粋なメタル材料を意味するものではなく、当該材料成分を主要な構成成分とし、必要に応じて他の副次的成分を配合又は添加して合金を形成したものも含むことは言うまでもない。

【0037】

更に、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0038】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0039】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0040】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0041】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0042】

1.本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド形成から再配線等のウエハ・プロセスの説明(主に図1から図16)

以下では、図1から図16に基づいて、主に半導体集積回路装置のウエハ・プロセスにおけるアルミニウム系パッド(銅系パッドその他でもよい)形成工程周辺以降を説明する。アルミニウム系パッド層より下層には、通常、銅系ダマシン多層配線層またはアルミニウム系通常多層配線層(一般に3層から10層程度)がある。以下の説明する図面では、ウエハについて説明する際も、簡潔性を確保するために、原則として単位チップ領域のみを表示する。

【0043】

図1に示すように、半導体ウエハ1(チップ領域1c)のデバイス面1a(裏面1bに対向する主面)には、多数のアルミニウム系ボンディング・パッド2(第1のパッド電極)が形成されている。パッド周辺部CのX−X’断面を図2に示す。以下に平面構造とともに製造プロセスを説明する。

【0044】

図2に示すように、ボンディング・パッド2下の多層配線層を含む半導体基板1p(本来の基板部分は通常、たとえば300ファイのp型の単結晶シリコン・ウエハである)のデバイス面1a側には、ファイナル・パッシベーション膜4が形成されている。ボンディング・パッド2を構成するアルミニウム系パッド層は、最上層配線層を兼ねてもよい。ボンディング・パッド2およびファイナル・パッシベーション膜4の形成については、以下のように形成する。まず、多層配線層上にスパッタリングにより、アルミニウム系メタル膜(通常、中間のアルミニウムを主要な成分とし、銅その他を数パーセント程度添加した主配線金属層の上下にTiN等の薄膜を有する)を成膜する。通常のリソグラフィにより、アルミニウム系メタル膜をパターニングし、ボンディング・パッド2を形成する。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の無機ファイナル・パッシベーション膜となる酸化シリコン系絶縁膜をプラズマCVD法により成膜する。続いて、その上に、たとえば、上層の無機ファイナル・パッシベーション膜となる窒化シリコン系絶縁膜をプラズマCVD法により成膜する。次に、この2層からなる無機ファイナル・パッシベーション膜に通常のリソグラフィにより、パッド開口3を形成する。この後、一般に主配線金属層上のTiN等が自己整合的にエッチング除去される。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、有機ファイナル・パッシベーション膜となるポリイミド膜を塗布する。続いて、先とほぼ同じ開口位置に再び通常のリソグラフィにより、パッド開口3を形成する。従って、最終的なファイナル・パッシベーション膜4(第1の絶縁膜)は、下層から酸化シリコン膜、窒化シリコン膜、およびポリイミド膜の三層重ね膜となる。これで、図2のような断面形態となる。このように、再配線パターン16上に、第2のポリイミド膜等の別のパッシベーション膜がないので、簡易な構造とすることができる。また、製造プロセスは大幅に簡素化される。このような簡素化が可能な理由は、最上層が膜質の良好な非腐食性の電解メッキによる金パッド膜15と成っているからである。

【0045】

次に、図3に示すように、半導体ウエハ1のデバイス面1a側のほぼ全面に、スパッタリングにより、拡散バリア・メタル膜5(たとえば75nm程度の厚さのクロム膜)を成膜する。バリア・メタルとしては、他にチタン、窒化チタン、および窒化タングステン等を主要な成分とするものが好適なものとして例示できる。

【0046】

その上に、図4に示すように、銅の電解メッキのためのシード膜6(たとえば250nm程度の厚さの銅膜)をスパッタリングにより、成膜する。

【0047】

次に、図5に示すように、半導体ウエハ1のデバイス面1a側のほぼ全面に、レジスト膜7(たとえば厚さ12マイクロ・メートル程度)を形成する。続いて、レジスト膜7を通常のリソグラフィにより、パターニングすることにより、第1のレジスト膜開口10を有する第1のレジスト膜パターン7を形成する。

【0048】

次に、図6に示すように、電解メッキにより、第1のレジスト膜開口10内に、選択的に第1の再配線金属膜8(たとえば、厚さ7.5マイクロ・メートル程度の銅メッキ膜)を形成する。

【0049】

更に、その上に、図7に示すように、電解メッキにより、第1のレジスト膜開口10内に、選択的に第2の再配線金属膜9(たとえば、厚さ2.3マイクロ・メートル程度のニッケル・メッキ膜)を形成する。この膜は、必須ではないが、付加することでデバイスの信頼性を向上させることができる。拡散または反応バリア膜として作用する。この第1の再配線金属膜8と第2の再配線金属膜9で再配線金属層16を構成している。

【0050】

次に、図8および図9に示すように、レジスト膜7(第1のレジスト膜パターン)を有する半導体ウエハ1のデバイス面1a側のほぼ全面に、レジスト膜11(たとえば厚さ12マイクロ・メートル程度)を形成する。続いて、レジスト膜11を通常のリソグラフィにより、パターニングすることにより、第2のレジスト膜開口12を有する第2のレジスト膜パターン11を形成する。

【0051】

次に、図10に示すように、電解メッキにより、第2のレジスト膜開口12内に、選択的にパッド下地膜14(たとえば、厚さ0.7マイクロ・メートル程度のニッケル・メッキ膜)を形成する。この膜は必須ではないが、付加することで、後の金メッキの膜質を良好にするメリットがある。

【0052】

更に、その上に、図11に示すように、電解メッキにより、第2のレジスト膜開口12内に、選択的に第2のパッド電極15(たとえば、厚さ1.0マイクロ・メートル程度の金メッキ膜)を形成する。メッキ液としては、たとえば、亜硫酸金ナトリウム系のメッキ液等が好適なものとして例示できる。

【0053】

次に、図12に示すように、不要になった第2のレジスト膜パターン11を除去溶剤・アッシング等により除去する。

【0054】

更に、図13に示すように、再配線金属層16の直下以外のシード・メタル層21(下層のクロム膜5および上層の銅シード膜6)を、たとえばウエット・エッチングにより除去する。まず、上層の銅シード膜6を自己整合的に、除去し(処理としては、たとえば、摂氏25度程度の過酸化水素水による10秒程度のウエット・エッチング処理を例示することができる)、続いて、下層のクロム膜5を除去する(処理としては、たとえば、摂氏25度程度の過マンガン酸カリウムとメタケイ酸ナトリウムの混合液等による20分程度のウエット・エッチング処理を例示することができる)。なお、以下の工程では、シード・メタル層21も含めて再配線金属層または再配線パターン等ということがある。

【0055】

以上により、図14に示すように、ここで、半導体ウエハ1のデバイス面1a側に、分離した再配線金属層または再配線パターン16が形成される。図15に図14のパッド周辺部Cの拡大平面図を示す。図16は、図15のX−X’断面でカットしたデバイスの斜視図である。

【0056】

2.本願の一実施の形態の半導体集積回路装置の製造方法における実装プロセスの説明(主に図17および図18)

ここでは、セクション1で説明したプロセスの、その後のプロセス(実装プロセス)を説明する。

【0057】

図17に示すように、ダイシング等により、個々のチップ1cに分割する。次に、チップ1cを配線基板17上にダイ・ボンディングする。その後、金を主要な成分とするボンディング・ワイヤ19を用いて、キャピラリを用いたボール・ボンディング(たとえばサーモ・ソニック・ボンディング)により、チップ1c上の金パッド15(第2のパッド電極)とチップ1c外の電極(たとえば配線基板17上の外部リード18)間を接続する。図18に図17の破線部分の斜視図(図16に続く)を示す。

【0058】

なお、この場合、いずれの電極にボールを配置してもよい。

【0059】

3.図1から図18について説明した半導体集積回路装置およびその製造方法に対する変形例の説明(主に図19)

この例は、セクション1および2に説明したプロセスにおいて、図7で説明した電解メッキ・ニッケル再配線層9(第2の再配線金属膜)の形成を省略したものである。これにより、再配線構造の簡略化が可能となる。電解メッキ・ニッケル再配線層9がなくとも、ニッケル・パッド膜14がバリア・メタル膜として作用するので、特性上の問題は比較的少ないと考えられる。

【0060】

4.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0061】

例えば、前記実施の形態においては、主に銅層とニッケル層の重ね膜を再配線の主要な構成部分とする例について、具体的に説明したが、本願発明はそれに限定されるものではなく、銅層単層を再配線の主要な構成部分とするもの等にも適用できることは言うまでもない。

【図面の簡単な説明】

【0062】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法におけるパッド開口工程以降のプロセスの流れを示すための半導体ウエハの単位チップ領域の上面図(パッド開口工程完了時点)である。

【図2】図1の破線部分CのX−X’に対応するデバイス断面図(パッド開口工程完了時点)である。

【図3】図1の破線部分CのX−X’に対応するデバイス断面図(クロム膜スパッタ工程完了時点)である。

【図4】図1の破線部分CのX−X’に対応するデバイス断面図(銅シード膜スパッタ工程完了時点)である。

【図5】図1の破線部分CのX−X’に対応するデバイス断面図(第1のレジスト膜パターン形成工程完了時点)である。

【図6】図1の破線部分CのX−X’に対応するデバイス断面図(銅再配線電解メッキ工程完了時点)である。

【図7】図1の破線部分CのX−X’に対応するデバイス断面図(ニッケル再配線電解メッキ工程完了時点)である。

【図8】図1の破線部分Cに対応するデバイス上面図(第2のレジスト膜パターン形成工程完了時点)である。

【図9】図1または図8の破線部分CのX−X’に対応するデバイス断面図(第2のレジスト膜パターン形成工程完了時点)である。

【図10】図1の破線部分CのX−X’に対応するデバイス断面図(ニッケル・パッド電解メッキ工程完了時点)である。

【図11】図1の破線部分CのX−X’に対応するデバイス断面図(金パッド電解メッキ工程完了時点)である。

【図12】図1の破線部分CのX−X’に対応するデバイス断面図(第2のレジスト膜パターン除去工程完了時点)である。

【図13】図1の破線部分CのX−X’に対応するデバイス断面図(パッド上シード&バリア・メタル層除去工程完了時点)である。

【図14】本願の一実施の形態の半導体集積回路装置の製造方法における金パッド形成工程以降のプロセスの流れを示すための半導体ウエハの単位チップ領域の上面図(金パッド形成工程完了時点)である。

【図15】図14の破線部分Cの拡大上面図(金パッド形成工程完了時点)である。

【図16】図15に対応するデバイス斜視図(金パッド形成工程完了時点)である。

【図17】図14および15の破線部分CのX−X’に対応するデバイス断面図(ワイヤ・ボンディング工程完了時点)である。

【図18】図17に対応するデバイス斜視図(ワイヤ・ボンディング工程完了時点)である。

【図19】図1から図18(特に図17)に対応するデバイスまたは同プロセスに対する変形例(図7の工程が省略されている)を示すデバイス断面図(ワイヤ・ボンディング工程完了時点)である。

【符号の説明】

【0063】

1 半導体基板(半導体ウエハまたは半導体チップ)

1a 半導体基板の表主面(デバイス面または第1の主面)

1b 半導体基板の裏面(第2の主面)

1c チップ領域または半導体チップ

1p ボンディング・パッド下の配線層を含む半導体基板

2 アルミニウム系または銅系ボンディング・パッド(第1のパッド電極)

3 パッド開口

4 ファイナル・パッシベーション膜または第1の絶縁膜(下層から酸化シリコン膜、窒化シリコン膜、ポリイミド膜)

5 アルミニウム系パッド上バリア・メタル膜または下層の拡散バリア・メタル膜(クロム膜)

6 銅シード膜(上層の銅シード膜)

7 レジスト膜(第1のレジスト膜パターン)

8 電解メッキ銅再配線層(第1の再配線金属膜)

9 電解メッキ・ニッケル再配線層(第2の再配線金属膜)

10 レジスト膜の開口(第1のレジスト膜開口)

11 レジスト膜(第2のレジスト膜パターン)

12 レジスト膜の開口(第2のレジスト膜開口)

14 ニッケル・パッド膜(パッド下地膜)

15 金パッドまたは金パッド膜(第2のパッド電極)

16 再配線金属層または再配線パターン(下層銅、上層ニッケル)

17 配線基板

18 外部リード

19 ボンディング・ワイヤ

21 パッド上シード&バリア・メタル層(シード・メタル層)

C パッド周辺部

【特許請求の範囲】

【請求項1】

以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハのデバイス面上の多層配線層上に、第1のパッド電極を形成する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記デバイス面側を第1の絶縁膜で被覆する工程;

(c)前記工程(b)の後、前記第1のパッド電極上の前記第1の絶縁膜にパッド開口を形成する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記デバイス面側にシード・メタル層を形成する工程;

(e)前記工程(d)の後、前記シード・メタル層上に、前記パッド開口を内部に含む第1のレジスト膜開口を有する第1のレジスト膜パターンを形成する工程;

(f)前記工程(e)の後、前記シード・メタル層上の前記第1のレジスト膜開口内に、電解メッキにより、再配線金属層を形成する工程;

(g)前記工程(f)の後、前記再配線金属層上に第2のレジスト膜開口を有する第2のレジスト膜パターンを、前記シード・メタル層および前記再配線金属層上に、形成する工程;

(h)前記工程(g)の後、前記再配線金属層上の前記第2のレジスト膜開口内に、電解メッキにより、金を主要な成分とする第2のパッド電極を形成する工程;

(i)前記工程(h)の後、前記第2のレジスト膜パターンを除去する工程。

【請求項2】

前記1項の半導体集積回路装置の製造方法において、更に以下の工程を含む:

(j)前記工程(i)の後、前記半導体ウエハを半導体チップに分割する工程;

(k)前記工程(j)の後、前記半導体チップの裏面を配線基板上に固定する工程;

(l)前記工程(k)の後、前記半導体チップの前記第2のパッド電極と前記半導体チップの外部の電極間を金を主要な成分とするボンディング・ワイヤで接続する工程。

【請求項3】

前記1項の半導体集積回路装置の製造方法において、前記再配線金属層は、銅を主要な成分とする第1の再配線金属膜を有する。

【請求項4】

前記3項の半導体集積回路装置の製造方法において、前記再配線金属層は、前記第1の再配線金属膜上に、ニッケルを主要な成分とする第2の再配線金属膜を有する。

【請求項5】

前記4項の半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内に電解メッキにより形成されたパッド下地膜がある。

【請求項6】

前記1項の半導体集積回路装置の製造方法において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【請求項7】

前記6項の半導体集積回路装置の製造方法において、前記シード・メタル層は、以下を含む:

(1)スパッタリングにより形成された下層の拡散バリア・メタル膜;

(2)スパッタリングにより形成された上層の銅シード膜。

【請求項8】

前記7項の半導体集積回路装置の製造方法において、前記下層の拡散バリア・メタル膜は、クロムを主要な成分とする。

【請求項9】

前記3項の半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内の前記第1の再配線金属膜上に直接、電解メッキにより形成されたパッド下地膜がある。

【請求項10】

前記1項の半導体集積回路装置の製造方法において、前記第1の絶縁膜よりも上には、他の絶縁膜が実質的に存在しない。

【請求項11】

前記1項の半導体集積回路装置の製造方法において、前記第1の絶縁膜は以下を含む:

(1)下層の無機系絶縁膜;

(2)上層の有機系絶縁膜。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記下層の無機系絶縁膜は、窒化シリコンを主要な成分とする膜を含む。

【請求項13】

前記12項の半導体集積回路装置の製造方法において、前記上層の有機系絶縁膜は、ポリイミドを主要な成分とする膜を含む。

【請求項14】

以下を含む半導体集積回路装置:

(a)デバイス面を有する半導体基板;

(b)前記デバイス面上の多層配線層;

(c)前記多層配線層上の第1のパッド電極;

(d)前記多層配線層および前記第1のパッド電極上のファイナル・パッシベーション膜;

(e)前記ファイナル・パッシベーション膜の前記第1のパッド電極上のパッド開口;

(f)前記パッド開口を通して、前記第1のパッド電極に接続された再配線金属層;

(g)前記再配線金属層の上面の一部に設けられた電解メッキによる金を主要な成分とする第2のパッド電極。

【請求項15】

前記14項の半導体集積回路装置において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【請求項16】

前記15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜;

(2)前記第1の再配線金属膜上に設けられた、ニッケルを主要な成分とする第2の再配線金属膜。

【請求項17】

前記16項の半導体集積回路装置において、前記第2の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【請求項18】

前記15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜。

【請求項19】

前記18項の半導体集積回路装置において、前記第1の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【請求項20】

前記14項の半導体集積回路装置において、前記ファイナル・パッシベーション膜上には、他の絶縁膜がない。

【請求項1】

以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハのデバイス面上の多層配線層上に、第1のパッド電極を形成する工程;

(b)前記工程(a)の後、前記半導体ウエハの前記デバイス面側を第1の絶縁膜で被覆する工程;

(c)前記工程(b)の後、前記第1のパッド電極上の前記第1の絶縁膜にパッド開口を形成する工程;

(d)前記工程(c)の後、前記半導体ウエハの前記デバイス面側にシード・メタル層を形成する工程;

(e)前記工程(d)の後、前記シード・メタル層上に、前記パッド開口を内部に含む第1のレジスト膜開口を有する第1のレジスト膜パターンを形成する工程;

(f)前記工程(e)の後、前記シード・メタル層上の前記第1のレジスト膜開口内に、電解メッキにより、再配線金属層を形成する工程;

(g)前記工程(f)の後、前記再配線金属層上に第2のレジスト膜開口を有する第2のレジスト膜パターンを、前記シード・メタル層および前記再配線金属層上に、形成する工程;

(h)前記工程(g)の後、前記再配線金属層上の前記第2のレジスト膜開口内に、電解メッキにより、金を主要な成分とする第2のパッド電極を形成する工程;

(i)前記工程(h)の後、前記第2のレジスト膜パターンを除去する工程。

【請求項2】

前記1項の半導体集積回路装置の製造方法において、更に以下の工程を含む:

(j)前記工程(i)の後、前記半導体ウエハを半導体チップに分割する工程;

(k)前記工程(j)の後、前記半導体チップの裏面を配線基板上に固定する工程;

(l)前記工程(k)の後、前記半導体チップの前記第2のパッド電極と前記半導体チップの外部の電極間を金を主要な成分とするボンディング・ワイヤで接続する工程。

【請求項3】

前記1項の半導体集積回路装置の製造方法において、前記再配線金属層は、銅を主要な成分とする第1の再配線金属膜を有する。

【請求項4】

前記3項の半導体集積回路装置の製造方法において、前記再配線金属層は、前記第1の再配線金属膜上に、ニッケルを主要な成分とする第2の再配線金属膜を有する。

【請求項5】

前記4項の半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内に電解メッキにより形成されたパッド下地膜がある。

【請求項6】

前記1項の半導体集積回路装置の製造方法において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【請求項7】

前記6項の半導体集積回路装置の製造方法において、前記シード・メタル層は、以下を含む:

(1)スパッタリングにより形成された下層の拡散バリア・メタル膜;

(2)スパッタリングにより形成された上層の銅シード膜。

【請求項8】

前記7項の半導体集積回路装置の製造方法において、前記下層の拡散バリア・メタル膜は、クロムを主要な成分とする。

【請求項9】

前記3項の半導体集積回路装置の製造方法において、前記再配線金属層と前記第2のパッド電極の間には、ニッケルを主要な成分とし、第2のレジスト膜開口内の前記第1の再配線金属膜上に直接、電解メッキにより形成されたパッド下地膜がある。

【請求項10】

前記1項の半導体集積回路装置の製造方法において、前記第1の絶縁膜よりも上には、他の絶縁膜が実質的に存在しない。

【請求項11】

前記1項の半導体集積回路装置の製造方法において、前記第1の絶縁膜は以下を含む:

(1)下層の無機系絶縁膜;

(2)上層の有機系絶縁膜。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記下層の無機系絶縁膜は、窒化シリコンを主要な成分とする膜を含む。

【請求項13】

前記12項の半導体集積回路装置の製造方法において、前記上層の有機系絶縁膜は、ポリイミドを主要な成分とする膜を含む。

【請求項14】

以下を含む半導体集積回路装置:

(a)デバイス面を有する半導体基板;

(b)前記デバイス面上の多層配線層;

(c)前記多層配線層上の第1のパッド電極;

(d)前記多層配線層および前記第1のパッド電極上のファイナル・パッシベーション膜;

(e)前記ファイナル・パッシベーション膜の前記第1のパッド電極上のパッド開口;

(f)前記パッド開口を通して、前記第1のパッド電極に接続された再配線金属層;

(g)前記再配線金属層の上面の一部に設けられた電解メッキによる金を主要な成分とする第2のパッド電極。

【請求項15】

前記14項の半導体集積回路装置において、前記第1のパッド電極は、アルミニウム系の膜を主要な構成要素とする。

【請求項16】

前記15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜;

(2)前記第1の再配線金属膜上に設けられた、ニッケルを主要な成分とする第2の再配線金属膜。

【請求項17】

前記16項の半導体集積回路装置において、前記第2の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【請求項18】

前記15項の半導体集積回路装置において、前記再配線金属層は、以下を含む:

(1)銅を主要な成分とする第1の再配線金属膜。

【請求項19】

前記18項の半導体集積回路装置において、前記第1の再配線金属膜と前記第2のパッド電極との間には、ニッケルを主要な成分とし、電解メッキにより形成されたパッド下地膜が設けられている。

【請求項20】

前記14項の半導体集積回路装置において、前記ファイナル・パッシベーション膜上には、他の絶縁膜がない。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2010−147051(P2010−147051A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−319355(P2008−319355)

【出願日】平成20年12月16日(2008.12.16)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月16日(2008.12.16)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]