半導体集積回路装置および半導体集積回路装置の製造方法

【課題】動作速度が高速になっても、パッド再配線間抵抗ばらつきに起因する不良モードの増加を抑えた半導体集積回路装置および半導体集積回路装置の製造方法を提供する。

【解決手段】ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッド2pと再配線16との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下とした。

【解決手段】ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッド2pと再配線16との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置のデバイス構造および半導体集積回路装置(または半導体装置)の製造方法におけるパッド周辺構造形成技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2008−60145号公報(特許文献1)または、その対応米国特許公開2008−0054479号公報(特許文献2)には、半導体デバイス・チップ上のアルミニウム系のパッドと上層の再配線との間にスパッタ法等によるチタン、窒化チタン、銅等の導電材料を複数積層して形成された下地金属層を設ける技術が開示されている。

【0003】

また、日本特開2000−306938号公報(特許文献3)については、半導体デバイス・チップ上のアルミニウム合金のパッドと上層のアルミニウム合金の再配線との間に、密着性向上目的で、チタン膜、あるいは窒化チタン膜、あるいは、チタン膜と窒化チタン膜との複合膜を形成する技術が開示されている。

【0004】

【特許文献1】特開2008−60145号公報

【特許文献2】米国特許公開2008−0054479号公報

【特許文献3】特開2000−306938号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本願発明者らは、再配線を有するウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗ばらつき(「パッド再配線間抵抗ばらつき」)が、デバイスの動作特性に与える影響について、検討した。それによると、従来製品では、パッド再配線間抵抗ばらつきは、通常の範囲では、ほとんど製品特性に影響しないとされてきた。しかし、最近の動作速度の高速化に伴い、パッド再配線間抵抗ばらつきに起因する不良モードが増加していることが明らかとなった。

【0006】

本願発明は、これらの課題を解決するためになされたものである。

【0007】

本発明の目的は、信頼性の高い半導体集積回路装置を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下としたものである。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下としたことにより、バリア効果を保持した状態で、抵抗の上昇またはプロセス・コストの上昇を回避することができる。

【発明を実施するための最良の形態】

【0013】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0014】

1.以下を含む半導体集積回路装置:

(a)多層配線層を含む半導体基板のデバイス面上の前記多層配線層上に設けられたアルミニウム系パッド電極;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜;

(c)前記開口を覆うように、前記アルミニウム系パッド電極上および前記絶縁膜上に設けられた再配線メタル・パターン;

(d)前記再配線メタル・パターン下の前記アルミニウム系パッド電極上および前記絶縁膜上に設けられたバリア・メタル層、

ここで、前記バリア・メタル層は、以下を含む:

(d1)チタンを主要な成分とする第1のメタル層;

(d2)前記第1のメタル層上に設けられた窒化チタンを主要な成分とする第2のメタル層;

(d3)前記第2のメタル層上に設けられたチタンを主要な成分とする第3のメタル層、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【0015】

2.前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、50nm以下である。

【0016】

3.前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、25nm以下である。

【0017】

4.前記1から3項のいずれか一つの半導体集積回路装置において、前記再配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【0018】

5.前記1から4項のいずれか一つの半導体集積回路装置において、前記第1のメタル層直下の前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【0019】

6.前記1から5項のいずれか一つの半導体集積回路装置において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【0020】

7.前記1から6項のいずれか一つの半導体集積回路装置において、前記再配線メタル・パターン上には、半田バンプが設けられている。

【0021】

8.前記6項の半導体集積回路装置において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【0022】

9.前記7項の半導体集積回路装置において、前記半田バンプは鉛フリーとされている。

【0023】

10.前記7または9項の半導体集積回路装置において、前記半田バンプは金を含む。

【0024】

11.以下の工程を含む半導体集積回路装置の製造方法:

(a)多層配線層を含む半導体ウエハのデバイス面側の前記多層配線層上に、アルミニウム系パッド電極を形成する工程;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜を形成する工程;

(c)前記ウエハの前記デバイス面側のほぼ全面に、アルミニウム系パッド電極に接続されたシード・メタル膜を、スパッタリングにより成膜する工程;

(d)前記シード・メタル膜上に、レジスト膜パターンを形成する工程;

(e)前記レジスト膜パターンが存在する状態で、前記シード・メタル膜上に、電解メッキにより、再配線メタル・パターンを形成する工程;

(f)前記再配線メタル・パターンをエッチング・マスクとして、前記再配線メタル・パターンがない部分の前記シード・メタル膜を除去する工程、

ここで、前記工程(c)は、以下の下位工程を含む:

(c1)前記半導体ウエハの前記デバイス面側に対して、アルゴン・ガスを主要な成分とする気相中において、プラズマ処理を実行する工程;

(c2)前記工程(c1)の後、チタンを主要な成分とする第1のメタル層をスパッタリングにより成膜する工程;

(c3)前記第1のメタル層上に、窒化チタンを主要な成分とする第2のメタル層をスパッタリングにより成膜する工程;

(c4)前記第2のメタル層上に、チタンを主要な成分とする第3のメタル層をスパッタリングにより成膜する工程;

(c5)前記第3のメタル層上に、前記再配線メタル・パターンに対し、シードとして作用する第4のメタル層をスパッタリングにより成膜する工程、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【0025】

12.前記11項の半導体集積回路装置の製造方法において、前記工程(c)は、同一のスパッタリング装置内において、大気に触れさせることなく実行される。

【0026】

13.前記11または12項の半導体集積回路装置の製造方法において、前記下位工程(c2)から(c4)は、同一のチャンバ内で実行される。

【0027】

14.前記11から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、50nm以下である。

【0028】

15.前記11から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、25nm以下である。

【0029】

16.前記11から15項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【0030】

17.前記11から16項のいずれか一つの半導体集積回路装置の製造方法において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【0031】

18.前記17項の半導体集積回路装置の製造方法において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【0032】

19.前記11から18項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線メタル・パターン上には、半田バンプが設けられている。

【0033】

20.前記11から19項のいずれか一つの半導体集積回路装置の製造方法において、前記下位工程(c2)を開始する時点では、前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【0034】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。

【0036】

具体的には、「金」、「ニッケル」、「銅」、「チタン」、「窒化チタン」、「アルミニウム」等といっても、特にそうでない旨、明示した場合又は理論的にそうでないことが明らかな場合等を除き、「各物質を主要な成分とする部材」を意味するものとする。また、たとえば「アルミニウム・パッド」、「アルミニウム系パッド」といっても、パッド構造の全てが、アルミニウムを主要な成分とする部材でできているのではなく、アルミニウムを主要な成分とする部材による構造要素がパッド構造の主要部を占めることを表す。このことは、アルミニウム系配線、銅系配線等についても同様である。

【0037】

更に、たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0038】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0039】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0040】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコン・ウエハを指すが、エピタキシャル・ウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0041】

6.「配線メタル・パターン」、「再配線メタル・パターン」、「再配線メタル膜」というときは、原則として、下地のシード・メタル層を含まないこととする。また、当該下地のシード・メタル層は、下層のバリア・メタル層、最上層のシード銅層等から構成されている。

【0042】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0043】

1.本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れの説明(主に図1から図18)

以下では、図1から図16(図17および図18を参照)に基づいて、主に半導体集積回路装置のウエハ・プロセスにおけるアルミニウム系パッド2p(図1参照、以下同じ。パッド電極は銅系パッドその他でもよい)形成工程周辺以降を説明する。アルミニウム系パッド層2より下層には、通常、銅系ダマシン多層配線層1wまたはアルミニウム系通常多層配線層1w(一般に3層から10層程度)がある。

【0044】

図1および、そのパッド近傍部Cの詳細である図2に示すように、半導体ウエハ1(チップ領域1c)のデバイス面1a(裏面1bに対向する主面)側のタングステン・プラグ7および最上層層間絶縁膜6上には、アルミニウム系パッド2pが形成されている。ボンディング・パッド2p下の多層配線層1wを含む半導体基板1p(本来の基板部分1sは通常、たとえば300ファイのp型の単結晶シリコン・ウエハである)のデバイス面1a側には、無機系ファイナル・パッシベーション膜3が形成されている。ボンディング・パッド2pを構成するアルミニウム系パッド層2は、この例では最上層配線層2wを兼ねている(パッド専用でもよい)。ボンディング・パッド2pおよびファイナル・パッシベーション膜3の形成については、以下のように形成する。まず、多層配線層上にスパッタリングにより、アルミニウム系メタル膜(通常、中間のアルミニウムを主要な成分とし、銅その他を数パーセント程度添加した1000nm程度の厚さの主配線金属層2pの上下に10nm程度の厚さのチタン膜8a,8c、50から75nm程度の厚さの窒化チタン膜8b,9等の薄膜を有する。チタン膜8a,8cと窒化チタン膜8bでパッド下地メタル層8を構成している)を成膜する。通常のリソグラフィにより、アルミニウム系メタル膜をパターニングし、ボンディング・パッド2pを形成する。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の無機ファイナル・パッシベーション膜3aとなる酸化シリコン系絶縁膜(たとえば厚さ200nm程度)をプラズマCVD法により成膜する。続いて、その上に、たとえば、上層の無機ファイナル・パッシベーション膜3bとなる窒化シリコン系絶縁膜(たとえば厚さ600nm程度)をプラズマCVD法により成膜する。次に、この2層からなる無機ファイナル・パッシベーション膜3に通常のリソグラフィにより、パッド開口5を形成する(この後、一般に主配線金属層上の窒化チタン膜9等が、たとえばアルゴン、塩素等の混合ガス雰囲気中で自己整合的にドライ・エッチング除去される。これで、図2のような断面形態となる)。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の有機ファイナル・パッシベーション膜4となるポリイミド膜(たとえば厚さ4マイクロ・メートル程度)を塗布する。続いて、先とほぼ同じ開口位置に再び通常のリソグラフィにより、パッド開口5を形成する(図17の下層ポリイミド層パターニング工程101)。従って、この段階の複合ファイナル・パッシベーション膜10(絶縁膜)は、下層から酸化シリコン膜3a、窒化シリコン膜3b、およびポリイミド膜4の三層重ね膜となる。なお、後ほど説明するが、通常、この上に更に、有機系の絶縁膜がもう一つのファイナル・パッシベーション膜として形成される。

【0045】

ここで、アルミニウム系パッド電極2pのアルミニウム系メタル表面(アルミニウムを主要な成分とする面が露出しているパッド上面)は非常に酸化されやすいので、下層有機系ファイナル・パッシベーション膜4をパターニングして、次の工程に仕掛かる段階でみると、図3に示すように、数nm程度の自然酸化膜11(酸化アルミニウム膜)が存在する。このままでは、パッド・再配線間抵抗ばらつきが増大する可能性があるので、図3の状態で、ウエハ1のデバイス面1aに対して、アルゴン・スパッタリング等のプラズマ・エッチング処理(スパッタリング・エッチ)を実行して(処理条件は、たとえば、室温、アルゴン雰囲気、0.05Pa程度の気圧、処理時間30秒程度)、図4に示すように、酸化アルミニウム膜11を除去または3nm程度以下に薄膜化することが有効である(図18のアルゴン・スパッタ工程102b)。ここでのプラズマ・エッチング処理(アルゴン・スパッタ工程102b)は、酸化アルミニウム膜11を完全に除去する必要はなく、全体に薄膜化すればよい。これは、薄膜の酸化アルミニウム膜11は、アルミニウム表面を保護する効果もあり、また、完全に除去しても、再度、生成するので、実質的な効果が期待できない。また、過剰に、プラズマ・エッチング処理を行うと、下層有機系ファイナル・パッシベーション膜4(ポリイミド膜)からの生成物の影響で、かえってデバイス特性が劣化する恐れがある。なお、良品の製品段階でも薄膜の酸化アルミニウム膜11が残存していることは、顕微鏡的に確認されている。

【0046】

次に、図5に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード・メタル層12をスパッタリングにより成膜する(図17および図18のシード層スパッタ工程102)。このシード層スパッタ工程102の詳細を図6から図9および図18に基づいて説明する。

【0047】

まず、図6に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル最下層12a(第1のメタル層)として、チタンを主要な成分とするメタル膜(比較的純粋なチタン膜が好適なものとして例示できる)をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン雰囲気、0.5Pa程度の気圧、処理時間8秒程度)により成膜する(図18の下層チタン・スパッタ工程102c)。この膜は、パッド表面の酸化アルミニウム膜を還元する作用がある。

【0048】

次に、図7に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル中間層12b(第2のメタル層)として、窒化チタンを主要な成分とするメタル膜を窒素ガス雰囲気中でのスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン+窒素ガス雰囲気、0.5Pa程度の気圧、処理時間30秒程度)により成膜する(図18の窒化チタン・スパッタ工程102d)。この膜は、窒素を多く含み、銅等に対する拡散バリア性が高い。チタン膜等に比べて厚さの割りにバリア性が高いので、窒化チタン膜を用いることにより、バリア・メタル膜全体を薄くするメリットがある。ただし、単独では電気抵抗が高く、上層との接着性にも若干問題がある。

【0049】

続いて、図8に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル最上層12c(第3のメタル層)として、チタンを主要な成分とするメタル膜をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン雰囲気、0.5Pa程度の気圧、処理時間8秒程度)により成膜する(図18の上層チタン・スパッタ工程102e)。この膜は、上層との接着性向上のためであり、比較的純粋なものである必要はない。

【0050】

これらのシード下地メタル最下層12a、シード下地メタル中間層12b、およびシード下地メタル最上層12cでバリア・メタル層14(図8)を構成している。また、下層チタン・スパッタ工程102cから上層チタン・スパッタ工程102eでバリア・メタル・スパッタ工程112を構成している。なお、シード下地メタル最下層12aおよびシード下地メタル最上層12cの膜厚目標値は、たとえば10nm程度であり、実用的な範囲は、5nmから60nm程度である。また、シード下地メタル中間層12bの膜厚目標値は、たとえば50nm程度であり、実用的な範囲は、30nmから100nm程度である。

【0051】

更に、図9に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード銅層12d(第4のメタル層)として、銅を主要な成分とするメタル膜をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度は室温、アルゴン雰囲気、0.05Pa程度の気圧、処理時間15秒程度)により成膜する。シード銅層12dの膜厚目標値は、たとえば150nm程度であり、実用的な範囲は、100nmから200nm程度である。これらのバリア・メタル層14およびシード銅層12dでシード・メタル層12を構成している。

【0052】

次に、図10に示すように、シード・メタル層12上に通常のリソグラフィにより、レジスト膜パターン15を形成する(図17のレジスト・パターニング工程)。続いて、図11に示すように、電解メッキにより、銅を主要な成分とする再配線メタル膜下層膜16a(膜厚目標値は、たとえば5.7マイクロ・メートル程度であり、実用的な範囲は、4マイクロ・メートルから10マイクロ・メートル程度である。)を選択的に形成する。次に、再配線メタル膜下層膜16a上に、電解メッキにより、ニッケルを主要な成分とする再配線メタル膜上層膜16b(膜厚目標値は、たとえば2.7マイクロ・メートル程度であり、実用的な範囲は、2マイクロ・メートルから4マイクロ・メートル程度である。)を選択的に形成する(図17の再配線電解メッキ工程104)。再配線メタル膜下層膜16a、再配線メタル膜上層膜16b等で再配線メタル膜(再配線メタル・パターン、配線メタル・パターン)16を構成する。

【0053】

次に、図12に示すように、不要なレジスト膜パターン15を除去するとともに、再配線メタル・パターン16外部の。次に、図13にシード・メタル層12をウエット・エッチングにより自己整合的に除去する(図17のレジスト除去&ウエット・エッチング工程105)。

【0054】

次に、図13に示すように、ウエハ1のデバイス面1a側に、通常のリソグラフィにより、上層有機系ファイナル・パッシベーション膜22として、バンプ形成用開口17(ランド開口部の径は、たとえば90から200マイクロ・メートル)を有するポリイミド膜パターン(たとえば厚さ6マイクロ・メートル程度)を形成する(図17の上層ポリイミド層パターニング工程106)。

【0055】

更に、図14に示すように、バンプ形成用開口17内のバンプ形成部21の表面に無電解メッキにより、金を主要な成分とする保護メタル層18を形成する(図17の無電解金メッキ工程)。

【0056】

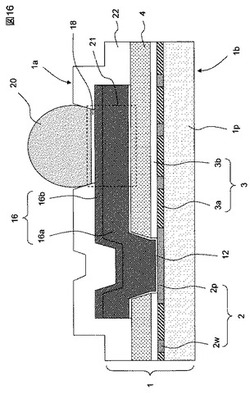

次に、図15に示すように、保護メタル層18にプローブ針19を接触させることにより、プローブ検査を実行する(図17のプローブ検査工程)。次に、図16に示すように、半田ペースト印刷法、ボール配列法等および半田リフロー処理により、バンプ形成部21のニッケル表面上に半田バンプ20を形成する。このとき、保護メタル層18の金はバンプ内に拡散するので、半田リフロー処理の結果として、最終的に保護メタル層18は消失する。

【0057】

なお、図17のプローブ検査工程108およびBG工程109は、バンプ形成工程110の後に実施してもよい。

【0058】

2.本願の一実施の形態の半導体集積回路装置の製造方法に使用する製造装置等の説明(主に図19から図22、図17および図18を参照)

このセクションでは、セクション1に説明したプロセスの一部について各製造装置プロセスの面から説明する。まず、図17および図18のシード層スパッタ成膜工程102について説明する。なお、半田リフロー処理以降のプロセスについても、便宜上このセクションで説明する。

【0059】

図17の下層ポリイミド層パターニング工程101に引き続き、図19に示すように、先ず、フープ52内に収容されたウエハ1は、ロード&アンロード用ロボット59によって、マルチ・チャンバ型のスパッタリング装置51(スパッタリング及び、それに関連する処理を連続的に実行する装置)のバッファ室56内に導入される。その後、ロード&アンロード用ロボット59によって、ロードロック室57を通して、真空搬送室58内に導入され、真空搬送ロボット60によって、アルゴン・スパッタ室53に導入される。そこで、まず、ウエハ1の表面に吸着されたガスを放出させるためのデガス処理102a(図18)が実施される(処理条件は、たとえば、ウエハ・ステージ設定温度は摂氏250度程度、添加ガスがない空引き状態、1KPa程度の気圧、規定圧力到達より処理時間30秒程度)。続いて、そのまま、アルゴン・スパッタ処理102bが実行される。

【0060】

次に、ウエハ1は、真空搬送ロボット60によって、チタン系メタル・スパッタ室54に移送される。そこで、バリア・メタル・スパッタ工程112が連続的に実行される。すなわち、順に下層チタン層スパッタ・ステップ102c、窒化チタン層スパッタ・ステップ102d、および上層チタン層スパッタ・ステップ102eである。

【0061】

次に、ウエハ1は、真空搬送ロボット60によって、銅スパッタ室55に移送される。そこで、銅シード層スパッタ・ステップ102fが実行される。ここで、ウエハ1は、最初にロードロック室57に導入され、各処理チャンバ53,54,55の処理が終わって、再びロードロック室57に戻るまで(ロードロック室が複数あるので同一とは限らない)の間、大気にさらされることがない。

【0062】

その後、ウエハ1は、真空搬送ロボット60によって、ロードロック室57に移送され、そこからロード&アンロード用ロボット59によって、フープ52内に戻され、次のレジスト・パターニング工程103(図17)のための処理セクションに移送される。そこで、レジスト膜パターン15が形成されたウエハ1は、再びフープ52に戻されて、メッキ装置71(メッキ関連処理装置)に移送される。メッキ装置71においては、以下のように処理される。

【0063】

図20に示すように、先ず、ウエハ1は、フープ52内から、ロード&アンロード用ロボット59によって、バッファ室56内に導入される。そこから内部搬送ユニット74の内部搬送ロボット75により、電解メッキ・ユニット72内のプリ・ディップ槽79に移送され、そこで濡れ性向上、有機成分除去等のために燐酸系の処理液により前処理(液温は室温、処理時間は200秒程度)が実施される。次に、ウエハ1は、内部搬送ロボット75により、水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次に、ウエハ1は、内部搬送ロボット75により、銅電解メッキ槽81に移送され、そこで再配線電解メッキ工程104(図17)の第1ステップである銅電解メッキ処理が、たとえば硫酸系銅メッキ液を用いて行われる(液温は室温、処理時間は460秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次に、ウエハ1は、内部搬送ロボット75により、酸処理槽77に移送され、そこで表面金属酸化物除去等のために硫酸系の処理液により前処理が実施される(液温は室温、処理時間は80秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1は、内部搬送ロボット75により、ニッケル電解メッキ槽82に移送され、そこで、再配線電解メッキ工程104(図17)の第2ステップであるニッケル電解メッキ処理が、たとえばホウ酸系ニッケル・メッキ液を用いて行われる(液温は摂氏55度程度、処理時間は450秒程度)。次にウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は50秒程度)。更に、ウエハ1は、内部搬送ロボット75により、スピン・リンス&ドライ・ステージ76に移送され、そこのスピンステージ上でリンス及びスピン乾燥が実施される(液温は室温、処理時間は90秒程度)。その後、ウエハ1は内部搬送ロボット75およびロード&アンロード用ロボット59によって、フープ52に戻される。次に、フープ52はレジスト除去&ウエット・エッチ工程105(図17)のためのユニットに移送される。

【0064】

上層ポリイミド層パターニング工程106(図17)が完了すると、ウエハ1は再び、フープ52内に収容されて、メッキ装置71に移送される。先と同様に、ウエハ1は、フープ52内から、ロード&アンロード用ロボット59によって、バッファ室56内に導入される。そこから内部搬送ユニット74の内部搬送ロボット75により、電解メッキ・ユニット72内のプリ・ディップ槽79に移送され、そこで濡れ性向上、有機成分除去等のために有機塩酸系の処理液により前処理が実施される。次にウエハ1、内部搬送ロボット75により、水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1、内部搬送ロボット75により、酸処理槽77に移送され、そこで表面金属酸化物除去、表面活性化等のために塩酸系の処理液により前処理が実施される(液温は室温、処理時間は80秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1、内部搬送ロボット75により、無電解メッキ槽91に移送され、そこで無電解金メッキ工程107(図17)が、たとえば亜硫酸金メッキ液を用いて実行される(液温は摂氏55度程度、処理時間は450秒程度)。次にウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は100秒程度)。更に、ウエハ1は、内部搬送ロボット75により、スピン・リンス&ドライ・ステージ76に移送され、そこのスピンステージ上でリンス及びスピン乾燥が実施される(液温は室温、処理時間は90秒程度)。その後、ウエハ1は内部搬送ロボット75およびロード&アンロード用ロボット59によって、フープ52に戻される。次に、フープ52はレジスト除去&ウエット・エッチ工程105(図17)のためのユニットに移送される。

【0065】

その後、ウエハ1を収容したフープ52は、順次、プローブ検査工程108(図17)およびバック・グラインディング工程109(図17)のためのそれぞれのユニットに送られえて、各処理を終えた後、バンプ形成工程110(図17)のため、半田ペースト印刷装置61(図21)または半田バンプ配列装置62(図22)へ搬送される。半田ペースト印刷装置61は、一般品に適しており、半田バンプ配列装置62は、バンプ・ピッチが100マイクロ・メートル程度以下の狭ピッチ品に適している。

【0066】

先ず、半田ペースト印刷装置61を使用したバンプ形成プロセス110(図17)について説明する。図21に示すように、ウエハ1上の複数のバンプ形成部21と印刷マスク32のマスク開口37が一致するように、ウエハ1上に印刷マスク32を重ねた状態で、スキージ(Squeegee)を水平移動させることにより、半田ペースト33が各マスク開口37を満たすようにする。その後、印刷マスク32を剥がすと、半田ペースト33がバンプ形成部21上に印刷された状態となる。これにリフロー処理をすると、半田が自立的に図16のような形状となる。

【0067】

次に、半田バンプ配列装置62を使用したバンプ形成プロセス110(図17)について説明する。図22に示すように、先ず、ウエハ1上の複数のバンプ形成部21にフラックス35を印刷しておく。その状態で、整列マスク34の各マスク開口37が複数のバンプ形成部21と一致するように、ウエハ1上に整列マスク32を一定の間隔を置いて重ねた状態で、上方から整形した半田ボール36を供給する。半田ボール36は、各マスク開口37内に一個ずつ入り、フラックス35と仮接着される。その後、整列マスク32を除去して、先と同様に、リフロー処理をすると、半田が自立的に図16のような形状となる。

【0068】

これらのバンプ形成プロセス110(図17)が完了した後、ウエハ1を個々のチップ1cに分割するダイシング工程111(図17)を実行する。

【0069】

3.各種データの説明(主に図23から図26)

このセクションでは、前2セクションで説明した本願発明の実施の形態についての各種検証データ、参考データ等について説明する。

【0070】

図23は、図12の構造における下層チタン膜厚と(単一のコンタクトについての)パッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図である。この図において、四角形のデータは、通常の10マイクロメータ角のパッド開口について測定したもので、円形のデータは、試験用に5マイクロメータ角のパッド開口について測定したものである。後者のほうが、より抵抗ばらつきに敏感になる傾向がある。

【0071】

図23に示されたように、シード下地メタル最下層(第1のメタル層)すなわち、下層チタン膜の膜厚が3nm程度では、パッド再配線間抵抗値は下層チタン膜がないのと同等である。一方、下層チタン膜の膜厚が5nm程度以上では、パッド再配線間抵抗値は安定的に低い値となる。従って、プロセスばらつきを考慮すると、下層チタン膜の膜厚の下限値は、5nm程度が好適である。

【0072】

図24は図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が10マイクロ・メートル角である場合)である。また、図25は図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が5マイクロ・メートル角である場合)である。これらから、パッド再配線間抵抗値の分布についても、下層チタン膜の膜厚が5nm程度以上では、ばらつきが小さいことがわかる。

【0073】

次に、下層チタン膜の膜厚の適正な上限について検討する。図26は図16の構造における下層チタン膜厚とパッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図(図23とは相違して、コンタクト数個分、バンプを経由して測定)である。このデータは、数個分の直列接続およびバンプその他の抵抗を含むため絶対値は高くなっているが、相対的な変化を見る上で有用である。

【0074】

図26に示されたように、下層チタン膜の膜厚が25nm程度以上で顕著な抵抗値の上昇が見られ、実用上、およびプロセス・コストを考慮すると60nm程度までが現実的な範囲と考えられる。したがって、下層チタン膜の膜厚の適正な上限は、60nm程度と見られる。

【0075】

図23及び図26等から、下層チタン膜の実用的な膜厚範囲は、5nm以上、60nm以下である。また、量産性を考慮した適正な範囲は、5nm以上、50nm以下である。更に、低抵抗性等も考慮した最も好適な範囲は、5nm以上、25nm以下である。

【0076】

4.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0077】

例えば、前記実施の形態では、下層の銅再配線層および上層のニッケル再配線層からなる2層構成の再配線について、具体的に説明したが、本発明はそれに限定されるものではなく、銅単独再配線層構造、その他多層の再配線構造にも適用できることは言うまでもない。また、半導体基板として、p型単結晶シリコン基板を用いた例について、具体的に説明したが、本発明はそれに限定されるものではなく、n型単結晶シリコン基板等のその他の単結晶半導体基板,SOI基板、ガラス基板等の絶縁性基板、GaAsその他の化合物半導体基板等を用いたものにも適用できることは言うまでもない。

【0078】

また、前記実施の形態では、有機系ファイナル・パッシベーション膜として、ポリイミド系の樹脂膜を使用する例を示したが、本発明はそれに限定されるものではなく、BCB(Benzo−Cyclo−Butene)その他の耐熱性ポリマー系の樹脂膜を用いたものでもよいことは、言うまでもない。

【図面の簡単な説明】

【0079】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(下層ポリイミド層パターニング工程)である。

【図2】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(下層ポリイミド層パターニング工程)である。

【図3】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(工程間における自然酸化膜の形成の様子を示す)である。

【図4】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(アルゴン・スパッタ・ステップ)である。

【図5】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(シード・メタル層スパッタ工程)である。

【図6】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(下層チタン層スパッタ・ステップ)である。

【図7】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(窒化チタン層スパッタ・ステップ)である。

【図8】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(上層チタン層スパッタ・ステップ)である。

【図9】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(銅シード層スパッタ・ステップ)である。

【図10】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(レジスト膜パターニング工程)である。

【図11】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(再配線メタル電解メッキ工程)である。

【図12】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(レジスト膜除去工程)である。

【図13】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(上層ポリイミド膜パターニング工程)である。

【図14】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(金無電解メッキ工程)である。

【図15】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(プローブ検査工程)である。

【図16】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(バンプ形成工程)である。

【図17】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すプロセス・ブロック・フロー図である。

【図18】図17のシード・スパッタ工程の詳細を示す詳細プロセス・ブロック・フロー図である。

【図19】本願の一実施の形態の半導体集積回路装置の製造方法に使用するスパッタ装置の平面レイアウト図である。

【図20】本願の一実施の形態の半導体集積回路装置の製造方法に使用するメッキ装置の平面レイアウト図である。

【図21】本願の一実施の形態の半導体集積回路装置の製造方法に使用する半田印刷装置の平面レイアウト図である。

【図22】本願の一実施の形態の半導体集積回路装置の製造方法に使用する半田ボール搭載装置の平面レイアウト図である。

【図23】図12の構造における下層チタン膜厚と(単一のコンタクトについての)パッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図である。

【図24】図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が10マイクロ・メートル角である場合)である。

【図25】図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が5マイクロ・メートル角である場合)である。

【図26】図16の構造における下層チタン膜厚とパッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図(図23とは相違して、コンタクト数個分、バンプを経由して測定)である。

【符号の説明】

【0080】

1 半導体ウエハまたは半導体基板(集積回路製造工程途中のものも含む)

1a 半導体ウエハ又は半導体チップのデバイス面(上面又は第1の主面)

1b 半導体ウエハ又は半導体チップの裏面(第2の主面)

1c 半導体チップまたはチップ領域

1p パッド下の多層配線層を含む半導体ウエハ又は半導体基板

1s ウエル領域等を含む半導体ウエハまたは半導体基板の単結晶基板部分(p型シリコン単結晶基板)

1w (プリ・メタル層等を含む)パッド下の多層配線層

2 最上層アルミニウム系メタル層

2p アルミニウム系パッド電極

2w アルミニウム系配線

3 無機系ファイナル・パッシベーション膜

3a 下層無機系ファイナル・パッシベーション膜

3b 上層無機系ファイナル・パッシベーション膜

4 下層有機系ファイナル・パッシベーション膜

5 パッド開口

6 最上層層間絶縁膜

7 タングステン・プラグ

8 パッド下地メタル層

8a パッド下地メタル層最下層

8b パッド下地メタル層中間層

8c パッド下地メタル層最上層

9 パッド上部メタル層

10 複合ファイナル・パッシベーション膜

11 酸化アルミニウム層(自然酸化膜)

12 シード・メタル層

12a シード下地メタル最下層(第1のメタル層)

12b シード下地メタル中間層(第2のメタル層)

12c シード下地メタル最上層(第3のメタル層)

12d シード銅層(第4のメタル層)

14 バリア・メタル層

15 レジスト膜パターン

16 再配線メタル膜(再配線メタル・パターン)

16a 再配線メタル膜下層膜

16b 再配線メタル膜上層膜

17 バンプ形成用開口(ランド開口部)

18 保護メタル層(無電解金メッキ膜)

19 プローブ針

20 半田バンプ

21 (再配線の)バンプ形成部

22 上層有機系ファイナル・パッシベーション膜

31 スキージ

32 印刷マスク

33 半田ペースト

34 整列マスク

35 フラックス

36 半田ボール

37 マスク開口

51 スパッタリング装置

52 フープ

53 アルゴン・スパッタ室

54 チタン系メタル・スパッタ室

55 銅スパッタ室

56 バッファ室

57 ロードロック室

58 真空搬送室

59 ロード&アンロード用ロボット

60 真空搬送ロボット

61 半田ペースト印刷装置

62 半田バンプ配列装置

71 メッキ装置

72 電解メッキ・ユニット

73 無電解メッキ・ユニット

74 内部搬送ユニット

75 内部搬送ロボット

76 スピン・リンス&ドライ・ステージ

77 酸処理槽

78 純水洗浄槽

79 プリ・ディップ槽

81 銅電解メッキ槽

82 ニッケル電解メッキ槽

91 金無電解メッキ槽

101 下層ポリイミド層パターニング工程

102 シード層スパッタ成膜工程(下地バリア・メタル・スパッタ工程を含む)

102a デガス処理ステップ

102b アルゴン・スパッタ・ステップ

102c 下層チタン層スパッタ・ステップ

102d 窒化チタン層スパッタ・ステップ

102e 上層チタン層スパッタ・ステップ

102f 銅シード層スパッタ・ステップ

103 レジスト・パターニング工程

104 再配線電解メッキ工程

105 レジスト除去&ウエット・エッチ工程

106 上層ポリイミド層パターニング工程

107 無電解金メッキ工程

108 プローブ検査工程

109 バック・グラインディング工程

110 バンプ形成工程

111 ダイシング工程

112 バリア・メタル・スパッタ工程

C パッド近傍部

【技術分野】

【0001】

本発明は、半導体集積回路装置のデバイス構造および半導体集積回路装置(または半導体装置)の製造方法におけるパッド周辺構造形成技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2008−60145号公報(特許文献1)または、その対応米国特許公開2008−0054479号公報(特許文献2)には、半導体デバイス・チップ上のアルミニウム系のパッドと上層の再配線との間にスパッタ法等によるチタン、窒化チタン、銅等の導電材料を複数積層して形成された下地金属層を設ける技術が開示されている。

【0003】

また、日本特開2000−306938号公報(特許文献3)については、半導体デバイス・チップ上のアルミニウム合金のパッドと上層のアルミニウム合金の再配線との間に、密着性向上目的で、チタン膜、あるいは窒化チタン膜、あるいは、チタン膜と窒化チタン膜との複合膜を形成する技術が開示されている。

【0004】

【特許文献1】特開2008−60145号公報

【特許文献2】米国特許公開2008−0054479号公報

【特許文献3】特開2000−306938号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本願発明者らは、再配線を有するウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗ばらつき(「パッド再配線間抵抗ばらつき」)が、デバイスの動作特性に与える影響について、検討した。それによると、従来製品では、パッド再配線間抵抗ばらつきは、通常の範囲では、ほとんど製品特性に影響しないとされてきた。しかし、最近の動作速度の高速化に伴い、パッド再配線間抵抗ばらつきに起因する不良モードが増加していることが明らかとなった。

【0006】

本願発明は、これらの課題を解決するためになされたものである。

【0007】

本発明の目的は、信頼性の高い半導体集積回路装置を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0010】

すなわち、本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下としたものである。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッドと再配線との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下としたことにより、バリア効果を保持した状態で、抵抗の上昇またはプロセス・コストの上昇を回避することができる。

【発明を実施するための最良の形態】

【0013】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0014】

1.以下を含む半導体集積回路装置:

(a)多層配線層を含む半導体基板のデバイス面上の前記多層配線層上に設けられたアルミニウム系パッド電極;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜;

(c)前記開口を覆うように、前記アルミニウム系パッド電極上および前記絶縁膜上に設けられた再配線メタル・パターン;

(d)前記再配線メタル・パターン下の前記アルミニウム系パッド電極上および前記絶縁膜上に設けられたバリア・メタル層、

ここで、前記バリア・メタル層は、以下を含む:

(d1)チタンを主要な成分とする第1のメタル層;

(d2)前記第1のメタル層上に設けられた窒化チタンを主要な成分とする第2のメタル層;

(d3)前記第2のメタル層上に設けられたチタンを主要な成分とする第3のメタル層、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【0015】

2.前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、50nm以下である。

【0016】

3.前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、25nm以下である。

【0017】

4.前記1から3項のいずれか一つの半導体集積回路装置において、前記再配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【0018】

5.前記1から4項のいずれか一つの半導体集積回路装置において、前記第1のメタル層直下の前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【0019】

6.前記1から5項のいずれか一つの半導体集積回路装置において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【0020】

7.前記1から6項のいずれか一つの半導体集積回路装置において、前記再配線メタル・パターン上には、半田バンプが設けられている。

【0021】

8.前記6項の半導体集積回路装置において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【0022】

9.前記7項の半導体集積回路装置において、前記半田バンプは鉛フリーとされている。

【0023】

10.前記7または9項の半導体集積回路装置において、前記半田バンプは金を含む。

【0024】

11.以下の工程を含む半導体集積回路装置の製造方法:

(a)多層配線層を含む半導体ウエハのデバイス面側の前記多層配線層上に、アルミニウム系パッド電極を形成する工程;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜を形成する工程;

(c)前記ウエハの前記デバイス面側のほぼ全面に、アルミニウム系パッド電極に接続されたシード・メタル膜を、スパッタリングにより成膜する工程;

(d)前記シード・メタル膜上に、レジスト膜パターンを形成する工程;

(e)前記レジスト膜パターンが存在する状態で、前記シード・メタル膜上に、電解メッキにより、再配線メタル・パターンを形成する工程;

(f)前記再配線メタル・パターンをエッチング・マスクとして、前記再配線メタル・パターンがない部分の前記シード・メタル膜を除去する工程、

ここで、前記工程(c)は、以下の下位工程を含む:

(c1)前記半導体ウエハの前記デバイス面側に対して、アルゴン・ガスを主要な成分とする気相中において、プラズマ処理を実行する工程;

(c2)前記工程(c1)の後、チタンを主要な成分とする第1のメタル層をスパッタリングにより成膜する工程;

(c3)前記第1のメタル層上に、窒化チタンを主要な成分とする第2のメタル層をスパッタリングにより成膜する工程;

(c4)前記第2のメタル層上に、チタンを主要な成分とする第3のメタル層をスパッタリングにより成膜する工程;

(c5)前記第3のメタル層上に、前記再配線メタル・パターンに対し、シードとして作用する第4のメタル層をスパッタリングにより成膜する工程、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【0025】

12.前記11項の半導体集積回路装置の製造方法において、前記工程(c)は、同一のスパッタリング装置内において、大気に触れさせることなく実行される。

【0026】

13.前記11または12項の半導体集積回路装置の製造方法において、前記下位工程(c2)から(c4)は、同一のチャンバ内で実行される。

【0027】

14.前記11から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、50nm以下である。

【0028】

15.前記11から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、25nm以下である。

【0029】

16.前記11から15項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【0030】

17.前記11から16項のいずれか一つの半導体集積回路装置の製造方法において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【0031】

18.前記17項の半導体集積回路装置の製造方法において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【0032】

19.前記11から18項のいずれか一つの半導体集積回路装置の製造方法において、前記再配線メタル・パターン上には、半田バンプが設けられている。

【0033】

20.前記11から19項のいずれか一つの半導体集積回路装置の製造方法において、前記下位工程(c2)を開始する時点では、前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【0034】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。

【0036】

具体的には、「金」、「ニッケル」、「銅」、「チタン」、「窒化チタン」、「アルミニウム」等といっても、特にそうでない旨、明示した場合又は理論的にそうでないことが明らかな場合等を除き、「各物質を主要な成分とする部材」を意味するものとする。また、たとえば「アルミニウム・パッド」、「アルミニウム系パッド」といっても、パッド構造の全てが、アルミニウムを主要な成分とする部材でできているのではなく、アルミニウムを主要な成分とする部材による構造要素がパッド構造の主要部を占めることを表す。このことは、アルミニウム系配線、銅系配線等についても同様である。

【0037】

更に、たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0038】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0039】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0040】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコン・ウエハを指すが、エピタキシャル・ウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0041】

6.「配線メタル・パターン」、「再配線メタル・パターン」、「再配線メタル膜」というときは、原則として、下地のシード・メタル層を含まないこととする。また、当該下地のシード・メタル層は、下層のバリア・メタル層、最上層のシード銅層等から構成されている。

【0042】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0043】

1.本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れの説明(主に図1から図18)

以下では、図1から図16(図17および図18を参照)に基づいて、主に半導体集積回路装置のウエハ・プロセスにおけるアルミニウム系パッド2p(図1参照、以下同じ。パッド電極は銅系パッドその他でもよい)形成工程周辺以降を説明する。アルミニウム系パッド層2より下層には、通常、銅系ダマシン多層配線層1wまたはアルミニウム系通常多層配線層1w(一般に3層から10層程度)がある。

【0044】

図1および、そのパッド近傍部Cの詳細である図2に示すように、半導体ウエハ1(チップ領域1c)のデバイス面1a(裏面1bに対向する主面)側のタングステン・プラグ7および最上層層間絶縁膜6上には、アルミニウム系パッド2pが形成されている。ボンディング・パッド2p下の多層配線層1wを含む半導体基板1p(本来の基板部分1sは通常、たとえば300ファイのp型の単結晶シリコン・ウエハである)のデバイス面1a側には、無機系ファイナル・パッシベーション膜3が形成されている。ボンディング・パッド2pを構成するアルミニウム系パッド層2は、この例では最上層配線層2wを兼ねている(パッド専用でもよい)。ボンディング・パッド2pおよびファイナル・パッシベーション膜3の形成については、以下のように形成する。まず、多層配線層上にスパッタリングにより、アルミニウム系メタル膜(通常、中間のアルミニウムを主要な成分とし、銅その他を数パーセント程度添加した1000nm程度の厚さの主配線金属層2pの上下に10nm程度の厚さのチタン膜8a,8c、50から75nm程度の厚さの窒化チタン膜8b,9等の薄膜を有する。チタン膜8a,8cと窒化チタン膜8bでパッド下地メタル層8を構成している)を成膜する。通常のリソグラフィにより、アルミニウム系メタル膜をパターニングし、ボンディング・パッド2pを形成する。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の無機ファイナル・パッシベーション膜3aとなる酸化シリコン系絶縁膜(たとえば厚さ200nm程度)をプラズマCVD法により成膜する。続いて、その上に、たとえば、上層の無機ファイナル・パッシベーション膜3bとなる窒化シリコン系絶縁膜(たとえば厚さ600nm程度)をプラズマCVD法により成膜する。次に、この2層からなる無機ファイナル・パッシベーション膜3に通常のリソグラフィにより、パッド開口5を形成する(この後、一般に主配線金属層上の窒化チタン膜9等が、たとえばアルゴン、塩素等の混合ガス雰囲気中で自己整合的にドライ・エッチング除去される。これで、図2のような断面形態となる)。次に、半導体ウエハ1のデバイス面1a側のほぼ全面に、たとえば、下層の有機ファイナル・パッシベーション膜4となるポリイミド膜(たとえば厚さ4マイクロ・メートル程度)を塗布する。続いて、先とほぼ同じ開口位置に再び通常のリソグラフィにより、パッド開口5を形成する(図17の下層ポリイミド層パターニング工程101)。従って、この段階の複合ファイナル・パッシベーション膜10(絶縁膜)は、下層から酸化シリコン膜3a、窒化シリコン膜3b、およびポリイミド膜4の三層重ね膜となる。なお、後ほど説明するが、通常、この上に更に、有機系の絶縁膜がもう一つのファイナル・パッシベーション膜として形成される。

【0045】

ここで、アルミニウム系パッド電極2pのアルミニウム系メタル表面(アルミニウムを主要な成分とする面が露出しているパッド上面)は非常に酸化されやすいので、下層有機系ファイナル・パッシベーション膜4をパターニングして、次の工程に仕掛かる段階でみると、図3に示すように、数nm程度の自然酸化膜11(酸化アルミニウム膜)が存在する。このままでは、パッド・再配線間抵抗ばらつきが増大する可能性があるので、図3の状態で、ウエハ1のデバイス面1aに対して、アルゴン・スパッタリング等のプラズマ・エッチング処理(スパッタリング・エッチ)を実行して(処理条件は、たとえば、室温、アルゴン雰囲気、0.05Pa程度の気圧、処理時間30秒程度)、図4に示すように、酸化アルミニウム膜11を除去または3nm程度以下に薄膜化することが有効である(図18のアルゴン・スパッタ工程102b)。ここでのプラズマ・エッチング処理(アルゴン・スパッタ工程102b)は、酸化アルミニウム膜11を完全に除去する必要はなく、全体に薄膜化すればよい。これは、薄膜の酸化アルミニウム膜11は、アルミニウム表面を保護する効果もあり、また、完全に除去しても、再度、生成するので、実質的な効果が期待できない。また、過剰に、プラズマ・エッチング処理を行うと、下層有機系ファイナル・パッシベーション膜4(ポリイミド膜)からの生成物の影響で、かえってデバイス特性が劣化する恐れがある。なお、良品の製品段階でも薄膜の酸化アルミニウム膜11が残存していることは、顕微鏡的に確認されている。

【0046】

次に、図5に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード・メタル層12をスパッタリングにより成膜する(図17および図18のシード層スパッタ工程102)。このシード層スパッタ工程102の詳細を図6から図9および図18に基づいて説明する。

【0047】

まず、図6に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル最下層12a(第1のメタル層)として、チタンを主要な成分とするメタル膜(比較的純粋なチタン膜が好適なものとして例示できる)をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン雰囲気、0.5Pa程度の気圧、処理時間8秒程度)により成膜する(図18の下層チタン・スパッタ工程102c)。この膜は、パッド表面の酸化アルミニウム膜を還元する作用がある。

【0048】

次に、図7に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル中間層12b(第2のメタル層)として、窒化チタンを主要な成分とするメタル膜を窒素ガス雰囲気中でのスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン+窒素ガス雰囲気、0.5Pa程度の気圧、処理時間30秒程度)により成膜する(図18の窒化チタン・スパッタ工程102d)。この膜は、窒素を多く含み、銅等に対する拡散バリア性が高い。チタン膜等に比べて厚さの割りにバリア性が高いので、窒化チタン膜を用いることにより、バリア・メタル膜全体を薄くするメリットがある。ただし、単独では電気抵抗が高く、上層との接着性にも若干問題がある。

【0049】

続いて、図8に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード下地メタル最上層12c(第3のメタル層)として、チタンを主要な成分とするメタル膜をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度摂氏300度程度、アルゴン雰囲気、0.5Pa程度の気圧、処理時間8秒程度)により成膜する(図18の上層チタン・スパッタ工程102e)。この膜は、上層との接着性向上のためであり、比較的純粋なものである必要はない。

【0050】

これらのシード下地メタル最下層12a、シード下地メタル中間層12b、およびシード下地メタル最上層12cでバリア・メタル層14(図8)を構成している。また、下層チタン・スパッタ工程102cから上層チタン・スパッタ工程102eでバリア・メタル・スパッタ工程112を構成している。なお、シード下地メタル最下層12aおよびシード下地メタル最上層12cの膜厚目標値は、たとえば10nm程度であり、実用的な範囲は、5nmから60nm程度である。また、シード下地メタル中間層12bの膜厚目標値は、たとえば50nm程度であり、実用的な範囲は、30nmから100nm程度である。

【0051】

更に、図9に示すように、ウエハ1のデバイス面1aのほぼ全面に、シード銅層12d(第4のメタル層)として、銅を主要な成分とするメタル膜をスパッタリング(処理条件は、たとえば、ウエハ・ステージ設定温度は室温、アルゴン雰囲気、0.05Pa程度の気圧、処理時間15秒程度)により成膜する。シード銅層12dの膜厚目標値は、たとえば150nm程度であり、実用的な範囲は、100nmから200nm程度である。これらのバリア・メタル層14およびシード銅層12dでシード・メタル層12を構成している。

【0052】

次に、図10に示すように、シード・メタル層12上に通常のリソグラフィにより、レジスト膜パターン15を形成する(図17のレジスト・パターニング工程)。続いて、図11に示すように、電解メッキにより、銅を主要な成分とする再配線メタル膜下層膜16a(膜厚目標値は、たとえば5.7マイクロ・メートル程度であり、実用的な範囲は、4マイクロ・メートルから10マイクロ・メートル程度である。)を選択的に形成する。次に、再配線メタル膜下層膜16a上に、電解メッキにより、ニッケルを主要な成分とする再配線メタル膜上層膜16b(膜厚目標値は、たとえば2.7マイクロ・メートル程度であり、実用的な範囲は、2マイクロ・メートルから4マイクロ・メートル程度である。)を選択的に形成する(図17の再配線電解メッキ工程104)。再配線メタル膜下層膜16a、再配線メタル膜上層膜16b等で再配線メタル膜(再配線メタル・パターン、配線メタル・パターン)16を構成する。

【0053】

次に、図12に示すように、不要なレジスト膜パターン15を除去するとともに、再配線メタル・パターン16外部の。次に、図13にシード・メタル層12をウエット・エッチングにより自己整合的に除去する(図17のレジスト除去&ウエット・エッチング工程105)。

【0054】

次に、図13に示すように、ウエハ1のデバイス面1a側に、通常のリソグラフィにより、上層有機系ファイナル・パッシベーション膜22として、バンプ形成用開口17(ランド開口部の径は、たとえば90から200マイクロ・メートル)を有するポリイミド膜パターン(たとえば厚さ6マイクロ・メートル程度)を形成する(図17の上層ポリイミド層パターニング工程106)。

【0055】

更に、図14に示すように、バンプ形成用開口17内のバンプ形成部21の表面に無電解メッキにより、金を主要な成分とする保護メタル層18を形成する(図17の無電解金メッキ工程)。

【0056】

次に、図15に示すように、保護メタル層18にプローブ針19を接触させることにより、プローブ検査を実行する(図17のプローブ検査工程)。次に、図16に示すように、半田ペースト印刷法、ボール配列法等および半田リフロー処理により、バンプ形成部21のニッケル表面上に半田バンプ20を形成する。このとき、保護メタル層18の金はバンプ内に拡散するので、半田リフロー処理の結果として、最終的に保護メタル層18は消失する。

【0057】

なお、図17のプローブ検査工程108およびBG工程109は、バンプ形成工程110の後に実施してもよい。

【0058】

2.本願の一実施の形態の半導体集積回路装置の製造方法に使用する製造装置等の説明(主に図19から図22、図17および図18を参照)

このセクションでは、セクション1に説明したプロセスの一部について各製造装置プロセスの面から説明する。まず、図17および図18のシード層スパッタ成膜工程102について説明する。なお、半田リフロー処理以降のプロセスについても、便宜上このセクションで説明する。

【0059】

図17の下層ポリイミド層パターニング工程101に引き続き、図19に示すように、先ず、フープ52内に収容されたウエハ1は、ロード&アンロード用ロボット59によって、マルチ・チャンバ型のスパッタリング装置51(スパッタリング及び、それに関連する処理を連続的に実行する装置)のバッファ室56内に導入される。その後、ロード&アンロード用ロボット59によって、ロードロック室57を通して、真空搬送室58内に導入され、真空搬送ロボット60によって、アルゴン・スパッタ室53に導入される。そこで、まず、ウエハ1の表面に吸着されたガスを放出させるためのデガス処理102a(図18)が実施される(処理条件は、たとえば、ウエハ・ステージ設定温度は摂氏250度程度、添加ガスがない空引き状態、1KPa程度の気圧、規定圧力到達より処理時間30秒程度)。続いて、そのまま、アルゴン・スパッタ処理102bが実行される。

【0060】

次に、ウエハ1は、真空搬送ロボット60によって、チタン系メタル・スパッタ室54に移送される。そこで、バリア・メタル・スパッタ工程112が連続的に実行される。すなわち、順に下層チタン層スパッタ・ステップ102c、窒化チタン層スパッタ・ステップ102d、および上層チタン層スパッタ・ステップ102eである。

【0061】

次に、ウエハ1は、真空搬送ロボット60によって、銅スパッタ室55に移送される。そこで、銅シード層スパッタ・ステップ102fが実行される。ここで、ウエハ1は、最初にロードロック室57に導入され、各処理チャンバ53,54,55の処理が終わって、再びロードロック室57に戻るまで(ロードロック室が複数あるので同一とは限らない)の間、大気にさらされることがない。

【0062】

その後、ウエハ1は、真空搬送ロボット60によって、ロードロック室57に移送され、そこからロード&アンロード用ロボット59によって、フープ52内に戻され、次のレジスト・パターニング工程103(図17)のための処理セクションに移送される。そこで、レジスト膜パターン15が形成されたウエハ1は、再びフープ52に戻されて、メッキ装置71(メッキ関連処理装置)に移送される。メッキ装置71においては、以下のように処理される。

【0063】

図20に示すように、先ず、ウエハ1は、フープ52内から、ロード&アンロード用ロボット59によって、バッファ室56内に導入される。そこから内部搬送ユニット74の内部搬送ロボット75により、電解メッキ・ユニット72内のプリ・ディップ槽79に移送され、そこで濡れ性向上、有機成分除去等のために燐酸系の処理液により前処理(液温は室温、処理時間は200秒程度)が実施される。次に、ウエハ1は、内部搬送ロボット75により、水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次に、ウエハ1は、内部搬送ロボット75により、銅電解メッキ槽81に移送され、そこで再配線電解メッキ工程104(図17)の第1ステップである銅電解メッキ処理が、たとえば硫酸系銅メッキ液を用いて行われる(液温は室温、処理時間は460秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次に、ウエハ1は、内部搬送ロボット75により、酸処理槽77に移送され、そこで表面金属酸化物除去等のために硫酸系の処理液により前処理が実施される(液温は室温、処理時間は80秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1は、内部搬送ロボット75により、ニッケル電解メッキ槽82に移送され、そこで、再配線電解メッキ工程104(図17)の第2ステップであるニッケル電解メッキ処理が、たとえばホウ酸系ニッケル・メッキ液を用いて行われる(液温は摂氏55度程度、処理時間は450秒程度)。次にウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は50秒程度)。更に、ウエハ1は、内部搬送ロボット75により、スピン・リンス&ドライ・ステージ76に移送され、そこのスピンステージ上でリンス及びスピン乾燥が実施される(液温は室温、処理時間は90秒程度)。その後、ウエハ1は内部搬送ロボット75およびロード&アンロード用ロボット59によって、フープ52に戻される。次に、フープ52はレジスト除去&ウエット・エッチ工程105(図17)のためのユニットに移送される。

【0064】

上層ポリイミド層パターニング工程106(図17)が完了すると、ウエハ1は再び、フープ52内に収容されて、メッキ装置71に移送される。先と同様に、ウエハ1は、フープ52内から、ロード&アンロード用ロボット59によって、バッファ室56内に導入される。そこから内部搬送ユニット74の内部搬送ロボット75により、電解メッキ・ユニット72内のプリ・ディップ槽79に移送され、そこで濡れ性向上、有機成分除去等のために有機塩酸系の処理液により前処理が実施される。次にウエハ1、内部搬送ロボット75により、水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1、内部搬送ロボット75により、酸処理槽77に移送され、そこで表面金属酸化物除去、表面活性化等のために塩酸系の処理液により前処理が実施される(液温は室温、処理時間は80秒程度)。次に、ウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、水洗される(液温は室温、処理時間は30秒程度)。次にウエハ1、内部搬送ロボット75により、無電解メッキ槽91に移送され、そこで無電解金メッキ工程107(図17)が、たとえば亜硫酸金メッキ液を用いて実行される(液温は摂氏55度程度、処理時間は450秒程度)。次にウエハ1は、内部搬送ロボット75により、再び水洗槽78に移送され、そこで、水洗される(液温は室温、処理時間は100秒程度)。更に、ウエハ1は、内部搬送ロボット75により、スピン・リンス&ドライ・ステージ76に移送され、そこのスピンステージ上でリンス及びスピン乾燥が実施される(液温は室温、処理時間は90秒程度)。その後、ウエハ1は内部搬送ロボット75およびロード&アンロード用ロボット59によって、フープ52に戻される。次に、フープ52はレジスト除去&ウエット・エッチ工程105(図17)のためのユニットに移送される。

【0065】

その後、ウエハ1を収容したフープ52は、順次、プローブ検査工程108(図17)およびバック・グラインディング工程109(図17)のためのそれぞれのユニットに送られえて、各処理を終えた後、バンプ形成工程110(図17)のため、半田ペースト印刷装置61(図21)または半田バンプ配列装置62(図22)へ搬送される。半田ペースト印刷装置61は、一般品に適しており、半田バンプ配列装置62は、バンプ・ピッチが100マイクロ・メートル程度以下の狭ピッチ品に適している。

【0066】

先ず、半田ペースト印刷装置61を使用したバンプ形成プロセス110(図17)について説明する。図21に示すように、ウエハ1上の複数のバンプ形成部21と印刷マスク32のマスク開口37が一致するように、ウエハ1上に印刷マスク32を重ねた状態で、スキージ(Squeegee)を水平移動させることにより、半田ペースト33が各マスク開口37を満たすようにする。その後、印刷マスク32を剥がすと、半田ペースト33がバンプ形成部21上に印刷された状態となる。これにリフロー処理をすると、半田が自立的に図16のような形状となる。

【0067】

次に、半田バンプ配列装置62を使用したバンプ形成プロセス110(図17)について説明する。図22に示すように、先ず、ウエハ1上の複数のバンプ形成部21にフラックス35を印刷しておく。その状態で、整列マスク34の各マスク開口37が複数のバンプ形成部21と一致するように、ウエハ1上に整列マスク32を一定の間隔を置いて重ねた状態で、上方から整形した半田ボール36を供給する。半田ボール36は、各マスク開口37内に一個ずつ入り、フラックス35と仮接着される。その後、整列マスク32を除去して、先と同様に、リフロー処理をすると、半田が自立的に図16のような形状となる。

【0068】

これらのバンプ形成プロセス110(図17)が完了した後、ウエハ1を個々のチップ1cに分割するダイシング工程111(図17)を実行する。

【0069】

3.各種データの説明(主に図23から図26)

このセクションでは、前2セクションで説明した本願発明の実施の形態についての各種検証データ、参考データ等について説明する。

【0070】

図23は、図12の構造における下層チタン膜厚と(単一のコンタクトについての)パッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図である。この図において、四角形のデータは、通常の10マイクロメータ角のパッド開口について測定したもので、円形のデータは、試験用に5マイクロメータ角のパッド開口について測定したものである。後者のほうが、より抵抗ばらつきに敏感になる傾向がある。

【0071】

図23に示されたように、シード下地メタル最下層(第1のメタル層)すなわち、下層チタン膜の膜厚が3nm程度では、パッド再配線間抵抗値は下層チタン膜がないのと同等である。一方、下層チタン膜の膜厚が5nm程度以上では、パッド再配線間抵抗値は安定的に低い値となる。従って、プロセスばらつきを考慮すると、下層チタン膜の膜厚の下限値は、5nm程度が好適である。

【0072】

図24は図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が10マイクロ・メートル角である場合)である。また、図25は図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が5マイクロ・メートル角である場合)である。これらから、パッド再配線間抵抗値の分布についても、下層チタン膜の膜厚が5nm程度以上では、ばらつきが小さいことがわかる。

【0073】

次に、下層チタン膜の膜厚の適正な上限について検討する。図26は図16の構造における下層チタン膜厚とパッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図(図23とは相違して、コンタクト数個分、バンプを経由して測定)である。このデータは、数個分の直列接続およびバンプその他の抵抗を含むため絶対値は高くなっているが、相対的な変化を見る上で有用である。

【0074】

図26に示されたように、下層チタン膜の膜厚が25nm程度以上で顕著な抵抗値の上昇が見られ、実用上、およびプロセス・コストを考慮すると60nm程度までが現実的な範囲と考えられる。したがって、下層チタン膜の膜厚の適正な上限は、60nm程度と見られる。

【0075】

図23及び図26等から、下層チタン膜の実用的な膜厚範囲は、5nm以上、60nm以下である。また、量産性を考慮した適正な範囲は、5nm以上、50nm以下である。更に、低抵抗性等も考慮した最も好適な範囲は、5nm以上、25nm以下である。

【0076】

4.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0077】

例えば、前記実施の形態では、下層の銅再配線層および上層のニッケル再配線層からなる2層構成の再配線について、具体的に説明したが、本発明はそれに限定されるものではなく、銅単独再配線層構造、その他多層の再配線構造にも適用できることは言うまでもない。また、半導体基板として、p型単結晶シリコン基板を用いた例について、具体的に説明したが、本発明はそれに限定されるものではなく、n型単結晶シリコン基板等のその他の単結晶半導体基板,SOI基板、ガラス基板等の絶縁性基板、GaAsその他の化合物半導体基板等を用いたものにも適用できることは言うまでもない。

【0078】

また、前記実施の形態では、有機系ファイナル・パッシベーション膜として、ポリイミド系の樹脂膜を使用する例を示したが、本発明はそれに限定されるものではなく、BCB(Benzo−Cyclo−Butene)その他の耐熱性ポリマー系の樹脂膜を用いたものでもよいことは、言うまでもない。

【図面の簡単な説明】

【0079】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(下層ポリイミド層パターニング工程)である。

【図2】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(下層ポリイミド層パターニング工程)である。

【図3】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(工程間における自然酸化膜の形成の様子を示す)である。

【図4】図1のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(アルゴン・スパッタ・ステップ)である。

【図5】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(シード・メタル層スパッタ工程)である。

【図6】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(下層チタン層スパッタ・ステップ)である。

【図7】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(窒化チタン層スパッタ・ステップ)である。

【図8】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(上層チタン層スパッタ・ステップ)である。

【図9】図5のパッド近傍部Cの詳細プロセスを示すデバイス拡大断面フロー図(銅シード層スパッタ・ステップ)である。

【図10】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(レジスト膜パターニング工程)である。

【図11】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(再配線メタル電解メッキ工程)である。

【図12】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(レジスト膜除去工程)である。

【図13】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(上層ポリイミド膜パターニング工程)である。

【図14】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(金無電解メッキ工程)である。

【図15】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(プローブ検査工程)である。

【図16】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すデバイス断面フロー図(バンプ形成工程)である。

【図17】本願の一実施の形態の半導体集積回路装置の製造方法におけるアルミニウム系パッド後のプロセスの流れを示すプロセス・ブロック・フロー図である。

【図18】図17のシード・スパッタ工程の詳細を示す詳細プロセス・ブロック・フロー図である。

【図19】本願の一実施の形態の半導体集積回路装置の製造方法に使用するスパッタ装置の平面レイアウト図である。

【図20】本願の一実施の形態の半導体集積回路装置の製造方法に使用するメッキ装置の平面レイアウト図である。

【図21】本願の一実施の形態の半導体集積回路装置の製造方法に使用する半田印刷装置の平面レイアウト図である。

【図22】本願の一実施の形態の半導体集積回路装置の製造方法に使用する半田ボール搭載装置の平面レイアウト図である。

【図23】図12の構造における下層チタン膜厚と(単一のコンタクトについての)パッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図である。

【図24】図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が10マイクロ・メートル角である場合)である。

【図25】図12の構造における再配線間抵抗の分布を示すデータ・プロット図(パッド開口が5マイクロ・メートル角である場合)である。

【図26】図16の構造における下層チタン膜厚とパッド・再配線間抵抗(単一のコンタクトについての)の関係を示すデータ・プロット図(図23とは相違して、コンタクト数個分、バンプを経由して測定)である。

【符号の説明】

【0080】

1 半導体ウエハまたは半導体基板(集積回路製造工程途中のものも含む)

1a 半導体ウエハ又は半導体チップのデバイス面(上面又は第1の主面)

1b 半導体ウエハ又は半導体チップの裏面(第2の主面)

1c 半導体チップまたはチップ領域

1p パッド下の多層配線層を含む半導体ウエハ又は半導体基板

1s ウエル領域等を含む半導体ウエハまたは半導体基板の単結晶基板部分(p型シリコン単結晶基板)

1w (プリ・メタル層等を含む)パッド下の多層配線層

2 最上層アルミニウム系メタル層

2p アルミニウム系パッド電極

2w アルミニウム系配線

3 無機系ファイナル・パッシベーション膜

3a 下層無機系ファイナル・パッシベーション膜

3b 上層無機系ファイナル・パッシベーション膜

4 下層有機系ファイナル・パッシベーション膜

5 パッド開口

6 最上層層間絶縁膜

7 タングステン・プラグ

8 パッド下地メタル層

8a パッド下地メタル層最下層

8b パッド下地メタル層中間層

8c パッド下地メタル層最上層

9 パッド上部メタル層

10 複合ファイナル・パッシベーション膜

11 酸化アルミニウム層(自然酸化膜)

12 シード・メタル層

12a シード下地メタル最下層(第1のメタル層)

12b シード下地メタル中間層(第2のメタル層)

12c シード下地メタル最上層(第3のメタル層)

12d シード銅層(第4のメタル層)

14 バリア・メタル層

15 レジスト膜パターン

16 再配線メタル膜(再配線メタル・パターン)

16a 再配線メタル膜下層膜

16b 再配線メタル膜上層膜

17 バンプ形成用開口(ランド開口部)

18 保護メタル層(無電解金メッキ膜)

19 プローブ針

20 半田バンプ

21 (再配線の)バンプ形成部

22 上層有機系ファイナル・パッシベーション膜

31 スキージ

32 印刷マスク

33 半田ペースト

34 整列マスク

35 フラックス

36 半田ボール

37 マスク開口

51 スパッタリング装置

52 フープ

53 アルゴン・スパッタ室

54 チタン系メタル・スパッタ室

55 銅スパッタ室

56 バッファ室

57 ロードロック室

58 真空搬送室

59 ロード&アンロード用ロボット

60 真空搬送ロボット

61 半田ペースト印刷装置

62 半田バンプ配列装置

71 メッキ装置

72 電解メッキ・ユニット

73 無電解メッキ・ユニット

74 内部搬送ユニット

75 内部搬送ロボット

76 スピン・リンス&ドライ・ステージ

77 酸処理槽

78 純水洗浄槽

79 プリ・ディップ槽

81 銅電解メッキ槽

82 ニッケル電解メッキ槽

91 金無電解メッキ槽

101 下層ポリイミド層パターニング工程

102 シード層スパッタ成膜工程(下地バリア・メタル・スパッタ工程を含む)

102a デガス処理ステップ

102b アルゴン・スパッタ・ステップ

102c 下層チタン層スパッタ・ステップ

102d 窒化チタン層スパッタ・ステップ

102e 上層チタン層スパッタ・ステップ

102f 銅シード層スパッタ・ステップ

103 レジスト・パターニング工程

104 再配線電解メッキ工程

105 レジスト除去&ウエット・エッチ工程

106 上層ポリイミド層パターニング工程

107 無電解金メッキ工程

108 プローブ検査工程

109 バック・グラインディング工程

110 バンプ形成工程

111 ダイシング工程

112 バリア・メタル・スパッタ工程

C パッド近傍部

【特許請求の範囲】

【請求項1】

以下を含む半導体集積回路装置:

(a)多層配線層を含む半導体基板のデバイス面上の前記多層配線層上に設けられたアルミニウム系パッド電極;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜;

(c)前記開口を覆うように、前記アルミニウム系パッド電極上および前記絶縁膜上に設けられた配線メタル・パターン;

(d)前記配線メタル・パターン下の前記アルミニウム系パッド電極上および前記絶縁膜上に設けられたバリア・メタル層、

ここで、前記バリア・メタル層は、以下を含む:

(d1)チタンを主要な成分とする第1のメタル層;

(d2)前記第1のメタル層上に設けられた窒化チタンを主要な成分とする第2のメタル層;

(d3)前記第2のメタル層上に設けられたチタンを主要な成分とする第3のメタル層、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【請求項2】

前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、50nm以下である。

【請求項3】

前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、25nm以下である。

【請求項4】

前記1項の半導体集積回路装置において、前記配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【請求項5】

前記1項の半導体集積回路装置において、前記第1のメタル層直下の前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【請求項6】

前記1項の半導体集積回路装置において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【請求項7】

前記1項の半導体集積回路装置において、前記配線メタル・パターン上には、半田バンプが設けられている。

【請求項8】

前記6項の半導体集積回路装置において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【請求項9】

前記7項の半導体集積回路装置において、前記半田バンプは鉛フリーとされている。

【請求項10】

前記9項の半導体集積回路装置において、前記半田バンプは金を含む。

【請求項11】

以下の工程を含む半導体集積回路装置の製造方法:

(a)多層配線層を含む半導体ウエハのデバイス面側の前記多層配線層上に、アルミニウム系パッド電極を形成する工程;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜を形成する工程;

(c)前記ウエハの前記デバイス面側のほぼ全面に、アルミニウム系パッド電極に接続されたシード・メタル膜を、スパッタリングにより成膜する工程;

(d)前記シード・メタル膜上に、レジスト膜パターンを形成する工程;

(e)前記レジスト膜パターンが存在する状態で、前記シード・メタル膜上に、電解メッキにより、配線メタル・パターンを形成する工程;

(f)前記配線メタル・パターンをエッチング・マスクとして、前記配線メタル・パターンがない部分の前記シード・メタル膜を除去する工程、

ここで、前記工程(c)は、以下の下位工程を含む:

(c1)前記半導体ウエハの前記デバイス面側に対して、アルゴン・ガスを主要な成分とする気相中において、プラズマ処理を実行する工程;

(c2)前記工程(c1)の後、チタンを主要な成分とする第1のメタル層をスパッタリングにより成膜する工程;

(c3)前記第1のメタル層上に、窒化チタンを主要な成分とする第2のメタル層をスパッタリングにより成膜する工程;

(c4)前記第2のメタル層上に、チタンを主要な成分とする第3のメタル層をスパッタリングにより成膜する工程;

(c5)前記第3のメタル層上に、前記配線メタル・パターンに対し、シードとして作用する第4のメタル層をスパッタリングにより成膜する工程、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記工程(c)は、同一のスパッタリング装置内において、大気に触れさせることなく実行される。

【請求項13】

前記12項の半導体集積回路装置の製造方法において、前記下位工程(c2)から(c4)は、同一のチャンバ内で実行される。

【請求項14】

前記11項の半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、50nm以下である。

【請求項15】

前記11項の半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、25nm以下である。

【請求項16】

前記11項の半導体集積回路装置の製造方法において、前記配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【請求項17】

前記11項の半導体集積回路装置の製造方法において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【請求項18】

前記17項の半導体集積回路装置の製造方法において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【請求項19】

前記11項の半導体集積回路装置の製造方法において、前記配線メタル・パターン上には、半田バンプが設けられている。

【請求項20】

前記11項の半導体集積回路装置の製造方法において、前記下位工程(c2)を開始する時点では、前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【請求項1】

以下を含む半導体集積回路装置:

(a)多層配線層を含む半導体基板のデバイス面上の前記多層配線層上に設けられたアルミニウム系パッド電極;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜;

(c)前記開口を覆うように、前記アルミニウム系パッド電極上および前記絶縁膜上に設けられた配線メタル・パターン;

(d)前記配線メタル・パターン下の前記アルミニウム系パッド電極上および前記絶縁膜上に設けられたバリア・メタル層、

ここで、前記バリア・メタル層は、以下を含む:

(d1)チタンを主要な成分とする第1のメタル層;

(d2)前記第1のメタル層上に設けられた窒化チタンを主要な成分とする第2のメタル層;

(d3)前記第2のメタル層上に設けられたチタンを主要な成分とする第3のメタル層、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【請求項2】

前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、50nm以下である。

【請求項3】

前記1項の半導体集積回路装置において、前記第1のメタル層の厚さは、25nm以下である。

【請求項4】

前記1項の半導体集積回路装置において、前記配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【請求項5】

前記1項の半導体集積回路装置において、前記第1のメタル層直下の前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【請求項6】

前記1項の半導体集積回路装置において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【請求項7】

前記1項の半導体集積回路装置において、前記配線メタル・パターン上には、半田バンプが設けられている。

【請求項8】

前記6項の半導体集積回路装置において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【請求項9】

前記7項の半導体集積回路装置において、前記半田バンプは鉛フリーとされている。

【請求項10】

前記9項の半導体集積回路装置において、前記半田バンプは金を含む。

【請求項11】

以下の工程を含む半導体集積回路装置の製造方法:

(a)多層配線層を含む半導体ウエハのデバイス面側の前記多層配線層上に、アルミニウム系パッド電極を形成する工程;

(b)前記アルミニウム系パッド電極の少なくとも一部の上に開口を有する絶縁膜を形成する工程;

(c)前記ウエハの前記デバイス面側のほぼ全面に、アルミニウム系パッド電極に接続されたシード・メタル膜を、スパッタリングにより成膜する工程;

(d)前記シード・メタル膜上に、レジスト膜パターンを形成する工程;

(e)前記レジスト膜パターンが存在する状態で、前記シード・メタル膜上に、電解メッキにより、配線メタル・パターンを形成する工程;

(f)前記配線メタル・パターンをエッチング・マスクとして、前記配線メタル・パターンがない部分の前記シード・メタル膜を除去する工程、

ここで、前記工程(c)は、以下の下位工程を含む:

(c1)前記半導体ウエハの前記デバイス面側に対して、アルゴン・ガスを主要な成分とする気相中において、プラズマ処理を実行する工程;

(c2)前記工程(c1)の後、チタンを主要な成分とする第1のメタル層をスパッタリングにより成膜する工程;

(c3)前記第1のメタル層上に、窒化チタンを主要な成分とする第2のメタル層をスパッタリングにより成膜する工程;

(c4)前記第2のメタル層上に、チタンを主要な成分とする第3のメタル層をスパッタリングにより成膜する工程;

(c5)前記第3のメタル層上に、前記配線メタル・パターンに対し、シードとして作用する第4のメタル層をスパッタリングにより成膜する工程、

ここで、前記第1のメタル層の厚さは、5nm以上、60nm以下である。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記工程(c)は、同一のスパッタリング装置内において、大気に触れさせることなく実行される。

【請求項13】

前記12項の半導体集積回路装置の製造方法において、前記下位工程(c2)から(c4)は、同一のチャンバ内で実行される。

【請求項14】

前記11項の半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、50nm以下である。

【請求項15】

前記11項の半導体集積回路装置の製造方法において、前記第1のメタル層の厚さは、25nm以下である。

【請求項16】

前記11項の半導体集積回路装置の製造方法において、前記配線メタル・パターンは、以下を含む:

(c1)銅を主要な成分とする第1のメッキ層;

(c2)前記第1のメッキ層上に設けられたニッケルを主要な成分とする第2のメッキ層。

【請求項17】

前記11項の半導体集積回路装置の製造方法において、前記絶縁膜は、以下を含む:

(b1)無機系の第1のパッシベーション膜;

(b2)前記第1のパッシベーション膜に設けられ有機系の第2のパッシベーション膜。

【請求項18】

前記17項の半導体集積回路装置の製造方法において、前記第2のパッシベーション膜は、ポリイミド系の樹脂膜である。

【請求項19】

前記11項の半導体集積回路装置の製造方法において、前記配線メタル・パターン上には、半田バンプが設けられている。

【請求項20】

前記11項の半導体集積回路装置の製造方法において、前記下位工程(c2)を開始する時点では、前記前記アルミニウム系パッド電極上には、酸化アルミニウムを主要な成分とする層が存在する。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2010−147267(P2010−147267A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−323343(P2008−323343)

【出願日】平成20年12月19日(2008.12.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月19日(2008.12.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

[ Back to top ]