半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、主にMISFET(Metal Insulator Semiconductor Field Effect Transistor)またはMOSFET(Metal Oxide Semiconductor Field Effect Transistor)を集積した半導体集積回路装置および半導体集積回路装置(または半導体装置)の製造方法における絶縁膜形成技術、特にプリ・メタル(Pre−Metal)層間絶縁膜形成技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開平5−21620号公報(特許文献1)には、プリ・メタル層間絶縁膜形成技術として、TEOS(Tetra−Ethyl−Ortho−Silicate)を用いたTEOS−CVD(Chemical Vapor Deposition)シリコン酸化膜の上にSOG(Spin−On−Glass)シリコン酸化膜を塗布して平坦化し、これらをドライ・エッチングによりエッチ・バックする技術が開示されている。

【0003】

日本特開平5−206474号公報(特許文献2)には、TEOSを用いたTEOS−CVDシリコン酸化膜をリフローして平坦化した後、エッチ・バックする技術が開示されている。

【0004】

日本特開2002−110666号公報(特許文献3)には、HDP(High Density Plasma)によるCVDシリコン酸化膜の上にP−TEOS(Plasma−TEOS)によるCVDシリコン酸化膜を形成し、このP−TEOSによるCVDシリコン酸化膜をCMP(Chemical Mechanical Polishing)またはエッチ・バックして平坦化した後、キャップ膜としてP−TEOSによるCVDシリコン酸化膜を形成する技術が開示されている。

【0005】

日本特開特開2000−208624号公報(特許文献4)には、プリ・メタル層間絶縁膜の形成技術として、O3−TEOSを用いたプラズマCVD法により酸化シリコン膜を形成し、その後、CMP法により前記酸化シリコン膜をゲート電極の導電層が露出するまで研磨し、更にその上に、PH3−SiH4−O2を用いたCVD法により酸化シリコン膜を形成する技術が開示されている。

【0006】

日本特開平7−147281号公報(特許文献5)および日本特開平3−194932号公報(特許文献6)には、配線間をO3−TEOSを用いたCVDにより酸化シリコン膜を形成し、その後エッチバック又はCMPにより前記配線の上部を露出するまで前記酸化シリコン膜を除去し、更にその上に、TEOSを用いたプラズマCVDによる酸化シリコン膜を形成する技術が開示されている。

【0007】

日本特開平7−221179号公報(特許文献7)には、配線間をO3−TEOS NSGシリコン膜(堆積時点でin−situリフローを生じている)で埋め込んだ後、プラズマCVDによるシリコン酸化膜を形成し、その後、CMPにより平坦化する技術が開示されている。

【0008】

【特許文献1】特開平5−21620号公報

【特許文献2】特開平5−206474号公報

【特許文献3】特開2002−110666号公報

【特許文献4】特開2000−208624号公報

【特許文献5】特開平7−147281号公報

【特許文献6】特開平3−194932号公報

【特許文献7】特開平7−221179号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

半導体集積回路装置のプリ・メタル層間絶縁膜の構成法としては、たとえばオゾンTEOSによる酸化シリコン膜(以下、混乱のない場合「オゾンTEOS膜」または「O3−TEOS膜」と略称する)等の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜(以下、混乱のない場合「プラズマTEOS膜」または「P−TEOS膜」と略称する)等を積層し、更にCMPで平坦化することが考えられる。また、オゾンTEOSによる酸化シリコン膜およびプラズマTEOSによる酸化シリコン膜等の代わりに、埋め込み特性の良好なHDPによるCVDシリコン酸化膜の適用も考えられる。

【0010】

しかし、本願発明者等が検討したところによると、前者においては、コンタクト・ホール形成プロセスにおいて、キャップ絶縁膜によって、一旦、塞がれたプリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。このクラックの原因は、ゲート構造上部でプラズマTEOS膜が薄くなると、比較的軟らかい下地のオゾンTEOS膜上のプラズマTEOS膜にCMPによる応力が集中するためである。これは、オゾンTEOS膜の成膜温度の低温化に伴い顕著になる問題であることが、本願発明者等によって明らかになった。

【0011】

一方、後者については、膜内のストレスによるトランジスタ特性への悪影響が懸念されるほか、成膜初期にシリコン・リッチな難エッチング性の膜を生成するという問題もある。

【0012】

なお、特許文献1、5,6には、TEOS−CVD膜の低温化に起因した膜強度の低下について考慮されておらず、特許文献2,7においても、TEOS−CVD膜はリフロー処理が成されているため、低温化に起因した膜強度の低下について考慮されておらず、特許文献3,4においても、プラズマ処理した酸化膜を用いているため、低温化に起因した膜強度の低下については考慮されていない。

【0013】

本願発明は、これらの課題を解決するためになされたものである。

【0014】

本発明の目的は、信頼性の高い半導体集積回路装置の製造プロセスを提供することにある。

【0015】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0017】

すなわち、本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

【発明の効果】

【0018】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0019】

すなわち、プリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化することにより、ゲート構造上部のプラズマTEOS膜の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、CMPの研削方向(Si基板の主面に対し平行な方向)にストレスが集中するゲート構造上部の機械的強度の向上が可能である。

【発明を実施するための最良の形態】

【0020】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0021】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ポリ・シリコン・ゲート電極の上面および前記ソース・ドレイン領域の上面をシリサイド化する工程;

(d)前記シリサイド化された前記ポリ・シリコン・ゲート電極の前記上面および前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上のほぼ全面に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、プリ・メタル層間絶縁膜の一部であり、オゾンおよびTEOSを用いた熱CVDによる第1の酸化シリコン膜を形成する工程;

(f)前記第1の酸化シリコン膜をエッチングすることにより、各ゲート構造上において前記エッチ・ストップ膜を露出させる工程;

(g)前記工程(f)の後、前記エッチ・ストップ膜の露出された部分及び前記第1のCVD酸化シリコン膜の残存した部分に、前記プリ・メタル層間絶縁膜の一部であり、TEOSを用いたプラズマCVDによる第2の酸化シリコン膜を形成する工程;

(h)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程。

【0022】

2.前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程。

【0023】

3.前記1または2項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去する工程。

【0024】

4.前記1または2項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【0025】

5.前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程;

(j)前記工程(i)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【0026】

6.前記5項の半導体集積回路装置の製造方法において、前記工程(n)は、以下の下位工程を含む:

(n1)前記第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程;

(n2)前記第2の化学機械研磨処理を実施することにより、前記第3の酸化シリコン膜を除去する工程。

【0027】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(a)および(b)は、相前後して又は一部並行して実行される。

【0028】

8.前記1から7項のいずれか一つの半導体集積回路装置の製造方法において、前記エッチ・ストップ膜は、窒化シリコン膜である。

【0029】

9.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(c)は、ニッケルのシリサイド化工程である。

【0030】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)の後、前記第1の酸化シリコン膜のアニール処理を施すことなく前記工程(f)が実行される。

【0031】

11.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(c)は、コバルトのシリサイド化工程または、低次のコバルト・シリサイドのより高次のシリサイド化工程である。

【0032】

12.前記11項の半導体集積回路装置の製造方法において、

(o)前記工程(e)の後、(f)の前に、摂氏700度から750度の温度で前記半導体ウエハの前記第1の主面側をアニール処理する工程。

【0033】

13.前記1から12項のいずれか一つの半導体集積回路装置の製造方法において、前記エッチ・ストップ膜の成膜完了時の膜厚は、前記第1の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【0034】

14.前記1から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の酸化シリコン膜の成膜完了時の膜厚は、前記第2の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【0035】

15.前記1から14項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(h)開始時点における前記第1の酸化シリコン膜の破壊靭性は、前記工程(h)開始時点における前記第2の酸化シリコン膜の破壊靭性よりも小さい。

【0036】

16.前記1から15項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(f)は、ドライ・エッチングによって実行される。

【0037】

17.前記1から15項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(f)は、ウエット・エッチングによって実行される。

【0038】

18.前記1から17項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、準常圧CVDによって行われる。

【0039】

19.前記1から18項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、摂氏400度から550度の間に設定されたウエハ・ステージ上にウエハを設置した状態で実行される。

【0040】

20.前記4項の半導体集積回路装置の製造方法において、前記バリア・メタル膜は、下層のチタンを主要な成分とする膜と、上層の窒化チタンを主要な成分とする膜とを含む。

【0041】

21.前記2項の半導体集積回路装置の製造方法において、前記第3の酸化シリコン膜は、TEOSを用いたプラズマCVDによる酸化シリコン膜である。

【0042】

22.前記1から21項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の酸化シリコン膜は、コールド・ウォール方式の枚葉CVD装置を用いて形成される。

【0043】

23.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をニッケル・シリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜とからなるプリ・メタル層間絶縁膜を形成する工程;

(f)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程;

とを備え、

前記工程(e)では、以下の工程を更に含む;

(e−1)前記第1の酸化シリコン膜を摂氏400〜550度の温度での熱CVDにより形成する工程、

(e−2)前記第2の酸化シリコン膜をプラズマCVDにより形成する工程。

【0044】

24.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ゲート構造体の上面および前記ソース・ドレイン領域の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(d)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であり、熱CVD法により形成された第1の酸化シリコン膜であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を露出するように形成された前記第1の酸化シリコン膜;

(e)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、プラズマCVD法により形成された第2の酸化シリコン膜;

(f)前記ソース・ドレイン領域と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0045】

25.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記ソース・ドレイン領域の前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成された第1の酸化シリコン膜;

(f)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成された第2の酸化シリコン膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0046】

26.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜から構成され、前記各ゲート構造体間に埋め込まれる層間絶縁膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔;

を備え、

前記第1の酸化シリコン膜は、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成され、

前記第2の酸化シリコン膜は、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、

前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0047】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0048】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。

【0049】

また、「銅、タングステン、チタン、窒化チタン、アルミニウム」等といっても、そうでない旨、特に明記した場合、または、そうでないことが論理的に明白な場合を除き、純粋なものばかりでなく、これらの部材を主要な成分とする部材を含むものとする。

【0050】

同様に、「酸化シリコン膜」と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボン・ドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0051】

更に、「窒化シリコン」といっても、そうでない旨、特に明記した場合、または、そうでないことが論理的に明白な場合を除き、純粋なものばかりでなく、これらの部材を主要な成分とする部材を含むものとする。特に、当該技術分野で多用される窒化シリコン部材は、多くの場合、相当量の水素原子を含む。本願では、「窒化シリコン」は、このような窒化シリコン部材を含む。

【0052】

更に、本明細書で述べるニッケル・シリサイドは、ニッケル(Ni)とシリコン(Si)のみから成るシリサイド膜に限られるものではなく、ニッケルを主成分とするシリサイド膜に、例えば、白金(Pt)、パラジウム(Pd)、イットリウム(Y)、イッテルビウム(Yb)、エルビウム(Er)、バナジウム(V)等の他の金属が添加されたシリサイド膜も上記ニッケル・シリサイドに含まれるものである。

【0053】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0054】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0055】

5.「ウエハ」または「半導体」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0056】

6.「ゲート構造」とは、MISFETのゲート電極、ゲート絶縁膜、サイド・ウォール等を含むゲート電極を中心とする構造体をいう。

【0057】

7.「プリ・メタル絶縁膜」とは、タングステン第1層配線層、銅系ダマシン第1層配線層、またはアルミニウム系第1層配線層等の配線層よりも下層、すなわち、一般にタングステン・プラグと同層で、窒化シリコン膜等の基板コンタクト・ホール形成用のエッチ・ストップ膜より上層で、最下層のダマシン配線層下の絶縁性バリア膜または最下層配線よりも下層の層間絶縁膜を言う。一般に、単層または2から4層の多層膜で構成されることが多い。しかし、最上層のキャップ膜等は、タングステン・プラグCMP処理で、全部除去される場合もあるので、最終構造には残らないものもあるが、製造工程途中においては、このキャップ膜もプリ・メタル絶縁膜の一部を構成するものということができる。

【0058】

8.「化学機械研磨」または”CMP”は、対象物で大きく分けると、絶縁膜CMPとメタルCMPに分類することができる。また、研磨機構で分類すると、浮遊砥粒を用いる一般的なCMP、固定砥粒を用いるCMP,および電界作用を利用するECMP等に分類することができる。本願では、これらを全て含む意味で用いている。

【0059】

9.「準常圧CVD」とは、いわゆるSA−CVD(Sub−Atmospheric CVD)であり、通常、2KPaから80KPa程度の圧力範囲で行われる。

【0060】

10.CVD装置等に関して「コールド・ウォール方式」とは、加熱源がウエハ・ステージ部分又はその近傍にあり、被処理ウエハおよびウエハ・ステージ(抵抗加熱源を含む)が最も高い温度(ウエハ処理温度、すなわちウエハ・ステージの設定温度)になり、チャンバの壁部分が比較的低温になるようにされているものを言う。また「枚葉」とは、ウエハ1枚単位で処理するもので、チャンバに1枚のウエハを収容して処理するもののほか、複数枚(たとえば2枚から4枚)を連結したチャンバに収容して処理するが、ウエハ・ステージが独立しているもの等を含む。

【0061】

11.ウエハ上の積層構造に関する上下関係については、そのときの重力の方向にかかわらず、ウエハの裏面を下として、ウエハのデバイス面方向を上という。

【0062】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。なお、以下の各実施の形態は、CMOS(Complementary Metal Oxide Semiconductor)FETまたはCMIS(Complementary Metal Insulator Semiconductor)FETを集積したシリコン・ベースの半導体集積回路装置に関するものであるが、ほぼP−N対称構造であるため、図上では、主にNチャネル・デバイス側を例にとり具体的に説明する。

【0063】

1.本願の実施形態の半導体集積回路装置の製造方法による半導体集積回路装置デバイス構造の説明(主に図1)

図1は本願発明の実施の形態の半導体集積回路装置の製造方法による65nmテクノロジ・ノードのデバイスの断面構造の一例を示すデバイス断面図である。図1に基づいて、本願の実施形態の半導体集積回路装置の製造方法による半導体集積回路装置デバイス構造の概要を説明する。

【0064】

図1に示すように、たとえば、STI(Shallow Trench Isolation)型の素子分離フィールド絶縁膜2で分離されたP型単結晶シリコン基板1のデバイス面上には、PチャネルMOSFETまたはNチャネルMOSFETのゲート電極8が形成されている。それらの上には、エッチ・ストップ膜である窒化シリコン・ライナー膜4(たとえば約30nm)が形成されている。その上には、窒化シリコン・ライナー膜4よりもずっと厚く、下層の熱CVD法によるオゾンTEOS酸化シリコン膜(たとえば約200nm)および上層のプラズマTEOS酸化シリコン膜(たとえば約270nm)等からなるプリ・メタル(Premetal)層間絶縁膜5が形成されている。また、これらのプリ・メタル絶縁膜を貫通して、タングステン・プラグ3が形成されている。ここまでがプリ・メタル領域PMである。

【0065】

その上の第1配線層M1は、下層のSiCN膜(たとえば約50nm)等の絶縁性バリア膜14および主層間絶縁膜であるプラズマシリコン酸化膜15(たとえば約150nm)等およびそれらに形成された配線溝に埋め込まれた銅配線13等から構成されている。

【0066】

その上の第2配線層から第6配線層M2,M3,M4,M5,M6は、相互にほぼ同様の構造をしている。各層は、下層のSiCO膜(たとえば約30nm)/SiCN膜(たとえば約30nm)等からなる複合絶縁性バリア膜(ライナー膜)24、34,44、54,64、および上層のほとんどの領域を占める主層間絶縁膜25,35,45,55,65等から構成されている。この主層間絶縁膜25,35,45,55,65は、下層よりカーボン・ドープ酸化シリコン膜、すなわち、SiOC膜(たとえば約350nm)とキャップ膜であるプラズマTEOSシリコン酸化膜(たとえば約80nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線23,33,43,53,63が形成されている。

【0067】

その上の第7配線層から第8配線層M7,M8は、相互にほぼ同様の構造をしている。各層は、下層のSiCN膜(たとえば約70nm)等の絶縁性バリア膜74,84および上層の主層間絶縁膜75,85等から構成されている。この主層間絶縁膜75,85は、下層よりプラズマTEOSシリコン酸化膜(たとえば約250nm)、FSG膜(たとえば約300nm)、およびキャップ膜であるUSG膜(たとえば約200nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線73,83が形成されている。

【0068】

その上の第9配線層から第10配線層M9,M10は、相互にほぼ同様の構造をしている。各層は下層の層間と上層の層内に分かれている。層間絶縁膜は、下層のSiCN膜(たとえば約70nm)等の絶縁性バリア膜94b,104bおよび上層の主層間絶縁膜等から構成されている。主層間絶縁膜は下層のFSG膜95b,105b(たとえば約800nm)及び上層のキャップ膜であるUSG膜96b,106b(たとえば約100nm)等から構成されている。また、層内絶縁膜は、下層のSiCN膜(たとえば約50nm)等の絶縁性バリア膜94a,104aおよび上層の主層間絶縁膜等から構成されている。主層内絶縁膜は下層のFSG膜95a,105a(たとえば約1200nm)及び上層のキャップ膜であるUSG膜96a,106a(たとえば約100nm)等から構成されている。これらの層間絶縁膜および層内絶縁膜等を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線93,103が形成されている。

【0069】

その上の最上層配線層APは、下層のSiCN膜114(たとえば約100nm)等の絶縁性バリア膜、中間のUSG膜117(たとえば約900nm)等の主層間絶縁膜、および、最外部のプラズマSiN119(たとえば約600nm)等のファイナル・パッシベーション膜等から構成されている。また、これらの層間絶縁膜を貫通して、タングステン・プラグ113が設けられており、USG膜117上にはアルミニウム配線118(たとえば約1000nm)およびボンディング・パッドが設けられている。

【0070】

2.本願の一実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(ニッケル・シリサイド・プロセス)の説明(主に図2から図14)

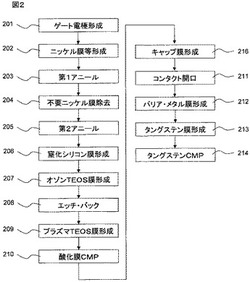

図2は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。図3は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(ソース・ドレイン領域およびゲート電極上面シリサイド化工程)である。図4は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOS膜成膜工程)である。図5は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOSエッチ・バック工程)である。図6は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜成膜工程)である。図7は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程開始時点)である。図8は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程終了時点)である。図9は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(キャップ・プラズマTEOS膜成膜工程)である。図10は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール形成工程)である。図11は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール底のエッチ・ストップ膜除去工程)である。図12は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(バリア・メタル膜成膜工程)である。図13は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステン膜成膜工程)である。図14は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステンCMP工程終了時点)である。これらに基づいて、本願の一実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(ニッケル・シリサイド・プロセス)を説明する。

【0071】

まず、図2に示すゲート電極形成工程201まで(図3の状態に至るまで)を簡単に説明する。最初に、たとえば300φのP型シリコン単結晶ウエハ1(図3参照、以下同じ)を準備する(ウエハ・サイズは200ファイでも、450ファイでも、その他のものでもよい。また、不純物型も必要に応じて、N型でもよい。また、エピタキシャル型のウエハでも、SOIウエハその他の絶縁性ウエハでもよい)。次に、ウエハ1のデバイス面1a(反対側の面は裏面1bである)の表面領域に、STI(Shallow Trench Isolation)領域2を形成する。ここで、STI領域2の深さは、たとえば300nm程度であり、その幅は、たとえば、70nm程度である。

【0072】

続いて、PチャネルMISFET形成領域とNチャネルMISFET形成領域の内のPチャネルMISFET形成領域に対応するデバイス面1a下にN型ウエル領域を形成する。次に、ウエハ1のデバイス面1aの表面に、たとえば2nmから4nm程度の厚さの酸化シリコン膜9または酸窒化シリコン膜を熱酸化等により、形成する。その上に、たとえば150nm程度の厚さのノンドープ・ポリシリコン膜8をCVD法により形成する。次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ポリシリコン膜8へのP型不純物のドープのためのレジスト膜パターンとする。レジスト膜(以下のレジストも同じ)は、たとえば化学増幅型のポジ型レジストである(たとえばポリ・ヒドロキシ・スチレン系)。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばホウ素イオン、ドーズ量は2X1015/cm2程度)を実行する。その後、不要なレジスト膜パターンを除去する。

【0073】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ポリシリコン膜8へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえば燐イオン、ドーズ量は6X1015/cm2程度)を実行する。その後、不要なレジスト膜パターンを除去する。

【0074】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ゲート電極のパターニングのためのレジスト膜パターンとする。続いて、ゲート電極のパターニングのためのレジスト膜パターンがある状態で、ポリシリコン膜8のドライ・エッチングを実行し、幅65nm程度のゲート電極8を形成する。このポリシリコン膜8のドライ・エッチングは、たとえば、HBr,Cl2,O2等の混合ガスを用いて実行することができる。続いて、不要なレジスト膜パターンを除去する。

【0075】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1のN型ウエル領域の表面1aのP型ソース・ドレイン・エクステンション領域(P型LDD領域)となるべき部分へのP型不純物のドープのためのレジスト膜パターンとする。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばBF2+をドープ量3X1014cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0076】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1の表面1aのN型ソース・ドレイン・エクステンション領域(N型LDD領域)となるべき部分へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえばAs+をドープ量1X1015cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0077】

次に、サイド・ウォール・スペーサとなるべき絶縁膜(たとえば、下層の厚さ10nm程度のオゾンTEOS膜と厚さ45nm程度上層のシリコン・ナイトライド膜からなる)をウエハ1のデバイス面1aの全面にCVD法により形成する。次に、異方性ドライ・エッチングによりエッチ・バックして、サイド・ウォール10を形成する。

【0078】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1のN型ウエル領域の表面1aの高濃度P型ソース・ドレイン領域となるべき部分へのP型不純物のドープのためのレジスト膜パターンとする。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばB+をドープ量4X1015cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0079】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1の表面1aの高濃度N型ソース・ドレイン領域となるべき部分へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえばAs+をドープ量4X1014cm−2および、それに続いて、P+をドープ量5X1014cm−2の2段階で行う)を実行する。その後、不要なレジスト膜パターンを除去する。以上により、図3に示すように、N型ソース・ドレイン・エクステンション領域および高濃度N型ソース・ドレイン領域から構成されるn型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)が形成される。

【0080】

次に、半導体基板(ウエハ)の上面1aの自然酸化膜を除去し、基板上面1aを露出させる。その状態で、ニッケル膜およびキャップ膜であるチタン・ナイトライド膜をスパッタリングにより、ほぼ全面に形成する(図2のニッケル膜等形成工程202)。その後、ウエハ上面1aを摂氏300度前後の温度でアニール処理(非酸化性雰囲気中)することにより、ニッケル膜とウエハ上面1a部分のシリコンを反応させて、ニッケル・シリサイドを形成する(図2の第1アニール工程203)。その後、ウエット・エッチングにより(エッチング液は、たとえば硫酸、過酸化水素水の混合液)、未反応のニッケル膜およびチタン・ナイトライド膜を除去する(図2の不要ニッケル膜除去工程204)。その後、再び、ウエハ上面1aを摂氏500度前後の温度でアニール処理(非酸化性雰囲気中)することにより、シリサイド反応を進行させる(図2の第2アニール工程205)。これにより、図3に示すように、n型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)およびゲート・ポリシリコン膜8の上部にシリサイド層7(ニッケル・シリサイド層7a)が形成される。これにより、ゲート酸化膜9、ゲート・ポリシリコン膜8、サイド・ウォール・スペーサ絶縁膜10、およびゲート・ポリシリコン上シリサイド層7等から構成されるゲート構造18が形成される。

【0081】

次に、図4に示すように、ゲート構造18上を含むウエハ1の上面1aのほぼ全面に、たとえば30nm程度の厚さの窒化シリコン膜4をCVDにより成膜する(図2の窒化シリコン膜形成工程206)。その上に更に、オゾンおよびTEOSを用いた熱CVDによる酸化シリコン膜5a(第1の酸化シリコン膜)をたとえば厚さ200nm程度、ゲート構造18間が埋まるように成膜する(図2のオゾンTEOS膜形成工程207)。ここで、成膜条件は、たとえば処理室内気圧は2kPaから80kPa、成膜温度(ウエハ・ステージの設定温度)は摂氏400度から550度程度、ガス流量は、TEOS/O3/He=1000から5000mgm/10000から30000sccm/10000から30000sccm等である。

【0082】

次に、図5に示すように、酸化シリコン膜5aを選択的にエッチ・バックする(ガス雰囲気はフルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガス雰囲気で、流量は、たとえば、C4F6,O2,Ar=18/11/1100sccm、気圧4Pa、処理時間30秒)ことにより、ゲート構造18の上部の窒化シリコン膜4を露出させる(図2のエッチ・バック工程208)。なお、エッチ・バックは前記のように、ドライ・エッチングで簡易に処理することができるが、下地との選択比を更にあげたい場合は、緩衝弗酸水溶液(HF,NH4F,H2O混合液)等のシリコン酸化膜エッチング用ウエット・エッチ液によるウエット・エッチングによってもよい。また、ドライ・エッチング(前半)とウエット・エッチング(後半)を併用してもよい。

【0083】

次に、図6に示すように、酸化シリコン膜5a上およびゲート構造18の上部の窒化シリコン膜4上に、TEOSを用いたプラズマCVDによる酸化シリコン膜5b(第2の酸化シリコン膜)をたとえば厚さ550nm程度、成膜する(図2のプラズマTEOS膜形成工程209)。ここで、成膜条件は、たとえば処理室内気圧は300から1100Pa、成膜温度(ウエハ・ステージの設定温度)は摂氏370から400度程度、ガス流量は、TEOS/O2=200から1500sccm/0.5から3.0slm、高周波電力(13.56MHz:500から1500W,400から430KHz:250から600W)等である。酸化シリコン膜5bは下地の酸化シリコン膜5aとともに、プリ・メタル層間絶縁膜5を構成している。

【0084】

次に、図7および図8に示すように、CMP処理(第1の化学機械研磨)により(たとえば、第1の化学機械研磨により除去する下限面Z1まで研磨除去する)、酸化シリコン膜5bをたとえば280nm程度研磨することによって平坦化する(図2の酸化膜CMP工程210)。このとき、スラリの組成は、たとえばヒュームド・シリカ砥粒12重量%、アンモニア、分散剤等を添加、pHは10.9程度である。

【0085】

次に、図9に示すように、酸化シリコン膜5b上に、キャップ膜としてTEOSを用いたプラズマCVDによる酸化シリコン膜5cを100nm程度の厚さで成膜する(図2のキャップ膜形成工程216)。この酸化シリコン膜5cも、この時点ではプリ・メタル層間絶縁膜5の一部を構成している。キャップ膜としては、TEOSを用いたプラズマCVDによる酸化シリコン膜だけでなく、その他のCVDまたは塗布によるシリコン酸化物ベースの絶縁膜が利用できる。

【0086】

次に、この酸化シリコン膜5c上に、コンタクト・ホール開口のためのレジスト膜パターンを通常のリソグラフィにより形成する。そのレジスト膜パターンをマスクとして、たとえばCF4,C2F6,C4F8,C5F8フルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガスを用いた異方性ドライ・エッチングにより、窒化シリコン膜4をエッチ・ストップ膜として、図10に示すようにコンタクト・ホール12を開口する。続いて、図11に示すように、たとえばCF4,CHF3等のフルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガスを用いた孔底の窒化シリコン膜4を除去して、コンタクト・ホール12をシリサイド層7まで延長する。その後、不要なレジスト膜パターンを除去する(図2のコンタクト開口工程211)。

【0087】

次に、図12に示すように、酸化シリコン膜5cの上面、およびコンタクト・ホール12内面に、たとえばTiCl4をメタル・ソース・ガスとして用いたメタルCVD処理により、バリア・メタル11として、チタン膜および窒化チタン膜を順次成膜する(図2のバリア・メタル膜形成工程212)。なお、バリア・メタル11の形成方法については、被覆性等の問題がないのであれば、メタルCVD処理のほか、スパッタリング成膜、またはメタルCVD処理とスパッタリング成膜の組み合わせ等の方法が適用できる(セクション3でも同じ)。

【0088】

次に、図13及び図14に示すように、バリア・メタル11上に、たとえばWF6をメタル・ソース・ガスとして用いたメタルCVD処理により、コンタクト・ホール12をタングステンにより、埋め込むようにタングステン層3を形成する(図2のタングステン膜形成工程213)。次に、メタルCMP処理(第2の化学機械研磨)により、コンタクト・ホール12外部のバリア・メタル11を除去するとともに、プリ・メタル層間絶縁膜5の上部を前記メタルCMP処理の延長として(たとえば、第2の化学機械研磨により除去する下限面Z2まで除去する。通常、酸化シリコン膜5cはこの処理でほぼ完全に除去される。しかし、必要に応じて酸化シリコン膜5cを残存させてもよい。セクション3でも同じ)除去する(図2のタングステンCMP工程214)。スラリ組成は、たとえばアルミナ砥粒5重量%、Fe(NO3)3等添加、pHは4程度である。これにより、図14に示すように、タングステン・プラグ3が完成する。以後は、セクション1の第1配線層M1の形成工程に移る。

【0089】

3.本願のその他の実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(コバルト・シリサイド・プロセス)の説明(主に図15から図26)

図15は本願発明のその他の実施の形態の半導体集積回路装置の製造方法(コバルト・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。なお、本願のその他の実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(コバルト・シリサイド・プロセス)の説明においては、前述のニッケル・シリサイド・プロセスにて使用した図2から図14を代用して説明するが、重複する部分は説明を繰り返さない。n型ソース・ドレイン不純物領域6等の形成までは、セクション2とほぼ同一であり、説明を繰り返さない。

【0090】

図15および図3に示すように、半導体基板(ウエハ)の上面1aのシリコン酸化膜を除去し、基板上面1aを露出させる。その状態で、コバルト膜およびキャップ膜であるチタン・ナイトライド膜をスパッタリングにより、ほぼ全面に形成する(図15のコバルト膜等形成工程202)。その後、ウエハ上面1aを摂氏450度前後の温度でアニール処理(非酸化性雰囲気中)することにより、コバルト膜とウエハ上面1a部分のシリコンを反応させて、コバルト・シリサイドを形成する(図15の第1アニール工程203)。その後、ウエット・エッチング(エッチング液は、たとえば塩酸と過酸化水素水の混合液)により、未反応のコバルト膜およびチタン・ナイトライド膜を除去する(図15の不要コバルト膜除去工程204)。その後、再び、ウエハ上面1aを摂氏740度前後の温度でアニール処理(非酸化性雰囲気中)することにより、シリサイド反応を進行させる(図15の第2アニール工程205)。これにより、図3に示すように、n型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)およびゲート・ポリシリコン膜8の上部にシリサイド層7(コバルト・シリサイド層7b)が形成される。これにより、ゲート酸化膜9、ゲート・ポリシリコン膜8、サイド・ウォール・スペーサ絶縁膜10、およびゲート・ポリシリコン上シリサイド層7等から構成されるゲート構造18が形成される。

【0091】

次に、図15の窒化シリコン膜形成工程206およびオゾンTEOS膜形成工程207における処理を行うが、この処理は前述したニッケル・シリサイド・プロセスの工程206および工程207と同様なため、詳細説明は省略する。

【0092】

次に、酸化シリコン膜5aに対して、摂氏750度程度の温度でアニール処理(リフローによる平坦化および膜硬度の向上を図る)を施す(図15のオゾンTEOSアニール工程215)。この処理により、ニッケル・シリサイド・プロセスに比較して、コバルト・シリサイド・プロセスでは、酸化シリコン膜5a(オゾンTEOS膜)の硬度は若干高くなっている。一方、ニッケル・シリサイド・プロセスにおいては、ニッケル・シリサイドの特性上の制約があり、シリサイド形成後は、せいぜい摂氏550度程度の温度でしか、熱処理をすることができないため、アニールによって、酸化シリコン膜5a(オゾンTEOS膜)の硬度を上げることができない。

【0093】

次に、図15のエッチ・バック工程208、プラズマTEOS膜形成工程209、酸化膜CMP工程210、キャップ膜形成工程216、コンタクト開口工程211、バリア・メタル膜形成工程212、タングステン膜形成工程213、タングステンCMP工程214の処理を行うが、これらについては、図2で説明したニッケル・シリサイド・プロセスの工程208から工程210、工程216、工程211から工程214と重複するため、ここでは詳細な説明を省略する。

【0094】

4.本願の実施形態の半導体集積回路装置の製造方法に使用する各種CVD装置、膜特性、およびプリ・メタル・プロセスに関する詳細の説明(主に図16から図18)

このセクションでは、セクション2または3で使用する酸化シリコン膜(オゾンTEOS膜5a、プラズマTEOS膜5b、キャップ・プラズマTEOS膜5c)の成膜装置、成膜プロセスおよびそれによって生成された膜特性について説明する。

【0095】

図16はCVD酸化シリコン膜の硬度、ヤング率、およびそれらのアニール温度依存性を示すデータ・プロット図である。図17は本願発明の実施の形態の半導体集積回路装置の製造方法に使用するオゾンおよびTEOSを用いるコールド・ウォール方式の枚葉式熱CVD装置の模式断面図である。図18は本願発明の実施の形態の半導体集積回路装置の製造方法に使用するTEOSを用いる枚葉式プラズマCVD装置の模式断面図である。これらに基づいて、本願の実施形態の半導体集積回路装置の製造方法に使用する各種CVD装置、膜特性、およびプリ・メタル・プロセスに関する詳細を説明する。

【0096】

まず、オゾンTEOS膜5aの成膜のための準常圧成膜装置150(コールド・ウォール型枚葉装置)について説明する。図17に示すように、この装置は熱CVD装置で、チャンバ151は被処理ウエハ1を載置するウエハ・ステージ152、およびシャワー・ヘッド156等を有しており、枚葉方式の反応炉となっている。ウエハ1はウエハ・ステージ152上に、デバイス面1aを上にして、設置される。加熱はウエハ・ステージ152に内蔵された加熱機構(抵抗加熱方式)による。この加熱機構はウエハ1の処理時は摂氏400から550度程度(ウエハ処理温度)に設定されている。一方、チャンバ壁162は、所定の温度に冷却されている。成膜時には、チャンバ151内部は2KPaから80KPa程度の真空度になるように、排気されている。オゾンおよびTEOSを含んだヘリウム・ガス(キャリア・ガス)はガス導入管155から導入され、真空排気系154から排気される。

【0097】

次に、プラズマTEOS酸化シリコン膜5b(第2の酸化シリコン膜)およびキャップ・プラズマTEOS酸化シリコン膜(第3の酸化シリコン膜)の成膜のための成膜装置161(枚葉プラズマCVD装置)について説明する。図18に示すように、この装置ではチャンバ151内の下部電極159(接地電極)が加熱機構を内蔵するとともに、ウエハ・ステージを兼ねている。一方、上部電極160は、ガス供給管155およびシャワー・ヘッド156とともにガス供給機構を兼ねている。上部電極160には、高周波電源157からマッチング回路158を介して、高周波電力(13.56MHz,400から430kHz)が供給される。成膜時は、被処理ウエハ1はデバイス面1aを上にして、下部電極159上に設置される。チャンバ151内は、成膜時には排気系154により、300から1100Pa程度の真空度に保持される。また、チャンバ壁162の温度は所定の温度に保たれている。一方、ウエハ・ステージ159は加熱機構により、摂氏370から400度程度(ウエハ処理温度)に設定されている。

【0098】

次に、これらの装置で形成されたオゾンTEOS膜5aおよびプラズマTEOS膜5bの機械的特性について説明する。図16に示すように、成膜してアニールしない状態のオゾンTEOS膜5aは、ヤング率および硬度ともに、比較的低い値を示す。しかし、摂氏750度以上でアニールすると、急速に硬化して、比較的高めのヤング率および硬度を示すようになる。

【0099】

一方、プラズマTEOS膜5b、成膜してアニールしない状態でも、アニール後のオゾンTEOS膜5aと同等か、またはそれよりも高いヤング率および硬度を示す。これは、プラズマの励起作用により、実効的な反応温度がより高くなっているためと考えられる。

【0100】

現在のプリ・メタル絶縁膜5は、ゲート構造18間のピッチの狭小化およびアスペクト・レシオの増大により、より高度のギャップ・フィル(Gap Fill)特性が求められている。しかし、パターンの微細化に伴い、コバルト・シリサイド・プロセスにおいては、シリコン酸化膜アニール温度の低温化が必要になっており、ニッケル・シリサイド・プロセスにおいては、シリサイド形成後は摂氏550度を超える高温処理が困難なため、シリコン酸化膜アニールの省略が不可避となっている。

【0101】

ここで、本願発明者らが行った解析結果によると、図4の状態でゲート構造18上のオゾンTEOS膜5aが薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5bとの界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12の開口時に再びコンタクト・ホール12内に露出し、そこへバリア・メタル11が入り込む結果、近接したコンタクト・ホール12間でショート不良が発生する。

【0102】

これを防ぐには、オゾンTEOS膜5aに対して、図16に示すように摂氏850度程度で十分に、アニール処理を施すとよいが、前に説明したようなプロセスの低温化は不可避であり、高温アニールを実施することができない。

【0103】

そこで、図4の状態の後、図5に示すように、一度、オゾンTEOS膜5aを、ゲート構造18上のエッチ・ストップ膜4が露出するように、エッチ・バックし、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5bを成膜するようにした。窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5bの界面に応力が集中することもない。プラズマTEOS膜5bは、硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0104】

なお、オゾンTEOS膜5aの代わりに、モノシラン等のガス系を用いたHDP−CVDによる酸化シリコン膜を用いることも考えられる。しかし、HDP−CVDによる酸化シリコン膜は、成膜したそのままの状態でも比較的ヤング率および硬度が高いが、膜のストレスが高く、トランジスタ特性に十分配慮する必要がある。この場合、ヤング率および硬度が高いので、クラックの発生の恐れがないので、エッチ・バックの必要性は比較的低いとも考えられる。また、HDP−CVDによる酸化シリコン膜を使用する場合は、オゾンTEOS膜5aおよびプラズマTEOS膜5bの両方をHDP−CVDによる酸化シリコン膜として、ワン・ステップで成膜した後、酸化膜CMP処理し、キャップ膜としてプラズマTEOS酸化シリコン膜その他のCVD酸化シリコン膜を使用する方が効率的な場合もある。

【0105】

5.その他の実施形態

その他の実施形態として、以下の(1)〜(20)項に示す実施形態についても明示される。

【0106】

(1)以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をニッケル・シリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜とからなるプリ・メタル層間絶縁膜を形成する工程;

(f)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程;

とを備え、

前記工程(e)では、以下の工程を更に含む;

(e−1)前記第1の酸化シリコン膜を摂氏400〜550度の温度での熱CVDにより形成する工程、

(e−2)前記第2の酸化シリコン膜をプラズマCVDにより形成する工程。

【0107】

(2)前記(1)項の半導体集積回路装置の製造方法において、

前記工程(e−1)と工程(e−2)との間には、前記第1の酸化シリコン膜に対する摂氏550度を超える温度でのアニール処理は実行されない。

【0108】

(3)前記(1)または(2)項の半導体集積回路装置の製造方法において、

前記工程(e−1)では、オゾンおよびTEOSを用いた熱CVDにより前記第1の酸化シリコン膜を形成し、

前記工程(e−2)では、TEOSを用いたプラズマCVDにより前記第2の酸化シリコン膜を形成する。

【0109】

ここで、前述したようにニッケル・シリサイド・プロセスにおいては、ニッケル・シリサイド膜の特性上の制約から摂氏550度を超える温度での熱処理(アニール)をすることができない。また、図27に示されるように、摂氏550度以下で生成したオゾンTEOS膜の硬度は低いため、このオゾンTEOS膜をCMPにて研摩するとオゾンTEOS膜にクラックが発生する等の問題が生じる。よって、上述した(1)〜(3)の実施形態では、膜の硬度が低いオゾンTEOS膜の上面に硬度が高いプラズマTEOS膜を形成し、プラズマTEOS膜をCMPにて研摩処理を行うため、クラック等の発生が抑制された層間絶縁膜を形成することが可能となる。

【0110】

(4)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ゲート構造体の上面および前記ソース・ドレイン領域の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(d)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であり、熱CVD法により形成された第1の酸化シリコン膜であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を露出するように形成された前記第1の酸化シリコン膜;

(e)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、プラズマCVD法により形成された第2の酸化シリコン膜;

(f)前記ソース・ドレイン領域と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0111】

(5)前記(4)項の半導体集積回路装置において、前記半導体ウエハの第1の主面上には、STI構造の素子分離フィールド絶縁膜が更に形成され、前記エッチ・ストッパ膜は前記素子分離フィールド絶縁膜の上面をも含み形成されている。

【0112】

(6)前記(4)または(5)項の半導体集積回路装置において、前記接続孔と前記ソース・ドレイン領域とは、シリサイド膜を介して電気的に接続されている。

【0113】

(7)前記(6)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0114】

(8)前記(6)項の半導体集積回路装置において、前記シリサイド膜はコバルト・シリサイド膜である。

【0115】

(9)前記(4)から(8)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0116】

(10)前記(7)項の半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0117】

(11)前記(4)から(10)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0118】

ここで、前述したように、図4の状態でゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)が薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)との界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12(接続孔)の開口時に再びコンタクト・ホール12内に露出し、そこへプラグを構成するバリア・メタル11が入り込む結果、近接したコンタクトプラグ間でショート不良が発生する。

【0119】

そこで、ゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)をエッチ・バックし、エッチ・ストップ膜4を露出する構造とする。そして、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)を堆積する構造とした。ゲート構造体上部のプラズマTEOS膜(第2の酸化シリコン膜)の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、エッチ・ストップ膜である窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5b(第2の酸化シリコン膜)の界面に応力が集中することもない。なお、プラズマTEOS膜5bは、膜の硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0120】

よって、上述した(4)〜(11)の実施の形態に示される半導体集積回路装置の構造を採用することで、CMPによる応力集中から生じるクラックの発生が抑制でき、更にはコンタクト・ホール12(接続孔)のショート不良の発生が抑制できる。

【0121】

(12)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記ソース・ドレイン領域の前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成された第1の酸化シリコン膜;

(f)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成された第2の酸化シリコン膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0122】

(13)前記(12)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0123】

(14)前記(12)から(13)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0124】

(15)前記(12)から(14)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0125】

(16)前記(12)から(15)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0126】

(17)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜から構成され、前記各ゲート構造体間に埋め込まれる層間絶縁膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔;

を備え、

前記第1の酸化シリコン膜は、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成され、

前記第2の酸化シリコン膜は、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、

前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0127】

(18)前記(17)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0128】

(19)前記(17)または(18)項の半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0129】

(20)前記(17)から(19)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0130】

ここで、前述したように、図4の状態でゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)が薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)との界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12(接続孔)の開口時に再びコンタクト・ホール12内に露出し、そこへプラグを構成するバリア・メタル11が入り込む結果、近接したコンタクトプラグ間でショート不良が発生する。

【0131】

これを防ぐには、オゾンTEOS膜5aに対して、図27に示すように摂氏850度程度で十分に、アニール処理を施すとよいが、前に説明したようなシリサイド・プロセスの低温化は不可避であり、高温アニールを実施することができない。

【0132】

そこで、ゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)をエッチ・バックし、前記第1の酸化シリコン膜が前記エッチ・ストップ膜4を覆わない構造とする。そして、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)を堆積する構造とした。ゲート構造体上部のプラズマTEOS膜(第2の酸化シリコン膜)の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、エッチ・ストップ膜である窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5b(第2の酸化シリコン膜)の界面に応力が集中することもない。なお、プラズマTEOS膜5b(熱CVD法により形成した第1の酸化シリコン膜)は、オゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)よりも膜の硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0133】

よって、上述した(12)〜(20)の実施の形態に示される半導体集積回路装置の構造を採用することで、CMPによる応力集中から生じるクラックの発生が抑制でき、更にはコンタクト・ホール12(接続孔)のショート不良の発生が抑制できる。

【0134】

なお、上記(1)〜(20)に示す実施形態は、この明細書にて記載された他の効果を排除するものではなく、相乗的に奏するものであることは言うまでもない。

【0135】

6.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0136】

例えば、前記各実施の形態では、バック・エンド・プロセスについては、銅ダマシン配線を主とする構成について具体的に説明したが、本発明はそれに限定されるものではなく、銀等のダマシン配線をバック・エンド・プロセスに適用したもの、および、アルミニウム系の配線をバック・エンド・プロセスに使用したものにも適用できることは言うまでもない。

【0137】

また、前記各実施の形態では、CVD装置について、枚葉装置について具体的に説明したが、本発明はそれに限定されるものではなく、バッチ式装置やミニ・バッチ式装置を用いたプロセスにも適用できることは言うまでもない。

【0138】

また、オゾンTEOS−熱CVD装置に関して、準常圧装置について具体的に説明したが、常圧装置を用いたプロセスでもよいことは言うまでもない。

【0139】

更に、オゾンTEOS膜またはプラズマTEOS膜は、不純物ドープの面から言って、デバイス設計の必要に応じて、非ドープ酸化シリコン膜であってもよいし、燐、ボロンその他の不純物を添加した酸化シリコン系の絶縁膜でもよい。

【図面の簡単な説明】

【0140】

【図1】本願発明の実施の形態の半導体集積回路装置の製造方法によるデバイスの断面構造の一例を示すデバイス断面図である。

【図2】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。

【図3】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(ソース・ドレイン領域およびゲート電極上面シリサイド化工程)である。

【図4】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOS膜成膜工程)である。

【図5】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOSエッチ・バック工程)である。

【図6】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜成膜工程)である。

【図7】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程開始時点)である。

【図8】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程終了時点)である。

【図9】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(キャップ・プラズマTEOS膜成膜工程)である。

【図10】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール形成工程)である。

【図11】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール底のエッチ・ストップ膜除去工程)である。

【図12】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(バリア・メタル膜成膜工程)である。

【図13】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステン膜成膜工程)である。

【図14】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステンCMP工程終了時点)である。

【図15】本願発明のその他の実施の形態の半導体集積回路装置の製造方法(コバルト・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。

【図16】CVD酸化シリコン膜の硬度、ヤング率、およびそれらのアニール温度依存性を示すデータ・プロット図である。

【図17】本願発明の実施の形態の半導体集積回路装置の製造方法に使用するオゾンおよびTEOSを用いるコールド・ウォール方式の枚葉式熱CVD装置の模式断面図である。

【図18】本願発明の実施の形態の半導体集積回路装置の製造方法に使用するTEOSを用いる枚葉式プラズマCVD装置の模式断面図である。

【符号の説明】

【0141】

1 P型単結晶シリコン基板(半導体ウエハ)

1a 基板又はウエハのデバイス面(第1の主面)

1b 基板又はウエハの裏面(第2の主面)

2 素子分離フィールド絶縁膜

3 タングステン・プラグ

4 窒化シリコン・ライナー膜(エッチ・ストップ膜)

5 プリ・メタル層間絶縁膜

5a (プリ・メタル層間絶縁膜の内の)オゾンTEOS酸化シリコン膜(第1の酸化シリコン膜)

5b (プリ・メタル層間絶縁膜の内の)プラズマTEOS酸化シリコン膜(第2の酸化シリコン膜)

5c (プリ・メタル層間絶縁膜の内の)キャップ・プラズマTEOS酸化シリコン膜(第3の酸化シリコン膜)

6 n型ソース・ドレイン不純物領域

7 シリサイド層

7a ニッケル・シリサイド層

7b コバルト・シリサイド層

8 ゲート電極(ポリシリコン膜)

9 ゲート絶縁膜

10 サイド・ウォール絶縁膜

11 バリア・メタル膜

12 コンタクト・ホール

13 埋め込まれた銅配線

14 絶縁性バリア膜

15 プラズマシリコン酸化膜

18 ゲート構造

23 銅埋め込み配線

24 絶縁性バリア膜

25 主層間絶縁膜

33 銅埋め込み配線

34 絶縁性バリア膜

35 主層間絶縁膜

43 銅埋め込み配線

44 絶縁性バリア膜

45 主層間絶縁膜

53 銅埋め込み配線

54 絶縁性バリア膜

55 主層間絶縁膜

63 銅埋め込み配線

64 絶縁性バリア膜

65 主層間絶縁膜

73 銅埋め込み配線

74 絶縁性バリア膜

75 主層間絶縁膜

83 銅埋め込み配線

84 絶縁性バリア膜

85 主層間絶縁膜

93 銅埋め込み配線

94a 絶縁性バリア膜

94b 絶縁性バリア膜

95a FSG膜

95b FSG膜

96a USG膜

96b USG膜

103 銅埋め込み配線

104a 絶縁性バリア膜

104b 絶縁性バリア膜

105a FSG膜

105b FSG膜

106a USG膜

106b USG膜

113 タングステン・プラグ

114 SiCN膜

117 USG膜

118 アルミニウム配線

119 プラズマSiN

150 準常圧熱CVD装置

151 処理チャンバ

152 ウエハ・ステージ

154 真空排気系

155 ガス供給系

156 シャワー・ヘッド

157 高周波電源

158 マッチング機構

159 下部電極(ウエハ・ステージ)

160 上部電極

161 プラズマCVD装置

162 チャンバ壁

201 ゲート電極形成

202 シリサイド形成用メタル膜等形成

203 シリサイド化のための第1アニール

204 余剰シリサイド形成用メタル膜等除去

205 シリサイド化のための第2アニール

206 エッチ・ストップのための窒化シリコン膜形成

207 オゾンTEOSによる酸化シリコン膜形成

208 エッチ・バック処理

209 プラズマTEOSによる酸化シリコン膜形成

210 化学機械研磨による平坦化処理

211 コンタクト・ホール開口

212 バリア・メタル膜形成

213 プラグ用タングステン膜形成

214 メタルCMP処理

215 オゾンTEOS膜アニール処理

216 キャップ膜形成

AP 最上層配線層

M1 第1配線層

M2 第2配線層

M3 第3配線層

M4 第4配線層

M5 第5配線層

M6 第6配線層

M7 第7配線層

M8 第8配線層

M9 第9配線層

M10 第10配線層

PM プリ・メタル領域

Z1 第1の化学機械研磨により除去する下限面

Z2 第2の化学機械研磨により除去する下限面

【技術分野】

【0001】

本発明は、主にMISFET(Metal Insulator Semiconductor Field Effect Transistor)またはMOSFET(Metal Oxide Semiconductor Field Effect Transistor)を集積した半導体集積回路装置および半導体集積回路装置(または半導体装置)の製造方法における絶縁膜形成技術、特にプリ・メタル(Pre−Metal)層間絶縁膜形成技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開平5−21620号公報(特許文献1)には、プリ・メタル層間絶縁膜形成技術として、TEOS(Tetra−Ethyl−Ortho−Silicate)を用いたTEOS−CVD(Chemical Vapor Deposition)シリコン酸化膜の上にSOG(Spin−On−Glass)シリコン酸化膜を塗布して平坦化し、これらをドライ・エッチングによりエッチ・バックする技術が開示されている。

【0003】

日本特開平5−206474号公報(特許文献2)には、TEOSを用いたTEOS−CVDシリコン酸化膜をリフローして平坦化した後、エッチ・バックする技術が開示されている。

【0004】

日本特開2002−110666号公報(特許文献3)には、HDP(High Density Plasma)によるCVDシリコン酸化膜の上にP−TEOS(Plasma−TEOS)によるCVDシリコン酸化膜を形成し、このP−TEOSによるCVDシリコン酸化膜をCMP(Chemical Mechanical Polishing)またはエッチ・バックして平坦化した後、キャップ膜としてP−TEOSによるCVDシリコン酸化膜を形成する技術が開示されている。

【0005】

日本特開特開2000−208624号公報(特許文献4)には、プリ・メタル層間絶縁膜の形成技術として、O3−TEOSを用いたプラズマCVD法により酸化シリコン膜を形成し、その後、CMP法により前記酸化シリコン膜をゲート電極の導電層が露出するまで研磨し、更にその上に、PH3−SiH4−O2を用いたCVD法により酸化シリコン膜を形成する技術が開示されている。

【0006】

日本特開平7−147281号公報(特許文献5)および日本特開平3−194932号公報(特許文献6)には、配線間をO3−TEOSを用いたCVDにより酸化シリコン膜を形成し、その後エッチバック又はCMPにより前記配線の上部を露出するまで前記酸化シリコン膜を除去し、更にその上に、TEOSを用いたプラズマCVDによる酸化シリコン膜を形成する技術が開示されている。

【0007】

日本特開平7−221179号公報(特許文献7)には、配線間をO3−TEOS NSGシリコン膜(堆積時点でin−situリフローを生じている)で埋め込んだ後、プラズマCVDによるシリコン酸化膜を形成し、その後、CMPにより平坦化する技術が開示されている。

【0008】

【特許文献1】特開平5−21620号公報

【特許文献2】特開平5−206474号公報

【特許文献3】特開2002−110666号公報

【特許文献4】特開2000−208624号公報

【特許文献5】特開平7−147281号公報

【特許文献6】特開平3−194932号公報

【特許文献7】特開平7−221179号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

半導体集積回路装置のプリ・メタル層間絶縁膜の構成法としては、たとえばオゾンTEOSによる酸化シリコン膜(以下、混乱のない場合「オゾンTEOS膜」または「O3−TEOS膜」と略称する)等の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜(以下、混乱のない場合「プラズマTEOS膜」または「P−TEOS膜」と略称する)等を積層し、更にCMPで平坦化することが考えられる。また、オゾンTEOSによる酸化シリコン膜およびプラズマTEOSによる酸化シリコン膜等の代わりに、埋め込み特性の良好なHDPによるCVDシリコン酸化膜の適用も考えられる。

【0010】

しかし、本願発明者等が検討したところによると、前者においては、コンタクト・ホール形成プロセスにおいて、キャップ絶縁膜によって、一旦、塞がれたプリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。このクラックの原因は、ゲート構造上部でプラズマTEOS膜が薄くなると、比較的軟らかい下地のオゾンTEOS膜上のプラズマTEOS膜にCMPによる応力が集中するためである。これは、オゾンTEOS膜の成膜温度の低温化に伴い顕著になる問題であることが、本願発明者等によって明らかになった。

【0011】

一方、後者については、膜内のストレスによるトランジスタ特性への悪影響が懸念されるほか、成膜初期にシリコン・リッチな難エッチング性の膜を生成するという問題もある。

【0012】

なお、特許文献1、5,6には、TEOS−CVD膜の低温化に起因した膜強度の低下について考慮されておらず、特許文献2,7においても、TEOS−CVD膜はリフロー処理が成されているため、低温化に起因した膜強度の低下について考慮されておらず、特許文献3,4においても、プラズマ処理した酸化膜を用いているため、低温化に起因した膜強度の低下については考慮されていない。

【0013】

本願発明は、これらの課題を解決するためになされたものである。

【0014】

本発明の目的は、信頼性の高い半導体集積回路装置の製造プロセスを提供することにある。

【0015】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0017】

すなわち、本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

【発明の効果】

【0018】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0019】

すなわち、プリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化することにより、ゲート構造上部のプラズマTEOS膜の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、CMPの研削方向(Si基板の主面に対し平行な方向)にストレスが集中するゲート構造上部の機械的強度の向上が可能である。

【発明を実施するための最良の形態】

【0020】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0021】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ポリ・シリコン・ゲート電極の上面および前記ソース・ドレイン領域の上面をシリサイド化する工程;

(d)前記シリサイド化された前記ポリ・シリコン・ゲート電極の前記上面および前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上のほぼ全面に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、プリ・メタル層間絶縁膜の一部であり、オゾンおよびTEOSを用いた熱CVDによる第1の酸化シリコン膜を形成する工程;

(f)前記第1の酸化シリコン膜をエッチングすることにより、各ゲート構造上において前記エッチ・ストップ膜を露出させる工程;

(g)前記工程(f)の後、前記エッチ・ストップ膜の露出された部分及び前記第1のCVD酸化シリコン膜の残存した部分に、前記プリ・メタル層間絶縁膜の一部であり、TEOSを用いたプラズマCVDによる第2の酸化シリコン膜を形成する工程;

(h)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程。

【0022】

2.前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程。

【0023】

3.前記1または2項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去する工程。

【0024】

4.前記1または2項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【0025】

5.前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程;

(j)前記工程(i)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【0026】

6.前記5項の半導体集積回路装置の製造方法において、前記工程(n)は、以下の下位工程を含む:

(n1)前記第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程;

(n2)前記第2の化学機械研磨処理を実施することにより、前記第3の酸化シリコン膜を除去する工程。

【0027】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(a)および(b)は、相前後して又は一部並行して実行される。

【0028】

8.前記1から7項のいずれか一つの半導体集積回路装置の製造方法において、前記エッチ・ストップ膜は、窒化シリコン膜である。

【0029】

9.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(c)は、ニッケルのシリサイド化工程である。

【0030】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)の後、前記第1の酸化シリコン膜のアニール処理を施すことなく前記工程(f)が実行される。

【0031】

11.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(c)は、コバルトのシリサイド化工程または、低次のコバルト・シリサイドのより高次のシリサイド化工程である。

【0032】

12.前記11項の半導体集積回路装置の製造方法において、

(o)前記工程(e)の後、(f)の前に、摂氏700度から750度の温度で前記半導体ウエハの前記第1の主面側をアニール処理する工程。

【0033】

13.前記1から12項のいずれか一つの半導体集積回路装置の製造方法において、前記エッチ・ストップ膜の成膜完了時の膜厚は、前記第1の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【0034】

14.前記1から13項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の酸化シリコン膜の成膜完了時の膜厚は、前記第2の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【0035】

15.前記1から14項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(h)開始時点における前記第1の酸化シリコン膜の破壊靭性は、前記工程(h)開始時点における前記第2の酸化シリコン膜の破壊靭性よりも小さい。

【0036】

16.前記1から15項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(f)は、ドライ・エッチングによって実行される。

【0037】

17.前記1から15項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(f)は、ウエット・エッチングによって実行される。

【0038】

18.前記1から17項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、準常圧CVDによって行われる。

【0039】

19.前記1から18項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、摂氏400度から550度の間に設定されたウエハ・ステージ上にウエハを設置した状態で実行される。

【0040】

20.前記4項の半導体集積回路装置の製造方法において、前記バリア・メタル膜は、下層のチタンを主要な成分とする膜と、上層の窒化チタンを主要な成分とする膜とを含む。

【0041】

21.前記2項の半導体集積回路装置の製造方法において、前記第3の酸化シリコン膜は、TEOSを用いたプラズマCVDによる酸化シリコン膜である。

【0042】

22.前記1から21項のいずれか一つの半導体集積回路装置の製造方法において、前記第1の酸化シリコン膜は、コールド・ウォール方式の枚葉CVD装置を用いて形成される。

【0043】

23.以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をニッケル・シリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜とからなるプリ・メタル層間絶縁膜を形成する工程;

(f)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程;

とを備え、

前記工程(e)では、以下の工程を更に含む;

(e−1)前記第1の酸化シリコン膜を摂氏400〜550度の温度での熱CVDにより形成する工程、

(e−2)前記第2の酸化シリコン膜をプラズマCVDにより形成する工程。

【0044】

24.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ゲート構造体の上面および前記ソース・ドレイン領域の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(d)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であり、熱CVD法により形成された第1の酸化シリコン膜であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を露出するように形成された前記第1の酸化シリコン膜;

(e)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、プラズマCVD法により形成された第2の酸化シリコン膜;

(f)前記ソース・ドレイン領域と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0045】

25.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記ソース・ドレイン領域の前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成された第1の酸化シリコン膜;

(f)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成された第2の酸化シリコン膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0046】

26.以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜から構成され、前記各ゲート構造体間に埋め込まれる層間絶縁膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔;

を備え、

前記第1の酸化シリコン膜は、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成され、

前記第2の酸化シリコン膜は、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、

前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0047】

〔本願における記載形式・基本的用語・用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0048】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。

【0049】

また、「銅、タングステン、チタン、窒化チタン、アルミニウム」等といっても、そうでない旨、特に明記した場合、または、そうでないことが論理的に明白な場合を除き、純粋なものばかりでなく、これらの部材を主要な成分とする部材を含むものとする。

【0050】

同様に、「酸化シリコン膜」と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボン・ドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノ・クラスタリング・シリカ(Nano-Clustering Silica:NSC)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0051】

更に、「窒化シリコン」といっても、そうでない旨、特に明記した場合、または、そうでないことが論理的に明白な場合を除き、純粋なものばかりでなく、これらの部材を主要な成分とする部材を含むものとする。特に、当該技術分野で多用される窒化シリコン部材は、多くの場合、相当量の水素原子を含む。本願では、「窒化シリコン」は、このような窒化シリコン部材を含む。

【0052】

更に、本明細書で述べるニッケル・シリサイドは、ニッケル(Ni)とシリコン(Si)のみから成るシリサイド膜に限られるものではなく、ニッケルを主成分とするシリサイド膜に、例えば、白金(Pt)、パラジウム(Pd)、イットリウム(Y)、イッテルビウム(Yb)、エルビウム(Er)、バナジウム(V)等の他の金属が添加されたシリサイド膜も上記ニッケル・シリサイドに含まれるものである。

【0053】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0054】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0055】

5.「ウエハ」または「半導体」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0056】

6.「ゲート構造」とは、MISFETのゲート電極、ゲート絶縁膜、サイド・ウォール等を含むゲート電極を中心とする構造体をいう。

【0057】

7.「プリ・メタル絶縁膜」とは、タングステン第1層配線層、銅系ダマシン第1層配線層、またはアルミニウム系第1層配線層等の配線層よりも下層、すなわち、一般にタングステン・プラグと同層で、窒化シリコン膜等の基板コンタクト・ホール形成用のエッチ・ストップ膜より上層で、最下層のダマシン配線層下の絶縁性バリア膜または最下層配線よりも下層の層間絶縁膜を言う。一般に、単層または2から4層の多層膜で構成されることが多い。しかし、最上層のキャップ膜等は、タングステン・プラグCMP処理で、全部除去される場合もあるので、最終構造には残らないものもあるが、製造工程途中においては、このキャップ膜もプリ・メタル絶縁膜の一部を構成するものということができる。

【0058】

8.「化学機械研磨」または”CMP”は、対象物で大きく分けると、絶縁膜CMPとメタルCMPに分類することができる。また、研磨機構で分類すると、浮遊砥粒を用いる一般的なCMP、固定砥粒を用いるCMP,および電界作用を利用するECMP等に分類することができる。本願では、これらを全て含む意味で用いている。

【0059】

9.「準常圧CVD」とは、いわゆるSA−CVD(Sub−Atmospheric CVD)であり、通常、2KPaから80KPa程度の圧力範囲で行われる。

【0060】

10.CVD装置等に関して「コールド・ウォール方式」とは、加熱源がウエハ・ステージ部分又はその近傍にあり、被処理ウエハおよびウエハ・ステージ(抵抗加熱源を含む)が最も高い温度(ウエハ処理温度、すなわちウエハ・ステージの設定温度)になり、チャンバの壁部分が比較的低温になるようにされているものを言う。また「枚葉」とは、ウエハ1枚単位で処理するもので、チャンバに1枚のウエハを収容して処理するもののほか、複数枚(たとえば2枚から4枚)を連結したチャンバに収容して処理するが、ウエハ・ステージが独立しているもの等を含む。

【0061】

11.ウエハ上の積層構造に関する上下関係については、そのときの重力の方向にかかわらず、ウエハの裏面を下として、ウエハのデバイス面方向を上という。

【0062】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。なお、以下の各実施の形態は、CMOS(Complementary Metal Oxide Semiconductor)FETまたはCMIS(Complementary Metal Insulator Semiconductor)FETを集積したシリコン・ベースの半導体集積回路装置に関するものであるが、ほぼP−N対称構造であるため、図上では、主にNチャネル・デバイス側を例にとり具体的に説明する。

【0063】

1.本願の実施形態の半導体集積回路装置の製造方法による半導体集積回路装置デバイス構造の説明(主に図1)

図1は本願発明の実施の形態の半導体集積回路装置の製造方法による65nmテクノロジ・ノードのデバイスの断面構造の一例を示すデバイス断面図である。図1に基づいて、本願の実施形態の半導体集積回路装置の製造方法による半導体集積回路装置デバイス構造の概要を説明する。

【0064】

図1に示すように、たとえば、STI(Shallow Trench Isolation)型の素子分離フィールド絶縁膜2で分離されたP型単結晶シリコン基板1のデバイス面上には、PチャネルMOSFETまたはNチャネルMOSFETのゲート電極8が形成されている。それらの上には、エッチ・ストップ膜である窒化シリコン・ライナー膜4(たとえば約30nm)が形成されている。その上には、窒化シリコン・ライナー膜4よりもずっと厚く、下層の熱CVD法によるオゾンTEOS酸化シリコン膜(たとえば約200nm)および上層のプラズマTEOS酸化シリコン膜(たとえば約270nm)等からなるプリ・メタル(Premetal)層間絶縁膜5が形成されている。また、これらのプリ・メタル絶縁膜を貫通して、タングステン・プラグ3が形成されている。ここまでがプリ・メタル領域PMである。

【0065】

その上の第1配線層M1は、下層のSiCN膜(たとえば約50nm)等の絶縁性バリア膜14および主層間絶縁膜であるプラズマシリコン酸化膜15(たとえば約150nm)等およびそれらに形成された配線溝に埋め込まれた銅配線13等から構成されている。

【0066】

その上の第2配線層から第6配線層M2,M3,M4,M5,M6は、相互にほぼ同様の構造をしている。各層は、下層のSiCO膜(たとえば約30nm)/SiCN膜(たとえば約30nm)等からなる複合絶縁性バリア膜(ライナー膜)24、34,44、54,64、および上層のほとんどの領域を占める主層間絶縁膜25,35,45,55,65等から構成されている。この主層間絶縁膜25,35,45,55,65は、下層よりカーボン・ドープ酸化シリコン膜、すなわち、SiOC膜(たとえば約350nm)とキャップ膜であるプラズマTEOSシリコン酸化膜(たとえば約80nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線23,33,43,53,63が形成されている。

【0067】

その上の第7配線層から第8配線層M7,M8は、相互にほぼ同様の構造をしている。各層は、下層のSiCN膜(たとえば約70nm)等の絶縁性バリア膜74,84および上層の主層間絶縁膜75,85等から構成されている。この主層間絶縁膜75,85は、下層よりプラズマTEOSシリコン酸化膜(たとえば約250nm)、FSG膜(たとえば約300nm)、およびキャップ膜であるUSG膜(たとえば約200nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線73,83が形成されている。

【0068】

その上の第9配線層から第10配線層M9,M10は、相互にほぼ同様の構造をしている。各層は下層の層間と上層の層内に分かれている。層間絶縁膜は、下層のSiCN膜(たとえば約70nm)等の絶縁性バリア膜94b,104bおよび上層の主層間絶縁膜等から構成されている。主層間絶縁膜は下層のFSG膜95b,105b(たとえば約800nm)及び上層のキャップ膜であるUSG膜96b,106b(たとえば約100nm)等から構成されている。また、層内絶縁膜は、下層のSiCN膜(たとえば約50nm)等の絶縁性バリア膜94a,104aおよび上層の主層間絶縁膜等から構成されている。主層内絶縁膜は下層のFSG膜95a,105a(たとえば約1200nm)及び上層のキャップ膜であるUSG膜96a,106a(たとえば約100nm)等から構成されている。これらの層間絶縁膜および層内絶縁膜等を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線93,103が形成されている。

【0069】

その上の最上層配線層APは、下層のSiCN膜114(たとえば約100nm)等の絶縁性バリア膜、中間のUSG膜117(たとえば約900nm)等の主層間絶縁膜、および、最外部のプラズマSiN119(たとえば約600nm)等のファイナル・パッシベーション膜等から構成されている。また、これらの層間絶縁膜を貫通して、タングステン・プラグ113が設けられており、USG膜117上にはアルミニウム配線118(たとえば約1000nm)およびボンディング・パッドが設けられている。

【0070】

2.本願の一実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(ニッケル・シリサイド・プロセス)の説明(主に図2から図14)

図2は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。図3は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(ソース・ドレイン領域およびゲート電極上面シリサイド化工程)である。図4は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOS膜成膜工程)である。図5は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOSエッチ・バック工程)である。図6は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜成膜工程)である。図7は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程開始時点)である。図8は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程終了時点)である。図9は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(キャップ・プラズマTEOS膜成膜工程)である。図10は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール形成工程)である。図11は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール底のエッチ・ストップ膜除去工程)である。図12は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(バリア・メタル膜成膜工程)である。図13は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステン膜成膜工程)である。図14は本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステンCMP工程終了時点)である。これらに基づいて、本願の一実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(ニッケル・シリサイド・プロセス)を説明する。

【0071】

まず、図2に示すゲート電極形成工程201まで(図3の状態に至るまで)を簡単に説明する。最初に、たとえば300φのP型シリコン単結晶ウエハ1(図3参照、以下同じ)を準備する(ウエハ・サイズは200ファイでも、450ファイでも、その他のものでもよい。また、不純物型も必要に応じて、N型でもよい。また、エピタキシャル型のウエハでも、SOIウエハその他の絶縁性ウエハでもよい)。次に、ウエハ1のデバイス面1a(反対側の面は裏面1bである)の表面領域に、STI(Shallow Trench Isolation)領域2を形成する。ここで、STI領域2の深さは、たとえば300nm程度であり、その幅は、たとえば、70nm程度である。

【0072】

続いて、PチャネルMISFET形成領域とNチャネルMISFET形成領域の内のPチャネルMISFET形成領域に対応するデバイス面1a下にN型ウエル領域を形成する。次に、ウエハ1のデバイス面1aの表面に、たとえば2nmから4nm程度の厚さの酸化シリコン膜9または酸窒化シリコン膜を熱酸化等により、形成する。その上に、たとえば150nm程度の厚さのノンドープ・ポリシリコン膜8をCVD法により形成する。次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ポリシリコン膜8へのP型不純物のドープのためのレジスト膜パターンとする。レジスト膜(以下のレジストも同じ)は、たとえば化学増幅型のポジ型レジストである(たとえばポリ・ヒドロキシ・スチレン系)。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばホウ素イオン、ドーズ量は2X1015/cm2程度)を実行する。その後、不要なレジスト膜パターンを除去する。

【0073】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ポリシリコン膜8へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえば燐イオン、ドーズ量は6X1015/cm2程度)を実行する。その後、不要なレジスト膜パターンを除去する。

【0074】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、ゲート電極のパターニングのためのレジスト膜パターンとする。続いて、ゲート電極のパターニングのためのレジスト膜パターンがある状態で、ポリシリコン膜8のドライ・エッチングを実行し、幅65nm程度のゲート電極8を形成する。このポリシリコン膜8のドライ・エッチングは、たとえば、HBr,Cl2,O2等の混合ガスを用いて実行することができる。続いて、不要なレジスト膜パターンを除去する。

【0075】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1のN型ウエル領域の表面1aのP型ソース・ドレイン・エクステンション領域(P型LDD領域)となるべき部分へのP型不純物のドープのためのレジスト膜パターンとする。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばBF2+をドープ量3X1014cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0076】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1の表面1aのN型ソース・ドレイン・エクステンション領域(N型LDD領域)となるべき部分へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえばAs+をドープ量1X1015cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0077】

次に、サイド・ウォール・スペーサとなるべき絶縁膜(たとえば、下層の厚さ10nm程度のオゾンTEOS膜と厚さ45nm程度上層のシリコン・ナイトライド膜からなる)をウエハ1のデバイス面1aの全面にCVD法により形成する。次に、異方性ドライ・エッチングによりエッチ・バックして、サイド・ウォール10を形成する。

【0078】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1のN型ウエル領域の表面1aの高濃度P型ソース・ドレイン領域となるべき部分へのP型不純物のドープのためのレジスト膜パターンとする。続いて、NチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にP型の不純物イオン注入処理(たとえばB+をドープ量4X1015cm−2)を実行する。その後、不要なレジスト膜パターンを除去する。

【0079】

次に、ウエハ1のデバイス面1aの全面にレジスト膜を塗布して、通常のリソグラフィにより、半導体基板1の表面1aの高濃度N型ソース・ドレイン領域となるべき部分へのN型不純物のドープのためのレジスト膜パターンとする。続いて、PチャネルMISFET形成領域をレジスト膜(レジスト膜パターン)で被覆した状態で、全面にN型の不純物イオン注入処理(たとえばAs+をドープ量4X1014cm−2および、それに続いて、P+をドープ量5X1014cm−2の2段階で行う)を実行する。その後、不要なレジスト膜パターンを除去する。以上により、図3に示すように、N型ソース・ドレイン・エクステンション領域および高濃度N型ソース・ドレイン領域から構成されるn型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)が形成される。

【0080】

次に、半導体基板(ウエハ)の上面1aの自然酸化膜を除去し、基板上面1aを露出させる。その状態で、ニッケル膜およびキャップ膜であるチタン・ナイトライド膜をスパッタリングにより、ほぼ全面に形成する(図2のニッケル膜等形成工程202)。その後、ウエハ上面1aを摂氏300度前後の温度でアニール処理(非酸化性雰囲気中)することにより、ニッケル膜とウエハ上面1a部分のシリコンを反応させて、ニッケル・シリサイドを形成する(図2の第1アニール工程203)。その後、ウエット・エッチングにより(エッチング液は、たとえば硫酸、過酸化水素水の混合液)、未反応のニッケル膜およびチタン・ナイトライド膜を除去する(図2の不要ニッケル膜除去工程204)。その後、再び、ウエハ上面1aを摂氏500度前後の温度でアニール処理(非酸化性雰囲気中)することにより、シリサイド反応を進行させる(図2の第2アニール工程205)。これにより、図3に示すように、n型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)およびゲート・ポリシリコン膜8の上部にシリサイド層7(ニッケル・シリサイド層7a)が形成される。これにより、ゲート酸化膜9、ゲート・ポリシリコン膜8、サイド・ウォール・スペーサ絶縁膜10、およびゲート・ポリシリコン上シリサイド層7等から構成されるゲート構造18が形成される。

【0081】

次に、図4に示すように、ゲート構造18上を含むウエハ1の上面1aのほぼ全面に、たとえば30nm程度の厚さの窒化シリコン膜4をCVDにより成膜する(図2の窒化シリコン膜形成工程206)。その上に更に、オゾンおよびTEOSを用いた熱CVDによる酸化シリコン膜5a(第1の酸化シリコン膜)をたとえば厚さ200nm程度、ゲート構造18間が埋まるように成膜する(図2のオゾンTEOS膜形成工程207)。ここで、成膜条件は、たとえば処理室内気圧は2kPaから80kPa、成膜温度(ウエハ・ステージの設定温度)は摂氏400度から550度程度、ガス流量は、TEOS/O3/He=1000から5000mgm/10000から30000sccm/10000から30000sccm等である。

【0082】

次に、図5に示すように、酸化シリコン膜5aを選択的にエッチ・バックする(ガス雰囲気はフルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガス雰囲気で、流量は、たとえば、C4F6,O2,Ar=18/11/1100sccm、気圧4Pa、処理時間30秒)ことにより、ゲート構造18の上部の窒化シリコン膜4を露出させる(図2のエッチ・バック工程208)。なお、エッチ・バックは前記のように、ドライ・エッチングで簡易に処理することができるが、下地との選択比を更にあげたい場合は、緩衝弗酸水溶液(HF,NH4F,H2O混合液)等のシリコン酸化膜エッチング用ウエット・エッチ液によるウエット・エッチングによってもよい。また、ドライ・エッチング(前半)とウエット・エッチング(後半)を併用してもよい。

【0083】

次に、図6に示すように、酸化シリコン膜5a上およびゲート構造18の上部の窒化シリコン膜4上に、TEOSを用いたプラズマCVDによる酸化シリコン膜5b(第2の酸化シリコン膜)をたとえば厚さ550nm程度、成膜する(図2のプラズマTEOS膜形成工程209)。ここで、成膜条件は、たとえば処理室内気圧は300から1100Pa、成膜温度(ウエハ・ステージの設定温度)は摂氏370から400度程度、ガス流量は、TEOS/O2=200から1500sccm/0.5から3.0slm、高周波電力(13.56MHz:500から1500W,400から430KHz:250から600W)等である。酸化シリコン膜5bは下地の酸化シリコン膜5aとともに、プリ・メタル層間絶縁膜5を構成している。

【0084】

次に、図7および図8に示すように、CMP処理(第1の化学機械研磨)により(たとえば、第1の化学機械研磨により除去する下限面Z1まで研磨除去する)、酸化シリコン膜5bをたとえば280nm程度研磨することによって平坦化する(図2の酸化膜CMP工程210)。このとき、スラリの組成は、たとえばヒュームド・シリカ砥粒12重量%、アンモニア、分散剤等を添加、pHは10.9程度である。

【0085】

次に、図9に示すように、酸化シリコン膜5b上に、キャップ膜としてTEOSを用いたプラズマCVDによる酸化シリコン膜5cを100nm程度の厚さで成膜する(図2のキャップ膜形成工程216)。この酸化シリコン膜5cも、この時点ではプリ・メタル層間絶縁膜5の一部を構成している。キャップ膜としては、TEOSを用いたプラズマCVDによる酸化シリコン膜だけでなく、その他のCVDまたは塗布によるシリコン酸化物ベースの絶縁膜が利用できる。

【0086】

次に、この酸化シリコン膜5c上に、コンタクト・ホール開口のためのレジスト膜パターンを通常のリソグラフィにより形成する。そのレジスト膜パターンをマスクとして、たとえばCF4,C2F6,C4F8,C5F8フルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガスを用いた異方性ドライ・エッチングにより、窒化シリコン膜4をエッチ・ストップ膜として、図10に示すようにコンタクト・ホール12を開口する。続いて、図11に示すように、たとえばCF4,CHF3等のフルオロ・カーボン・ガス、酸素ガス、およびアルゴン・ガス等の混合ガスを用いた孔底の窒化シリコン膜4を除去して、コンタクト・ホール12をシリサイド層7まで延長する。その後、不要なレジスト膜パターンを除去する(図2のコンタクト開口工程211)。

【0087】

次に、図12に示すように、酸化シリコン膜5cの上面、およびコンタクト・ホール12内面に、たとえばTiCl4をメタル・ソース・ガスとして用いたメタルCVD処理により、バリア・メタル11として、チタン膜および窒化チタン膜を順次成膜する(図2のバリア・メタル膜形成工程212)。なお、バリア・メタル11の形成方法については、被覆性等の問題がないのであれば、メタルCVD処理のほか、スパッタリング成膜、またはメタルCVD処理とスパッタリング成膜の組み合わせ等の方法が適用できる(セクション3でも同じ)。

【0088】

次に、図13及び図14に示すように、バリア・メタル11上に、たとえばWF6をメタル・ソース・ガスとして用いたメタルCVD処理により、コンタクト・ホール12をタングステンにより、埋め込むようにタングステン層3を形成する(図2のタングステン膜形成工程213)。次に、メタルCMP処理(第2の化学機械研磨)により、コンタクト・ホール12外部のバリア・メタル11を除去するとともに、プリ・メタル層間絶縁膜5の上部を前記メタルCMP処理の延長として(たとえば、第2の化学機械研磨により除去する下限面Z2まで除去する。通常、酸化シリコン膜5cはこの処理でほぼ完全に除去される。しかし、必要に応じて酸化シリコン膜5cを残存させてもよい。セクション3でも同じ)除去する(図2のタングステンCMP工程214)。スラリ組成は、たとえばアルミナ砥粒5重量%、Fe(NO3)3等添加、pHは4程度である。これにより、図14に示すように、タングステン・プラグ3が完成する。以後は、セクション1の第1配線層M1の形成工程に移る。

【0089】

3.本願のその他の実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(コバルト・シリサイド・プロセス)の説明(主に図15から図26)

図15は本願発明のその他の実施の形態の半導体集積回路装置の製造方法(コバルト・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。なお、本願のその他の実施形態の半導体集積回路装置の製造方法によるプロセス・フロー(コバルト・シリサイド・プロセス)の説明においては、前述のニッケル・シリサイド・プロセスにて使用した図2から図14を代用して説明するが、重複する部分は説明を繰り返さない。n型ソース・ドレイン不純物領域6等の形成までは、セクション2とほぼ同一であり、説明を繰り返さない。

【0090】

図15および図3に示すように、半導体基板(ウエハ)の上面1aのシリコン酸化膜を除去し、基板上面1aを露出させる。その状態で、コバルト膜およびキャップ膜であるチタン・ナイトライド膜をスパッタリングにより、ほぼ全面に形成する(図15のコバルト膜等形成工程202)。その後、ウエハ上面1aを摂氏450度前後の温度でアニール処理(非酸化性雰囲気中)することにより、コバルト膜とウエハ上面1a部分のシリコンを反応させて、コバルト・シリサイドを形成する(図15の第1アニール工程203)。その後、ウエット・エッチング(エッチング液は、たとえば塩酸と過酸化水素水の混合液)により、未反応のコバルト膜およびチタン・ナイトライド膜を除去する(図15の不要コバルト膜除去工程204)。その後、再び、ウエハ上面1aを摂氏740度前後の温度でアニール処理(非酸化性雰囲気中)することにより、シリサイド反応を進行させる(図15の第2アニール工程205)。これにより、図3に示すように、n型ソース・ドレイン不純物領域6(p型ソース・ドレイン不純物領域についても同様である)およびゲート・ポリシリコン膜8の上部にシリサイド層7(コバルト・シリサイド層7b)が形成される。これにより、ゲート酸化膜9、ゲート・ポリシリコン膜8、サイド・ウォール・スペーサ絶縁膜10、およびゲート・ポリシリコン上シリサイド層7等から構成されるゲート構造18が形成される。

【0091】

次に、図15の窒化シリコン膜形成工程206およびオゾンTEOS膜形成工程207における処理を行うが、この処理は前述したニッケル・シリサイド・プロセスの工程206および工程207と同様なため、詳細説明は省略する。

【0092】

次に、酸化シリコン膜5aに対して、摂氏750度程度の温度でアニール処理(リフローによる平坦化および膜硬度の向上を図る)を施す(図15のオゾンTEOSアニール工程215)。この処理により、ニッケル・シリサイド・プロセスに比較して、コバルト・シリサイド・プロセスでは、酸化シリコン膜5a(オゾンTEOS膜)の硬度は若干高くなっている。一方、ニッケル・シリサイド・プロセスにおいては、ニッケル・シリサイドの特性上の制約があり、シリサイド形成後は、せいぜい摂氏550度程度の温度でしか、熱処理をすることができないため、アニールによって、酸化シリコン膜5a(オゾンTEOS膜)の硬度を上げることができない。

【0093】

次に、図15のエッチ・バック工程208、プラズマTEOS膜形成工程209、酸化膜CMP工程210、キャップ膜形成工程216、コンタクト開口工程211、バリア・メタル膜形成工程212、タングステン膜形成工程213、タングステンCMP工程214の処理を行うが、これらについては、図2で説明したニッケル・シリサイド・プロセスの工程208から工程210、工程216、工程211から工程214と重複するため、ここでは詳細な説明を省略する。

【0094】

4.本願の実施形態の半導体集積回路装置の製造方法に使用する各種CVD装置、膜特性、およびプリ・メタル・プロセスに関する詳細の説明(主に図16から図18)

このセクションでは、セクション2または3で使用する酸化シリコン膜(オゾンTEOS膜5a、プラズマTEOS膜5b、キャップ・プラズマTEOS膜5c)の成膜装置、成膜プロセスおよびそれによって生成された膜特性について説明する。

【0095】

図16はCVD酸化シリコン膜の硬度、ヤング率、およびそれらのアニール温度依存性を示すデータ・プロット図である。図17は本願発明の実施の形態の半導体集積回路装置の製造方法に使用するオゾンおよびTEOSを用いるコールド・ウォール方式の枚葉式熱CVD装置の模式断面図である。図18は本願発明の実施の形態の半導体集積回路装置の製造方法に使用するTEOSを用いる枚葉式プラズマCVD装置の模式断面図である。これらに基づいて、本願の実施形態の半導体集積回路装置の製造方法に使用する各種CVD装置、膜特性、およびプリ・メタル・プロセスに関する詳細を説明する。

【0096】

まず、オゾンTEOS膜5aの成膜のための準常圧成膜装置150(コールド・ウォール型枚葉装置)について説明する。図17に示すように、この装置は熱CVD装置で、チャンバ151は被処理ウエハ1を載置するウエハ・ステージ152、およびシャワー・ヘッド156等を有しており、枚葉方式の反応炉となっている。ウエハ1はウエハ・ステージ152上に、デバイス面1aを上にして、設置される。加熱はウエハ・ステージ152に内蔵された加熱機構(抵抗加熱方式)による。この加熱機構はウエハ1の処理時は摂氏400から550度程度(ウエハ処理温度)に設定されている。一方、チャンバ壁162は、所定の温度に冷却されている。成膜時には、チャンバ151内部は2KPaから80KPa程度の真空度になるように、排気されている。オゾンおよびTEOSを含んだヘリウム・ガス(キャリア・ガス)はガス導入管155から導入され、真空排気系154から排気される。

【0097】

次に、プラズマTEOS酸化シリコン膜5b(第2の酸化シリコン膜)およびキャップ・プラズマTEOS酸化シリコン膜(第3の酸化シリコン膜)の成膜のための成膜装置161(枚葉プラズマCVD装置)について説明する。図18に示すように、この装置ではチャンバ151内の下部電極159(接地電極)が加熱機構を内蔵するとともに、ウエハ・ステージを兼ねている。一方、上部電極160は、ガス供給管155およびシャワー・ヘッド156とともにガス供給機構を兼ねている。上部電極160には、高周波電源157からマッチング回路158を介して、高周波電力(13.56MHz,400から430kHz)が供給される。成膜時は、被処理ウエハ1はデバイス面1aを上にして、下部電極159上に設置される。チャンバ151内は、成膜時には排気系154により、300から1100Pa程度の真空度に保持される。また、チャンバ壁162の温度は所定の温度に保たれている。一方、ウエハ・ステージ159は加熱機構により、摂氏370から400度程度(ウエハ処理温度)に設定されている。

【0098】

次に、これらの装置で形成されたオゾンTEOS膜5aおよびプラズマTEOS膜5bの機械的特性について説明する。図16に示すように、成膜してアニールしない状態のオゾンTEOS膜5aは、ヤング率および硬度ともに、比較的低い値を示す。しかし、摂氏750度以上でアニールすると、急速に硬化して、比較的高めのヤング率および硬度を示すようになる。

【0099】

一方、プラズマTEOS膜5b、成膜してアニールしない状態でも、アニール後のオゾンTEOS膜5aと同等か、またはそれよりも高いヤング率および硬度を示す。これは、プラズマの励起作用により、実効的な反応温度がより高くなっているためと考えられる。

【0100】

現在のプリ・メタル絶縁膜5は、ゲート構造18間のピッチの狭小化およびアスペクト・レシオの増大により、より高度のギャップ・フィル(Gap Fill)特性が求められている。しかし、パターンの微細化に伴い、コバルト・シリサイド・プロセスにおいては、シリコン酸化膜アニール温度の低温化が必要になっており、ニッケル・シリサイド・プロセスにおいては、シリサイド形成後は摂氏550度を超える高温処理が困難なため、シリコン酸化膜アニールの省略が不可避となっている。

【0101】

ここで、本願発明者らが行った解析結果によると、図4の状態でゲート構造18上のオゾンTEOS膜5aが薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5bとの界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12の開口時に再びコンタクト・ホール12内に露出し、そこへバリア・メタル11が入り込む結果、近接したコンタクト・ホール12間でショート不良が発生する。

【0102】

これを防ぐには、オゾンTEOS膜5aに対して、図16に示すように摂氏850度程度で十分に、アニール処理を施すとよいが、前に説明したようなプロセスの低温化は不可避であり、高温アニールを実施することができない。

【0103】

そこで、図4の状態の後、図5に示すように、一度、オゾンTEOS膜5aを、ゲート構造18上のエッチ・ストップ膜4が露出するように、エッチ・バックし、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5bを成膜するようにした。窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5bの界面に応力が集中することもない。プラズマTEOS膜5bは、硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0104】

なお、オゾンTEOS膜5aの代わりに、モノシラン等のガス系を用いたHDP−CVDによる酸化シリコン膜を用いることも考えられる。しかし、HDP−CVDによる酸化シリコン膜は、成膜したそのままの状態でも比較的ヤング率および硬度が高いが、膜のストレスが高く、トランジスタ特性に十分配慮する必要がある。この場合、ヤング率および硬度が高いので、クラックの発生の恐れがないので、エッチ・バックの必要性は比較的低いとも考えられる。また、HDP−CVDによる酸化シリコン膜を使用する場合は、オゾンTEOS膜5aおよびプラズマTEOS膜5bの両方をHDP−CVDによる酸化シリコン膜として、ワン・ステップで成膜した後、酸化膜CMP処理し、キャップ膜としてプラズマTEOS酸化シリコン膜その他のCVD酸化シリコン膜を使用する方が効率的な場合もある。

【0105】

5.その他の実施形態

その他の実施形態として、以下の(1)〜(20)項に示す実施形態についても明示される。

【0106】

(1)以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をニッケル・シリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜とからなるプリ・メタル層間絶縁膜を形成する工程;

(f)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程;

とを備え、

前記工程(e)では、以下の工程を更に含む;

(e−1)前記第1の酸化シリコン膜を摂氏400〜550度の温度での熱CVDにより形成する工程、

(e−2)前記第2の酸化シリコン膜をプラズマCVDにより形成する工程。

【0107】

(2)前記(1)項の半導体集積回路装置の製造方法において、

前記工程(e−1)と工程(e−2)との間には、前記第1の酸化シリコン膜に対する摂氏550度を超える温度でのアニール処理は実行されない。

【0108】

(3)前記(1)または(2)項の半導体集積回路装置の製造方法において、

前記工程(e−1)では、オゾンおよびTEOSを用いた熱CVDにより前記第1の酸化シリコン膜を形成し、

前記工程(e−2)では、TEOSを用いたプラズマCVDにより前記第2の酸化シリコン膜を形成する。

【0109】

ここで、前述したようにニッケル・シリサイド・プロセスにおいては、ニッケル・シリサイド膜の特性上の制約から摂氏550度を超える温度での熱処理(アニール)をすることができない。また、図27に示されるように、摂氏550度以下で生成したオゾンTEOS膜の硬度は低いため、このオゾンTEOS膜をCMPにて研摩するとオゾンTEOS膜にクラックが発生する等の問題が生じる。よって、上述した(1)〜(3)の実施形態では、膜の硬度が低いオゾンTEOS膜の上面に硬度が高いプラズマTEOS膜を形成し、プラズマTEOS膜をCMPにて研摩処理を行うため、クラック等の発生が抑制された層間絶縁膜を形成することが可能となる。

【0110】

(4)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ゲート構造体の上面および前記ソース・ドレイン領域の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(d)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であり、熱CVD法により形成された第1の酸化シリコン膜であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を露出するように形成された前記第1の酸化シリコン膜;

(e)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、プラズマCVD法により形成された第2の酸化シリコン膜;

(f)前記ソース・ドレイン領域と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0111】

(5)前記(4)項の半導体集積回路装置において、前記半導体ウエハの第1の主面上には、STI構造の素子分離フィールド絶縁膜が更に形成され、前記エッチ・ストッパ膜は前記素子分離フィールド絶縁膜の上面をも含み形成されている。

【0112】

(6)前記(4)または(5)項の半導体集積回路装置において、前記接続孔と前記ソース・ドレイン領域とは、シリサイド膜を介して電気的に接続されている。

【0113】

(7)前記(6)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0114】

(8)前記(6)項の半導体集積回路装置において、前記シリサイド膜はコバルト・シリサイド膜である。

【0115】

(9)前記(4)から(8)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0116】

(10)前記(7)項の半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0117】

(11)前記(4)から(10)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0118】

ここで、前述したように、図4の状態でゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)が薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)との界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12(接続孔)の開口時に再びコンタクト・ホール12内に露出し、そこへプラグを構成するバリア・メタル11が入り込む結果、近接したコンタクトプラグ間でショート不良が発生する。

【0119】

そこで、ゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)をエッチ・バックし、エッチ・ストップ膜4を露出する構造とする。そして、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)を堆積する構造とした。ゲート構造体上部のプラズマTEOS膜(第2の酸化シリコン膜)の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、エッチ・ストップ膜である窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5b(第2の酸化シリコン膜)の界面に応力が集中することもない。なお、プラズマTEOS膜5bは、膜の硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0120】

よって、上述した(4)〜(11)の実施の形態に示される半導体集積回路装置の構造を採用することで、CMPによる応力集中から生じるクラックの発生が抑制でき、更にはコンタクト・ホール12(接続孔)のショート不良の発生が抑制できる。

【0121】

(12)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記ソース・ドレイン領域の前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成された第1の酸化シリコン膜;

(f)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成された第2の酸化シリコン膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【0122】

(13)前記(12)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0123】

(14)前記(12)から(13)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0124】

(15)前記(12)から(14)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0125】

(16)前記(12)から(15)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0126】

(17)以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ソース・ドレイン領域の上面に形成されたシリサイド膜;

(d)前記ゲート構造体の上面および前記シリサイド膜の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(e)少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜から構成され、前記各ゲート構造体間に埋め込まれる層間絶縁膜;

(g)前記ソース・ドレイン領域の上面に形成された前記シリサイド膜と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔;

を備え、

前記第1の酸化シリコン膜は、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を覆わないように形成され、

前記第2の酸化シリコン膜は、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、

前記第1の酸化シリコン膜の膜硬度は、前記第2の酸化シリコン膜の膜硬度よりも低い。

【0127】

(18)前記(17)項の半導体集積回路装置において、前記シリサイド膜はニッケル・シリサイド膜である。

【0128】

(19)前記(17)または(18)項の半導体集積回路装置において、前記第1の酸化シリコン膜はオゾンおよびTEOSを用いて、摂氏400〜550度の温度での熱CVD法により形成された膜である。

【0129】

(20)前記(17)から(19)項のいずれか一つの半導体集積回路装置において、前記第1の酸化シリコン膜は、摂氏550度を超える温度でのアニール処理が施されていない膜である。

【0130】

ここで、前述したように、図4の状態でゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)が薄くなると(前記オゾンTEOS膜は低温で形成されるため、硬度が低い膜となる)、CMP処理の際、その上のプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)との界面に応力が集中し、クラックが発生することが明らかとなった。そして、このクラックは、キャップ膜5cによって、一度、覆われるが、コンタクト・ホール12(接続孔)の開口時に再びコンタクト・ホール12内に露出し、そこへプラグを構成するバリア・メタル11が入り込む結果、近接したコンタクトプラグ間でショート不良が発生する。

【0131】

これを防ぐには、オゾンTEOS膜5aに対して、図27に示すように摂氏850度程度で十分に、アニール処理を施すとよいが、前に説明したようなシリサイド・プロセスの低温化は不可避であり、高温アニールを実施することができない。

【0132】

そこで、ゲート構造18上(ゲート構造体)のオゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)をエッチ・バックし、前記第1の酸化シリコン膜が前記エッチ・ストップ膜4を覆わない構造とする。そして、その上に、成膜したそのままの状態でも比較的ヤング率および硬度が高いプラズマTEOS酸化シリコン膜5b(プラズマCVD法により形成した第2の酸化シリコン膜)を堆積する構造とした。ゲート構造体上部のプラズマTEOS膜(第2の酸化シリコン膜)の下地が比較的硬いエッチ・ストップ膜となるため、CMP応力の集中を回避することができる。即ち、エッチ・ストップ膜である窒化シリコン膜4は、もともと、硬い膜であるから、窒化シリコン膜4とプラズマTEOS膜5b(第2の酸化シリコン膜)の界面に応力が集中することもない。なお、プラズマTEOS膜5b(熱CVD法により形成した第1の酸化シリコン膜)は、オゾンTEOS膜5a(熱CVD法により形成した第1の酸化シリコン膜)よりも膜の硬度が高いため、その後のCMP処理に関しても、比較的良好なスクラッチ耐性を示す。

【0133】

よって、上述した(12)〜(20)の実施の形態に示される半導体集積回路装置の構造を採用することで、CMPによる応力集中から生じるクラックの発生が抑制でき、更にはコンタクト・ホール12(接続孔)のショート不良の発生が抑制できる。

【0134】

なお、上記(1)〜(20)に示す実施形態は、この明細書にて記載された他の効果を排除するものではなく、相乗的に奏するものであることは言うまでもない。

【0135】

6.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0136】

例えば、前記各実施の形態では、バック・エンド・プロセスについては、銅ダマシン配線を主とする構成について具体的に説明したが、本発明はそれに限定されるものではなく、銀等のダマシン配線をバック・エンド・プロセスに適用したもの、および、アルミニウム系の配線をバック・エンド・プロセスに使用したものにも適用できることは言うまでもない。

【0137】

また、前記各実施の形態では、CVD装置について、枚葉装置について具体的に説明したが、本発明はそれに限定されるものではなく、バッチ式装置やミニ・バッチ式装置を用いたプロセスにも適用できることは言うまでもない。

【0138】

また、オゾンTEOS−熱CVD装置に関して、準常圧装置について具体的に説明したが、常圧装置を用いたプロセスでもよいことは言うまでもない。

【0139】

更に、オゾンTEOS膜またはプラズマTEOS膜は、不純物ドープの面から言って、デバイス設計の必要に応じて、非ドープ酸化シリコン膜であってもよいし、燐、ボロンその他の不純物を添加した酸化シリコン系の絶縁膜でもよい。

【図面の簡単な説明】

【0140】

【図1】本願発明の実施の形態の半導体集積回路装置の製造方法によるデバイスの断面構造の一例を示すデバイス断面図である。

【図2】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。

【図3】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(ソース・ドレイン領域およびゲート電極上面シリサイド化工程)である。

【図4】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOS膜成膜工程)である。

【図5】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(オゾンTEOSエッチ・バック工程)である。

【図6】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜成膜工程)である。

【図7】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程開始時点)である。

【図8】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(プラズマTEOS膜CMP工程終了時点)である。

【図9】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(キャップ・プラズマTEOS膜成膜工程)である。

【図10】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール形成工程)である。

【図11】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(コンタクト・ホール底のエッチ・ストップ膜除去工程)である。

【図12】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(バリア・メタル膜成膜工程)である。

【図13】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステン膜成膜工程)である。

【図14】本願発明の一実施の形態の半導体集積回路装置の製造方法(ニッケル・シリサイド・プロセス)におけるプロセス断面フロー図(タングステンCMP工程終了時点)である。

【図15】本願発明のその他の実施の形態の半導体集積回路装置の製造方法(コバルト・シリサイド・プロセス)におけるプロセス・ブロック・フロー図である。

【図16】CVD酸化シリコン膜の硬度、ヤング率、およびそれらのアニール温度依存性を示すデータ・プロット図である。

【図17】本願発明の実施の形態の半導体集積回路装置の製造方法に使用するオゾンおよびTEOSを用いるコールド・ウォール方式の枚葉式熱CVD装置の模式断面図である。

【図18】本願発明の実施の形態の半導体集積回路装置の製造方法に使用するTEOSを用いる枚葉式プラズマCVD装置の模式断面図である。

【符号の説明】

【0141】

1 P型単結晶シリコン基板(半導体ウエハ)

1a 基板又はウエハのデバイス面(第1の主面)

1b 基板又はウエハの裏面(第2の主面)

2 素子分離フィールド絶縁膜

3 タングステン・プラグ

4 窒化シリコン・ライナー膜(エッチ・ストップ膜)

5 プリ・メタル層間絶縁膜

5a (プリ・メタル層間絶縁膜の内の)オゾンTEOS酸化シリコン膜(第1の酸化シリコン膜)

5b (プリ・メタル層間絶縁膜の内の)プラズマTEOS酸化シリコン膜(第2の酸化シリコン膜)

5c (プリ・メタル層間絶縁膜の内の)キャップ・プラズマTEOS酸化シリコン膜(第3の酸化シリコン膜)

6 n型ソース・ドレイン不純物領域

7 シリサイド層

7a ニッケル・シリサイド層

7b コバルト・シリサイド層

8 ゲート電極(ポリシリコン膜)

9 ゲート絶縁膜

10 サイド・ウォール絶縁膜

11 バリア・メタル膜

12 コンタクト・ホール

13 埋め込まれた銅配線

14 絶縁性バリア膜

15 プラズマシリコン酸化膜

18 ゲート構造

23 銅埋め込み配線

24 絶縁性バリア膜

25 主層間絶縁膜

33 銅埋め込み配線

34 絶縁性バリア膜

35 主層間絶縁膜

43 銅埋め込み配線

44 絶縁性バリア膜

45 主層間絶縁膜

53 銅埋め込み配線

54 絶縁性バリア膜

55 主層間絶縁膜

63 銅埋め込み配線

64 絶縁性バリア膜

65 主層間絶縁膜

73 銅埋め込み配線

74 絶縁性バリア膜

75 主層間絶縁膜

83 銅埋め込み配線

84 絶縁性バリア膜

85 主層間絶縁膜

93 銅埋め込み配線

94a 絶縁性バリア膜

94b 絶縁性バリア膜

95a FSG膜

95b FSG膜

96a USG膜

96b USG膜

103 銅埋め込み配線

104a 絶縁性バリア膜

104b 絶縁性バリア膜

105a FSG膜

105b FSG膜

106a USG膜

106b USG膜

113 タングステン・プラグ

114 SiCN膜

117 USG膜

118 アルミニウム配線

119 プラズマSiN

150 準常圧熱CVD装置

151 処理チャンバ

152 ウエハ・ステージ

154 真空排気系

155 ガス供給系

156 シャワー・ヘッド

157 高周波電源

158 マッチング機構

159 下部電極(ウエハ・ステージ)

160 上部電極

161 プラズマCVD装置

162 チャンバ壁

201 ゲート電極形成

202 シリサイド形成用メタル膜等形成

203 シリサイド化のための第1アニール

204 余剰シリサイド形成用メタル膜等除去

205 シリサイド化のための第2アニール

206 エッチ・ストップのための窒化シリコン膜形成

207 オゾンTEOSによる酸化シリコン膜形成

208 エッチ・バック処理

209 プラズマTEOSによる酸化シリコン膜形成

210 化学機械研磨による平坦化処理

211 コンタクト・ホール開口

212 バリア・メタル膜形成

213 プラグ用タングステン膜形成

214 メタルCMP処理

215 オゾンTEOS膜アニール処理

216 キャップ膜形成

AP 最上層配線層

M1 第1配線層

M2 第2配線層

M3 第3配線層

M4 第4配線層

M5 第5配線層

M6 第6配線層

M7 第7配線層

M8 第8配線層

M9 第9配線層

M10 第10配線層

PM プリ・メタル領域

Z1 第1の化学機械研磨により除去する下限面

Z2 第2の化学機械研磨により除去する下限面

【特許請求の範囲】

【請求項1】

以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をシリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、プリ・メタル層間絶縁膜の一部であり、オゾンおよびTEOSを用いた熱CVDによる第1の酸化シリコン膜を形成する工程;

(f)前記第1の酸化シリコン膜をエッチングすることにより、各ゲート構造上において前記エッチ・ストップ膜を露出させる工程;

(g)前記工程(f)の後、前記エッチ・ストップ膜の露出された部分及び前記第1のCVD酸化シリコン膜の残存した部分に、前記プリ・メタル層間絶縁膜の一部であり、TEOSを用いたプラズマCVDによる第2の酸化シリコン膜を形成する工程;

(h)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程。

【請求項2】

前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程。

【請求項3】

前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去する工程。

【請求項4】

前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(j)前記工程(h)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【請求項5】

前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(i)前記工程(h)の後、前記第2の酸化シリコン膜上に、前記プリ・メタル層間絶縁膜の一部である第3の酸化シリコン膜を形成する工程;

(j)前記工程(i)の後、前記エッチ・ストップ膜を利用して、ドライ・エッチングにより前記プリ・メタル層間絶縁膜にコンタクト・ホールを開口する工程;

(k)前記工程(j)の後、前記コンタクト・ホールの孔底の、前記エッチ・ストップ膜を除去することにより前記コンタクト・ホールを延長する工程;

(l)前記工程(k)の後、前記コンタクト・ホールの内面および前記プリ・メタル層間絶縁膜の上面に、バリア・メタル膜を形成する工程;

(m)前記工程(l)の後、前記バリア・メタル膜上に、前記コンタクト・ホールを埋めるように、タングステンを主要な成分とする金属部材層を形成する工程;

(n)前記工程(m)の後、第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程。

【請求項6】

前記5項の半導体集積回路装置の製造方法において、前記工程(n)は、以下の下位工程を含む:

(n1)前記第2の化学機械研磨処理を実施することにより、前記コンタクト・ホール外の前記金属部材層および前記バリア・メタル膜を除去する工程;

(n2)前記第2の化学機械研磨処理を実施することにより、前記第3の酸化シリコン膜を除去する工程。

【請求項7】

前記1項の半導体集積回路装置の製造方法において、前記工程(a)および(b)は、相前後して又は一部並行して実行される。

【請求項8】

前記1項の半導体集積回路装置の製造方法において、前記エッチ・ストップ膜は、窒化シリコン膜である。

【請求項9】

前記1項の半導体集積回路装置の製造方法において、前記工程(c)は、ニッケルのシリサイド化工程である。

【請求項10】

前記9項の半導体集積回路装置の製造方法において、前記工程(e)の後、前記第1の酸化シリコン膜のアニール処理を施すことなく前記工程(f)が実行される。

【請求項11】

前記1項の半導体集積回路装置の製造方法において、前記工程(c)は、コバルトのシリサイド化工程または、低次のコバルト・シリサイドのより高次のシリサイド化工程である。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、

(o)前記工程(e)の後、(f)の前に、摂氏700度から750度の温度で前記半導体ウエハの前記第1の主面側をアニール処理する工程。

【請求項13】

前記1項の半導体集積回路装置の製造方法において、前記エッチ・ストップ膜の成膜完了時の膜厚は、前記第1の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【請求項14】

前記1項の半導体集積回路装置の製造方法において、前記第1の酸化シリコン膜の成膜完了時の膜厚は、前記第2の酸化シリコン膜の成膜完了時の膜厚よりも薄い。

【請求項15】

前記1項の半導体集積回路装置の製造方法において、前記工程(h)開始時点における前記第1の酸化シリコン膜の破壊靭性は、前記工程(h)開始時点における前記第2の酸化シリコン膜の破壊靭性よりも小さい。

【請求項16】

前記1項の半導体集積回路装置の製造方法において、前記工程(f)は、ドライ・エッチングによって実行される。

【請求項17】

前記1項の半導体集積回路装置の製造方法において、前記工程(f)は、ウエット・エッチングによって実行される。

【請求項18】

前記1項の半導体集積回路装置の製造方法において、前記工程(e)は、準常圧CVDによって行われる。

【請求項19】

前記1項の半導体集積回路装置の製造方法において、前記工程(e)は、摂氏400度から550度の間に設定されたウエハ・ステージ上にウエハを設置した状態で実行される。

【請求項20】

前記4項の半導体集積回路装置の製造方法において、前記バリア・メタル膜は、下層のチタンを主要な成分とする膜と、上層の窒化チタンを主要な成分とする膜とを含む。

【請求項21】

前記2項の半導体集積回路装置の製造方法において、前記第3の酸化シリコン膜は、TEOSを用いたプラズマCVDによる酸化シリコン膜である。

【請求項22】

以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体ウエハの第1の主面上に、ポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造を形成する工程;

(b)前記半導体ウエハの第1の主面の各ゲート構造の両側近傍に、ソース・ドレイン領域を形成する工程;

(c)前記工程(a)および(b)の後、前記ソース・ドレイン領域の上面をニッケル・シリサイド化する工程;

(d)前記シリサイド化された前記ソース・ドレイン領域の前記上面を含む前記半導体ウエハの前記第1の主面上に、エッチ・ストップ膜を形成する工程;

(e)前記エッチ・ストップ膜上に、少なくとも第1の酸化シリコン膜と第2の酸化シリコン膜とからなるプリ・メタル層間絶縁膜を形成する工程;

(f)前記第2の酸化シリコン膜の上面に対して、第1の化学機械研磨処理を実施する工程;

とを備え、

前記工程(e)では、以下の工程を更に含む;

(e−1)前記第1の酸化シリコン膜を摂氏400〜550度の温度での熱CVDにより形成する工程、

(e−2)前記第2の酸化シリコン膜をプラズマCVDにより形成する工程。

【請求項23】

前記22項の半導体集積回路装置の製造方法において、

前記工程(e−1)と工程(e−2)との間には、前記第1の酸化シリコン膜に対する摂氏550度を超える温度でのアニール処理は実行されない。

【請求項24】

前記22項の半導体集積回路装置の製造方法において、

前記工程(e−1)では、オゾンおよびTEOSを用いた熱CVDにより前記第1の酸化シリコン膜を形成し、

前記工程(e−2)では、TEOSを用いたプラズマCVDにより前記第2の酸化シリコン膜を形成する。

【請求項25】

以下を含む半導体集積回路装置:

(a)半導体ウエハの第1の主面上に形成されたポリ・シリコン・ゲート電極を含む複数のMISFETのゲート構造体;

(b)前記半導体ウエハの第1の主面の前記ゲート構造体の両側近傍に形成されたソース・ドレイン領域;

(c)前記ゲート構造体の上面および前記ソース・ドレイン領域の上面を含む前記半導体ウエハの前記第1の主面上に形成されたエッチ・ストップ膜;

(d)前記各ゲート構造体間に埋め込まれる層間絶縁膜の一部であり、熱CVD法により形成された第1の酸化シリコン膜であって、前記ゲート構造体の上面に形成された前記エッチ・ストップ膜を露出するように形成された前記第1の酸化シリコン膜;

(e)前記層間絶縁膜の一部であって、前記第1の酸化シリコン膜および前記ゲート構造体の上面に形成された前記エッチ・ストップ膜の上に形成され、プラズマCVD法により形成された第2の酸化シリコン膜;

(f)前記ソース・ドレイン領域と前記層間絶縁膜の上に形成された配線とを電気的に接続するプラグが埋め込まれる接続孔。

【請求項26】