半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置および遅延路の制御方法に係り、特に、2つの回路間で信号伝送を行う半導体集積回路装置およびそこに含まれる遅延路の制御方法に係る。

【背景技術】

【0002】

論理回路を半導体集積回路装置上に構成する場合、遅延時間に関して、最悪ケースでデバイスのばらつきも考慮し、セットアップ時間、ホールド時間の規定を満足するように設計が行なわれる。例えば、クロック信号に同期して動作する2つの同期動作回路の間では、CMOS回路におけるトランジスタサイズ、閾値電圧、ゲート種類、ゲート段数等を変更して適切な遅延時間を有する回路が挿入され、ホールド時間の規定を満足するように構成される。

【0003】

2つの同期動作回路間に挿入される遅延回路としては、例えば、通常のCMOS回路や非特許文献1に記載されるようなDCVSL(Differential Cascode Voltage Switch Logic)を組み合わせて用いることで、安定した遅延時間を得ることができる。

【0004】

なお、関連する技術として、複数のデジタル処理回路のいずれかの系統で設定状態にずれが生じた場合に、正常系統のデジタル処理回路のいずれかを停止させても、多数決結果の正当性を確保し、正常動作に対する信頼性を維持する冗長回路装置が特許文献1に記載されている。

【0005】

【非特許文献1】Kan M. Chu and David L. Pulfrey,”A Comparison of CMOS Circuit Techniques: Differential Cascode Voltage Switch Logic Versus Conventional Logic”,IEEE Journal of Solid-state Circuits, vol. SC-22, pp.528-532, August 1987

【特許文献1】特開2008−191939号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

以下の分析は本発明において与えられる。

【0007】

近年、半導体の微細化および低電圧化の進展に伴ってデバイスのばらつきおよび遅延のばらつきが増大している。このため、最悪ケースを想定した設計が徐々に困難となってきている。そこで、2つの同期動作回路間に複数の遅延回路を挿入した多重化設計が考えられる。例えば、特許文献1に記載したような多数決結果を適用するような多重化設計による半導体集積回路装置が考えられる。しかしながら、このような多重化設計による半導体集積回路装置では、多重化したハードウェアが動作し続けるために消費電力およびリーク電流が増大し、電力効率が低下してしまう虞がある。

【課題を解決するための手段】

【0008】

本発明の1つのアスペクト(側面)に係る半導体集積回路装置は、クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路と、複数の遅延路におけるそれぞれの遅延時間を検出する遅延検出部と、遅延検出部の検出結果に基づいて複数の遅延路の内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部と、を備える。

【0009】

本発明の他のアスペクト(側面)に係る遅延路の制御方法は、クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路の制御方法であって、複数の遅延路におけるそれぞれの遅延時間を検出するステップと、遅延時間の検出結果に基づいて複数の遅延路の内の一の遅延路を選択するステップと、選択された一の遅延路以外における信号伝送を阻止するように制御するステップと、を含む。

【発明の効果】

【0010】

本発明によれば、一の遅延路以外における信号伝送が阻止されるので、電力効率が向上する。

【発明を実施するための最良の形態】

【0011】

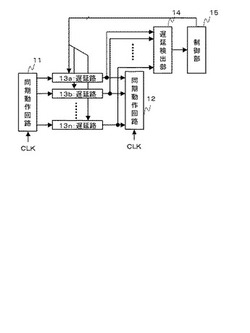

図1は、本発明の実施形態に係る半導体集積回路装置の構成を示す図である。図1において、半導体集積回路装置は、クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択された一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。このような半導体集積回路装置によれば、一の遅延路以外における信号伝送が阻止されるので、半導体集積回路装置における電力効率が向上する。

【0012】

複数の遅延路は、電源が供給されて動作する能動回路を含んでそれぞれ構成され、制御部は、通常動作時に一の遅延路以外における遅延路中の能動回路への電源供給を停止するようにしてもよい。

【0013】

能動回路は、組み合わせ論理回路として構成されてもよい。

【0014】

制御部は、複数の遅延路の内の遅延時間が最小値となる遅延路を一の遅延路として選択するようにしてもよい。このような制御によれば、デバイスのばらつきに起因する遅延の大きな遅延路を除外することで速度性能を向上することができる。

【0015】

また、制御部は、複数の遅延路の内の遅延時間が中央値となる遅延路を一の遅延路として選択するようにしてもよい。このような制御によれば、デバイスのばらつきに起因する遅延の小さな遅延路を除外することで高速の遅延路に予想される過大なリーク電流を削減することができる。

【0016】

さらに、制御部は、選択された一の遅延路における電源供給電圧を所定の電圧まで低下させるようにしてもよい。このような制御によれば、所望の性能まで電源電圧を下げることができ、電力効率が改善される。

【0017】

また、制御部は、複数の遅延路への電源供給電圧に対応させて一の遅延路を選択するようにしてもよい。このような制御によれば、電源電圧毎に適切な遅延路を選択することで充分な遅延マージンを確保することができる。

【0018】

遅延検出部は、複数の遅延路にそれぞれ対応させてラッチタイミングのそれぞれ異なる2つのレジスタを備え、制御部は、ラッチタイミングを変化させていった場合における2つのレジスタのラッチデータに基づいて得た複数の遅延路における遅延時間順に基づいて一の遅延路を選択するようにしてもよい。

【0019】

2つのレジスタの一方は、通常動作時にクロック信号のラッチタイミングで動作するようにしてもよい。

【0020】

遅延路は、相補的に動作する論理回路で構成され、遅延検出部による遅延時間検出時には相補的に動作するように機能するようにしてもよい。

【0021】

また、遅延路は、二線式論理回路で構成され、遅延検出部による遅延時間検出時に二線式論理回路として機能し、通常動作時に二線式論理回路または単線式論理回路として機能するようにしてもよい。このような二線式論理回路を用いることで、遅延検出を効率よく行うことができる。また、通常動作時に単線式論理回路として機能させるならば、消費電力が低減される。

【0022】

遅延検出部は、遅延時間検出時に二線式論理回路における論理値の変化順を検出するようにしてもよい。

【0023】

さらに、遅延路は、ダイナミック回路として構成され、遅延検出部による遅延時間検出時にダイナミック回路として機能し、通常動作時にスタティック回路として機能するようにしてもよい。このようなダイナミック回路を用いることで、遅延検出を効率よく行うことができる。また、通常動作時にスタティック回路として機能させるならば、消費電力が低減される。

【0024】

また、遅延路は、スタティック回路として構成され、遅延検出部による遅延時間検出時および通常動作時にスタティック回路として機能するようにしてもよい。

【0025】

以下、実施例に即し、図面を参照して半導体集積回路装置の各部について詳しく説明する。

【実施例1】

【0026】

図2は、本発明の第1の実施例に係る半導体集積回路装置の主要部の回路図である。図2において、組み合わせ論理回路21は、図1の遅延路13a、13b、・・13nの一つに相当する。フリップフロップ回路FF11は、遅延路にそれぞれ対応して設けられる同期動作回路11中の最終段のフリップフロップ回路であって、クロック信号CLKでラッチした信号を組み合わせ論理回路21に出力する。また、フリップフロップ回路FF12は、遅延路にそれぞれ対応して設けられる同期動作回路12中の初段のフリップフロップ回路であって、組み合わせ論理回路21の出力をクロック信号CLKでラッチする。遅延検出部14は、図1における一つの遅延路に対応してフリップフロップ回路FF13、排他的論理和回路XOR0を備える。

【0027】

フリップフロップ回路FF13は、組み合わせ論理回路21の出力をクロック信号CLK’でラッチする。クロック信号CLK’は、クロック信号CLKに対して所定の遅延量だけ先行するクロック信号であり、例えば、クロック信号CLKを分配するクロックツリーの上位(供給源に近い側)から供給される。

【0028】

排他的論理和回路EXOR0は、フリップフロップ回路FF12、FF13のそれぞれの出力信号Q、Q’の排他的論理和を演算し、演算結果である比較結果信号CMPを制御部15に出力する。

【0029】

次に、図2の回路の動作について説明する。図3は、本発明の第1の実施例に係る半導体集積回路装置の主要部の動作を表すタイミングチャートである。組み合わせ論理回路21の出力D1は、クロック信号CLKの立ち上がりであるタイミングt1と、クロック信号CLKに対して所定の遅延量だけ先行するクロック信号CLK’の立ち上がりであるタイミングt0とでそれぞれラッチされ、出力信号Q、Q’として出力される。出力信号Q、Q’に対し、排他的論理和演算がなされ比較結果信号CMPとなる。図3(a)では、出力信号Q、Q’としてHレベルがラッチされるので、クロック信号CLKの立ち下がりであるタイミングt2では、比較結果信号CMPとして一致(Lレベル、0)が出力される。すなわち、組み合わせ論理回路21は、タイミングt0であってもD1=Hレベルを出力可能であって、遅延時間に関し余裕があることが示される。

【0030】

これに対し、図3(b)において、クロック信号CLKの周波数を上昇させていくと、組み合わせ論理回路21の出力D1は、相対的な遅延量が増大していくことになる。なお、図3(a)、(b)において図示の簡略化のために、クロック信号CLKの周期を同一であるとして図示している。このため、最終的にはフリップフロップ回路FF13は、タイミングt0で出力D1がHレベルであることをラッチできなくなり、タイミングt0で出力信号Q’としてLレベルを出力することになる。したがって、クロック信号CLKの立ち下がりであるタイミングt2では、比較結果信号CMPとして不一致(Hレベル、1)が出力されてしまうことになる。

【0031】

制御部15は、このようにクロック信号CLKの周波数を上昇させていき、複数の遅延路における比較結果信号CMPを観測することで複数の遅延路におけるそれぞれ遅延検知を行う。図4は、本発明の第1の実施例に係る半導体集積回路装置の制御部の動作を表すフローチャートである。

【0032】

ステップS11において、制御部15は、各遅延路(組み合わせ論理回路21)に与えるクロック信号CLKの周波数を初期化する。

【0033】

ステップS12において、制御部15は、検知の対象とされる最初の遅延路に対応する排他的論理和回路EXOR0の比較結果信号CMPが一致(0)であるか否かをチェックする。比較結果信号CMPが一致(0)を示していれば、ステップS13において、クロック信号CLKの周波数を所定量上昇させ、ステップS12に戻る。

【0034】

比較結果信号CMPが不一致(1)を示していれば、ステップS14において、制御部15は、クロック信号CLKの周波数の値を記録する。

【0035】

ステップS15において、制御部15は、検知の対象となる次のパス(遅延路)の有無を調べる。次のパスがあれば、ステップS16において、検知の対象を次のパスとして選択し、ステップS11に戻る。

【0036】

ステップS15において次のパスがなければ、全てのパスにおける遅延検知が行われたので、制御部15は、ステップS17において、全てのパスに対する記録された周波数の順位付けを行う。

【0037】

ステップS18において、制御部15は、周波数の順位付けに基づいて遅延時間が最速または中央値となるパスを一の遅延路として選定する。通常は、最速となるパスを選定する。ただし、最速となるパスの場合、後段のフリップフロップ回路がデータをラッチできないですり抜けさせることもあり得る。また、最速パスにはリーク電流の大きなトランジスタが存在する可能性が高い。このような場合には、適切な遅延時間を与えるように遅延時間が中央値であるパスを選定する。なお、ここでは、遅延時間が最速または中央値となるパスを選定するとしたが、厳密にこのようにする必要はない。すなわち、最速から2番目や中央値の前後など必要に応じて選択するようにしてもよい。

【0038】

ステップS19において、制御部15は、選定された一の遅延路以外の遅延路における電源供給を停止(パワーゲーティング)する。

【0039】

ステップS20において、通常動作として選定された一の遅延路を介した信号伝送がなされる。

【0040】

以上のように制御部15は、クロック信号CLKの周波数を上昇させていった場合の周波数の上限を元に各遅延路すなわち組み合わせ論理回路21のそれぞれの遅延時間の長短を検出することができる。このような出力における一致不一致を検出する2つのフリップフロップ回路FF12、FF13による構成は、RazorFFとして知られている。

【0041】

以上のような半導体集積回路は、複数の遅延路中の遅延時間が最小(最速)あるいは中央値となる一の遅延路として選定し、選定された一の遅延路以外の遅延路における電源供給を停止すると供に、選定された一の遅延路を介した信号伝送を行う。したがって、一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。

【実施例2】

【0042】

図5は、本発明の第2の実施例に係る半導体集積回路装置の主要部の回路図である。図5において、組み合わせ論理回路22a、22b、22c、22dは、図1の遅延路にそれぞれ相当する。ここでは、組み合わせ論理回路である遅延路(パス)の数を4として示すが、これに限定されるものではない。組み合わせ論理回路22a、22b、22c、22dは、後述する実施例5、6にあるように単位論理ゲート回路の組み合わせからなり、組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路において排他的論理和をOUT3a、OUT3b、OUT3c、OUT3dとして出力する。

【0043】

フリップフロップ回路FF2a、FF2b、FF2c、FF2dは、遅延路にそれぞれ対応して設けられる同期動作回路11中の最終段のフリップフロップ回路であって、クロック信号CLKでラッチした信号をそれぞれ組み合わせ論理回路22a、22b、22c、22dに出力する。また、フリップフロップ回路FF3a、FF3b、FF3c、FF3dは、遅延路にそれぞれ対応して設けられる同期動作回路12中の初段のフリップフロップ回路であって、組み合わせ論理回路22a、22b、22c、22dのそれぞれ出力をクロック信号CLKでラッチする。セレクタSEL1は、フリップフロップ回路FF3a、FF3b、FF3c、FF3dのいずれか一つの出力を選択して出力する。なお、フリップフロップ回路は、チップ面積が大きいので、フリップフロップ回路FF2a、FF2b、FF2c、FF2dを一つに纏めてもよい。また、フリップフロップ回路FF3a、FF3b、FF3c、FF3dをセレクタと1つのフリップフロップ回路として構成することも可能である。

【0044】

遅延検出部14は、セレクタSEL2、SEL3、フリップフロップ回路FF4を備える。セレクタSEL2は、以下で述べるような制御部15の制御にしたがってOUT3a、OUT3b、OUT3c、OUT3dのいずれか一つを選択し、フリップフロップ回路FF4のD端子に出力する。セレクタSEL3は、制御部15の制御にしたがってOUT3a、OUT3b、OUT3c、OUT3dのいずれか一つを選択し、フリップフロップ回路FF4のクロック端子に出力する。フリップフロップ回路FF4は、D端子の信号をクロック端子の信号の立ち上がりでラッチして制御部15に信号CMP1を出力する位相比較器として機能する。

【0045】

次に、第2の実施例に係る制御部15の動作について説明する。図6は、本発明の第2の実施例に係る制御部の第1の動作を表すフローチャートである。ここで制御部15は、遅延検出部14によって遅延時間が最小(最速)となるパスを選択する。

【0046】

ステップ30において、制御部15は、セレクタSEL2、SEL3に対し初期設定を行う。例えば、セレクタSEL2がOUT3bを選択し、セレクタSEL3がOUT3aを選択するように制御する。

【0047】

ステップ31において、制御部15は、信号CMP1が0か1かを判定する。すなわち、信号CMP1が0であることは、OUT3aの立ち上がりに対し、OUT3bの立ち上がりが遅れていてフリップフロップ回路FF4が0をラッチしたことを意味する。したがって、組み合わせ論理回路22aが組み合わせ論理回路22bに比べて遅延時間は短いと判断される。また、信号CMP1が1であることは、OUT3aの立ち上がりに対し、OUT3bの立ち上がりが進んでいて、組み合わせ論理回路22aが組み合わせ論理回路22bに比べて遅延時間が長いことを意味する。

【0048】

ステップ32において、制御部15は、セレクタSEL2を切り替えたときの信号CMP1が0であった組み合わせが「パス数−1」続いたか否かをチェックする。

【0049】

「パス数−1」続いていない場合、ステップ33において、制御部15は、セレクタSEL2の選択先を次に切り替える。例えば、OUT3cを選択する。そして、ステップS31に戻る。

【0050】

ステップ32において、「パス数−1」続いた場合、セレクタSEL2の選択が全て終わったことを意味し、ステップ34において、セレクタSEL3が選択しているOUT3x(x=a〜dのいずれか)に対応する組み合わせ論理回路が最速のパスであるとして選定し、ステップ38に進む。

【0051】

一方、ステップ31において、信号CMP1が1である場合、ステップ35において、制御部15は、セレクタSEL2を切り替えたときの信号CMP1が1であった組み合わせが「パス数−1」続いたか否かをチェックする。

【0052】

「パス数−1」続いていない場合、ステップ36において、制御部15は、セレクタSEL3の選択先を次に切り替える。例えば、OUT3cを選択する。そして、ステップS31に戻る。

【0053】

ステップ35において、「パス数−1」続いた場合、セレクタSEL3の選択が全て終わったことを意味し、ステップ37において、セレクタSEL2が選択しているOUT3x(x=a〜dのいずれか)に対応する組み合わせ論理回路が最速のパスであるとして選定し、ステップ38に進む。

【0054】

ステップ38において、選定されなかったパス、すなわち最速でなかったパスを不要のパスであるとして電源の遮断(パワーゲーティング)を行う。

【0055】

ステップ39において、選定されたパス、すなわち最速のパスを一の遅延路とし、通常動作として一の遅延路を介した信号伝送がなされる。

【0056】

制御部15は、以上のように動作し、フリップフロップ回路FF4のD端子とクロック端子の入力の位相を、それぞれセレクタSEL2、SEL3を切り替えながら比較し、遅延時間が最小(最速)となるパスを選択する。

【0057】

図7は、本発明の第2の実施例に係る制御部の第2の動作を表すフローチャートである。ここで制御部15は、遅延検出部14によって遅延時間が中央値となるパスを選択する。

【0058】

ステップS40において、制御部15は、セレクタSEL2、SEL3に対し初期設定を行う。ステップS41〜S48は、セレクタSEL2、SEL3を切り替えながら、最も遅いパスを選択して不要のパスであるとして電源の遮断(パワーゲーティング)を行う処理である。また、ステップS51〜S58は、セレクタSEL2、SEL3を切り替えながら、最も速いパスを選択して不要のパスであるとして電源の遮断(パワーゲーティング)を行う処理であり、それぞれ図6のステップS31〜S38と同様の処理を行う。

【0059】

制御部15は、ステップS41〜S49を処理することで、最も遅いパスを次々と除いていき、ステップS51〜S59を処理することで、最も速いパスを次々と除いていき、結果としてステップS49またはS59において残った1個のパスは、遅延時間が中央値であるパスとなる。

【0060】

ステップ60において、選定されたパス、すなわち遅延時間が中央値であるパスを一の遅延路とし、通常動作として一の遅延路を介した信号伝送がなされる。

【0061】

以上のような半導体集積回路によれば、実施例1と同様に一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。

【実施例3】

【0062】

図8は、本発明の第3の実施例に係る制御部の動作を表すフローチャートである。ここで制御部15は、遅延路における電源電圧が変化するごとに選定される一の遅延路が変わりうる場合に適用される。制御部15は、遅延検出部14によって遅延時間が最小(最速)または中央値となるパスを選択する。図8において、ステップS61〜S68、S72、S73は、図4のステップS11〜S18、S19、S20とそれぞれ同等の処理を行うので、その説明を省略する。

【0063】

ステップS69において、制御部15は、前回の電源電圧において選定されたパスが今回の電源電圧において選定されたパスと同一であるか否かを判定する。同一パスである場合、ステップS72に進む。同一パスでは無い場合、ステップS70において、制御部15は、電源電圧を所定量下げる。制御部15は、下げた電源電圧で、再び遅延時間が最速または中央値となるパスを一の遅延路として選定するために、ステップS71において、検知の対象とされる最初のパスを設定し、ステップS61に戻る。

【0064】

制御部15は、以上のように動作することで、電源電圧が変化しても選定される遅延路が変わらなかった場合に、この遅延路を一の遅延路とする。そして、通常動作として一の遅延路を介した信号伝送がなされる。

【0065】

以上のような半導体集積回路によれば、実施例1と同様に一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。さらに、電源電圧が変化した場合であっても、安定的に一の遅延路が保持される。

【実施例4】

【0066】

図9は、本発明の第4の実施例に係る電源電圧制御遅延モニタの回路図である。図9において、レプリカ回路25は、図1の遅延路に対応して設けられ、第1または第2の実施例における選定された一の遅延路の遅延時間と遅延時間が同等となるように設定可能な回路である。

【0067】

フリップフロップ回路FF21は、図2のフリップフロップ回路11あるいは図5におけるフリップフロップ回路FF2a〜FF2dと同等の回路である。レプリカ回路25は、フリップフロップ回路FF21の出力を入力し、遅延回路26に出力する。遅延回路26は、レプリカ回路25の出力信号を所定量遅延し、フリップフロップ回路FF23および遅延回路27に出力する。遅延回路27は、遅延回路26の出力信号を所定量遅延し、フリップフロップ回路FF24に出力する。フリップフロップ回路FF23、FF24は、それぞれの入力をクロック信号CLKでラッチする。フリップフロップ回路FF23は、反転出力信号を電源電圧アップ信号Vupとして出力する。フリップフロップ回路FF24は、電源電圧ダウン信号Vdownを出力する。

【0068】

次に、このように構成される電源電圧制御遅延モニタの動作について説明する。図10は、本発明の第4の実施例に係る電源電圧制御遅延モニタの動作を表すタイミングチャートである。ここで、レプリカ回路25、遅延回路26、27の出力信号をそれぞれSm1、Sm2、Sm3とし、遅延回路26、27の遅延時間をTとする。

【0069】

フリップフロップ回路FF23、FF24のクロック信号CLKによるラッチタイミングが信号Sm2の立ち上がりタイミングより早いt31である場合、フリップフロップ回路FF23は、反転出力信号である電源電圧アップ信号VupをHレベルとして出力する。この場合、出力信号Sm1の立ち上がりのタイミングがクロック信号CLKによるラッチタイミングに接近していて、制御部15は、選定された一の遅延路の遅延時間に余裕がないものと判断する。したがって、制御部15は、遅延路に供給する電源の電圧を上げるように制御し、遅延路の遅延時間を短くなるようにする。

【0070】

一方、フリップフロップ回路FF23、FF24のクロック信号CLKによるラッチタイミングが信号Sm3の立ち上がりタイミングより遅いt32である場合、フリップフロップ回路FF24は、電源電圧ダウン信号VdownをHレベルとして出力する。この場合、出力信号Sm1の立ち上がりのタイミングがクロック信号CLKによるラッチタイミングから離れていて、制御部15は、選定された一の遅延路の遅延時間に余裕があるものと判断する。したがって、制御部15は、遅延路に供給する電源の電圧を下げるように制御し、遅延路の遅延時間を長くなるようにする。

【0071】

電源電圧制御遅延モニタは、以上のように動作して、選定された一の遅延路において適切な遅延時間を得られる限りにおいて、遅延路に供給される電源電圧を下げて、電力効率を向上させることができる。

【実施例5】

【0072】

図11は、本発明の第5の実施例に係る単位論理ゲート回路の回路図である。図11に示す単位論理ゲート回路は、図2の組み合わせ論理回路21あるいは図5の組み合わせ論理回路22a〜22dを構成する最小要素となる回路であって、相補的に動作するAND回路を構成する。

【0073】

単位論理ゲート回路は、PMOSトランジスタMP1〜MP4、NMOSトランジスタMN1〜MN6、インバータ回路INV1、INV2、AND回路AND1、排他的論理和回路EXOR1を備える。ただし、排他的論理和回路EXOR1は、図1の遅延路を構成する組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路においてのみ存在するものとする。

【0074】

PMOSトランジスタMP1、MP4は、ソースを電源Vddにそれぞれ接続し、制御部15から速度評価用クロック信号φをそれぞれのゲートに供給する。PMOSトランジスタMP2、MP3は、ソースを電源Vddにそれぞれ接続し、互いのゲートとドレインとを交互に接続する。

【0075】

NMOSトランジスタMN1は、ドレインをPMOSトランジスタMP1、MP2のドレイン、インバータ回路INV1の入力端、排他的論理和回路EXOR1の一方の入力端に接続し、ゲートを入力端子INaに接続し、ソースをNMOSトランジスタMN2のドレインに接続する。NMOSトランジスタMN2は、ゲートを入力端子INbに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。インバータ回路INV1の出力端は、出力端子OUT1に接続される。ここで入力端子INa、INbにそれぞれ与えられる信号の論理値をA、Bとする。

【0076】

NMOSトランジスタMN3は、ドレインをPMOSトランジスタMP3、MP4のドレイン、インバータ回路INV2の入力端、排他的論理和回路EXOR1の他方の入力端に接続し、ゲートを端子INabに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。NMOSトランジスタMN4は、ドレインをNMOSトランジスタMP3、MP4のドレインに接続し、ゲートを端子INbbに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。インバータ回路INV2の出力端は、出力端子OUT2に接続される。排他的論理和回路EXOR1の出力端は、出力端子OUT3に接続される。ここで入力端子INab、INbbにそれぞれ与えられる信号の論理値をAb、Bbとし、論理値Ab、Bbをそれぞれ論理値A、Bの否定論理とする。

【0077】

AND回路AND1は、一方の入力端に速度評価用クロック信号φを供給し、他方の入力端に制御部15からパワーゲーティング用の信号Spgを供給し、出力端をNMOSトランジスタMN5のゲートに接続する。NMOSトランジスタMN5のソースは接地される。NMOSトランジスタMN6は、ソースを接地し、ゲートに信号Spgを供給し、ドレインをインバータ回路INV1、INV2、排他的論理和回路EXOR1のそれぞれの接地側電源供給端子に接続する。

【0078】

次に、以上のような構成の単位論理ゲート回路の動作について説明する。図12は、本発明の第5の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。図12において、速度評価用クロック信号φがLレベルである期間は、プリチャージ期間であり、PMOSトランジスタMP1、MP4がオンし、NMOSトランジスタMN5がオフし、インバータ回路INV1、INV2の入力端は、Hレベルになる。したがって、インバータ回路INV1、INV2の出力端、すなわち出力端子OUT1、OUT2は、Lレベルとなる。

【0079】

速度評価用クロック信号φがHレベルである期間は、遅延時間の判定期間であり、PMOSトランジスタMP1、MP4がオフし、NMOSトランジスタMN5がオンする。したがって、判定期間では、出力端子OUT1からは、論理値A、Bの論理積A*Bが出力される。また、出力端子OUT2からは、論理値Ab、Bbの論理和Ab+Bb、すなわちA、Bの論理積の否定論理である(A*B)bが出力される。このように単位論理ゲート回路は、一方の入出力論理値に対しそれぞれ否定論理を表す他方の入出力論理値を備える相補的に動作する論理回路で構成され、二線式論理回路として機能する。なお、図12において、出力端子OUT1、OUT2の出力A*B、(A*B)bは、単位論理ゲート回路内部の遅延があるものとして示される。

【0080】

なお、図2のフリップフロップ回路11あるいは図5におけるフリップフロップ回路FF2a〜FF2dでは、正論理側(Q)のみしか出力していないが、上記の否定論理側(Qb)も出力可能とするように構成することが好ましい。

【0081】

以上のように動作する単位論理ゲート回路は、速度評価用クロック信号φの論理レベルに応じて動作する二線式論理回路のダイナミック回路として構成され、遅延検出部による遅延時間検出時にダイナミック回路として機能する。一方、通常動作時には、速度評価用クロック信号φをHレベルに保ちスタティック回路として機能する。

【0082】

なお、判定期間において、排他的論理和回路EXOR1の出力端、すなわち出力端子OUT3は、論理値A、Bの排他的論理和を出力し、単位論理ゲート回路内部の遅延があるものとして示される。この場合、遅延路の最終段の単位論理ゲート回路において、論理値A、Bの排他的論理和の出力OUT3の遅延時間(例えば立ち上がり時間p1、p2)は、異なる遅延路同士で異なり遅延路のばらつきによって例えばOUT3、OUT3’のようになる。

【0083】

このような遅延路のばらつきによる遅延時間の長短は、実施例2において説明したような遅延検出部14と制御回路15とによって検出され、遅延時間の最速値あるいは中央値となるパス(遅延路)が選定される。

【0084】

また、第5の実施例の単位論理ゲート回路を実施例1の組み合わせ論理回路21に適用する場合、排他的論理和回路EXOR1は不要である。

【実施例6】

【0085】

図13は、本発明の第6の実施例に係る単位論理ゲート回路の回路図である。図13に示す単位論理ゲート回路は、図2の組み合わせ論理回路21あるいは図5の組み合わせ論理回路22a〜22dを構成する最小要素となる回路であって、相補的に動作するAND回路を構成する。

【0086】

単位論理ゲート回路は、PMOSトランジスタMP5、MP6、インバータ回路INV3、INV4、NAND回路NAND1、NOR回路NOR1、排他的論理和回路EXOR2を備える。ただし、排他的論理和回路EXOR2は、図1の遅延路を構成する組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路においてのみ存在するものとする。

【0087】

PMOSトランジスタMP5、MP6は、ソースを電源Vddにそれぞれ接続し、制御部15からパワーゲーティング用の信号Spg1、Spg2をそれぞれのゲートに供給する。PMOSトランジスタMP5は、ドレインをインバータ回路INV3、NAND回路NAND1のそれぞれの電源供給端に接続する。PMOSトランジスタMP6は、ドレインをインバータ回路INV4、NOR回路NOR1、排他的論理和回路EXOR2のそれぞれの電源供給端に接続する。

【0088】

NAND回路NAND1は、一方の入力端を入力端子INaに接続し、他方の入力端を入力端子INbに接続し、出力端をインバータ回路INV3の入力端および排他的論理和回路EXOR2の一方の入力端に接続する。インバータ回路INV3は、出力端を出力端子OUT1に接続する。

【0089】

NOR回路NOR1は、一方の入力端を入力端子INabに接続し、他方の入力端を入力端子INbbに接続し、出力端をインバータ回路INV4の入力端および排他的論理和回路EXOR2の他方の入力端に接続する。インバータ回路INV4は、出力端を出力端子OUT2に接続する。排他的論理和回路EXOR2は、出力端を出力端子OUT3に接続する。ここで入力端子INa、INbにそれぞれ与えられる信号の論理値をA、Bとする。また、入力端子INab、INbbにそれぞれ与えられる信号の論理値をAb、Bbとし、論理値Ab、Bbをそれぞれ論理値A、Bの否定論理とする。

【0090】

なお、図2のフリップフロップ回路FF11あるいは図5におけるフリップフロップ回路FF2a〜FF2dでは、正論理側(Q)のみしか出力していないが、上記の否定論理側(Qb)も出力可能とするように構成することが好ましい。図14は、本発明の第6の実施例に係る単位論理ゲート回路の初段の駆動回路の回路図であり、フリップフロップ回路FF5、AND回路AND2、AND3を備える。フリップフロップ回路FF5は、図2のフリップフロップ回路FF11あるいは図5におけるフリップフロップ回路FF2a〜FF2dに対応する。AND回路AND2は、フリップフロップ回路FF5の正論理側出力とタイミング信号Tmとの論理積を求めて正論理側出力Qとする。AND回路AND3は、フリップフロップ回路FF5の否定論理側出力とタイミング信号Tmとの論理積を求めて否定論理側出力Qbとする。Q、Qbは単位論理ゲート回路に入力される。

【0091】

次に、以上のような構成の単位論理ゲート回路の動作について説明する。図15は、本発明の第6の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。図15において、タイミング信号TmがHレベルである期間は、単位論理ゲート回路の遅延判定期間および通常動作期間であり、入力端子INa、INb、INab、INbbにそれぞれ与えられる論理値に応じた論理演算結果が出力端子OUT1、OUT2に出力される。すなわち、出力端子OUT1からは、論理値A、Bの論理積A*Bが出力される。また、出力端子OUT2からは、論理値Ab、Bbの論理和Ab+Bb、すなわちA、Bの論理積の否定論理である(A*B)bが出力される。

【0092】

以上のように動作する単位論理ゲート回路は、実施例5と同様に相補的に動作する論理回路で構成され、二線式論理回路として機能する。ただし、実施例5の速度評価用クロック信号φが不要であるスタティック回路として構成され、遅延時間検出時に二線式論理のスタティック回路として機能する。また、通常動作時には単線式論理のスタティック回路として機能する。すなわち、遅延時間検出時には、パワーゲーティング用の信号Spg1、Spg2のレベルをLレベルとしてPMOSトランジスタMP5、MP6をオンとする。したがって、NAND回路NAND1、インバータ回路INV3からなる経路と、NOR回路NOR1、インバータ回路INV4からなる経路の双方が機能し、二線式論理回路を形成する。一方、通常動作時には、パワーゲーティング用の信号Spg1(あるいは信号Spg2)のレベルをのみをLレベルとしてPMOSトランジスタMP5(あるいはMP6)だけをオンとする。したがって、NAND回路NAND1、インバータ回路INV3(NOR回路NOR1、インバータ回路INV4)からなる一つの経路のみが機能し、単線式論理回路を形成する。

【0093】

なお、遅延判定期間において、排他的論理和回路EXOR2の出力端、すなわち出力端子OUT3は、論理値A、Bの排他的論理和を出力し、単位論理ゲート回路内部の遅延があるものとして示される。この場合、遅延路の最終段の単位論理ゲート回路において、異なる遅延路同士で論理値A、Bの排他的論理和の出力OUT3の遅延時間は、遅延路のばらつきによって異なる。

【0094】

このような遅延路のばらつきによる遅延時間の長短は、実施例2において説明したような遅延検出部14と制御回路15とによって検出され、遅延時間の最速値あるいは中央値となるパス(遅延路)が選定される。

【0095】

また、第6の実施例の単位論理ゲート回路を実施例1の組み合わせ論理回路21に適用する場合、排他的論理和回路EXOR2は不要である。

【0096】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【図面の簡単な説明】

【0097】

【図1】本発明の実施形態に係る半導体集積回路装置の構成を示す図である。

【図2】本発明の第1の実施例に係る半導体集積回路装置の主要部の回路図である。

【図3】本発明の第1の実施例に係る半導体集積回路装置の主要部の動作を表すタイミングチャートである。

【図4】本発明の第1の実施例に係る半導体集積回路装置の制御部の動作を表すフローチャートである。

【図5】本発明の第2の実施例に係る半導体集積回路装置の主要部の回路図である。

【図6】本発明の第2の実施例に係る制御部の第1の動作を表すフローチャートである。

【図7】本発明の第2の実施例に係る制御部の第2の動作を表すフローチャートである。

【図8】本発明の第3の実施例に係る制御部の動作を表すフローチャートである。

【図9】本発明の第4の実施例に係る電源電圧制御遅延モニタの回路図である。

【図10】本発明の第4の実施例に係る電源電圧制御遅延モニタの動作を表すタイミングチャートである。

【図11】本発明の第5の実施例に係る単位論理ゲート回路の回路図である。

【図12】本発明の第5の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。

【図13】本発明の第6の実施例に係る単位論理ゲート回路の回路図である。

【図14】本発明の第6の実施例に係る単位論理ゲート回路の初段の駆動回路の回路図である。

【図15】本発明の第6の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。

【符号の説明】

【0098】

11、12 同期動作回路

13a、13b、・・13n 遅延路

14 遅延検出部

15 制御部

21、22a〜22d 組み合わせ論理回路

25 レプリカ回路

26、27 遅延回路

AND0〜AND3 AND回路

EXOR0、EXOR1、EXOR2 排他的論理和回路

FF11〜FF13、FF21、FF23、FF24、FF2a〜FF2d、FF3a〜FF3d、FF4、FF5 フリップフロップ回路

INV1〜INV4 インバータ回路

MN1〜MN6 NMOSトランジスタ

SEL1〜SEL3 セレクタ

MP1〜MP6 PMOSトランジスタ

【技術分野】

【0001】

本発明は、半導体集積回路装置および遅延路の制御方法に係り、特に、2つの回路間で信号伝送を行う半導体集積回路装置およびそこに含まれる遅延路の制御方法に係る。

【背景技術】

【0002】

論理回路を半導体集積回路装置上に構成する場合、遅延時間に関して、最悪ケースでデバイスのばらつきも考慮し、セットアップ時間、ホールド時間の規定を満足するように設計が行なわれる。例えば、クロック信号に同期して動作する2つの同期動作回路の間では、CMOS回路におけるトランジスタサイズ、閾値電圧、ゲート種類、ゲート段数等を変更して適切な遅延時間を有する回路が挿入され、ホールド時間の規定を満足するように構成される。

【0003】

2つの同期動作回路間に挿入される遅延回路としては、例えば、通常のCMOS回路や非特許文献1に記載されるようなDCVSL(Differential Cascode Voltage Switch Logic)を組み合わせて用いることで、安定した遅延時間を得ることができる。

【0004】

なお、関連する技術として、複数のデジタル処理回路のいずれかの系統で設定状態にずれが生じた場合に、正常系統のデジタル処理回路のいずれかを停止させても、多数決結果の正当性を確保し、正常動作に対する信頼性を維持する冗長回路装置が特許文献1に記載されている。

【0005】

【非特許文献1】Kan M. Chu and David L. Pulfrey,”A Comparison of CMOS Circuit Techniques: Differential Cascode Voltage Switch Logic Versus Conventional Logic”,IEEE Journal of Solid-state Circuits, vol. SC-22, pp.528-532, August 1987

【特許文献1】特開2008−191939号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

以下の分析は本発明において与えられる。

【0007】

近年、半導体の微細化および低電圧化の進展に伴ってデバイスのばらつきおよび遅延のばらつきが増大している。このため、最悪ケースを想定した設計が徐々に困難となってきている。そこで、2つの同期動作回路間に複数の遅延回路を挿入した多重化設計が考えられる。例えば、特許文献1に記載したような多数決結果を適用するような多重化設計による半導体集積回路装置が考えられる。しかしながら、このような多重化設計による半導体集積回路装置では、多重化したハードウェアが動作し続けるために消費電力およびリーク電流が増大し、電力効率が低下してしまう虞がある。

【課題を解決するための手段】

【0008】

本発明の1つのアスペクト(側面)に係る半導体集積回路装置は、クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路と、複数の遅延路におけるそれぞれの遅延時間を検出する遅延検出部と、遅延検出部の検出結果に基づいて複数の遅延路の内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部と、を備える。

【0009】

本発明の他のアスペクト(側面)に係る遅延路の制御方法は、クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路の制御方法であって、複数の遅延路におけるそれぞれの遅延時間を検出するステップと、遅延時間の検出結果に基づいて複数の遅延路の内の一の遅延路を選択するステップと、選択された一の遅延路以外における信号伝送を阻止するように制御するステップと、を含む。

【発明の効果】

【0010】

本発明によれば、一の遅延路以外における信号伝送が阻止されるので、電力効率が向上する。

【発明を実施するための最良の形態】

【0011】

図1は、本発明の実施形態に係る半導体集積回路装置の構成を示す図である。図1において、半導体集積回路装置は、クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択された一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。このような半導体集積回路装置によれば、一の遅延路以外における信号伝送が阻止されるので、半導体集積回路装置における電力効率が向上する。

【0012】

複数の遅延路は、電源が供給されて動作する能動回路を含んでそれぞれ構成され、制御部は、通常動作時に一の遅延路以外における遅延路中の能動回路への電源供給を停止するようにしてもよい。

【0013】

能動回路は、組み合わせ論理回路として構成されてもよい。

【0014】

制御部は、複数の遅延路の内の遅延時間が最小値となる遅延路を一の遅延路として選択するようにしてもよい。このような制御によれば、デバイスのばらつきに起因する遅延の大きな遅延路を除外することで速度性能を向上することができる。

【0015】

また、制御部は、複数の遅延路の内の遅延時間が中央値となる遅延路を一の遅延路として選択するようにしてもよい。このような制御によれば、デバイスのばらつきに起因する遅延の小さな遅延路を除外することで高速の遅延路に予想される過大なリーク電流を削減することができる。

【0016】

さらに、制御部は、選択された一の遅延路における電源供給電圧を所定の電圧まで低下させるようにしてもよい。このような制御によれば、所望の性能まで電源電圧を下げることができ、電力効率が改善される。

【0017】

また、制御部は、複数の遅延路への電源供給電圧に対応させて一の遅延路を選択するようにしてもよい。このような制御によれば、電源電圧毎に適切な遅延路を選択することで充分な遅延マージンを確保することができる。

【0018】

遅延検出部は、複数の遅延路にそれぞれ対応させてラッチタイミングのそれぞれ異なる2つのレジスタを備え、制御部は、ラッチタイミングを変化させていった場合における2つのレジスタのラッチデータに基づいて得た複数の遅延路における遅延時間順に基づいて一の遅延路を選択するようにしてもよい。

【0019】

2つのレジスタの一方は、通常動作時にクロック信号のラッチタイミングで動作するようにしてもよい。

【0020】

遅延路は、相補的に動作する論理回路で構成され、遅延検出部による遅延時間検出時には相補的に動作するように機能するようにしてもよい。

【0021】

また、遅延路は、二線式論理回路で構成され、遅延検出部による遅延時間検出時に二線式論理回路として機能し、通常動作時に二線式論理回路または単線式論理回路として機能するようにしてもよい。このような二線式論理回路を用いることで、遅延検出を効率よく行うことができる。また、通常動作時に単線式論理回路として機能させるならば、消費電力が低減される。

【0022】

遅延検出部は、遅延時間検出時に二線式論理回路における論理値の変化順を検出するようにしてもよい。

【0023】

さらに、遅延路は、ダイナミック回路として構成され、遅延検出部による遅延時間検出時にダイナミック回路として機能し、通常動作時にスタティック回路として機能するようにしてもよい。このようなダイナミック回路を用いることで、遅延検出を効率よく行うことができる。また、通常動作時にスタティック回路として機能させるならば、消費電力が低減される。

【0024】

また、遅延路は、スタティック回路として構成され、遅延検出部による遅延時間検出時および通常動作時にスタティック回路として機能するようにしてもよい。

【0025】

以下、実施例に即し、図面を参照して半導体集積回路装置の各部について詳しく説明する。

【実施例1】

【0026】

図2は、本発明の第1の実施例に係る半導体集積回路装置の主要部の回路図である。図2において、組み合わせ論理回路21は、図1の遅延路13a、13b、・・13nの一つに相当する。フリップフロップ回路FF11は、遅延路にそれぞれ対応して設けられる同期動作回路11中の最終段のフリップフロップ回路であって、クロック信号CLKでラッチした信号を組み合わせ論理回路21に出力する。また、フリップフロップ回路FF12は、遅延路にそれぞれ対応して設けられる同期動作回路12中の初段のフリップフロップ回路であって、組み合わせ論理回路21の出力をクロック信号CLKでラッチする。遅延検出部14は、図1における一つの遅延路に対応してフリップフロップ回路FF13、排他的論理和回路XOR0を備える。

【0027】

フリップフロップ回路FF13は、組み合わせ論理回路21の出力をクロック信号CLK’でラッチする。クロック信号CLK’は、クロック信号CLKに対して所定の遅延量だけ先行するクロック信号であり、例えば、クロック信号CLKを分配するクロックツリーの上位(供給源に近い側)から供給される。

【0028】

排他的論理和回路EXOR0は、フリップフロップ回路FF12、FF13のそれぞれの出力信号Q、Q’の排他的論理和を演算し、演算結果である比較結果信号CMPを制御部15に出力する。

【0029】

次に、図2の回路の動作について説明する。図3は、本発明の第1の実施例に係る半導体集積回路装置の主要部の動作を表すタイミングチャートである。組み合わせ論理回路21の出力D1は、クロック信号CLKの立ち上がりであるタイミングt1と、クロック信号CLKに対して所定の遅延量だけ先行するクロック信号CLK’の立ち上がりであるタイミングt0とでそれぞれラッチされ、出力信号Q、Q’として出力される。出力信号Q、Q’に対し、排他的論理和演算がなされ比較結果信号CMPとなる。図3(a)では、出力信号Q、Q’としてHレベルがラッチされるので、クロック信号CLKの立ち下がりであるタイミングt2では、比較結果信号CMPとして一致(Lレベル、0)が出力される。すなわち、組み合わせ論理回路21は、タイミングt0であってもD1=Hレベルを出力可能であって、遅延時間に関し余裕があることが示される。

【0030】

これに対し、図3(b)において、クロック信号CLKの周波数を上昇させていくと、組み合わせ論理回路21の出力D1は、相対的な遅延量が増大していくことになる。なお、図3(a)、(b)において図示の簡略化のために、クロック信号CLKの周期を同一であるとして図示している。このため、最終的にはフリップフロップ回路FF13は、タイミングt0で出力D1がHレベルであることをラッチできなくなり、タイミングt0で出力信号Q’としてLレベルを出力することになる。したがって、クロック信号CLKの立ち下がりであるタイミングt2では、比較結果信号CMPとして不一致(Hレベル、1)が出力されてしまうことになる。

【0031】

制御部15は、このようにクロック信号CLKの周波数を上昇させていき、複数の遅延路における比較結果信号CMPを観測することで複数の遅延路におけるそれぞれ遅延検知を行う。図4は、本発明の第1の実施例に係る半導体集積回路装置の制御部の動作を表すフローチャートである。

【0032】

ステップS11において、制御部15は、各遅延路(組み合わせ論理回路21)に与えるクロック信号CLKの周波数を初期化する。

【0033】

ステップS12において、制御部15は、検知の対象とされる最初の遅延路に対応する排他的論理和回路EXOR0の比較結果信号CMPが一致(0)であるか否かをチェックする。比較結果信号CMPが一致(0)を示していれば、ステップS13において、クロック信号CLKの周波数を所定量上昇させ、ステップS12に戻る。

【0034】

比較結果信号CMPが不一致(1)を示していれば、ステップS14において、制御部15は、クロック信号CLKの周波数の値を記録する。

【0035】

ステップS15において、制御部15は、検知の対象となる次のパス(遅延路)の有無を調べる。次のパスがあれば、ステップS16において、検知の対象を次のパスとして選択し、ステップS11に戻る。

【0036】

ステップS15において次のパスがなければ、全てのパスにおける遅延検知が行われたので、制御部15は、ステップS17において、全てのパスに対する記録された周波数の順位付けを行う。

【0037】

ステップS18において、制御部15は、周波数の順位付けに基づいて遅延時間が最速または中央値となるパスを一の遅延路として選定する。通常は、最速となるパスを選定する。ただし、最速となるパスの場合、後段のフリップフロップ回路がデータをラッチできないですり抜けさせることもあり得る。また、最速パスにはリーク電流の大きなトランジスタが存在する可能性が高い。このような場合には、適切な遅延時間を与えるように遅延時間が中央値であるパスを選定する。なお、ここでは、遅延時間が最速または中央値となるパスを選定するとしたが、厳密にこのようにする必要はない。すなわち、最速から2番目や中央値の前後など必要に応じて選択するようにしてもよい。

【0038】

ステップS19において、制御部15は、選定された一の遅延路以外の遅延路における電源供給を停止(パワーゲーティング)する。

【0039】

ステップS20において、通常動作として選定された一の遅延路を介した信号伝送がなされる。

【0040】

以上のように制御部15は、クロック信号CLKの周波数を上昇させていった場合の周波数の上限を元に各遅延路すなわち組み合わせ論理回路21のそれぞれの遅延時間の長短を検出することができる。このような出力における一致不一致を検出する2つのフリップフロップ回路FF12、FF13による構成は、RazorFFとして知られている。

【0041】

以上のような半導体集積回路は、複数の遅延路中の遅延時間が最小(最速)あるいは中央値となる一の遅延路として選定し、選定された一の遅延路以外の遅延路における電源供給を停止すると供に、選定された一の遅延路を介した信号伝送を行う。したがって、一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。

【実施例2】

【0042】

図5は、本発明の第2の実施例に係る半導体集積回路装置の主要部の回路図である。図5において、組み合わせ論理回路22a、22b、22c、22dは、図1の遅延路にそれぞれ相当する。ここでは、組み合わせ論理回路である遅延路(パス)の数を4として示すが、これに限定されるものではない。組み合わせ論理回路22a、22b、22c、22dは、後述する実施例5、6にあるように単位論理ゲート回路の組み合わせからなり、組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路において排他的論理和をOUT3a、OUT3b、OUT3c、OUT3dとして出力する。

【0043】

フリップフロップ回路FF2a、FF2b、FF2c、FF2dは、遅延路にそれぞれ対応して設けられる同期動作回路11中の最終段のフリップフロップ回路であって、クロック信号CLKでラッチした信号をそれぞれ組み合わせ論理回路22a、22b、22c、22dに出力する。また、フリップフロップ回路FF3a、FF3b、FF3c、FF3dは、遅延路にそれぞれ対応して設けられる同期動作回路12中の初段のフリップフロップ回路であって、組み合わせ論理回路22a、22b、22c、22dのそれぞれ出力をクロック信号CLKでラッチする。セレクタSEL1は、フリップフロップ回路FF3a、FF3b、FF3c、FF3dのいずれか一つの出力を選択して出力する。なお、フリップフロップ回路は、チップ面積が大きいので、フリップフロップ回路FF2a、FF2b、FF2c、FF2dを一つに纏めてもよい。また、フリップフロップ回路FF3a、FF3b、FF3c、FF3dをセレクタと1つのフリップフロップ回路として構成することも可能である。

【0044】

遅延検出部14は、セレクタSEL2、SEL3、フリップフロップ回路FF4を備える。セレクタSEL2は、以下で述べるような制御部15の制御にしたがってOUT3a、OUT3b、OUT3c、OUT3dのいずれか一つを選択し、フリップフロップ回路FF4のD端子に出力する。セレクタSEL3は、制御部15の制御にしたがってOUT3a、OUT3b、OUT3c、OUT3dのいずれか一つを選択し、フリップフロップ回路FF4のクロック端子に出力する。フリップフロップ回路FF4は、D端子の信号をクロック端子の信号の立ち上がりでラッチして制御部15に信号CMP1を出力する位相比較器として機能する。

【0045】

次に、第2の実施例に係る制御部15の動作について説明する。図6は、本発明の第2の実施例に係る制御部の第1の動作を表すフローチャートである。ここで制御部15は、遅延検出部14によって遅延時間が最小(最速)となるパスを選択する。

【0046】

ステップ30において、制御部15は、セレクタSEL2、SEL3に対し初期設定を行う。例えば、セレクタSEL2がOUT3bを選択し、セレクタSEL3がOUT3aを選択するように制御する。

【0047】

ステップ31において、制御部15は、信号CMP1が0か1かを判定する。すなわち、信号CMP1が0であることは、OUT3aの立ち上がりに対し、OUT3bの立ち上がりが遅れていてフリップフロップ回路FF4が0をラッチしたことを意味する。したがって、組み合わせ論理回路22aが組み合わせ論理回路22bに比べて遅延時間は短いと判断される。また、信号CMP1が1であることは、OUT3aの立ち上がりに対し、OUT3bの立ち上がりが進んでいて、組み合わせ論理回路22aが組み合わせ論理回路22bに比べて遅延時間が長いことを意味する。

【0048】

ステップ32において、制御部15は、セレクタSEL2を切り替えたときの信号CMP1が0であった組み合わせが「パス数−1」続いたか否かをチェックする。

【0049】

「パス数−1」続いていない場合、ステップ33において、制御部15は、セレクタSEL2の選択先を次に切り替える。例えば、OUT3cを選択する。そして、ステップS31に戻る。

【0050】

ステップ32において、「パス数−1」続いた場合、セレクタSEL2の選択が全て終わったことを意味し、ステップ34において、セレクタSEL3が選択しているOUT3x(x=a〜dのいずれか)に対応する組み合わせ論理回路が最速のパスであるとして選定し、ステップ38に進む。

【0051】

一方、ステップ31において、信号CMP1が1である場合、ステップ35において、制御部15は、セレクタSEL2を切り替えたときの信号CMP1が1であった組み合わせが「パス数−1」続いたか否かをチェックする。

【0052】

「パス数−1」続いていない場合、ステップ36において、制御部15は、セレクタSEL3の選択先を次に切り替える。例えば、OUT3cを選択する。そして、ステップS31に戻る。

【0053】

ステップ35において、「パス数−1」続いた場合、セレクタSEL3の選択が全て終わったことを意味し、ステップ37において、セレクタSEL2が選択しているOUT3x(x=a〜dのいずれか)に対応する組み合わせ論理回路が最速のパスであるとして選定し、ステップ38に進む。

【0054】

ステップ38において、選定されなかったパス、すなわち最速でなかったパスを不要のパスであるとして電源の遮断(パワーゲーティング)を行う。

【0055】

ステップ39において、選定されたパス、すなわち最速のパスを一の遅延路とし、通常動作として一の遅延路を介した信号伝送がなされる。

【0056】

制御部15は、以上のように動作し、フリップフロップ回路FF4のD端子とクロック端子の入力の位相を、それぞれセレクタSEL2、SEL3を切り替えながら比較し、遅延時間が最小(最速)となるパスを選択する。

【0057】

図7は、本発明の第2の実施例に係る制御部の第2の動作を表すフローチャートである。ここで制御部15は、遅延検出部14によって遅延時間が中央値となるパスを選択する。

【0058】

ステップS40において、制御部15は、セレクタSEL2、SEL3に対し初期設定を行う。ステップS41〜S48は、セレクタSEL2、SEL3を切り替えながら、最も遅いパスを選択して不要のパスであるとして電源の遮断(パワーゲーティング)を行う処理である。また、ステップS51〜S58は、セレクタSEL2、SEL3を切り替えながら、最も速いパスを選択して不要のパスであるとして電源の遮断(パワーゲーティング)を行う処理であり、それぞれ図6のステップS31〜S38と同様の処理を行う。

【0059】

制御部15は、ステップS41〜S49を処理することで、最も遅いパスを次々と除いていき、ステップS51〜S59を処理することで、最も速いパスを次々と除いていき、結果としてステップS49またはS59において残った1個のパスは、遅延時間が中央値であるパスとなる。

【0060】

ステップ60において、選定されたパス、すなわち遅延時間が中央値であるパスを一の遅延路とし、通常動作として一の遅延路を介した信号伝送がなされる。

【0061】

以上のような半導体集積回路によれば、実施例1と同様に一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。

【実施例3】

【0062】

図8は、本発明の第3の実施例に係る制御部の動作を表すフローチャートである。ここで制御部15は、遅延路における電源電圧が変化するごとに選定される一の遅延路が変わりうる場合に適用される。制御部15は、遅延検出部14によって遅延時間が最小(最速)または中央値となるパスを選択する。図8において、ステップS61〜S68、S72、S73は、図4のステップS11〜S18、S19、S20とそれぞれ同等の処理を行うので、その説明を省略する。

【0063】

ステップS69において、制御部15は、前回の電源電圧において選定されたパスが今回の電源電圧において選定されたパスと同一であるか否かを判定する。同一パスである場合、ステップS72に進む。同一パスでは無い場合、ステップS70において、制御部15は、電源電圧を所定量下げる。制御部15は、下げた電源電圧で、再び遅延時間が最速または中央値となるパスを一の遅延路として選定するために、ステップS71において、検知の対象とされる最初のパスを設定し、ステップS61に戻る。

【0064】

制御部15は、以上のように動作することで、電源電圧が変化しても選定される遅延路が変わらなかった場合に、この遅延路を一の遅延路とする。そして、通常動作として一の遅延路を介した信号伝送がなされる。

【0065】

以上のような半導体集積回路によれば、実施例1と同様に一の遅延路以外における消費電流(スイッチング電流やリーク電流)がほとんど無くなり、電力効率が向上する。さらに、電源電圧が変化した場合であっても、安定的に一の遅延路が保持される。

【実施例4】

【0066】

図9は、本発明の第4の実施例に係る電源電圧制御遅延モニタの回路図である。図9において、レプリカ回路25は、図1の遅延路に対応して設けられ、第1または第2の実施例における選定された一の遅延路の遅延時間と遅延時間が同等となるように設定可能な回路である。

【0067】

フリップフロップ回路FF21は、図2のフリップフロップ回路11あるいは図5におけるフリップフロップ回路FF2a〜FF2dと同等の回路である。レプリカ回路25は、フリップフロップ回路FF21の出力を入力し、遅延回路26に出力する。遅延回路26は、レプリカ回路25の出力信号を所定量遅延し、フリップフロップ回路FF23および遅延回路27に出力する。遅延回路27は、遅延回路26の出力信号を所定量遅延し、フリップフロップ回路FF24に出力する。フリップフロップ回路FF23、FF24は、それぞれの入力をクロック信号CLKでラッチする。フリップフロップ回路FF23は、反転出力信号を電源電圧アップ信号Vupとして出力する。フリップフロップ回路FF24は、電源電圧ダウン信号Vdownを出力する。

【0068】

次に、このように構成される電源電圧制御遅延モニタの動作について説明する。図10は、本発明の第4の実施例に係る電源電圧制御遅延モニタの動作を表すタイミングチャートである。ここで、レプリカ回路25、遅延回路26、27の出力信号をそれぞれSm1、Sm2、Sm3とし、遅延回路26、27の遅延時間をTとする。

【0069】

フリップフロップ回路FF23、FF24のクロック信号CLKによるラッチタイミングが信号Sm2の立ち上がりタイミングより早いt31である場合、フリップフロップ回路FF23は、反転出力信号である電源電圧アップ信号VupをHレベルとして出力する。この場合、出力信号Sm1の立ち上がりのタイミングがクロック信号CLKによるラッチタイミングに接近していて、制御部15は、選定された一の遅延路の遅延時間に余裕がないものと判断する。したがって、制御部15は、遅延路に供給する電源の電圧を上げるように制御し、遅延路の遅延時間を短くなるようにする。

【0070】

一方、フリップフロップ回路FF23、FF24のクロック信号CLKによるラッチタイミングが信号Sm3の立ち上がりタイミングより遅いt32である場合、フリップフロップ回路FF24は、電源電圧ダウン信号VdownをHレベルとして出力する。この場合、出力信号Sm1の立ち上がりのタイミングがクロック信号CLKによるラッチタイミングから離れていて、制御部15は、選定された一の遅延路の遅延時間に余裕があるものと判断する。したがって、制御部15は、遅延路に供給する電源の電圧を下げるように制御し、遅延路の遅延時間を長くなるようにする。

【0071】

電源電圧制御遅延モニタは、以上のように動作して、選定された一の遅延路において適切な遅延時間を得られる限りにおいて、遅延路に供給される電源電圧を下げて、電力効率を向上させることができる。

【実施例5】

【0072】

図11は、本発明の第5の実施例に係る単位論理ゲート回路の回路図である。図11に示す単位論理ゲート回路は、図2の組み合わせ論理回路21あるいは図5の組み合わせ論理回路22a〜22dを構成する最小要素となる回路であって、相補的に動作するAND回路を構成する。

【0073】

単位論理ゲート回路は、PMOSトランジスタMP1〜MP4、NMOSトランジスタMN1〜MN6、インバータ回路INV1、INV2、AND回路AND1、排他的論理和回路EXOR1を備える。ただし、排他的論理和回路EXOR1は、図1の遅延路を構成する組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路においてのみ存在するものとする。

【0074】

PMOSトランジスタMP1、MP4は、ソースを電源Vddにそれぞれ接続し、制御部15から速度評価用クロック信号φをそれぞれのゲートに供給する。PMOSトランジスタMP2、MP3は、ソースを電源Vddにそれぞれ接続し、互いのゲートとドレインとを交互に接続する。

【0075】

NMOSトランジスタMN1は、ドレインをPMOSトランジスタMP1、MP2のドレイン、インバータ回路INV1の入力端、排他的論理和回路EXOR1の一方の入力端に接続し、ゲートを入力端子INaに接続し、ソースをNMOSトランジスタMN2のドレインに接続する。NMOSトランジスタMN2は、ゲートを入力端子INbに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。インバータ回路INV1の出力端は、出力端子OUT1に接続される。ここで入力端子INa、INbにそれぞれ与えられる信号の論理値をA、Bとする。

【0076】

NMOSトランジスタMN3は、ドレインをPMOSトランジスタMP3、MP4のドレイン、インバータ回路INV2の入力端、排他的論理和回路EXOR1の他方の入力端に接続し、ゲートを端子INabに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。NMOSトランジスタMN4は、ドレインをNMOSトランジスタMP3、MP4のドレインに接続し、ゲートを端子INbbに接続し、ソースをNMOSトランジスタMN5のドレインに接続する。インバータ回路INV2の出力端は、出力端子OUT2に接続される。排他的論理和回路EXOR1の出力端は、出力端子OUT3に接続される。ここで入力端子INab、INbbにそれぞれ与えられる信号の論理値をAb、Bbとし、論理値Ab、Bbをそれぞれ論理値A、Bの否定論理とする。

【0077】

AND回路AND1は、一方の入力端に速度評価用クロック信号φを供給し、他方の入力端に制御部15からパワーゲーティング用の信号Spgを供給し、出力端をNMOSトランジスタMN5のゲートに接続する。NMOSトランジスタMN5のソースは接地される。NMOSトランジスタMN6は、ソースを接地し、ゲートに信号Spgを供給し、ドレインをインバータ回路INV1、INV2、排他的論理和回路EXOR1のそれぞれの接地側電源供給端子に接続する。

【0078】

次に、以上のような構成の単位論理ゲート回路の動作について説明する。図12は、本発明の第5の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。図12において、速度評価用クロック信号φがLレベルである期間は、プリチャージ期間であり、PMOSトランジスタMP1、MP4がオンし、NMOSトランジスタMN5がオフし、インバータ回路INV1、INV2の入力端は、Hレベルになる。したがって、インバータ回路INV1、INV2の出力端、すなわち出力端子OUT1、OUT2は、Lレベルとなる。

【0079】

速度評価用クロック信号φがHレベルである期間は、遅延時間の判定期間であり、PMOSトランジスタMP1、MP4がオフし、NMOSトランジスタMN5がオンする。したがって、判定期間では、出力端子OUT1からは、論理値A、Bの論理積A*Bが出力される。また、出力端子OUT2からは、論理値Ab、Bbの論理和Ab+Bb、すなわちA、Bの論理積の否定論理である(A*B)bが出力される。このように単位論理ゲート回路は、一方の入出力論理値に対しそれぞれ否定論理を表す他方の入出力論理値を備える相補的に動作する論理回路で構成され、二線式論理回路として機能する。なお、図12において、出力端子OUT1、OUT2の出力A*B、(A*B)bは、単位論理ゲート回路内部の遅延があるものとして示される。

【0080】

なお、図2のフリップフロップ回路11あるいは図5におけるフリップフロップ回路FF2a〜FF2dでは、正論理側(Q)のみしか出力していないが、上記の否定論理側(Qb)も出力可能とするように構成することが好ましい。

【0081】

以上のように動作する単位論理ゲート回路は、速度評価用クロック信号φの論理レベルに応じて動作する二線式論理回路のダイナミック回路として構成され、遅延検出部による遅延時間検出時にダイナミック回路として機能する。一方、通常動作時には、速度評価用クロック信号φをHレベルに保ちスタティック回路として機能する。

【0082】

なお、判定期間において、排他的論理和回路EXOR1の出力端、すなわち出力端子OUT3は、論理値A、Bの排他的論理和を出力し、単位論理ゲート回路内部の遅延があるものとして示される。この場合、遅延路の最終段の単位論理ゲート回路において、論理値A、Bの排他的論理和の出力OUT3の遅延時間(例えば立ち上がり時間p1、p2)は、異なる遅延路同士で異なり遅延路のばらつきによって例えばOUT3、OUT3’のようになる。

【0083】

このような遅延路のばらつきによる遅延時間の長短は、実施例2において説明したような遅延検出部14と制御回路15とによって検出され、遅延時間の最速値あるいは中央値となるパス(遅延路)が選定される。

【0084】

また、第5の実施例の単位論理ゲート回路を実施例1の組み合わせ論理回路21に適用する場合、排他的論理和回路EXOR1は不要である。

【実施例6】

【0085】

図13は、本発明の第6の実施例に係る単位論理ゲート回路の回路図である。図13に示す単位論理ゲート回路は、図2の組み合わせ論理回路21あるいは図5の組み合わせ論理回路22a〜22dを構成する最小要素となる回路であって、相補的に動作するAND回路を構成する。

【0086】

単位論理ゲート回路は、PMOSトランジスタMP5、MP6、インバータ回路INV3、INV4、NAND回路NAND1、NOR回路NOR1、排他的論理和回路EXOR2を備える。ただし、排他的論理和回路EXOR2は、図1の遅延路を構成する組み合わせ論理回路における最終段、すなわち同期動作回路12に隣接する単位論理ゲート回路においてのみ存在するものとする。

【0087】

PMOSトランジスタMP5、MP6は、ソースを電源Vddにそれぞれ接続し、制御部15からパワーゲーティング用の信号Spg1、Spg2をそれぞれのゲートに供給する。PMOSトランジスタMP5は、ドレインをインバータ回路INV3、NAND回路NAND1のそれぞれの電源供給端に接続する。PMOSトランジスタMP6は、ドレインをインバータ回路INV4、NOR回路NOR1、排他的論理和回路EXOR2のそれぞれの電源供給端に接続する。

【0088】

NAND回路NAND1は、一方の入力端を入力端子INaに接続し、他方の入力端を入力端子INbに接続し、出力端をインバータ回路INV3の入力端および排他的論理和回路EXOR2の一方の入力端に接続する。インバータ回路INV3は、出力端を出力端子OUT1に接続する。

【0089】

NOR回路NOR1は、一方の入力端を入力端子INabに接続し、他方の入力端を入力端子INbbに接続し、出力端をインバータ回路INV4の入力端および排他的論理和回路EXOR2の他方の入力端に接続する。インバータ回路INV4は、出力端を出力端子OUT2に接続する。排他的論理和回路EXOR2は、出力端を出力端子OUT3に接続する。ここで入力端子INa、INbにそれぞれ与えられる信号の論理値をA、Bとする。また、入力端子INab、INbbにそれぞれ与えられる信号の論理値をAb、Bbとし、論理値Ab、Bbをそれぞれ論理値A、Bの否定論理とする。

【0090】

なお、図2のフリップフロップ回路FF11あるいは図5におけるフリップフロップ回路FF2a〜FF2dでは、正論理側(Q)のみしか出力していないが、上記の否定論理側(Qb)も出力可能とするように構成することが好ましい。図14は、本発明の第6の実施例に係る単位論理ゲート回路の初段の駆動回路の回路図であり、フリップフロップ回路FF5、AND回路AND2、AND3を備える。フリップフロップ回路FF5は、図2のフリップフロップ回路FF11あるいは図5におけるフリップフロップ回路FF2a〜FF2dに対応する。AND回路AND2は、フリップフロップ回路FF5の正論理側出力とタイミング信号Tmとの論理積を求めて正論理側出力Qとする。AND回路AND3は、フリップフロップ回路FF5の否定論理側出力とタイミング信号Tmとの論理積を求めて否定論理側出力Qbとする。Q、Qbは単位論理ゲート回路に入力される。

【0091】

次に、以上のような構成の単位論理ゲート回路の動作について説明する。図15は、本発明の第6の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。図15において、タイミング信号TmがHレベルである期間は、単位論理ゲート回路の遅延判定期間および通常動作期間であり、入力端子INa、INb、INab、INbbにそれぞれ与えられる論理値に応じた論理演算結果が出力端子OUT1、OUT2に出力される。すなわち、出力端子OUT1からは、論理値A、Bの論理積A*Bが出力される。また、出力端子OUT2からは、論理値Ab、Bbの論理和Ab+Bb、すなわちA、Bの論理積の否定論理である(A*B)bが出力される。

【0092】

以上のように動作する単位論理ゲート回路は、実施例5と同様に相補的に動作する論理回路で構成され、二線式論理回路として機能する。ただし、実施例5の速度評価用クロック信号φが不要であるスタティック回路として構成され、遅延時間検出時に二線式論理のスタティック回路として機能する。また、通常動作時には単線式論理のスタティック回路として機能する。すなわち、遅延時間検出時には、パワーゲーティング用の信号Spg1、Spg2のレベルをLレベルとしてPMOSトランジスタMP5、MP6をオンとする。したがって、NAND回路NAND1、インバータ回路INV3からなる経路と、NOR回路NOR1、インバータ回路INV4からなる経路の双方が機能し、二線式論理回路を形成する。一方、通常動作時には、パワーゲーティング用の信号Spg1(あるいは信号Spg2)のレベルをのみをLレベルとしてPMOSトランジスタMP5(あるいはMP6)だけをオンとする。したがって、NAND回路NAND1、インバータ回路INV3(NOR回路NOR1、インバータ回路INV4)からなる一つの経路のみが機能し、単線式論理回路を形成する。

【0093】

なお、遅延判定期間において、排他的論理和回路EXOR2の出力端、すなわち出力端子OUT3は、論理値A、Bの排他的論理和を出力し、単位論理ゲート回路内部の遅延があるものとして示される。この場合、遅延路の最終段の単位論理ゲート回路において、異なる遅延路同士で論理値A、Bの排他的論理和の出力OUT3の遅延時間は、遅延路のばらつきによって異なる。

【0094】

このような遅延路のばらつきによる遅延時間の長短は、実施例2において説明したような遅延検出部14と制御回路15とによって検出され、遅延時間の最速値あるいは中央値となるパス(遅延路)が選定される。

【0095】

また、第6の実施例の単位論理ゲート回路を実施例1の組み合わせ論理回路21に適用する場合、排他的論理和回路EXOR2は不要である。

【0096】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【図面の簡単な説明】

【0097】

【図1】本発明の実施形態に係る半導体集積回路装置の構成を示す図である。

【図2】本発明の第1の実施例に係る半導体集積回路装置の主要部の回路図である。

【図3】本発明の第1の実施例に係る半導体集積回路装置の主要部の動作を表すタイミングチャートである。

【図4】本発明の第1の実施例に係る半導体集積回路装置の制御部の動作を表すフローチャートである。

【図5】本発明の第2の実施例に係る半導体集積回路装置の主要部の回路図である。

【図6】本発明の第2の実施例に係る制御部の第1の動作を表すフローチャートである。

【図7】本発明の第2の実施例に係る制御部の第2の動作を表すフローチャートである。

【図8】本発明の第3の実施例に係る制御部の動作を表すフローチャートである。

【図9】本発明の第4の実施例に係る電源電圧制御遅延モニタの回路図である。

【図10】本発明の第4の実施例に係る電源電圧制御遅延モニタの動作を表すタイミングチャートである。

【図11】本発明の第5の実施例に係る単位論理ゲート回路の回路図である。

【図12】本発明の第5の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。

【図13】本発明の第6の実施例に係る単位論理ゲート回路の回路図である。

【図14】本発明の第6の実施例に係る単位論理ゲート回路の初段の駆動回路の回路図である。

【図15】本発明の第6の実施例に係る単位論理ゲート回路の動作を表すタイミングチャートである。

【符号の説明】

【0098】

11、12 同期動作回路

13a、13b、・・13n 遅延路

14 遅延検出部

15 制御部

21、22a〜22d 組み合わせ論理回路

25 レプリカ回路

26、27 遅延回路

AND0〜AND3 AND回路

EXOR0、EXOR1、EXOR2 排他的論理和回路

FF11〜FF13、FF21、FF23、FF24、FF2a〜FF2d、FF3a〜FF3d、FF4、FF5 フリップフロップ回路

INV1〜INV4 インバータ回路

MN1〜MN6 NMOSトランジスタ

SEL1〜SEL3 セレクタ

MP1〜MP6 PMOSトランジスタ

【特許請求の範囲】

【請求項1】

クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路と、

前記複数の遅延路におけるそれぞれの遅延時間を検出する遅延検出部と、

前記遅延検出部の検出結果に基づいて前記複数の遅延路の内の一の遅延路を選択し、選択した前記一の遅延路以外における信号伝送を阻止するように制御する制御部と、

を備えることを特徴とする半導体集積回路装置。

【請求項2】

前記複数の遅延路は、電源が供給されて動作する能動回路を含んでそれぞれ構成され、

前記制御部は、通常動作時に前記一の遅延路以外における遅延路中の前記能動回路への電源供給を停止することを特徴とする請求項1記載の半導体集積回路装置。

【請求項3】

前記能動回路は、組み合わせ論理回路として構成されることを特徴とする請求項2記載の半導体集積回路装置。

【請求項4】

前記制御部は、前記複数の遅延路の内の遅延時間が最小値となる遅延路を前記一の遅延路として選択することを特徴とする請求項1または2記載の半導体集積回路装置。

【請求項5】

前記制御部は、前記複数の遅延路の内の遅延時間が中央値となる遅延路を前記一の遅延路として選択することを特徴とする請求項1または2記載の半導体集積回路装置。

【請求項6】

前記制御部は、選択された前記一の遅延路における電源供給電圧を所定の電圧まで低下させることを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項7】

前記制御部は、前記複数の遅延路への電源供給電圧に対応させて前記一の遅延路を選択することを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項8】

前記遅延検出部は、前記複数の遅延路にそれぞれ対応させてラッチタイミングのそれぞれ異なる2つのレジスタを備え、

前記制御部は、前記ラッチタイミングを変化させていった場合における前記2つのレジスタのラッチデータに基づいて得た前記複数の遅延路における遅延時間順に基づいて前記一の遅延路を選択することを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項9】

前記2つのレジスタの一方は、通常動作時に前記クロック信号のラッチタイミングで動作することを特徴とする請求項8記載の半導体集積回路装置。

【請求項10】

前記遅延路は、相補的に動作する論理回路で構成され、前記遅延検出部による遅延時間検出時には相補的に動作するように機能することを特徴とする請求項1乃至3のいずれか一に記載の半導体集積回路装置。

【請求項11】

前記遅延路は、二線式論理回路で構成され、前記遅延検出部による遅延時間検出時に前記二線式論理回路として機能し、通常動作時に前記二線式論理回路または単線式論理回路として機能することを特徴とする請求項1、2、3、10のいずれか一に記載の半導体集積回路装置。

【請求項12】

前記遅延検出部は、遅延時間検出時に前記二線式論理回路における論理値の変化順を検出することを特徴とする請求項11記載の半導体集積回路装置。

【請求項13】

前記遅延路は、ダイナミック回路として構成され、前記遅延検出部による遅延時間検出時に前記ダイナミック回路として機能し、通常動作時にスタティック回路として機能することを特徴とする請求項11記載の半導体集積回路装置。

【請求項14】

前記遅延路は、スタティック回路として構成され、前記遅延検出部による遅延時間検出時および通常動作時にスタティック回路として機能することを特徴とする請求項11記載の半導体集積回路装置。

【請求項15】

クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路の制御方法であって、

前記複数の遅延路におけるそれぞれの遅延時間を検出するステップと、

前記遅延時間の検出結果に基づいて前記複数の遅延路の内の一の遅延路を選択するステップと、

選択された前記一の遅延路以外における信号伝送を阻止するように制御するステップと、

を含むことを特徴とする遅延路の制御方法。

【請求項1】

クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路と、

前記複数の遅延路におけるそれぞれの遅延時間を検出する遅延検出部と、

前記遅延検出部の検出結果に基づいて前記複数の遅延路の内の一の遅延路を選択し、選択した前記一の遅延路以外における信号伝送を阻止するように制御する制御部と、

を備えることを特徴とする半導体集積回路装置。

【請求項2】

前記複数の遅延路は、電源が供給されて動作する能動回路を含んでそれぞれ構成され、

前記制御部は、通常動作時に前記一の遅延路以外における遅延路中の前記能動回路への電源供給を停止することを特徴とする請求項1記載の半導体集積回路装置。

【請求項3】

前記能動回路は、組み合わせ論理回路として構成されることを特徴とする請求項2記載の半導体集積回路装置。

【請求項4】

前記制御部は、前記複数の遅延路の内の遅延時間が最小値となる遅延路を前記一の遅延路として選択することを特徴とする請求項1または2記載の半導体集積回路装置。

【請求項5】

前記制御部は、前記複数の遅延路の内の遅延時間が中央値となる遅延路を前記一の遅延路として選択することを特徴とする請求項1または2記載の半導体集積回路装置。

【請求項6】

前記制御部は、選択された前記一の遅延路における電源供給電圧を所定の電圧まで低下させることを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項7】

前記制御部は、前記複数の遅延路への電源供給電圧に対応させて前記一の遅延路を選択することを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項8】

前記遅延検出部は、前記複数の遅延路にそれぞれ対応させてラッチタイミングのそれぞれ異なる2つのレジスタを備え、

前記制御部は、前記ラッチタイミングを変化させていった場合における前記2つのレジスタのラッチデータに基づいて得た前記複数の遅延路における遅延時間順に基づいて前記一の遅延路を選択することを特徴とする請求項4または5記載の半導体集積回路装置。

【請求項9】

前記2つのレジスタの一方は、通常動作時に前記クロック信号のラッチタイミングで動作することを特徴とする請求項8記載の半導体集積回路装置。

【請求項10】

前記遅延路は、相補的に動作する論理回路で構成され、前記遅延検出部による遅延時間検出時には相補的に動作するように機能することを特徴とする請求項1乃至3のいずれか一に記載の半導体集積回路装置。

【請求項11】

前記遅延路は、二線式論理回路で構成され、前記遅延検出部による遅延時間検出時に前記二線式論理回路として機能し、通常動作時に前記二線式論理回路または単線式論理回路として機能することを特徴とする請求項1、2、3、10のいずれか一に記載の半導体集積回路装置。

【請求項12】

前記遅延検出部は、遅延時間検出時に前記二線式論理回路における論理値の変化順を検出することを特徴とする請求項11記載の半導体集積回路装置。

【請求項13】

前記遅延路は、ダイナミック回路として構成され、前記遅延検出部による遅延時間検出時に前記ダイナミック回路として機能し、通常動作時にスタティック回路として機能することを特徴とする請求項11記載の半導体集積回路装置。

【請求項14】

前記遅延路は、スタティック回路として構成され、前記遅延検出部による遅延時間検出時および通常動作時にスタティック回路として機能することを特徴とする請求項11記載の半導体集積回路装置。

【請求項15】

クロック信号に同期して動作する2つの同期動作回路の間を並列形態で接続して信号伝送可能とされる複数の遅延路の制御方法であって、

前記複数の遅延路におけるそれぞれの遅延時間を検出するステップと、

前記遅延時間の検出結果に基づいて前記複数の遅延路の内の一の遅延路を選択するステップと、

選択された前記一の遅延路以外における信号伝送を阻止するように制御するステップと、

を含むことを特徴とする遅延路の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2010−118748(P2010−118748A)

【公開日】平成22年5月27日(2010.5.27)

【国際特許分類】

【出願番号】特願2008−288846(P2008−288846)

【出願日】平成20年11月11日(2008.11.11)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年5月27日(2010.5.27)

【国際特許分類】

【出願日】平成20年11月11日(2008.11.11)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]