半導体集積回路装置の製造方法

【課題】LSIプロセスによる制約のない最上位配線層を提供することで長距離配線における信号遅延を低減可能な半導体集積回路装置の製造方法を提供する。

【解決手段】

半導体集積回路基板を提供する過程は、半導体集積回路用ベース基板11上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層12を形成する過程と、半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッド13を形成する過程とからなる。配線基板を提供する過程は、配線基板用ベース基板1上に、半導体集積回路用の最上位配線層となる厚膜配線層3をメッキ形成する過程と、厚膜配線層上に、該厚膜配線層に接続される接合バンプ6を形成する過程とからなる。そして、半導体集積回路基板の接続パッドが形成される面と配線基板の接合バンプが形成される面とを対向させ接続パッド及び接合バンプを位置合わせして接合する。

【解決手段】

半導体集積回路基板を提供する過程は、半導体集積回路用ベース基板11上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層12を形成する過程と、半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッド13を形成する過程とからなる。配線基板を提供する過程は、配線基板用ベース基板1上に、半導体集積回路用の最上位配線層となる厚膜配線層3をメッキ形成する過程と、厚膜配線層上に、該厚膜配線層に接続される接合バンプ6を形成する過程とからなる。そして、半導体集積回路基板の接続パッドが形成される面と配線基板の接合バンプが形成される面とを対向させ接続パッド及び接合バンプを位置合わせして接合する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体集積回路装置の製造方法に関し、特に、最上位配線層を厚膜配線で構成する半導体集積回路装置の製造方法に関する。

【背景技術】

【0002】

集積度の高い大規模集積回路装置(LSI)においては、1つの平面上で複雑な配線を行うにはスペースが足りないため、多数の配線層を用いて3次元的に配線を行う多層配線構造が採用されている。多層配線構造では、下位層ほど配線が細く密度が濃いが、上位層にいくほど配線が太く密度が薄くなっている。また、上位層の配線ほど離れたトランジスタ間を接続するのに用いられるため、配線長が長くなっている。高性能で多機能なLSIを1チップに集積するシステムオンチップ(SoC)技術においては、チップサイズが大きくなることから配線長がさらに増加する傾向にある。

【0003】

LSIの高速化を妨げている原因の一つに信号遅延の問題がある。これまでの信号遅延の問題は、トランジスタのゲートにおけるゲート遅延が支配的であった。しかしながら、半導体集積回路の微細化が進むにつれ、ゲート遅延よりも配線長が長くなることによる長距離配線における信号遅延の影響が支配的になってきている。配線における信号遅延時間は配線抵抗と配線間容量に比例するため、LSIの高速化には、配線の低抵抗化と配線間容量の低減が不可欠である。このため、配線遅延を低減するための新たな多層配線技術の開発が課題となっている(非特許文献1)。

【0004】

【非特許文献1】特許庁編「平成15年度 特許出願技術動向調査報告書 LSIの多層配線技術」平成16年3月

【発明の開示】

【発明が解決しようとする課題】

【0005】

配線遅延を低減するためには、配線層数を多くし、トータルの配線長を短くして配線抵抗を低減することも考えられるが、配線層数の増加は製造コストの観点から限界があり、現実的な解ではない。また、現状のLSI配線形成プロセスでは配線の膜厚は最大で1〜2μm程度が限界であり、配線の低抵抗化にも限界があった。したがって、今後益々顕在化する長距離配線における信号遅延の影響を低減することが望まれていた。

【0006】

本発明は、斯かる実情に鑑み、LSIプロセスによる制約のない最上位配線層を提供することで長距離配線における信号遅延を低減可能な半導体集積回路装置の製造方法を提供しようとするものである。

【課題を解決するための手段】

【0007】

上述した本発明の目的を達成するために、本発明による半導体集積回路装置の製造方法は、半導体集積回路基板と配線基板とを提供する過程であって、半導体集積回路基板を提供する過程は、半導体集積回路用ベース基板上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層を形成する過程と、半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッドを形成する過程と、を有し、配線基板を提供する過程は、配線基板用ベース基板上に、半導体集積回路用の最上位配線層となる厚膜配線層をメッキ形成する過程と、厚膜配線層上に、該厚膜配線層に接続される接合バンプを形成する過程と、を有する、半導体集積回路基板と配線基板とを提供する過程と、半導体集積回路基板の接続パッドが形成される面と配線基板の接合バンプが形成される面とを対向させる過程と、接続パッド及び接合バンプを位置合わせして接合する過程と、を具備するものである。

【0008】

ここで、厚膜配線層をメッキ形成する過程は、配線基板用ベース基板上に第1絶縁層を形成し、該第1絶縁層上に厚膜配線層をメッキ形成する過程であっても良い。

【0009】

また、第1絶縁層は、低誘電率絶縁層からなっても良い。

【0010】

また、第1絶縁層は、膜厚が10μm以上であっても良い。

【0011】

さらに、接合バンプを形成する過程は、厚膜配線層上に第2絶縁層を形成し、該第2絶縁層に開口部をパターンニング形成し、該開口部に接合バンプを形成する過程であっても良い。

【0012】

さらにまた、半導体集積回路用ベース基板と配線基板用ベース基板は、同一の材料からなるものであっても良い。

【0013】

さらに、接合する過程の後に、アンダーフィルを流入する過程を具備するものであっても良い。

【0014】

またさらに、配線基板用ベース基板上に、インダクタ素子を形成する過程を具備するものであっても良い。

【0015】

また、配線基板には、複数の厚膜配線層がメッキ形成されても良い。

【発明の効果】

【0016】

本発明の半導体集積回路装置の製造方法には、LSIプロセスによる制約のない厚い低抵抗な最上位配線層を提供することで、長距離配線における信号遅延を低減可能であるという利点がある。また、別途用意した基板上に厚膜配線層を形成するだけなので、低コストで製造可能であるという利点もある。さらに、配線基板側にインダクタ素子等の受動素子を形成することも可能であるという利点もある。

【発明を実施するための最良の形態】

【0017】

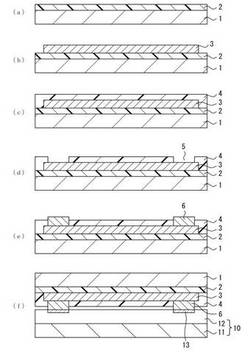

以下、本発明を実施するための最良の形態を図示例と共に説明する。図1は、本発明の半導体集積回路装置の配線基板の製造方法を説明するための図であり、図1(a)〜図1(f)は各過程における半導体集積回路装置の配線基板の横断面図である。なお、図1では半導体デバイスを有するLSI基板の製造過程については省略してあるが、本発明は特定のLSI基板の製造方法に限定されるものではなく、一般的なLSI基板の製造方法を適用すれば良い。

【0018】

まず、図1(a)に示されるように、本発明の半導体集積回路装置の配線基板は、配線基板用ベース基板1上に第1絶縁層2を形成する。配線基板用ベース基板1としては、Si等からなれば良いが、GaAs等からなる化合物半導体からなるものであっても良い。さらに、ガラスやプラスチック等の絶縁体からなるものであっても良い。なお、配線基板用ベース基板1がガラスやプラスチック等の絶縁体からなる場合には、絶縁層の作用が配線基板用ベース基板1に含まれることになるので、物理的な第1絶縁層2は用いなくても良い。

【0019】

第1絶縁層2は、例えばポリイミドやエポキシ、シリコーン樹脂等からなるものであれば良く、その膜厚は例えば10μm〜20μm、好ましくは10μmであれば良い。第1絶縁層2は、回転塗布法や印刷法、ラミネート法等により形成すれば良い。さらに、第1絶縁層2は、低誘電率絶縁層(Low−k絶縁層)からなることが好ましい。

【0020】

次に、図1(b)に示されるように、第1絶縁層2の上に半導体集積回路用の最上位配線層となる厚膜配線層3をメッキ形成する。厚膜配線層3は、例えばCu等の低抵抗材料からなるものであり、その膜厚は例えば10μm〜50μmである。厚膜配線層3は、例えば第1絶縁層2の全面にTi,Cr等からなるシード層を形成後、厚膜配線に相当するパターンをフォトリソグラフィ技術によってエッチング開口し、メッキ法により開口にCu等を成膜すれば良い。

【0021】

このように、本発明による半導体集積回路装置の最上位配線層は、LSI基板とは別の基板上に形成するため、LSIプロセスに制限されることなく、任意の膜厚で配線を形成することが可能となる。また、既存の半導体製造プロセスを用いることが可能であるので、安価に製造可能である。ここで、LSIプロセスでは複数の井桁状の配線により多層配線が形成されるが、本発明によれば、LSIプロセスには拠らないので最上位配線は任意の形状の配線とすることが可能であるため、任意の角度に曲げたり曲線の配線とすることも可能となる。

【0022】

さらに、最上位配線層は単層である必要はなく、必要により複数の厚膜配線層が形成されるものであっても構わない。これにより、最上位配線層だけでなく、さらにその下の配線層も含めて厚膜配線化、すなわち低抵抗化を図ることが可能となる。また、配線基板には、厚膜配線だけでなく、インダクタ素子等の受動素子を形成することも可能である。例えば、既存の半導体プロセスを用いて、メアンダ形状やスパイラル形状等のインダクタ素子を配線基板用ベース基板上にパターンニング形成することが可能である。これにより、Q値の高い高性能なインダクタも含まれる半導体集積回路装置が製造可能となる。

【0023】

次に、図1(c)に示されるように、厚膜配線層3上に第2絶縁層4を形成する。第2絶縁層4は、第1絶縁層と同様、例えばポリイミドやエポキシ、シリコーン樹脂等からなるものであれば良く、その膜厚は例えば10μm〜20μmであれば良い。第2絶縁層4は、第1配線層と同様、回転塗布法や印刷法、ラミネート法等により形成すれば良い。

【0024】

そして、図1(d)に示されるように、第2絶縁層4に開口部5が形成される。開口部5は、LSI基板側の半導体集積回路の下層配線と接続される位置に形成される。開口部5には、後述の接合バンプが形成される。開口部5は、例えば第2絶縁層4をフォトリソグラフィ技術によりパターンニングして形成されれば良い。

【0025】

その後、図1(e)に示されるように、開口部5に接合バンプ6が形成される。接合バンプ6は、Au等からなるものであり、例えばボンディング法によるスタッドバンプからなるものである。また、蒸着法やメッキ法、印刷法等により形成しても良い。なお、図示例では第2絶縁層4を設けて開口部5に接合バンプ6を形成したが、本発明はこれに限定されず、厚膜配線層3上に直接接合バンプ6を形成しても良い。

【0026】

一方、半導体集積回路を有するLSI基板10は、図1(f)に示されるように、半導体集積回路用ベース基板11上に半導体集積回路及び半導体集積回路用の最上位配線層を含まない配線層12(多層配線層)からなる。この配線層12上には、配線層に接続される接続パッド13が形成されている。

【0027】

図1(f)に示されるように、上述した図1(a)〜図1(e)のように形成された配線基板及びLSI基板は、LSI基板の接続パッド13が形成される面と配線基板の接合バンプ6が形成される面とが対向させられる。そして、接続パッド13及び接合バンプ6が位置合わせされて接合される。接合は、例えば、フリップチップボンダを用いて超音波接合されれば良い。これにより、LSI基板の配線層と配線基板の厚膜配線層が電気的に接続される。接合後、LSI基板と配線基板の間にアンダーフィルを流入しても良い。これにより、ヒートサイクル等の熱的応力に対する接続信頼性や衝撃や折り曲げ等の物理的応力に対する接続信頼性の向上が図れる。

【0028】

ここで、半導体集積回路用ベース基板11と配線基板用ベース基板1とは、異なる材料からなるものであっても構わないが、同一の材料からなることが好ましい。同一の材料で構成することにより、ベース基板の熱膨張率が等しくなるので接合バンプ6と接続パッド13の接合部のクラック等が起こり難くなる。

【0029】

なお、本発明の半導体集積回路装置の製造方法は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。

【図面の簡単な説明】

【0030】

【図1】図1は、本発明の半導体集積回路装置の配線基板の製造方法を説明するための図であり、図1(a)〜図1(f)は各過程における半導体集積回路装置の配線基板の横断面図である。

【符号の説明】

【0031】

1 配線基板用ベース基板

2 第1絶縁層

3 厚膜配線層

4 第2絶縁層

5 開口部

6 接合バンプ

10 LSI基板

11 半導体集積回路用ベース基板

12 配線層

13 接続パッド

【技術分野】

【0001】

本発明は半導体集積回路装置の製造方法に関し、特に、最上位配線層を厚膜配線で構成する半導体集積回路装置の製造方法に関する。

【背景技術】

【0002】

集積度の高い大規模集積回路装置(LSI)においては、1つの平面上で複雑な配線を行うにはスペースが足りないため、多数の配線層を用いて3次元的に配線を行う多層配線構造が採用されている。多層配線構造では、下位層ほど配線が細く密度が濃いが、上位層にいくほど配線が太く密度が薄くなっている。また、上位層の配線ほど離れたトランジスタ間を接続するのに用いられるため、配線長が長くなっている。高性能で多機能なLSIを1チップに集積するシステムオンチップ(SoC)技術においては、チップサイズが大きくなることから配線長がさらに増加する傾向にある。

【0003】

LSIの高速化を妨げている原因の一つに信号遅延の問題がある。これまでの信号遅延の問題は、トランジスタのゲートにおけるゲート遅延が支配的であった。しかしながら、半導体集積回路の微細化が進むにつれ、ゲート遅延よりも配線長が長くなることによる長距離配線における信号遅延の影響が支配的になってきている。配線における信号遅延時間は配線抵抗と配線間容量に比例するため、LSIの高速化には、配線の低抵抗化と配線間容量の低減が不可欠である。このため、配線遅延を低減するための新たな多層配線技術の開発が課題となっている(非特許文献1)。

【0004】

【非特許文献1】特許庁編「平成15年度 特許出願技術動向調査報告書 LSIの多層配線技術」平成16年3月

【発明の開示】

【発明が解決しようとする課題】

【0005】

配線遅延を低減するためには、配線層数を多くし、トータルの配線長を短くして配線抵抗を低減することも考えられるが、配線層数の増加は製造コストの観点から限界があり、現実的な解ではない。また、現状のLSI配線形成プロセスでは配線の膜厚は最大で1〜2μm程度が限界であり、配線の低抵抗化にも限界があった。したがって、今後益々顕在化する長距離配線における信号遅延の影響を低減することが望まれていた。

【0006】

本発明は、斯かる実情に鑑み、LSIプロセスによる制約のない最上位配線層を提供することで長距離配線における信号遅延を低減可能な半導体集積回路装置の製造方法を提供しようとするものである。

【課題を解決するための手段】

【0007】

上述した本発明の目的を達成するために、本発明による半導体集積回路装置の製造方法は、半導体集積回路基板と配線基板とを提供する過程であって、半導体集積回路基板を提供する過程は、半導体集積回路用ベース基板上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層を形成する過程と、半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッドを形成する過程と、を有し、配線基板を提供する過程は、配線基板用ベース基板上に、半導体集積回路用の最上位配線層となる厚膜配線層をメッキ形成する過程と、厚膜配線層上に、該厚膜配線層に接続される接合バンプを形成する過程と、を有する、半導体集積回路基板と配線基板とを提供する過程と、半導体集積回路基板の接続パッドが形成される面と配線基板の接合バンプが形成される面とを対向させる過程と、接続パッド及び接合バンプを位置合わせして接合する過程と、を具備するものである。

【0008】

ここで、厚膜配線層をメッキ形成する過程は、配線基板用ベース基板上に第1絶縁層を形成し、該第1絶縁層上に厚膜配線層をメッキ形成する過程であっても良い。

【0009】

また、第1絶縁層は、低誘電率絶縁層からなっても良い。

【0010】

また、第1絶縁層は、膜厚が10μm以上であっても良い。

【0011】

さらに、接合バンプを形成する過程は、厚膜配線層上に第2絶縁層を形成し、該第2絶縁層に開口部をパターンニング形成し、該開口部に接合バンプを形成する過程であっても良い。

【0012】

さらにまた、半導体集積回路用ベース基板と配線基板用ベース基板は、同一の材料からなるものであっても良い。

【0013】

さらに、接合する過程の後に、アンダーフィルを流入する過程を具備するものであっても良い。

【0014】

またさらに、配線基板用ベース基板上に、インダクタ素子を形成する過程を具備するものであっても良い。

【0015】

また、配線基板には、複数の厚膜配線層がメッキ形成されても良い。

【発明の効果】

【0016】

本発明の半導体集積回路装置の製造方法には、LSIプロセスによる制約のない厚い低抵抗な最上位配線層を提供することで、長距離配線における信号遅延を低減可能であるという利点がある。また、別途用意した基板上に厚膜配線層を形成するだけなので、低コストで製造可能であるという利点もある。さらに、配線基板側にインダクタ素子等の受動素子を形成することも可能であるという利点もある。

【発明を実施するための最良の形態】

【0017】

以下、本発明を実施するための最良の形態を図示例と共に説明する。図1は、本発明の半導体集積回路装置の配線基板の製造方法を説明するための図であり、図1(a)〜図1(f)は各過程における半導体集積回路装置の配線基板の横断面図である。なお、図1では半導体デバイスを有するLSI基板の製造過程については省略してあるが、本発明は特定のLSI基板の製造方法に限定されるものではなく、一般的なLSI基板の製造方法を適用すれば良い。

【0018】

まず、図1(a)に示されるように、本発明の半導体集積回路装置の配線基板は、配線基板用ベース基板1上に第1絶縁層2を形成する。配線基板用ベース基板1としては、Si等からなれば良いが、GaAs等からなる化合物半導体からなるものであっても良い。さらに、ガラスやプラスチック等の絶縁体からなるものであっても良い。なお、配線基板用ベース基板1がガラスやプラスチック等の絶縁体からなる場合には、絶縁層の作用が配線基板用ベース基板1に含まれることになるので、物理的な第1絶縁層2は用いなくても良い。

【0019】

第1絶縁層2は、例えばポリイミドやエポキシ、シリコーン樹脂等からなるものであれば良く、その膜厚は例えば10μm〜20μm、好ましくは10μmであれば良い。第1絶縁層2は、回転塗布法や印刷法、ラミネート法等により形成すれば良い。さらに、第1絶縁層2は、低誘電率絶縁層(Low−k絶縁層)からなることが好ましい。

【0020】

次に、図1(b)に示されるように、第1絶縁層2の上に半導体集積回路用の最上位配線層となる厚膜配線層3をメッキ形成する。厚膜配線層3は、例えばCu等の低抵抗材料からなるものであり、その膜厚は例えば10μm〜50μmである。厚膜配線層3は、例えば第1絶縁層2の全面にTi,Cr等からなるシード層を形成後、厚膜配線に相当するパターンをフォトリソグラフィ技術によってエッチング開口し、メッキ法により開口にCu等を成膜すれば良い。

【0021】

このように、本発明による半導体集積回路装置の最上位配線層は、LSI基板とは別の基板上に形成するため、LSIプロセスに制限されることなく、任意の膜厚で配線を形成することが可能となる。また、既存の半導体製造プロセスを用いることが可能であるので、安価に製造可能である。ここで、LSIプロセスでは複数の井桁状の配線により多層配線が形成されるが、本発明によれば、LSIプロセスには拠らないので最上位配線は任意の形状の配線とすることが可能であるため、任意の角度に曲げたり曲線の配線とすることも可能となる。

【0022】

さらに、最上位配線層は単層である必要はなく、必要により複数の厚膜配線層が形成されるものであっても構わない。これにより、最上位配線層だけでなく、さらにその下の配線層も含めて厚膜配線化、すなわち低抵抗化を図ることが可能となる。また、配線基板には、厚膜配線だけでなく、インダクタ素子等の受動素子を形成することも可能である。例えば、既存の半導体プロセスを用いて、メアンダ形状やスパイラル形状等のインダクタ素子を配線基板用ベース基板上にパターンニング形成することが可能である。これにより、Q値の高い高性能なインダクタも含まれる半導体集積回路装置が製造可能となる。

【0023】

次に、図1(c)に示されるように、厚膜配線層3上に第2絶縁層4を形成する。第2絶縁層4は、第1絶縁層と同様、例えばポリイミドやエポキシ、シリコーン樹脂等からなるものであれば良く、その膜厚は例えば10μm〜20μmであれば良い。第2絶縁層4は、第1配線層と同様、回転塗布法や印刷法、ラミネート法等により形成すれば良い。

【0024】

そして、図1(d)に示されるように、第2絶縁層4に開口部5が形成される。開口部5は、LSI基板側の半導体集積回路の下層配線と接続される位置に形成される。開口部5には、後述の接合バンプが形成される。開口部5は、例えば第2絶縁層4をフォトリソグラフィ技術によりパターンニングして形成されれば良い。

【0025】

その後、図1(e)に示されるように、開口部5に接合バンプ6が形成される。接合バンプ6は、Au等からなるものであり、例えばボンディング法によるスタッドバンプからなるものである。また、蒸着法やメッキ法、印刷法等により形成しても良い。なお、図示例では第2絶縁層4を設けて開口部5に接合バンプ6を形成したが、本発明はこれに限定されず、厚膜配線層3上に直接接合バンプ6を形成しても良い。

【0026】

一方、半導体集積回路を有するLSI基板10は、図1(f)に示されるように、半導体集積回路用ベース基板11上に半導体集積回路及び半導体集積回路用の最上位配線層を含まない配線層12(多層配線層)からなる。この配線層12上には、配線層に接続される接続パッド13が形成されている。

【0027】

図1(f)に示されるように、上述した図1(a)〜図1(e)のように形成された配線基板及びLSI基板は、LSI基板の接続パッド13が形成される面と配線基板の接合バンプ6が形成される面とが対向させられる。そして、接続パッド13及び接合バンプ6が位置合わせされて接合される。接合は、例えば、フリップチップボンダを用いて超音波接合されれば良い。これにより、LSI基板の配線層と配線基板の厚膜配線層が電気的に接続される。接合後、LSI基板と配線基板の間にアンダーフィルを流入しても良い。これにより、ヒートサイクル等の熱的応力に対する接続信頼性や衝撃や折り曲げ等の物理的応力に対する接続信頼性の向上が図れる。

【0028】

ここで、半導体集積回路用ベース基板11と配線基板用ベース基板1とは、異なる材料からなるものであっても構わないが、同一の材料からなることが好ましい。同一の材料で構成することにより、ベース基板の熱膨張率が等しくなるので接合バンプ6と接続パッド13の接合部のクラック等が起こり難くなる。

【0029】

なお、本発明の半導体集積回路装置の製造方法は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。

【図面の簡単な説明】

【0030】

【図1】図1は、本発明の半導体集積回路装置の配線基板の製造方法を説明するための図であり、図1(a)〜図1(f)は各過程における半導体集積回路装置の配線基板の横断面図である。

【符号の説明】

【0031】

1 配線基板用ベース基板

2 第1絶縁層

3 厚膜配線層

4 第2絶縁層

5 開口部

6 接合バンプ

10 LSI基板

11 半導体集積回路用ベース基板

12 配線層

13 接続パッド

【特許請求の範囲】

【請求項1】

半導体集積回路装置の製造方法であって、該方法は、

半導体集積回路基板と配線基板とを提供する過程であって、

前記半導体集積回路基板を提供する過程は、

半導体集積回路用ベース基板上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層を形成する過程と、

前記半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッドを形成する過程と、

を有し、

前記配線基板を提供する過程は、

配線基板用ベース基板上に、前記半導体集積回路用の最上位配線層となる厚膜配線層をメッキ形成する過程と、

前記厚膜配線層上に、該厚膜配線層に接続される接合バンプを形成する過程と、

を有する、

半導体集積回路基板と配線基板とを提供する過程と、

前記半導体集積回路基板の接続パッドが形成される面と前記配線基板の接合バンプが形成される面とを対向させる過程と、

前記接続パッド及び接合バンプを位置合わせして接合する過程と、

を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項2】

請求項1に記載の半導体集積回路装置の製造方法において、前記厚膜配線層をメッキ形成する過程は、前記配線基板用ベース基板上に第1絶縁層を形成し、該第1絶縁層上に厚膜配線層をメッキ形成する過程であることを特徴とする半導体集積回路装置の製造方法。

【請求項3】

請求項2に記載の半導体集積回路装置の製造方法において、前記第1絶縁層は、低誘電率絶縁層からなることを特徴とする半導体集積回路装置の製造方法。

【請求項4】

請求項2又は請求項3に記載の半導体集積回路装置の製造方法において、前記第1絶縁層は、膜厚が10μm以上であることを特徴とする半導体集積回路装置の製造方法。

【請求項5】

請求項1乃至請求項4の何れかに記載の半導体集積回路装置の製造方法において、前記接合バンプを形成する過程は、前記厚膜配線層上に第2絶縁層を形成し、該第2絶縁層に開口部をパターンニング形成し、該開口部に接合バンプを形成する過程であることを特徴とする半導体集積回路装置の製造方法。

【請求項6】

請求項1乃至請求項5の何れかに記載の半導体集積回路装置の製造方法において、前記半導体集積回路用ベース基板と前記配線基板用ベース基板は、同一の材料からなることを特徴とする半導体集積回路装置の製造方法。

【請求項7】

請求項1乃至請求項6の何れかに記載の半導体集積回路装置の製造方法であって、さらに、前記接合する過程の後に、アンダーフィルを流入する過程を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項8】

請求項1乃至請求項7の何れかに記載の半導体集積回路装置の製造方法であって、さらに、前記配線基板用ベース基板上に、インダクタ素子を形成する過程を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項9】

請求項1乃至請求項8の何れかに記載の半導体集積回路装置の製造方法において、前記配線基板には、複数の厚膜配線層がメッキ形成されることを特徴とする半導体集積回路装置の製造方法。

【請求項1】

半導体集積回路装置の製造方法であって、該方法は、

半導体集積回路基板と配線基板とを提供する過程であって、

前記半導体集積回路基板を提供する過程は、

半導体集積回路用ベース基板上に、半導体集積回路及び該半導体集積回路用の最上位配線層を含まない配線層を形成する過程と、

前記半導体集積回路用ベース基板の配線層上に、該配線層に接続される接続パッドを形成する過程と、

を有し、

前記配線基板を提供する過程は、

配線基板用ベース基板上に、前記半導体集積回路用の最上位配線層となる厚膜配線層をメッキ形成する過程と、

前記厚膜配線層上に、該厚膜配線層に接続される接合バンプを形成する過程と、

を有する、

半導体集積回路基板と配線基板とを提供する過程と、

前記半導体集積回路基板の接続パッドが形成される面と前記配線基板の接合バンプが形成される面とを対向させる過程と、

前記接続パッド及び接合バンプを位置合わせして接合する過程と、

を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項2】

請求項1に記載の半導体集積回路装置の製造方法において、前記厚膜配線層をメッキ形成する過程は、前記配線基板用ベース基板上に第1絶縁層を形成し、該第1絶縁層上に厚膜配線層をメッキ形成する過程であることを特徴とする半導体集積回路装置の製造方法。

【請求項3】

請求項2に記載の半導体集積回路装置の製造方法において、前記第1絶縁層は、低誘電率絶縁層からなることを特徴とする半導体集積回路装置の製造方法。

【請求項4】

請求項2又は請求項3に記載の半導体集積回路装置の製造方法において、前記第1絶縁層は、膜厚が10μm以上であることを特徴とする半導体集積回路装置の製造方法。

【請求項5】

請求項1乃至請求項4の何れかに記載の半導体集積回路装置の製造方法において、前記接合バンプを形成する過程は、前記厚膜配線層上に第2絶縁層を形成し、該第2絶縁層に開口部をパターンニング形成し、該開口部に接合バンプを形成する過程であることを特徴とする半導体集積回路装置の製造方法。

【請求項6】

請求項1乃至請求項5の何れかに記載の半導体集積回路装置の製造方法において、前記半導体集積回路用ベース基板と前記配線基板用ベース基板は、同一の材料からなることを特徴とする半導体集積回路装置の製造方法。

【請求項7】

請求項1乃至請求項6の何れかに記載の半導体集積回路装置の製造方法であって、さらに、前記接合する過程の後に、アンダーフィルを流入する過程を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項8】

請求項1乃至請求項7の何れかに記載の半導体集積回路装置の製造方法であって、さらに、前記配線基板用ベース基板上に、インダクタ素子を形成する過程を具備することを特徴とする半導体集積回路装置の製造方法。

【請求項9】

請求項1乃至請求項8の何れかに記載の半導体集積回路装置の製造方法において、前記配線基板には、複数の厚膜配線層がメッキ形成されることを特徴とする半導体集積回路装置の製造方法。

【図1】

【公開番号】特開2008−78514(P2008−78514A)

【公開日】平成20年4月3日(2008.4.3)

【国際特許分類】

【出願番号】特願2006−258175(P2006−258175)

【出願日】平成18年9月25日(2006.9.25)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

【公開日】平成20年4月3日(2008.4.3)

【国際特許分類】

【出願日】平成18年9月25日(2006.9.25)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

[ Back to top ]