半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)の製造方法におけるゲート電極等の加工技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2002−175981号公報(特許文献1)または、これに対応する米国特許公開2002−59557号公報(特許文献2)には、SRAM(Static Random Access Memory)等のゲート電極等のパターニングにおいて、パターンコーナ部のラウンディング(Rounding)を回避するために、ハードマスク膜に対して、レジスト膜のパターニング、そのレジスト膜によるハードマスク膜パターニング、レジスト膜の除去の工程を2度繰り返して、コーナ部がラウンド(Round)しないハードマスク膜パターンを得る技術が開示されている。

【0003】

日本特開2008−91824号公報(特許文献3)または、これに対応する米国特許第7462566号公報(特許文献4)には、ゲート電極等のパターニングにおいて、最初にハードマスクをライン&スペースパターンを有する第1のレジスト膜でパターニングし、そのレジスト膜を除去した後、第2のレジスト膜に微細パターンを焼き付けて、この新たなレジスト膜を用いて、ハードマスクを加工する技術が開示されている。

【0004】

日本特開2010−118599号公報(特許文献5)には、ゲート電極等のパターニングにおいて、最初に第1のレジスト膜を用いて、阻止分離領域上にあるゲート突き当て部分の分離のための対象膜のエッチングを実行し、レジスト除去後、ライン&スペースパターンを有する第2のレジスト膜を用いて、対象膜のエッチングを行う技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−175981号公報

【特許文献2】米国特許公開2002−59557号公報

【特許文献3】特開2008−91824号公報

【特許文献4】米国特許第7462566号公報

【特許文献5】特開2010−118599号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArF(波長193nm)による単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ライン&スペースパターンのエッチング後の新たなレジスト膜が平坦にならない等の問題や、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【0007】

本願発明は、これらの課題を解決するためになされたものである。

【0008】

本発明の目的は、信頼性の高い半導体集積回路装置の製造プロセスを提供することにある。

【0009】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0011】

すなわち、本願の一つの発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜(ダミーゲート積層膜を含む)のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

【発明の効果】

【0012】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0013】

すなわち、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜(ダミーゲート積層膜を含む)のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するので、酸化処理や繰り返される薬液処理によるゲート積層膜側面の損傷を防止することができる。

【図面の簡単な説明】

【0014】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明するためのウエハ及びチップ上面図である。

【図2】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

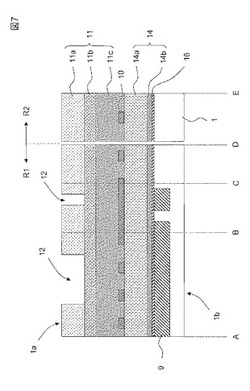

【図3】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

【図4】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。

【図5】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。

【図6】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図7】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図8】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング完了時)である。

【図9】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング完了時)である。

【図10】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用多層レジスト膜形成完了時)である。

【図11】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

【図12】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜トリミング完了時)である。

【図13】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極パターニング用ハードマスクのライン&スペースパターニング完了時)である。

【図14】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜形成完了時)である。

【図15】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図16】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用中層レジスト膜パターニング完了時)である。

【図17】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用下層レジスト膜パターニング完了時)である。

【図18】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜開口シュリンク完了時)である。

【図19】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域のハードマスクへのパターニング完了時)である。

【図20】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜除去完了時)である。

【図21】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(ゲート電極膜等のエッチング完了時)である。

【図22】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(図21と同じ、すなわち、ゲート電極膜等のエッチング完了時)である。

【図23】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(オフセットスペーサおよびエクステンション領域導入完了時)である。

【図24】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(サイドウォール形成用絶縁膜成膜完了時)である。

【図25】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側サイドウォール形成完了時)である。

【図26】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域リセス形成完了時)である。

【図27】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域埋め込み選択エピタキシ成長完了時)である。

【図28】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成完了時)である。

【図29】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成用レジスト膜除去完了時)である。

【図30】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(窒化シリコン膜エッチストップ用基板表面酸化膜形成完了時)である。

【図31】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(ハードマスク除去完了時)である。

【図32】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(プリメタル絶縁膜成膜完了時)である。

【図33】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(コンタクトホール形成完了時)である。

【図34】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(タングステンプラグ埋め込み完了時)である。

【図35】本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの回路図である。

【図36】本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの実際の平面レイアウトの一例を示すメモリセル平面レイアウト図である。

【発明を実施するための形態】

【0015】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0016】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)第1及び第2の主面を有する半導体ウエハであって、その第1の主面上に、メモリ領域および非メモリ領域を含む複数のチップ領域を有する前記半導体ウエハを準備する工程;

(b)前記半導体ウエハの前記第1の主面上に、下層のhigh−kゲート絶縁膜および上層のゲートメタル電極膜を有するゲート積層膜を形成する工程;

(c)前記ゲート積層膜上に、ゲート加工用ハードマスク膜を形成する工程;

(d)前記ゲート加工用ハードマスク膜上に、前記メモリ領域におけるゲート電極の延在方向において、隣接ゲート電極間切断領域を規定するための第1のレジスト膜を形成する工程;

(e)前記第1のレジスト膜に対して、パターニングを実行することにより、前記隣接ゲート電極間切断領域に対応するレジスト膜開口を形成する工程;

(f)パターニングされた前記第1のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(g)前記工程(f)の後、前記第1のレジスト膜を除去する工程;

(h)前記工程(c)の後、前記ゲート加工用ハードマスク膜上に、前記メモリ領域における前記ゲート電極に対応するライン&スペースパターンを規定するための第2のレジスト膜を形成する工程;

(i)前記第2のレジスト膜に対して、パターニングを実行する工程;

(j)パターニングされた前記第2のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(k)前記工程(j)の後、前記第2のレジスト膜を除去する工程;

(l)前記工程(g)および(k)の後、パターニングされた前記ゲート加工用ハードマスク膜がある状態で、前記ゲート積層膜に対するエッチングを実行する工程;

(m)前記工程(m)の後、前記ゲート加工用ハードマスク膜を除去する工程。

【0017】

2.前記1項の半導体集積回路装置の製造方法において、前記工程(h)は、前記工程(d)よりも、先に実行される。

【0018】

3.前記1または2項の半導体集積回路装置の製造方法において、前記工程(h)の前記第2のレジスト膜は、前記非メモリ領域におけるゲート電極に対応するライン&スペースパターンを規定するためのものでもある。

【0019】

4.前記1から3項のいずれか一つの半導体集積回路装置の製造方法において、前記隣接ゲート電極間切断領域は、素子分離領域内にある。

【0020】

5.前記1から4項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のレジスト膜および前記第2のレジスト膜は、それぞれ多層レジスト膜である。

【0021】

6.前記1から5項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、以下の下位工程を含む:

(e1)前記レジスト膜開口を縮小させる処理を実行する工程;

(e2)前記工程(e1)の後、前記レジスト膜開口下の前記ゲート加工用ハードマスク膜に対する異方性ドライエッチングを実行する工程。

【0022】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(i)は、以下の下位工程を含む:

(i1)パターニングされた前記第2のレジスト膜の幅を縮小させる処理を実行する工程;

(i2)前記工程(i1)の後、前記ゲート加工用ハードマスク膜の内、前記第2のレジスト膜が被覆しない部分に対して、異方性ドライエッチングを実行する工程。

【0023】

8.前記1から7項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)および(i)におけるパターニングは、193nmの露光光を用いたArFリソグラフィにより実行される。

【0024】

9.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【0025】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記第2のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層塗布系レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【0026】

11.前記1から10項のいずれか一つの半導体集積回路装置の製造方法において、更に以下の工程を有する:

(n)前記工程(l)の後であって前記工程(m)の前に、前記半導体ウエハの前記第1の主面に対して、選択エピタキシャル層を成長させる工程。

【0027】

12.前記11項の半導体集積回路装置の製造方法において、前記選択エピタキシャル層は、SiGe系エピタキシャル層である。

【0028】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0029】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ(能動素子)単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、集積回路構成の代表的なものとしては、Nチャネル型MISFETとPチャネル型MISFETを組み合わせたCMOS(Complemetary Metal Oxide Semiconductor)型集積回路に代表されるCMIS(Complemetary Metal Insulator Semiconductor)型集積回路を例示することができる。

【0030】

今日の半導体集積回路装置、すなわち、LSI(Large Scale Integration)のウエハ工程は、通常、原材料としてのシリコンウエハの搬入からプリメタル(Premetal)工程(M1配線層下端とゲート電極構造の間の層間絶縁膜等の形成、コンタクトホール形成、タングステンプラグ、埋め込み等からなる工程)あたりまでのFEOL(Front End of Line)工程と、M1配線層形成から始まり、アルミニウム系パッド電極上のファイナルパッシベーション膜へのパッド開口の形成あたりまで(ウエハレベルパッケージプロセスにおいては、当該プロセスも含む)のBEOL(Back End of Line)工程に大別できる。

【0031】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0032】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0033】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0034】

窒化シリコン膜は、SAC(Self−Aligned Contact)技術におけるエッチストップ膜として、多用されるほか、SMT(Stress Memorization Technique)における応力付与膜(Stressor Film)としても使用される。

【0035】

同様に、本願において、「シリサイド」または「シリサイド層」というときは、通常、ニッケルシリサイドやニッケル白金シリサイドを指すが、ニッケルモノシリサイドを主要な構成要素の一つとする合金、混晶等を含む。また、シリサイドは、ニッケルシリサイド、ニッケル白金シリサイド等に限らず、従来から実績のあるコバルトシリサイド、チタンシリサイド、タングステンシリサイド等でもよい。また、シリサイド化のための金属膜としては、Ni(ニッケル)膜以外にも、例えばNi−Pt合金膜(NiとPtの合金膜)、Ni−V合金膜(NiとVの合金膜)、Ni−Pd合金膜(NiとPdの合金膜)、Ni−Yb合金膜(NiとYbの合金膜)またはNi−Er合金膜(NiとErの合金膜)のようなニッケル合金膜などを用いることができる。なお、これらのニッケルを主要な金属元素とするシリサイドを「ニッケル系のシリサイド」と総称する。

【0036】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0037】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0038】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0039】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0040】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0041】

1.本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等の説明(主に図1)

図1は本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明するためのウエハ及びチップ上面図である。これに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明する。

【0042】

図1に示すように、ウエハ工程途中のウエハ1(ここでは、300φシリコン単結晶ウエハを例に取り説明するが、直径は450φでも200ファイでも良い)のデバイス主面1a(第1の主面)には、多数のチップ領域2が形成されている。また、ウエハ1には、その配向を判別するためのノッチ3が設けられている。なお、ウエハ1のデバイス主面1aの面方位は、たとえば(100)面(これと等価な面を含む)であり、ノッチ3方向の結晶方位は、たとえば〈110〉方位である。なお、各MISFETのチャネル方向CD1,CD2すなわち、チャネル長方向(ソースからドレインへ、またはドレインからソースの方向、すなわち、〈110〉と等価な方向である)は、特にそうでない旨、明示しない場合には、矢印の方向である。また、方位又は結晶面は、実質的な意味であり、当該方位(又は結晶面)自体のみでなく、その周辺で若干ずらせたものも含む(たとえば、前後に7度程度以内)。

【0043】

次に、各チップ2(チップ領域)のレイアウトの詳細を説明する。チップ領域2の周辺部4には、多数のボンディングパッド5が設けられており、内部領域にはメモリ領域6および非メモリ領域7が設けられている。ここで、メモリ領域6としては、SRAM(Static Random Access Memory)を例示するが、これに限らず、DRAM(Dynamic Random Access Memory)でもフラッシュメモリでもよい。なお、「メモリ領域」とは、正確にはメモリセル領域を指す。従って、メモリ周辺回路の多くの部分は、非メモリ領域7に属する。従って、非メモリ領域7には、このようなメモリ周辺回路のほか、ロジック回路、アナログ回路等が含まれる。

【0044】

2.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要説明(主に図2から図9)

ここでは、セクション1のSRAM混載ロジックチップの説明を受けて、メモリ領域6および非メモリ領域7(図1)におけるゲート電極等のパターニング(ダブルパターニングプロセス)について説明する。

【0045】

図2は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図3は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図4は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。図5は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。図6は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図7は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図8は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング完了時)である。図9は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明する。

【0046】

まず、ゲート電極膜加工前のウエハ1を準備する(図2及び図3を参照)。これは、たとえば、以下のように行う。たとえば、P型のシリコン単結晶ウエハ1を準備して、デバイス主面1a(裏面1bの反対の主面)に、たとえばSTI(Shallow Trench Isolation)等の素子分離領域9を形成し、続いて、アクティブ領域8にウエル領域等の必要な不純物ドープ領域を形成する。

【0047】

更に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、High−kゲート絶縁膜16(High−kゲート絶縁膜を含むゲート絶縁膜)を成膜する。ここで、「High−kゲート絶縁膜」とは、従前の酸化シリコン膜を主要な膜構成要素とするゲート絶縁膜(酸化シリコン膜、酸窒化シリコン膜、窒化シリコン膜又はこれらの積層膜)よりも誘電率の高いゲート絶縁膜をいう。

【0048】

次に、High−kゲート絶縁膜16上のほぼ全面に、たとえば、窒化チタン膜等のゲート電極膜14の下層膜14bを成膜する。

【0049】

次に、窒化チタン膜14b上のほぼ全面に、たとえば、ゲート電極膜14の上層膜としてポリシリコン膜14a(アモルファスシリコン膜でも良い)を成膜する。

【0050】

次に、ポリシリコン膜14a上のほぼ全面に、ゲート加工用ハードマスク膜10(たとえば、窒化シリコン膜)を、たとえばCVD(Chemical Vapor Deposition)により成膜する。

【0051】

次に、窒化シリコン膜10上のほぼ全面に、ゲート電極パターニング用レジスト膜15(第2のレジスト膜またはゲート電極ライン&スペースパターニング用レジスト膜)を塗布等により形成する。ゲート電極パターニング用レジスト膜15は、SOC(Spin On Carbon)膜等の炭素系下層非感光性膜15c(下層膜)、Si−BARC(Silicon−Bottom Anti−Reflection Coating)膜等のシリコン系中間層非感光性膜15b(中間層膜)、ArF化学増幅型レジスト膜等の有機系上層感光性膜15a(上層膜)等から構成されている。Si−BARC膜は、シリコンを主要な成分の一つとして含む(シリコン含有量は、たとえば、15重量%から45重量%程度、以下の第2のレジスト膜についても同じ)塗布系またはCVDによる反射防止膜である。また、SOC膜は、炭素を主要な成分の一つとして含む(炭素含有量は、たとえば、80重量%から90重量%程度、以下の第2のレジスト膜についても同じ)塗布系またはCVD(CVD系の炭素系膜は、アモルファスカーボンと呼ばれる)による下地膜(シリコン系の部材に対してエッチング選択性を持つ膜)である。

【0052】

次に、図2及び図3に示すように、ArF化学増幅型レジスト膜15aの露光および現像を実行して、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aを形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。ここで、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aの幅は、パターニング当初、45nm程度であるが、以下に説明するトリミング処理によって、30nm程度とする。なお、このステップにおける炭素系の下層膜は、SOC膜等の塗布系の平坦化膜が好適である。

【0053】

続いて、多層レジスト膜15のArF化学増幅型レジスト膜15a(上層膜)のパターンを順次、Si−BARC膜15b(中間層膜)、SOC膜15c(下層膜)に転写する(詳細は、セクション3で説明する)。

【0054】

次に、図4及び図5に示すように、パターニングされたゲート電極パターニング用多層レジスト膜15(第2のレジスト膜)マスクとして、ドライエッチングにより、ゲート加工用ハードマスク膜10(窒化シリコン膜)をパターニングする。その後、残留するゲート電極パターニング用レジスト膜15をアッシング等により除去する。

【0055】

次に、図6及び図7に示すように、先と同様に、ウエハ1のデバイス面1a側のほぼ全面に、隣接ゲート電極間切断領域パターニング用多層レジスト膜11(第1のレジスト膜)を、たとえば塗布等により形成する。多層レジスト膜11は、先と同様に、SOC(Spin On Carbon)膜等の炭素系下層非感光性膜11c(下層膜)、Si−BARC(Silicon−Bottom Anti−Reflection Coating)膜等のシリコン系中間層非感光性膜11b(中間層膜)、ArF化学増幅型レジスト膜等の有機系上層感光性膜11a(上層膜)等から構成されている。

【0056】

次に、ArF化学増幅型レジスト膜11aの露光および現像を実行して、隣接ゲート電極間切断領域に対応するレジスト膜開口12を形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。ここで、レジスト膜開口12の幅(短い方の変の長さに等価)は、たとえば60から70nm程度であり、素子分離領域の幅と同程度であるが、後に述べるシュリンク処理により、たとえば、20から25nm程度とする。

【0057】

続いて、多層レジスト膜11のArF化学増幅型レジスト膜11a(上層膜)のパターンを順次、Si−BARC膜11b(中間層膜)、SOC膜11c(下層膜)に転写する(詳細は、セクション3で説明する)。その後、残留するゲート電極パターニング用レジスト膜11をアッシング等により除去する。

【0058】

次に、図8及び図9に示すように、パターニングされたゲート加工用ハードマスク膜10(窒化シリコン膜)をマスクとして、ドライエッチングにより、ゲート電極膜14(ポリシリコン膜14a、窒化チタン膜14b)およびHigh−kゲート絶縁膜16を加工して、ゲート電極14を形成する。

【0059】

3.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細説明(主に図10から図13および図14から図21)

図10は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用多層レジスト膜形成完了時)である。図11は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図12は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜トリミング完了時)である。図13は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極パターニング用ハードマスクのライン&スペースパターニング完了時)である。図14は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜形成完了時)である。図15は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図16は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用中層レジスト膜パターニング完了時)である。図17は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用下層レジスト膜パターニング完了時)である。図18は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜開口シュリンク完了時)である。図19は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域のハードマスクへのパターニング完了時)である。図20は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜除去完了時)である。図21は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(ゲート電極膜等のエッチング完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明する。

【0060】

まず、図10に示すように、たとえば、P型のシリコン単結晶ウエハ1を準備して、デバイス主面1aに、たとえばSTI等の素子分離領域9を形成し、続いて、アクティブ領域8にウエル領域等の必要な不純物ドープ領域を形成する。

【0061】

更に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、High−kゲート絶縁膜16(High−kゲート絶縁膜を含むゲート絶縁膜)を成膜する。High−kゲート絶縁膜16としては、たとえば、厚さ0.7から1.5nm程度の酸化ハフニウム系絶縁膜を例示することができる。

【0062】

次に、High−kゲート絶縁膜16上のほぼ全面に、たとえば、窒化チタン膜(たとえば厚さ10nm程度)等のゲート電極膜14の下層膜14bを成膜する。

【0063】

次に、窒化チタン膜14b上のほぼ全面に、ゲート電極膜14の上層膜として、たとえば厚さ50nm程度のポリシリコン膜14a(アモルファスシリコン膜でも良い)を成膜する。

【0064】

次に、ポリシリコン膜14a上のほぼ全面に、ゲート加工用ハードマスク膜10として、たとえば、CVDにより、窒化シリコン膜(たとえば、厚さ50nm程度)を成膜する。

【0065】

次に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、ゲート電極パターニング用多層レジスト膜15(第2のレジスト膜)を塗布等により形成する。多層レジスト膜15は、たとえば、以下のように形成する。すなわち、最初に、ウエハ1のデバイス面1a上のほぼ全面に、SOC膜等の炭素系下層非感光性膜15c(下層膜)を塗布等により形成する(たとえば厚さ100から300nm程度)。続いて、SOC膜15c上のほぼ全面に、たとえばSi−BARC膜等のシリコン系中間層非感光性膜15b(中間層膜)を塗布等により形成する(たとえば厚さ10から100nm程度)。続いて、Si−BARC膜15b上のほぼ全面に、たとえばArF化学増幅型レジスト膜等の有機系上層感光性膜15a(上層膜)を塗布等により形成する(たとえば厚さ50から180nm程度)。

【0066】

次に、図11に示すように、ArF化学増幅型レジスト膜15aの露光および現像を実行して、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aを形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。

【0067】

次に、図12に示すように、パターニングされたレジスト膜パターン15aに対して、トリミング(Trimming)処理を施すことにより、最終的なレジスト膜パターン15aの幅を元のレジスト膜の幅19よりも狭くする。トリミング処理は、ドライエッチングと同様の処理であり、通常、後続のエッチングプロセスと同一の装置又は同一のチャンバ内で実行される。トリミング処理の雰囲気ガスとしては、たとえば、Cl2/O2系ガスを例示することができる。

【0068】

続いて、トリミングされたレジスト膜パターン15aを先と同様に、順次、Si−BARC膜15b(エッチング雰囲気は、たとえばCF4系ガス雰囲気)、SOC膜15c(エッチング雰囲気は、たとえばO2系ガス雰囲気)へ転写する。

【0069】

次に、図13に示すように、パターニングされたSOC膜15cをマスクとして、ドライエッチングにより、ゲート加工用ハードマスク膜10(窒化シリコン膜)をパターニングする。その後、残留するゲート電極パターニング用レジスト膜15をアッシング等により除去する。

【0070】

次に、図14に示すように、窒化チタン膜14b上のほぼ全面に、隣接ゲート電極間切断領域パターニング用多層レジスト膜11(第1のレジスト膜)を塗布等により形成する。多層レジスト膜11は、たとえば、以下のように形成する。すなわち、最初に、ポリシリコン膜14a上のほぼ全面に、SOC膜等の炭素系下層非感光性膜11c(下層膜)を塗布等により形成する(たとえば厚さ100から300nm程度)。なお、CVD(Chemical Vapor Deposition)によるアモルファスカーボン膜等でもよい。続いて、SOC膜11c上のほぼ全面に、たとえばSi−BARC膜(たとえば厚さ10から100nm程度)等のシリコン系中間層非感光性膜11b(中間層膜)を塗布等により形成する。続いて、Si−BARC膜11b上のほぼ全面に、たとえばArF化学増幅型レジスト膜等の有機系上層感光性膜11a(上層膜)を塗布等により形成する(たとえば厚さ50から180nm程度)。

【0071】

次に、図15に示すように、ArF化学増幅型レジスト膜11aの露光および現像を実行して、隣接ゲート電極間切断領域に対応するレジスト膜開口12を形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。

【0072】

次に、図16に示すように、パターニングされたArF化学増幅型レジスト膜11aをマスクとして、たとえばフルオロカーボン(Fluorocarbon)系ガス(たとえばCF4等)を用いたドライエッチングにより、ArF化学増幅型レジスト膜11aのパターンをSi−BARC膜11bに転写する。

【0073】

次に、図17に示すように、パターニングされたSi−BARC膜11bをマスクとして、たとえば酸素系ガス(たとえばO2等)を用いたドライエッチングにより、Si−BARC膜11bのパターンをSOC膜11cに転写する。このとき、同時に、残存していたArF化学増幅型レジスト膜11aが除去される。

【0074】

次に、図18に示すように、ウエハ1を、たとえば、ゲート電極14をエッチングするためのドライエチング装置のエッチング室に導入した状態で、エッチング前処理(シュリンク処理)を実行する(一種のドライエッチング処理である)。すなわち、レジスト膜開口12の側壁にシュリンク用側壁18を形成する。シュリンク処理条件としては、ガス雰囲気:たとえばCHF3(100から300sccm)/O2(10から50sccm)、RF電力:たとえば500から1000ワット程度、ウエハバイアス:100から300ボルト、ウエハステージ温度:摂氏10から50度程度を例示することができる。

【0075】

次に、図19に示すように、パターニングされたSOC膜11cをマスクとして、ドライエッチング(たとえばCH4,CHF3系ガス雰囲気)により、ゲート加工用ハードマスク膜10をパターニングする。このとき同時に、残存していたSi−BARC膜11bが除去される。

【0076】

次に、図20に示すように、SOC膜11cおよびシュリンク用側壁18をアッシング処理およびウエット洗浄等により、除去する。ウエット洗浄の条件としては、たとえば、

(1)第1ステップ:薬液は希塩酸で、組成は、たとえば、塩化水素濃度0.0418モル%程度、処理時間は、常温(摂氏15度から25度)で60秒程度、

(2)第2ステップ:薬液は混酸で、組成は、たとえば、塩化水素濃度0.411モル%程度、弗化水素濃度0.0106モル%程度、処理時間は、常温(摂氏15度から25度)で60秒程度を好適な一例として示すことができる。

【0077】

次に、図21に示すように、パターニングされたゲート加工用ハードマスク膜10をマスクとして、ドライエッチングにより、ポリシリコン膜14a(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、HBr等)、窒化チタン膜14b(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、Cl2/HBr等)、ゲート絶縁膜16(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、BCl3/Cl2等)に順次、ゲート電極14(図22参照)を形成する。

【0078】

4.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要説明(主に図22から図34)

図22は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(図21と同じ、すなわち、ゲート電極膜等のエッチング完了時)である。図23は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(オフセットスペーサおよびエクステンション領域導入完了時)である。図24は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(サイドウォール形成用絶縁膜成膜完了時)である。図25は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側サイドウォール形成完了時)である。図26は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域リセス形成完了時)である。図27は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域埋め込み選択エピタキシ成長完了時)である。図28は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成完了時)である。図29は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成用レジスト膜除去完了時)である。図30は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(窒化シリコン膜エッチストップ用基板表面酸化膜形成完了時)である。図31は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(ハードマスク除去完了時)である。図32は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(プリメタル絶縁膜成膜完了時)である。図33は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(コンタクトホール形成完了時)である。図34は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(タングステンプラグ埋め込み完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明する。

【0079】

図22(図9及び図21と同じプロセスステップ)に基づいて、ゲート電極のラインアンドスペースパターンのパターニングが完了した時点以降の図1の非メモリ領域CMISFET対切り出し部のPチャネルデバイス領域R3pおよび非メモリ領域CMISFET対切り出し部のNチャネルデバイス領域R3nに対応する部分を説明する。図22に示すように、ウエハ1のP型単結晶シリコン基板部の上半部に、Nウエル領域1nおよびPウエル領域1pが設けられている。

【0080】

次に、図23に示すように、ウエハ1のデバイス面1a上のほぼ全面に、たとえばCVDにより、オフセットスペーサ窒化シリコン膜21(たとえば厚さ2から7nm程度)を成膜する。続いて、異方性ドライエッチングによって、オフセットスペーサ窒化シリコン膜21をエッチバックして、オフセットスペーサ21を形成する。

【0081】

続いて、Pチャネルデバイス領域R3pおよびNチャネルデバイス領域R3nのそれぞれのウエハ1のデバイス面1a表面領域に、イオン注入により、P型エクステンション領域22p(イオン注入条件としては、たとえば、イオン種:BF2、打ち込みエネルギー:1KeVから5KeV、ドーズ量:1x1015/cm2から8x1015/cm2;イオン種:C、打ち込みエネルギー:1KeVから5KeV、ドーズ量:4x1014/cm2から9x1014/cm2)およびN型エクステンション領域22n(イオン注入条件としては、たとえば、イオン種:As、打ち込みエネルギー:1KeVから10KeV、ドーズ量:1x1015/cm2から9x1015/cm2;イオン種:C、打ち込みエネルギー:1KeVから5KeV、ドーズ量:4x1014/cm2から9x1014/cm2)を導入する。

【0082】

次に、図24に示すように、ウエハ1のデバイス面1a上のほぼ全面に、たとえばCVDにより、サイドウォール酸化シリコン膜23a(たとえば厚さ5から10nm程度)を成膜する。続いて、サイドウォール酸化シリコン膜23a上のほぼ全面に、たとえばCVDにより、サイドウォール窒化シリコン膜23b(たとえば厚さ20から30nm程度)を成膜する。

【0083】

次に、図25に示すように、Nチャネル側をPチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜31で被覆した状態で、異方性ドライエッチングにより、Pチャネル領域のサイドウォール絶縁膜23a,23bを形成する。その後、Pチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜31を除去する。

【0084】

次に、図26に示すように、たとえば、ウエットエッチング(たとえば、アルカリ系シリコンエッチング液)または等方性ドライエッチング(ガス系は、たとえば、O2/CF4など)により、P型高濃度SiGeソースドレイン領域24pe(図27参照)となるべき部分にソースドレイン埋め込み用リセス32を形成する。

【0085】

次に、図27に示すように、たとえば、選択エピタキシャル成長により、ソースドレイン埋め込み用リセス32を、ボロンをドープした(ボロン濃度は、たとえば1x1019/cm3から5x1020/cm3程度)SiGe(Ge組成は、たとえば20から40atm%程度)エピタキシャル層すなわちP型高濃度SiGeソースドレイン領域24peで埋め込む(ガス系は、たとえば、SiH4,SiH2Cl2,Si2H6等)。これにより、チャネル領域等に、圧縮応力が作用し、ホール移動度を向上させることができる。また、同様に、Nチャネル領域のソースドレインにも同様にN型不純物をドープしたSiC(炭素組成は、たとえば1atm%程度)エピタキシャル層を導入することにより、チャネル領域等に、引っ張り応力が作用し、電子移動度を向上させることができる。

【0086】

次に、図28に示すように、Pチャネル側をNチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜33で被覆した状態で、異方性ドライエッチングにより、Nチャネル領域のサイドウォール絶縁膜23a,23bを形成する。

【0087】

次に、図29に示すように、Nチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜33を除去する。

【0088】

次に、図30に示すように、熱酸化等により、基板1の表面1a側に、薄い酸化シリコン膜、すなわち窒化シリコン膜エッチストップ用基板表面酸化膜34を形成する。

【0089】

次に、図31に示すように、たとえば、熱燐酸等によるウエット処理によって、ゲート加工用ハードマスク膜10(窒化シリコン膜)等を除去する。

【0090】

次に、図32に示すように、サリサイド(Salicide)方式により、ニッケル系シリサイド膜25(たとえば、NiPtシリサイドなど)を形成する。続いて、ウエハ1のデバイス面1a上のほぼ全面に、たとえばプラズマCVDにより、CESL(Contact Etch Stop Layer)およびプリメタル下層絶縁膜26aとして、窒化シリコン膜(たとえば厚さ20から30nm程度)を成膜する。続いて、窒化シリコン膜26a上のほぼ全面に、たとえばプラズマCVDにより、プリメタル上層絶縁膜26bとして、酸化シリコン膜(たとえば厚さ150から240nm程度)を成膜する。

【0091】

次に、図33に示すように、酸化シリコン膜26b上のほぼ全面に、コンタクトホール形成用レジスト膜27を塗布等する。続いて、通常のリソグラフィにより(たとえば、ArFリソグラフィ)、レジスト膜27をパターニングする。パターニングされたレジスト膜27をマスクとして、順次、異方性ドライエッチングにより、酸化シリコン膜26bおよび窒化シリコン膜26aのコンタクトホール28を開口する。その後、不要になったレジスト膜27をアッシング等により除去する。

【0092】

次に、図34に示すように、コンタクトホール28内にタングステンプラグ29を埋め込む。その後、必要に応じて、多層配線を銅系ダマシン方式(埋め込み配線方式)またはアルミニウム系通常配線方式(非埋め込み配線方式)によって形成する。

【0093】

5.本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセル等の説明(主に図35および図36)

ここでは、6トランジスタセルを例に取り具体的に説明したが、本願の発明は、それに限定されるものではなく、その他の構造のメモリセルにも適用できることは言うまでもない。

【0094】

図35は本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの回路図である。図36は本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの実際の平面レイアウトの一例を示すメモリセル平面レイアウト図である。

【0095】

これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセル等を説明する。

【0096】

図35に示すように、SRAMメモリセルMCには、相互に直行して走るワードラインWLおよび一対のビット線BL,BLBが設けられており、それらの交点の近傍には、N型記憶用トランジスタQ1,Q2、P型記憶用トランジスタQ3,Q4、読み出し用トランジスタQ5,Q6、および、これらに電源を供給する電源供給ラインVdd、基準電圧ラインVss等が配置されている。

【0097】

図35のSRAMメモリセルMCを実際のレイアウトの中で示すと、図36のようになる。図36に示すように、縦に走る多数のゲート電極14が、規則的に隣接ゲート電極間切断領域12によって、切断されているのがわかる。多数のコンタクト部28,30の内、横長で示したものは、シェアードコンタクト部30である。ここで、Nチャネルデバイスのアクティブ領域8nのコンタクト部28と、Pチャネルデバイスのアクティブ領域8pのシェアードコンタクト部30の間を相互接続メタル配線ICで連結している。

【0098】

6.本願の前記一実施の形態の半導体集積回路装置の製造方法に関する補足的説明並びに考察等

セクション5に示したようなSRAM幅広セルにおいては、隣り合うゲート間の長手方向の間隔部、すなわち、隣接ゲート電極間切断領域12(図2参照)を小さくすることが、セル面積縮小のために重要な技術課題となる。しかし、28nmテクノロジノード(Technology Node)または、それ以降の世代においては、解像限界以下であるため、ゲート電極のパターニングを1回の光リソグラフィ(たとえば、波長193nmの露光光および液浸縮小投影露光装置を用いたArFリソグラフィ)で実行することは不可能である。また、28nmテクノロジノードまたは、それ以降の世代においては、ゲート積層構造(Gate stack Structure)がHigh−kゲート絶縁膜およびメタル系ゲートを含むものになるため、酸化耐性やウエット処理耐性は、低下する傾向にある。更に、多層レジストプロセスを採用する必要があるため(45nmテクノロジノードまたは、それ以降の世代)、多層レジストプロセスに固有の問題も存在する。

【0099】

解像限界の問題を解決するために、本願においては、レジスト膜等のエッチングマスク膜のパターニングおよび、それを用いた下地膜のエッチングを複数回繰り返す、多重パターニングプロセス(Multiple Patterning Process)を採用している。しかし、単純に、ゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を先行し、続いて、隣接ゲート電極間切断領域12(図2参照)をパターニング(2度目のリソグラフィ)する方法(「L&Sファースト方式」という)では、2度目のリソグラフィにおけるレジスト膜が、メモリ領域6(パターン高密度領域)および非メモリ領域7(パターン低密度領域)の間で平坦性を確保できないという問題がある(図1参照)。

【0100】

そこで、セクション2から4に示した例では、たとえば、先に、ハードマスク10(図5参照)に対して、ゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を実行し、次に、ハードマスクに対して、隣接ゲート電極間切断領域12(図6参照)をパターニング(2度目のリソグラフィ)し、パターニングされたハードマスクを用いて、下地のゲートスタック構造を加工している(「ハードマスク多重パターニング方式」という)。このようにすると、ハードマスク10(図7参照)は、比較的薄いので、2度目の露光の際の平坦性が問題となることがない。なお、前記実施の形態では、露光の順序については、ラインアンドスペースパターンのパターニングを先行するL&Sファースト方式を採用したが、隣接ゲート電極間切断領域のパターニングを先行する方法(「L&Sラスト方式」という)を採用しても良い。

【0101】

また、隣接ゲート電極間切断領域12(図6参照)のパターニングにおいて、シュリンク処理(隣接ゲート電極間切断領域12に対応するレジスト開口の面積を縮小する処理)を伴う場合には、単純なL&Sファースト方式では、下地の凹凸が激しいため、シュリンク形状が下地に依存して不安定な形状となる。一方、ハードマスク多重パターニング方式では、下地が比較的平坦であるため、シュリンク形状が安定する。

【0102】

さらに、酸化耐性やウエット処理耐性の低下の問題を解決するために、ハードマスク多重パターニング方式に加えて、隣接ゲート電極間切断領域12(図6参照)が素子分離領域9の内部に含まれるようにレイアウトすることが有効である(「ゲート端部素子分離領域内レイアウト方式」という)。多重パターニングプロセスにおいては、アッシングやウエット薬液処理を伴うレジスト膜の除去が複数回にわたって行われるため、ゲート絶縁膜の過剰な後退やメタル系ゲート電極部の過剰な酸化が発生しやすい(もっとも、ハードマスクを使用する方式では、ハードマスクを使用しない方式に比べて、アッシングやウエット薬液処理を伴うダメージは、相対的に小さい)。しかし、ゲート端部素子分離領域内レイアウト方式では、そのような多重処理が行われるのは、アクティブ領域上ではなく、主に、素子分離領域9(図6参照)上となるので、デバイス特性への影響を少なくすることができる。

【0103】

なお、ハードマスク多重パターニング方式(露光の順序に無関係である)では、非メモリ領域7のゲート電極のパターニングをメモリ領域6のゲート電極のラインアンドスペースパターンのパターニングと同時に実行するのが有効である。これは、シュリンク処理は、レジストの被覆部分の幅を増加させる処理であるため、ゲート電極のラインアンドスペースパターンのパターニングには適用できないためである。また、そのようにすることによって(シュリンク処理の有無に係らず)、メモリ領域6および非メモリ領域7のゲート電極のラインアンドスペースパターンのパターニングにトリミング処理を適用できるメリットもある。

【0104】

また、ハードマスク多重パターニング方式(露光の順序に無関係である)では、ソースドレイン領域への選択エピタキシ埋め込み方式(図27参照)とのプロセス整合性も良好である。

【0105】

7.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0106】

例えば、前記実施の形態では、非メモリ領域7のゲート電極のパターニングをメモリ領域6のゲート電極のラインアンドスペースパターンのパターニング時のみで行ったが、非メモリ領域7のパターニングに関して以下のようにしてもよい。ハードマスクに対して、メモリ領域6と同時にゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を実行し、次にハードマスクに対して、メモリ領域6の隣接ゲート電極間切断領域をパターニングすると同時に、非メモリ領域の不要なラインアンドスペースパターンを一部除去するようにパターニング(2度目のリソグラフィ)し、パターニングされたハードマスクを用いて、下地のゲートスタック構造を加工してもよい。32nmや28nm以降のテクノロジノードにおいては、非メモリ領域のゲート電極においてもラインアンドスペース構造を取る方が露光の関係から都合がよい。更に本実施例ではハードマスクを用いているために、非メモリ領域の活性領域上のハードマスクを2度目のリソグラフィでパターニングしてもデバイス特性の影響は軽微である。

【0107】

例えば、前記実施の形態では、主にゲートファースト(Gate First)方式を例に取り具体的に説明したが、本発明はそれに限定されるものではなく、ゲートラスト(Gate Last)方式におけるダミーゲートプロセス(Dummy Gate Process)にも適用できることは言うまでもない。

【0108】

また、前記実施の形態では、主にハードマスク(Hard Mask)を使用する方式を例にとり具体的に説明したが、本発明はそれに限定されるものではなく、隣接ゲート電極間切断領域のパターニング(Patterning)およびゲート電極のラインアンドスペースパターン(Line and Space Pattern)のパターニングにハードマスクを使用しなくてもよいことは、言うまでもない。

【0109】

更に、前記実施の形態では、主にPチャネル側のソースドレインにSiGe系部材を用いた例について具体的に説明したが、本発明はそれに限定されるものではなく、Pチャネル側およびNチャネル側のソースドレインに通常のシリコン系部材(SiGe等の合金ではない)やシリコン系合金(SiGe,SiC等)を使用したものにも適用できることは言うまでもない。

【符号の説明】

【0110】

1 ウエハ

1a ウエハ又はチップのデバイス主面(第1の主面)

1b ウエハ又はチップの裏面

1n Nウエル領域

1p Pウエル領域

1s 半導体基板領域(P型シリコン単結晶基板領域)

2 半導体チップ又はチップ領域

3 ノッチ

4 チップ周辺部

5 ボンディングパッド

6 メモリ領域

7 非メモリ領域

8 アクティブ領域

8n Nチャネルデバイスのアクティブ領域

8p Pチャネルデバイスのアクティブ領域

9 素子分離領域(STI)

10 ゲート加工用ハードマスク膜(窒化シリコン膜)

11 隣接ゲート電極間切断領域パターニング用レジスト膜(第1のレジスト膜、またはゲート電極間切断用レジスト膜)

11a 隣接ゲート電極間切断領域パターニング用多層レジスト膜の上層膜

11b 隣接ゲート電極間切断領域パターニング用多層レジスト膜の中間層膜

11c 隣接ゲート電極間切断領域パターニング用多層レジスト膜の下層膜

12 隣接ゲート電極間切断領域(これに対応するレジスト膜開口)

14 ゲート電極(またはゲート電極膜)

14a 多層ゲート電極(またはゲート電極膜)の上層膜

14b 多層ゲート電極(またはゲート電極膜)の下層膜

15 ゲート電極パターニング用レジスト膜(第2のレジスト膜またはゲート電極ライン&スペースパターニング用レジスト膜)

15a ゲート電極パターニング用多層レジスト膜の上層膜

15b ゲート電極パターニング用多層レジスト膜の中間層膜

15c ゲート電極パターニング用多層レジスト膜の下層膜

16 ゲート絶縁膜(High−k膜を有するゲート絶縁膜)

18 シュリンク用側壁

19 トリミングされた部分(元のレジスト膜の幅)

21 オフセットスペーサ窒化シリコン膜(オフセットスペーサ)

22n N型エクステンション領域

22p P型エクステンション領域

23a サイドウォール酸化シリコン膜(酸化シリコン膜サイドウォール)

23b サイドウォール窒化シリコン膜(窒化シリコン膜サイドウォール)

24n N型高濃度ソースドレイン領域

24p P型高濃度ソースドレイン領域

24pe P型高濃度SiGeソースドレイン領域

25 シリサイド層

26a プリメタル下層絶縁膜

26b プリメタル上層絶縁膜

27 コンタクトホール形成用レジスト膜

28 通常のコンタクトホール(またはコンタクト部)

29 タングステンプラグ

30 シェアードコンタクトホール(または当該コンタクト部)

31 Pチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜

32 ソースドレイン埋め込み用リセス

33 Nチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜

34 窒化シリコン膜エッチストップ用基板表面酸化膜

BL,BLB ビット線

IC 相互接続メタル配線

MC メモリセル

Q1,Q2 N型記憶用トランジスタ

Q3,Q4 P型記憶用トランジスタ

Q5,Q6 読み出し用トランジスタ

R1 メモリ領域切り出し部

R2 非メモリ領域切り出し部

R3 非メモリ領域CMISFET対切り出し部

R3n 非メモリ領域CMISFET対切り出し部のNチャネルデバイス領域

R3p 非メモリ領域CMISFET対切り出し部のPチャネルデバイス領域

Vdd 電源供給ライン

Vss 基準電圧ライン

WL ワードライン

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)の製造方法におけるゲート電極等の加工技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2002−175981号公報(特許文献1)または、これに対応する米国特許公開2002−59557号公報(特許文献2)には、SRAM(Static Random Access Memory)等のゲート電極等のパターニングにおいて、パターンコーナ部のラウンディング(Rounding)を回避するために、ハードマスク膜に対して、レジスト膜のパターニング、そのレジスト膜によるハードマスク膜パターニング、レジスト膜の除去の工程を2度繰り返して、コーナ部がラウンド(Round)しないハードマスク膜パターンを得る技術が開示されている。

【0003】

日本特開2008−91824号公報(特許文献3)または、これに対応する米国特許第7462566号公報(特許文献4)には、ゲート電極等のパターニングにおいて、最初にハードマスクをライン&スペースパターンを有する第1のレジスト膜でパターニングし、そのレジスト膜を除去した後、第2のレジスト膜に微細パターンを焼き付けて、この新たなレジスト膜を用いて、ハードマスクを加工する技術が開示されている。

【0004】

日本特開2010−118599号公報(特許文献5)には、ゲート電極等のパターニングにおいて、最初に第1のレジスト膜を用いて、阻止分離領域上にあるゲート突き当て部分の分離のための対象膜のエッチングを実行し、レジスト除去後、ライン&スペースパターンを有する第2のレジスト膜を用いて、対象膜のエッチングを行う技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−175981号公報

【特許文献2】米国特許公開2002−59557号公報

【特許文献3】特開2008−91824号公報

【特許文献4】米国特許第7462566号公報

【特許文献5】特開2010−118599号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArF(波長193nm)による単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ライン&スペースパターンのエッチング後の新たなレジスト膜が平坦にならない等の問題や、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【0007】

本願発明は、これらの課題を解決するためになされたものである。

【0008】

本発明の目的は、信頼性の高い半導体集積回路装置の製造プロセスを提供することにある。

【0009】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0011】

すなわち、本願の一つの発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜(ダミーゲート積層膜を含む)のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

【発明の効果】

【0012】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0013】

すなわち、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜(ダミーゲート積層膜を含む)のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するので、酸化処理や繰り返される薬液処理によるゲート積層膜側面の損傷を防止することができる。

【図面の簡単な説明】

【0014】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明するためのウエハ及びチップ上面図である。

【図2】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

【図3】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

【図4】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。

【図5】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。

【図6】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図7】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図8】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング完了時)である。

【図9】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング完了時)である。

【図10】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用多層レジスト膜形成完了時)である。

【図11】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。

【図12】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜トリミング完了時)である。

【図13】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極パターニング用ハードマスクのライン&スペースパターニング完了時)である。

【図14】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜形成完了時)である。

【図15】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。

【図16】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用中層レジスト膜パターニング完了時)である。

【図17】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用下層レジスト膜パターニング完了時)である。

【図18】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜開口シュリンク完了時)である。

【図19】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域のハードマスクへのパターニング完了時)である。

【図20】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜除去完了時)である。

【図21】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(ゲート電極膜等のエッチング完了時)である。

【図22】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(図21と同じ、すなわち、ゲート電極膜等のエッチング完了時)である。

【図23】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(オフセットスペーサおよびエクステンション領域導入完了時)である。

【図24】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(サイドウォール形成用絶縁膜成膜完了時)である。

【図25】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側サイドウォール形成完了時)である。

【図26】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域リセス形成完了時)である。

【図27】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域埋め込み選択エピタキシ成長完了時)である。

【図28】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成完了時)である。

【図29】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成用レジスト膜除去完了時)である。

【図30】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(窒化シリコン膜エッチストップ用基板表面酸化膜形成完了時)である。

【図31】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(ハードマスク除去完了時)である。

【図32】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(プリメタル絶縁膜成膜完了時)である。

【図33】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(コンタクトホール形成完了時)である。

【図34】本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(タングステンプラグ埋め込み完了時)である。

【図35】本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの回路図である。

【図36】本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの実際の平面レイアウトの一例を示すメモリセル平面レイアウト図である。

【発明を実施するための形態】

【0015】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0016】

1.以下の工程を含む半導体集積回路装置の製造方法:

(a)第1及び第2の主面を有する半導体ウエハであって、その第1の主面上に、メモリ領域および非メモリ領域を含む複数のチップ領域を有する前記半導体ウエハを準備する工程;

(b)前記半導体ウエハの前記第1の主面上に、下層のhigh−kゲート絶縁膜および上層のゲートメタル電極膜を有するゲート積層膜を形成する工程;

(c)前記ゲート積層膜上に、ゲート加工用ハードマスク膜を形成する工程;

(d)前記ゲート加工用ハードマスク膜上に、前記メモリ領域におけるゲート電極の延在方向において、隣接ゲート電極間切断領域を規定するための第1のレジスト膜を形成する工程;

(e)前記第1のレジスト膜に対して、パターニングを実行することにより、前記隣接ゲート電極間切断領域に対応するレジスト膜開口を形成する工程;

(f)パターニングされた前記第1のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(g)前記工程(f)の後、前記第1のレジスト膜を除去する工程;

(h)前記工程(c)の後、前記ゲート加工用ハードマスク膜上に、前記メモリ領域における前記ゲート電極に対応するライン&スペースパターンを規定するための第2のレジスト膜を形成する工程;

(i)前記第2のレジスト膜に対して、パターニングを実行する工程;

(j)パターニングされた前記第2のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(k)前記工程(j)の後、前記第2のレジスト膜を除去する工程;

(l)前記工程(g)および(k)の後、パターニングされた前記ゲート加工用ハードマスク膜がある状態で、前記ゲート積層膜に対するエッチングを実行する工程;

(m)前記工程(m)の後、前記ゲート加工用ハードマスク膜を除去する工程。

【0017】

2.前記1項の半導体集積回路装置の製造方法において、前記工程(h)は、前記工程(d)よりも、先に実行される。

【0018】

3.前記1または2項の半導体集積回路装置の製造方法において、前記工程(h)の前記第2のレジスト膜は、前記非メモリ領域におけるゲート電極に対応するライン&スペースパターンを規定するためのものでもある。

【0019】

4.前記1から3項のいずれか一つの半導体集積回路装置の製造方法において、前記隣接ゲート電極間切断領域は、素子分離領域内にある。

【0020】

5.前記1から4項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のレジスト膜および前記第2のレジスト膜は、それぞれ多層レジスト膜である。

【0021】

6.前記1から5項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)は、以下の下位工程を含む:

(e1)前記レジスト膜開口を縮小させる処理を実行する工程;

(e2)前記工程(e1)の後、前記レジスト膜開口下の前記ゲート加工用ハードマスク膜に対する異方性ドライエッチングを実行する工程。

【0022】

7.前記1から6項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(i)は、以下の下位工程を含む:

(i1)パターニングされた前記第2のレジスト膜の幅を縮小させる処理を実行する工程;

(i2)前記工程(i1)の後、前記ゲート加工用ハードマスク膜の内、前記第2のレジスト膜が被覆しない部分に対して、異方性ドライエッチングを実行する工程。

【0023】

8.前記1から7項のいずれか一つの半導体集積回路装置の製造方法において、前記工程(e)および(i)におけるパターニングは、193nmの露光光を用いたArFリソグラフィにより実行される。

【0024】

9.前記1から8項のいずれか一つの半導体集積回路装置の製造方法において、前記第1のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【0025】

10.前記1から9項のいずれか一つの半導体集積回路装置の製造方法において、前記第2のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層塗布系レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【0026】

11.前記1から10項のいずれか一つの半導体集積回路装置の製造方法において、更に以下の工程を有する:

(n)前記工程(l)の後であって前記工程(m)の前に、前記半導体ウエハの前記第1の主面に対して、選択エピタキシャル層を成長させる工程。

【0027】

12.前記11項の半導体集積回路装置の製造方法において、前記選択エピタキシャル層は、SiGe系エピタキシャル層である。

【0028】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0029】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ(能動素子)単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、集積回路構成の代表的なものとしては、Nチャネル型MISFETとPチャネル型MISFETを組み合わせたCMOS(Complemetary Metal Oxide Semiconductor)型集積回路に代表されるCMIS(Complemetary Metal Insulator Semiconductor)型集積回路を例示することができる。

【0030】

今日の半導体集積回路装置、すなわち、LSI(Large Scale Integration)のウエハ工程は、通常、原材料としてのシリコンウエハの搬入からプリメタル(Premetal)工程(M1配線層下端とゲート電極構造の間の層間絶縁膜等の形成、コンタクトホール形成、タングステンプラグ、埋め込み等からなる工程)あたりまでのFEOL(Front End of Line)工程と、M1配線層形成から始まり、アルミニウム系パッド電極上のファイナルパッシベーション膜へのパッド開口の形成あたりまで(ウエハレベルパッケージプロセスにおいては、当該プロセスも含む)のBEOL(Back End of Line)工程に大別できる。

【0031】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0032】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0033】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0034】

窒化シリコン膜は、SAC(Self−Aligned Contact)技術におけるエッチストップ膜として、多用されるほか、SMT(Stress Memorization Technique)における応力付与膜(Stressor Film)としても使用される。

【0035】

同様に、本願において、「シリサイド」または「シリサイド層」というときは、通常、ニッケルシリサイドやニッケル白金シリサイドを指すが、ニッケルモノシリサイドを主要な構成要素の一つとする合金、混晶等を含む。また、シリサイドは、ニッケルシリサイド、ニッケル白金シリサイド等に限らず、従来から実績のあるコバルトシリサイド、チタンシリサイド、タングステンシリサイド等でもよい。また、シリサイド化のための金属膜としては、Ni(ニッケル)膜以外にも、例えばNi−Pt合金膜(NiとPtの合金膜)、Ni−V合金膜(NiとVの合金膜)、Ni−Pd合金膜(NiとPdの合金膜)、Ni−Yb合金膜(NiとYbの合金膜)またはNi−Er合金膜(NiとErの合金膜)のようなニッケル合金膜などを用いることができる。なお、これらのニッケルを主要な金属元素とするシリサイドを「ニッケル系のシリサイド」と総称する。

【0036】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0037】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0038】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0039】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0040】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0041】

1.本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等の説明(主に図1)

図1は本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明するためのウエハ及びチップ上面図である。これに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップの上面レイアウト等を説明する。

【0042】

図1に示すように、ウエハ工程途中のウエハ1(ここでは、300φシリコン単結晶ウエハを例に取り説明するが、直径は450φでも200ファイでも良い)のデバイス主面1a(第1の主面)には、多数のチップ領域2が形成されている。また、ウエハ1には、その配向を判別するためのノッチ3が設けられている。なお、ウエハ1のデバイス主面1aの面方位は、たとえば(100)面(これと等価な面を含む)であり、ノッチ3方向の結晶方位は、たとえば〈110〉方位である。なお、各MISFETのチャネル方向CD1,CD2すなわち、チャネル長方向(ソースからドレインへ、またはドレインからソースの方向、すなわち、〈110〉と等価な方向である)は、特にそうでない旨、明示しない場合には、矢印の方向である。また、方位又は結晶面は、実質的な意味であり、当該方位(又は結晶面)自体のみでなく、その周辺で若干ずらせたものも含む(たとえば、前後に7度程度以内)。

【0043】

次に、各チップ2(チップ領域)のレイアウトの詳細を説明する。チップ領域2の周辺部4には、多数のボンディングパッド5が設けられており、内部領域にはメモリ領域6および非メモリ領域7が設けられている。ここで、メモリ領域6としては、SRAM(Static Random Access Memory)を例示するが、これに限らず、DRAM(Dynamic Random Access Memory)でもフラッシュメモリでもよい。なお、「メモリ領域」とは、正確にはメモリセル領域を指す。従って、メモリ周辺回路の多くの部分は、非メモリ領域7に属する。従って、非メモリ領域7には、このようなメモリ周辺回路のほか、ロジック回路、アナログ回路等が含まれる。

【0044】

2.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要説明(主に図2から図9)

ここでは、セクション1のSRAM混載ロジックチップの説明を受けて、メモリ領域6および非メモリ領域7(図1)におけるゲート電極等のパターニング(ダブルパターニングプロセス)について説明する。

【0045】

図2は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図3は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図4は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。図5は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング用ハードマスクライン&スペースエッチング完了時)である。図6は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図7は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図8は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明するための図1のメモリ領域切り出し部R1および非メモリ領域切り出し部R2の上面図(ゲート電極パターニング完了時)である。図9は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明するための図2のA−B−C−D−E断面に対応するデバイス断面図(ゲート電極パターニング完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの概要を説明する。

【0046】

まず、ゲート電極膜加工前のウエハ1を準備する(図2及び図3を参照)。これは、たとえば、以下のように行う。たとえば、P型のシリコン単結晶ウエハ1を準備して、デバイス主面1a(裏面1bの反対の主面)に、たとえばSTI(Shallow Trench Isolation)等の素子分離領域9を形成し、続いて、アクティブ領域8にウエル領域等の必要な不純物ドープ領域を形成する。

【0047】

更に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、High−kゲート絶縁膜16(High−kゲート絶縁膜を含むゲート絶縁膜)を成膜する。ここで、「High−kゲート絶縁膜」とは、従前の酸化シリコン膜を主要な膜構成要素とするゲート絶縁膜(酸化シリコン膜、酸窒化シリコン膜、窒化シリコン膜又はこれらの積層膜)よりも誘電率の高いゲート絶縁膜をいう。

【0048】

次に、High−kゲート絶縁膜16上のほぼ全面に、たとえば、窒化チタン膜等のゲート電極膜14の下層膜14bを成膜する。

【0049】

次に、窒化チタン膜14b上のほぼ全面に、たとえば、ゲート電極膜14の上層膜としてポリシリコン膜14a(アモルファスシリコン膜でも良い)を成膜する。

【0050】

次に、ポリシリコン膜14a上のほぼ全面に、ゲート加工用ハードマスク膜10(たとえば、窒化シリコン膜)を、たとえばCVD(Chemical Vapor Deposition)により成膜する。

【0051】

次に、窒化シリコン膜10上のほぼ全面に、ゲート電極パターニング用レジスト膜15(第2のレジスト膜またはゲート電極ライン&スペースパターニング用レジスト膜)を塗布等により形成する。ゲート電極パターニング用レジスト膜15は、SOC(Spin On Carbon)膜等の炭素系下層非感光性膜15c(下層膜)、Si−BARC(Silicon−Bottom Anti−Reflection Coating)膜等のシリコン系中間層非感光性膜15b(中間層膜)、ArF化学増幅型レジスト膜等の有機系上層感光性膜15a(上層膜)等から構成されている。Si−BARC膜は、シリコンを主要な成分の一つとして含む(シリコン含有量は、たとえば、15重量%から45重量%程度、以下の第2のレジスト膜についても同じ)塗布系またはCVDによる反射防止膜である。また、SOC膜は、炭素を主要な成分の一つとして含む(炭素含有量は、たとえば、80重量%から90重量%程度、以下の第2のレジスト膜についても同じ)塗布系またはCVD(CVD系の炭素系膜は、アモルファスカーボンと呼ばれる)による下地膜(シリコン系の部材に対してエッチング選択性を持つ膜)である。

【0052】

次に、図2及び図3に示すように、ArF化学増幅型レジスト膜15aの露光および現像を実行して、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aを形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。ここで、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aの幅は、パターニング当初、45nm程度であるが、以下に説明するトリミング処理によって、30nm程度とする。なお、このステップにおける炭素系の下層膜は、SOC膜等の塗布系の平坦化膜が好適である。

【0053】

続いて、多層レジスト膜15のArF化学増幅型レジスト膜15a(上層膜)のパターンを順次、Si−BARC膜15b(中間層膜)、SOC膜15c(下層膜)に転写する(詳細は、セクション3で説明する)。

【0054】

次に、図4及び図5に示すように、パターニングされたゲート電極パターニング用多層レジスト膜15(第2のレジスト膜)マスクとして、ドライエッチングにより、ゲート加工用ハードマスク膜10(窒化シリコン膜)をパターニングする。その後、残留するゲート電極パターニング用レジスト膜15をアッシング等により除去する。

【0055】

次に、図6及び図7に示すように、先と同様に、ウエハ1のデバイス面1a側のほぼ全面に、隣接ゲート電極間切断領域パターニング用多層レジスト膜11(第1のレジスト膜)を、たとえば塗布等により形成する。多層レジスト膜11は、先と同様に、SOC(Spin On Carbon)膜等の炭素系下層非感光性膜11c(下層膜)、Si−BARC(Silicon−Bottom Anti−Reflection Coating)膜等のシリコン系中間層非感光性膜11b(中間層膜)、ArF化学増幅型レジスト膜等の有機系上層感光性膜11a(上層膜)等から構成されている。

【0056】

次に、ArF化学増幅型レジスト膜11aの露光および現像を実行して、隣接ゲート電極間切断領域に対応するレジスト膜開口12を形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。ここで、レジスト膜開口12の幅(短い方の変の長さに等価)は、たとえば60から70nm程度であり、素子分離領域の幅と同程度であるが、後に述べるシュリンク処理により、たとえば、20から25nm程度とする。

【0057】

続いて、多層レジスト膜11のArF化学増幅型レジスト膜11a(上層膜)のパターンを順次、Si−BARC膜11b(中間層膜)、SOC膜11c(下層膜)に転写する(詳細は、セクション3で説明する)。その後、残留するゲート電極パターニング用レジスト膜11をアッシング等により除去する。

【0058】

次に、図8及び図9に示すように、パターニングされたゲート加工用ハードマスク膜10(窒化シリコン膜)をマスクとして、ドライエッチングにより、ゲート電極膜14(ポリシリコン膜14a、窒化チタン膜14b)およびHigh−kゲート絶縁膜16を加工して、ゲート電極14を形成する。

【0059】

3.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細説明(主に図10から図13および図14から図21)

図10は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用多層レジスト膜形成完了時)である。図11は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜パターニング完了時)である。図12は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極ライン&スペースパターニング用上層レジスト膜トリミング完了時)である。図13は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するX−X’断面およびD−E断面のデバイス断面図(ゲート電極パターニング用ハードマスクのライン&スペースパターニング完了時)である。図14は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜形成完了時)である。図15は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用上層レジスト膜パターニング完了時)である。図16は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用中層レジスト膜パターニング完了時)である。図17は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用下層レジスト膜パターニング完了時)である。図18は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜開口シュリンク完了時)である。図19は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域のハードマスクへのパターニング完了時)である。図20は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(隣接ゲート電極間切断領域パターニング用多層レジスト膜除去完了時)である。図21は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細ステップを説明するための図2から図9のプロセスフローに対応するy−y’断面およびD−E断面のデバイス断面図(ゲート電極膜等のエッチング完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲートパターニングプロセスの詳細を説明する。

【0060】

まず、図10に示すように、たとえば、P型のシリコン単結晶ウエハ1を準備して、デバイス主面1aに、たとえばSTI等の素子分離領域9を形成し、続いて、アクティブ領域8にウエル領域等の必要な不純物ドープ領域を形成する。

【0061】

更に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、High−kゲート絶縁膜16(High−kゲート絶縁膜を含むゲート絶縁膜)を成膜する。High−kゲート絶縁膜16としては、たとえば、厚さ0.7から1.5nm程度の酸化ハフニウム系絶縁膜を例示することができる。

【0062】

次に、High−kゲート絶縁膜16上のほぼ全面に、たとえば、窒化チタン膜(たとえば厚さ10nm程度)等のゲート電極膜14の下層膜14bを成膜する。

【0063】

次に、窒化チタン膜14b上のほぼ全面に、ゲート電極膜14の上層膜として、たとえば厚さ50nm程度のポリシリコン膜14a(アモルファスシリコン膜でも良い)を成膜する。

【0064】

次に、ポリシリコン膜14a上のほぼ全面に、ゲート加工用ハードマスク膜10として、たとえば、CVDにより、窒化シリコン膜(たとえば、厚さ50nm程度)を成膜する。

【0065】

次に、ウエハ1のデバイス主面1a(第1の主面)のほぼ全面に、ゲート電極パターニング用多層レジスト膜15(第2のレジスト膜)を塗布等により形成する。多層レジスト膜15は、たとえば、以下のように形成する。すなわち、最初に、ウエハ1のデバイス面1a上のほぼ全面に、SOC膜等の炭素系下層非感光性膜15c(下層膜)を塗布等により形成する(たとえば厚さ100から300nm程度)。続いて、SOC膜15c上のほぼ全面に、たとえばSi−BARC膜等のシリコン系中間層非感光性膜15b(中間層膜)を塗布等により形成する(たとえば厚さ10から100nm程度)。続いて、Si−BARC膜15b上のほぼ全面に、たとえばArF化学増幅型レジスト膜等の有機系上層感光性膜15a(上層膜)を塗布等により形成する(たとえば厚さ50から180nm程度)。

【0066】

次に、図11に示すように、ArF化学増幅型レジスト膜15aの露光および現像を実行して、ゲート電極のラインアンドスペースパターンに対応するレジスト膜パターン15aを形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。

【0067】

次に、図12に示すように、パターニングされたレジスト膜パターン15aに対して、トリミング(Trimming)処理を施すことにより、最終的なレジスト膜パターン15aの幅を元のレジスト膜の幅19よりも狭くする。トリミング処理は、ドライエッチングと同様の処理であり、通常、後続のエッチングプロセスと同一の装置又は同一のチャンバ内で実行される。トリミング処理の雰囲気ガスとしては、たとえば、Cl2/O2系ガスを例示することができる。

【0068】

続いて、トリミングされたレジスト膜パターン15aを先と同様に、順次、Si−BARC膜15b(エッチング雰囲気は、たとえばCF4系ガス雰囲気)、SOC膜15c(エッチング雰囲気は、たとえばO2系ガス雰囲気)へ転写する。

【0069】

次に、図13に示すように、パターニングされたSOC膜15cをマスクとして、ドライエッチングにより、ゲート加工用ハードマスク膜10(窒化シリコン膜)をパターニングする。その後、残留するゲート電極パターニング用レジスト膜15をアッシング等により除去する。

【0070】

次に、図14に示すように、窒化チタン膜14b上のほぼ全面に、隣接ゲート電極間切断領域パターニング用多層レジスト膜11(第1のレジスト膜)を塗布等により形成する。多層レジスト膜11は、たとえば、以下のように形成する。すなわち、最初に、ポリシリコン膜14a上のほぼ全面に、SOC膜等の炭素系下層非感光性膜11c(下層膜)を塗布等により形成する(たとえば厚さ100から300nm程度)。なお、CVD(Chemical Vapor Deposition)によるアモルファスカーボン膜等でもよい。続いて、SOC膜11c上のほぼ全面に、たとえばSi−BARC膜(たとえば厚さ10から100nm程度)等のシリコン系中間層非感光性膜11b(中間層膜)を塗布等により形成する。続いて、Si−BARC膜11b上のほぼ全面に、たとえばArF化学増幅型レジスト膜等の有機系上層感光性膜11a(上層膜)を塗布等により形成する(たとえば厚さ50から180nm程度)。

【0071】

次に、図15に示すように、ArF化学増幅型レジスト膜11aの露光および現像を実行して、隣接ゲート電極間切断領域に対応するレジスト膜開口12を形成する。ArFエキシマレーザ光(波長は193nm)による露光は、たとえば、光学マスクおよび液浸縮小投影露光装置(液浸スキャナー)を使用して行う。

【0072】

次に、図16に示すように、パターニングされたArF化学増幅型レジスト膜11aをマスクとして、たとえばフルオロカーボン(Fluorocarbon)系ガス(たとえばCF4等)を用いたドライエッチングにより、ArF化学増幅型レジスト膜11aのパターンをSi−BARC膜11bに転写する。

【0073】

次に、図17に示すように、パターニングされたSi−BARC膜11bをマスクとして、たとえば酸素系ガス(たとえばO2等)を用いたドライエッチングにより、Si−BARC膜11bのパターンをSOC膜11cに転写する。このとき、同時に、残存していたArF化学増幅型レジスト膜11aが除去される。

【0074】

次に、図18に示すように、ウエハ1を、たとえば、ゲート電極14をエッチングするためのドライエチング装置のエッチング室に導入した状態で、エッチング前処理(シュリンク処理)を実行する(一種のドライエッチング処理である)。すなわち、レジスト膜開口12の側壁にシュリンク用側壁18を形成する。シュリンク処理条件としては、ガス雰囲気:たとえばCHF3(100から300sccm)/O2(10から50sccm)、RF電力:たとえば500から1000ワット程度、ウエハバイアス:100から300ボルト、ウエハステージ温度:摂氏10から50度程度を例示することができる。

【0075】

次に、図19に示すように、パターニングされたSOC膜11cをマスクとして、ドライエッチング(たとえばCH4,CHF3系ガス雰囲気)により、ゲート加工用ハードマスク膜10をパターニングする。このとき同時に、残存していたSi−BARC膜11bが除去される。

【0076】

次に、図20に示すように、SOC膜11cおよびシュリンク用側壁18をアッシング処理およびウエット洗浄等により、除去する。ウエット洗浄の条件としては、たとえば、

(1)第1ステップ:薬液は希塩酸で、組成は、たとえば、塩化水素濃度0.0418モル%程度、処理時間は、常温(摂氏15度から25度)で60秒程度、

(2)第2ステップ:薬液は混酸で、組成は、たとえば、塩化水素濃度0.411モル%程度、弗化水素濃度0.0106モル%程度、処理時間は、常温(摂氏15度から25度)で60秒程度を好適な一例として示すことができる。

【0077】

次に、図21に示すように、パターニングされたゲート加工用ハードマスク膜10をマスクとして、ドライエッチングにより、ポリシリコン膜14a(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、HBr等)、窒化チタン膜14b(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、Cl2/HBr等)、ゲート絶縁膜16(エッチングガスとしては、ハロゲン系ガスで、具体的には、たとえば、BCl3/Cl2等)に順次、ゲート電極14(図22参照)を形成する。

【0078】

4.本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要説明(主に図22から図34)

図22は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(図21と同じ、すなわち、ゲート電極膜等のエッチング完了時)である。図23は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(オフセットスペーサおよびエクステンション領域導入完了時)である。図24は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(サイドウォール形成用絶縁膜成膜完了時)である。図25は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側サイドウォール形成完了時)である。図26は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域リセス形成完了時)である。図27は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Pチャネル側ソースドレイン領域埋め込み選択エピタキシ成長完了時)である。図28は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成完了時)である。図29は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(Nチャネル側サイドウォール形成用レジスト膜除去完了時)である。図30は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(窒化シリコン膜エッチストップ用基板表面酸化膜形成完了時)である。図31は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(ハードマスク除去完了時)である。図32は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(プリメタル絶縁膜成膜完了時)である。図33は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(コンタクトホール形成完了時)である。図34は本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明するための図1の非メモリ領域CMISFET対切り出し部R3の模式的デバイス断面図(タングステンプラグ埋め込み完了時)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法におけるゲート加工後の主要プロセスの概要を説明する。

【0079】

図22(図9及び図21と同じプロセスステップ)に基づいて、ゲート電極のラインアンドスペースパターンのパターニングが完了した時点以降の図1の非メモリ領域CMISFET対切り出し部のPチャネルデバイス領域R3pおよび非メモリ領域CMISFET対切り出し部のNチャネルデバイス領域R3nに対応する部分を説明する。図22に示すように、ウエハ1のP型単結晶シリコン基板部の上半部に、Nウエル領域1nおよびPウエル領域1pが設けられている。

【0080】

次に、図23に示すように、ウエハ1のデバイス面1a上のほぼ全面に、たとえばCVDにより、オフセットスペーサ窒化シリコン膜21(たとえば厚さ2から7nm程度)を成膜する。続いて、異方性ドライエッチングによって、オフセットスペーサ窒化シリコン膜21をエッチバックして、オフセットスペーサ21を形成する。

【0081】

続いて、Pチャネルデバイス領域R3pおよびNチャネルデバイス領域R3nのそれぞれのウエハ1のデバイス面1a表面領域に、イオン注入により、P型エクステンション領域22p(イオン注入条件としては、たとえば、イオン種:BF2、打ち込みエネルギー:1KeVから5KeV、ドーズ量:1x1015/cm2から8x1015/cm2;イオン種:C、打ち込みエネルギー:1KeVから5KeV、ドーズ量:4x1014/cm2から9x1014/cm2)およびN型エクステンション領域22n(イオン注入条件としては、たとえば、イオン種:As、打ち込みエネルギー:1KeVから10KeV、ドーズ量:1x1015/cm2から9x1015/cm2;イオン種:C、打ち込みエネルギー:1KeVから5KeV、ドーズ量:4x1014/cm2から9x1014/cm2)を導入する。

【0082】

次に、図24に示すように、ウエハ1のデバイス面1a上のほぼ全面に、たとえばCVDにより、サイドウォール酸化シリコン膜23a(たとえば厚さ5から10nm程度)を成膜する。続いて、サイドウォール酸化シリコン膜23a上のほぼ全面に、たとえばCVDにより、サイドウォール窒化シリコン膜23b(たとえば厚さ20から30nm程度)を成膜する。

【0083】

次に、図25に示すように、Nチャネル側をPチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜31で被覆した状態で、異方性ドライエッチングにより、Pチャネル領域のサイドウォール絶縁膜23a,23bを形成する。その後、Pチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜31を除去する。

【0084】

次に、図26に示すように、たとえば、ウエットエッチング(たとえば、アルカリ系シリコンエッチング液)または等方性ドライエッチング(ガス系は、たとえば、O2/CF4など)により、P型高濃度SiGeソースドレイン領域24pe(図27参照)となるべき部分にソースドレイン埋め込み用リセス32を形成する。

【0085】

次に、図27に示すように、たとえば、選択エピタキシャル成長により、ソースドレイン埋め込み用リセス32を、ボロンをドープした(ボロン濃度は、たとえば1x1019/cm3から5x1020/cm3程度)SiGe(Ge組成は、たとえば20から40atm%程度)エピタキシャル層すなわちP型高濃度SiGeソースドレイン領域24peで埋め込む(ガス系は、たとえば、SiH4,SiH2Cl2,Si2H6等)。これにより、チャネル領域等に、圧縮応力が作用し、ホール移動度を向上させることができる。また、同様に、Nチャネル領域のソースドレインにも同様にN型不純物をドープしたSiC(炭素組成は、たとえば1atm%程度)エピタキシャル層を導入することにより、チャネル領域等に、引っ張り応力が作用し、電子移動度を向上させることができる。

【0086】

次に、図28に示すように、Pチャネル側をNチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜33で被覆した状態で、異方性ドライエッチングにより、Nチャネル領域のサイドウォール絶縁膜23a,23bを形成する。

【0087】

次に、図29に示すように、Nチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜33を除去する。

【0088】

次に、図30に示すように、熱酸化等により、基板1の表面1a側に、薄い酸化シリコン膜、すなわち窒化シリコン膜エッチストップ用基板表面酸化膜34を形成する。

【0089】

次に、図31に示すように、たとえば、熱燐酸等によるウエット処理によって、ゲート加工用ハードマスク膜10(窒化シリコン膜)等を除去する。

【0090】

次に、図32に示すように、サリサイド(Salicide)方式により、ニッケル系シリサイド膜25(たとえば、NiPtシリサイドなど)を形成する。続いて、ウエハ1のデバイス面1a上のほぼ全面に、たとえばプラズマCVDにより、CESL(Contact Etch Stop Layer)およびプリメタル下層絶縁膜26aとして、窒化シリコン膜(たとえば厚さ20から30nm程度)を成膜する。続いて、窒化シリコン膜26a上のほぼ全面に、たとえばプラズマCVDにより、プリメタル上層絶縁膜26bとして、酸化シリコン膜(たとえば厚さ150から240nm程度)を成膜する。

【0091】

次に、図33に示すように、酸化シリコン膜26b上のほぼ全面に、コンタクトホール形成用レジスト膜27を塗布等する。続いて、通常のリソグラフィにより(たとえば、ArFリソグラフィ)、レジスト膜27をパターニングする。パターニングされたレジスト膜27をマスクとして、順次、異方性ドライエッチングにより、酸化シリコン膜26bおよび窒化シリコン膜26aのコンタクトホール28を開口する。その後、不要になったレジスト膜27をアッシング等により除去する。

【0092】

次に、図34に示すように、コンタクトホール28内にタングステンプラグ29を埋め込む。その後、必要に応じて、多層配線を銅系ダマシン方式(埋め込み配線方式)またはアルミニウム系通常配線方式(非埋め込み配線方式)によって形成する。

【0093】

5.本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセル等の説明(主に図35および図36)

ここでは、6トランジスタセルを例に取り具体的に説明したが、本願の発明は、それに限定されるものではなく、その他の構造のメモリセルにも適用できることは言うまでもない。

【0094】

図35は本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの回路図である。図36は本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセルの実際の平面レイアウトの一例を示すメモリセル平面レイアウト図である。

【0095】

これらに基づいて、本願の前記一実施の形態の半導体集積回路装置の製造方法における対象デバイスの一例であるSOCチップのSRAMメモリセル等を説明する。

【0096】

図35に示すように、SRAMメモリセルMCには、相互に直行して走るワードラインWLおよび一対のビット線BL,BLBが設けられており、それらの交点の近傍には、N型記憶用トランジスタQ1,Q2、P型記憶用トランジスタQ3,Q4、読み出し用トランジスタQ5,Q6、および、これらに電源を供給する電源供給ラインVdd、基準電圧ラインVss等が配置されている。

【0097】

図35のSRAMメモリセルMCを実際のレイアウトの中で示すと、図36のようになる。図36に示すように、縦に走る多数のゲート電極14が、規則的に隣接ゲート電極間切断領域12によって、切断されているのがわかる。多数のコンタクト部28,30の内、横長で示したものは、シェアードコンタクト部30である。ここで、Nチャネルデバイスのアクティブ領域8nのコンタクト部28と、Pチャネルデバイスのアクティブ領域8pのシェアードコンタクト部30の間を相互接続メタル配線ICで連結している。

【0098】

6.本願の前記一実施の形態の半導体集積回路装置の製造方法に関する補足的説明並びに考察等

セクション5に示したようなSRAM幅広セルにおいては、隣り合うゲート間の長手方向の間隔部、すなわち、隣接ゲート電極間切断領域12(図2参照)を小さくすることが、セル面積縮小のために重要な技術課題となる。しかし、28nmテクノロジノード(Technology Node)または、それ以降の世代においては、解像限界以下であるため、ゲート電極のパターニングを1回の光リソグラフィ(たとえば、波長193nmの露光光および液浸縮小投影露光装置を用いたArFリソグラフィ)で実行することは不可能である。また、28nmテクノロジノードまたは、それ以降の世代においては、ゲート積層構造(Gate stack Structure)がHigh−kゲート絶縁膜およびメタル系ゲートを含むものになるため、酸化耐性やウエット処理耐性は、低下する傾向にある。更に、多層レジストプロセスを採用する必要があるため(45nmテクノロジノードまたは、それ以降の世代)、多層レジストプロセスに固有の問題も存在する。

【0099】

解像限界の問題を解決するために、本願においては、レジスト膜等のエッチングマスク膜のパターニングおよび、それを用いた下地膜のエッチングを複数回繰り返す、多重パターニングプロセス(Multiple Patterning Process)を採用している。しかし、単純に、ゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を先行し、続いて、隣接ゲート電極間切断領域12(図2参照)をパターニング(2度目のリソグラフィ)する方法(「L&Sファースト方式」という)では、2度目のリソグラフィにおけるレジスト膜が、メモリ領域6(パターン高密度領域)および非メモリ領域7(パターン低密度領域)の間で平坦性を確保できないという問題がある(図1参照)。

【0100】

そこで、セクション2から4に示した例では、たとえば、先に、ハードマスク10(図5参照)に対して、ゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を実行し、次に、ハードマスクに対して、隣接ゲート電極間切断領域12(図6参照)をパターニング(2度目のリソグラフィ)し、パターニングされたハードマスクを用いて、下地のゲートスタック構造を加工している(「ハードマスク多重パターニング方式」という)。このようにすると、ハードマスク10(図7参照)は、比較的薄いので、2度目の露光の際の平坦性が問題となることがない。なお、前記実施の形態では、露光の順序については、ラインアンドスペースパターンのパターニングを先行するL&Sファースト方式を採用したが、隣接ゲート電極間切断領域のパターニングを先行する方法(「L&Sラスト方式」という)を採用しても良い。

【0101】

また、隣接ゲート電極間切断領域12(図6参照)のパターニングにおいて、シュリンク処理(隣接ゲート電極間切断領域12に対応するレジスト開口の面積を縮小する処理)を伴う場合には、単純なL&Sファースト方式では、下地の凹凸が激しいため、シュリンク形状が下地に依存して不安定な形状となる。一方、ハードマスク多重パターニング方式では、下地が比較的平坦であるため、シュリンク形状が安定する。

【0102】

さらに、酸化耐性やウエット処理耐性の低下の問題を解決するために、ハードマスク多重パターニング方式に加えて、隣接ゲート電極間切断領域12(図6参照)が素子分離領域9の内部に含まれるようにレイアウトすることが有効である(「ゲート端部素子分離領域内レイアウト方式」という)。多重パターニングプロセスにおいては、アッシングやウエット薬液処理を伴うレジスト膜の除去が複数回にわたって行われるため、ゲート絶縁膜の過剰な後退やメタル系ゲート電極部の過剰な酸化が発生しやすい(もっとも、ハードマスクを使用する方式では、ハードマスクを使用しない方式に比べて、アッシングやウエット薬液処理を伴うダメージは、相対的に小さい)。しかし、ゲート端部素子分離領域内レイアウト方式では、そのような多重処理が行われるのは、アクティブ領域上ではなく、主に、素子分離領域9(図6参照)上となるので、デバイス特性への影響を少なくすることができる。

【0103】

なお、ハードマスク多重パターニング方式(露光の順序に無関係である)では、非メモリ領域7のゲート電極のパターニングをメモリ領域6のゲート電極のラインアンドスペースパターンのパターニングと同時に実行するのが有効である。これは、シュリンク処理は、レジストの被覆部分の幅を増加させる処理であるため、ゲート電極のラインアンドスペースパターンのパターニングには適用できないためである。また、そのようにすることによって(シュリンク処理の有無に係らず)、メモリ領域6および非メモリ領域7のゲート電極のラインアンドスペースパターンのパターニングにトリミング処理を適用できるメリットもある。

【0104】

また、ハードマスク多重パターニング方式(露光の順序に無関係である)では、ソースドレイン領域への選択エピタキシ埋め込み方式(図27参照)とのプロセス整合性も良好である。

【0105】

7.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0106】

例えば、前記実施の形態では、非メモリ領域7のゲート電極のパターニングをメモリ領域6のゲート電極のラインアンドスペースパターンのパターニング時のみで行ったが、非メモリ領域7のパターニングに関して以下のようにしてもよい。ハードマスクに対して、メモリ領域6と同時にゲート電極のラインアンドスペースパターンのパターニング(1度目のリソグラフィ)を実行し、次にハードマスクに対して、メモリ領域6の隣接ゲート電極間切断領域をパターニングすると同時に、非メモリ領域の不要なラインアンドスペースパターンを一部除去するようにパターニング(2度目のリソグラフィ)し、パターニングされたハードマスクを用いて、下地のゲートスタック構造を加工してもよい。32nmや28nm以降のテクノロジノードにおいては、非メモリ領域のゲート電極においてもラインアンドスペース構造を取る方が露光の関係から都合がよい。更に本実施例ではハードマスクを用いているために、非メモリ領域の活性領域上のハードマスクを2度目のリソグラフィでパターニングしてもデバイス特性の影響は軽微である。

【0107】

例えば、前記実施の形態では、主にゲートファースト(Gate First)方式を例に取り具体的に説明したが、本発明はそれに限定されるものではなく、ゲートラスト(Gate Last)方式におけるダミーゲートプロセス(Dummy Gate Process)にも適用できることは言うまでもない。

【0108】

また、前記実施の形態では、主にハードマスク(Hard Mask)を使用する方式を例にとり具体的に説明したが、本発明はそれに限定されるものではなく、隣接ゲート電極間切断領域のパターニング(Patterning)およびゲート電極のラインアンドスペースパターン(Line and Space Pattern)のパターニングにハードマスクを使用しなくてもよいことは、言うまでもない。

【0109】

更に、前記実施の形態では、主にPチャネル側のソースドレインにSiGe系部材を用いた例について具体的に説明したが、本発明はそれに限定されるものではなく、Pチャネル側およびNチャネル側のソースドレインに通常のシリコン系部材(SiGe等の合金ではない)やシリコン系合金(SiGe,SiC等)を使用したものにも適用できることは言うまでもない。

【符号の説明】

【0110】

1 ウエハ

1a ウエハ又はチップのデバイス主面(第1の主面)

1b ウエハ又はチップの裏面

1n Nウエル領域

1p Pウエル領域

1s 半導体基板領域(P型シリコン単結晶基板領域)

2 半導体チップ又はチップ領域

3 ノッチ

4 チップ周辺部

5 ボンディングパッド

6 メモリ領域

7 非メモリ領域

8 アクティブ領域

8n Nチャネルデバイスのアクティブ領域

8p Pチャネルデバイスのアクティブ領域

9 素子分離領域(STI)

10 ゲート加工用ハードマスク膜(窒化シリコン膜)

11 隣接ゲート電極間切断領域パターニング用レジスト膜(第1のレジスト膜、またはゲート電極間切断用レジスト膜)

11a 隣接ゲート電極間切断領域パターニング用多層レジスト膜の上層膜

11b 隣接ゲート電極間切断領域パターニング用多層レジスト膜の中間層膜

11c 隣接ゲート電極間切断領域パターニング用多層レジスト膜の下層膜

12 隣接ゲート電極間切断領域(これに対応するレジスト膜開口)

14 ゲート電極(またはゲート電極膜)

14a 多層ゲート電極(またはゲート電極膜)の上層膜

14b 多層ゲート電極(またはゲート電極膜)の下層膜

15 ゲート電極パターニング用レジスト膜(第2のレジスト膜またはゲート電極ライン&スペースパターニング用レジスト膜)

15a ゲート電極パターニング用多層レジスト膜の上層膜

15b ゲート電極パターニング用多層レジスト膜の中間層膜

15c ゲート電極パターニング用多層レジスト膜の下層膜

16 ゲート絶縁膜(High−k膜を有するゲート絶縁膜)

18 シュリンク用側壁

19 トリミングされた部分(元のレジスト膜の幅)

21 オフセットスペーサ窒化シリコン膜(オフセットスペーサ)

22n N型エクステンション領域

22p P型エクステンション領域

23a サイドウォール酸化シリコン膜(酸化シリコン膜サイドウォール)

23b サイドウォール窒化シリコン膜(窒化シリコン膜サイドウォール)

24n N型高濃度ソースドレイン領域

24p P型高濃度ソースドレイン領域

24pe P型高濃度SiGeソースドレイン領域

25 シリサイド層

26a プリメタル下層絶縁膜

26b プリメタル上層絶縁膜

27 コンタクトホール形成用レジスト膜

28 通常のコンタクトホール(またはコンタクト部)

29 タングステンプラグ

30 シェアードコンタクトホール(または当該コンタクト部)

31 Pチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜

32 ソースドレイン埋め込み用リセス

33 Nチャネル領域のサイドウォール絶縁膜エッチバック用レジスト膜

34 窒化シリコン膜エッチストップ用基板表面酸化膜

BL,BLB ビット線

IC 相互接続メタル配線

MC メモリセル

Q1,Q2 N型記憶用トランジスタ

Q3,Q4 P型記憶用トランジスタ

Q5,Q6 読み出し用トランジスタ

R1 メモリ領域切り出し部

R2 非メモリ領域切り出し部

R3 非メモリ領域CMISFET対切り出し部

R3n 非メモリ領域CMISFET対切り出し部のNチャネルデバイス領域

R3p 非メモリ領域CMISFET対切り出し部のPチャネルデバイス領域

Vdd 電源供給ライン

Vss 基準電圧ライン

WL ワードライン

【特許請求の範囲】

【請求項1】

以下の工程を含む半導体集積回路装置の製造方法:

(a)第1及び第2の主面を有する半導体ウエハであって、その第1の主面上に、メモリ領域および非メモリ領域を含む複数のチップ領域を有する前記半導体ウエハを準備する工程;

(b)前記半導体ウエハの前記第1の主面上に、下層のhigh−kゲート絶縁膜および上層のゲートメタル電極膜を有するゲート積層膜を形成する工程;

(c)前記ゲート積層膜上に、ゲート加工用ハードマスク膜を形成する工程;

(d)前記ゲート加工用ハードマスク膜上に、前記メモリ領域におけるゲート電極の延在方向において、隣接ゲート電極間切断領域を規定するための第1のレジスト膜を形成する工程;

(e)前記第1のレジスト膜に対して、パターニングを実行することにより、前記隣接ゲート電極間切断領域に対応するレジスト膜開口を形成する工程;

(f)パターニングされた前記第1のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(g)前記工程(f)の後、前記第1のレジスト膜を除去する工程;

(h)前記工程(c)の後、前記ゲート加工用ハードマスク膜上に、前記メモリ領域における前記ゲート電極に対応するライン&スペースパターンを規定するための第2のレジスト膜を形成する工程;

(i)前記第2のレジスト膜に対して、パターニングを実行する工程;

(j)パターニングされた前記第2のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(k)前記工程(j)の後、前記第2のレジスト膜を除去する工程;

(l)前記工程(g)および(k)の後、パターニングされた前記ゲート加工用ハードマスク膜がある状態で、前記ゲート積層膜に対するエッチングを実行する工程;

(m)前記工程(m)の後、前記ゲート加工用ハードマスク膜を除去する工程。

【請求項2】

前記1項の半導体集積回路装置の製造方法において、前記工程(h)は、前記工程(d)よりも、先に実行される。

【請求項3】

前記1項の半導体集積回路装置の製造方法において、前記工程(h)の前記第2のレジスト膜は、前記非メモリ領域におけるゲート電極に対応するライン&スペースパターンを規定するためのものでもある。

【請求項4】

前記2項の半導体集積回路装置の製造方法において、前記隣接ゲート電極間切断領域は、素子分離領域内にある。

【請求項5】

前記2項の半導体集積回路装置の製造方法において、前記第1のレジスト膜および前記第2のレジスト膜は、それぞれ多層レジスト膜である。

【請求項6】

前記5項の半導体集積回路装置の製造方法において、前記工程(e)は、以下の下位工程を含む:

(e1)前記レジスト膜開口を縮小させる処理を実行する工程;

(e2)前記工程(e1)の後、前記レジスト膜開口下の前記ゲート加工用ハードマスク膜に対する異方性ドライエッチングを実行する工程。

【請求項7】

前記6項の半導体集積回路装置の製造方法において、前記工程(i)は、以下の下位工程を含む:

(i1)パターニングされた前記第2のレジスト膜の幅を縮小させる処理を実行する工程;

(i2)前記工程(i1)の後、前記ゲート加工用ハードマスク膜の内、前記第2のレジスト膜が被覆しない部分に対して、異方性ドライエッチングを実行する工程。

【請求項8】

前記1項の半導体集積回路装置の製造方法において、前記工程(e)および(i)におけるパターニングは、193nmの露光光を用いたArFリソグラフィにより実行される。

【請求項9】

前記5項の半導体集積回路装置の製造方法において、前記第1のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【請求項10】

前記5項の半導体集積回路装置の製造方法において、前記第2のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層塗布系レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【請求項11】

前記5項の半導体集積回路装置の製造方法において、更に以下の工程を有する:

(n)前記工程(l)の後であって前記工程(m)の前に、前記半導体ウエハの前記第1の主面に対して、選択エピタキシャル層を成長させる工程。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記選択エピタキシャル層は、SiGe系エピタキシャル層である。

【請求項1】

以下の工程を含む半導体集積回路装置の製造方法:

(a)第1及び第2の主面を有する半導体ウエハであって、その第1の主面上に、メモリ領域および非メモリ領域を含む複数のチップ領域を有する前記半導体ウエハを準備する工程;

(b)前記半導体ウエハの前記第1の主面上に、下層のhigh−kゲート絶縁膜および上層のゲートメタル電極膜を有するゲート積層膜を形成する工程;

(c)前記ゲート積層膜上に、ゲート加工用ハードマスク膜を形成する工程;

(d)前記ゲート加工用ハードマスク膜上に、前記メモリ領域におけるゲート電極の延在方向において、隣接ゲート電極間切断領域を規定するための第1のレジスト膜を形成する工程;

(e)前記第1のレジスト膜に対して、パターニングを実行することにより、前記隣接ゲート電極間切断領域に対応するレジスト膜開口を形成する工程;

(f)パターニングされた前記第1のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(g)前記工程(f)の後、前記第1のレジスト膜を除去する工程;

(h)前記工程(c)の後、前記ゲート加工用ハードマスク膜上に、前記メモリ領域における前記ゲート電極に対応するライン&スペースパターンを規定するための第2のレジスト膜を形成する工程;

(i)前記第2のレジスト膜に対して、パターニングを実行する工程;

(j)パターニングされた前記第2のレジスト膜がある状態で、前記ゲート加工用ハードマスク膜に対するエッチングを実行する工程;

(k)前記工程(j)の後、前記第2のレジスト膜を除去する工程;

(l)前記工程(g)および(k)の後、パターニングされた前記ゲート加工用ハードマスク膜がある状態で、前記ゲート積層膜に対するエッチングを実行する工程;

(m)前記工程(m)の後、前記ゲート加工用ハードマスク膜を除去する工程。

【請求項2】

前記1項の半導体集積回路装置の製造方法において、前記工程(h)は、前記工程(d)よりも、先に実行される。

【請求項3】

前記1項の半導体集積回路装置の製造方法において、前記工程(h)の前記第2のレジスト膜は、前記非メモリ領域におけるゲート電極に対応するライン&スペースパターンを規定するためのものでもある。

【請求項4】

前記2項の半導体集積回路装置の製造方法において、前記隣接ゲート電極間切断領域は、素子分離領域内にある。

【請求項5】

前記2項の半導体集積回路装置の製造方法において、前記第1のレジスト膜および前記第2のレジスト膜は、それぞれ多層レジスト膜である。

【請求項6】

前記5項の半導体集積回路装置の製造方法において、前記工程(e)は、以下の下位工程を含む:

(e1)前記レジスト膜開口を縮小させる処理を実行する工程;

(e2)前記工程(e1)の後、前記レジスト膜開口下の前記ゲート加工用ハードマスク膜に対する異方性ドライエッチングを実行する工程。

【請求項7】

前記6項の半導体集積回路装置の製造方法において、前記工程(i)は、以下の下位工程を含む:

(i1)パターニングされた前記第2のレジスト膜の幅を縮小させる処理を実行する工程;

(i2)前記工程(i1)の後、前記ゲート加工用ハードマスク膜の内、前記第2のレジスト膜が被覆しない部分に対して、異方性ドライエッチングを実行する工程。

【請求項8】

前記1項の半導体集積回路装置の製造方法において、前記工程(e)および(i)におけるパターニングは、193nmの露光光を用いたArFリソグラフィにより実行される。

【請求項9】

前記5項の半導体集積回路装置の製造方法において、前記第1のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【請求項10】

前記5項の半導体集積回路装置の製造方法において、前記第2のレジスト膜は、以下を有する:

(x1)炭素を主要な成分とする下層塗布系レジスト膜;

(x2)前記下層レジスト膜上に形成されたシリコンを主要な成分の一つとして含む中層レジスト膜;

(x3)前記中層レジスト膜上に形成された感光性の上層レジスト膜。

【請求項11】

前記5項の半導体集積回路装置の製造方法において、更に以下の工程を有する:

(n)前記工程(l)の後であって前記工程(m)の前に、前記半導体ウエハの前記第1の主面に対して、選択エピタキシャル層を成長させる工程。

【請求項12】

前記11項の半導体集積回路装置の製造方法において、前記選択エピタキシャル層は、SiGe系エピタキシャル層である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【公開番号】特開2012−199360(P2012−199360A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−62137(P2011−62137)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]