半導体集積回路装置

【課題】フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供する。

【解決手段】周期的に配置された信号電極線BLと、ワード線方向に、信号電極線BLと同一周期で一列に配置された信号電極線コンタクト13と、を備え、信号電極線BLの側面は、第1絶縁材14と、この第1絶縁材14上に積層された第2絶縁材15とに接しており、ワード線方向の断面において、信号電極線BLの、信号電極線コンタクト13に接する部分の径Dbtmは、信号電極線BLの最上面の径Dtopよりも狭い。

【解決手段】周期的に配置された信号電極線BLと、ワード線方向に、信号電極線BLと同一周期で一列に配置された信号電極線コンタクト13と、を備え、信号電極線BLの側面は、第1絶縁材14と、この第1絶縁材14上に積層された第2絶縁材15とに接しており、ワード線方向の断面において、信号電極線BLの、信号電極線コンタクト13に接する部分の径Dbtmは、信号電極線BLの最上面の径Dtopよりも狭い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、ビット線コンタクトのような周期的コンタクトを有した半導体集積回路装置に関する。

【背景技術】

【0002】

メモリセルを高密度に配置するために信号入力線であるビット線やメモリセルの駆動信号線であるワード線の短周期化が重要なことは言うまでもない。特に、高密度、大容量メモリの代表であるフラッシュメモリにおいては、ビット線周期はメモリセル周期と同一である。そして、ビット線をメモリセルに繋げるにはビット線コンタクトが利用されるが、ビット線コンタクトは、ビット線方向に交差するワード線方向に、ビット線周期と同じ周期で横一列に配置される。ビット線コンタクトの径は、基本的にメモリセルの拡散層幅より広い。孔状パターン(hole pattern)の光学的解像力は、線状パターン(line pattern)に比べて劣るため、径を広めに解像する必要があるからである。

【0003】

このような事情のもと、ビット線コンタクトは、ビット線と同じ周期で配置されるにも関わらず、コンタクトどうし間のスペースは、ビット線どうし間のスペースに比べて狭い。これは、コンタクトどうし間の耐圧が、ビット線どうし間の耐圧に比べて厳しいことを示している。さらに、コンタクトどうし間においては、リークによる不良が、ビット線どうし間に比べて発生しやすいことを示している。

【0004】

また、ビット線は、フォトリソグラフィ技術を用いてパターン転写されるが、その際にビット線コンタクトに対して合わせずれが生じないように工夫しなければならない。合わせずれが大きく生じると、ビット線が、ビット線コンタクトどうし間にずれて形成される。これは、ビット線とこれに隣接するビット線コンタクトとの間の距離が、ビット線コンタクトどうし間の距離よりも狭くなることを示す。つまり、大きな合わせずれは、耐圧不良、及びリーク不良を発生させる可能性を高める。このような合わせずれは、セルの微細化が進むにつれ、無視できない事情となりつつある。特に、ビット線コンタクトが横一列に配置され、メモリセルの密度が極めて高いNANDフラッシュやNORフラッシュなどのフラッシュメモリにおいては、顕著である。

【0005】

なお、ビット線コンタクトを開示した公知例としては、特許文献1がある。

【特許文献1】特開2002−151665号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明は、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供する。

【課題を解決するための手段】

【0007】

この発明の一態様に係る半導体集積回路装置は、周期的に配置された信号電極線と、信号電極線方向と交差する方向に、該信号電極線と同一周期で一列に配置された、前記信号電極線に接続される信号電極線コンタクトと、を備え、前記信号電極線の側面は、第1絶縁材と、この第1絶縁材上に積層された第2絶縁材とに接しており、前記信号電極線方向と交差する方向の断面において、前記信号電極線の、前記信号電極線コンタクトに接する部分の径は、前記信号電極線の最上面の径よりも狭い。

【発明の効果】

【0008】

この発明によれば、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供できる。

【発明を実施するための最良の形態】

【0009】

以下、この発明の一実施形態を、図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。本例では、NAND型フラッシュメモリを示すが、本実施形態は、NAND型フラッシュメモリ以外の電気的に書き換えが可能な不揮発性半導体記憶装置にも、また、不揮発性半導体記憶装置以外の半導体記憶装置にも適用することができる。

【0010】

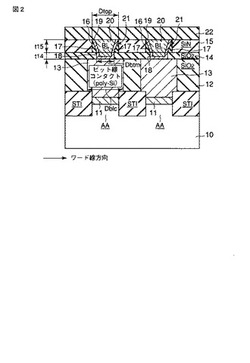

図1はこの発明の一実施形態に係る半導体集積回路装置の平面パターン例を示す平面図、図2は図1中の2−2線に沿う断面図である。図1、図2には、半導体集積回路装置の一例とし、NAND型フラッシュメモリのビット線、及びビット線コンタクトの構造を示す。

【0011】

図1、及び図2に示すように、信号電極線、例えば、ビット線BLは、ビット線方向に延び、ビット線方向に交差、例えば、直交するワード線方向に沿ってビット線周期BLpで一列に配置される。ビット線BLの下面は、信号電極線コンタクト、例えば、ビット線コンタクト13の上面に接続される。

【0012】

ビット線コンタクト13は、ワード線方向に沿って、ビット線周期BLpと同一の周期BLCpで一列に配置される。ビット線コンタクト13の下面は、ドレイン側ブロック選択トランジスタSTDのドレイン拡散層11に接続される。ドレイン拡散層11は、半導体基板、例えば、シリコン基板10のアクティブエリアAAに形成される。アクティブエリアAAは、基板10に素子分離領域STIによって分離される。ビット線コンタクト13は、層間絶縁膜12にホール状の開孔を形成し、この開孔に低抵抗導電性材料を埋め込むことで形成される。ビット線コンタクト13の材料の一例は、導電性多結晶シリコン(poly-Si)である。しかし、これに限られるものではなく金属材料を用いることも可能である。その一例はタングステンである。また、金属材料を用いる場合には、金属材料の側面、及び下面をバリアメタル膜によって覆うようにしても良い。バリアメタル膜の材料は、層間絶縁膜12との密着性、例えば、二酸化シリコンとの密着性が良いものが選ばれる。かつ、ビット線コンタクト13は基板10と接触するため、基板10との合金化性、例えば、シリコンとの合金化性に優れた材料が選ばれる。そのような材料の一例は、窒化チタン膜、あるいはチタンと窒化チタンとの積層膜である。ワード線方向に沿った断面において、ビット線コンタクト13の径Dblcは、同断面におけるビット線BLの最上面径Dtop、あるいはその最下面径Dbtmよりも広い。

【0013】

本例のビット線BLは、層間絶縁膜15から層間絶縁膜14にかけてライン状の溝21を形成し、溝21に低抵抗材料を埋め込むことで形成される。層間絶縁膜14は層間絶縁膜12の上面上、及びビット線コンタクト13の上面上に形成され、層間絶縁膜15は層間絶縁膜14上に形成される。

【0014】

本例では、層間絶縁膜14の材料が層間絶縁膜15の材料と違う。これにより、溝21を形成するとき、層間絶縁膜14をエッチングする際には層間絶縁膜15に対してエッチング選択比をとることができ、反対に、層間絶縁膜14をエッチングする際には層間絶縁膜14に対してエッチング選択比をとることが可能となる。材料の一例は層間絶縁膜14が二酸化シリコンであり、層間絶縁膜15が窒化シリコンである。さらに、本例では、層間絶縁膜14の厚さt14が層間絶縁膜15の厚さt15よりも薄い。これによれば、例えば、ビット線コンタクト13の表面をクリーニングするとき、溝21の側壁に露出する絶縁膜のうち、ビット線コンタクト13に近い側の絶縁膜において、クリーニング剤の影響を受け難くできる、という利点を得ることができる。つまり、クリーニング時において、溝21の不用意な拡大を抑制できる。また、溝21を形成するとき、層間絶縁膜14に対するエッチング時間を、層間絶縁膜15に対するエッチング時間よりも短くできる、という利点が得られる。

【0015】

本例の溝21の断面形状は、間口が広く、奥行きが狭い形状である。具体的には、ワード線方向に沿った断面において、溝21の上部、例えば、ビット線BLの上面における径を“Dtop(最上面径)”としたとき、溝21の下部、例えば、ビット線BLの下面における径Dbtm(最下面径)は、径Dtopよりも狭い。即ち、ワード線方向に沿ったビット線BLの断面において、ビット線コンタクトに接する部分の径は、ビット線BLの最上面の径よりも狭い。また、ワード線方向に沿ったビット線BLの断面において、層間絶縁膜14に接する部分の径は、ビット線BLの最上面の径よりも狭い、とも言える。

【0016】

ビット線BLの材料は、ビット線コンタクト13と同様に、低抵抗導電性材料が選ばれる。本例では、金属材料が選ばれる。その一例はタングステンである。そして、本例では、金属材料膜、例えば、タングステン膜20の側面、及び下面をバリアメタル膜19によって覆う。バリアメタル膜19の材料は、ビット線コンタクト13と同様に、層間絶縁膜12との密着性、例えば、二酸化シリコンとの密着性が良いものが選ばれる。その一例は、窒化チタン膜、あるいはチタンと窒化チタンとの積層膜である。

【0017】

ビット線BLの上面は、平坦化される。平坦化されたビット線BLの上面上、及び層間絶縁膜15の上面上には、周知のNAND型フラッシュメモリと同様に、層間絶縁膜22が形成される。層間絶縁膜22上にも、ビット線BLよりも上方に形成される配線、及び層間絶縁膜が形成される。これらについては、本明細書においては省略する。

【0018】

次に、一実施形態に係る半導体集積回路装置の製造方法の一例を説明する。

【0019】

図3〜図7はこの発明の一実施形態に係る半導体集積回路装置の製造方法の一例を、主要な工程順に示す断面図である。

【0020】

まず、周知の製造方法に従って、層間絶縁膜12、及びビット線コンタクト13までを形成する。例えば、周知の製造方法に従って、素子分離領域STI、浮遊ゲート、ワード線WL、及びブロック選択線SG、メモリセルトランジスタ、及びブロック選択トランジスタのソース、及びドレイン拡散層を形成する。次いで、これらを層間絶縁膜12で覆う。次いで、層間絶縁膜12に対して、ドレイン側ブロック選択トランジスタSTDのドレイン拡散層11に達するホール状の開孔を形成する。次いで、ホール状の開孔を、低抵抗導電性材料、例えば、導電性多結晶シリコンで埋め込み、導電性多結晶シリコンを、エッチバック、あるいはCMPし、平坦化する。これにより、ビット線コンタクト13を形成する。

【0021】

次に、図3に示すように、層間絶縁膜12の上面上、及びビット線コンタクト13の上面上に、例えば、二酸化シリコンを堆積し、層間絶縁膜14を形成する。

【0022】

次に、図4に示すように、層間絶縁膜14上に、例えば、窒化シリコンを堆積し、層間絶縁膜15を形成する。本例では、層間絶縁膜15は、層間絶縁膜14よりも厚く形成する。次いで、層間絶縁膜15上に、フォトレジストを塗布し、フォトレジスト膜30を形成する。次いで、フォトリソグラフィ技術を用いて、フォトレジスト膜30に、ビット線レイアウトに対応したライン状のパターン31を形成する。

【0023】

次に、図5に示すように、フォトレジスト膜30をマスクに用いて、層間絶縁膜15を層間絶縁膜14に達するまでエッチングし、層間絶縁膜15にライン状の溝16を形成する。このエッチングには、例えば、RIE法を用い、そのエッチング条件は層間絶縁膜15をエッチングし易く、層間絶縁膜14をエッチングし難い条件とする。

【0024】

次に、図6に示すように、フォトレジスト膜30を除去した後、層間絶縁膜15の上面上、溝16の底に露呈した層間絶縁膜14上に、例えば、窒化シリコンを堆積し、窒化シリコン膜を形成する。次いで、窒化シリコン膜を、例えば、RIE法を用いてエッチバックし、溝16の側壁に、スペーサ、本例では窒化シリコンスペーサ17を形成する。

【0025】

次に、図7に示すように、層間絶縁膜(窒化シリコン)15、及び窒化シリコンスペーサ17をマスクに用いて、層間絶縁膜(二酸化シリコン)14をビット線コンタクト13に達するまでエッチングし、層間絶縁膜14に溝18を形成する。これにより、ビット線レイアウトに対応したライン状の溝21が形成される。次いで、溝21の底に露呈したビット線コンタクト13の上面に、ウェット、あるいはドライクリーニングを施し、ビット線コンタクト13の上面を清浄化する。ビット線コンタクト13のクリーニングである。クリーニング剤の一例は、フッ酸(HF)である。なお、フッ酸は、層間絶縁膜14、及び層間絶縁膜15をエッチングする性質を持つ。このため、クリーニング時には、溝21の径を、不用意に拡大させる可能性がある。しかも、フッ酸の二酸化シリコンに対するエッチングレートは、窒化シリコンに対するエッチングレートよりも高い。このため、溝21のビット線コンタクト13に接する部分の径は、不用意に拡大しやすい。この点、本例では、層間絶縁膜(二酸化シリコン)14を、層間絶縁膜(窒化シリコン)15の厚さよりも薄くすることで、溝21のビット線コンタクト13に接する部分の径を拡大し難くしている。例えば、層間絶縁膜14を薄くすることで、クリーニング剤の、層間絶縁膜14に対する浸透、又は到達を抑制する。また、耐圧特性は、層間絶縁膜(窒化シリコン)15の方が、層間絶縁膜(二酸化シリコン)14よりも優れる。このため、層間絶縁膜14を薄く、層間絶縁膜15を厚くすることで、ビット線BLどうし間の耐圧特性を向上できる。

【0026】

なお、窒化シリコンスペーサ17のワード線方向に沿った幅は、フォトリソグラフィ時のビット線幅と、最終的に要求されるビット線幅との差に加えて、クリーニング時の後退量等の加工変換差を考慮して決定すれば良い。

【0027】

次に、図2に示すように、層間絶縁膜15上、窒化シリコンスペーサ17上、層間絶縁膜14の側面上、及びビット線コンタクト13の上面上に、バリアメタル材料、例えば、窒化チタン、又はチタンと窒化チタンを堆積し、バリアメタル膜19を形成する。次いで、バリアメタル膜19上に、ビット線材料、例えば、タングステンを堆積し、タングステン膜20を形成する。次いで、タングステン膜20、及びバリアメタル膜19を、CMP法を用いて平坦化し、これら膜を、ライン状の溝21に埋め込む。これにより、溝21に埋め込まれたビット線BLが形成される。

【0028】

以後の工程は周知の製造方法に従えば良い。よって、本明細書では省略する。

【0029】

一実施形態に係る半導体集積回路装置によれば、層間絶縁膜15には、ワード線方向に沿った断面の径が広い溝16を形成し、一旦、その径を、窒化シリコンスペーサ17で細めて層間絶縁膜14に溝18を形成する。このため、ビット線レイアウトに対応したライン状のパターン、本例では、溝21を、フォトリソグラフィでは余裕のある寸法で形成することが可能となる。その一方で、ビット線コンタクト13と隣接するビット線BLの下部の寸法を縮小化できる。このため、合わせずれが生じた場合でも、ビット線BLとこれ隣接するビット線コンタクト13との間の距離は充分に離すことが可能となり、耐圧不良や、リーク不良の悪化を抑制することが可能となる。

【0030】

このように、一実施形態によれば、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を得ることができる。

【0031】

また、溝21を、フォトリソグラフィでは余裕のある寸法で形成できるので、合わせ規格を厳しくする傾向から、反対に、緩和する傾向に向かわせることも可能となる。これによれば、製造工程中の合わせずれによるリソグラフィのやり直し、例えば、フォトマスクの位置修正の頻度を下げることができ、半導体集積回路装置、例えば、NAND型フラッシュメモリのスループットを向上できる、という利点も得られる。スループットが向上することで、半導体集積回路装置、例えば、NAND型フラッシュメモリの製造コスト、ひいてはチップコストの上昇を抑制することもできる。

【0032】

以上、この発明を一実施形態により説明したが、この発明の実施形態は、上記一実施形態が唯一のものではない。その実施にあたっては発明の要旨を逸脱しない範囲で種々に変形することが可能である。

【0033】

また、上記一実施形態は種々の段階の発明を含んでおり、一実施形態において開示した複数の構成要件の適宜な組み合わせにより、種々の段階の発明を抽出することが可能である。

【0034】

また、実施形態は、この発明をNAND型フラッシュメモリに適用した例に基づき説明したが、この発明はNAND型フラッシュメモリに限られるものではなく、NAND型以外のフラッシュメモリにも、さらには、DRAM、SRAM、MRAM、FeRAM等フラッシュメモリ以外のメモリにも適用することができる。さらに、これらメモリを内蔵した半導体集積回路装置、例えば、プロセッサ、システムLSI等もまた、この発明の範疇である。

【図面の簡単な説明】

【0035】

【図1】図1はこの発明の一実施形態に係る半導体集積回路装置の平面パターン例を示す平面図

【図2】図2は図1中の2−2線に沿う断面図

【図3】図3はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図4】図4はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図5】図5はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図6】図6はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図7】図7はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【符号の説明】

【0036】

1…シリコン基板、13…ビット線コンタクト、BL…ビット線、14…層間絶縁膜(二酸化シリコン)、15…層間絶縁膜(窒化シリコン)、17…スペーサ。

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、ビット線コンタクトのような周期的コンタクトを有した半導体集積回路装置に関する。

【背景技術】

【0002】

メモリセルを高密度に配置するために信号入力線であるビット線やメモリセルの駆動信号線であるワード線の短周期化が重要なことは言うまでもない。特に、高密度、大容量メモリの代表であるフラッシュメモリにおいては、ビット線周期はメモリセル周期と同一である。そして、ビット線をメモリセルに繋げるにはビット線コンタクトが利用されるが、ビット線コンタクトは、ビット線方向に交差するワード線方向に、ビット線周期と同じ周期で横一列に配置される。ビット線コンタクトの径は、基本的にメモリセルの拡散層幅より広い。孔状パターン(hole pattern)の光学的解像力は、線状パターン(line pattern)に比べて劣るため、径を広めに解像する必要があるからである。

【0003】

このような事情のもと、ビット線コンタクトは、ビット線と同じ周期で配置されるにも関わらず、コンタクトどうし間のスペースは、ビット線どうし間のスペースに比べて狭い。これは、コンタクトどうし間の耐圧が、ビット線どうし間の耐圧に比べて厳しいことを示している。さらに、コンタクトどうし間においては、リークによる不良が、ビット線どうし間に比べて発生しやすいことを示している。

【0004】

また、ビット線は、フォトリソグラフィ技術を用いてパターン転写されるが、その際にビット線コンタクトに対して合わせずれが生じないように工夫しなければならない。合わせずれが大きく生じると、ビット線が、ビット線コンタクトどうし間にずれて形成される。これは、ビット線とこれに隣接するビット線コンタクトとの間の距離が、ビット線コンタクトどうし間の距離よりも狭くなることを示す。つまり、大きな合わせずれは、耐圧不良、及びリーク不良を発生させる可能性を高める。このような合わせずれは、セルの微細化が進むにつれ、無視できない事情となりつつある。特に、ビット線コンタクトが横一列に配置され、メモリセルの密度が極めて高いNANDフラッシュやNORフラッシュなどのフラッシュメモリにおいては、顕著である。

【0005】

なお、ビット線コンタクトを開示した公知例としては、特許文献1がある。

【特許文献1】特開2002−151665号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明は、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供する。

【課題を解決するための手段】

【0007】

この発明の一態様に係る半導体集積回路装置は、周期的に配置された信号電極線と、信号電極線方向と交差する方向に、該信号電極線と同一周期で一列に配置された、前記信号電極線に接続される信号電極線コンタクトと、を備え、前記信号電極線の側面は、第1絶縁材と、この第1絶縁材上に積層された第2絶縁材とに接しており、前記信号電極線方向と交差する方向の断面において、前記信号電極線の、前記信号電極線コンタクトに接する部分の径は、前記信号電極線の最上面の径よりも狭い。

【発明の効果】

【0008】

この発明によれば、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を提供できる。

【発明を実施するための最良の形態】

【0009】

以下、この発明の一実施形態を、図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。本例では、NAND型フラッシュメモリを示すが、本実施形態は、NAND型フラッシュメモリ以外の電気的に書き換えが可能な不揮発性半導体記憶装置にも、また、不揮発性半導体記憶装置以外の半導体記憶装置にも適用することができる。

【0010】

図1はこの発明の一実施形態に係る半導体集積回路装置の平面パターン例を示す平面図、図2は図1中の2−2線に沿う断面図である。図1、図2には、半導体集積回路装置の一例とし、NAND型フラッシュメモリのビット線、及びビット線コンタクトの構造を示す。

【0011】

図1、及び図2に示すように、信号電極線、例えば、ビット線BLは、ビット線方向に延び、ビット線方向に交差、例えば、直交するワード線方向に沿ってビット線周期BLpで一列に配置される。ビット線BLの下面は、信号電極線コンタクト、例えば、ビット線コンタクト13の上面に接続される。

【0012】

ビット線コンタクト13は、ワード線方向に沿って、ビット線周期BLpと同一の周期BLCpで一列に配置される。ビット線コンタクト13の下面は、ドレイン側ブロック選択トランジスタSTDのドレイン拡散層11に接続される。ドレイン拡散層11は、半導体基板、例えば、シリコン基板10のアクティブエリアAAに形成される。アクティブエリアAAは、基板10に素子分離領域STIによって分離される。ビット線コンタクト13は、層間絶縁膜12にホール状の開孔を形成し、この開孔に低抵抗導電性材料を埋め込むことで形成される。ビット線コンタクト13の材料の一例は、導電性多結晶シリコン(poly-Si)である。しかし、これに限られるものではなく金属材料を用いることも可能である。その一例はタングステンである。また、金属材料を用いる場合には、金属材料の側面、及び下面をバリアメタル膜によって覆うようにしても良い。バリアメタル膜の材料は、層間絶縁膜12との密着性、例えば、二酸化シリコンとの密着性が良いものが選ばれる。かつ、ビット線コンタクト13は基板10と接触するため、基板10との合金化性、例えば、シリコンとの合金化性に優れた材料が選ばれる。そのような材料の一例は、窒化チタン膜、あるいはチタンと窒化チタンとの積層膜である。ワード線方向に沿った断面において、ビット線コンタクト13の径Dblcは、同断面におけるビット線BLの最上面径Dtop、あるいはその最下面径Dbtmよりも広い。

【0013】

本例のビット線BLは、層間絶縁膜15から層間絶縁膜14にかけてライン状の溝21を形成し、溝21に低抵抗材料を埋め込むことで形成される。層間絶縁膜14は層間絶縁膜12の上面上、及びビット線コンタクト13の上面上に形成され、層間絶縁膜15は層間絶縁膜14上に形成される。

【0014】

本例では、層間絶縁膜14の材料が層間絶縁膜15の材料と違う。これにより、溝21を形成するとき、層間絶縁膜14をエッチングする際には層間絶縁膜15に対してエッチング選択比をとることができ、反対に、層間絶縁膜14をエッチングする際には層間絶縁膜14に対してエッチング選択比をとることが可能となる。材料の一例は層間絶縁膜14が二酸化シリコンであり、層間絶縁膜15が窒化シリコンである。さらに、本例では、層間絶縁膜14の厚さt14が層間絶縁膜15の厚さt15よりも薄い。これによれば、例えば、ビット線コンタクト13の表面をクリーニングするとき、溝21の側壁に露出する絶縁膜のうち、ビット線コンタクト13に近い側の絶縁膜において、クリーニング剤の影響を受け難くできる、という利点を得ることができる。つまり、クリーニング時において、溝21の不用意な拡大を抑制できる。また、溝21を形成するとき、層間絶縁膜14に対するエッチング時間を、層間絶縁膜15に対するエッチング時間よりも短くできる、という利点が得られる。

【0015】

本例の溝21の断面形状は、間口が広く、奥行きが狭い形状である。具体的には、ワード線方向に沿った断面において、溝21の上部、例えば、ビット線BLの上面における径を“Dtop(最上面径)”としたとき、溝21の下部、例えば、ビット線BLの下面における径Dbtm(最下面径)は、径Dtopよりも狭い。即ち、ワード線方向に沿ったビット線BLの断面において、ビット線コンタクトに接する部分の径は、ビット線BLの最上面の径よりも狭い。また、ワード線方向に沿ったビット線BLの断面において、層間絶縁膜14に接する部分の径は、ビット線BLの最上面の径よりも狭い、とも言える。

【0016】

ビット線BLの材料は、ビット線コンタクト13と同様に、低抵抗導電性材料が選ばれる。本例では、金属材料が選ばれる。その一例はタングステンである。そして、本例では、金属材料膜、例えば、タングステン膜20の側面、及び下面をバリアメタル膜19によって覆う。バリアメタル膜19の材料は、ビット線コンタクト13と同様に、層間絶縁膜12との密着性、例えば、二酸化シリコンとの密着性が良いものが選ばれる。その一例は、窒化チタン膜、あるいはチタンと窒化チタンとの積層膜である。

【0017】

ビット線BLの上面は、平坦化される。平坦化されたビット線BLの上面上、及び層間絶縁膜15の上面上には、周知のNAND型フラッシュメモリと同様に、層間絶縁膜22が形成される。層間絶縁膜22上にも、ビット線BLよりも上方に形成される配線、及び層間絶縁膜が形成される。これらについては、本明細書においては省略する。

【0018】

次に、一実施形態に係る半導体集積回路装置の製造方法の一例を説明する。

【0019】

図3〜図7はこの発明の一実施形態に係る半導体集積回路装置の製造方法の一例を、主要な工程順に示す断面図である。

【0020】

まず、周知の製造方法に従って、層間絶縁膜12、及びビット線コンタクト13までを形成する。例えば、周知の製造方法に従って、素子分離領域STI、浮遊ゲート、ワード線WL、及びブロック選択線SG、メモリセルトランジスタ、及びブロック選択トランジスタのソース、及びドレイン拡散層を形成する。次いで、これらを層間絶縁膜12で覆う。次いで、層間絶縁膜12に対して、ドレイン側ブロック選択トランジスタSTDのドレイン拡散層11に達するホール状の開孔を形成する。次いで、ホール状の開孔を、低抵抗導電性材料、例えば、導電性多結晶シリコンで埋め込み、導電性多結晶シリコンを、エッチバック、あるいはCMPし、平坦化する。これにより、ビット線コンタクト13を形成する。

【0021】

次に、図3に示すように、層間絶縁膜12の上面上、及びビット線コンタクト13の上面上に、例えば、二酸化シリコンを堆積し、層間絶縁膜14を形成する。

【0022】

次に、図4に示すように、層間絶縁膜14上に、例えば、窒化シリコンを堆積し、層間絶縁膜15を形成する。本例では、層間絶縁膜15は、層間絶縁膜14よりも厚く形成する。次いで、層間絶縁膜15上に、フォトレジストを塗布し、フォトレジスト膜30を形成する。次いで、フォトリソグラフィ技術を用いて、フォトレジスト膜30に、ビット線レイアウトに対応したライン状のパターン31を形成する。

【0023】

次に、図5に示すように、フォトレジスト膜30をマスクに用いて、層間絶縁膜15を層間絶縁膜14に達するまでエッチングし、層間絶縁膜15にライン状の溝16を形成する。このエッチングには、例えば、RIE法を用い、そのエッチング条件は層間絶縁膜15をエッチングし易く、層間絶縁膜14をエッチングし難い条件とする。

【0024】

次に、図6に示すように、フォトレジスト膜30を除去した後、層間絶縁膜15の上面上、溝16の底に露呈した層間絶縁膜14上に、例えば、窒化シリコンを堆積し、窒化シリコン膜を形成する。次いで、窒化シリコン膜を、例えば、RIE法を用いてエッチバックし、溝16の側壁に、スペーサ、本例では窒化シリコンスペーサ17を形成する。

【0025】

次に、図7に示すように、層間絶縁膜(窒化シリコン)15、及び窒化シリコンスペーサ17をマスクに用いて、層間絶縁膜(二酸化シリコン)14をビット線コンタクト13に達するまでエッチングし、層間絶縁膜14に溝18を形成する。これにより、ビット線レイアウトに対応したライン状の溝21が形成される。次いで、溝21の底に露呈したビット線コンタクト13の上面に、ウェット、あるいはドライクリーニングを施し、ビット線コンタクト13の上面を清浄化する。ビット線コンタクト13のクリーニングである。クリーニング剤の一例は、フッ酸(HF)である。なお、フッ酸は、層間絶縁膜14、及び層間絶縁膜15をエッチングする性質を持つ。このため、クリーニング時には、溝21の径を、不用意に拡大させる可能性がある。しかも、フッ酸の二酸化シリコンに対するエッチングレートは、窒化シリコンに対するエッチングレートよりも高い。このため、溝21のビット線コンタクト13に接する部分の径は、不用意に拡大しやすい。この点、本例では、層間絶縁膜(二酸化シリコン)14を、層間絶縁膜(窒化シリコン)15の厚さよりも薄くすることで、溝21のビット線コンタクト13に接する部分の径を拡大し難くしている。例えば、層間絶縁膜14を薄くすることで、クリーニング剤の、層間絶縁膜14に対する浸透、又は到達を抑制する。また、耐圧特性は、層間絶縁膜(窒化シリコン)15の方が、層間絶縁膜(二酸化シリコン)14よりも優れる。このため、層間絶縁膜14を薄く、層間絶縁膜15を厚くすることで、ビット線BLどうし間の耐圧特性を向上できる。

【0026】

なお、窒化シリコンスペーサ17のワード線方向に沿った幅は、フォトリソグラフィ時のビット線幅と、最終的に要求されるビット線幅との差に加えて、クリーニング時の後退量等の加工変換差を考慮して決定すれば良い。

【0027】

次に、図2に示すように、層間絶縁膜15上、窒化シリコンスペーサ17上、層間絶縁膜14の側面上、及びビット線コンタクト13の上面上に、バリアメタル材料、例えば、窒化チタン、又はチタンと窒化チタンを堆積し、バリアメタル膜19を形成する。次いで、バリアメタル膜19上に、ビット線材料、例えば、タングステンを堆積し、タングステン膜20を形成する。次いで、タングステン膜20、及びバリアメタル膜19を、CMP法を用いて平坦化し、これら膜を、ライン状の溝21に埋め込む。これにより、溝21に埋め込まれたビット線BLが形成される。

【0028】

以後の工程は周知の製造方法に従えば良い。よって、本明細書では省略する。

【0029】

一実施形態に係る半導体集積回路装置によれば、層間絶縁膜15には、ワード線方向に沿った断面の径が広い溝16を形成し、一旦、その径を、窒化シリコンスペーサ17で細めて層間絶縁膜14に溝18を形成する。このため、ビット線レイアウトに対応したライン状のパターン、本例では、溝21を、フォトリソグラフィでは余裕のある寸法で形成することが可能となる。その一方で、ビット線コンタクト13と隣接するビット線BLの下部の寸法を縮小化できる。このため、合わせずれが生じた場合でも、ビット線BLとこれ隣接するビット線コンタクト13との間の距離は充分に離すことが可能となり、耐圧不良や、リーク不良の悪化を抑制することが可能となる。

【0030】

このように、一実施形態によれば、フォトリソグラフィにおける合わせずれに対して強い構造を持つ半導体集積回路装置を得ることができる。

【0031】

また、溝21を、フォトリソグラフィでは余裕のある寸法で形成できるので、合わせ規格を厳しくする傾向から、反対に、緩和する傾向に向かわせることも可能となる。これによれば、製造工程中の合わせずれによるリソグラフィのやり直し、例えば、フォトマスクの位置修正の頻度を下げることができ、半導体集積回路装置、例えば、NAND型フラッシュメモリのスループットを向上できる、という利点も得られる。スループットが向上することで、半導体集積回路装置、例えば、NAND型フラッシュメモリの製造コスト、ひいてはチップコストの上昇を抑制することもできる。

【0032】

以上、この発明を一実施形態により説明したが、この発明の実施形態は、上記一実施形態が唯一のものではない。その実施にあたっては発明の要旨を逸脱しない範囲で種々に変形することが可能である。

【0033】

また、上記一実施形態は種々の段階の発明を含んでおり、一実施形態において開示した複数の構成要件の適宜な組み合わせにより、種々の段階の発明を抽出することが可能である。

【0034】

また、実施形態は、この発明をNAND型フラッシュメモリに適用した例に基づき説明したが、この発明はNAND型フラッシュメモリに限られるものではなく、NAND型以外のフラッシュメモリにも、さらには、DRAM、SRAM、MRAM、FeRAM等フラッシュメモリ以外のメモリにも適用することができる。さらに、これらメモリを内蔵した半導体集積回路装置、例えば、プロセッサ、システムLSI等もまた、この発明の範疇である。

【図面の簡単な説明】

【0035】

【図1】図1はこの発明の一実施形態に係る半導体集積回路装置の平面パターン例を示す平面図

【図2】図2は図1中の2−2線に沿う断面図

【図3】図3はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図4】図4はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図5】図5はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図6】図6はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【図7】図7はこの発明の一実施形態に係る半導体集積回路装置の一製造工程を示す断面図

【符号の説明】

【0036】

1…シリコン基板、13…ビット線コンタクト、BL…ビット線、14…層間絶縁膜(二酸化シリコン)、15…層間絶縁膜(窒化シリコン)、17…スペーサ。

【特許請求の範囲】

【請求項1】

周期的に配置された信号電極線と、

信号電極線方向と交差する方向に、該信号電極線と同一周期で一列に配置された、前記信号電極線に接続される信号電極線コンタクトと、を備え、

前記信号電極線の側面は、第1絶縁材と、この第1絶縁材上に積層された第2絶縁材とに接しており、

前記信号電極線方向と交差する方向の断面において、前記信号電極線の、前記信号電極線コンタクトに接する部分の径は、前記信号電極線の最上面の径よりも狭いことを特徴とする半導体集積回路装置。

【請求項2】

前記信号電極線の前記第1絶縁材に接する部分の径は、前記信号電極線の最上面の径よりも狭いことを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記信号電極線は、導電膜と、この導電膜の側面、及びその下面を被覆するバリア膜との積層構造であることを特徴とする請求項1及び請求項2いずれかに記載の半導体集積回路装置。

【請求項4】

前記第1絶縁材のフッ酸エッチングレートは、前記第2絶縁材のフッ酸エッチングレートよりも高いことを特徴とする請求項3に記載の半導体集積回路装置。

【請求項5】

前記第1絶縁材の厚さは、前記第2絶縁材の厚さよりも薄いことを特徴とする請求項3及び請求項4いずれかに記載の半導体集積回路装置。

【請求項1】

周期的に配置された信号電極線と、

信号電極線方向と交差する方向に、該信号電極線と同一周期で一列に配置された、前記信号電極線に接続される信号電極線コンタクトと、を備え、

前記信号電極線の側面は、第1絶縁材と、この第1絶縁材上に積層された第2絶縁材とに接しており、

前記信号電極線方向と交差する方向の断面において、前記信号電極線の、前記信号電極線コンタクトに接する部分の径は、前記信号電極線の最上面の径よりも狭いことを特徴とする半導体集積回路装置。

【請求項2】

前記信号電極線の前記第1絶縁材に接する部分の径は、前記信号電極線の最上面の径よりも狭いことを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記信号電極線は、導電膜と、この導電膜の側面、及びその下面を被覆するバリア膜との積層構造であることを特徴とする請求項1及び請求項2いずれかに記載の半導体集積回路装置。

【請求項4】

前記第1絶縁材のフッ酸エッチングレートは、前記第2絶縁材のフッ酸エッチングレートよりも高いことを特徴とする請求項3に記載の半導体集積回路装置。

【請求項5】

前記第1絶縁材の厚さは、前記第2絶縁材の厚さよりも薄いことを特徴とする請求項3及び請求項4いずれかに記載の半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2007−27571(P2007−27571A)

【公開日】平成19年2月1日(2007.2.1)

【国際特許分類】

【出願番号】特願2005−210293(P2005−210293)

【出願日】平成17年7月20日(2005.7.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成19年2月1日(2007.2.1)

【国際特許分類】

【出願日】平成17年7月20日(2005.7.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]