半導体集積回路装置

【課題】 実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供する。

【解決手段】 第1メモリセルユニット(MU1)の電流通路の一端、及び第2メモリセルユニット(MU2)の電流通路の一端に共通接続された第1ビット線(BL1)と、第3メモリセルユニット(MU3)の電流通路の一端に接続された第2ビット線(BL2)と、第1メモリセルユニット(MU1)の電流通路の他端に接続された第1ソース線(SL1)と、第2メモリセルユニット(MU2)の電流通路の他端、及び第3メモリセルユニット(MU3)の電流通路の他端に共通接続された第2ソース線(SL2)とを具備する。

【解決手段】 第1メモリセルユニット(MU1)の電流通路の一端、及び第2メモリセルユニット(MU2)の電流通路の一端に共通接続された第1ビット線(BL1)と、第3メモリセルユニット(MU3)の電流通路の一端に接続された第2ビット線(BL2)と、第1メモリセルユニット(MU1)の電流通路の他端に接続された第1ソース線(SL1)と、第2メモリセルユニット(MU2)の電流通路の他端、及び第3メモリセルユニット(MU3)の電流通路の他端に共通接続された第2ソース線(SL2)とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、電気的に書き換えが可能な不揮発性半導体記憶装置を備えた半導体集積回路装置に関する。

【背景技術】

【0002】

不揮発性半導体記憶装置、特に、NAND型フラッシュメモリの微細化が進んでいる。近時では、最小加工寸法をFとしたとき、面積が“2F×2F=4F2”となるメモリセルが開発されている(非特許文献1)。

【0003】

このメモリセルを集積したメモリセルアレイにおいては、素子領域の配置ピッチが2Fである。故に、ビット線の配置ピッチは2Fとなり、ビット線とブロック選択トランジスタの拡散層とを接続するビット線コンタクトの配置ピッチも2Fとなる。

【0004】

しかしながら、ビット線コンタクトのパターンは、素子領域のパターンや、ビット線のパターンのようにラインパターンではなく、ホールパターンである。ホールパターンは、ラインパターンよりも解像度が弱く、エッチング時の誤差も大きい。このため、ビット線コンタクトをピッチ2Fで配置したメモリセルを形成することは、技術的に極めてタイトである。

【0005】

そこで、ビット線コンタクトを2倍のピッチに緩和したメモリセルアレイが、特許文献1に記載されている。本明細書においては、この種のメモリセルアレイに用いるメモリセルを、倍ピッチセルと呼ぶ。

【非特許文献1】三宅 常之、「16GビットNANDフラッシュへの道、東芝が50nmで4F2の「究極のセル」実現へ」、日経マイクロデバイス2003年8月号、pp57−62

【特許文献1】特開2005−56989

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明は、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供する。

【課題を解決するための手段】

【0007】

この発明の一態様に係る半導体集積回路装置は、選択トランジスタ間に、直列に接続されたメモリセルトランジスタを含む第1乃至第3メモリセルユニットと、前記第1メモリセルユニットの電流通路の一端、及び前記第2メモリセルユニットの電流通路の一端に共通接続された第1ビット線と、前記第3メモリセルユニットの電流通路の一端に接続された第2ビット線と、前記第1メモリセルユニットの電流通路の他端に接続された第1ソース線と、前記第2メモリセルユニットの電流通路の他端、及び前記第3メモリセルユニットの電流通路の他端に共通接続された第2ソース線とを具備する。

【発明の効果】

【0008】

この発明によれば、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供できる。

【発明を実施するための最良の形態】

【0009】

特許文献1には、倍ピッチセルが開示されている。倍ピッチセルは、ビット線コンタクトを2倍のピッチに緩和でき、典型的なメモリセルに比較して加工しやすい。即ち、微細化に適している。そして、特許文献1は、倍ピッチセルを利用したNAND型フラッシュメモリ基本的な回路構成を記載する。しかしながら、より実用に適した回路構成については記載がない。

【0010】

以下、この発明の一実施形態を、図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。この一実施形態は、半導体集積回路装置としてNAND型フラッシュメモリを例示するが、この発明は、NAND型フラッシュメモリに限って適用されるものではなく、NAND型フラッシュメモリ以外のメモリにも適用することができる。

【0011】

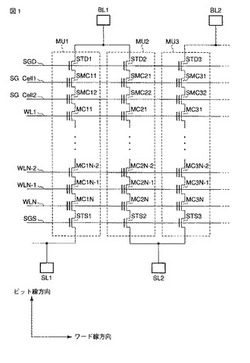

図1はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの等価回路の一例を示す回路図、図2はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの構造の一例を示す平面図、図3は図2に示す3−3線に沿う断面図である。

【0012】

図1〜図3に示すように、半導体基板、例えば、P型シリコン基板(又はP型シリコンウェル)1上には、素子分離領域2が形成される。素子分離領域2は、基板1の表面に、素子領域AAを分離する。素子分離領域2の一例は、シャロートレンチアイソレーション(STI)である。素子領域AA、及び素子分離領域2は、基板1上に、ピッチPで配置される。ピッチPの一例は2Fである。“F”は最小加工寸法である。素子領域AA、及び素子分離領域2は、例えば、双方とも最小加工寸法Fで形成される。

【0013】

素子領域AAには、メモリセルユニットMU(MU1、MU2、MU3、…)が配置される。本例のメモリセルユニットMUは、ブロック選択トランジスタSTD(STD1、STD2、STD3、…)、STS(STS1、STS2、STS3、…)間に、直列に接続されたメモリセルトランジスタMC(MC11〜MC3N、…)を含む。

【0014】

ビット線BL(BL1、BL2、BL3、…)は、本例では、例えば、2つの素子領域AAに対して1つ配置される。

【0015】

第1ビット線BL1は第1メモリセルユニットMU1の電流通路の一端、及び第2メモリセルユニットMU2の電流通路の一端に共通接続され、第2ビット線BL2は第3メモリセルユニットの電流通路の一端に接続される。第1メモリセルユニットMU1、第2メモリセルユニットMU2、及び第3メモリセルユニットMU3は、ワード線方向に隣接し、ワード線WL(WL1、WL2、…WLN)を共有する。第1メモリセルユニットMU1〜第3メモリセルユニットMU3の電流通路の一端は、本例ではN型拡散層3Dである。N型拡散層3Dは、ドレイン側ブロック選択トランジスタSTDのドレインである。ビット線BL(BL1、BL2、BL3、…)は、本例では、ビット線コンタクト4Dを介してN型拡散層3Dに接続される。ビット線コンタクト4Dは、基板1上に、ピッチ2Pで配置される。ピッチPの一例は、上述の通り2F(Fは最小加工寸法)である。本例のビット線コンタクト4Dは、層間絶縁膜5に形成されたコンタクト孔6に埋め込まれた導電物である。層間絶縁膜5は、素子分離領域2を有した基板1上に形成される。導電物の一例は、タングステンである。なお、本例では、ビット線BL(BL1、BL2、BL3、…)を、ビット線コンタクト4Dを介してN型拡散層3Dに接続しているが、これに限られるものではない。例えば、ビット線BLを、ビット線コンタクト4Dを使わずに、コンタクト孔6を介してN型拡散層3Dに、直接に接続しても良い。

【0016】

ソース線SL(SL1、SL2)は、本例では2組設けられる。2組の第1、第2ソース線SL1、SL2は、メモリセルユニットMUに対して、互いに異なるソース電位を供給することが可能とされる。

【0017】

第1ソース線SL1は第1メモリセルユニットMU1の電流通路の他端に接続され、第2ソース線SL2は、第2メモリセルユニットMU2の電流通路の他端、及び第3メモリセルユニットMU3の電流通路の他端に共通接続される。第1メモリセルユニットMU1〜第3メモリセルユニットMU3の電流通路の他端は、本例ではN型拡散層3Sである。N型拡散層3Sは、ソース側ブロック選択トランジスタSTSのソースである。第1、第2ソース線SL1、SL2は、本例では、ソース線コンタクト4Sを介してN型拡散層3Sに接続される。ソース線コンタクト4Sは、ビット線コンタクト4Dと同様に、基板1上に、ピッチ2Pで配置される。ピッチPの一例は、上述の通り2F(Fは最小加工寸法)である。本例のソース線コンタクト4Sは、ビット線コンタクト4Dと同様に、層間絶縁膜5に形成されたコンタクト孔6に埋め込まれた導電物である。導電物の一例は、タングステンである。なお、本例では、第1、第2ソース線SL1、SL2を、ソース線コンタクト4Sを介してN型拡散層3Sに接続しているが、これに限られるものではない。例えば、第1、第2ソース線SL1、SL2を、コンタクト孔6を介してN型拡散層3Sに、直接に接続しても良い。

【0018】

本例は、ブロック選択トランジスタSTD、STSの他に、さらに、選択トランジスタを有する。この選択トランジスタにはメモリセルトランジスタが利用される。本例では、行列状に配置されたメモリセルトランジスタMCのうち、メモリセルユニットMUの、ドレイン側ブロック選択トランジスタに隣接するメモリセルトランジスタMC(STMC11、STMC21、STMC31、…)、及びこれらメモリセルトランジスタMC(STMC11、STMC21、STMC31、…)に隣接するメモリセルトランジスタMC(STMC12、STMC22、STMC32、…)を選択トランジスタとして利用する。

【0019】

以下、選択トランジスタとしての利用方法の一例を説明する。

【0020】

図4はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの初期状態の一例を示す図である。

【0021】

図4に示すように、初期状態においては、メモリセルトランジスタMCの全てが、消去状態である。消去状態のメモリセルトランジスタMCは、例えば、デプレッション型とされる。この状態をデータ“1”とする。メモリセルトランジスタMCの全てが、データ“1”であると、メモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…、STMC12、STMC22、STMC32、…)を選択トランジスタとして利用することができない。そこで、本例では、データ消去後、かつ、データ書き込み前に、予備データ書き込みを、メモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…、STMC12、STMC22、STMC32、…)に対して行う。

【0022】

図5、及び図6はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図である。

【0023】

本例の予備データ書き込みは第1、第2ソース線SL1、SL2を利用し、予備データ書き込みのデータは、第1、第2ソース線SL1、SL2から入力する。

【0024】

<予備データ書き込み(1)>

まず、第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)に対して、予備データ書き込みを行う。

【0025】

図5に示すように、ドレイン側ブロック選択ゲート線SGDの電位を0V、ソース側ブロック選択ゲート線SGSの電位をVccとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)は全てオフし、ソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は全てオンする。

【0026】

なお、ビット線BL(BL1、BL2、…)の電位は、例えば、Vccとする。

【0027】

次いで、第1ソース線SL1の電位を0V、第2ソース線SL2の電位をVccとする。

【0028】

次いで、ワード線WL(WL1〜WLN)の電位、及び第2セル選択ゲート線SG Cell2の電位を、Vpassとする。さらに、第1セル選択ゲート線SG Cell1の電位を、Vpassよりも高いVpgmとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)には、第1、第2ソース線SL1、SL2の電位に応じたデータが書き込まれる。

【0029】

本例では、第1ソース線SL1に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC11、STMC41、STMC51、…)には、データ“0”が書き込まれる。メモリセルトランジスタSTMC(STMC11、STMC41、STMC51、…)は、例えば、デプレッション型からエンハンスメント型に変わる。

【0030】

また、第2ソース線SL2に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)は、データ“0”を維持する。メモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)は、デプレッション型のままである。

【0031】

<予備データ書き込み(2)>

次に、第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)に対して、予備データ書き込みを行う。

【0032】

図6に示すように、ブロック選択ゲート線SGD、SGS、ビット線BL(BL1、BL2、…)の電位は、予備データ書き込み(1)と同じである。

【0033】

次いで、第1ソース線SL1の電位を予備データ書き込み(1)とは逆にVcc、第2ソース線SL2の電位も逆に0Vとする。

【0034】

次いで、ワード線WL(WL1〜WLN)の電位、及び第1セル選択ゲート線SG Cell1の電位を、Vpassとする。さらに、第2セル選択ゲート線SG Cell2の電位を、Vpassよりも高いVpgmとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)には、第1、第2ソース線SL1、SL2の電位に応じたデータが書き込まれる。

【0035】

本例では、第2ソース線SL2に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC22、STMC32、STMC62、STMC72、…)には、データ“0”が書き込まれる。メモリセルトランジスタSTMC(STMC22、STMC32、STMC62、STMC72、…)は、例えば、デプレッション型からエンハンスメント型に変わる。

【0036】

また、第1ソース線SL1に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)は、データ“0”を維持する。メモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)は、デプレッション型のままである。

【0037】

以上で、予備データ書き込みが終了する。この後、例えば、データ書き込みが行われる。

【0038】

図7、及び図8はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図である。

【0039】

<データ書き込み(1)>

まず、第1ソース線SL1、又は第2ソース線SL2のいずれかに接続されるメモリセルユニットMUに対して、データ書き込みを行う。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対してデータ書き込みを行うが、データ書き込みの順番は任意である。

【0040】

図7に示すように、ドレイン側ブロック選択ゲート線SGDの電位をVcc、ソース側ブロック選択ゲート線SGSの電位を0Vとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)は全てオンし、ソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は全てオフする。

【0041】

ビット線BL(BL1、BL2、…)の電位は、書き込みデータに応じた電位とする。例えば、書き込みデータが“0”の場合は0Vとし、“1”の場合はVccとする。

【0042】

なお、第1、第2ソース線SL1、SL2の電位は、例えば、Vccとする。

【0043】

次いで、非選択ワード線WLの電位、及び第2セル選択ゲート線SG Cell2の電位を、Vpassとする。選択したワード線WLの電位は、Vpassよりも高いVpgmとする。そして、第1セル選択ゲート線SG Cell1の電位は、0Vとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。ビット線BL(BL1、BL2、…)の電位は、オンしたメモリセルSTMCを含むメモリセルユニットMUに対して、伝えられる。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対して、伝えられる。

【0044】

この結果、第2ソース線SL2に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCには、ビット線BL(BL1、BL2、…)の電位に応じて、データ“0”、又はデータ“1”が書き込まれる。

【0045】

<データ書き込み(2)>

次に、第1ソース線SL1に接続されるメモリセルユニットMUに対して、データ書き込みを行う。

【0046】

図8に示すように、ブロック選択ゲート線SGD、SGS、第1、第2ソース線SL1、SL2の電位は、データ書き込み(1)と同じである。

【0047】

ビット線BL(BL1、BL2、…)の電位は、データ書き込み(1)と同様に、書き込みデータに応じた電位とする。例えば、書き込みデータが“0”の場合は0Vとし、“1”の場合はVccとする。

【0048】

次いで、非選択ワード線WLの電位、及び第1セル選択ゲート線SG Cell1の電位を、Vpassとする。選択したワード線WLの電位は、Vpassよりも高いVpgmとする。そして、第2セル選択ゲート線SG Cell2の電位は、0Vとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。ビット線BL(BL1、BL2、…)の電位は、データ書き込み(1)と同様に、オンしたメモリセルSTMCを含むメモリセルユニットMUに対して、伝えられる。本例では、第1ソース線SL1に接続されるメモリセルユニットMUに対して、伝えられる。

【0049】

この結果、第1ソース線SL1に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCには、ビット線BL(BL1、BL2、…)の電位に応じて、データ“0”、又はデータ“1”が書き込まれる。

【0050】

以上で、データ書き込みが終了する。この後、例えば、データ読み出しが行われる。

【0051】

図9、及び図10はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図である。

【0052】

<データ読み出し(1)>

まず、第1ソース線SL1、又は第2ソース線SL2のいずれかに接続されるメモリセルユニットMUに対して、データ読み出しを行う。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対してデータ読み出しを行うが、データ読み出しの順番は任意である。

【0053】

まず、ビット線BL(BL1、BL2、…)の電位は、プリチャージ電位とし、第1、第2ソース線SL1、SL2の電位は、0Vとする。

【0054】

この後、図9に示すように、非選択ワード線WLの電位、及び第2セル選択ゲート線SG Cell2の電位を、Vreadとする。選択したワード線WLの電位は、0Vとする。

【0055】

さらに、第1セル選択ゲート線SG Cell1の電位は、0Vとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに含まれたメモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)がオンする。

【0056】

さらに、ドレイン側ブロック選択ゲート線SGDの電位、及びソース側ブロック選択ゲート線SGSの電位を、双方ともVccとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)、及びソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は、全てオンする。

【0057】

この結果、第2ソース線SL2に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCが、データ“0”を記憶しているか、又はデータ“1”を記憶しているかで、ビット線BL(BL1、BL2、…)の電位が維持、又は変化する。例えば、メモリセルトランジスタMCがデータ“0”を記憶している場合、メモリセルトランジスタMCは、本例ではエンハンスメント型となるのでオフする。従って、ビット線BLの電位は、プリチャージ電位を維持する。反対に、メモリセルトランジスタMCがデータ“1”を記憶している場合、メモリセルトランジスタMCは、本例ではデプレッション型となるのでオンする。従って、ビット線BLの電位は、プリチャージ電位から下がる。このビット線BL(BL1、BL2、…)の電位を、センスアンプ(S/A)で読み取ることで、読み出したデータが、“0”であるか“1”であるかが確定される。

【0058】

<データ読み出し(2)>

次に、第1ソース線SL1に接続されるメモリセルユニットMUに対して、データ読み出しを行う。

【0059】

まず、ビット線BL(BL1、BL2、…)の電位は、プリチャージ電位とし、第1、第2ソース線SL1、SL2の電位は、0Vとする。これは、データ読み出し(1)と同じである。

【0060】

この後、図10に示すように、非選択ワード線WLの電位、及び第1セル選択ゲート線SG Cell1の電位を、Vreadとする。選択したワード線WLの電位は、0Vとする。

【0061】

さらに、第2セル選択ゲート線SG Cell2の電位は、0Vとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。本例では、第1ソース線SL1に接続されるメモリセルユニットMUに含まれたメモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)がオンする。

【0062】

さらに、データ読み出し(1)と同様に、ドレイン側ブロック選択ゲート線SGDの電位、及びソース側ブロック選択ゲート線SGSの電位を、双方ともVccとする。

【0063】

この結果、データ読み出し(1)と同様に、第1ソース線SL1に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCが、データ“0”を記憶しているか、又はデータ“1”を記憶しているかで、ビット線BL(BL1、BL2、…)の電位が維持、又は変化する。このビット線BL(BL1、BL2、…)の電位を、センスアンプ(S/A)で読み取ることで、データ読み出し(1)と同様に、読み出したデータが、“0”であるか“1”であるかが確定される。

【0064】

以上で、データ読み出しが終了する。

【0065】

上記一実施形態によれば、実用に適した回路構成を持つ、倍ピッチセルを備えたNAND型フラッシュメモリを備えた半導体集積回路装置が得られる。

【0066】

例えば、特許文献1に記載された倍ピッチセルでは、一実施形態のように、メモリセルトランジスタMCを、選択トランジスタとして利用しない。このため、ブロック選択トランジスタに、ワード線方向に沿って隣接するメモリセルユニットのうち、どちらをビット線に接続するかを決める役割を持たせなければならない。簡単には、ドレイン側選択ゲート線SGDが2本必要であり、いずれか一本をハイレベルにすることによって、ビット線に接続するメモリセルユニットを決める。

【0067】

対して、一実施形態によれば、メモリセルトランジスタMCを、選択トランジスタとして利用するので、ドレイン側選択ゲート線SGDは1本で良い。

【0068】

また、特許文献1のように、ドレイン側選択ゲート線SGDが2本必要となると、メモリセルアレイの加工上、ドレイン側選択トランジスタを、直列に2つ接続しなければならない。さらに、直列接続されたドレイン側選択トランジスタは、交互にデプレッション型及びエンハンスメント型としなければならない。ドレイン側選択トランジスタをデプレッション型とするためには、チャネルイオン注入工程が別途必要である。このため、製造プロセスが増加する。しかも、チャネルイオン注入工程は、フォトリソグラフィ技術を利用するため、合わせ余裕が必要である。つまり、微細化も難しい。

【0069】

対して、一実施形態によれば、メモリセルトランジスタMC(STMC)を、選択トランジスタとして利用する。このため、データ書き込みによって、デプレッション型、及びエンハンスメント型とできる。従って、特許文献1のように、製造プロセスが増加することもない。そして、合わせ余裕もとる必要が無いので、微細化にも有利である。

【0070】

さらに、一実施形態によれば、ビット線コンタクト4Dばかりでなく、ソース線コンタクト4Sについても、素子分離領域2、及び素子領域AAのピッチの2倍のピッチで形成できる。つまり、ソース線コンタクト4Sも、ビット線コンタクト4Dと同様に、加工しやすく、微細化にも適している。

【0071】

さらに、ソース線は、第1ソース線SL1と、第2ソース線SL2との2組を設ける。これら第1、第2ソース線SL1、SL2は、それぞれビット線BLを共有する2つのメモリセルユニットのソースに接続する。選択トランジスタとして利用するメモリセルトランジスタMC(STMC)へのデータ書き込みには、例えば、第1、第2ソース線SL1、SL2の電位を利用すると良い。このデータ書き込み時において、第1、第2ソース線SL1、SL2の電位を異ならせると、選択トランジスタとして利用する2つのメモリセルトランジスタ(例えば、STMC11とSTMC21や、STMC12、STMC22)には、一度のデータ書き込みで異なったデータを書き込むことができる。従って、一実施形態によれば、選択トランジスタとして利用するメモリセルトランジスタへのデータ書き込みも速い。

【0072】

このように、一実施形態によれば、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を得ることができる。

【0073】

以上、この発明を一実施形態により説明したが、この発明の実施形態は、一実施形態が唯一の実施形態ではない。また、その実施にあたっては発明の要旨を逸脱しない範囲で種々に変形することが可能である。

【0074】

また、上記実施形態は種々の段階の発明を含んでおり、一実施形態において開示した複数の構成要件の適宜な組み合わせにより、種々の段階の発明を抽出することが可能である。

【0075】

また、上記実施形態は、この発明をNAND型フラッシュメモリに適用した例に基づき説明したが、この発明はNAND型フラッシュメモリに限られるものではなく、NAND型以外のフラッシュメモリにも適用することができる。さらに、これらフラッシュメモリを内蔵した半導体集積回路装置、例えば、プロセッサ、システムLSI等もまた、この発明の範疇である。

【図面の簡単な説明】

【0076】

【図1】図1はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの等価回路の一例を示す回路図

【図2】図2はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの構造の一例を示す平面図

【図3】図3は図2に示す3−3線に沿う断面図

【図4】図4はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの初期状態の一例を示す図

【図5】図5はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図

【図6】図6はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図

【図7】図7はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図

【図8】図8はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図

【図9】図9はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図

【図10】図10はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図

【符号の説明】

【0077】

1…P型シリコン基板(半導体基板)、2…素子分離領域、3D、3S…N型拡散層(電流通路の一端、他端)、4D…ビット線コンタクト、4S…ソース線コンタクト、MU…メモリセルユニット、STD、STS…ブロック選択トランジスタ(選択トランジスタ)、STMC、MC…メモリセルトランジスタ、BL…ビット線、SL…ソース線

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、電気的に書き換えが可能な不揮発性半導体記憶装置を備えた半導体集積回路装置に関する。

【背景技術】

【0002】

不揮発性半導体記憶装置、特に、NAND型フラッシュメモリの微細化が進んでいる。近時では、最小加工寸法をFとしたとき、面積が“2F×2F=4F2”となるメモリセルが開発されている(非特許文献1)。

【0003】

このメモリセルを集積したメモリセルアレイにおいては、素子領域の配置ピッチが2Fである。故に、ビット線の配置ピッチは2Fとなり、ビット線とブロック選択トランジスタの拡散層とを接続するビット線コンタクトの配置ピッチも2Fとなる。

【0004】

しかしながら、ビット線コンタクトのパターンは、素子領域のパターンや、ビット線のパターンのようにラインパターンではなく、ホールパターンである。ホールパターンは、ラインパターンよりも解像度が弱く、エッチング時の誤差も大きい。このため、ビット線コンタクトをピッチ2Fで配置したメモリセルを形成することは、技術的に極めてタイトである。

【0005】

そこで、ビット線コンタクトを2倍のピッチに緩和したメモリセルアレイが、特許文献1に記載されている。本明細書においては、この種のメモリセルアレイに用いるメモリセルを、倍ピッチセルと呼ぶ。

【非特許文献1】三宅 常之、「16GビットNANDフラッシュへの道、東芝が50nmで4F2の「究極のセル」実現へ」、日経マイクロデバイス2003年8月号、pp57−62

【特許文献1】特開2005−56989

【発明の開示】

【発明が解決しようとする課題】

【0006】

この発明は、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供する。

【課題を解決するための手段】

【0007】

この発明の一態様に係る半導体集積回路装置は、選択トランジスタ間に、直列に接続されたメモリセルトランジスタを含む第1乃至第3メモリセルユニットと、前記第1メモリセルユニットの電流通路の一端、及び前記第2メモリセルユニットの電流通路の一端に共通接続された第1ビット線と、前記第3メモリセルユニットの電流通路の一端に接続された第2ビット線と、前記第1メモリセルユニットの電流通路の他端に接続された第1ソース線と、前記第2メモリセルユニットの電流通路の他端、及び前記第3メモリセルユニットの電流通路の他端に共通接続された第2ソース線とを具備する。

【発明の効果】

【0008】

この発明によれば、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供できる。

【発明を実施するための最良の形態】

【0009】

特許文献1には、倍ピッチセルが開示されている。倍ピッチセルは、ビット線コンタクトを2倍のピッチに緩和でき、典型的なメモリセルに比較して加工しやすい。即ち、微細化に適している。そして、特許文献1は、倍ピッチセルを利用したNAND型フラッシュメモリ基本的な回路構成を記載する。しかしながら、より実用に適した回路構成については記載がない。

【0010】

以下、この発明の一実施形態を、図面を参照して説明する。この説明に際し、全図にわたり、共通する部分には共通する参照符号を付す。この一実施形態は、半導体集積回路装置としてNAND型フラッシュメモリを例示するが、この発明は、NAND型フラッシュメモリに限って適用されるものではなく、NAND型フラッシュメモリ以外のメモリにも適用することができる。

【0011】

図1はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの等価回路の一例を示す回路図、図2はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの構造の一例を示す平面図、図3は図2に示す3−3線に沿う断面図である。

【0012】

図1〜図3に示すように、半導体基板、例えば、P型シリコン基板(又はP型シリコンウェル)1上には、素子分離領域2が形成される。素子分離領域2は、基板1の表面に、素子領域AAを分離する。素子分離領域2の一例は、シャロートレンチアイソレーション(STI)である。素子領域AA、及び素子分離領域2は、基板1上に、ピッチPで配置される。ピッチPの一例は2Fである。“F”は最小加工寸法である。素子領域AA、及び素子分離領域2は、例えば、双方とも最小加工寸法Fで形成される。

【0013】

素子領域AAには、メモリセルユニットMU(MU1、MU2、MU3、…)が配置される。本例のメモリセルユニットMUは、ブロック選択トランジスタSTD(STD1、STD2、STD3、…)、STS(STS1、STS2、STS3、…)間に、直列に接続されたメモリセルトランジスタMC(MC11〜MC3N、…)を含む。

【0014】

ビット線BL(BL1、BL2、BL3、…)は、本例では、例えば、2つの素子領域AAに対して1つ配置される。

【0015】

第1ビット線BL1は第1メモリセルユニットMU1の電流通路の一端、及び第2メモリセルユニットMU2の電流通路の一端に共通接続され、第2ビット線BL2は第3メモリセルユニットの電流通路の一端に接続される。第1メモリセルユニットMU1、第2メモリセルユニットMU2、及び第3メモリセルユニットMU3は、ワード線方向に隣接し、ワード線WL(WL1、WL2、…WLN)を共有する。第1メモリセルユニットMU1〜第3メモリセルユニットMU3の電流通路の一端は、本例ではN型拡散層3Dである。N型拡散層3Dは、ドレイン側ブロック選択トランジスタSTDのドレインである。ビット線BL(BL1、BL2、BL3、…)は、本例では、ビット線コンタクト4Dを介してN型拡散層3Dに接続される。ビット線コンタクト4Dは、基板1上に、ピッチ2Pで配置される。ピッチPの一例は、上述の通り2F(Fは最小加工寸法)である。本例のビット線コンタクト4Dは、層間絶縁膜5に形成されたコンタクト孔6に埋め込まれた導電物である。層間絶縁膜5は、素子分離領域2を有した基板1上に形成される。導電物の一例は、タングステンである。なお、本例では、ビット線BL(BL1、BL2、BL3、…)を、ビット線コンタクト4Dを介してN型拡散層3Dに接続しているが、これに限られるものではない。例えば、ビット線BLを、ビット線コンタクト4Dを使わずに、コンタクト孔6を介してN型拡散層3Dに、直接に接続しても良い。

【0016】

ソース線SL(SL1、SL2)は、本例では2組設けられる。2組の第1、第2ソース線SL1、SL2は、メモリセルユニットMUに対して、互いに異なるソース電位を供給することが可能とされる。

【0017】

第1ソース線SL1は第1メモリセルユニットMU1の電流通路の他端に接続され、第2ソース線SL2は、第2メモリセルユニットMU2の電流通路の他端、及び第3メモリセルユニットMU3の電流通路の他端に共通接続される。第1メモリセルユニットMU1〜第3メモリセルユニットMU3の電流通路の他端は、本例ではN型拡散層3Sである。N型拡散層3Sは、ソース側ブロック選択トランジスタSTSのソースである。第1、第2ソース線SL1、SL2は、本例では、ソース線コンタクト4Sを介してN型拡散層3Sに接続される。ソース線コンタクト4Sは、ビット線コンタクト4Dと同様に、基板1上に、ピッチ2Pで配置される。ピッチPの一例は、上述の通り2F(Fは最小加工寸法)である。本例のソース線コンタクト4Sは、ビット線コンタクト4Dと同様に、層間絶縁膜5に形成されたコンタクト孔6に埋め込まれた導電物である。導電物の一例は、タングステンである。なお、本例では、第1、第2ソース線SL1、SL2を、ソース線コンタクト4Sを介してN型拡散層3Sに接続しているが、これに限られるものではない。例えば、第1、第2ソース線SL1、SL2を、コンタクト孔6を介してN型拡散層3Sに、直接に接続しても良い。

【0018】

本例は、ブロック選択トランジスタSTD、STSの他に、さらに、選択トランジスタを有する。この選択トランジスタにはメモリセルトランジスタが利用される。本例では、行列状に配置されたメモリセルトランジスタMCのうち、メモリセルユニットMUの、ドレイン側ブロック選択トランジスタに隣接するメモリセルトランジスタMC(STMC11、STMC21、STMC31、…)、及びこれらメモリセルトランジスタMC(STMC11、STMC21、STMC31、…)に隣接するメモリセルトランジスタMC(STMC12、STMC22、STMC32、…)を選択トランジスタとして利用する。

【0019】

以下、選択トランジスタとしての利用方法の一例を説明する。

【0020】

図4はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの初期状態の一例を示す図である。

【0021】

図4に示すように、初期状態においては、メモリセルトランジスタMCの全てが、消去状態である。消去状態のメモリセルトランジスタMCは、例えば、デプレッション型とされる。この状態をデータ“1”とする。メモリセルトランジスタMCの全てが、データ“1”であると、メモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…、STMC12、STMC22、STMC32、…)を選択トランジスタとして利用することができない。そこで、本例では、データ消去後、かつ、データ書き込み前に、予備データ書き込みを、メモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…、STMC12、STMC22、STMC32、…)に対して行う。

【0022】

図5、及び図6はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図である。

【0023】

本例の予備データ書き込みは第1、第2ソース線SL1、SL2を利用し、予備データ書き込みのデータは、第1、第2ソース線SL1、SL2から入力する。

【0024】

<予備データ書き込み(1)>

まず、第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)に対して、予備データ書き込みを行う。

【0025】

図5に示すように、ドレイン側ブロック選択ゲート線SGDの電位を0V、ソース側ブロック選択ゲート線SGSの電位をVccとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)は全てオフし、ソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は全てオンする。

【0026】

なお、ビット線BL(BL1、BL2、…)の電位は、例えば、Vccとする。

【0027】

次いで、第1ソース線SL1の電位を0V、第2ソース線SL2の電位をVccとする。

【0028】

次いで、ワード線WL(WL1〜WLN)の電位、及び第2セル選択ゲート線SG Cell2の電位を、Vpassとする。さらに、第1セル選択ゲート線SG Cell1の電位を、Vpassよりも高いVpgmとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)には、第1、第2ソース線SL1、SL2の電位に応じたデータが書き込まれる。

【0029】

本例では、第1ソース線SL1に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC11、STMC41、STMC51、…)には、データ“0”が書き込まれる。メモリセルトランジスタSTMC(STMC11、STMC41、STMC51、…)は、例えば、デプレッション型からエンハンスメント型に変わる。

【0030】

また、第2ソース線SL2に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)は、データ“0”を維持する。メモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)は、デプレッション型のままである。

【0031】

<予備データ書き込み(2)>

次に、第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)に対して、予備データ書き込みを行う。

【0032】

図6に示すように、ブロック選択ゲート線SGD、SGS、ビット線BL(BL1、BL2、…)の電位は、予備データ書き込み(1)と同じである。

【0033】

次いで、第1ソース線SL1の電位を予備データ書き込み(1)とは逆にVcc、第2ソース線SL2の電位も逆に0Vとする。

【0034】

次いで、ワード線WL(WL1〜WLN)の電位、及び第1セル選択ゲート線SG Cell1の電位を、Vpassとする。さらに、第2セル選択ゲート線SG Cell2の電位を、Vpassよりも高いVpgmとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)には、第1、第2ソース線SL1、SL2の電位に応じたデータが書き込まれる。

【0035】

本例では、第2ソース線SL2に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC22、STMC32、STMC62、STMC72、…)には、データ“0”が書き込まれる。メモリセルトランジスタSTMC(STMC22、STMC32、STMC62、STMC72、…)は、例えば、デプレッション型からエンハンスメント型に変わる。

【0036】

また、第1ソース線SL1に接続されるメモリセルユニットMUのメモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)は、データ“0”を維持する。メモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)は、デプレッション型のままである。

【0037】

以上で、予備データ書き込みが終了する。この後、例えば、データ書き込みが行われる。

【0038】

図7、及び図8はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図である。

【0039】

<データ書き込み(1)>

まず、第1ソース線SL1、又は第2ソース線SL2のいずれかに接続されるメモリセルユニットMUに対して、データ書き込みを行う。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対してデータ書き込みを行うが、データ書き込みの順番は任意である。

【0040】

図7に示すように、ドレイン側ブロック選択ゲート線SGDの電位をVcc、ソース側ブロック選択ゲート線SGSの電位を0Vとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)は全てオンし、ソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は全てオフする。

【0041】

ビット線BL(BL1、BL2、…)の電位は、書き込みデータに応じた電位とする。例えば、書き込みデータが“0”の場合は0Vとし、“1”の場合はVccとする。

【0042】

なお、第1、第2ソース線SL1、SL2の電位は、例えば、Vccとする。

【0043】

次いで、非選択ワード線WLの電位、及び第2セル選択ゲート線SG Cell2の電位を、Vpassとする。選択したワード線WLの電位は、Vpassよりも高いVpgmとする。そして、第1セル選択ゲート線SG Cell1の電位は、0Vとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。ビット線BL(BL1、BL2、…)の電位は、オンしたメモリセルSTMCを含むメモリセルユニットMUに対して、伝えられる。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対して、伝えられる。

【0044】

この結果、第2ソース線SL2に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCには、ビット線BL(BL1、BL2、…)の電位に応じて、データ“0”、又はデータ“1”が書き込まれる。

【0045】

<データ書き込み(2)>

次に、第1ソース線SL1に接続されるメモリセルユニットMUに対して、データ書き込みを行う。

【0046】

図8に示すように、ブロック選択ゲート線SGD、SGS、第1、第2ソース線SL1、SL2の電位は、データ書き込み(1)と同じである。

【0047】

ビット線BL(BL1、BL2、…)の電位は、データ書き込み(1)と同様に、書き込みデータに応じた電位とする。例えば、書き込みデータが“0”の場合は0Vとし、“1”の場合はVccとする。

【0048】

次いで、非選択ワード線WLの電位、及び第1セル選択ゲート線SG Cell1の電位を、Vpassとする。選択したワード線WLの電位は、Vpassよりも高いVpgmとする。そして、第2セル選択ゲート線SG Cell2の電位は、0Vとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。ビット線BL(BL1、BL2、…)の電位は、データ書き込み(1)と同様に、オンしたメモリセルSTMCを含むメモリセルユニットMUに対して、伝えられる。本例では、第1ソース線SL1に接続されるメモリセルユニットMUに対して、伝えられる。

【0049】

この結果、第1ソース線SL1に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCには、ビット線BL(BL1、BL2、…)の電位に応じて、データ“0”、又はデータ“1”が書き込まれる。

【0050】

以上で、データ書き込みが終了する。この後、例えば、データ読み出しが行われる。

【0051】

図9、及び図10はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図である。

【0052】

<データ読み出し(1)>

まず、第1ソース線SL1、又は第2ソース線SL2のいずれかに接続されるメモリセルユニットMUに対して、データ読み出しを行う。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに対してデータ読み出しを行うが、データ読み出しの順番は任意である。

【0053】

まず、ビット線BL(BL1、BL2、…)の電位は、プリチャージ電位とし、第1、第2ソース線SL1、SL2の電位は、0Vとする。

【0054】

この後、図9に示すように、非選択ワード線WLの電位、及び第2セル選択ゲート線SG Cell2の電位を、Vreadとする。選択したワード線WLの電位は、0Vとする。

【0055】

さらに、第1セル選択ゲート線SG Cell1の電位は、0Vとする。第1セル選択ゲート線SG Cell1をゲートとするメモリセルトランジスタSTMC(STMC11、STMC21、STMC31、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。本例では、第2ソース線SL2に接続されるメモリセルユニットMUに含まれたメモリセルトランジスタSTMC(STMC21、STMC31、STMC61、STMC71、…)がオンする。

【0056】

さらに、ドレイン側ブロック選択ゲート線SGDの電位、及びソース側ブロック選択ゲート線SGSの電位を、双方ともVccとする。ドレイン側ブロック選択トランジスタSTD(STD1、STD2、STD3、…)、及びソース側ブロック選択トランジスタSTS(STS1、STS2、STS3、…)は、全てオンする。

【0057】

この結果、第2ソース線SL2に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCが、データ“0”を記憶しているか、又はデータ“1”を記憶しているかで、ビット線BL(BL1、BL2、…)の電位が維持、又は変化する。例えば、メモリセルトランジスタMCがデータ“0”を記憶している場合、メモリセルトランジスタMCは、本例ではエンハンスメント型となるのでオフする。従って、ビット線BLの電位は、プリチャージ電位を維持する。反対に、メモリセルトランジスタMCがデータ“1”を記憶している場合、メモリセルトランジスタMCは、本例ではデプレッション型となるのでオンする。従って、ビット線BLの電位は、プリチャージ電位から下がる。このビット線BL(BL1、BL2、…)の電位を、センスアンプ(S/A)で読み取ることで、読み出したデータが、“0”であるか“1”であるかが確定される。

【0058】

<データ読み出し(2)>

次に、第1ソース線SL1に接続されるメモリセルユニットMUに対して、データ読み出しを行う。

【0059】

まず、ビット線BL(BL1、BL2、…)の電位は、プリチャージ電位とし、第1、第2ソース線SL1、SL2の電位は、0Vとする。これは、データ読み出し(1)と同じである。

【0060】

この後、図10に示すように、非選択ワード線WLの電位、及び第1セル選択ゲート線SG Cell1の電位を、Vreadとする。選択したワード線WLの電位は、0Vとする。

【0061】

さらに、第2セル選択ゲート線SG Cell2の電位は、0Vとする。第2セル選択ゲート線SG Cell2をゲートとするメモリセルトランジスタSTMC(STMC12、STMC22、STMC32、…)のうち、エンハンスメント型のものはオフし、デプレション型のものはオンする。本例では、第1ソース線SL1に接続されるメモリセルユニットMUに含まれたメモリセルトランジスタSTMC(STMC12、STMC42、STMC52、…)がオンする。

【0062】

さらに、データ読み出し(1)と同様に、ドレイン側ブロック選択ゲート線SGDの電位、及びソース側ブロック選択ゲート線SGSの電位を、双方ともVccとする。

【0063】

この結果、データ読み出し(1)と同様に、第1ソース線SL1に接続されるメモリセルユニットMUであり、かつ、選択したワード線WLをゲートするメモリセルトランジスタMCが、データ“0”を記憶しているか、又はデータ“1”を記憶しているかで、ビット線BL(BL1、BL2、…)の電位が維持、又は変化する。このビット線BL(BL1、BL2、…)の電位を、センスアンプ(S/A)で読み取ることで、データ読み出し(1)と同様に、読み出したデータが、“0”であるか“1”であるかが確定される。

【0064】

以上で、データ読み出しが終了する。

【0065】

上記一実施形態によれば、実用に適した回路構成を持つ、倍ピッチセルを備えたNAND型フラッシュメモリを備えた半導体集積回路装置が得られる。

【0066】

例えば、特許文献1に記載された倍ピッチセルでは、一実施形態のように、メモリセルトランジスタMCを、選択トランジスタとして利用しない。このため、ブロック選択トランジスタに、ワード線方向に沿って隣接するメモリセルユニットのうち、どちらをビット線に接続するかを決める役割を持たせなければならない。簡単には、ドレイン側選択ゲート線SGDが2本必要であり、いずれか一本をハイレベルにすることによって、ビット線に接続するメモリセルユニットを決める。

【0067】

対して、一実施形態によれば、メモリセルトランジスタMCを、選択トランジスタとして利用するので、ドレイン側選択ゲート線SGDは1本で良い。

【0068】

また、特許文献1のように、ドレイン側選択ゲート線SGDが2本必要となると、メモリセルアレイの加工上、ドレイン側選択トランジスタを、直列に2つ接続しなければならない。さらに、直列接続されたドレイン側選択トランジスタは、交互にデプレッション型及びエンハンスメント型としなければならない。ドレイン側選択トランジスタをデプレッション型とするためには、チャネルイオン注入工程が別途必要である。このため、製造プロセスが増加する。しかも、チャネルイオン注入工程は、フォトリソグラフィ技術を利用するため、合わせ余裕が必要である。つまり、微細化も難しい。

【0069】

対して、一実施形態によれば、メモリセルトランジスタMC(STMC)を、選択トランジスタとして利用する。このため、データ書き込みによって、デプレッション型、及びエンハンスメント型とできる。従って、特許文献1のように、製造プロセスが増加することもない。そして、合わせ余裕もとる必要が無いので、微細化にも有利である。

【0070】

さらに、一実施形態によれば、ビット線コンタクト4Dばかりでなく、ソース線コンタクト4Sについても、素子分離領域2、及び素子領域AAのピッチの2倍のピッチで形成できる。つまり、ソース線コンタクト4Sも、ビット線コンタクト4Dと同様に、加工しやすく、微細化にも適している。

【0071】

さらに、ソース線は、第1ソース線SL1と、第2ソース線SL2との2組を設ける。これら第1、第2ソース線SL1、SL2は、それぞれビット線BLを共有する2つのメモリセルユニットのソースに接続する。選択トランジスタとして利用するメモリセルトランジスタMC(STMC)へのデータ書き込みには、例えば、第1、第2ソース線SL1、SL2の電位を利用すると良い。このデータ書き込み時において、第1、第2ソース線SL1、SL2の電位を異ならせると、選択トランジスタとして利用する2つのメモリセルトランジスタ(例えば、STMC11とSTMC21や、STMC12、STMC22)には、一度のデータ書き込みで異なったデータを書き込むことができる。従って、一実施形態によれば、選択トランジスタとして利用するメモリセルトランジスタへのデータ書き込みも速い。

【0072】

このように、一実施形態によれば、実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を得ることができる。

【0073】

以上、この発明を一実施形態により説明したが、この発明の実施形態は、一実施形態が唯一の実施形態ではない。また、その実施にあたっては発明の要旨を逸脱しない範囲で種々に変形することが可能である。

【0074】

また、上記実施形態は種々の段階の発明を含んでおり、一実施形態において開示した複数の構成要件の適宜な組み合わせにより、種々の段階の発明を抽出することが可能である。

【0075】

また、上記実施形態は、この発明をNAND型フラッシュメモリに適用した例に基づき説明したが、この発明はNAND型フラッシュメモリに限られるものではなく、NAND型以外のフラッシュメモリにも適用することができる。さらに、これらフラッシュメモリを内蔵した半導体集積回路装置、例えば、プロセッサ、システムLSI等もまた、この発明の範疇である。

【図面の簡単な説明】

【0076】

【図1】図1はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの等価回路の一例を示す回路図

【図2】図2はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの構造の一例を示す平面図

【図3】図3は図2に示す3−3線に沿う断面図

【図4】図4はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイの初期状態の一例を示す図

【図5】図5はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図

【図6】図6はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへの予備データ書き込みの一例を示す図

【図7】図7はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図

【図8】図8はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ書き込みの一例を示す図

【図9】図9はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図

【図10】図10はこの発明の一実施形態に係る半導体集積回路装置が有するメモリセルアレイへのデータ読み出しの一例を示す図

【符号の説明】

【0077】

1…P型シリコン基板(半導体基板)、2…素子分離領域、3D、3S…N型拡散層(電流通路の一端、他端)、4D…ビット線コンタクト、4S…ソース線コンタクト、MU…メモリセルユニット、STD、STS…ブロック選択トランジスタ(選択トランジスタ)、STMC、MC…メモリセルトランジスタ、BL…ビット線、SL…ソース線

【特許請求の範囲】

【請求項1】

選択トランジスタ間に、直列に接続されたメモリセルトランジスタを含む第1乃至第3メモリセルユニットと、

前記第1メモリセルユニットの電流通路の一端、及び前記第2メモリセルユニットの電流通路の一端に共通接続された第1ビット線と、

前記第3メモリセルユニットの電流通路の一端に接続された第2ビット線と、

前記第1メモリセルユニットの電流通路の他端に接続された第1ソース線と、

前記第2メモリセルユニットの電流通路の他端、及び前記第3メモリセルユニットの電流通路の他端に共通接続された第2ソース線と

を具備することを特徴とする半導体集積回路装置。

【請求項2】

前記第1〜第3メモリセルユニットの一方の選択トランジスタに隣接する第1〜第3メモリセルトランジスタ、及びこれら第1〜第3メモリセルトランジスタに隣接する第4〜第6メモリセルトランジスタを、選択トランジスタとして利用することを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記第1メモリセルトランジスタをエンハンスメント型とし、

前記第2、第3のメモリセルトランジスタをデプレッション型とし、

前記第4メモリセルトランジスタをデプレッション型とし、

前記第5、第6メモリセルトランジスタをエンハンスメント型とすることを特徴とする請求項2に記載の半導体集積回路装置。

【請求項4】

データ消去後、かつ、データ書き込み前に、予備データ書き込みを、前記第1〜第6メモリセルトランジスタに対して行うことを特徴とする請求項2及び請求項3いずれかに記載の半導体集積回路装置。

【請求項5】

前記予備データ書き込みのデータは、前記第1、第2ソース線から入力することを特徴とする請求項4に記載の半導体集積回路装置。

【請求項1】

選択トランジスタ間に、直列に接続されたメモリセルトランジスタを含む第1乃至第3メモリセルユニットと、

前記第1メモリセルユニットの電流通路の一端、及び前記第2メモリセルユニットの電流通路の一端に共通接続された第1ビット線と、

前記第3メモリセルユニットの電流通路の一端に接続された第2ビット線と、

前記第1メモリセルユニットの電流通路の他端に接続された第1ソース線と、

前記第2メモリセルユニットの電流通路の他端、及び前記第3メモリセルユニットの電流通路の他端に共通接続された第2ソース線と

を具備することを特徴とする半導体集積回路装置。

【請求項2】

前記第1〜第3メモリセルユニットの一方の選択トランジスタに隣接する第1〜第3メモリセルトランジスタ、及びこれら第1〜第3メモリセルトランジスタに隣接する第4〜第6メモリセルトランジスタを、選択トランジスタとして利用することを特徴とする請求項1に記載の半導体集積回路装置。

【請求項3】

前記第1メモリセルトランジスタをエンハンスメント型とし、

前記第2、第3のメモリセルトランジスタをデプレッション型とし、

前記第4メモリセルトランジスタをデプレッション型とし、

前記第5、第6メモリセルトランジスタをエンハンスメント型とすることを特徴とする請求項2に記載の半導体集積回路装置。

【請求項4】

データ消去後、かつ、データ書き込み前に、予備データ書き込みを、前記第1〜第6メモリセルトランジスタに対して行うことを特徴とする請求項2及び請求項3いずれかに記載の半導体集積回路装置。

【請求項5】

前記予備データ書き込みのデータは、前記第1、第2ソース線から入力することを特徴とする請求項4に記載の半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2007−35166(P2007−35166A)

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願番号】特願2005−217513(P2005−217513)

【出願日】平成17年7月27日(2005.7.27)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願日】平成17年7月27日(2005.7.27)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]