半導体集積回路装置

【課題】スタンダードセルを小型化することのできる技術を提供する。

【解決手段】電源電位Vddを供給し、第1方向に沿って形成された第1タップと、電源電位Vssを供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセル3において、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さ(距離L)を[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とする。

【解決手段】電源電位Vddを供給し、第1方向に沿って形成された第1タップと、電源電位Vssを供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセル3において、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さ(距離L)を[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、スタンダードセルを複数配列して構成されるセルアレイを含む機能装置を備えた半導体集積回路装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

従来、半導体集積回路装置のレイアウト設計にあたり、給電用の拡散層を一方向に延在させ、その間に所望の回路を構成するMOSトランジスタを配置することで、それらをセルとして認識している。このようなセルのレイアウトの一例については、例えば特開2006−253375号公報(特許文献1)に記載されている。また、一方向に延在するように形成された給電用の拡散層を、「タップ」と称することもある。

【0003】

また、特開2006−228982号公報(特許文献2)には、回路を形成するための回路用拡散層を有するスタンダードセルを複数配列する半導体集積回路において、隣接するスタンダードセル同士の回路用拡散層が予め定められた拡散層間隔で配置されるとともに位相シフトによって互いに異なる位相で形成される場合に、その隣接する回路用拡散層の近傍において電源電位または接地電位をとるためのタップ用拡散層を非連続的に形成する技術が開示されている。それにより、パターンの解像度を低下させることなく、位相矛盾等の不具合なく比較的容易にパターンを高集積化している。

【特許文献1】特開2006−253375号公報

【特許文献2】特開2006−228982号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

セルの高さ(タップと直交する方向のセルの長さ)は、スタンダードセル上をタップと平行する方向に通過できる配線の本数によって決められている。特に、第2層目以上の配線の配線ピッチ(グリッド、トラック)を基準にして、配線との整合性からセルの高さは決まっている。配線ピッチとは配線の幅と配線の間隔とを足したものであり、配線の整合性が良く、また配線との間で無駄なギャップも生じることがないことから、配線ピッチの整数倍をセルの高さとする概念が用いられている。

【0005】

図10に、配線ピッチの整数倍をセルの高さとするスタンダードセルの要部平面図を示す。このスタンダードセルでは7配線ピッチを例として挙げる。すなわち、上下に配置されたタップ100間を6本の第2層目の配線M2が通過可能であり、片方のタップ100上の第2層目の配線M2を加えて、7本の第2層目の配線M2が通過可能なスタンダードセルとして認識される。

【0006】

しかしながら、この手法では、スタンダードセル内の原始的回路がレイアウトルール上ではもっと小さく形成できるにもかかわらず、配線ピッチの整数倍で規定される領域に原始的回路を配置しなければならない。従って、スタンダードセルが必ずしも最小単位で設計されているとは言えない。すなわち、スタンダードセルに形成される半導体素子自体は、さらに微細化が可能であるのに、配線ピッチでセルの高さを定義しているため、必ずしも最小単位で微細化できているとは言えない。

【0007】

本発明の目的は、スタンダードセルを小型化することのできる技術を提供することにある。

【0008】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0010】

この実施の形態は、第1電位を供給し、第1方向に沿って形成された第1タップと、第2電位を供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1の方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセルとを複数配列して構成されるセルアレイを含む半導体集積回路装置であり、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さを[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とするものである。

【発明の効果】

【0011】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0012】

スタンダードセルを有する半導体集積回路装置を小型化することができる。

【発明を実施するための最良の形態】

【0013】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0014】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0015】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態においては、電界効果トランジスタを代表するMISFET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型MISFETをpMISと略し、nチャネル型MISFETをnMISと略す。

【0016】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0017】

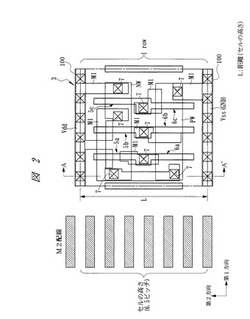

なお、以下の実施の形態においては、一方向に延在するように形成された給電用の拡散層を「タップ」と称する。また、上下のタップ間に複数のMISFETを配置している。これら複数のMISFETは所望の回路の一部を構成する。上述のスタンダードセルとは、所望の回路を構成するために、これら複数のMISFETが第1層目の配線によって結線されたものを指す。例えば図2に示す3入力NAND回路のスタンダードセルは、上下に配置されたタップ100と、各ゲート電極、各ソース領域および各ドレイン領域とを有する6つのMISFET(pMIS5a,5b,5cおよびnMIS6a,6b,6c)と、各MISFETとを結線する第1層目の配線M1によって構成されている。ここで、各MISFETを結線する配線には、必要であれば第2層目の配線M2や、さらに上層の配線層を使用してもよい。なお、セルの高さ方向にスタンダードセルが隣接する場合、タップ100は上下に隣接するセルで共通となり、2つのタップ100が隣接して配置されることはない。

【0018】

また、セルの高さは、タップと直行する方向のセルの長さであり、1つのセルの一端のタップの中心から、そのセルの他端のタップの中心までの距離のことである。言い換えれば、一端のタップに配置されたコンタクトホールの中心から、他端のタップに配置されたコンタクトホールの中心までの距離である。

【0019】

また、以下の実施の形態では、セルの例として、上下に配置されたタップ100間を6本の第2層目の配線M2が通過可能であるスタンダードセルを挙げる。

【0020】

(実施の形態1)

本実施の形態1に用いるスタンダードセルを構成する原始的回路とは、基本論理回路または基本機能回路であって、例えばNAND、NOR、EOR(Exclusive OR:XOR)、ENOR、フリップフロップ(Flip/Flop)、マルチプレクサ(Multiplexer)、インバータ(Inverter)、バッファ(Buffer)などである。

【0021】

本実施の形態1による半導体集積回路装置は、ライブラリに登録されているスタンダードセルを半導体チップ上に配置および配線することによって作られる機能装置、例えば演算論理装置(Arithmetic Logical Unit:ALU)またはマルチプライヤ(Multiplier:MUL)などを備えている。

【0022】

本実施の形態1による半導体集積回路装置の構成の一例を、図1に示す概略図を用いて説明する。

【0023】

半導体集積回路装置1は、ALUまたはMULなどの複数の機能装置2によって構成されている。これら機能装置2は、複数のスタンダードセル3が配置および配線されることによって形成されたセルアレイを含んでいる。スタンダードセル3は1つまたは複数の原始的回路4からなる標準化された回路ブロックであり、セルの高さ(回路ブロックの高さ)を揃えることでスタンダードセル3の配置および配線を容易とすることができる。そのスタンダードセル3の相互間の結線には2層目以上の配線が用いられる。そのスタンダードセル3内の原始的回路4の相互間の結線および原始的回路4内の結線には第1層目の配線が用いられる。

【0024】

図2に、本実施の形態1による1つのスタンダードセル(1row)の要部平面図を示す。また、図3は、図2を簡略化したもので、第1層目の配線M1およびコンタクトホール7を削除したものを示しており、素子分離領域8で区画される活性領域とゲート電極GEのみを示したものである。また、図4に、本実施の形態1による隣接する2つのスタンダードセル(2row)の要部平面図を示す。スタンダードセルを構成する原始的回路として、図2では3入力NAND回路を例示し、図4では2つの3入力NAND回路を例示しているが、これに限定されるものではない。また、図2および図4の左側に示すパターンは、タップ100と平行する方向に通過可能な第2層目の配線の本数を示している。図2に示すように、3入力NAND回路は、半導体基板に形成されたn型ウェル領域NWに3つのpMIS5a,5b,5cが形成され、p型ウェル領域PWに3つのnMIS6a,6b,6cが形成されている。pMIS5aのゲート電極とnMIS6aのゲート電極とは共通の導体膜から形成され、その導体膜に接して形成されたコンタクトホール7を介して第1層目の配線M1と電気的に接続されている。同様に、pMIS5bのゲート電極とnMIS6bのゲート電極とは共通の導体膜から形成されて第1層目の配線M1と電気的に接続され、pMIS5cのゲート電極とnMIS6cのゲート電極とは共通の導体膜から形成されて第1層目の配線M1と電気的に接続されている。

【0025】

図9には、図2のA−A’線に沿った要部断面図が示されている。p型半導体基板p−subには、n型半導体領域NiSOが形成されており、n型半導体領域NiSOによって、各半導体素子が形成されるウェル領域が分離されている。n型半導体領域NiSOには、n型ウェル領域NWとp型ウェル領域PWとが形成されている。

【0026】

p型半導体基板p−subには、素子分離領域8が形成されており、これにより主に半導体素子が形成される活性領域が区画されている。素子分離領域8は、p型半導体基板p−subに形成された溝内に、酸化シリコン膜等の絶縁膜が埋め込まれて形成されている。図2および図3では、活性領域を示す領域として、p型ウェル領域PW、n型ウェル領域NWおよびタップ100を示している。

【0027】

n型ウェル領域NWには、複数のpチャネル型電界効果トランジスタ(pMIS)が形成されており、p型ウェル領域PWには、複数のnチャネル型電界効果トランジスタ(nMIS)が形成されている。pMISおよびnMISは、それぞれp型半導体基板p−sub上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極GEと、p型半導体基板p−sub内に形成されたソース領域およびドレイン領域とを有する。ゲート絶縁膜は、例えば酸化シリコン膜で形成されている。ゲート電極GEは、導電性膜で形成されており、例えば多結晶シリコン膜で形成されている。pMISのゲート電極とnMISのゲート電極とは同一の導電性膜で一体化されて形成されている。p型ウェル領域PW上のゲート電極GEには、燐または砒素などのn型導電性の不純物が導入されており、n型ウェル領域NW上のゲート電極GEには、ボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。

【0028】

pMISのソース領域またはドレイン領域は、n型ウェル領域NWに形成された低濃度p型半導体領域と高濃度p型半導体領域p+とからなる。本実施の形態1では、説明簡略化のため、pMISのゲート長方向の図示を行っておらず、低濃度p型半導体領域は図示していない。図2のA−A’線に沿った断面図である図9において、pMISのドレイン領域であるp型半導体領域p+を示している。また、電源電位Vddのタップ100の表面は、n型ウェル領域NWに形成された高濃度n型半導体領域n+が形成されている。この領域は、nMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ100はpMISが形成されるn型ウェル領域NWに電源電位Vddを供給し、一定の電位に固定するように構成されている。これらの高濃度p型半導体領域p+、高濃度n型半導体領域n+およびpMISのゲート電極GEの表面には、シリサイド膜9が形成されている。このシリサイド膜9は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜10が形成され、層間絶縁膜10内にコンタクトホール7が形成され、コンタクトホール7内にプラグ11が形成される。プラグ11は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0029】

nMISのソース領域またはドレイン領域は、p型ウェル領域PWに形成された低濃度n型半導体領域と高濃度n型半導体領域n+とからなる。本実施の形態1では、説明簡略化のため、nMISのゲート長方向の図示を行っておらず、低濃度n型半導体領域は図示していない。図2のA−A’線に沿った断面図である図9において、nMISのドレイン領域であるn型半導体領域n+を示している。また、電源電位Vssのタップ100の表面は、p型ウェル領域PWに形成された高濃度p型半導体領域p+が形成されている。この領域は、pMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ100はnMISが形成されるp型ウェル領域PWに電源電位Vssを供給し、一定の電位に固定するように構成されている。これらの高濃度n型半導体領域n+、高濃度p型半導体領域p+およびnMISのゲート電極GEの表面には、シリサイド膜9が形成されている。このシリサイド膜9は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜10が形成され、層間絶縁膜10内にコンタクトホール7が形成され、コンタクトホール7内にプラグ11が形成される。プラグ11は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0030】

また、図2では、一部のpMISのソース領域を電源電位Vddのタップ100まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。また、本実施の形態1では、pMISのソース領域の場合を例示しているが、nMISのソース領域に適用しても、同様の効果を得られる。

【0031】

また、nMISの駆動電流を増加させる目的で、図2の上下方向(A−A’方向)において、p型ウェル領域PWの幅をn型ウェル領域NWの幅よりも広くしても良い。

【0032】

また、pMIS5cのソースは第1層目の配線M1を介して、第1方向に沿って形成された電源電位Vdd(給電用の半導体領域(第1タップ))に電気的に接続され、pMIS5a,5bのソースは半導体領域を介して電源電位Vddに電気的に接続されている。pMIS5a,5b,5cのドレインは第1層目の配線M1を介してnMIS6aのドレインに電気的に接続されている。また、nMIS6cのソースは第1層目の配線M1を介して、第1方向に沿って形成された電源電位Vss(給電用の半導体領域(第2タップ))に電気的に接続されている。電源電位Vssは基準電位(接地電位)GNDとすることができる。

【0033】

従って、3入力NAND回路を構成する3つのpMIS5a,5b,5cおよび3つのnMIS6a,6b,6cの相互間の結線には第1層目の配線M1が用いられている。また、第1層目の配線M1は、層間絶縁膜12に形成された溝内に、バリアメタル膜および銅を主体とする導電性膜が埋め込まれて形成されている。バリアメタル膜は、タンタル、窒化タンタルまたはそれらの積層膜からなる。また、第2層目の配線以降についても、同様の構成である。また、本実施の形態1では、配線とプラグとを別々に形成しているが、先にコンタクトホールと配線用の溝を形成し、その後、バリアメタル膜および銅を主体とする導電性膜を埋め込むことで、一体化して形成しても良い。

【0034】

なお、図4に示されるように、セルの高さ方向で隣接する2つのスタンダードセルを結線する場合は、タップ100と交差する方向に延在し、かつ、タップ100上を通過する配線によって行われる。このような配線は、第1層目の配線M1でも良いし、第2層目の配線M2を使用しても良い。すなわち、各スタンダードセルを繋ぐ配線は、スタンダードセルとして所望の回路を構成するための配線とは、別の配線によって行われている。

【0035】

上述のように、本実施の形態1で説明するスタンダードセル3のセルの高さは、第1タップと第2タップとの間(スタンダードセル3上)を通過できる第2層目以上の配線の本数によって決められる。

【0036】

ここで、セルの高さとは、第1方向と直交する第2方向のセルの長さであって、電源電位Vddを供給する給電用の半導体領域(第1タップ)の中心から、電源電位Vssを供給する給電用の半導体領域(第2タップ)の中心までの距離Lを言う。言い換えれば、第1タップに配置されたコンタクトホールの中心から、第2タップに配置されたコンタクトホールの中心までの距離である。

【0037】

しかし、前述した図10に示すスタンダードセルとは異なり、セルの高さは配線ピッチの整数倍ではない。具体的には、セルの高さは(整数+整数分の1)×配線ピッチの高さである。本実施の形態1によるセルの高さは、(整数+0.5)×配線ピッチとしている。ここで整数とは第1タップと第2タップとの間を通過できる第2層目以上の配線の本数であり、特に第2層目の配線M2の本数である。また、このときの配線ピッチとは、第2層目の配線層のピッチである。例えば図2に示すスタンダードセル3では、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数は6本であることから、上記整数は6となり、(6+0.5)×配線ピッチ=6.5配線ピッチがセルの高さとなる。また配線ピッチとは配線の幅と配線の間隔とを足した値である。本実施の形態1で示す配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチを用いている。

【0038】

セルの高さを(整数+0.5)×配線ピッチとした場合は、図4に示すように、第2層目の配線M2の配線ピッチは2セル段(2row)で一旦整数となる。従って、複数のスタンダードセル3を配置および配線して形成されるセルアレイでみると、第2層目の配線M2とセルの高さとの整合性をとることができる。

【0039】

このように、セルの高さを(整数+0.5)×配線ピッチとすることにより、タップ100と直交する方向のセルアレイの面積を縮小することができる。

【0040】

例えば第2層目の配線M2が等間隔で1000本配置され、セルの高さを配線ピッチの整数倍とした従来のレイアウトの場合、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数が6本のときのセルの高さは、前述の図10に示したように、7配線ピッチとなる。その結果、この場合のセル段は142セル段となる。これに対して、例えば第2層目の配線が等間隔で1000本配置され、セルの高さを(整数+0.5)×配線ピッチとした本実施の形態1のレイアウトの場合、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数が6本のときのセルの高さは6.5配線ピッチとなる。その結果、この場合のセル段は153セル段となり、従来のレイアウトに比べてセル段数は約7.7%増加する。これにより、同じレイアウトルールであれば、本実施の形態1のレイアウトは従来のレイアウトに比べてセルアレイの面積を約7%縮小することができる。

【0041】

また、図5に示すように、セルの高さを7配線ピッチ(配線ピッチの整数倍)から6.5配線ピッチ((整数+0.5)×配線ピッチ)へ変更することにより、最小加工寸法を問わず、セル段数が約7.7%増加する。

【0042】

(実施の形態2)

本実施の形態2は、前述の実施の形態1のセルの高さを(整数+0.25)×配線ピッチとした場合を示している。

【0043】

図6に、本実施の形態2による1つのスタンダードセル(1row)の要部平面図を示し、図7に、本実施の形態2による隣接する4つのスタンダードセル(4row)の要部平面図を示す。スタンダードセルを構成する原始的回路として、図6では3入力NAND回路を例示し、図7では4つの3入力NAND回路が例示しているが、これに限定されるものではない。また、前述の実施の形態1と同様に、セルの高さ方向で隣接する2つのスタンダードセルを結線する場合は、タップ100と交差する方向に延在し、かつ、タップ100上を通過する配線によって行われる。このような配線は、第1層目の配線M1でも良いし、第2層目の配線M2を使用しても良い。すなわち、各スタンダードセルを繋ぐ配線は、スタンダードセルとして所望の回路を構成するための配線とは、別の配線によって行われている。

【0044】

前述した実施の形態1では、セルの高さを(整数+0.5)×配線ピッチとしたが、本実施の形態2では、セルの高さを(整数+0.25)×配線ピッチとしている。

【0045】

本実施の形態2で説明するスタンダードセル3のセルの高さは、前述の実施の形態1と同様、第1タップと第2タップとの間(スタンダードセル3上)を通過できる第2層目以上の配線の本数によって決められる。しかし、セルの高さを(配線の整数倍+0.25)×配線ピッチとしている。ここで整数とは第1タップと第2タップとの間を通過できる第2層目以上の配線の本数であり、特に第2層目の配線M2の本数である。例えば図6に示すスタンダードセル3では、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数は6本であることから、上記配線の整数倍は6となり、(6+0.25)×配線ピッチ=6.25配線ピッチがセルの高さとなる。

【0046】

セルの高さを(整数+0.25)×配線ピッチとした場合は、図7に示すように、第2層目の配線M2の配線ピッチは4セル段(4row)で一旦整数となる。従って、複数のスタンダードセル3を配置および配線して形成されるセルアレイでみると、第2層目の配線M2とセルの高さとの整合性をとることができる。

【0047】

このように、セルの高さを(整数+0.25)×配線ピッチとすることにより、タップ100と直交する方向のセルアレイの面積を縮小することができる。

【0048】

図8に、配線ピッチの整数倍((整数+1)×配線ピッチ)で配置されたスタンダードセルのセルの高さ、(整数+0.5)×配線ピッチで配置されたスタンダードセルのセルの高さ、および(整数+0.25)×配線ピッチで配置されたスタンダードセルのセルの高さを比較するためのそれぞれの要部平面図を示す。ここでは、第1タップと第2タップとの間を通過できる第2層目の配線M2を6本としている。

【0049】

4つのスタンダードセルをタップ100と直交する方向に配置した場合、配線ピッチの整数倍で配置されたスタンダードセルのセルの高さは(4×7)配線ピッチ=28配線ピッチとなる。また(整数+0.5)×配線ピッチで配置されたスタンダードセルのセルの高さは(4×6.5)配線ピッチ=26配線ピッチとなる。また(整数+0.25)×配線ピッチで配置されたスタンダードセルのセルの高さは(4×6.25)配線ピッチ=25配線ピッチとなる。

【0050】

従って4つのスタンダードセルで配線ピッチを比較すると、(整数+0.25)×配線ピッチで配置されたスタンダードセルでは3配線ピッチ、(整数+0.5)×配線ピッチで配置されたスタンダードセルでは2配線ピッチ、配線ピッチの整数倍で配置されたスタンダードセルよりもセルの高さを縮小することができる。また、4つのスタンダードセルで面積を比較すると、(整数+0.25)×配線ピッチで配置されたスタンダードセルでは約11%、(整数+0.5)×配線ピッチで配置されたスタンダードセルでは約7%、配線ピッチの整数倍で配置されたスタンダードセルよりもセルの面積を縮小することができる。

【0051】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0052】

例えば、前記実施の形態では、pMISおよびnMISのゲート電極を多結晶シリコン膜で形成する例を示したが、これに限られるものではなく、例えば金属膜で形成してもよい。そのような金属膜としては、Ti、TiN、PtまたはAl等が挙げられる。

【0053】

また、前記実施の形態では、ゲート絶縁膜を酸化シリコン膜で形成した例を示したが、これに限られるものではなく、例えば窒化シリコン膜よりも高い誘電率を有する膜で形成してもよい。そのような高誘電率膜としては、HfO、HfAlO、HfSiAlO、HfSiO、ZrO、ZrAlO、ZrSiO、LaO、LaSiO、TaOまたはTiO等が挙げられる。

【産業上の利用可能性】

【0054】

本発明の半導体集積回路装置は、小型化の進んだスタンダードセルから形成された集積回路を有する半導体集積回路装置に適用することができる。

【図面の簡単な説明】

【0055】

【図1】本発明の実施の形態1による半導体集積回路装置の構成の一例を示す概略図である。

【図2】本発明の実施の形態1による1つのスタンダードセル(1row)の要部平面図である。

【図3】図2における活性領域およびゲート電極のみを示す簡略図である。

【図4】本発明の実施の形態1による隣接する2つのスタンダードセル(2row)の要部平面図である。

【図5】本発明の実施の形態1によるセル段数の増加をまとめた説明図である。

【図6】本発明の実施の形態2による1つのスタンダードセル(1row)の要部平面図である。

【図7】本発明の実施の形態2による隣接する4つのスタンダードセル(4row)の要部平面図である。

【図8】本発明者が検討したスタンダードセルのセルの高さを比較するための説明図である。

【図9】図2のA−A’線に沿った要部断面図である。

【図10】本発明者が検討した配線ピッチの整数倍をセルの高さとするスタンダードセルの要部平面図である。

【符号の説明】

【0056】

1 半導体集積回路装置

2 機能装置

3 スタンダードセル

4 原始的回路

5a,5b,5c pチャネル型MISFET

6a,6b,6c nチャネル型MISFET

7 コンタクトホール

8 素子分離領域

9 シリサイド膜

10 層間絶縁膜

11 プラグ

12 層間絶縁膜

100 タップ

GE ゲート電極

GND 基準電位

L 距離(セルの高さ)

M1 第1層目の配線

M2 第2層目の配線

n+ 高濃度n型半導体領域

NiSO n型半導体領域

NW n型ウェル領域

p−sub p型半導体基板

p+ 高濃度p型半導体領域

PW p型ウェル領域

Vdd 電源電位

Vss 電源電位

【技術分野】

【0001】

本発明は、半導体集積回路装置に関し、特に、スタンダードセルを複数配列して構成されるセルアレイを含む機能装置を備えた半導体集積回路装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

従来、半導体集積回路装置のレイアウト設計にあたり、給電用の拡散層を一方向に延在させ、その間に所望の回路を構成するMOSトランジスタを配置することで、それらをセルとして認識している。このようなセルのレイアウトの一例については、例えば特開2006−253375号公報(特許文献1)に記載されている。また、一方向に延在するように形成された給電用の拡散層を、「タップ」と称することもある。

【0003】

また、特開2006−228982号公報(特許文献2)には、回路を形成するための回路用拡散層を有するスタンダードセルを複数配列する半導体集積回路において、隣接するスタンダードセル同士の回路用拡散層が予め定められた拡散層間隔で配置されるとともに位相シフトによって互いに異なる位相で形成される場合に、その隣接する回路用拡散層の近傍において電源電位または接地電位をとるためのタップ用拡散層を非連続的に形成する技術が開示されている。それにより、パターンの解像度を低下させることなく、位相矛盾等の不具合なく比較的容易にパターンを高集積化している。

【特許文献1】特開2006−253375号公報

【特許文献2】特開2006−228982号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

セルの高さ(タップと直交する方向のセルの長さ)は、スタンダードセル上をタップと平行する方向に通過できる配線の本数によって決められている。特に、第2層目以上の配線の配線ピッチ(グリッド、トラック)を基準にして、配線との整合性からセルの高さは決まっている。配線ピッチとは配線の幅と配線の間隔とを足したものであり、配線の整合性が良く、また配線との間で無駄なギャップも生じることがないことから、配線ピッチの整数倍をセルの高さとする概念が用いられている。

【0005】

図10に、配線ピッチの整数倍をセルの高さとするスタンダードセルの要部平面図を示す。このスタンダードセルでは7配線ピッチを例として挙げる。すなわち、上下に配置されたタップ100間を6本の第2層目の配線M2が通過可能であり、片方のタップ100上の第2層目の配線M2を加えて、7本の第2層目の配線M2が通過可能なスタンダードセルとして認識される。

【0006】

しかしながら、この手法では、スタンダードセル内の原始的回路がレイアウトルール上ではもっと小さく形成できるにもかかわらず、配線ピッチの整数倍で規定される領域に原始的回路を配置しなければならない。従って、スタンダードセルが必ずしも最小単位で設計されているとは言えない。すなわち、スタンダードセルに形成される半導体素子自体は、さらに微細化が可能であるのに、配線ピッチでセルの高さを定義しているため、必ずしも最小単位で微細化できているとは言えない。

【0007】

本発明の目的は、スタンダードセルを小型化することのできる技術を提供することにある。

【0008】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0010】

この実施の形態は、第1電位を供給し、第1方向に沿って形成された第1タップと、第2電位を供給し、第1方向と交差する第2方向に第1タップと対向して配置され、第1の方向に沿って形成された第2タップと、第1タップと第2タップとの間に形成されたスタンダードセルとを複数配列して構成されるセルアレイを含む半導体集積回路装置であり、第2方向における第1タップの中心と第2方向における第2タップの中心との間のセルの高さを[(整数+0.5)×第2層目の配線の配線ピッチ]または[(整数+0.25)×第2層目の配線の配線ピッチ]とするものである。

【発明の効果】

【0011】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0012】

スタンダードセルを有する半導体集積回路装置を小型化することができる。

【発明を実施するための最良の形態】

【0013】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0014】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0015】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態においては、電界効果トランジスタを代表するMISFET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型MISFETをpMISと略し、nチャネル型MISFETをnMISと略す。

【0016】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0017】

なお、以下の実施の形態においては、一方向に延在するように形成された給電用の拡散層を「タップ」と称する。また、上下のタップ間に複数のMISFETを配置している。これら複数のMISFETは所望の回路の一部を構成する。上述のスタンダードセルとは、所望の回路を構成するために、これら複数のMISFETが第1層目の配線によって結線されたものを指す。例えば図2に示す3入力NAND回路のスタンダードセルは、上下に配置されたタップ100と、各ゲート電極、各ソース領域および各ドレイン領域とを有する6つのMISFET(pMIS5a,5b,5cおよびnMIS6a,6b,6c)と、各MISFETとを結線する第1層目の配線M1によって構成されている。ここで、各MISFETを結線する配線には、必要であれば第2層目の配線M2や、さらに上層の配線層を使用してもよい。なお、セルの高さ方向にスタンダードセルが隣接する場合、タップ100は上下に隣接するセルで共通となり、2つのタップ100が隣接して配置されることはない。

【0018】

また、セルの高さは、タップと直行する方向のセルの長さであり、1つのセルの一端のタップの中心から、そのセルの他端のタップの中心までの距離のことである。言い換えれば、一端のタップに配置されたコンタクトホールの中心から、他端のタップに配置されたコンタクトホールの中心までの距離である。

【0019】

また、以下の実施の形態では、セルの例として、上下に配置されたタップ100間を6本の第2層目の配線M2が通過可能であるスタンダードセルを挙げる。

【0020】

(実施の形態1)

本実施の形態1に用いるスタンダードセルを構成する原始的回路とは、基本論理回路または基本機能回路であって、例えばNAND、NOR、EOR(Exclusive OR:XOR)、ENOR、フリップフロップ(Flip/Flop)、マルチプレクサ(Multiplexer)、インバータ(Inverter)、バッファ(Buffer)などである。

【0021】

本実施の形態1による半導体集積回路装置は、ライブラリに登録されているスタンダードセルを半導体チップ上に配置および配線することによって作られる機能装置、例えば演算論理装置(Arithmetic Logical Unit:ALU)またはマルチプライヤ(Multiplier:MUL)などを備えている。

【0022】

本実施の形態1による半導体集積回路装置の構成の一例を、図1に示す概略図を用いて説明する。

【0023】

半導体集積回路装置1は、ALUまたはMULなどの複数の機能装置2によって構成されている。これら機能装置2は、複数のスタンダードセル3が配置および配線されることによって形成されたセルアレイを含んでいる。スタンダードセル3は1つまたは複数の原始的回路4からなる標準化された回路ブロックであり、セルの高さ(回路ブロックの高さ)を揃えることでスタンダードセル3の配置および配線を容易とすることができる。そのスタンダードセル3の相互間の結線には2層目以上の配線が用いられる。そのスタンダードセル3内の原始的回路4の相互間の結線および原始的回路4内の結線には第1層目の配線が用いられる。

【0024】

図2に、本実施の形態1による1つのスタンダードセル(1row)の要部平面図を示す。また、図3は、図2を簡略化したもので、第1層目の配線M1およびコンタクトホール7を削除したものを示しており、素子分離領域8で区画される活性領域とゲート電極GEのみを示したものである。また、図4に、本実施の形態1による隣接する2つのスタンダードセル(2row)の要部平面図を示す。スタンダードセルを構成する原始的回路として、図2では3入力NAND回路を例示し、図4では2つの3入力NAND回路を例示しているが、これに限定されるものではない。また、図2および図4の左側に示すパターンは、タップ100と平行する方向に通過可能な第2層目の配線の本数を示している。図2に示すように、3入力NAND回路は、半導体基板に形成されたn型ウェル領域NWに3つのpMIS5a,5b,5cが形成され、p型ウェル領域PWに3つのnMIS6a,6b,6cが形成されている。pMIS5aのゲート電極とnMIS6aのゲート電極とは共通の導体膜から形成され、その導体膜に接して形成されたコンタクトホール7を介して第1層目の配線M1と電気的に接続されている。同様に、pMIS5bのゲート電極とnMIS6bのゲート電極とは共通の導体膜から形成されて第1層目の配線M1と電気的に接続され、pMIS5cのゲート電極とnMIS6cのゲート電極とは共通の導体膜から形成されて第1層目の配線M1と電気的に接続されている。

【0025】

図9には、図2のA−A’線に沿った要部断面図が示されている。p型半導体基板p−subには、n型半導体領域NiSOが形成されており、n型半導体領域NiSOによって、各半導体素子が形成されるウェル領域が分離されている。n型半導体領域NiSOには、n型ウェル領域NWとp型ウェル領域PWとが形成されている。

【0026】

p型半導体基板p−subには、素子分離領域8が形成されており、これにより主に半導体素子が形成される活性領域が区画されている。素子分離領域8は、p型半導体基板p−subに形成された溝内に、酸化シリコン膜等の絶縁膜が埋め込まれて形成されている。図2および図3では、活性領域を示す領域として、p型ウェル領域PW、n型ウェル領域NWおよびタップ100を示している。

【0027】

n型ウェル領域NWには、複数のpチャネル型電界効果トランジスタ(pMIS)が形成されており、p型ウェル領域PWには、複数のnチャネル型電界効果トランジスタ(nMIS)が形成されている。pMISおよびnMISは、それぞれp型半導体基板p−sub上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極GEと、p型半導体基板p−sub内に形成されたソース領域およびドレイン領域とを有する。ゲート絶縁膜は、例えば酸化シリコン膜で形成されている。ゲート電極GEは、導電性膜で形成されており、例えば多結晶シリコン膜で形成されている。pMISのゲート電極とnMISのゲート電極とは同一の導電性膜で一体化されて形成されている。p型ウェル領域PW上のゲート電極GEには、燐または砒素などのn型導電性の不純物が導入されており、n型ウェル領域NW上のゲート電極GEには、ボロンまたはフッ化ボロンなどのp型導電性の不純物が導入されている。

【0028】

pMISのソース領域またはドレイン領域は、n型ウェル領域NWに形成された低濃度p型半導体領域と高濃度p型半導体領域p+とからなる。本実施の形態1では、説明簡略化のため、pMISのゲート長方向の図示を行っておらず、低濃度p型半導体領域は図示していない。図2のA−A’線に沿った断面図である図9において、pMISのドレイン領域であるp型半導体領域p+を示している。また、電源電位Vddのタップ100の表面は、n型ウェル領域NWに形成された高濃度n型半導体領域n+が形成されている。この領域は、nMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ100はpMISが形成されるn型ウェル領域NWに電源電位Vddを供給し、一定の電位に固定するように構成されている。これらの高濃度p型半導体領域p+、高濃度n型半導体領域n+およびpMISのゲート電極GEの表面には、シリサイド膜9が形成されている。このシリサイド膜9は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜10が形成され、層間絶縁膜10内にコンタクトホール7が形成され、コンタクトホール7内にプラグ11が形成される。プラグ11は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0029】

nMISのソース領域またはドレイン領域は、p型ウェル領域PWに形成された低濃度n型半導体領域と高濃度n型半導体領域n+とからなる。本実施の形態1では、説明簡略化のため、nMISのゲート長方向の図示を行っておらず、低濃度n型半導体領域は図示していない。図2のA−A’線に沿った断面図である図9において、nMISのドレイン領域であるn型半導体領域n+を示している。また、電源電位Vssのタップ100の表面は、p型ウェル領域PWに形成された高濃度p型半導体領域p+が形成されている。この領域は、pMISのソース領域およびドレイン領域と同工程で形成されたものである。タップ100はnMISが形成されるp型ウェル領域PWに電源電位Vssを供給し、一定の電位に固定するように構成されている。これらの高濃度n型半導体領域n+、高濃度p型半導体領域p+およびnMISのゲート電極GEの表面には、シリサイド膜9が形成されている。このシリサイド膜9は、例えばニッケルシリサイド膜、コバルトシリサイド膜またはプラチナシリサイド膜からなる。その後、これらの領域を覆う層間絶縁膜10が形成され、層間絶縁膜10内にコンタクトホール7が形成され、コンタクトホール7内にプラグ11が形成される。プラグ11は、チタン、窒化チタンまたはこれらの積層膜からなる。

【0030】

また、図2では、一部のpMISのソース領域を電源電位Vddのタップ100まで延在している。これにより、配線層を用いずに、シリサイド膜を用いて電源電位Vddを直接ソース領域に接続している。この場合、配線層を用いないので、配線レイアウトの自由度を高めることができる。また、本実施の形態1では、pMISのソース領域の場合を例示しているが、nMISのソース領域に適用しても、同様の効果を得られる。

【0031】

また、nMISの駆動電流を増加させる目的で、図2の上下方向(A−A’方向)において、p型ウェル領域PWの幅をn型ウェル領域NWの幅よりも広くしても良い。

【0032】

また、pMIS5cのソースは第1層目の配線M1を介して、第1方向に沿って形成された電源電位Vdd(給電用の半導体領域(第1タップ))に電気的に接続され、pMIS5a,5bのソースは半導体領域を介して電源電位Vddに電気的に接続されている。pMIS5a,5b,5cのドレインは第1層目の配線M1を介してnMIS6aのドレインに電気的に接続されている。また、nMIS6cのソースは第1層目の配線M1を介して、第1方向に沿って形成された電源電位Vss(給電用の半導体領域(第2タップ))に電気的に接続されている。電源電位Vssは基準電位(接地電位)GNDとすることができる。

【0033】

従って、3入力NAND回路を構成する3つのpMIS5a,5b,5cおよび3つのnMIS6a,6b,6cの相互間の結線には第1層目の配線M1が用いられている。また、第1層目の配線M1は、層間絶縁膜12に形成された溝内に、バリアメタル膜および銅を主体とする導電性膜が埋め込まれて形成されている。バリアメタル膜は、タンタル、窒化タンタルまたはそれらの積層膜からなる。また、第2層目の配線以降についても、同様の構成である。また、本実施の形態1では、配線とプラグとを別々に形成しているが、先にコンタクトホールと配線用の溝を形成し、その後、バリアメタル膜および銅を主体とする導電性膜を埋め込むことで、一体化して形成しても良い。

【0034】

なお、図4に示されるように、セルの高さ方向で隣接する2つのスタンダードセルを結線する場合は、タップ100と交差する方向に延在し、かつ、タップ100上を通過する配線によって行われる。このような配線は、第1層目の配線M1でも良いし、第2層目の配線M2を使用しても良い。すなわち、各スタンダードセルを繋ぐ配線は、スタンダードセルとして所望の回路を構成するための配線とは、別の配線によって行われている。

【0035】

上述のように、本実施の形態1で説明するスタンダードセル3のセルの高さは、第1タップと第2タップとの間(スタンダードセル3上)を通過できる第2層目以上の配線の本数によって決められる。

【0036】

ここで、セルの高さとは、第1方向と直交する第2方向のセルの長さであって、電源電位Vddを供給する給電用の半導体領域(第1タップ)の中心から、電源電位Vssを供給する給電用の半導体領域(第2タップ)の中心までの距離Lを言う。言い換えれば、第1タップに配置されたコンタクトホールの中心から、第2タップに配置されたコンタクトホールの中心までの距離である。

【0037】

しかし、前述した図10に示すスタンダードセルとは異なり、セルの高さは配線ピッチの整数倍ではない。具体的には、セルの高さは(整数+整数分の1)×配線ピッチの高さである。本実施の形態1によるセルの高さは、(整数+0.5)×配線ピッチとしている。ここで整数とは第1タップと第2タップとの間を通過できる第2層目以上の配線の本数であり、特に第2層目の配線M2の本数である。また、このときの配線ピッチとは、第2層目の配線層のピッチである。例えば図2に示すスタンダードセル3では、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数は6本であることから、上記整数は6となり、(6+0.5)×配線ピッチ=6.5配線ピッチがセルの高さとなる。また配線ピッチとは配線の幅と配線の間隔とを足した値である。本実施の形態1で示す配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチを用いている。

【0038】

セルの高さを(整数+0.5)×配線ピッチとした場合は、図4に示すように、第2層目の配線M2の配線ピッチは2セル段(2row)で一旦整数となる。従って、複数のスタンダードセル3を配置および配線して形成されるセルアレイでみると、第2層目の配線M2とセルの高さとの整合性をとることができる。

【0039】

このように、セルの高さを(整数+0.5)×配線ピッチとすることにより、タップ100と直交する方向のセルアレイの面積を縮小することができる。

【0040】

例えば第2層目の配線M2が等間隔で1000本配置され、セルの高さを配線ピッチの整数倍とした従来のレイアウトの場合、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数が6本のときのセルの高さは、前述の図10に示したように、7配線ピッチとなる。その結果、この場合のセル段は142セル段となる。これに対して、例えば第2層目の配線が等間隔で1000本配置され、セルの高さを(整数+0.5)×配線ピッチとした本実施の形態1のレイアウトの場合、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数が6本のときのセルの高さは6.5配線ピッチとなる。その結果、この場合のセル段は153セル段となり、従来のレイアウトに比べてセル段数は約7.7%増加する。これにより、同じレイアウトルールであれば、本実施の形態1のレイアウトは従来のレイアウトに比べてセルアレイの面積を約7%縮小することができる。

【0041】

また、図5に示すように、セルの高さを7配線ピッチ(配線ピッチの整数倍)から6.5配線ピッチ((整数+0.5)×配線ピッチ)へ変更することにより、最小加工寸法を問わず、セル段数が約7.7%増加する。

【0042】

(実施の形態2)

本実施の形態2は、前述の実施の形態1のセルの高さを(整数+0.25)×配線ピッチとした場合を示している。

【0043】

図6に、本実施の形態2による1つのスタンダードセル(1row)の要部平面図を示し、図7に、本実施の形態2による隣接する4つのスタンダードセル(4row)の要部平面図を示す。スタンダードセルを構成する原始的回路として、図6では3入力NAND回路を例示し、図7では4つの3入力NAND回路が例示しているが、これに限定されるものではない。また、前述の実施の形態1と同様に、セルの高さ方向で隣接する2つのスタンダードセルを結線する場合は、タップ100と交差する方向に延在し、かつ、タップ100上を通過する配線によって行われる。このような配線は、第1層目の配線M1でも良いし、第2層目の配線M2を使用しても良い。すなわち、各スタンダードセルを繋ぐ配線は、スタンダードセルとして所望の回路を構成するための配線とは、別の配線によって行われている。

【0044】

前述した実施の形態1では、セルの高さを(整数+0.5)×配線ピッチとしたが、本実施の形態2では、セルの高さを(整数+0.25)×配線ピッチとしている。

【0045】

本実施の形態2で説明するスタンダードセル3のセルの高さは、前述の実施の形態1と同様、第1タップと第2タップとの間(スタンダードセル3上)を通過できる第2層目以上の配線の本数によって決められる。しかし、セルの高さを(配線の整数倍+0.25)×配線ピッチとしている。ここで整数とは第1タップと第2タップとの間を通過できる第2層目以上の配線の本数であり、特に第2層目の配線M2の本数である。例えば図6に示すスタンダードセル3では、第1タップと第2タップとの間を通過できる第2層目の配線M2の本数は6本であることから、上記配線の整数倍は6となり、(6+0.25)×配線ピッチ=6.25配線ピッチがセルの高さとなる。

【0046】

セルの高さを(整数+0.25)×配線ピッチとした場合は、図7に示すように、第2層目の配線M2の配線ピッチは4セル段(4row)で一旦整数となる。従って、複数のスタンダードセル3を配置および配線して形成されるセルアレイでみると、第2層目の配線M2とセルの高さとの整合性をとることができる。

【0047】

このように、セルの高さを(整数+0.25)×配線ピッチとすることにより、タップ100と直交する方向のセルアレイの面積を縮小することができる。

【0048】

図8に、配線ピッチの整数倍((整数+1)×配線ピッチ)で配置されたスタンダードセルのセルの高さ、(整数+0.5)×配線ピッチで配置されたスタンダードセルのセルの高さ、および(整数+0.25)×配線ピッチで配置されたスタンダードセルのセルの高さを比較するためのそれぞれの要部平面図を示す。ここでは、第1タップと第2タップとの間を通過できる第2層目の配線M2を6本としている。

【0049】

4つのスタンダードセルをタップ100と直交する方向に配置した場合、配線ピッチの整数倍で配置されたスタンダードセルのセルの高さは(4×7)配線ピッチ=28配線ピッチとなる。また(整数+0.5)×配線ピッチで配置されたスタンダードセルのセルの高さは(4×6.5)配線ピッチ=26配線ピッチとなる。また(整数+0.25)×配線ピッチで配置されたスタンダードセルのセルの高さは(4×6.25)配線ピッチ=25配線ピッチとなる。

【0050】

従って4つのスタンダードセルで配線ピッチを比較すると、(整数+0.25)×配線ピッチで配置されたスタンダードセルでは3配線ピッチ、(整数+0.5)×配線ピッチで配置されたスタンダードセルでは2配線ピッチ、配線ピッチの整数倍で配置されたスタンダードセルよりもセルの高さを縮小することができる。また、4つのスタンダードセルで面積を比較すると、(整数+0.25)×配線ピッチで配置されたスタンダードセルでは約11%、(整数+0.5)×配線ピッチで配置されたスタンダードセルでは約7%、配線ピッチの整数倍で配置されたスタンダードセルよりもセルの面積を縮小することができる。

【0051】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0052】

例えば、前記実施の形態では、pMISおよびnMISのゲート電極を多結晶シリコン膜で形成する例を示したが、これに限られるものではなく、例えば金属膜で形成してもよい。そのような金属膜としては、Ti、TiN、PtまたはAl等が挙げられる。

【0053】

また、前記実施の形態では、ゲート絶縁膜を酸化シリコン膜で形成した例を示したが、これに限られるものではなく、例えば窒化シリコン膜よりも高い誘電率を有する膜で形成してもよい。そのような高誘電率膜としては、HfO、HfAlO、HfSiAlO、HfSiO、ZrO、ZrAlO、ZrSiO、LaO、LaSiO、TaOまたはTiO等が挙げられる。

【産業上の利用可能性】

【0054】

本発明の半導体集積回路装置は、小型化の進んだスタンダードセルから形成された集積回路を有する半導体集積回路装置に適用することができる。

【図面の簡単な説明】

【0055】

【図1】本発明の実施の形態1による半導体集積回路装置の構成の一例を示す概略図である。

【図2】本発明の実施の形態1による1つのスタンダードセル(1row)の要部平面図である。

【図3】図2における活性領域およびゲート電極のみを示す簡略図である。

【図4】本発明の実施の形態1による隣接する2つのスタンダードセル(2row)の要部平面図である。

【図5】本発明の実施の形態1によるセル段数の増加をまとめた説明図である。

【図6】本発明の実施の形態2による1つのスタンダードセル(1row)の要部平面図である。

【図7】本発明の実施の形態2による隣接する4つのスタンダードセル(4row)の要部平面図である。

【図8】本発明者が検討したスタンダードセルのセルの高さを比較するための説明図である。

【図9】図2のA−A’線に沿った要部断面図である。

【図10】本発明者が検討した配線ピッチの整数倍をセルの高さとするスタンダードセルの要部平面図である。

【符号の説明】

【0056】

1 半導体集積回路装置

2 機能装置

3 スタンダードセル

4 原始的回路

5a,5b,5c pチャネル型MISFET

6a,6b,6c nチャネル型MISFET

7 コンタクトホール

8 素子分離領域

9 シリサイド膜

10 層間絶縁膜

11 プラグ

12 層間絶縁膜

100 タップ

GE ゲート電極

GND 基準電位

L 距離(セルの高さ)

M1 第1層目の配線

M2 第2層目の配線

n+ 高濃度n型半導体領域

NiSO n型半導体領域

NW n型ウェル領域

p−sub p型半導体基板

p+ 高濃度p型半導体領域

PW p型ウェル領域

Vdd 電源電位

Vss 電源電位

【特許請求の範囲】

【請求項1】

第1電位を供給し、第1方向に沿って形成された第1タップと、

前記第1電位と異なる電位である第2電位を供給し、前記第1方向と交差する第2方向に前記第1タップと対向して配置され、前記第1方向に沿って形成された第2タップと、

前記第2方向における前記第1タップの中心と、前記第2方向における前記第2タップの中心との間に形成されたスタンダードセルとを複数配列して構成されるセルアレイと、

前記第1タップ、前記第2タップおよび前記セルアレイ上に形成された複数層の配線とを含む半導体集積回路装置であって、

前記第1タップと前記第2タップとの間のセルの高さを[(整数+0.5)×前記複数層の配線のうち第2層目の配線の配線ピッチ]とすることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、前記整数は、前記第1タップと前記第2タップとの間を通過できる前記第1方向に沿って形成された第2層目以上の配線の本数であることを特徴とする半導体集積回路装置。

【請求項3】

請求項1記載の半導体集積回路装置において、前記第1電位は電源電位、前記第2電位は接地電位であることを特徴とする半導体集積回路装置。

【請求項4】

請求項1記載の半導体集積回路装置において、前記配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチであることを特徴とする半導体集積回路装置。

【請求項5】

請求項1記載の半導体集積回路装置において、前記スタンダードセル内は前記複数層の配線のうち第1層目の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1記載の半導体集積回路装置において、前記セルアレイは、前記スタンダードセルを複数有し、

前記複数のスタンダードセルの相互間は第2層目以上の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項7】

第1電位を供給し、第1方向に沿って形成された第1タップと、

前記第1電位と異なる電位である第2電位を供給し、前記第1方向と交差する第2方向に前記第1タップと対向して配置され、前記第1方向に沿って形成された第2タップと、

前記第2方向における前記第1タップの中心と、前記第2方向における前記第2タップの中心との間に形成されたスタンダードセルとを複数配列して構成されるセルアレイと、

前記第1タップ、前記第2タップおよび前記セルアレイ上に形成された複数層の配線とを含む半導体集積回路装置であって、

前記第1タップと前記第2タップとの間のセルの高さを[(整数+0.25)×前記複数層の配線のうち第2層目の配線の配線ピッチ]とすることを特徴とする半導体集積回路装置。

【請求項8】

請求項7記載の半導体集積回路装置において、前記整数は、前記第1タップと前記第2タップとの間を通過できる前記第1方向に沿って形成された第2層目以上の配線の本数であることを特徴とする半導体集積回路装置。

【請求項9】

請求項7記載の半導体集積回路装置において、前記第1電位は電源電位、前記第2電位は接地電位であることを特徴とする半導体集積回路装置。

【請求項10】

請求項7記載の半導体集積回路装置において、前記配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチであることを特徴とする半導体集積回路装置。

【請求項11】

請求項7記載の半導体集積回路装置において、前記スタンダードセル内は前記複数層の配線のうち第1層目の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項12】

請求項7記載の半導体集積回路装置において、前記セルアレイは、前記スタンダードセルを複数有し、

前記複数のスタンダードセルの相互間は第2層目以上の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項1】

第1電位を供給し、第1方向に沿って形成された第1タップと、

前記第1電位と異なる電位である第2電位を供給し、前記第1方向と交差する第2方向に前記第1タップと対向して配置され、前記第1方向に沿って形成された第2タップと、

前記第2方向における前記第1タップの中心と、前記第2方向における前記第2タップの中心との間に形成されたスタンダードセルとを複数配列して構成されるセルアレイと、

前記第1タップ、前記第2タップおよび前記セルアレイ上に形成された複数層の配線とを含む半導体集積回路装置であって、

前記第1タップと前記第2タップとの間のセルの高さを[(整数+0.5)×前記複数層の配線のうち第2層目の配線の配線ピッチ]とすることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、前記整数は、前記第1タップと前記第2タップとの間を通過できる前記第1方向に沿って形成された第2層目以上の配線の本数であることを特徴とする半導体集積回路装置。

【請求項3】

請求項1記載の半導体集積回路装置において、前記第1電位は電源電位、前記第2電位は接地電位であることを特徴とする半導体集積回路装置。

【請求項4】

請求項1記載の半導体集積回路装置において、前記配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチであることを特徴とする半導体集積回路装置。

【請求項5】

請求項1記載の半導体集積回路装置において、前記スタンダードセル内は前記複数層の配線のうち第1層目の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項6】

請求項1記載の半導体集積回路装置において、前記セルアレイは、前記スタンダードセルを複数有し、

前記複数のスタンダードセルの相互間は第2層目以上の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項7】

第1電位を供給し、第1方向に沿って形成された第1タップと、

前記第1電位と異なる電位である第2電位を供給し、前記第1方向と交差する第2方向に前記第1タップと対向して配置され、前記第1方向に沿って形成された第2タップと、

前記第2方向における前記第1タップの中心と、前記第2方向における前記第2タップの中心との間に形成されたスタンダードセルとを複数配列して構成されるセルアレイと、

前記第1タップ、前記第2タップおよび前記セルアレイ上に形成された複数層の配線とを含む半導体集積回路装置であって、

前記第1タップと前記第2タップとの間のセルの高さを[(整数+0.25)×前記複数層の配線のうち第2層目の配線の配線ピッチ]とすることを特徴とする半導体集積回路装置。

【請求項8】

請求項7記載の半導体集積回路装置において、前記整数は、前記第1タップと前記第2タップとの間を通過できる前記第1方向に沿って形成された第2層目以上の配線の本数であることを特徴とする半導体集積回路装置。

【請求項9】

請求項7記載の半導体集積回路装置において、前記第1電位は電源電位、前記第2電位は接地電位であることを特徴とする半導体集積回路装置。

【請求項10】

請求項7記載の半導体集積回路装置において、前記配線ピッチは、最小加工寸法で形成された配線の幅と最小加工寸法で形成された配線の間隔とを足した最小配線ピッチであることを特徴とする半導体集積回路装置。

【請求項11】

請求項7記載の半導体集積回路装置において、前記スタンダードセル内は前記複数層の配線のうち第1層目の配線により結線されていることを特徴とする半導体集積回路装置。

【請求項12】

請求項7記載の半導体集積回路装置において、前記セルアレイは、前記スタンダードセルを複数有し、

前記複数のスタンダードセルの相互間は第2層目以上の配線により結線されていることを特徴とする半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−141187(P2010−141187A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−316965(P2008−316965)

【出願日】平成20年12月12日(2008.12.12)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月12日(2008.12.12)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]