半導体集積回路装置

【課題】PAD on I/Oセル構造において、パッド引き出し部のレイアウトをI/O部の略中心に配置し、半導体チップのレイアウト面積を削減する。

【解決手段】I/O部5において、トランジスタ8は、半導体チップの周辺部に最も近い位置にレイアウトされている。このトランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。これにより、パッド2からトランジスタ9のドレインまでを同じノードとすることができるので、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

【解決手段】I/O部5において、トランジスタ8は、半導体チップの周辺部に最も近い位置にレイアウトされている。このトランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。これにより、パッド2からトランジスタ9のドレインまでを同じノードとすることができるので、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置におけるチップ面関の削減技術に関し、特に、PAD on I/O(Input/Output)セル構造におけるレイアウト面積の削減に有効な技術に関する。

【背景技術】

【0002】

近年、半導体集積回路装置の低コスト化、および小型化などの要求から、半導体チップのサイズを縮小するコスト削減が進んでいる。チップサイズを小さくするには、搭載する各部品のレイアウト面積削減が必要となっている。

【0003】

そこで、レイアウト面積削減技術の1つとして、たとえば、ボンディングワイヤなどが接続されるパッドを、外部とのインタフェースであるI/Oセルと重ねる、いわゆるPAD on I/Oセルという構造が知られている。

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところが、上記のようなPAD on I/Oセル技術では、次のような問題点があることが本発明者により見い出された。

【0005】

I/Oセルにおける出力バッファ部は、たとえば、PチャネルMOSのトランジスタとNチャネルMOSのトランジスタとから構成される出力バッファ、ESD(ElectroStatic Discharge)保護用となる第1、および第2のダイオードと第1、および第2の抵抗、およびESD保護回路から構成されている。

【0006】

ESD保護用となる第1、および第2のダイオードは、電源電圧と基準電位との間に直列接続されている。PチャネルMOSのトランジスタの一方の接続部には、電源電圧が接続されており、該トランジスタの他方の接続部には、第1の抵抗の一方の接続部が接続されている。

【0007】

この第1の抵抗の他方の接続部には、第2の抵抗の一方の接続部が接続されており、該第2の抵抗の他方の接続部には、NチャネルMOSのトランジスタの一方の接続部が接続されている。

【0008】

NチャネルMOSのトランジスタの他方の接続部には、基準電位が接続されている。ESD保護回路は、電源電圧と基準電位との間に接続されており、第1のダイオードと第2のダイオード、および第1の抵抗と第2の抵抗との接続部には、パッドが接続されている。

【0009】

パッドは、ボンディングワイヤによるボンディング時の制約などから、小型化することが難しく、チップ面積の削減の効果を最大限にするためには、パッドとI/Oセルとの重なる部分を最大にするのが望ましい。

【0010】

しかし、上記した回路構成では、パッドが第1、および第2の抵抗の接続部と接続されるために、パッドと接続される引き出し部が、これら2つの抵抗の間にしか配置することができず、その結果、パッドがI/Oセルからはみ出してレイアウトされてしまい、チップ面積削減の効果が小さくなってしまうという問題がある。

【0011】

また、近年のプロセスの微細化に伴い、配線抵抗が高抵抗となっており、ESD保護回路までの配線抵抗も高くなっている。そのために、ESD保護回路の放電特性が低下し、該ESD保護回路から遠くに配置されているNチャネルMOSのトランジスタなどを介してESDサージが基準電位へと放電し、素子破壊を招いてしまう恐れがある。

【0012】

さらに、配線抵抗が高くなった分、ESD保護回路の個数を増やして素子を保護することも考えられるが、その場合、チップ面積が増大してしまうという問題がある。

【0013】

本発明の目的は、PAD on I/O(Input/Output)セル構造において、パッド引き出し部のレイアウトをI/O部の略中心に配置することにより、半導体チップのレイアウト面積を削減することのできる技術を提供することにある。

【0014】

本発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0016】

本発明は、半導体チップを備え、該半導体チップは、半導体チップの辺に沿って配置された複数のI/Oパッドと、半導体チップの配置され、任意のI/Oパッドと接続される複数のI/O部とを有し、該I/O部は、出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、出力バッファ、および入力バッファを制御するロジック部とを含み、I/O部は、ロジック部、Nチャネルトランジスタ、およびPチャネルトランジスタの順に半導体チップの辺に向かってレイアウトされ、ロジック部とNチャネルトランジスタとの間にI/Oパッドと接続されるパッド引き出し部が形成されているものである。

【0017】

また、本発明は、前記Nチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0018】

さらに、本発明は、前記出力バッファ部が、ESD保護用の第1、および第2のダイオードを備え、第1、および第2のダイオードは、NチャネルトランジスタとPチャネルトランジスタとの間にレイアウトされているものである。

【0019】

また、本発明は、前記出力バッファ部が、ESD保護用の抵抗を備え、前記抵抗は、第1、および第2のダイオードとPチャネルトランジスタとの間にレイアウトされているものである。

【0020】

さらに、本発明は、前記Pチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0021】

また、本願のその他の発明の概要を簡単に示す。

【0022】

本発明は、半導体チップを備え、該半導体チップは、半導体チップの辺に沿って配置された複数のI/Oパッドと、該半導体チップに配置され、任意のI/Oパッドと接続される複数のI/O部とを有し、該I/O部は、出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、外部からの信号が入力される際のインタフェースとなる入力バッファ部を含み、出力バッファ、および入力バッファを制御するロジック部とよりなり、I/O部は、ロジック部、Pチャネルトランジスタ、およびNチャネルトランジスタの順に直線状にレイアウトされ、ロジック部とPチャネルトランジスタとの間にI/Oパッドと接続されるパッド引き出し部が形成されているものである。

【0023】

また、本発明は、前記Nチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0024】

さらに、本発明は、前記出力バッファ部が、ESD保護用の第1、および第2のダイオードを備え、前記第1、および前記第2のダイオードは、NチャネルトランジスタとPチャネルトランジスタとの間にレイアウトされているものである。

【0025】

また、本発明は、前記出力バッファ部が、ESD保護用の抵抗を備え、前記抵抗は、第1、および第2のダイオードとPチャネルトランジスタとの間にレイアウトされているものである。

【0026】

さらに、本発明は、前記Pチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【発明の効果】

【0027】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0028】

(1)出力バッファ部における保護回路の素子構成を少なくすることができる。

【0029】

(2)I/O部からはみ出すパッドの面積を大幅に削減することが可能となり、半導体チップのチップ面積を小さくすることができる。

【0030】

(3)上記(1)、(2)により、半導体集積回路装置の小型化、および低コスト化を実現することができる。

【発明を実施するための最良の形態】

【0031】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0032】

(実施の形態1)

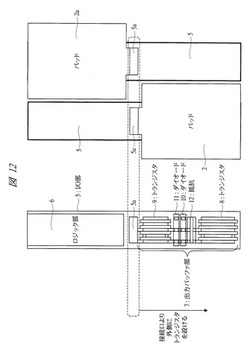

図1は、本発明の実施の形態1による半導体チップのレイアウトイメージを示す説明図、図2は、図1の半導体チップのパッドとI/O領域との一部を拡大した説明図、図3は、図1の半導体チップに設けられたI/O部の一例を示すレイアウト図、図4は、図3のI/O部に設けられた出力バッファ部の構成例を示す回路図、図5は、図3のI/O部の上方に配線層に形成されている周回電源配線のレイアウト図、図6は、図3のI/O部に接続されるパッドのレイアウト図、図7は、図3のI/O部の断面を示した説明図、図8は、図3の出力バッファ部に設けられたトランジスタの平面、および断面を示す説明図、図9は、本発明者が検討した一般的なI/O部の回路図、図10は、図9のI/O部における出力バッファ部のレイアウト図、図11は、本実施の形態1によるI/O部と本発明者が検討した一般的なI/O部とのレイアウト比較図、図12は、本実施の形態1によるI/O部とパッドとのレイアウト関係を示す説明図である。

【0033】

本実施の形態1において、半導体集積回路装置に設けられる半導体チップ1は、図1に示すように、4つの周辺部に、たとえば、ボンディングワイヤなどが接続される複数のパッド2が直線状にそれぞれ配置されている。

【0034】

I/Oパッドとなるパッド2の内側(半導体チップ1の中心側)には、同じくI/Oパッドとなる複数のパッド2aが直線状にそれぞれ配置されており、これらパッド2、ならびにパッド2aは、2列で千鳥足状にレイアウトされている。

【0035】

また、半導体チップ1は、パッド2,2aの下方に、外部とのインタフェースであるI/O領域3がレイアウトされた、いわゆるPAD on I/O部構造となっている。そして、半導体チップ1の中央には、トランジスタなどの半導体素子によるロジックが形成されたコア領域4が位置している。

【0036】

図2は、PAD on I/O部構造によるパッド2,2aとI/O領域3との一部(図1の点線で示す領域)を拡大した説明図である。

【0037】

I/O領域3は、複数のI/O部5が半導体チップ1の辺方向に一列にレイアウトされており、それらの上方に、2列で千鳥足状のパッド2,2aがレイアウトされている。I/O部5、およびパッド2、2aは、それぞれ長方形状からなり、パッド2,2aの長辺は、たとえば、I/O部5の長辺の約半分程度の長さにそれぞれなっている。

【0038】

各々のI/O部5の一方の短辺側には、パッド引き出し部5aが形成されており、このパッド引き出し部5aを介してI/O部5と対応するパッド2(またはパッド2a)の中央部とがそれぞれ接続されている。

【0039】

図3は、I/O部5の一例を示すレイアウト図であり、図4は、図3のI/O部5に設けられた出力バッファ部7の構成例を示す回路図である。

【0040】

I/O部5は、図3に示すように、ロジック部6、および出力バッファ部7から構成されている。ロジック部6は、たとえば、ESD保護回路6a(図4に示す)、入力用バッファとなる入力バッファ部、電圧レベルを変換するレベルシフタ、ならびに出力バッファ部7に駆動信号を出力するインバータなどから構成されている。

【0041】

また、出力バッファ部7は、図4に示すように、出力バッファ用のトランジスタ8,9、ESD保護用のダイオード10,11、および同じくESD保護用の抵抗12から構成されている。トランジスタ8は、たとえば、PチャネルMOSからなり、トランジスタ9は、NチャネルMOSからなる。

【0042】

ダイオード10,11は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。トランジスタ8の一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ8の他方の接続部には、抵抗12の一方の接続部が接続されている。

【0043】

抵抗12の他方の接続部には、トランジスタ9の一方の接続部が接続されており、該トランジスタ9の他方の接続部には、基準電位VSSQが接続されている。また、第1のダイオードであるダイオード10と第2のダイオードであるダイオード11との接続部、および抵抗12の他方の接続部とトランジスタ9の一方の接続部とが接続された接続部が、出力バッファ部7の出力部となり、パッド2(またはパッド2a)が接続される構成となっている。

【0044】

そして、I/O部5において、図3に示すように、トランジスタ8は、半導体チップ1の周辺部に最も近い位置にレイアウトされている。そして、トランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。

【0045】

ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。

【0046】

図5は、図3のI/O部5の上方に形成されている周回電源配線のレイアウト図である。

【0047】

周回電源配線は、図5の上方から下方にかけて、コア電源電圧用周回配線13、コア基準電位用周回配線14、I/O用電源電圧周回配線15、およびI/O用基準電位周回配線16が、ロジック部6の上方に形成されている。そして、パッド引き出し部5aを挟んで、I/O用基準電位周回配線17、ならびにI/O用電源電圧周回配線18が、出力バッファ部7の上方に形成されている。

【0048】

コア電源電圧用周回配線13は、コア領域4に電源電圧を供給し、コア基準電位用周回配線14は、コア領域4に基準電位を供給する。I/O用電源電圧周回配線15,18は、I/O部5に電源電圧VCCQを供給し、I/O用基準電位周回配線16,17は、基準電位VSSQを供給する。

【0049】

図6は、図3のI/O部5に接続されるパッド2のレイアウト図である。

【0050】

このパッド2は、千鳥足状に配列されたパッド2のうち、外側(半導体チップ1の周辺部側)のパッド2を示しており、該パッド2は、半導体チップ1の周辺部側に位置するI/O部5の短辺側からはみ出ない程度にレイアウトされている。

【0051】

図7は、図3のI/O部5の断面を示した説明図である。

【0052】

最下部の素子形成層には、図7の上方から下方にかけて、ロジック部6、および出力バッファ部7のトランジスタ9、ダイオード11、ダイオード10、抵抗12、ならびにトランジスタ8がそれぞれ形成されている。

【0053】

そして、素子形成層の上方に位置する配線層には、図7の左側から右側にかけて、コア電源電圧用周回配線13、コア基準電位用周回配線14、I/O用電源電圧周回配線15、I/O用基準電位周回配線16、I/O用基準電位周回配線17、ならびにI/O用電源電圧周回配線18がそれぞれ形成されている。

【0054】

そして、パッド形成層には、パッド引き出し部5a、およびパッド2がそれぞれ形成されている。これらパッド引き出し部5a、およびパッド2は、素子形成層に形成された出力バッファ部7の上方に位置するように形成されている。

【0055】

ここで、トランジスタ9(図4の点線丸印に示す)は、該トランジスタ9のドレインが高抵抗となるように導電膜を拡散層の形成しないように製造されている。

【0056】

図8は、トランジスタ9の平面、および断面を示す説明図である。

【0057】

トランジスタ9は、たとえば、半導体基板上にP−WELL19が形成されており、このP−WELL19の上方の左右には、ドレインとして機能するN+型半導体領域20とソースとして機能するN+型半導体領域21がそれぞれ形成されている。

【0058】

N+型半導体領域21の上部には、導電膜であり、たとえば、コバルトシリサイドやニッケルシリサイドなどからなる金属シリサイド22が形成されている。一方、N+型半導体領域20の上部にも金属シリサイド23が形成されているが、この金属シリサイド23は、N+型半導体領域21のように全面に形成されておらず、上方の配線層に形成された配線24に接続されるビア25が接続される一部の領域を除いては形成されていない。

【0059】

N+型半導体領域20の全面に金属シリサイドを形成した場合に比べて、たとえば、約10倍〜約50倍程度のシート抵抗値の増加を得ることができる。また、P−WELL19の上方には、酸化シリコンなどの絶縁膜を介してゲート26が形成されている。

【0060】

このように、N+型半導体領域20の上部に一部、金属シリサイド23を形成しないことによってドレイン端子に高抵抗を持たせることができ、ESD放電などからトランジスタ9を保護することができる。

【0061】

図9は、本発明者が検討した一般的なI/O部50の回路図である。

【0062】

I/O部50(図10に示す)は、図示するように、ロジック部51(図10に示す)、および出力バッファ部52から構成されている。ロジック部51は、たとえば、ESD保護回路、入力用バッファとなる入力バッファ部、電圧レベルを変換するレベルシフタ、ならびに出力バッファ部52に駆動信号を出力するインバータなどから構成されている。

【0063】

また、出力バッファ部52は、出力バッファ用のトランジスタ53,54、ESD保護用のダイオード55,56、および同じくESD保護用の抵抗57,58から構成されている。

【0064】

トランジスタ53は、たとえば、PチャネルMOSからなり、トランジスタ54は、NチャネルMOSからなる。ダイオード55,56は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。

【0065】

トランジスタ53の一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ53の他方の接続部には、抵抗57の一方の接続部が接続されている。抵抗57の他方の接続部には、抵抗58の一方の接続が接続されており、該抵抗58の他方の接続部には、トランジスタ54の一方の接続部が接続されている。

【0066】

このトランジスタ54の他方の接続部には、基準電位VSSQが接続されている。また、ダイオード55とダイオード56との接続部、および抵抗53と抵抗54との接続部には、パッド59が接続され、出力バッファ部52の出力部となっている。

【0067】

また、図10は、図9のI/O部50における出力バッファ部52のレイアウト図である。

【0068】

I/O部50は、図の上方にロジック部51がレイアウトされており、該ロジック部51の下方には、出力バッファ部52のトランジスタ54がレイアウトされている。トランジスタ54の下方には、抵抗58がレイアウトされており、該抵抗58の下方には、ダイオード56がレイアウトされている。

【0069】

ダイオード56の下方には、パッド引き出し部59を挟んでダイオード55がレイアウトされている。ダイオード55の下方には、抵抗57がレイアウトされており、該抵抗57の下方には、トランジスタ53がレイアウトされている。

【0070】

このような回路構成では、パッド60が接続されるパッド引き出し部59を、抵抗57と抵抗58との間にしか配置できないことになり、その結果、パッド引き出し部59がI/O部50の中央部よりもオフセットして配置されるので、図11の左側に示すように、I/O部50の短辺側からはみ出してレイアウトされてしまうことになる。それにより、半導体チップサイズが大きくなってしまうことになる。

【0071】

一方、I/O部5の場合には、図8に示したトランジスタ9の構成によって抵抗58に相当する抵抗を不要にし、パッド2(またはパッド2a)からトランジスタ9のドレインまでを同じノードとすることができるので、図11の右側に示すように、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

【0072】

パッド引き出し部5aがI/O部5の略中央にレイアウトされることにより、図12に示すように、千鳥足状に配列されたパッド2のうち、外側(半導体チップ1の周辺部側)のパッド2は、半導体チップ1の中心方向に移動して配置が可能となり、パッド2よりも半導体チップ1の中心側に配置された内側のパッド2aは、半導体チップ1の外周部方向に移動して配置することができる。

【0073】

よって、パッド2,2aの大きさを小さくすることなく、パッド2,2aがI/O部5からはみ出ないようにレイアウトすることができる。

【0074】

また、トランジスタ8とトランジスタ9と間に、ダイオード10,11、および抵抗12を配置することによって、トランジスタ8とトランジスタ9との距離を離してレイアウトすることが可能となるので、寄生サイリスタ(SCR)によるラッチアップを防止することができ、信頼性を向上させることができる。

【0075】

それにより、本実施の形態1によれば、出力バッファ部7における保護回路の構成をより小さくすることができる。

【0076】

また、I/O部5からはみ出さないように、パッド2,2aを重ねてレイアウトすることができるので、半導体チップ1のチップ面積を小さくすることができ、半導体集積回路装置の小型化、および低コスト化を実現することができる。

【0077】

さらに、本実施の形態1では、出力バッファ部7が、図3の上方から下方にかけて、トランジスタ9、ダイオード11、ダイオード10、抵抗12、ならびにトランジスタ8の順番でレイアウトされた場合について記載したが、これら素子のレイアウトは、変更することもできる。

【0078】

出力バッファのレイアウトは、たとえば、図13に示すように、上方から下方にかけて、ダイオード11、ダイオード10、トランジスタ9、抵抗12、およびトランジスタ8の順番、あるいは、図14に示すように、上方から下方にかけて、ダイオード10、トランジスタ9、ダイオード11、抵抗12、ならびにトランジスタ8の順番などであってもよい。

【0079】

(実施の形態2)

図15は、本発明の実施の形態2による出力バッファ部の一例を示す回路図、図16は、図15の出力バッファ部のレイアウト例を示す説明図である。

【0080】

本実施の形態2において、半導体チップ1は、前記実施の形態の図1と同様であり、異なる点は、I/O部5に設けられた出力バッファ部7の構成である。出力バッファ部7は、図15に示すように、ダイオード10,11、およびトランジスタ8a、9から構成されている。

【0081】

ダイオード10,11は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。PチャネルMOSからなるトランジスタ8aの一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ8aの他方の接続部には、NチャネルMOSからなるトランジスタ9の一方の接続部が接続されている。

【0082】

トランジスタ9の他方の接続部には、基準電位VSSQが接続されており、ダイオード10とダイオード11との接続部、およびトランジスタ8aとトランジスタ9との接続部が、出力バッファ部7の出力部となり、パッド2,2aが接続される構成となっている。

【0083】

この場合、トランジスタ9だけでなく、トランジスタ8aにおいても、ドレインとして機能するN+型半導体領域の上面の一部に、金属シリサイドを形成しないことによって、ドレイン端子に高抵抗を持たせた構造となっている。

【0084】

それにより、抵抗12(図4)の機能をトランジスタ8aのドレイン端子に持たせることができるので、抵抗12を不要とすることができる。

【0085】

図16は、I/O部5におけるレイアウトの一例を示す説明図である。

【0086】

I/O部5は、図16の上方にロジック部6がレイアウトされており、該ロジック部6の下方に、パッド引き出し部5aを挟んでトランジスタ9がレイアウトされている。トランジスタ9の下方には、ダイオード10,11がレイアウトされており、その下方には、トランジスタ8aがレイアウトされている。

【0087】

この場合も、パッド引き出し部5aがI/O部5の略中央にレイアウトすることが可能となり、半導体チップ1(図1)のチップ面積を小さくすることができる。また、抵抗12(図4)も不要とできるので、出力バッファ部7の回路構成をより小さくすることができる。

【0088】

また、出力バッファ部7のレイアウトは、図16に示したレイアウトの他に、たとえば、図17に示すように、ダイオード11,10をトランジスタ8aとトランジスタ9との間にレイアウトしたり、図18に示すように、トランジスタ8aとトランジスタ9とを図16と逆にレイアウトする構成としてもよい。

【0089】

さらに、出力バッファ部7は、図19に示すように、ダイオード11,10をトランジスタ9とをパッド引き出し部5aを挟んでレイアウトしたり、図20に示すように、ダイオード11とダイオード10との間にパッド引き出し部5aが位置するようにレイアウトするようにしてもよい。

【0090】

(実施の形態3)

図21は、本発明の実施の形態3による出力バッファ部の一例を示す回路図、図22は、図21の出力バッファ部のレイアウト例を示す説明図である。

【0091】

本実施の形態3において、出力バッファ部7は、図21に示すように、ダイオード10,11、およびトランジスタ8a、9からなる前記実施の形態2の図15の構成に、新たに抵抗27が追加された回路構成となっている。

【0092】

抵抗27の一方の接続部には、ダイオード10,11の接続部に接続されており、該抵抗27の他方の接続部には、トランジスタ8aとトランジスタ9との接続部が接続されている。また、その他の接続構成については、前記実施の形態2の図15と同様となっている。

【0093】

図22は、I/O部5におけるレイアウトの一例を示す説明図である。

【0094】

I/O部5は、図22の上方にロジック部6がレイアウトされており、該ロジック部6の下方に、パッド引き出し部5aを挟んでダイオード11、およびダイオード10がそれぞれレイアウトされている。

【0095】

ダイオード10の下方には、抵抗27がレイアウトされており、該抵抗27の下方には、トランジスタ9がレイアウトされ、その下方には、トランジスタ8aがレイアウトされている。

【0096】

この場合においても、パッド引き出し部5aがI/O部5の略中央にレイアウトすることが可能となり、半導体チップ1(図1)のチップ面積を小さくすることができる。

【0097】

また、出力バッファ部7のレイアウトは、図21に示したレイアウトの他に、たとえば、図23に示すように、トランジスタ8aとトランジスタ9とを図21に示したレイアウトと逆にレイアウトする構成としてもよい。

【0098】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0099】

本発明は、PAD on I/O(Input/Output)セル構造を有した半導体集積回路装置におけるチップ面積の削減技術に適している。

【図面の簡単な説明】

【0100】

【図1】本発明の実施の形態1による半導体チップのレイアウトイメージを示す説明図である。

【図2】図1の半導体チップのパッドとI/O領域との一部を拡大した説明図である。

【図3】図1の半導体チップに設けられたI/O部の一例を示すレイアウト図である。

【図4】図3のI/O部に設けられた出力バッファ部の構成例を示す回路図である。

【図5】図3のI/O部の上方に配線層に形成されている周回電源配線のレイアウト図である。

【図6】図3のI/O部に接続されるパッドのレイアウト図である。

【図7】図3のI/O部の断面を示した説明図である。

【図8】図3の出力バッファ部に設けられたトランジスタの平面、および断面を示す説明図である。

【図9】本発明者が検討した一般的なI/O部の回路図である。

【図10】図9のI/O部における出力バッファ部のレイアウト図である。

【図11】本実施の形態1によるI/O部と本発明者が検討した一般的なI/O部とのレイアウト比較図である。

【図12】本実施の形態1によるI/O部とパッドとのレイアウト関係を示す説明図である。

【図13】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図14】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図15】本発明の実施の形態2による出力バッファ部の一例を示す回路図である。

【図16】図15の出力バッファ部のレイアウト例を示す説明図である。

【図17】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図18】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図19】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図20】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図21】本発明の実施の形態3による出力バッファ部の一例を示す回路図である。

【図22】図21の出力バッファ部のレイアウト例を示す説明図である。

【図23】本発明の他の実施の形態による出力バッファ部の一例を示すレイアウト図である。

【符号の説明】

【0101】

1 半導体チップ

2 パッド

3 I/O領域

4 コア領域

5 I/O部

5a パッド引き出し部

6 ロジック部

7 出力バッファ部

8,8a トランジスタ

9 トランジスタ

10,11 ダイオード

12 抵抗

13 コア電源電圧用周回配線

14 コア基準電位用周回配線

15 I/O用電源電圧周回配線

16 I/O用基準電位周回配線

17 I/O用基準電位周回配線

18 I/O用電源電圧周回配線

19 P−WELL

20 N+型半導体領域

21 N+型半導体領域

22 金属シリサイド

23 金属シリサイド

24 配線

25 ビア

26 ゲート

27 抵抗

50 I/O部

51 ロジック部

52 出力バッファ部

53,54 トランジスタ

55,56 ダイオード

57,58 抵抗

59 パッド引き出し部

60 パッド

【技術分野】

【0001】

本発明は、半導体装置におけるチップ面関の削減技術に関し、特に、PAD on I/O(Input/Output)セル構造におけるレイアウト面積の削減に有効な技術に関する。

【背景技術】

【0002】

近年、半導体集積回路装置の低コスト化、および小型化などの要求から、半導体チップのサイズを縮小するコスト削減が進んでいる。チップサイズを小さくするには、搭載する各部品のレイアウト面積削減が必要となっている。

【0003】

そこで、レイアウト面積削減技術の1つとして、たとえば、ボンディングワイヤなどが接続されるパッドを、外部とのインタフェースであるI/Oセルと重ねる、いわゆるPAD on I/Oセルという構造が知られている。

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところが、上記のようなPAD on I/Oセル技術では、次のような問題点があることが本発明者により見い出された。

【0005】

I/Oセルにおける出力バッファ部は、たとえば、PチャネルMOSのトランジスタとNチャネルMOSのトランジスタとから構成される出力バッファ、ESD(ElectroStatic Discharge)保護用となる第1、および第2のダイオードと第1、および第2の抵抗、およびESD保護回路から構成されている。

【0006】

ESD保護用となる第1、および第2のダイオードは、電源電圧と基準電位との間に直列接続されている。PチャネルMOSのトランジスタの一方の接続部には、電源電圧が接続されており、該トランジスタの他方の接続部には、第1の抵抗の一方の接続部が接続されている。

【0007】

この第1の抵抗の他方の接続部には、第2の抵抗の一方の接続部が接続されており、該第2の抵抗の他方の接続部には、NチャネルMOSのトランジスタの一方の接続部が接続されている。

【0008】

NチャネルMOSのトランジスタの他方の接続部には、基準電位が接続されている。ESD保護回路は、電源電圧と基準電位との間に接続されており、第1のダイオードと第2のダイオード、および第1の抵抗と第2の抵抗との接続部には、パッドが接続されている。

【0009】

パッドは、ボンディングワイヤによるボンディング時の制約などから、小型化することが難しく、チップ面積の削減の効果を最大限にするためには、パッドとI/Oセルとの重なる部分を最大にするのが望ましい。

【0010】

しかし、上記した回路構成では、パッドが第1、および第2の抵抗の接続部と接続されるために、パッドと接続される引き出し部が、これら2つの抵抗の間にしか配置することができず、その結果、パッドがI/Oセルからはみ出してレイアウトされてしまい、チップ面積削減の効果が小さくなってしまうという問題がある。

【0011】

また、近年のプロセスの微細化に伴い、配線抵抗が高抵抗となっており、ESD保護回路までの配線抵抗も高くなっている。そのために、ESD保護回路の放電特性が低下し、該ESD保護回路から遠くに配置されているNチャネルMOSのトランジスタなどを介してESDサージが基準電位へと放電し、素子破壊を招いてしまう恐れがある。

【0012】

さらに、配線抵抗が高くなった分、ESD保護回路の個数を増やして素子を保護することも考えられるが、その場合、チップ面積が増大してしまうという問題がある。

【0013】

本発明の目的は、PAD on I/O(Input/Output)セル構造において、パッド引き出し部のレイアウトをI/O部の略中心に配置することにより、半導体チップのレイアウト面積を削減することのできる技術を提供することにある。

【0014】

本発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0016】

本発明は、半導体チップを備え、該半導体チップは、半導体チップの辺に沿って配置された複数のI/Oパッドと、半導体チップの配置され、任意のI/Oパッドと接続される複数のI/O部とを有し、該I/O部は、出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、出力バッファ、および入力バッファを制御するロジック部とを含み、I/O部は、ロジック部、Nチャネルトランジスタ、およびPチャネルトランジスタの順に半導体チップの辺に向かってレイアウトされ、ロジック部とNチャネルトランジスタとの間にI/Oパッドと接続されるパッド引き出し部が形成されているものである。

【0017】

また、本発明は、前記Nチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0018】

さらに、本発明は、前記出力バッファ部が、ESD保護用の第1、および第2のダイオードを備え、第1、および第2のダイオードは、NチャネルトランジスタとPチャネルトランジスタとの間にレイアウトされているものである。

【0019】

また、本発明は、前記出力バッファ部が、ESD保護用の抵抗を備え、前記抵抗は、第1、および第2のダイオードとPチャネルトランジスタとの間にレイアウトされているものである。

【0020】

さらに、本発明は、前記Pチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0021】

また、本願のその他の発明の概要を簡単に示す。

【0022】

本発明は、半導体チップを備え、該半導体チップは、半導体チップの辺に沿って配置された複数のI/Oパッドと、該半導体チップに配置され、任意のI/Oパッドと接続される複数のI/O部とを有し、該I/O部は、出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、外部からの信号が入力される際のインタフェースとなる入力バッファ部を含み、出力バッファ、および入力バッファを制御するロジック部とよりなり、I/O部は、ロジック部、Pチャネルトランジスタ、およびNチャネルトランジスタの順に直線状にレイアウトされ、ロジック部とPチャネルトランジスタとの間にI/Oパッドと接続されるパッド引き出し部が形成されているものである。

【0023】

また、本発明は、前記Nチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【0024】

さらに、本発明は、前記出力バッファ部が、ESD保護用の第1、および第2のダイオードを備え、前記第1、および前記第2のダイオードは、NチャネルトランジスタとPチャネルトランジスタとの間にレイアウトされているものである。

【0025】

また、本発明は、前記出力バッファ部が、ESD保護用の抵抗を備え、前記抵抗は、第1、および第2のダイオードとPチャネルトランジスタとの間にレイアウトされているものである。

【0026】

さらに、本発明は、前記Pチャネルトランジスタが、ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したものである。

【発明の効果】

【0027】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0028】

(1)出力バッファ部における保護回路の素子構成を少なくすることができる。

【0029】

(2)I/O部からはみ出すパッドの面積を大幅に削減することが可能となり、半導体チップのチップ面積を小さくすることができる。

【0030】

(3)上記(1)、(2)により、半導体集積回路装置の小型化、および低コスト化を実現することができる。

【発明を実施するための最良の形態】

【0031】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0032】

(実施の形態1)

図1は、本発明の実施の形態1による半導体チップのレイアウトイメージを示す説明図、図2は、図1の半導体チップのパッドとI/O領域との一部を拡大した説明図、図3は、図1の半導体チップに設けられたI/O部の一例を示すレイアウト図、図4は、図3のI/O部に設けられた出力バッファ部の構成例を示す回路図、図5は、図3のI/O部の上方に配線層に形成されている周回電源配線のレイアウト図、図6は、図3のI/O部に接続されるパッドのレイアウト図、図7は、図3のI/O部の断面を示した説明図、図8は、図3の出力バッファ部に設けられたトランジスタの平面、および断面を示す説明図、図9は、本発明者が検討した一般的なI/O部の回路図、図10は、図9のI/O部における出力バッファ部のレイアウト図、図11は、本実施の形態1によるI/O部と本発明者が検討した一般的なI/O部とのレイアウト比較図、図12は、本実施の形態1によるI/O部とパッドとのレイアウト関係を示す説明図である。

【0033】

本実施の形態1において、半導体集積回路装置に設けられる半導体チップ1は、図1に示すように、4つの周辺部に、たとえば、ボンディングワイヤなどが接続される複数のパッド2が直線状にそれぞれ配置されている。

【0034】

I/Oパッドとなるパッド2の内側(半導体チップ1の中心側)には、同じくI/Oパッドとなる複数のパッド2aが直線状にそれぞれ配置されており、これらパッド2、ならびにパッド2aは、2列で千鳥足状にレイアウトされている。

【0035】

また、半導体チップ1は、パッド2,2aの下方に、外部とのインタフェースであるI/O領域3がレイアウトされた、いわゆるPAD on I/O部構造となっている。そして、半導体チップ1の中央には、トランジスタなどの半導体素子によるロジックが形成されたコア領域4が位置している。

【0036】

図2は、PAD on I/O部構造によるパッド2,2aとI/O領域3との一部(図1の点線で示す領域)を拡大した説明図である。

【0037】

I/O領域3は、複数のI/O部5が半導体チップ1の辺方向に一列にレイアウトされており、それらの上方に、2列で千鳥足状のパッド2,2aがレイアウトされている。I/O部5、およびパッド2、2aは、それぞれ長方形状からなり、パッド2,2aの長辺は、たとえば、I/O部5の長辺の約半分程度の長さにそれぞれなっている。

【0038】

各々のI/O部5の一方の短辺側には、パッド引き出し部5aが形成されており、このパッド引き出し部5aを介してI/O部5と対応するパッド2(またはパッド2a)の中央部とがそれぞれ接続されている。

【0039】

図3は、I/O部5の一例を示すレイアウト図であり、図4は、図3のI/O部5に設けられた出力バッファ部7の構成例を示す回路図である。

【0040】

I/O部5は、図3に示すように、ロジック部6、および出力バッファ部7から構成されている。ロジック部6は、たとえば、ESD保護回路6a(図4に示す)、入力用バッファとなる入力バッファ部、電圧レベルを変換するレベルシフタ、ならびに出力バッファ部7に駆動信号を出力するインバータなどから構成されている。

【0041】

また、出力バッファ部7は、図4に示すように、出力バッファ用のトランジスタ8,9、ESD保護用のダイオード10,11、および同じくESD保護用の抵抗12から構成されている。トランジスタ8は、たとえば、PチャネルMOSからなり、トランジスタ9は、NチャネルMOSからなる。

【0042】

ダイオード10,11は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。トランジスタ8の一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ8の他方の接続部には、抵抗12の一方の接続部が接続されている。

【0043】

抵抗12の他方の接続部には、トランジスタ9の一方の接続部が接続されており、該トランジスタ9の他方の接続部には、基準電位VSSQが接続されている。また、第1のダイオードであるダイオード10と第2のダイオードであるダイオード11との接続部、および抵抗12の他方の接続部とトランジスタ9の一方の接続部とが接続された接続部が、出力バッファ部7の出力部となり、パッド2(またはパッド2a)が接続される構成となっている。

【0044】

そして、I/O部5において、図3に示すように、トランジスタ8は、半導体チップ1の周辺部に最も近い位置にレイアウトされている。そして、トランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。

【0045】

ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。

【0046】

図5は、図3のI/O部5の上方に形成されている周回電源配線のレイアウト図である。

【0047】

周回電源配線は、図5の上方から下方にかけて、コア電源電圧用周回配線13、コア基準電位用周回配線14、I/O用電源電圧周回配線15、およびI/O用基準電位周回配線16が、ロジック部6の上方に形成されている。そして、パッド引き出し部5aを挟んで、I/O用基準電位周回配線17、ならびにI/O用電源電圧周回配線18が、出力バッファ部7の上方に形成されている。

【0048】

コア電源電圧用周回配線13は、コア領域4に電源電圧を供給し、コア基準電位用周回配線14は、コア領域4に基準電位を供給する。I/O用電源電圧周回配線15,18は、I/O部5に電源電圧VCCQを供給し、I/O用基準電位周回配線16,17は、基準電位VSSQを供給する。

【0049】

図6は、図3のI/O部5に接続されるパッド2のレイアウト図である。

【0050】

このパッド2は、千鳥足状に配列されたパッド2のうち、外側(半導体チップ1の周辺部側)のパッド2を示しており、該パッド2は、半導体チップ1の周辺部側に位置するI/O部5の短辺側からはみ出ない程度にレイアウトされている。

【0051】

図7は、図3のI/O部5の断面を示した説明図である。

【0052】

最下部の素子形成層には、図7の上方から下方にかけて、ロジック部6、および出力バッファ部7のトランジスタ9、ダイオード11、ダイオード10、抵抗12、ならびにトランジスタ8がそれぞれ形成されている。

【0053】

そして、素子形成層の上方に位置する配線層には、図7の左側から右側にかけて、コア電源電圧用周回配線13、コア基準電位用周回配線14、I/O用電源電圧周回配線15、I/O用基準電位周回配線16、I/O用基準電位周回配線17、ならびにI/O用電源電圧周回配線18がそれぞれ形成されている。

【0054】

そして、パッド形成層には、パッド引き出し部5a、およびパッド2がそれぞれ形成されている。これらパッド引き出し部5a、およびパッド2は、素子形成層に形成された出力バッファ部7の上方に位置するように形成されている。

【0055】

ここで、トランジスタ9(図4の点線丸印に示す)は、該トランジスタ9のドレインが高抵抗となるように導電膜を拡散層の形成しないように製造されている。

【0056】

図8は、トランジスタ9の平面、および断面を示す説明図である。

【0057】

トランジスタ9は、たとえば、半導体基板上にP−WELL19が形成されており、このP−WELL19の上方の左右には、ドレインとして機能するN+型半導体領域20とソースとして機能するN+型半導体領域21がそれぞれ形成されている。

【0058】

N+型半導体領域21の上部には、導電膜であり、たとえば、コバルトシリサイドやニッケルシリサイドなどからなる金属シリサイド22が形成されている。一方、N+型半導体領域20の上部にも金属シリサイド23が形成されているが、この金属シリサイド23は、N+型半導体領域21のように全面に形成されておらず、上方の配線層に形成された配線24に接続されるビア25が接続される一部の領域を除いては形成されていない。

【0059】

N+型半導体領域20の全面に金属シリサイドを形成した場合に比べて、たとえば、約10倍〜約50倍程度のシート抵抗値の増加を得ることができる。また、P−WELL19の上方には、酸化シリコンなどの絶縁膜を介してゲート26が形成されている。

【0060】

このように、N+型半導体領域20の上部に一部、金属シリサイド23を形成しないことによってドレイン端子に高抵抗を持たせることができ、ESD放電などからトランジスタ9を保護することができる。

【0061】

図9は、本発明者が検討した一般的なI/O部50の回路図である。

【0062】

I/O部50(図10に示す)は、図示するように、ロジック部51(図10に示す)、および出力バッファ部52から構成されている。ロジック部51は、たとえば、ESD保護回路、入力用バッファとなる入力バッファ部、電圧レベルを変換するレベルシフタ、ならびに出力バッファ部52に駆動信号を出力するインバータなどから構成されている。

【0063】

また、出力バッファ部52は、出力バッファ用のトランジスタ53,54、ESD保護用のダイオード55,56、および同じくESD保護用の抵抗57,58から構成されている。

【0064】

トランジスタ53は、たとえば、PチャネルMOSからなり、トランジスタ54は、NチャネルMOSからなる。ダイオード55,56は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。

【0065】

トランジスタ53の一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ53の他方の接続部には、抵抗57の一方の接続部が接続されている。抵抗57の他方の接続部には、抵抗58の一方の接続が接続されており、該抵抗58の他方の接続部には、トランジスタ54の一方の接続部が接続されている。

【0066】

このトランジスタ54の他方の接続部には、基準電位VSSQが接続されている。また、ダイオード55とダイオード56との接続部、および抵抗53と抵抗54との接続部には、パッド59が接続され、出力バッファ部52の出力部となっている。

【0067】

また、図10は、図9のI/O部50における出力バッファ部52のレイアウト図である。

【0068】

I/O部50は、図の上方にロジック部51がレイアウトされており、該ロジック部51の下方には、出力バッファ部52のトランジスタ54がレイアウトされている。トランジスタ54の下方には、抵抗58がレイアウトされており、該抵抗58の下方には、ダイオード56がレイアウトされている。

【0069】

ダイオード56の下方には、パッド引き出し部59を挟んでダイオード55がレイアウトされている。ダイオード55の下方には、抵抗57がレイアウトされており、該抵抗57の下方には、トランジスタ53がレイアウトされている。

【0070】

このような回路構成では、パッド60が接続されるパッド引き出し部59を、抵抗57と抵抗58との間にしか配置できないことになり、その結果、パッド引き出し部59がI/O部50の中央部よりもオフセットして配置されるので、図11の左側に示すように、I/O部50の短辺側からはみ出してレイアウトされてしまうことになる。それにより、半導体チップサイズが大きくなってしまうことになる。

【0071】

一方、I/O部5の場合には、図8に示したトランジスタ9の構成によって抵抗58に相当する抵抗を不要にし、パッド2(またはパッド2a)からトランジスタ9のドレインまでを同じノードとすることができるので、図11の右側に示すように、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

【0072】

パッド引き出し部5aがI/O部5の略中央にレイアウトされることにより、図12に示すように、千鳥足状に配列されたパッド2のうち、外側(半導体チップ1の周辺部側)のパッド2は、半導体チップ1の中心方向に移動して配置が可能となり、パッド2よりも半導体チップ1の中心側に配置された内側のパッド2aは、半導体チップ1の外周部方向に移動して配置することができる。

【0073】

よって、パッド2,2aの大きさを小さくすることなく、パッド2,2aがI/O部5からはみ出ないようにレイアウトすることができる。

【0074】

また、トランジスタ8とトランジスタ9と間に、ダイオード10,11、および抵抗12を配置することによって、トランジスタ8とトランジスタ9との距離を離してレイアウトすることが可能となるので、寄生サイリスタ(SCR)によるラッチアップを防止することができ、信頼性を向上させることができる。

【0075】

それにより、本実施の形態1によれば、出力バッファ部7における保護回路の構成をより小さくすることができる。

【0076】

また、I/O部5からはみ出さないように、パッド2,2aを重ねてレイアウトすることができるので、半導体チップ1のチップ面積を小さくすることができ、半導体集積回路装置の小型化、および低コスト化を実現することができる。

【0077】

さらに、本実施の形態1では、出力バッファ部7が、図3の上方から下方にかけて、トランジスタ9、ダイオード11、ダイオード10、抵抗12、ならびにトランジスタ8の順番でレイアウトされた場合について記載したが、これら素子のレイアウトは、変更することもできる。

【0078】

出力バッファのレイアウトは、たとえば、図13に示すように、上方から下方にかけて、ダイオード11、ダイオード10、トランジスタ9、抵抗12、およびトランジスタ8の順番、あるいは、図14に示すように、上方から下方にかけて、ダイオード10、トランジスタ9、ダイオード11、抵抗12、ならびにトランジスタ8の順番などであってもよい。

【0079】

(実施の形態2)

図15は、本発明の実施の形態2による出力バッファ部の一例を示す回路図、図16は、図15の出力バッファ部のレイアウト例を示す説明図である。

【0080】

本実施の形態2において、半導体チップ1は、前記実施の形態の図1と同様であり、異なる点は、I/O部5に設けられた出力バッファ部7の構成である。出力バッファ部7は、図15に示すように、ダイオード10,11、およびトランジスタ8a、9から構成されている。

【0081】

ダイオード10,11は、電源電圧VCCQと基準電位VSSQとの間に直列接続されている。PチャネルMOSからなるトランジスタ8aの一方の接続部には、電源電圧VCCQが接続されており、該トランジスタ8aの他方の接続部には、NチャネルMOSからなるトランジスタ9の一方の接続部が接続されている。

【0082】

トランジスタ9の他方の接続部には、基準電位VSSQが接続されており、ダイオード10とダイオード11との接続部、およびトランジスタ8aとトランジスタ9との接続部が、出力バッファ部7の出力部となり、パッド2,2aが接続される構成となっている。

【0083】

この場合、トランジスタ9だけでなく、トランジスタ8aにおいても、ドレインとして機能するN+型半導体領域の上面の一部に、金属シリサイドを形成しないことによって、ドレイン端子に高抵抗を持たせた構造となっている。

【0084】

それにより、抵抗12(図4)の機能をトランジスタ8aのドレイン端子に持たせることができるので、抵抗12を不要とすることができる。

【0085】

図16は、I/O部5におけるレイアウトの一例を示す説明図である。

【0086】

I/O部5は、図16の上方にロジック部6がレイアウトされており、該ロジック部6の下方に、パッド引き出し部5aを挟んでトランジスタ9がレイアウトされている。トランジスタ9の下方には、ダイオード10,11がレイアウトされており、その下方には、トランジスタ8aがレイアウトされている。

【0087】

この場合も、パッド引き出し部5aがI/O部5の略中央にレイアウトすることが可能となり、半導体チップ1(図1)のチップ面積を小さくすることができる。また、抵抗12(図4)も不要とできるので、出力バッファ部7の回路構成をより小さくすることができる。

【0088】

また、出力バッファ部7のレイアウトは、図16に示したレイアウトの他に、たとえば、図17に示すように、ダイオード11,10をトランジスタ8aとトランジスタ9との間にレイアウトしたり、図18に示すように、トランジスタ8aとトランジスタ9とを図16と逆にレイアウトする構成としてもよい。

【0089】

さらに、出力バッファ部7は、図19に示すように、ダイオード11,10をトランジスタ9とをパッド引き出し部5aを挟んでレイアウトしたり、図20に示すように、ダイオード11とダイオード10との間にパッド引き出し部5aが位置するようにレイアウトするようにしてもよい。

【0090】

(実施の形態3)

図21は、本発明の実施の形態3による出力バッファ部の一例を示す回路図、図22は、図21の出力バッファ部のレイアウト例を示す説明図である。

【0091】

本実施の形態3において、出力バッファ部7は、図21に示すように、ダイオード10,11、およびトランジスタ8a、9からなる前記実施の形態2の図15の構成に、新たに抵抗27が追加された回路構成となっている。

【0092】

抵抗27の一方の接続部には、ダイオード10,11の接続部に接続されており、該抵抗27の他方の接続部には、トランジスタ8aとトランジスタ9との接続部が接続されている。また、その他の接続構成については、前記実施の形態2の図15と同様となっている。

【0093】

図22は、I/O部5におけるレイアウトの一例を示す説明図である。

【0094】

I/O部5は、図22の上方にロジック部6がレイアウトされており、該ロジック部6の下方に、パッド引き出し部5aを挟んでダイオード11、およびダイオード10がそれぞれレイアウトされている。

【0095】

ダイオード10の下方には、抵抗27がレイアウトされており、該抵抗27の下方には、トランジスタ9がレイアウトされ、その下方には、トランジスタ8aがレイアウトされている。

【0096】

この場合においても、パッド引き出し部5aがI/O部5の略中央にレイアウトすることが可能となり、半導体チップ1(図1)のチップ面積を小さくすることができる。

【0097】

また、出力バッファ部7のレイアウトは、図21に示したレイアウトの他に、たとえば、図23に示すように、トランジスタ8aとトランジスタ9とを図21に示したレイアウトと逆にレイアウトする構成としてもよい。

【0098】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0099】

本発明は、PAD on I/O(Input/Output)セル構造を有した半導体集積回路装置におけるチップ面積の削減技術に適している。

【図面の簡単な説明】

【0100】

【図1】本発明の実施の形態1による半導体チップのレイアウトイメージを示す説明図である。

【図2】図1の半導体チップのパッドとI/O領域との一部を拡大した説明図である。

【図3】図1の半導体チップに設けられたI/O部の一例を示すレイアウト図である。

【図4】図3のI/O部に設けられた出力バッファ部の構成例を示す回路図である。

【図5】図3のI/O部の上方に配線層に形成されている周回電源配線のレイアウト図である。

【図6】図3のI/O部に接続されるパッドのレイアウト図である。

【図7】図3のI/O部の断面を示した説明図である。

【図8】図3の出力バッファ部に設けられたトランジスタの平面、および断面を示す説明図である。

【図9】本発明者が検討した一般的なI/O部の回路図である。

【図10】図9のI/O部における出力バッファ部のレイアウト図である。

【図11】本実施の形態1によるI/O部と本発明者が検討した一般的なI/O部とのレイアウト比較図である。

【図12】本実施の形態1によるI/O部とパッドとのレイアウト関係を示す説明図である。

【図13】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図14】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図15】本発明の実施の形態2による出力バッファ部の一例を示す回路図である。

【図16】図15の出力バッファ部のレイアウト例を示す説明図である。

【図17】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図18】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図19】本発明の他の実施の形態によるI/O部の一例を示すレイアウト図である。

【図20】本発明の他の実施の形態によるI/O部の他の例を示すレイアウト図である。

【図21】本発明の実施の形態3による出力バッファ部の一例を示す回路図である。

【図22】図21の出力バッファ部のレイアウト例を示す説明図である。

【図23】本発明の他の実施の形態による出力バッファ部の一例を示すレイアウト図である。

【符号の説明】

【0101】

1 半導体チップ

2 パッド

3 I/O領域

4 コア領域

5 I/O部

5a パッド引き出し部

6 ロジック部

7 出力バッファ部

8,8a トランジスタ

9 トランジスタ

10,11 ダイオード

12 抵抗

13 コア電源電圧用周回配線

14 コア基準電位用周回配線

15 I/O用電源電圧周回配線

16 I/O用基準電位周回配線

17 I/O用基準電位周回配線

18 I/O用電源電圧周回配線

19 P−WELL

20 N+型半導体領域

21 N+型半導体領域

22 金属シリサイド

23 金属シリサイド

24 配線

25 ビア

26 ゲート

27 抵抗

50 I/O部

51 ロジック部

52 出力バッファ部

53,54 トランジスタ

55,56 ダイオード

57,58 抵抗

59 パッド引き出し部

60 パッド

【特許請求の範囲】

【請求項1】

半導体チップを備え、

前記半導体チップは、

前記半導体チップの辺に沿って配置された複数のI/Oパッドと、

前記半導体チップに配置され、任意の前記I/Oパッドと接続される複数のI/O部とを有し、

前記I/O部は、

出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、

前記出力バッファ部、および入力バッファ部を制御するロジック部とを含み、

前記I/O部は、

前記ロジック部、前記Nチャネルトランジスタ、および前記Pチャネルトランジスタの順に前記半導体チップの辺に向かってレイアウトされ、

前記ロジック部と前記Nチャネルトランジスタとの間に前記I/Oパッドと接続されるパッド引き出し部が形成されていることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、

前記Nチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項3】

請求項1または2記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の第1、および第2のダイオードを備え、

前記第1、および第2のダイオードは、

前記Nチャネルトランジスタと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項4】

請求項3記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の抵抗を備え、

前記抵抗は、

前記第1、および前記第2のダイオードと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項5】

請求項1〜3のいずれか1項に記載の半導体集積回路装置において、

前記Pチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項6】

半導体チップを備え、

前記半導体チップは、

前記半導体チップの辺に沿って配置された複数のI/Oパッドと、

前記半導体チップに配置され、任意の前記I/Oパッドと接続される複数のI/O部とを有し、

前記I/O部は、

出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、

外部からの信号が入力される際のインタフェースとなる入力バッファ部を含み、前記出力バッファ部、および前記入力バッファ部を制御するロジック部とよりなり、

前記I/O部は、

前記ロジック部、前記Pチャネルトランジスタ、および前記Nチャネルトランジスタの順に直線状にレイアウトされ、

前記ロジック部と前記Pチャネルトランジスタとの間に前記I/Oパッドと接続されるパッド引き出し部が形成されていることを特徴とする半導体集積回路装置。

【請求項7】

請求項6記載の半導体集積回路装置において、

前記Nチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項8】

請求項6または7記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の第1、および第2のダイオードを備え、

前記第1、および第2のダイオードは、

前記Nチャネルトランジスタと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項9】

請求項8記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の抵抗を備え、

前記抵抗は、

前記第1、および前記第2のダイオードと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項10】

請求項6〜8のいずれか1項に記載の半導体集積回路装置において、

前記Pチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項1】

半導体チップを備え、

前記半導体チップは、

前記半導体チップの辺に沿って配置された複数のI/Oパッドと、

前記半導体チップに配置され、任意の前記I/Oパッドと接続される複数のI/O部とを有し、

前記I/O部は、

出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、

前記出力バッファ部、および入力バッファ部を制御するロジック部とを含み、

前記I/O部は、

前記ロジック部、前記Nチャネルトランジスタ、および前記Pチャネルトランジスタの順に前記半導体チップの辺に向かってレイアウトされ、

前記ロジック部と前記Nチャネルトランジスタとの間に前記I/Oパッドと接続されるパッド引き出し部が形成されていることを特徴とする半導体集積回路装置。

【請求項2】

請求項1記載の半導体集積回路装置において、

前記Nチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項3】

請求項1または2記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の第1、および第2のダイオードを備え、

前記第1、および第2のダイオードは、

前記Nチャネルトランジスタと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項4】

請求項3記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の抵抗を備え、

前記抵抗は、

前記第1、および前記第2のダイオードと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項5】

請求項1〜3のいずれか1項に記載の半導体集積回路装置において、

前記Pチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項6】

半導体チップを備え、

前記半導体チップは、

前記半導体チップの辺に沿って配置された複数のI/Oパッドと、

前記半導体チップに配置され、任意の前記I/Oパッドと接続される複数のI/O部とを有し、

前記I/O部は、

出力バッファとなるNチャネルトランジスタ、およびPチャネルトランジスタを備え、信号を外部に出力する際のインタフェースとなる出力バッファ部と、

外部からの信号が入力される際のインタフェースとなる入力バッファ部を含み、前記出力バッファ部、および前記入力バッファ部を制御するロジック部とよりなり、

前記I/O部は、

前記ロジック部、前記Pチャネルトランジスタ、および前記Nチャネルトランジスタの順に直線状にレイアウトされ、

前記ロジック部と前記Pチャネルトランジスタとの間に前記I/Oパッドと接続されるパッド引き出し部が形成されていることを特徴とする半導体集積回路装置。

【請求項7】

請求項6記載の半導体集積回路装置において、

前記Nチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Nチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【請求項8】

請求項6または7記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の第1、および第2のダイオードを備え、

前記第1、および第2のダイオードは、

前記Nチャネルトランジスタと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項9】

請求項8記載の半導体集積回路装置において、

前記出力バッファ部は、

ESD保護用の抵抗を備え、

前記抵抗は、

前記第1、および前記第2のダイオードと前記Pチャネルトランジスタとの間にレイアウトされていることを特徴とする半導体集積回路装置。

【請求項10】

請求項6〜8のいずれか1項に記載の半導体集積回路装置において、

前記Pチャネルトランジスタは、

ドレインとして機能する半導体領域の主面の一部に導電膜を形成せず、前記Pチャネルトランジスタのドレイン端子を高抵抗となるように形成したことを特徴とする半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2010−147282(P2010−147282A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−323589(P2008−323589)

【出願日】平成20年12月19日(2008.12.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月19日(2008.12.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]