半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)における配線およびボンディングパッド等構造技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2011−114049号公報(特許文献1)には、メモリ系半導体集積回路デバイスに於いて、アルミニウム系パッド層を除き、全ての配線層を銅配線とした配線層構成が開示されている。

【0003】

日本特開2011−129722号公報(特許文献2)には、多層の銅配線の上に、アルミニウム系パッド(ボンディングパッドおよびシールリング上のパッドを含む)を形成した半導体集積回路デバイスが開示されている。

【0004】

日本特開2011−9581号公報(特許文献3)または、これに対応する米国特許公開2010−330799号公報(特許文献4)には、銅埋め込み配線の最上層上にタングステンプラグ等の中継メタル部材を介せずに、アルミニウム系パッドを形成し、このボンディングパッドにボンディングワイヤを接続した半導体集積回路デバイスが開示されている。

【0005】

日本特開2010−147267号公報(特許文献5)には、アルミニウム系パッド層上に、再配線を形成したウエハレベルパッケージ(Wafer Level Package)方式の半導体集積回路デバイスに於いて、アルミニウム系パッド層を銅ダマシン配線の最上層のメタル配線として使用する他、同層をパッド専用とすることが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2011−114049号公報

【特許文献2】特開2011−129722号公報

【特許文献3】特開2011−9581号公報

【特許文献4】米国特許公開2010−330799号公報

【特許文献5】特開2010−147267号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。また、アルミニウム系パッド層に、このような一般相互接続配線がない場合に於いても、幅の広くチップサイズと同程度の寸法を有する電源リング等の電源幹配線等の存在は、これとファイナルパッシベーション膜との物理的性質の相違に基づく、クラック等の発生の原因になりやすい等の問題がある。

【0008】

本願発明は、これらの課題を解決するためになされたものである。

【0009】

本発明の目的は、信頼性の高い半導体集積回路装置を提供することにある。

【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0012】

すなわち、本願の一つの発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

【発明の効果】

【0013】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0014】

すなわち、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものとすることによって、信頼性の高い半導体集積回路装置とすることができる。

【図面の簡単な説明】

【0015】

【図1】本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明するためのメタル配線システム等のデバイス模式断面図である。

【図2】図1のチップ表面から埋め込み型第6配線層M6までのより詳細なデバイス模式断面図である。

【図3】本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。

【図4】本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(埋め込み型最上層配線層を中心に表示)である。

【図5】図3および図4のX−X’断面の実線部分に対応するチップ(ウエハのチップ領域およびその周辺)のデバイス模式断面図である。

【図6】図4のVssリング切り出し領域R1の電源リングの詳細レイアウト図である。

【図7】図6のA−B断面のデバイス模式断面図である。

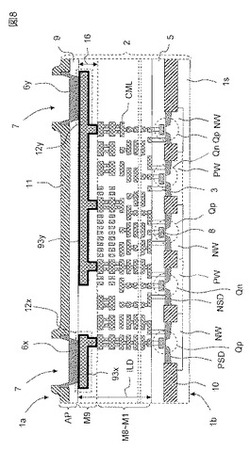

【図8】本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明するためのデバイス模式断面図である。

【図9】図8のアルミニウム系主ボンディングパッド膜6x,6yにほぼ対応するパッド周辺拡大上面図である。

【図10】図9のC−D断面のデバイス模式断面図である。

【図11】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第7配線層M7完成時点)である。

【図12】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第8配線層M8完成時点)である。

【図13】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型最上層配線層M9完成時点)である。

【図14】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(パッドコンタクト用スルーホール39完成時点)である。

【図15】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(アルミニウム系ボンディングパッド加工完成時点)である。

【図16】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ファイナルパッシベーション膜のパッド開口加工完成時点)である。

【図17】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ワイヤボンディング完成時点)である。

【図18】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(樹脂モールド完成時点)である。

【図19】本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明するための図9に対応するパッド周辺拡大上面図である。

【図20】図19のC−D断面のデバイス模式断面図である。

【図21】アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明するための図3に対応するチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。

【図22】アンテナ比の大きなウエハと、アンテナ比の小さなウエハに対して、プラズマ処理を施したサンプルについてのMISFETのソースドレイン電流および閾値電圧の分布を示すデータプロット図である。

【発明を実施するための形態】

【0016】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0017】

1.以下を含む半導体集積回路装置:

(a)第1の主面を有する半導体基板;

(b)前記半導体基板の前記第1の主面に設けられた複数のMISFET;

(c)前記半導体基板の前記第1の主面および前記複数のMISFETの上方に設けられた埋め込み型多層配線層;

(d)前記埋め込み型多層配線層上に設けられた非埋め込み型アルミニウム系パッドメタル層;

(e)前記非埋め込み型アルミニウム系パッドメタル層の一部として設けられた複数のメタルボンディングパッド;

(f)前記非埋め込み型アルミニウム系パッドメタル層よりも上層に形成されたファイナルパッシベーション膜;

(g)前記複数のメタルボンディングパッドの各々の上方の前記ファイナルパッシベーション膜に設けられたパッド開口、

ここで、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しない。

【0018】

2.前記1項の半導体集積回路装置において、更に以下を含む:

(h)前記埋め込み型多層配線層の内の埋め込み型最上層配線層の一部として設けられた電源リング配線。

【0019】

3.前記2項の半導体集積回路装置において、更に以下を含む:

(i)前記電源リング配線内に設けられたディッシング防止用スリット。

【0020】

4.前記2または3項の半導体集積回路装置において、前記複数のメタルボンディングパッドの各々は、プラグを介することなく、前記埋め込み型最上層配線層に接続されている。

【0021】

5.前記2から4項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(j)前記複数のメタルボンディングパッドの各々の下方に、前記埋め込み型最上層配線層の一部として設けられ、その上方のメタルボンディングパッドと形状および面積がほぼ同様の下地メタルパッド。

【0022】

6.前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた単一のスルーホール。

【0023】

7.前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた複数のスルーホール。

【0024】

8.前記1から7項のいずれか一つの半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に配線を有しない。

【0025】

9.前記1から8項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(m)前記第1の主面の内部領域に、前記非埋め込み型アルミニウム系パッドメタル層の一部として、ほぼ均一に分布するように設けられた多数の占有率調整用ダミーパターン。

【0026】

10.前記1から9項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(n)前記第1の主面の外周に沿って、前記非埋め込み型アルミニウム系パッドメタル層の一部として、アルミニウム系シールリング。

【0027】

11.前記1から10項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(p)前記複数のメタルボンディングパッドの各々の上面に接続されたボンディングワイヤ。

【0028】

12.前記1から11項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(q)前記ファイナルパッシベーション膜上を被う封止樹脂層。

【0029】

13.前記1から12項のいずれか一つの半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に信号配線を有しない。

【0030】

14.前記10から13項のいずれか一つの半導体集積回路装置において、前記複数のメタルボンディングパッドは、アルミニウム系シールリングに沿うように、その内側に、リング状に配列されている。

【0031】

15.前記1から14項のいずれか一つの半導体集積回路装置において、前記埋め込み型多層配線層は、銅系埋め込み型多層配線層である。

【0032】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0033】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ(能動素子)単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、集積回路構成の代表的なものとしては、Nチャネル型MISFETとPチャネル型MISFETを組み合わせたCMOS(Complemetary Metal Oxide Semiconductor)型集積回路に代表されるCMIS(Complemetary Metal Insulator Semiconductor)型集積回路を例示することができる。

【0034】

今日の半導体集積回路装置、すなわち、LSI(Large Scale Integration)のウエハ工程は、通常、原材料としてのシリコンウエハの搬入からプリメタル(Premetal)工程(M1配線層下端とゲート電極構造の間の層間絶縁膜等の形成、コンタクトホール形成、タングステンプラグ、埋め込み等からなる工程)あたりまでのFEOL(Front End of Line)工程と、M1配線層形成から始まり、アルミニウム系パッド電極上のファイナルパッシベーション膜へのパッド開口の形成あたりまで(ウエハレベルパッケージプロセスにおいては、当該プロセスも含む)のBEOL(Back End of Line)工程に大別できる。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0036】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0037】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0038】

窒化シリコン膜は、SAC(Self−Aligned Contact)技術におけるエッチストップ膜、すなわち、CESL(Contact Etch−Stop Layer)として、多用されるほか、SMT(Stress Memorization Technique)における応力付与膜としても使用される。

【0039】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0040】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0041】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0042】

6.本願に於いて、「リング」というときは、主に略矩形環状の図形を指す。しかし、「環状」といっても、必ずしも閉じている必要はない。具体的には、シールリング、電源リング、パッドリング、スルーホールリング等がある。シールリングは、一般に閉リングであるが、電源リングは、見かけ上は、ほぼ閉リング(厳密な平リングのこともある)であるが、厳密に言うと、一部が開いた開リングであることが多い。パッドリング、スルーホールリング等は、ドット状のパターン群が全体としてリング状に配列されたものである。

【0043】

なお、本願に於いて、「ボンディングパッド」というときは、ワイヤボンディングのためのパッドの外、その上に、バンプ電極や再配線を形成するものも含むこととする。

【0044】

7.本願に於いて、「メタルパターン」は、「配線パターン」と「非配線パターン」に分類される。「配線パターン」または「配線」とは、端子(または素子)と素子間を相互に繋ぐメタル電流通路であり、主に電流を流すことを主要な目的とするものである。「非配線パターン」には、素子パターン、パッドパターン、テストパターン、合わせパターン、ダミーパターン等が含まれる。「配線」は、電源リング(接地リング、Vddリング)等の電源幹配線その他の「電源配線」と「信号配線」に分類される。また、その幾何学的な用途から、以下のような分類も用いられる。すなわち、主に回路モジュール間の相互接続等に利用される「セミグローバル配線」(以下の実施の形態では、たとえば、埋め込み型第7、8配線層)、より広い範囲の接続等に使用される「グローバル配線」(以下の実施の形態では、たとえば、埋め込み型最上層配線層)、主に回路モジュール内の相互接続等に利用される「ローカル配線」(以下の実施の形態では、たとえば、埋め込み型第1配線層から埋め込み型第6配線層)等に分類される。

【0045】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0046】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0047】

1.本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインの説明(主に図1および図2)

このセクションでは、本願の一実施の形態の半導体集積回路装置の構造をメタル配線システム全体から概説する。

【0048】

以下では、65nmテクノロジノードのデバイスの例に取り具体的に説明するが、以下の例は、これに限定されるものではなく、これよりも微細なテクノロジノードのデバイスにも適用できるし、これよりも微細でないテクノロジノードのデバイスにも適用できることは言うまでもない。

【0049】

また、以下では、埋め込み型配線9層およびアルミニウム系非埋め込み配線(メタル層)1層のメタル配線系を例にとり、具体的に説明するが、これ以外の層数の配線系でも良いことは言うまでもない。

【0050】

図1は本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明するためのメタル配線システム等のデバイス模式断面図である。図2は図1のチップ表面から埋め込み型第6配線層M6までのより詳細なデバイス模式断面図である。これらに基づいて、本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明する。

【0051】

図1に示すように、たとえば、STI(Shallow Trench Isolation)型の素子分離フィールド絶縁膜10で分離されたP型単結晶シリコン基板1sのデバイス面1a(裏面1bの反対側の面)上には、PチャネルMOSFETまたはNチャネルMOSFETのゲート電極8が形成されている。それらの上には、エッチストップ膜である窒化シリコンライナー膜4(たとえば約30nm)が形成されている。その上には、たとえば、窒化シリコンライナー膜4よりもずっと厚く、下層の熱CVD法によるオゾンTEOS酸化シリコン膜(たとえば約200nm)および上層のプラズマTEOS酸化シリコン膜(たとえば約270nm)等からなるプリメタル(Premetal)層間絶縁膜5が形成されている。また、これらのプリメタル絶縁膜を貫通して、タングステンプラグ3が形成されている。ここまでがプリメタル領域PMである。

【0052】

その上の第1配線層M1は、たとえば、下層のSiC膜(たとえば約50nm)等の絶縁性バリア膜14および主層間絶縁膜であるプラズマシリコン酸化膜15(たとえば約150nm)等およびそれらに形成された配線溝に埋め込まれた銅配線13等から構成されている。

【0053】

その上の第2配線層から第6配線層M2,M3,M4,M5,M6は、相互にほぼ同様の構造をしている。各層は、たとえば、下層のSiC膜(たとえば約50nm)等からなる絶縁性バリア膜(ライナー膜)24、34,44、54,64、および上層のほとんどの領域を占める主層間絶縁膜25,35,45,55,65等から構成されている。この主層間絶縁膜25,35,45,55,65は、たとえば、カーボンドープ酸化シリコン膜、すなわち、SiOC膜(たとえば約400nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線23,33,43,53,63(たとえば、配線幅150nm程度、配線厚さ200nm程度)が形成されている。なお、第1配線層から第6配線層M1,M2,M3,M4,M5,M6は、たとえば、この例ではローカル配線である。

【0054】

その上の第7配線層から第8配線層M7,M8は、相互にほぼ同様の構造をしている。各層間絶縁膜、すなわち、セミグローバル下層配線層層間絶縁膜19およびセミグローバル上層配線層層間絶縁膜18は、たとえば、最下層のSiC膜(たとえば約70nm)等の絶縁性バリア膜74,84、中下層のプラズマTEOSシリコン酸化膜75a,85a(たとえば約250nm)、中上層のFSG膜75b,85b(たとえば約250nm)、およびキャップ膜であるプラズマTEOSシリコン酸化膜75c,85c(たとえば約100nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線73,83(たとえば、配線幅200nm程度、配線厚さ350nm程度)が形成されている。なお、この例では、セミグローバル配線を2層としたが、セミグローバル配線の層数は、必要に応じて、3層以上とすることもできるし、1層とすることもできる。

【0055】

その上の第9配線層M9は、たとえば、この例では、グローバル配線層であり、たとえば、以下のような構造をしている。埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)は、下層のSiC膜(たとえば約70nm)等の絶縁性バリア膜94b、中下層のプラズマTEOS系主層間絶縁膜95b(たとえば約800nm)、中上層のSiN系絶縁性バリア膜94a、およびプラズマTEOS系主層間絶縁膜95a(たとえば約900nm)等から構成されている。これらの層間絶縁膜等を貫通等して、銅プラグおよび銅配線を含む銅埋め込み配線93(たとえば、配線幅400nm程度、配線厚さ900nm程度)が形成されている。ここまでが、埋め込み型多層配線層DWである。

【0056】

その上の非埋め込み型アルミニウム系パッドメタル層APの絶縁膜構造は、たとえば、下層のパッド層層間絶縁膜9および上層のファイナルパッシベーション膜から構成されており、その間に、アルミニウム系ボンディングパッド6が形成されている。すなわち、パッド層層間絶縁膜9は、下層のSiN膜9b(たとえば約100nm)等の絶縁性バリア膜、プラズマTEOS系主層間絶縁膜9a(たとえば約900nm)等から構成されている。また、アルミニウム系ボンディングパッド6上には、パッド開口7が設けられている。なお、アルミニウム系ボンディングパッド6下の銅埋め込み配線93は、後に説明するように、下地メタルパッド12でもある。

【0057】

次に、図2を用いて、図1の埋め込み型第6配線層M6およびそれよりも上方の断面構造の詳細を説明する。図2に示すように、埋め込み型第6配線層M6の層間絶縁膜、すなわち、ローカル最上層配線層層間絶縁膜21は、たとえば、下層のSiC系絶縁性バリア膜64、上層のSiOC系主層間絶縁膜65等から構成されており、その中に埋め込まれた銅埋め込み配線63は、たとえば、主要部を占める埋め込み型第6配線層銅系メタル膜63a、その周辺(側面および下面)の窒化タンタル系バリアメタル膜63b等から構成されている。なお、第7層銅埋め込み配線73、第8層銅埋め込み配線83の詳細構造も銅埋め込み配線63とほぼ同じであるので、説明は繰り返さない。また、埋め込み型第7配線層M7および埋め込み型第8配線層M8の構造も、先に図1について説明したところと同じであるので、ここでは説明を繰り返さない。

【0058】

次に、埋め込み型第9配線層M9(埋め込み型最上層配線層)を説明するが、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)の構造は、先に図1について説明したところと同じであるので、ここでは説明を繰り返さず、最上層銅埋め込み配線等93(配線、ビア等)の詳細構造を説明する。これも、先に図1について説明したところと同じであり、たとえば、主要部を占める埋め込み型第9配線層銅系メタル膜93a、その周辺(側面および下面)の窒化タンタル系バリアメタル膜93b等から構成されている。

【0059】

次に、非埋め込み型アルミニウム系パッドメタル層APを説明する。非埋め込み型アルミニウム系パッドメタル層APの層間絶縁膜は、たとえば、下層のパッド層層間絶縁膜9および上層のファイナルパッシベーション膜11から構成されている。パッド層層間絶縁膜9は、たとえば下層のSiN系絶縁性バリア膜9b(たとえば厚さ約100nm程度)および上層のプラズマTEOS系主層間絶縁膜9a(たとえば厚さ約600nm程度)等から構成されている。上層のファイナルパッシベーション膜11は、たとえば下層のUSG(Undoped Silicon Glass)系ファイナルパッシベーション膜11a(たとえば厚さ約900nm程度)および上層のプラズマSiN系ファイナルパッシベーション膜11b(たとえば厚さ約600nm程度)等から構成されている。これらの間には、たとえば下層の窒化チタン系パッドバリアメタル膜6b(たとえば厚さ約100nm程度)およびアルミニウム系主ボンディングパッド膜6a(たとえば厚さ約1000nm程度)等から構成されている。

【0060】

2.本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等の説明(主に図3から図7)

このセクションでは、本願の前記一実施の形態の半導体集積回路装置の構造等を非埋め込み型アルミニウム系パッドメタル層および埋め込み型第9配線層(埋め込み型最上層配線層)の平面レイアウト等を中心に説明する。

【0061】

なお、このセクションでは、便宜上、ウエハ1(たとえば図3)のチップ領域2およびその周辺を説明するが、最終製品としての分離されたチップ2では、ダイシング領域27(スクライブ領域)は、ダイシングブレード等による加工の結果、すでに存在しない。

【0062】

なお、ここでは、チップサイズは、10ミリメートル角程度のものを例に取り具体的に説明する。

【0063】

図3は本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。図4は本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチプ領域およびその周辺の模式レイアウト図(埋め込み型最上層配線層を中心に表示)である。図5は図3および図4のX−X’断面の実線部分に対応するチップ(ウエハのチップ領域およびその周辺)のデバイス模式断面図である。図6は図4のVssリング切り出し領域R1の電源リングの詳細レイアウト図である。図7は図6のA−B断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明する。

【0064】

先ず、非埋め込み型アルミニウム系パッドメタル層APの平面レイアウトを図3に基づいて説明する。図3に示すように、非埋め込み型アルミニウム系パッドメタル層APにより構成されているパターンとしては、チップ領域2の外部においては、たとえば、アルミニウム系TEGパターン29a、アルミニウム系レーザートリム用位置決め基準パターン30a、アルミニウム系膜厚モニタ31a、アルミニウム系露光用アライメントパターン32a等がある。一方、チップ領域2の内部においては、外側から、たとえば、耐湿性や強度を確保するためのアルミニウム系シールリング20a、多数のボンディングパッド6から構成されたアルミニウム系パッドリング22a、アルミニウム系パッドリング22aの内側全面に敷き詰められた繰り返しパターン等からなる占有率調整用ダミーパターン28(非埋め込み型アルミニウム系パッドメタル層APの際のドライエッチング特性を確保するためのダミーパターン)がある。ここで、占有率調整用ダミーパターン28は、プラズマダメージ等を回避するためには、フローティングとすることが望ましいが、そのような問題がない場合は、フローティングにしなくても良い。また、アルミニウム系シールリング20aの存在は、チップ周辺からのクラック等の伝播を阻止するのに有効である。

【0065】

ここで、アルミニウム系TEGパターン29aの全体の平面サイズは、たとえば、50x2000マイクロメートル程度である。また、アルミニウム系レーザートリム用位置決め基準パターン30a、アルミニウム系膜厚モニタ31a、およびアルミニウム系露光用アライメントパターン32aの各々のサイズは、たとえば50x100マイクロメートル程度である。更に、アルミニウム系シールリング20aの幅は、たとえば10マイクロメートル程度であり、ボンディングパッド6のサイズとしては、たとえば、60x100マイクロメートル程度である。また、占有率調整用ダミーパターン28を構成する個々の要素パターンのサイズは、たとえば35マイクロメートル角程度であり、その配列ピッチとしては、たとえば、140マイクロメートル程度を好適なものとして例示することができる。ここでは、長方形のボンディングパッド6を具体的に示したが、ボンディングパッド6の平面形状は、長方形に限らず、正方形(寸法は、たとえば60x60マイクロメートル程度)等の他の図形でも良い。

【0066】

なお、占有率調整用ダミーパターン28が形成されている領域の中央部は、通常、チップ内部回路形成領域26と一致している。また、チップ領域のほぼ全体は、その外端部および各ボンディングパッド6の主要部を除き、ファイナルパッシベーション膜11(たとえば、無機系ファイナルパッシベーション膜、ポリイミド膜等の有機系ファイナルパッシベーション膜またはこれらの両方)に覆われている。

【0067】

次に、埋め込み型第9配線層M9(埋め込み型最上層配線層)の平面レイアウトを図4に基づいて説明する。図4に示すように、埋め込み型最上層配線層M9により構成されているパターンとしては、チップ領域2の外部においては、たとえば、銅系TEGパターン29b、銅系膜厚モニタ31b、銅系露光用アライメントパターン32b等がある。一方、チップ領域2の内部においては、外側から、たとえば、耐湿性や強度を確保するための銅系シールリング20b、多数の下地メタルパッド12から構成された銅系パッドリング22b、ほぼリング状の接地幹配線から構成されたVssリング(接地リング36g)およびほぼリング状の電源供給幹配線から構成されたVddリング(電源供給リング36d)等を含む電源リング36(電源幹配線)等がある。電源リング36の内側は、一般に、チップ内部回路形成領域26となっている。なお、複数電圧電源の場合は、電源の種類に対応して、電源供給リングは、複数本となる。

【0068】

次に、図3および図4のX−X’断面(実線部)の構造(主に非埋め込み型アルミニウム系パッドメタル層APおよび埋め込み型最上層配線層M9)を図5に基づいて説明する。図5に示すように、埋め込み型第8配線層M8上に、埋め込み型最上層配線層M9が形成されている。この埋め込み型最上層配線層M9は、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)および、これにデュアルダマシン(Dual Damascene)法等により埋め込まれた銅系配線等から構成されている。この層の銅系配線等としては、たとえばVssリング36g(接地リング)、Vddリング36d(電源供給リング)のほか、各アルミニウム系ボンディングパッド6の直下でこれとコンタクトし、これとほぼ同一の形状、位置、サイズを有する下地メタルパッド12、アルミニウム系シールリング20aの直下にあって、ほぼ同様の働きをする銅系シールリング20c等がある。

【0069】

埋め込み型最上層配線層M9上には、パッド層層間絶縁膜9があり、この上面(およびスルーホール)には、非埋め込み型アルミニウム系パッドメタル層APの一部として、占有率調整用ダミーパターン28、アルミニウム系ボンディングパッド6、アルミニウム系シールリング20a等が設けられている。パッド層層間絶縁膜9等の上には、ファイナルパッシベーション膜11が形成されており、各アルミニウム系ボンディングパッド6上には、パッド開口7が設けられている。

【0070】

次に、図4のVssリング切り出し領域の拡大平面図を図6に示す(ここでは、Vssリング36gについて、具体的に説明するが、Vddリング36dについても全く同一である)。図6に示すように、Vssリング36gには、たとえば一定に長さと幅を持ってほぼ等間隔で配置されたスリット37が設けられている。これは、メタルCMP(Chemical Mechanical Polishing)等による処理の際のディッシングを防止するためである。このスリット37の幅としては、たとえば1マイクロメートル程度、長さとしては、たとえば20から30マイクロメートル程度が好適なものとして例示することができる。この例では、Vssリング36gの幅は、一例として、20マイクロメートル程度とする。ここでは、一定に長さと幅を持ったスリット37の例を示したが、スリットの形状および寸法は、リングに沿った電流の流れを阻害しない形状であれば、どんなものでもよく、一定周期を持つ必要は特にない。ただし、ディッシング防止の観点から必然的に幅方向に周期性を持つことが自然である。

【0071】

次に、図6のA−B断面を上層も含めて、図7に示す。図7に示すように、この断面に於いては、Vssリング36gは、幅方向に多数個に分割されている。また、上層にあるのは、占有率調整用ダミーパターン28である。

【0072】

3.本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等の説明(主に図8から図10)

このセクションでは、本願の前記一実施の形態の半導体集積回路装置の構造等をその要部デバイス構造を中心に説明する。ここで、通常、下地メタルパッドは、例えば図8に示すように、その直下でビアを介して下層の配線に接続されるか、一体となった同層の配線を介して下層の配線等に接続されているが、図9および図10(図19および図20に於いても同じ)においては、図示が煩雑になるので、これらのビアおよび一体となった同層の配線は図示しない。

【0073】

なお、ここでは、P型単結晶シリコン基板上に形成されたCMOS(Complementary Metal Oxide Semiconductor)型の回路構成を有するデバイスを例にとり、具体的に説明するが、その他の基板上に作られたデバイスまたは、同様の基板に作られた他の回路構成のデバイスでもよいことはいうまでもない。

【0074】

図8は本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明するためのデバイス模式断面図である。図9は図8のアルミニウム系主ボンディングパッド膜6x,6yにほぼ対応するパッド周辺拡大上面図である。図10は図9のC−D断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明する。

【0075】

まず、図1および図2で説明した配線構造等のより具体的な形態を図8に基づいて説明する。図8に示すように、P型単結晶シリコン基板部1sのデバイス面1a(第1の主面)側には、N型ウエル領域NWおよびP型ウエル領域PWが設けられており、これとP型単結晶シリコン基板部1sの表面領域に設けられた素子分離フィールド絶縁膜10とともに、MISFET(Qn,Qp)等の能動素子を形成される半導体領域を区画している。各N型ウエル領域NWの半導体表面領域には、P型ソースドレイン領域PSDが設けられており、各P型ウエル領域PWの半導体表面領域には、N型ソースドレイン領域NSDが設けられている。また、各ソースドレイン領域NSD,PSDが設けられた基板部1sの半導体表面上には、たとえばゲート絶縁膜を介して、ゲート電極8が設けられている。なお、実際のソースドレイン構造、ゲート電極およびその周辺構造は、もっと複雑であるが、ここでは詳細構造を省略する。

【0076】

P型単結晶シリコン基板部1sの表面上には、ゲート電極8を被うように、プリメタル層間絶縁膜5が設けられており、この中に、タングステンプラグ3が埋め込まれている。プリメタル層間絶縁膜5上には、埋め込み型第1配線層M1から埋め込み型第8配線層M8の銅埋め込み配線(中層および下層銅埋め込み配線CML)が設けられており、埋め込み型第1配線層M1は、たとえばシングルダマシン(Single Damascene)方式で作られており、埋め込み型第2配線層M2から埋め込み型第8配線層M8は、たとえばデュアルダマシン方式で作られている。

【0077】

埋め込み型第8配線層M8上には、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)中に埋め込まれた埋め込み型最上層配線層M9(たとえば、デュアルダマシン方式による銅系埋め込み配線)が設けられている。この埋め込み型最上層配線層M9の一部として、下地メタルパッド12xとしての最上層銅埋め込み配線等93x(配線、ビア等)および、その一部を下地メタルパッド12yとする最上層銅埋め込み配線等(配線、ビア等)93yが設けられている。ここで、埋め込み型第1配線層M1から埋め込み型最上層配線層M9までの層間絶縁膜をまとめて埋め込み型多層配線層層間絶縁膜ILDとする。

【0078】

埋め込み配線最上層層間絶縁膜16上には、非埋め込み型アルミニウム系パッドメタル層APが設けられている。この非埋め込み型アルミニウム系パッドメタル層APは、下層のパッド層層間絶縁膜9、パッド層層間絶縁膜9に開口されたスルーホール中およびその周辺に形成されたアルミニウム系ボンディングパッド6x(例えば、信号パッド)、アルミニウム系ボンディングパッド6y(たとえば、電源パッド又は接地パッド)等を有している。そして、チップ2の最上部には、ファイナルパッシベーション膜11が設けられており、ファイナルパッシベーション膜11の内、各アルミニウム系ボンディングパッド6x、6y上にあたる部分には、パッド開口7が設けられている。なお、ファイナルパッシベーション膜11上に更にレジン層(たとえば、樹脂封止パッケージの場合)や再配線層(たとえばウエハれべりパッケージの場合)を形成しても良い。

【0079】

この例では、各アルミニウム系ボンディングパッド6x、6yは、間に、タングステンプラグ等の中間接続体を介することなく、直接、下地メタルパッド12x,12yと接続されている。なお、中間にタングステンプラグ等を介することも可能であるが、中間にタングステンプラグ等を介さない場合は、その分、構造が簡単になる。

【0080】

次に、アルミニウム系ボンディングパッド6(6x、6y)の詳細構造を図9および図10に基づいて説明する。図9および図10に示すように、この例では、アルミニウム系ボンディングパッド6と下地メタルパッド12(12x、12y)の中心ほぼ一致しており、形状および寸法もほぼ同じである。なお、必ずしも、このようにする必要はないが、このようにすることによって、チップ面積を増加させることなく、構造的強度が増加させることができる等のメリットがある。ここで、パッド開口7の外周の位置は、アルミニウム系ボンディングパッド6の外周よりも、若干内側とすることが望ましい。また、パッドコンタクト用スルーホール39の外周の位置は、パッド開口7の外周の位置よりも、若干内側とすることが望ましい(パッドコンタクト用スルーホール39の外周の位置とパッド開口7の外周の位置をほぼ同じ位置とすることもできる)。

【0081】

なお、図9および図10に関して、主要な部分の寸法の一例を示すとすれば以下のごとくである。すなわち、アルミニウム系ボンディングパッド6の厚さは、たとえば1000nm程度、下地メタルパッド12の厚さは、たとえば900程度、アルミニウム系ボンディングパッド6の平面寸法は、たとえば、60x100マイクロメートル程度、パッド開口7の平面寸法は、たとえば、50x90マイクロメートル程度、スルーホール39の平面寸法は、たとえば、40x80マイクロメートル程度である。

【0082】

4.本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等の説明(主に図11から図18)

このセクションでは、セクション1から3の主要なデバイス構造に対する製造方法の一例を示すが、前記構造は、以下に示す以外の製法によっても構成できることは言うまでもない。

【0083】

図11は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第7配線層M7完成時点)である。図12は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第8配線層M8完成時点)である。図13は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型最上層配線層M9完成時点)である。図14は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(パッドコンタクト用スルーホール39完成時点)である。図15は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(アルミニウム系ボンディングパッド加工完成時点)である。図16は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ファイナルパッシベーション膜のパッド開口加工完成時点)である。図17は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ワイヤボンディング完成時点)である。図18は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(樹脂モールド完成時点)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明する。

【0084】

埋め込み型第6配線層M6までにBEOL工程は、周知のダマシン工程と同じであるので、埋め込み型第7配線層M7に対応する工程から図11を用いて説明する。図11に示すように、ウエハ1上のデバイス面1a(第1の主面)側において、下層銅埋め込み配線等CL(配線、ビア等)を有する埋め込み型第1配線層M1から埋め込み型第6配線層M6上に、たとえばCVD(Chemical Vapor Deposition)によりセミグローバル下層配線層層間絶縁膜19を形成する。次に、通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、第7層銅埋め込み配線73を形成する。

【0085】

次に、図12に示すように、セミグローバル下層配線層層間絶縁膜19上に、たとえばCVDによりセミグローバル上層配線層層間絶縁膜18を形成する。次に、たとえば通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、第8層銅埋め込み配線83を形成する。

【0086】

次に、図13に示すように、中層銅埋め込み配線等CM(配線、ビア等)を有する埋め込み型第7配線層M7および埋め込み型第8配線層M8上に、たとえばCVDにより埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)を形成する。次に、たとえば通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、最上層銅埋め込み配線等93(配線、ビア等)を形成する。

【0087】

次に、図14に示すように、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)上に、たとえばCVDによりパッド層層間絶縁膜9を成膜し、たとえば通常のリソグラフィにより下地メタルパッド12x,12y上に、パッドコンタクト用スルーホール39(39x,39y)を開口する。

【0088】

次に、図15に示すように、パッドコンタクト用スルーホール39(39x,39y)を含むパッド層層間絶縁膜9の上面のほぼ全面に、たとえば、反応性スパッタリング成膜により、TiN膜を成膜して、続いて、たとえば、スパッタリング成膜により、アルミニウム系メタル膜(アルミニウムを主成分とするメタル膜)を形成する。この複合膜をたとえば、通常のリソグラフィにより形成したレジスト膜をマスクとして、例えばドライエッチングによりパターニングすることにより、アルミニウム系ボンディングパッド6(6x,6y)を形成する。

【0089】

次に、図16に示すように、パッド層層間絶縁膜9およびアルミニウム系ボンディングパッド6(6x,6y)上のほぼ全面に、たとえばCVDによりファイナルパッシベーション膜11を成膜する。次に、たとえば通常のリソグラフィにより、パッド開口7を開口する。

【0090】

その後、必要に応じて、バックグラインディングやプローブテストを実行した後、ダイシング等により、ウエハ1を個々のチップ2に分離する。

【0091】

その後、個々のチップ2を図17以降に示すように加工する。すなわち、図17に示すように、各アルミニウム系ボンディングパッド6x,6yと外部のリード等の間を、金線(ボンディングワイヤ40)等を用いて、例えば、ボール&ウエッジボンディング等により、相互接続する。このとき、通常、アルミニウム系ボンディングパッド6x,6yの側をボールボンディング(ボンディングボール40bを形成するボンディング)するが、これに限らず、必要に応じて、アルミニウム系ボンディングパッド6x,6yの側をウエッジボンディングしても良い。

【0092】

次に、図18に示すように、ファイナルパッシベーション膜11、各アルミニウム系ボンディングパッド6x,6yおよびボンディングワイヤ40等を被覆するように、たとえば、エポキシ系封止樹脂を用いたトランスファーモールド等により、チップ2の表面1a(必要に応じてチップ2全体を封止してもよい)に封止樹脂層42を形成する。

【0093】

5.本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例の説明(主に図19および図20)

このセクションでは、セクション3(図9および図10)で説明したパッド周辺構造(「単一スルーホール接続」という)の変形例の一例を示す。このセクションの方式を「スルーホールリング接続」という。

【0094】

図19は本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明するための図9に対応するパッド周辺拡大上面図である。図20は図19のC−D断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明する。

【0095】

図19および図20に示すように、スルーホールリング接続では、多数のパッドコンタクト用スルーホール39から構成されたスルーホールリング41を介して、アルミニウム系ボンディングパッド6と下地メタルパッド12を相互接続している。パッドコンタクト用スルーホール39の個々の寸法は、たとえば、3x3マイクロメートル程度を好適なものの一例として提示することができる。他の寸法は、単一スルーホール接続について示したものとほぼ同じである。ここで、スルーホールリング41の外周の寸法は、単一スルーホール接続についての単一スルーホール39の外周に対応させればよい。

【0096】

ここで、単一スルーホール接続とスルーホールリング接続を比較すると、以下のようになる。すなわち、単一スルーホール接続では、ボンディングパッドが盆地状になっているので、プローブ特性は良好であるが、平坦部分が狭いのでワイヤボンディング特性は相対的に劣る。一方、スルーホールリング接続では、平坦部分が広いので、ワイヤボンディング特性は相対的に良好であるが、プローブ特性は相対的に劣る。

【0097】

6.アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等の説明(主に図21)

このセクションでは、図3に示した占有率調整用ダミーパターンの一つの変形例を説明するとともに、これをMIMキャパシタとして利用する可能性を説明する。すなわち、占有率調整用ダミーパターンは、図3や図21に示すものばかりでなく、一定の占有率を均一に達成できるものであれば、種々変形可能である。また、他の素子としての利用も、キャパシタに限らず、インダクタンス、アンテナ、抵抗素子、その他としても可能である。

【0098】

図21はアルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明するための図3に対応するチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。これに基づいて、アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明する。

【0099】

図21は、図3に対応する非埋め込み型アルミニウム系パッドメタル層APの平面レイアウトの変形例である。図3と異なっているのは、図3に於いては、ドット状の占有率調整用ダミーパターン28となっていたところを、図21では、同層メタル櫛形MIMキャパシタ39(一対の同層メタルキャパシタ電極)としたところである。なお、このパターンは、同層メタル櫛形MIMキャパシタ39としてではなく、線形占有率調整用ダミーパターンとしても使用することができる。また、同層メタル櫛形MIMキャパシタの一対の同層メタルキャパシタ電極であると同時に線形占有率調整用ダミーパターンとしても使用することができる。

【0100】

7.前記各実施の形態等(変形例を含む)に関する予備的説明および一般的考察

このセクションでは、前記各実施の形態(変形例を含む)に関する予備的説明および一般的考察を行う。

【0101】

図22はアンテナ比の大きなウエハと、アンテナ比の小さなウエハに対して、プラズマ処理を施したサンプルについてのMISFETのソースドレイン電流(Ids)および閾値電圧(Vth)の分布を示すデータプロット図である。これは、ゲート酸化膜厚が、7.5nm程度のNチャネル型MOSFETについて、室温で測定した結果である。ソースドレイン電流は、ドレイン電圧およびゲート電圧がともに3.3ボルトの時の値である。

【0102】

非埋め込み型アルミニウム系パッドメタル層AP(図3)は、通常、パッド等の非配線パターンとともに、電源配線、信号配線等の配線パターン(または単に「配線」)を含むことが多い。これは、各配線層の利用度を高めるという一般的な要請に対応している。しかし、本発明者が検討したところによると、最上層メタル層である非埋め込み型アルミニウム系パッドメタル層APは、通常、ドライエッチングで加工されるので、プラズマダメージを受けやすいという問題がある。特に、全部の配線が接続された状態にあるこのステージに於いては、一般にアンテナ比が大きくなりやすく、半導体基板や素子(MISFET等の能動素子等)に接続されたものを含みやすい電源配線、信号配線等の配線パターンの存在は、デバイスの信頼性や性能の劣化を招く恐れがある。この傾向は、直接、MISFET等の能動素子の端子に接続される可能性の高い信号配線では、特に顕著である。また、電源配線は、アンテナ比が特に大きくなりやすい。以上の点は、たとえば、図22の見ると、理解することができる。すなわち、アンテナ比が相対的に小さいチップ内配線レイアウトを有するウエハでは、プロットは、ソースドレイン電流の目標値と閾値電圧の目標値を示す直線の交点近傍に分布するが、アンテナ比が相対的に大きなチップ内配線レイアウトを有するウエハでは、ソースドレイン電流に関しては、低めにシフトしており、閾値電圧に関しては、高めにシフトしているのがわかる。

【0103】

また、一般的な設計手法(「一般的設計手法」)では、最上層メタル層の一部として、接地リング、Vssリング、Vccリング等の電源リング(電源幹配線)を配置する。しかし、このような大面積且つ大寸法(差渡しサイズが大きい)のメタル図形を配置することは、プラズマダメージに関して問題であるばかりでなく、メタル層とその上のファイナルパッシベーション膜との間の物理的特性の相違に起因するクラックの発生等を招く恐れがある。

【0104】

これに対して、前記実施の形態に於いては、最上層メタル層(最上層非埋め込みメタル層)は、できるだけ非配線パターンにだけ使用するようにして、アンテナ比が大きくなりやすい信号配線、アンテナ比または幅(面積)等が大きくなりやすい電源リング(電源幹配線)その他の電源配線を直下の層、すなわち、埋め込み配線の内の最上層埋め込み配線層に移したものである。もちろん、全ての配線を下層に移すことが望ましいが、一部の比較的アンテナ比の小さな配線を最上層非埋め込みメタル層に残すこともできる(このことは以下に於いても同じ)。

【0105】

また、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、電源リング(電源幹配線)と信号配線を下層に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に電源リングおよび信号配線を有さない。なお、このとき、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、実質的に全ての配線を下層(たとえば、最上層埋め込み配線層)に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に配線を有さない。

【0106】

なお、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、主に電源リング(電源幹配線)を下層(たとえば、最上層埋め込み配線層)に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に電源リング(電源リング配線)を有さない。

【0107】

更に、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、幾つかの部分を移す先の埋め込み配線層(「移送先配線層」という)は、直下の埋め込み配線の内の最上層埋め込み配線層にすることがレイアウト上有利であるが、その他の層(主にセミグローバル配線のうちの1層または2層)に移すことも可能である。移送先配線層を最上層埋め込み配線層にすることは、もっとも好適である。これは、最上層埋め込み配線層は、他の配線層に比べて、配線の断面積が圧倒的に大きいので、一般に電流量の大きいアルミニウム系配線(特に電源配線リング等の電源配線)の代替配線層として好適だからである。

【0108】

更に、このように機械強度が強い最上層埋め込み配線層で下地メタルパッドを作ることが必須ではないが、設けることによって、アルミニウム系主ボンディングパッド膜およびその周辺の機械的強度を改善することができる。

【0109】

8.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0110】

例えば、前記実施の形態では、主に銅系埋め込み配線について具体的に説明したが、本発明はそれに限定されるものではなく、銀系埋め込み配線のその他のメタル系埋め込み配線にも適用できることは言うまでもない。

【0111】

また、銅に対するバリアメタルとして、窒化タンタル系バリアメタルを例にとり具体的に説明したが、本発明はそれに限定されるものではなく、窒化チタン系バリアメタル(Ti/TiNの多層バリアを含む)、ルテニウム系バリアメタル等のその他のバリアメタルでも良いことは、言うまでもない。また、ここでは、TaN膜単層のバリアメタルの例をとり具体的に説明したが、本発明はそれに限定されるものではなく、Ta/TaNの多層バリアでも良いことは、言うまでもない。

【0112】

更に、絶縁性銅拡散バリア膜として、主にSiC,SiN等を用いた例を具体的に説明したが、本発明はそれに限定されるものではなく、SiCN等、その他の膜であってもよいことは言うまでもない。

【符号の説明】

【0113】

1 半導体ウエハ

1a 基板又はウエハのデバイス面(第1の主面)

1b 基板又はウエハの裏面(第2の主面)

1s 基板又はウエハのP型単結晶シリコン基板部

2 半導体基板又は集積回路チップ(半導体チップ領域)

3 タングステンプラグ

4 窒化シリコンライナー膜(エッチストップ膜)

5 プリメタル層間絶縁膜

6,6x,6y アルミニウム系ボンディングパッド

6a アルミニウム系主ボンディングパッド膜

6b 窒化チタン系パッドバリアメタル膜

7 (ファイナルパッシベーション膜の)パッド開口

8 ゲート電極

9 パッド層層間絶縁膜

9a プラズマTEOS系主層間絶縁膜

9b SiN系絶縁性バリア膜

10 素子分離フィールド絶縁膜

11 ファイナルパッシベーション膜

11a USG系ファイナルパッシベーション膜

11b SiN系ファイナルパッシベーション膜

12,12x,12y 下地メタルパッド

13 埋め込まれた銅配線

14 SiC系絶縁性バリア膜

15 プラズマTEOS系主層間絶縁膜

16 埋め込み配線最上層層間絶縁膜(グローバル配線層層間絶縁膜)

18 セミグローバル上層配線層層間絶縁膜

19 セミグローバル下層配線層層間絶縁膜

20a アルミニウム系シールリング

20b 銅系シールリング

21 ローカル最上層配線層層間絶縁膜

22a アルミニウム系パッドリング

22b 銅系パッドリング

23 銅埋め込み配線

24 SiC系絶縁性バリア膜

25 SiOC系主層間絶縁膜

26 チップ内部回路形成領域

27 ダイシング領域(スクライブ領域)

28 占有率調整用ダミーパターン

29a アルミニウム系TEGパターン

29b 銅系TEGパターン

30a アルミニウム系レーザートリム用位置決め基準パターン

31a アルミニウム系膜厚モニタ

31b 銅系膜厚モニタ

32a アルミニウム系露光用アライメントパターン

32b 銅系露光用アライメントパターン

33 銅埋め込み配線

34 SiC系絶縁性バリア膜

35 SiOC系主層間絶縁膜

36 電源リング(電源幹配線)

36d Vddリング(電源供給リング)

36g Vssリング(接地リング)

37 スリット

38 同層メタル櫛形MIMキャパシタ

39,39x,39y パッドコンタクト用スルーホール

40 ボンディングワイヤ

40b ボンディングボール

41 スルーホールリング

42 封止樹脂(封止樹脂層)

43 銅埋め込み配線

44 SiC系絶縁性バリア膜

45 SiOC系主層間絶縁膜

53 銅埋め込み配線

54 SiC系絶縁性バリア膜

55 SiOC系主層間絶縁膜

63 銅埋め込み配線

63a 埋め込み型第6配線層銅系メタル膜

63b 窒化タンタル系バリアメタル膜

64 SiC系絶縁性バリア膜

65 SiOC系主層間絶縁膜

73 第7層銅埋め込み配線

74 SiC系絶縁性バリア膜

75a プラズマTEOS系主層間絶縁膜

75b FSG系主層間絶縁膜

75c プラズマTEOS系キャップ膜

83 第8層銅埋め込み配線

84 SiC系絶縁性バリア膜

85a プラズマTEOS系主層間絶縁膜

85b FSG系主層間絶縁膜

85c プラズマTEOS系キャップ膜

93,93x,93y 最上層銅埋め込み配線等(配線、ビア等)

93a 最上層銅埋め込み配線銅系メタル膜

93b 窒化タンタル系バリアメタル膜

94a SiN系絶縁性バリア膜

94b SiC系絶縁性バリア膜

95a プラズマTEOS系主層間絶縁膜

95b プラズマTEOS系主層間絶縁膜

AP 非埋め込み型アルミニウム系パッドメタル層

CM 中層銅埋め込み配線等(配線、ビア等)

CML 中層および下層銅埋め込み配線等(配線、ビア等)

CL 下層銅埋め込み配線等(配線、ビア等)

DW 埋め込み型多層配線層

ILD 埋め込み型多層配線層層間絶縁膜

M1 埋め込み型第1配線層

M2 埋め込み型第2配線層

M3 埋め込み型第3配線層

M4 埋め込み型第4配線層

M5 埋め込み型第5配線層

M6 埋め込み型第6配線層

M7 埋め込み型第7配線層

M8 埋め込み型第8配線層

M9 埋め込み型第9配線層(埋め込み型最上層配線層)

NSD N型ソースドレイン領域

NW N型ウエル領域

PM プリメタル領域

PSD P型ソースドレイン領域

PW P型ウエル領域

Qn Nチャネル型MISFET

Qp Pチャネル型MISFET

R1 Vssリング切り出し領域

【技術分野】

【0001】

本発明は、半導体集積回路装置(または半導体装置)における配線およびボンディングパッド等構造技術に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2011−114049号公報(特許文献1)には、メモリ系半導体集積回路デバイスに於いて、アルミニウム系パッド層を除き、全ての配線層を銅配線とした配線層構成が開示されている。

【0003】

日本特開2011−129722号公報(特許文献2)には、多層の銅配線の上に、アルミニウム系パッド(ボンディングパッドおよびシールリング上のパッドを含む)を形成した半導体集積回路デバイスが開示されている。

【0004】

日本特開2011−9581号公報(特許文献3)または、これに対応する米国特許公開2010−330799号公報(特許文献4)には、銅埋め込み配線の最上層上にタングステンプラグ等の中継メタル部材を介せずに、アルミニウム系パッドを形成し、このボンディングパッドにボンディングワイヤを接続した半導体集積回路デバイスが開示されている。

【0005】

日本特開2010−147267号公報(特許文献5)には、アルミニウム系パッド層上に、再配線を形成したウエハレベルパッケージ(Wafer Level Package)方式の半導体集積回路デバイスに於いて、アルミニウム系パッド層を銅ダマシン配線の最上層のメタル配線として使用する他、同層をパッド専用とすることが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2011−114049号公報

【特許文献2】特開2011−129722号公報

【特許文献3】特開2011−9581号公報

【特許文献4】米国特許公開2010−330799号公報

【特許文献5】特開2010−147267号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。また、アルミニウム系パッド層に、このような一般相互接続配線がない場合に於いても、幅の広くチップサイズと同程度の寸法を有する電源リング等の電源幹配線等の存在は、これとファイナルパッシベーション膜との物理的性質の相違に基づく、クラック等の発生の原因になりやすい等の問題がある。

【0008】

本願発明は、これらの課題を解決するためになされたものである。

【0009】

本発明の目的は、信頼性の高い半導体集積回路装置を提供することにある。

【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0012】

すなわち、本願の一つの発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

【発明の効果】

【0013】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0014】

すなわち、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものとすることによって、信頼性の高い半導体集積回路装置とすることができる。

【図面の簡単な説明】

【0015】

【図1】本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明するためのメタル配線システム等のデバイス模式断面図である。

【図2】図1のチップ表面から埋め込み型第6配線層M6までのより詳細なデバイス模式断面図である。

【図3】本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。

【図4】本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(埋め込み型最上層配線層を中心に表示)である。

【図5】図3および図4のX−X’断面の実線部分に対応するチップ(ウエハのチップ領域およびその周辺)のデバイス模式断面図である。

【図6】図4のVssリング切り出し領域R1の電源リングの詳細レイアウト図である。

【図7】図6のA−B断面のデバイス模式断面図である。

【図8】本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明するためのデバイス模式断面図である。

【図9】図8のアルミニウム系主ボンディングパッド膜6x,6yにほぼ対応するパッド周辺拡大上面図である。

【図10】図9のC−D断面のデバイス模式断面図である。

【図11】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第7配線層M7完成時点)である。

【図12】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第8配線層M8完成時点)である。

【図13】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型最上層配線層M9完成時点)である。

【図14】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(パッドコンタクト用スルーホール39完成時点)である。

【図15】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(アルミニウム系ボンディングパッド加工完成時点)である。

【図16】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ファイナルパッシベーション膜のパッド開口加工完成時点)である。

【図17】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ワイヤボンディング完成時点)である。

【図18】本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(樹脂モールド完成時点)である。

【図19】本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明するための図9に対応するパッド周辺拡大上面図である。

【図20】図19のC−D断面のデバイス模式断面図である。

【図21】アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明するための図3に対応するチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。

【図22】アンテナ比の大きなウエハと、アンテナ比の小さなウエハに対して、プラズマ処理を施したサンプルについてのMISFETのソースドレイン電流および閾値電圧の分布を示すデータプロット図である。

【発明を実施するための形態】

【0016】

〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

【0017】

1.以下を含む半導体集積回路装置:

(a)第1の主面を有する半導体基板;

(b)前記半導体基板の前記第1の主面に設けられた複数のMISFET;

(c)前記半導体基板の前記第1の主面および前記複数のMISFETの上方に設けられた埋め込み型多層配線層;

(d)前記埋め込み型多層配線層上に設けられた非埋め込み型アルミニウム系パッドメタル層;

(e)前記非埋め込み型アルミニウム系パッドメタル層の一部として設けられた複数のメタルボンディングパッド;

(f)前記非埋め込み型アルミニウム系パッドメタル層よりも上層に形成されたファイナルパッシベーション膜;

(g)前記複数のメタルボンディングパッドの各々の上方の前記ファイナルパッシベーション膜に設けられたパッド開口、

ここで、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しない。

【0018】

2.前記1項の半導体集積回路装置において、更に以下を含む:

(h)前記埋め込み型多層配線層の内の埋め込み型最上層配線層の一部として設けられた電源リング配線。

【0019】

3.前記2項の半導体集積回路装置において、更に以下を含む:

(i)前記電源リング配線内に設けられたディッシング防止用スリット。

【0020】

4.前記2または3項の半導体集積回路装置において、前記複数のメタルボンディングパッドの各々は、プラグを介することなく、前記埋め込み型最上層配線層に接続されている。

【0021】

5.前記2から4項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(j)前記複数のメタルボンディングパッドの各々の下方に、前記埋め込み型最上層配線層の一部として設けられ、その上方のメタルボンディングパッドと形状および面積がほぼ同様の下地メタルパッド。

【0022】

6.前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた単一のスルーホール。

【0023】

7.前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた複数のスルーホール。

【0024】

8.前記1から7項のいずれか一つの半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に配線を有しない。

【0025】

9.前記1から8項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(m)前記第1の主面の内部領域に、前記非埋め込み型アルミニウム系パッドメタル層の一部として、ほぼ均一に分布するように設けられた多数の占有率調整用ダミーパターン。

【0026】

10.前記1から9項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(n)前記第1の主面の外周に沿って、前記非埋め込み型アルミニウム系パッドメタル層の一部として、アルミニウム系シールリング。

【0027】

11.前記1から10項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(p)前記複数のメタルボンディングパッドの各々の上面に接続されたボンディングワイヤ。

【0028】

12.前記1から11項のいずれか一つの半導体集積回路装置において、更に以下を含む:

(q)前記ファイナルパッシベーション膜上を被う封止樹脂層。

【0029】

13.前記1から12項のいずれか一つの半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に信号配線を有しない。

【0030】

14.前記10から13項のいずれか一つの半導体集積回路装置において、前記複数のメタルボンディングパッドは、アルミニウム系シールリングに沿うように、その内側に、リング状に配列されている。

【0031】

15.前記1から14項のいずれか一つの半導体集積回路装置において、前記埋め込み型多層配線層は、銅系埋め込み型多層配線層である。

【0032】

〔本願における記載形式、基本的用語、用法の説明〕

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0033】

更に、本願において、「半導体装置」または「半導体集積回路装置」というときは、主に、各種トランジスタ(能動素子)単体、および、それらを中心に、抵抗、コンデンサ等を半導体チップ等(たとえば単結晶シリコン基板)上に集積したものをいう。ここで、各種トランジスタの代表的なものとしては、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)に代表されるMISFET(Metal Insulator Semiconductor Field Effect Transistor)を例示することができる。このとき、集積回路構成の代表的なものとしては、Nチャネル型MISFETとPチャネル型MISFETを組み合わせたCMOS(Complemetary Metal Oxide Semiconductor)型集積回路に代表されるCMIS(Complemetary Metal Insulator Semiconductor)型集積回路を例示することができる。

【0034】

今日の半導体集積回路装置、すなわち、LSI(Large Scale Integration)のウエハ工程は、通常、原材料としてのシリコンウエハの搬入からプリメタル(Premetal)工程(M1配線層下端とゲート電極構造の間の層間絶縁膜等の形成、コンタクトホール形成、タングステンプラグ、埋め込み等からなる工程)あたりまでのFEOL(Front End of Line)工程と、M1配線層形成から始まり、アルミニウム系パッド電極上のファイナルパッシベーション膜へのパッド開口の形成あたりまで(ウエハレベルパッケージプロセスにおいては、当該プロセスも含む)のBEOL(Back End of Line)工程に大別できる。

【0035】

2.同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といっても、特にそうでない旨明示した場合および文脈から明らかに、そうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といっても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。同様に、「酸化シリコン膜」、「酸化シリコン系絶縁膜」等と言っても、比較的純粋な非ドープ酸化シリコン(Undoped Silicon Dioxide)だけでなく、FSG(Fluorosilicate Glass)、TEOSベース酸化シリコン(TEOS-based silicon oxide)、SiOC(Silicon Oxicarbide)またはカーボンドープ酸化シリコン(Carbon-doped Silicon oxide)またはOSG(Organosilicate glass)、PSG(Phosphorus Silicate Glass)、BPSG(Borophosphosilicate Glass)等の熱酸化膜、CVD酸化膜、SOG(Spin ON Glass)、ナノクラスタリングシリカ(Nano-Clustering Silica:NCS)等の塗布系酸化シリコン、これらと同様な部材に空孔を導入したシリカ系Low-k絶縁膜(ポーラス系絶縁膜)、およびこれらを主要な構成要素とする他のシリコン系絶縁膜との複合膜等を含むことは言うまでもない。

【0036】

また、酸化シリコン系絶縁膜と並んで、半導体分野で常用されているシリコン系絶縁膜としては、窒化シリコン系絶縁膜がある。この系統の属する材料としては、SiN,SiCN,SiNH,SiCNH等がある。ここで、「窒化シリコン」というときは、特にそうでない旨明示したときを除き、SiNおよびSiNHの両方を含む。同様に、「SiCN」というときは、特にそうでない旨明示したときを除き、SiCNおよびSiCNHの両方を含む。

【0037】

なお、SiCは、SiNと類似の性質を有するが、SiONは、むしろ、酸化シリコン系絶縁膜に分類すべき場合が多い。

【0038】

窒化シリコン膜は、SAC(Self−Aligned Contact)技術におけるエッチストップ膜、すなわち、CESL(Contact Etch−Stop Layer)として、多用されるほか、SMT(Stress Memorization Technique)における応力付与膜としても使用される。

【0039】

3.同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0040】

4.さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

【0041】

5.「ウエハ」というときは、通常は半導体集積回路装置(半導体装置、電子装置も同じ)をその上に形成する単結晶シリコンウエハを指すが、エピタキシャルウエハ、SOI基板、LCDガラス基板等の絶縁基板と半導体層等の複合ウエハ等も含むことは言うまでもない。

【0042】

6.本願に於いて、「リング」というときは、主に略矩形環状の図形を指す。しかし、「環状」といっても、必ずしも閉じている必要はない。具体的には、シールリング、電源リング、パッドリング、スルーホールリング等がある。シールリングは、一般に閉リングであるが、電源リングは、見かけ上は、ほぼ閉リング(厳密な平リングのこともある)であるが、厳密に言うと、一部が開いた開リングであることが多い。パッドリング、スルーホールリング等は、ドット状のパターン群が全体としてリング状に配列されたものである。

【0043】

なお、本願に於いて、「ボンディングパッド」というときは、ワイヤボンディングのためのパッドの外、その上に、バンプ電極や再配線を形成するものも含むこととする。

【0044】

7.本願に於いて、「メタルパターン」は、「配線パターン」と「非配線パターン」に分類される。「配線パターン」または「配線」とは、端子(または素子)と素子間を相互に繋ぐメタル電流通路であり、主に電流を流すことを主要な目的とするものである。「非配線パターン」には、素子パターン、パッドパターン、テストパターン、合わせパターン、ダミーパターン等が含まれる。「配線」は、電源リング(接地リング、Vddリング)等の電源幹配線その他の「電源配線」と「信号配線」に分類される。また、その幾何学的な用途から、以下のような分類も用いられる。すなわち、主に回路モジュール間の相互接続等に利用される「セミグローバル配線」(以下の実施の形態では、たとえば、埋め込み型第7、8配線層)、より広い範囲の接続等に使用される「グローバル配線」(以下の実施の形態では、たとえば、埋め込み型最上層配線層)、主に回路モジュール内の相互接続等に利用される「ローカル配線」(以下の実施の形態では、たとえば、埋め込み型第1配線層から埋め込み型第6配線層)等に分類される。

【0045】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0046】

また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するために、ハッチングを付すことがある。

【0047】

1.本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインの説明(主に図1および図2)

このセクションでは、本願の一実施の形態の半導体集積回路装置の構造をメタル配線システム全体から概説する。

【0048】

以下では、65nmテクノロジノードのデバイスの例に取り具体的に説明するが、以下の例は、これに限定されるものではなく、これよりも微細なテクノロジノードのデバイスにも適用できるし、これよりも微細でないテクノロジノードのデバイスにも適用できることは言うまでもない。

【0049】

また、以下では、埋め込み型配線9層およびアルミニウム系非埋め込み配線(メタル層)1層のメタル配線系を例にとり、具体的に説明するが、これ以外の層数の配線系でも良いことは言うまでもない。

【0050】

図1は本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明するためのメタル配線システム等のデバイス模式断面図である。図2は図1のチップ表面から埋め込み型第6配線層M6までのより詳細なデバイス模式断面図である。これらに基づいて、本願の一実施の形態の半導体集積回路装置におけるメタル配線システム等のアウトラインを説明する。

【0051】

図1に示すように、たとえば、STI(Shallow Trench Isolation)型の素子分離フィールド絶縁膜10で分離されたP型単結晶シリコン基板1sのデバイス面1a(裏面1bの反対側の面)上には、PチャネルMOSFETまたはNチャネルMOSFETのゲート電極8が形成されている。それらの上には、エッチストップ膜である窒化シリコンライナー膜4(たとえば約30nm)が形成されている。その上には、たとえば、窒化シリコンライナー膜4よりもずっと厚く、下層の熱CVD法によるオゾンTEOS酸化シリコン膜(たとえば約200nm)および上層のプラズマTEOS酸化シリコン膜(たとえば約270nm)等からなるプリメタル(Premetal)層間絶縁膜5が形成されている。また、これらのプリメタル絶縁膜を貫通して、タングステンプラグ3が形成されている。ここまでがプリメタル領域PMである。

【0052】

その上の第1配線層M1は、たとえば、下層のSiC膜(たとえば約50nm)等の絶縁性バリア膜14および主層間絶縁膜であるプラズマシリコン酸化膜15(たとえば約150nm)等およびそれらに形成された配線溝に埋め込まれた銅配線13等から構成されている。

【0053】

その上の第2配線層から第6配線層M2,M3,M4,M5,M6は、相互にほぼ同様の構造をしている。各層は、たとえば、下層のSiC膜(たとえば約50nm)等からなる絶縁性バリア膜(ライナー膜)24、34,44、54,64、および上層のほとんどの領域を占める主層間絶縁膜25,35,45,55,65等から構成されている。この主層間絶縁膜25,35,45,55,65は、たとえば、カーボンドープ酸化シリコン膜、すなわち、SiOC膜(たとえば約400nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線23,33,43,53,63(たとえば、配線幅150nm程度、配線厚さ200nm程度)が形成されている。なお、第1配線層から第6配線層M1,M2,M3,M4,M5,M6は、たとえば、この例ではローカル配線である。

【0054】

その上の第7配線層から第8配線層M7,M8は、相互にほぼ同様の構造をしている。各層間絶縁膜、すなわち、セミグローバル下層配線層層間絶縁膜19およびセミグローバル上層配線層層間絶縁膜18は、たとえば、最下層のSiC膜(たとえば約70nm)等の絶縁性バリア膜74,84、中下層のプラズマTEOSシリコン酸化膜75a,85a(たとえば約250nm)、中上層のFSG膜75b,85b(たとえば約250nm)、およびキャップ膜であるプラズマTEOSシリコン酸化膜75c,85c(たとえば約100nm)等からなる。これらの層間絶縁膜を貫通して、銅プラグおよび銅配線を含む銅埋め込み配線73,83(たとえば、配線幅200nm程度、配線厚さ350nm程度)が形成されている。なお、この例では、セミグローバル配線を2層としたが、セミグローバル配線の層数は、必要に応じて、3層以上とすることもできるし、1層とすることもできる。

【0055】

その上の第9配線層M9は、たとえば、この例では、グローバル配線層であり、たとえば、以下のような構造をしている。埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)は、下層のSiC膜(たとえば約70nm)等の絶縁性バリア膜94b、中下層のプラズマTEOS系主層間絶縁膜95b(たとえば約800nm)、中上層のSiN系絶縁性バリア膜94a、およびプラズマTEOS系主層間絶縁膜95a(たとえば約900nm)等から構成されている。これらの層間絶縁膜等を貫通等して、銅プラグおよび銅配線を含む銅埋め込み配線93(たとえば、配線幅400nm程度、配線厚さ900nm程度)が形成されている。ここまでが、埋め込み型多層配線層DWである。

【0056】

その上の非埋め込み型アルミニウム系パッドメタル層APの絶縁膜構造は、たとえば、下層のパッド層層間絶縁膜9および上層のファイナルパッシベーション膜から構成されており、その間に、アルミニウム系ボンディングパッド6が形成されている。すなわち、パッド層層間絶縁膜9は、下層のSiN膜9b(たとえば約100nm)等の絶縁性バリア膜、プラズマTEOS系主層間絶縁膜9a(たとえば約900nm)等から構成されている。また、アルミニウム系ボンディングパッド6上には、パッド開口7が設けられている。なお、アルミニウム系ボンディングパッド6下の銅埋め込み配線93は、後に説明するように、下地メタルパッド12でもある。

【0057】

次に、図2を用いて、図1の埋め込み型第6配線層M6およびそれよりも上方の断面構造の詳細を説明する。図2に示すように、埋め込み型第6配線層M6の層間絶縁膜、すなわち、ローカル最上層配線層層間絶縁膜21は、たとえば、下層のSiC系絶縁性バリア膜64、上層のSiOC系主層間絶縁膜65等から構成されており、その中に埋め込まれた銅埋め込み配線63は、たとえば、主要部を占める埋め込み型第6配線層銅系メタル膜63a、その周辺(側面および下面)の窒化タンタル系バリアメタル膜63b等から構成されている。なお、第7層銅埋め込み配線73、第8層銅埋め込み配線83の詳細構造も銅埋め込み配線63とほぼ同じであるので、説明は繰り返さない。また、埋め込み型第7配線層M7および埋め込み型第8配線層M8の構造も、先に図1について説明したところと同じであるので、ここでは説明を繰り返さない。

【0058】

次に、埋め込み型第9配線層M9(埋め込み型最上層配線層)を説明するが、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)の構造は、先に図1について説明したところと同じであるので、ここでは説明を繰り返さず、最上層銅埋め込み配線等93(配線、ビア等)の詳細構造を説明する。これも、先に図1について説明したところと同じであり、たとえば、主要部を占める埋め込み型第9配線層銅系メタル膜93a、その周辺(側面および下面)の窒化タンタル系バリアメタル膜93b等から構成されている。

【0059】

次に、非埋め込み型アルミニウム系パッドメタル層APを説明する。非埋め込み型アルミニウム系パッドメタル層APの層間絶縁膜は、たとえば、下層のパッド層層間絶縁膜9および上層のファイナルパッシベーション膜11から構成されている。パッド層層間絶縁膜9は、たとえば下層のSiN系絶縁性バリア膜9b(たとえば厚さ約100nm程度)および上層のプラズマTEOS系主層間絶縁膜9a(たとえば厚さ約600nm程度)等から構成されている。上層のファイナルパッシベーション膜11は、たとえば下層のUSG(Undoped Silicon Glass)系ファイナルパッシベーション膜11a(たとえば厚さ約900nm程度)および上層のプラズマSiN系ファイナルパッシベーション膜11b(たとえば厚さ約600nm程度)等から構成されている。これらの間には、たとえば下層の窒化チタン系パッドバリアメタル膜6b(たとえば厚さ約100nm程度)およびアルミニウム系主ボンディングパッド膜6a(たとえば厚さ約1000nm程度)等から構成されている。

【0060】

2.本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等の説明(主に図3から図7)

このセクションでは、本願の前記一実施の形態の半導体集積回路装置の構造等を非埋め込み型アルミニウム系パッドメタル層および埋め込み型第9配線層(埋め込み型最上層配線層)の平面レイアウト等を中心に説明する。

【0061】

なお、このセクションでは、便宜上、ウエハ1(たとえば図3)のチップ領域2およびその周辺を説明するが、最終製品としての分離されたチップ2では、ダイシング領域27(スクライブ領域)は、ダイシングブレード等による加工の結果、すでに存在しない。

【0062】

なお、ここでは、チップサイズは、10ミリメートル角程度のものを例に取り具体的に説明する。

【0063】

図3は本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。図4は本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明するためのチプ領域およびその周辺の模式レイアウト図(埋め込み型最上層配線層を中心に表示)である。図5は図3および図4のX−X’断面の実線部分に対応するチップ(ウエハのチップ領域およびその周辺)のデバイス模式断面図である。図6は図4のVssリング切り出し領域R1の電源リングの詳細レイアウト図である。図7は図6のA−B断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置におけるチップ(またはウエハ上のチップ領域周辺)上レイアウト等を説明する。

【0064】

先ず、非埋め込み型アルミニウム系パッドメタル層APの平面レイアウトを図3に基づいて説明する。図3に示すように、非埋め込み型アルミニウム系パッドメタル層APにより構成されているパターンとしては、チップ領域2の外部においては、たとえば、アルミニウム系TEGパターン29a、アルミニウム系レーザートリム用位置決め基準パターン30a、アルミニウム系膜厚モニタ31a、アルミニウム系露光用アライメントパターン32a等がある。一方、チップ領域2の内部においては、外側から、たとえば、耐湿性や強度を確保するためのアルミニウム系シールリング20a、多数のボンディングパッド6から構成されたアルミニウム系パッドリング22a、アルミニウム系パッドリング22aの内側全面に敷き詰められた繰り返しパターン等からなる占有率調整用ダミーパターン28(非埋め込み型アルミニウム系パッドメタル層APの際のドライエッチング特性を確保するためのダミーパターン)がある。ここで、占有率調整用ダミーパターン28は、プラズマダメージ等を回避するためには、フローティングとすることが望ましいが、そのような問題がない場合は、フローティングにしなくても良い。また、アルミニウム系シールリング20aの存在は、チップ周辺からのクラック等の伝播を阻止するのに有効である。

【0065】

ここで、アルミニウム系TEGパターン29aの全体の平面サイズは、たとえば、50x2000マイクロメートル程度である。また、アルミニウム系レーザートリム用位置決め基準パターン30a、アルミニウム系膜厚モニタ31a、およびアルミニウム系露光用アライメントパターン32aの各々のサイズは、たとえば50x100マイクロメートル程度である。更に、アルミニウム系シールリング20aの幅は、たとえば10マイクロメートル程度であり、ボンディングパッド6のサイズとしては、たとえば、60x100マイクロメートル程度である。また、占有率調整用ダミーパターン28を構成する個々の要素パターンのサイズは、たとえば35マイクロメートル角程度であり、その配列ピッチとしては、たとえば、140マイクロメートル程度を好適なものとして例示することができる。ここでは、長方形のボンディングパッド6を具体的に示したが、ボンディングパッド6の平面形状は、長方形に限らず、正方形(寸法は、たとえば60x60マイクロメートル程度)等の他の図形でも良い。

【0066】

なお、占有率調整用ダミーパターン28が形成されている領域の中央部は、通常、チップ内部回路形成領域26と一致している。また、チップ領域のほぼ全体は、その外端部および各ボンディングパッド6の主要部を除き、ファイナルパッシベーション膜11(たとえば、無機系ファイナルパッシベーション膜、ポリイミド膜等の有機系ファイナルパッシベーション膜またはこれらの両方)に覆われている。

【0067】

次に、埋め込み型第9配線層M9(埋め込み型最上層配線層)の平面レイアウトを図4に基づいて説明する。図4に示すように、埋め込み型最上層配線層M9により構成されているパターンとしては、チップ領域2の外部においては、たとえば、銅系TEGパターン29b、銅系膜厚モニタ31b、銅系露光用アライメントパターン32b等がある。一方、チップ領域2の内部においては、外側から、たとえば、耐湿性や強度を確保するための銅系シールリング20b、多数の下地メタルパッド12から構成された銅系パッドリング22b、ほぼリング状の接地幹配線から構成されたVssリング(接地リング36g)およびほぼリング状の電源供給幹配線から構成されたVddリング(電源供給リング36d)等を含む電源リング36(電源幹配線)等がある。電源リング36の内側は、一般に、チップ内部回路形成領域26となっている。なお、複数電圧電源の場合は、電源の種類に対応して、電源供給リングは、複数本となる。

【0068】

次に、図3および図4のX−X’断面(実線部)の構造(主に非埋め込み型アルミニウム系パッドメタル層APおよび埋め込み型最上層配線層M9)を図5に基づいて説明する。図5に示すように、埋め込み型第8配線層M8上に、埋め込み型最上層配線層M9が形成されている。この埋め込み型最上層配線層M9は、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)および、これにデュアルダマシン(Dual Damascene)法等により埋め込まれた銅系配線等から構成されている。この層の銅系配線等としては、たとえばVssリング36g(接地リング)、Vddリング36d(電源供給リング)のほか、各アルミニウム系ボンディングパッド6の直下でこれとコンタクトし、これとほぼ同一の形状、位置、サイズを有する下地メタルパッド12、アルミニウム系シールリング20aの直下にあって、ほぼ同様の働きをする銅系シールリング20c等がある。

【0069】

埋め込み型最上層配線層M9上には、パッド層層間絶縁膜9があり、この上面(およびスルーホール)には、非埋め込み型アルミニウム系パッドメタル層APの一部として、占有率調整用ダミーパターン28、アルミニウム系ボンディングパッド6、アルミニウム系シールリング20a等が設けられている。パッド層層間絶縁膜9等の上には、ファイナルパッシベーション膜11が形成されており、各アルミニウム系ボンディングパッド6上には、パッド開口7が設けられている。

【0070】

次に、図4のVssリング切り出し領域の拡大平面図を図6に示す(ここでは、Vssリング36gについて、具体的に説明するが、Vddリング36dについても全く同一である)。図6に示すように、Vssリング36gには、たとえば一定に長さと幅を持ってほぼ等間隔で配置されたスリット37が設けられている。これは、メタルCMP(Chemical Mechanical Polishing)等による処理の際のディッシングを防止するためである。このスリット37の幅としては、たとえば1マイクロメートル程度、長さとしては、たとえば20から30マイクロメートル程度が好適なものとして例示することができる。この例では、Vssリング36gの幅は、一例として、20マイクロメートル程度とする。ここでは、一定に長さと幅を持ったスリット37の例を示したが、スリットの形状および寸法は、リングに沿った電流の流れを阻害しない形状であれば、どんなものでもよく、一定周期を持つ必要は特にない。ただし、ディッシング防止の観点から必然的に幅方向に周期性を持つことが自然である。

【0071】

次に、図6のA−B断面を上層も含めて、図7に示す。図7に示すように、この断面に於いては、Vssリング36gは、幅方向に多数個に分割されている。また、上層にあるのは、占有率調整用ダミーパターン28である。

【0072】

3.本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等の説明(主に図8から図10)

このセクションでは、本願の前記一実施の形態の半導体集積回路装置の構造等をその要部デバイス構造を中心に説明する。ここで、通常、下地メタルパッドは、例えば図8に示すように、その直下でビアを介して下層の配線に接続されるか、一体となった同層の配線を介して下層の配線等に接続されているが、図9および図10(図19および図20に於いても同じ)においては、図示が煩雑になるので、これらのビアおよび一体となった同層の配線は図示しない。

【0073】

なお、ここでは、P型単結晶シリコン基板上に形成されたCMOS(Complementary Metal Oxide Semiconductor)型の回路構成を有するデバイスを例にとり、具体的に説明するが、その他の基板上に作られたデバイスまたは、同様の基板に作られた他の回路構成のデバイスでもよいことはいうまでもない。

【0074】

図8は本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明するためのデバイス模式断面図である。図9は図8のアルミニウム系主ボンディングパッド膜6x,6yにほぼ対応するパッド周辺拡大上面図である。図10は図9のC−D断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等を説明する。

【0075】

まず、図1および図2で説明した配線構造等のより具体的な形態を図8に基づいて説明する。図8に示すように、P型単結晶シリコン基板部1sのデバイス面1a(第1の主面)側には、N型ウエル領域NWおよびP型ウエル領域PWが設けられており、これとP型単結晶シリコン基板部1sの表面領域に設けられた素子分離フィールド絶縁膜10とともに、MISFET(Qn,Qp)等の能動素子を形成される半導体領域を区画している。各N型ウエル領域NWの半導体表面領域には、P型ソースドレイン領域PSDが設けられており、各P型ウエル領域PWの半導体表面領域には、N型ソースドレイン領域NSDが設けられている。また、各ソースドレイン領域NSD,PSDが設けられた基板部1sの半導体表面上には、たとえばゲート絶縁膜を介して、ゲート電極8が設けられている。なお、実際のソースドレイン構造、ゲート電極およびその周辺構造は、もっと複雑であるが、ここでは詳細構造を省略する。

【0076】

P型単結晶シリコン基板部1sの表面上には、ゲート電極8を被うように、プリメタル層間絶縁膜5が設けられており、この中に、タングステンプラグ3が埋め込まれている。プリメタル層間絶縁膜5上には、埋め込み型第1配線層M1から埋め込み型第8配線層M8の銅埋め込み配線(中層および下層銅埋め込み配線CML)が設けられており、埋め込み型第1配線層M1は、たとえばシングルダマシン(Single Damascene)方式で作られており、埋め込み型第2配線層M2から埋め込み型第8配線層M8は、たとえばデュアルダマシン方式で作られている。

【0077】

埋め込み型第8配線層M8上には、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)中に埋め込まれた埋め込み型最上層配線層M9(たとえば、デュアルダマシン方式による銅系埋め込み配線)が設けられている。この埋め込み型最上層配線層M9の一部として、下地メタルパッド12xとしての最上層銅埋め込み配線等93x(配線、ビア等)および、その一部を下地メタルパッド12yとする最上層銅埋め込み配線等(配線、ビア等)93yが設けられている。ここで、埋め込み型第1配線層M1から埋め込み型最上層配線層M9までの層間絶縁膜をまとめて埋め込み型多層配線層層間絶縁膜ILDとする。

【0078】

埋め込み配線最上層層間絶縁膜16上には、非埋め込み型アルミニウム系パッドメタル層APが設けられている。この非埋め込み型アルミニウム系パッドメタル層APは、下層のパッド層層間絶縁膜9、パッド層層間絶縁膜9に開口されたスルーホール中およびその周辺に形成されたアルミニウム系ボンディングパッド6x(例えば、信号パッド)、アルミニウム系ボンディングパッド6y(たとえば、電源パッド又は接地パッド)等を有している。そして、チップ2の最上部には、ファイナルパッシベーション膜11が設けられており、ファイナルパッシベーション膜11の内、各アルミニウム系ボンディングパッド6x、6y上にあたる部分には、パッド開口7が設けられている。なお、ファイナルパッシベーション膜11上に更にレジン層(たとえば、樹脂封止パッケージの場合)や再配線層(たとえばウエハれべりパッケージの場合)を形成しても良い。

【0079】

この例では、各アルミニウム系ボンディングパッド6x、6yは、間に、タングステンプラグ等の中間接続体を介することなく、直接、下地メタルパッド12x,12yと接続されている。なお、中間にタングステンプラグ等を介することも可能であるが、中間にタングステンプラグ等を介さない場合は、その分、構造が簡単になる。

【0080】

次に、アルミニウム系ボンディングパッド6(6x、6y)の詳細構造を図9および図10に基づいて説明する。図9および図10に示すように、この例では、アルミニウム系ボンディングパッド6と下地メタルパッド12(12x、12y)の中心ほぼ一致しており、形状および寸法もほぼ同じである。なお、必ずしも、このようにする必要はないが、このようにすることによって、チップ面積を増加させることなく、構造的強度が増加させることができる等のメリットがある。ここで、パッド開口7の外周の位置は、アルミニウム系ボンディングパッド6の外周よりも、若干内側とすることが望ましい。また、パッドコンタクト用スルーホール39の外周の位置は、パッド開口7の外周の位置よりも、若干内側とすることが望ましい(パッドコンタクト用スルーホール39の外周の位置とパッド開口7の外周の位置をほぼ同じ位置とすることもできる)。

【0081】

なお、図9および図10に関して、主要な部分の寸法の一例を示すとすれば以下のごとくである。すなわち、アルミニウム系ボンディングパッド6の厚さは、たとえば1000nm程度、下地メタルパッド12の厚さは、たとえば900程度、アルミニウム系ボンディングパッド6の平面寸法は、たとえば、60x100マイクロメートル程度、パッド開口7の平面寸法は、たとえば、50x90マイクロメートル程度、スルーホール39の平面寸法は、たとえば、40x80マイクロメートル程度である。

【0082】

4.本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等の説明(主に図11から図18)

このセクションでは、セクション1から3の主要なデバイス構造に対する製造方法の一例を示すが、前記構造は、以下に示す以外の製法によっても構成できることは言うまでもない。

【0083】

図11は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第7配線層M7完成時点)である。図12は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型第8配線層M8完成時点)である。図13は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(埋め込み型最上層配線層M9完成時点)である。図14は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(パッドコンタクト用スルーホール39完成時点)である。図15は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(アルミニウム系ボンディングパッド加工完成時点)である。図16は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ファイナルパッシベーション膜のパッド開口加工完成時点)である。図17は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(ワイヤボンディング完成時点)である。図18は本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明するための図8に対応するデバイス模式断面図(樹脂モールド完成時点)である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置におけるウエハプロセス等を説明する。

【0084】

埋め込み型第6配線層M6までにBEOL工程は、周知のダマシン工程と同じであるので、埋め込み型第7配線層M7に対応する工程から図11を用いて説明する。図11に示すように、ウエハ1上のデバイス面1a(第1の主面)側において、下層銅埋め込み配線等CL(配線、ビア等)を有する埋め込み型第1配線層M1から埋め込み型第6配線層M6上に、たとえばCVD(Chemical Vapor Deposition)によりセミグローバル下層配線層層間絶縁膜19を形成する。次に、通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、第7層銅埋め込み配線73を形成する。

【0085】

次に、図12に示すように、セミグローバル下層配線層層間絶縁膜19上に、たとえばCVDによりセミグローバル上層配線層層間絶縁膜18を形成する。次に、たとえば通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、第8層銅埋め込み配線83を形成する。

【0086】

次に、図13に示すように、中層銅埋め込み配線等CM(配線、ビア等)を有する埋め込み型第7配線層M7および埋め込み型第8配線層M8上に、たとえばCVDにより埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)を形成する。次に、たとえば通常のリソグラフィにより、配線溝およびビアを開口し、そこに、たとえば、反応性スパッタリング成膜等により窒化タンタル膜を堆積し、続いて、たとえばスパッタリング成膜により、銅シード膜を形成する。続いて、たとえば電界メッキにより銅膜を充填する。次に、たとえばCMPにより、配線溝およびビア外部の窒化タンタル膜および銅膜を除去することにより、最上層銅埋め込み配線等93(配線、ビア等)を形成する。

【0087】

次に、図14に示すように、埋め込み配線最上層層間絶縁膜16(グローバル配線層層間絶縁膜)上に、たとえばCVDによりパッド層層間絶縁膜9を成膜し、たとえば通常のリソグラフィにより下地メタルパッド12x,12y上に、パッドコンタクト用スルーホール39(39x,39y)を開口する。

【0088】

次に、図15に示すように、パッドコンタクト用スルーホール39(39x,39y)を含むパッド層層間絶縁膜9の上面のほぼ全面に、たとえば、反応性スパッタリング成膜により、TiN膜を成膜して、続いて、たとえば、スパッタリング成膜により、アルミニウム系メタル膜(アルミニウムを主成分とするメタル膜)を形成する。この複合膜をたとえば、通常のリソグラフィにより形成したレジスト膜をマスクとして、例えばドライエッチングによりパターニングすることにより、アルミニウム系ボンディングパッド6(6x,6y)を形成する。

【0089】

次に、図16に示すように、パッド層層間絶縁膜9およびアルミニウム系ボンディングパッド6(6x,6y)上のほぼ全面に、たとえばCVDによりファイナルパッシベーション膜11を成膜する。次に、たとえば通常のリソグラフィにより、パッド開口7を開口する。

【0090】

その後、必要に応じて、バックグラインディングやプローブテストを実行した後、ダイシング等により、ウエハ1を個々のチップ2に分離する。

【0091】

その後、個々のチップ2を図17以降に示すように加工する。すなわち、図17に示すように、各アルミニウム系ボンディングパッド6x,6yと外部のリード等の間を、金線(ボンディングワイヤ40)等を用いて、例えば、ボール&ウエッジボンディング等により、相互接続する。このとき、通常、アルミニウム系ボンディングパッド6x,6yの側をボールボンディング(ボンディングボール40bを形成するボンディング)するが、これに限らず、必要に応じて、アルミニウム系ボンディングパッド6x,6yの側をウエッジボンディングしても良い。

【0092】

次に、図18に示すように、ファイナルパッシベーション膜11、各アルミニウム系ボンディングパッド6x,6yおよびボンディングワイヤ40等を被覆するように、たとえば、エポキシ系封止樹脂を用いたトランスファーモールド等により、チップ2の表面1a(必要に応じてチップ2全体を封止してもよい)に封止樹脂層42を形成する。

【0093】

5.本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例の説明(主に図19および図20)

このセクションでは、セクション3(図9および図10)で説明したパッド周辺構造(「単一スルーホール接続」という)の変形例の一例を示す。このセクションの方式を「スルーホールリング接続」という。

【0094】

図19は本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明するための図9に対応するパッド周辺拡大上面図である。図20は図19のC−D断面のデバイス模式断面図である。これらに基づいて、本願の前記一実施の形態の半導体集積回路装置における要部デバイス構造等におけるパッド周辺構造の変形例を説明する。

【0095】

図19および図20に示すように、スルーホールリング接続では、多数のパッドコンタクト用スルーホール39から構成されたスルーホールリング41を介して、アルミニウム系ボンディングパッド6と下地メタルパッド12を相互接続している。パッドコンタクト用スルーホール39の個々の寸法は、たとえば、3x3マイクロメートル程度を好適なものの一例として提示することができる。他の寸法は、単一スルーホール接続について示したものとほぼ同じである。ここで、スルーホールリング41の外周の寸法は、単一スルーホール接続についての単一スルーホール39の外周に対応させればよい。

【0096】

ここで、単一スルーホール接続とスルーホールリング接続を比較すると、以下のようになる。すなわち、単一スルーホール接続では、ボンディングパッドが盆地状になっているので、プローブ特性は良好であるが、平坦部分が狭いのでワイヤボンディング特性は相対的に劣る。一方、スルーホールリング接続では、平坦部分が広いので、ワイヤボンディング特性は相対的に良好であるが、プローブ特性は相対的に劣る。

【0097】

6.アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等の説明(主に図21)

このセクションでは、図3に示した占有率調整用ダミーパターンの一つの変形例を説明するとともに、これをMIMキャパシタとして利用する可能性を説明する。すなわち、占有率調整用ダミーパターンは、図3や図21に示すものばかりでなく、一定の占有率を均一に達成できるものであれば、種々変形可能である。また、他の素子としての利用も、キャパシタに限らず、インダクタンス、アンテナ、抵抗素子、その他としても可能である。

【0098】

図21はアルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明するための図3に対応するチップ領域およびその周辺の模式レイアウト図(非埋め込み型アルミニウム系パッドメタル層を中心に表示)である。これに基づいて、アルミニウム系同層メタル櫛形MIMキャパシタおよび占有率調整用ダミーパターンの変形例等を説明する。

【0099】

図21は、図3に対応する非埋め込み型アルミニウム系パッドメタル層APの平面レイアウトの変形例である。図3と異なっているのは、図3に於いては、ドット状の占有率調整用ダミーパターン28となっていたところを、図21では、同層メタル櫛形MIMキャパシタ39(一対の同層メタルキャパシタ電極)としたところである。なお、このパターンは、同層メタル櫛形MIMキャパシタ39としてではなく、線形占有率調整用ダミーパターンとしても使用することができる。また、同層メタル櫛形MIMキャパシタの一対の同層メタルキャパシタ電極であると同時に線形占有率調整用ダミーパターンとしても使用することができる。

【0100】

7.前記各実施の形態等(変形例を含む)に関する予備的説明および一般的考察

このセクションでは、前記各実施の形態(変形例を含む)に関する予備的説明および一般的考察を行う。

【0101】

図22はアンテナ比の大きなウエハと、アンテナ比の小さなウエハに対して、プラズマ処理を施したサンプルについてのMISFETのソースドレイン電流(Ids)および閾値電圧(Vth)の分布を示すデータプロット図である。これは、ゲート酸化膜厚が、7.5nm程度のNチャネル型MOSFETについて、室温で測定した結果である。ソースドレイン電流は、ドレイン電圧およびゲート電圧がともに3.3ボルトの時の値である。

【0102】

非埋め込み型アルミニウム系パッドメタル層AP(図3)は、通常、パッド等の非配線パターンとともに、電源配線、信号配線等の配線パターン(または単に「配線」)を含むことが多い。これは、各配線層の利用度を高めるという一般的な要請に対応している。しかし、本発明者が検討したところによると、最上層メタル層である非埋め込み型アルミニウム系パッドメタル層APは、通常、ドライエッチングで加工されるので、プラズマダメージを受けやすいという問題がある。特に、全部の配線が接続された状態にあるこのステージに於いては、一般にアンテナ比が大きくなりやすく、半導体基板や素子(MISFET等の能動素子等)に接続されたものを含みやすい電源配線、信号配線等の配線パターンの存在は、デバイスの信頼性や性能の劣化を招く恐れがある。この傾向は、直接、MISFET等の能動素子の端子に接続される可能性の高い信号配線では、特に顕著である。また、電源配線は、アンテナ比が特に大きくなりやすい。以上の点は、たとえば、図22の見ると、理解することができる。すなわち、アンテナ比が相対的に小さいチップ内配線レイアウトを有するウエハでは、プロットは、ソースドレイン電流の目標値と閾値電圧の目標値を示す直線の交点近傍に分布するが、アンテナ比が相対的に大きなチップ内配線レイアウトを有するウエハでは、ソースドレイン電流に関しては、低めにシフトしており、閾値電圧に関しては、高めにシフトしているのがわかる。

【0103】

また、一般的な設計手法(「一般的設計手法」)では、最上層メタル層の一部として、接地リング、Vssリング、Vccリング等の電源リング(電源幹配線)を配置する。しかし、このような大面積且つ大寸法(差渡しサイズが大きい)のメタル図形を配置することは、プラズマダメージに関して問題であるばかりでなく、メタル層とその上のファイナルパッシベーション膜との間の物理的特性の相違に起因するクラックの発生等を招く恐れがある。

【0104】

これに対して、前記実施の形態に於いては、最上層メタル層(最上層非埋め込みメタル層)は、できるだけ非配線パターンにだけ使用するようにして、アンテナ比が大きくなりやすい信号配線、アンテナ比または幅(面積)等が大きくなりやすい電源リング(電源幹配線)その他の電源配線を直下の層、すなわち、埋め込み配線の内の最上層埋め込み配線層に移したものである。もちろん、全ての配線を下層に移すことが望ましいが、一部の比較的アンテナ比の小さな配線を最上層非埋め込みメタル層に残すこともできる(このことは以下に於いても同じ)。

【0105】

また、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、電源リング(電源幹配線)と信号配線を下層に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に電源リングおよび信号配線を有さない。なお、このとき、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、実質的に全ての配線を下層(たとえば、最上層埋め込み配線層)に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に配線を有さない。

【0106】

なお、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、主に電源リング(電源幹配線)を下層(たとえば、最上層埋め込み配線層)に移すことも有効である。この場合は、最上層非埋め込みメタル層は、その一部として、実質的に電源リング(電源リング配線)を有さない。

【0107】

更に、一般的設計手法における最上層非埋め込みメタル層に属する配線のうち、幾つかの部分を移す先の埋め込み配線層(「移送先配線層」という)は、直下の埋め込み配線の内の最上層埋め込み配線層にすることがレイアウト上有利であるが、その他の層(主にセミグローバル配線のうちの1層または2層)に移すことも可能である。移送先配線層を最上層埋め込み配線層にすることは、もっとも好適である。これは、最上層埋め込み配線層は、他の配線層に比べて、配線の断面積が圧倒的に大きいので、一般に電流量の大きいアルミニウム系配線(特に電源配線リング等の電源配線)の代替配線層として好適だからである。

【0108】

更に、このように機械強度が強い最上層埋め込み配線層で下地メタルパッドを作ることが必須ではないが、設けることによって、アルミニウム系主ボンディングパッド膜およびその周辺の機械的強度を改善することができる。

【0109】

8.サマリ

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0110】

例えば、前記実施の形態では、主に銅系埋め込み配線について具体的に説明したが、本発明はそれに限定されるものではなく、銀系埋め込み配線のその他のメタル系埋め込み配線にも適用できることは言うまでもない。

【0111】

また、銅に対するバリアメタルとして、窒化タンタル系バリアメタルを例にとり具体的に説明したが、本発明はそれに限定されるものではなく、窒化チタン系バリアメタル(Ti/TiNの多層バリアを含む)、ルテニウム系バリアメタル等のその他のバリアメタルでも良いことは、言うまでもない。また、ここでは、TaN膜単層のバリアメタルの例をとり具体的に説明したが、本発明はそれに限定されるものではなく、Ta/TaNの多層バリアでも良いことは、言うまでもない。

【0112】

更に、絶縁性銅拡散バリア膜として、主にSiC,SiN等を用いた例を具体的に説明したが、本発明はそれに限定されるものではなく、SiCN等、その他の膜であってもよいことは言うまでもない。

【符号の説明】

【0113】

1 半導体ウエハ

1a 基板又はウエハのデバイス面(第1の主面)

1b 基板又はウエハの裏面(第2の主面)

1s 基板又はウエハのP型単結晶シリコン基板部

2 半導体基板又は集積回路チップ(半導体チップ領域)

3 タングステンプラグ

4 窒化シリコンライナー膜(エッチストップ膜)

5 プリメタル層間絶縁膜

6,6x,6y アルミニウム系ボンディングパッド

6a アルミニウム系主ボンディングパッド膜

6b 窒化チタン系パッドバリアメタル膜

7 (ファイナルパッシベーション膜の)パッド開口

8 ゲート電極

9 パッド層層間絶縁膜

9a プラズマTEOS系主層間絶縁膜

9b SiN系絶縁性バリア膜

10 素子分離フィールド絶縁膜

11 ファイナルパッシベーション膜

11a USG系ファイナルパッシベーション膜

11b SiN系ファイナルパッシベーション膜

12,12x,12y 下地メタルパッド

13 埋め込まれた銅配線

14 SiC系絶縁性バリア膜

15 プラズマTEOS系主層間絶縁膜

16 埋め込み配線最上層層間絶縁膜(グローバル配線層層間絶縁膜)

18 セミグローバル上層配線層層間絶縁膜

19 セミグローバル下層配線層層間絶縁膜

20a アルミニウム系シールリング

20b 銅系シールリング

21 ローカル最上層配線層層間絶縁膜

22a アルミニウム系パッドリング

22b 銅系パッドリング

23 銅埋め込み配線

24 SiC系絶縁性バリア膜

25 SiOC系主層間絶縁膜

26 チップ内部回路形成領域

27 ダイシング領域(スクライブ領域)

28 占有率調整用ダミーパターン

29a アルミニウム系TEGパターン

29b 銅系TEGパターン

30a アルミニウム系レーザートリム用位置決め基準パターン

31a アルミニウム系膜厚モニタ

31b 銅系膜厚モニタ

32a アルミニウム系露光用アライメントパターン

32b 銅系露光用アライメントパターン

33 銅埋め込み配線

34 SiC系絶縁性バリア膜

35 SiOC系主層間絶縁膜

36 電源リング(電源幹配線)

36d Vddリング(電源供給リング)

36g Vssリング(接地リング)

37 スリット

38 同層メタル櫛形MIMキャパシタ

39,39x,39y パッドコンタクト用スルーホール

40 ボンディングワイヤ

40b ボンディングボール

41 スルーホールリング

42 封止樹脂(封止樹脂層)

43 銅埋め込み配線

44 SiC系絶縁性バリア膜

45 SiOC系主層間絶縁膜

53 銅埋め込み配線

54 SiC系絶縁性バリア膜

55 SiOC系主層間絶縁膜

63 銅埋め込み配線

63a 埋め込み型第6配線層銅系メタル膜

63b 窒化タンタル系バリアメタル膜

64 SiC系絶縁性バリア膜

65 SiOC系主層間絶縁膜

73 第7層銅埋め込み配線

74 SiC系絶縁性バリア膜

75a プラズマTEOS系主層間絶縁膜

75b FSG系主層間絶縁膜

75c プラズマTEOS系キャップ膜

83 第8層銅埋め込み配線

84 SiC系絶縁性バリア膜

85a プラズマTEOS系主層間絶縁膜

85b FSG系主層間絶縁膜

85c プラズマTEOS系キャップ膜

93,93x,93y 最上層銅埋め込み配線等(配線、ビア等)

93a 最上層銅埋め込み配線銅系メタル膜

93b 窒化タンタル系バリアメタル膜

94a SiN系絶縁性バリア膜

94b SiC系絶縁性バリア膜

95a プラズマTEOS系主層間絶縁膜

95b プラズマTEOS系主層間絶縁膜

AP 非埋め込み型アルミニウム系パッドメタル層

CM 中層銅埋め込み配線等(配線、ビア等)

CML 中層および下層銅埋め込み配線等(配線、ビア等)

CL 下層銅埋め込み配線等(配線、ビア等)

DW 埋め込み型多層配線層

ILD 埋め込み型多層配線層層間絶縁膜

M1 埋め込み型第1配線層

M2 埋め込み型第2配線層

M3 埋め込み型第3配線層

M4 埋め込み型第4配線層

M5 埋め込み型第5配線層

M6 埋め込み型第6配線層

M7 埋め込み型第7配線層

M8 埋め込み型第8配線層

M9 埋め込み型第9配線層(埋め込み型最上層配線層)

NSD N型ソースドレイン領域

NW N型ウエル領域

PM プリメタル領域

PSD P型ソースドレイン領域

PW P型ウエル領域

Qn Nチャネル型MISFET

Qp Pチャネル型MISFET

R1 Vssリング切り出し領域

【特許請求の範囲】

【請求項1】

以下を含む半導体集積回路装置:

(a)第1の主面を有する半導体基板;

(b)前記半導体基板の前記第1の主面に設けられた複数のMISFET;

(c)前記半導体基板の前記第1の主面および前記複数のMISFETの上方に設けられた埋め込み型多層配線層;

(d)前記埋め込み型多層配線層上に設けられた非埋め込み型アルミニウム系パッドメタル層;

(e)前記非埋め込み型アルミニウム系パッドメタル層の一部として設けられた複数のメタルボンディングパッド;

(f)前記非埋め込み型アルミニウム系パッドメタル層よりも上層に形成されたファイナルパッシベーション膜;

(g)前記複数のメタルボンディングパッドの各々の上方の前記ファイナルパッシベーション膜に設けられたパッド開口、

ここで、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しない。

【請求項2】

前記1項の半導体集積回路装置において、更に以下を含む:

(h)前記埋め込み型多層配線層の内の埋め込み型最上層配線層の一部として設けられた電源リング配線。

【請求項3】

前記2項の半導体集積回路装置において、更に以下を含む:

(i)前記電源リング配線内に設けられたディッシング防止用スリット。

【請求項4】

前記2項の半導体集積回路装置において、前記複数のメタルボンディングパッドの各々は、プラグを介することなく、前記埋め込み型最上層配線層に接続されている。

【請求項5】

前記4項の半導体集積回路装置において、更に以下を含む:

(j)前記複数のメタルボンディングパッドの各々の下方に、前記埋め込み型最上層配線層の一部として設けられ、その上方のメタルボンディングパッドと形状および面積がほぼ同様の下地メタルパッド。

【請求項6】

前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた単一のスルーホール。

【請求項7】

前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた複数のスルーホール。

【請求項8】

前記6項の半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に配線を有しない。

【請求項9】

前記8項の半導体集積回路装置において、更に以下を含む:

(m)前記第1の主面の内部領域に、前記非埋め込み型アルミニウム系パッドメタル層の一部として、ほぼ均一に分布するように設けられた多数の占有率調整用ダミーパターン。

【請求項10】

前記9項の半導体集積回路装置において、更に以下を含む:

(n)前記第1の主面の外周に沿って、前記非埋め込み型アルミニウム系パッドメタル層の一部として、アルミニウム系シールリング。

【請求項11】

前記1項の半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に信号配線を有しない。

【請求項12】

前記1項の半導体集積回路装置において、更に以下を含む:

(p)前記複数のメタルボンディングパッドの各々の上面に接続されたボンディングワイヤ。

【請求項13】

前記11項の半導体集積回路装置において、更に以下を含む:

(q)前記ファイナルパッシベーション膜上を被う封止樹脂層。

【請求項14】

前記10項の半導体集積回路装置において、前記複数のメタルボンディングパッドは、アルミニウム系シールリングに沿うように、その内側に、リング状に配列されている。

【請求項15】

前記14項の半導体集積回路装置において、前記埋め込み型多層配線層は、銅系埋め込み型多層配線層である。

【請求項1】

以下を含む半導体集積回路装置:

(a)第1の主面を有する半導体基板;

(b)前記半導体基板の前記第1の主面に設けられた複数のMISFET;

(c)前記半導体基板の前記第1の主面および前記複数のMISFETの上方に設けられた埋め込み型多層配線層;

(d)前記埋め込み型多層配線層上に設けられた非埋め込み型アルミニウム系パッドメタル層;

(e)前記非埋め込み型アルミニウム系パッドメタル層の一部として設けられた複数のメタルボンディングパッド;

(f)前記非埋め込み型アルミニウム系パッドメタル層よりも上層に形成されたファイナルパッシベーション膜;

(g)前記複数のメタルボンディングパッドの各々の上方の前記ファイナルパッシベーション膜に設けられたパッド開口、

ここで、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しない。

【請求項2】

前記1項の半導体集積回路装置において、更に以下を含む:

(h)前記埋め込み型多層配線層の内の埋め込み型最上層配線層の一部として設けられた電源リング配線。

【請求項3】

前記2項の半導体集積回路装置において、更に以下を含む:

(i)前記電源リング配線内に設けられたディッシング防止用スリット。

【請求項4】

前記2項の半導体集積回路装置において、前記複数のメタルボンディングパッドの各々は、プラグを介することなく、前記埋め込み型最上層配線層に接続されている。

【請求項5】

前記4項の半導体集積回路装置において、更に以下を含む:

(j)前記複数のメタルボンディングパッドの各々の下方に、前記埋め込み型最上層配線層の一部として設けられ、その上方のメタルボンディングパッドと形状および面積がほぼ同様の下地メタルパッド。

【請求項6】

前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた単一のスルーホール。

【請求項7】

前記5項の半導体集積回路装置において、更に以下を含む:

(k)前記複数のメタルボンディングパッドの各々と、その下方の下地メタルパッドとの間に設けられた複数のスルーホール。

【請求項8】

前記6項の半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に配線を有しない。

【請求項9】

前記8項の半導体集積回路装置において、更に以下を含む:

(m)前記第1の主面の内部領域に、前記非埋め込み型アルミニウム系パッドメタル層の一部として、ほぼ均一に分布するように設けられた多数の占有率調整用ダミーパターン。

【請求項10】

前記9項の半導体集積回路装置において、更に以下を含む:

(n)前記第1の主面の外周に沿って、前記非埋め込み型アルミニウム系パッドメタル層の一部として、アルミニウム系シールリング。

【請求項11】

前記1項の半導体集積回路装置において、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に信号配線を有しない。

【請求項12】

前記1項の半導体集積回路装置において、更に以下を含む:

(p)前記複数のメタルボンディングパッドの各々の上面に接続されたボンディングワイヤ。

【請求項13】

前記11項の半導体集積回路装置において、更に以下を含む:

(q)前記ファイナルパッシベーション膜上を被う封止樹脂層。

【請求項14】

前記10項の半導体集積回路装置において、前記複数のメタルボンディングパッドは、アルミニウム系シールリングに沿うように、その内側に、リング状に配列されている。

【請求項15】

前記14項の半導体集積回路装置において、前記埋め込み型多層配線層は、銅系埋め込み型多層配線層である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−58584(P2013−58584A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−195707(P2011−195707)

【出願日】平成23年9月8日(2011.9.8)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月8日(2011.9.8)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]