半導体集積回路

【課題】長期信頼性が要求される部分回路を備える半導体集積回路の長寿命化を図る。

【解決手段】半導体集積回路1は、同一又は同様の機能を有する複数の部分回路3と、部分回路3が電源供給を受けた総通電時間を部分回路3毎に記憶する記憶回路5と、部分回路3への電源供給を部分回路3毎に遮断可能な電源遮断回路4と、記憶回路5に記憶された各総通電時間を参照し、総通電時間が最も短い部分回路3を除く部分回路3への電源供給を遮断するように、電源遮断回路4を制御する電源供給制御回路6とを備える。

【解決手段】半導体集積回路1は、同一又は同様の機能を有する複数の部分回路3と、部分回路3が電源供給を受けた総通電時間を部分回路3毎に記憶する記憶回路5と、部分回路3への電源供給を部分回路3毎に遮断可能な電源遮断回路4と、記憶回路5に記憶された各総通電時間を参照し、総通電時間が最も短い部分回路3を除く部分回路3への電源供給を遮断するように、電源遮断回路4を制御する電源供給制御回路6とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路に関し、特に冗長性を有する構成を制御する技術に関するものである。

【背景技術】

【0002】

半導体集積回路に使用されるトランジスタは、通常、HCI(Hot Carrier Injection)、NGTI(Negative Bias Temperature Instability)等の経時劣化特性を有し、通電(使用)時間に応じてスイッチング性能(応答速度)が低下するものである。半導体集積回路の用途によっては、長期間に渡ってトランジスタのスイッチング性能を高度に維持する必要がある。このような場合、想定される製品寿命に応じた経時劣化に相当するマージンを半導体集積回路の設計時に確保したり、性能維持が必要な部分回路を冗長化させたりする対策が取られる。

【0003】

特許文献1において、複数のHDD(Hard Disk Drive)を含んで構成されるディスクアレイ装置であって、マイクロコンピュータとファームウェアとの協働により、各HDDの通電時間を管理し、最も通電時間の長いHDDを予備ディスクとして設定する構成が開示されている。

【0004】

また、特許文献2において、少なくとも2つの同じ又は同種の機能ユニットを備えた半導体回路のコンフィギュレーション方法であって、各機能ユニットの欠陥を検出する手段を備え、欠陥があると判定された機能ユニットの電気的な接続を遮断する構成が開示されている。

【0005】

更に、特許文献3において、稼働中であっても故障診断が可能な診断回路を備える集積回路であって、論理回路の内部状態を保持し、診断後復帰させる構成が開示されている。

【0006】

更にまた、特許文献4において、サーマルヘッド用集積回路であって、複数の発熱抵抗体への通電時間を個別に制御する構成が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−293315号公報

【特許文献2】特表2009−514064号公報

【特許文献3】特開2006−300650号公報

【特許文献4】特開平11−277786号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記のように、長期信頼性が要求される半導体集積回路においては、経時劣化に対処するマージンを設計時に組み込む必要があるため、トランジスタ本来のスイッチング性能を十分に活かしたハイスペックな回路を提供することができないといった問題がある。また、長期信頼性が要求される部分回路を冗長化させる場合には、複数の部分回路のうち使用する部分回路を適切に選択しなければ、同一の部分回路が使用され続けることとなり、上記経時劣化の問題を解消することができない。

【0009】

また、特許文献1に開示される構成は、各HDDの通電時間を管理するために、ファームウェアにより制御されるマイクロコンピュータを必要とする。このような構成は、1つのコンピュータシステム内においてメイン制御システムとは別体に且つ交換可能に設置されるHDDを対象とする構成に適合するものであり、1つ又は少数のチップ上に部分回路が基本的に交換不可能に設置された半導体集積回路に適用する場合には、設計、コスト等の面で様々な不具合を生ずるものである。

【0010】

更に、特許文献2に開示される構成は、欠陥のある回路を非アクティブ状態にすることができるものであるが、回路(トランジスタ)の経時劣化を遅らせ、長寿命化を図ることはできない。

【0011】

そこで、本発明は、長期信頼性が要求される部分回路を備える半導体集積回路の長寿命化を図ることを目的とする。

【課題を解決するための手段】

【0012】

上記課題の解決を図る本発明の一態様は、同一又は同様の機能を有する複数の部分回路と、前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路とを備える半導体集積回路である。

【0013】

また、本発明の他の態様は、同一又は同様の機能を有する複数の部分回路と、前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、第1の前記部分回路への前記電源供給時であって、前記第1の部分回路の前記総通電時間が第2の前記部分回路の前記総通電時間を超えた場合に、前記第1の部分回路の内部状態を前記第2の部分回路に移送する内部状態移送回路とを備える半導体集積回路である。

【発明の効果】

【0014】

上記本発明の一態様によれば、各部分回路に対応する総通電時間に基づいて、最も総通電時間が短い部分回路にのみ電源供給が行われる。これにより、各部分回路の総通電時間の均等化を図ることができ、各部分回路の経時劣化の偏りを防止することができる。これにより、部分回路全体の長寿命化を図ることができる。また、上記本発明の他の態様によれば、上記効果に加え、使用する部分回路を切り替える際に、初期化等の処理を行わなくても、不具合を生ずることなく処理を継続することができる。

【図面の簡単な説明】

【0015】

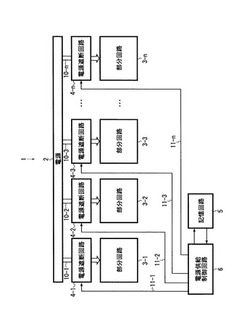

【図1】本発明の実施の形態1に係る半導体集積回路の機能的な構成を示すブロック図である。

【図2】実施の形態1に係る電源遮断回路の具体的な構成を例示する図である。

【図3】実施の形態1に係る記憶回路及び電源遮断制御回路の具体的な構成を例示する図である。

【図4】本発明の実施の形態2に係る半導体集積回路の機能的な構成を示すブロック図である。

【図5】実施の形態2に係る内部状態移送回路の具体的な構成を例示する図である。

【図6】実施の形態2に係る記憶回路及び電源遮断制御回路の具体的な構成を例示する図である。

【図7】実施の形態2に係る半導体集積回路の動作を示すタイムチャートである。

【図8】図7に示すタイムチャートにおけるクロックサイクルT2の動作を詳細に示すタイムチャートである。

【発明を実施するための形態】

【0016】

以下に、添付した図面を参照して本発明の実施の形態を説明する。尚、異なる実施の形態において、同一又は同様の作用効果を奏する箇所については同一の符号を付してその説明を省略する。

【0017】

実施の形態1

図1は、本実施の形態に係る半導体集積回路1の機能的な構成を示している。半導体集積回路1は、電源(電源配線)2、部分回路3−1,3−2,3−3,・・,3−n、電源遮断回路4−1,4−2,4−3,・・,4−n、記憶回路5、及び電源供給制御回路6を含む。

【0018】

電源2は、電力を発生させるバッテリ等の機構、又はバッテリ等と接続する配線に相当する。

【0019】

複数の部分回路3−1,3−2,3−3,・・,3−nは、それぞれ電源2からの電力供給により作動し、全て同一又は同様の機能を有するものである。各部分回路3−1,3−2,3−3,・・,3−nは、それぞれ独立の接続経路10−1,10−2,10−3,・・,10−nにより電源2と接続している。

【0020】

複数の電源遮断回路4−1,4−2,4−3,・・,4−nは、各接続経路10−1,10−2,10−3,・・,10−n上に接続され、各部分回路3−1,3−2,3−3,・・,3−nへの電源供給を独立に遮断可能なものである。各電源遮断回路4−1,4−2,4−3,・・,4−nは、電源供給制御回路6が出力する電源遮断制御信号11−1,11−2,11−3,・・,11−nにより制御される。

【0021】

記憶回路5は、各部分回路3−1,3−2,3−3,・・,3−nの電源供給を受けた時間の総和を示す総通電時間を、部分回路3−1,3−2,3−3,・・,3−n毎に記憶するものである。総通電時間は、例えば各電源遮断回路4−1,4−2,4−3,・・,4−nが対応する部分経路3−1,3−2,3−3,・・,3−nへの電源供給を遮断した時間(若しくは許可した時間)を、電源供給制御回路6の制御経過から把握すること等により、検知することができる。

【0022】

電源供給制御回路6は、記憶回路5に記憶された各部分回路3−1,3−2,3−3,・・,3−nの総通電時間に基づいて、総通電時間が最も短い部分回路3−1,3−2,3−3,・・,3−nのみに電源供給されるように、電源遮断回路4−1,4−2,4−3,・・,4−nを制御する電源遮断制御信号11−1,11−2,11−3,・・,11−nを出力する。

【0023】

図2は、電源遮断回路4(4−1,4−2,4−3,・・,4−n)の具体的な構成を例示している。電源遮断回路4は、複数のp−MOSトランジスタ15を含んで構成される。各p−MOSトランジスタ15のゲートには、電源供給制御回路6と接続する信号線16が接続されている。p−MOSトランジスタ15は、信号線16から入力される電源遮断制御信号11−1,11−2,11−3,・・,11−nが論理「1」である場合にOFFとなり、部分回路3への電源供給を遮断する。逆に、電源遮断制御信号11−1,11−2,11−3,・・,11−nが論理「0」である場合に、p−MOSトランジスタ15はONとなり、部分回路3への電源供給が行われる。

【0024】

図3は、記憶回路5及び電源遮断制御回路6の具体的な構成を例示している。この例は、半導体集積回路1が4つの部分回路3(3−1,3−2,3−3,3−4)を備える場合を示している。

【0025】

この例に係る記憶回路5は、各部分回路3の秒単位で表された総通電時間を記憶する。各部分回路3に32ビット幅の記憶領域を割り当てることにより、約136年間に相当する時間を扱うことができる。記憶回路5が出力する4つの32ビット幅の信号21,22,23,24は、それぞれ部分回路3の総通電時間を示す。

【0026】

半導体集積回路1の初期化時に、記憶回路5から読み出された信号21,22,23,24は、それぞれセレクタ27,28,29,30を経由して、経過時間レジスタ33,34,35,36に保持される。経過時間レジスタ33,34,35,36の出力は、比較回路39,40,41,42,43,44により比較される。これらの比較結果は、判定回路47,48,49,50に入力され、判定回路47,48,49,50は、組み合わせ論理により何れの部分回路3の総通電時間が最も短いかを判定する。各判定回路47,48,49,50は、各部分回路3に対応付けられている。そして、総通電時間が最も短い部分回路3に対応する判定回路47,48,49,50の出力は論理「0」となり、その他の判定回路47,48,49,50の出力は論理「1」となる。判定回路47,48,49,50の出力は、それぞれセレクタ53,54,55,56を経由してフリップフロップ59,60,61,62に保持される。各フリップフロップ59,60,61,62は、上述した電源遮断制御信号11−1,11−2,11−3,11−4を出力する。

【0027】

半導体集積回路1の初期化終了後には、セレクタ53,54,55,56は、それぞれフリップフロップ59,60,61,62の出力である電源遮断制御信号11−1,11−2,11−3,11−4を入力として選択し、フリップフロップ59,60,61,62に出力する。これにより、フリップフロップ59,60,61,62の値はそれ以降変化せず、電源遮断信号11−1,11−2,11−3,11−4の状態は維持される。

【0028】

加算回路70,71,72,73は、各経過時間レジスタ33,34,35,36の値に1を加えた値を出力する。半導体集積回路1の初期化終了後には、各セレクタ27,28,29,30は、電源遮断制御信号11−1,11−2,11−3,11−4の値に応じて、経過時間レジスタ33,34,35,36への出力を変化させる。即ち、各セレクタ27,28,29,30は、電源制御信号11−1,11−2,11−3,11−4が論理「0」の場合には、加算回路70,71,72,73の出力を経過時間レジスタ33,34,35,36への出力とし、電源制御信号11−1,11−2,11−3,11−4が論理「1」の場合には、経過時間レジスタ33,34,35,36の出力を経過時間レジスタ33,34,35,36への出力とする。これにより、電源遮断制御信号11−1,11−2,11−3,11−4が論理「1」となり電源供給が遮断された部分回路3に対応する経過時間レジスタ33,34,35,36の値は、保持される。一方、電源遮断制御信号11−1,11−2,11−3,11−4が論理「0」となり電源供給された部分回路3に対応する経過時間レジスタ33,34,35,36の値は、クロック信号に同期してカウントアップされる。

【0029】

経過時間レジスタ33,34,35,36の値は、信号76,77,78,79として記憶回路5に入力され、書き込まれる。タイミングレジスタ82は、半導体集積回路1の初期化時に固定値「0」がセレクタ83を経由して入力され、これを保持する。初期化終了後には、加算回路84がタイミングレジスタ82の値に1を加えた値を出力し、セレクタ83が加算回路84の出力を選択してタイミングレジスタ82に出力する。これにより、タイミングレジスタ82の値は、クロック信号に同期してカウントアップされる。

【0030】

ライト制御回路87は、タイミングレジスタ82の全てのビットのAND演算により、記憶回路5への書き込み指示である信号88を生成する。記憶回路5は、信号88が論理「1」である場合に、クロック信号90に同期して、信号76,77,78,79から経過時間レジスタ33,34,35,36の値を取り込み、各部分回路3(3−1,3−2,3−3,3−4)の総通電時間として記憶する。

【0031】

上記構成において、電源供給制御回路6は、クロック信号90に同期して動作する。クロック信号90は、総通電時間を積算する際の基準時間としても使用され、例えばその周波数を1Hzとすることが好ましい。

【0032】

記憶回路5が出力する各信号21,22,23,24は、セレクタ27,28,29,30の入力1Xに入力される。半導体集積回路1の使用開始時にリセット信号91が論理「1」となると、セレクタ27,28,29,30の入力1Xの値が選択され、これらの値が各経過時間レジスタ33,34,35,36に入力される。経過時間レジスタ33,34,35,36は、クロック信号90に同期して、各セレクタ27,28,29,30が出力した値を入力して保持する。

【0033】

セレクタ27,28,29,30は、リセット信号91が論理「0」である場合に、入力S0に入力される電源遮断制御信号11−1,11−2,11−3,11−4が論理「1」であるならば、入力01に入力される経過時間レジスタ33,34,35,36の出力を選択して出力する。

【0034】

加算回路70,71,72,73は、経過時間レジスタ33,34,35,36の値に1を加算した値を出力する。セレクタ27,28,29,30は、リセット信号91が論理「0」である場合に、入力S0に入力された電源遮断制御信号11−1,11−2,11−3,11−4が論理「0」であるならば、入力00に入力された加算回路70,71,72,73の出力を選択して出力する。加算回路70,71,72,73、セレクタ27,28,29,30、及び経過時間レジスタ33,34,35,36は、記憶回路5が出力する信号21,22,23,24と同じビット幅のデータを扱うものとする。

【0035】

比較回路39,40,41,42,43,44は、経過時間レジスタ33,34,35,36の出力を比較し、入力Aの値が入力Bの値以下である場合に、論理「1」を出力する。比較回路39,40,41,42,43,44が比較するデータのビット幅を、経過時間レジスタ33,34,35,36のビット幅より小さくすることにより、回路規模を縮小することが可能となる。例えば、32ビットのデータのうち、上位16ビットを比較対象とすると、判定の粒度は、35536秒(約18時間)となる。

【0036】

判定回路47,48,49,50は、NAND回路で構成され、比較回路39,40,41,42,43,44の出力から最も総通電時間の短い部分回路3を判定する。判定回路47,48,49,50は、それぞれ部分回路3(3−1,3−2,3−3,3−4)に対応しており、最も総通電時間が短い部分回路3に対応する判定回路47,48,49,50の出力が論理「0」となり、その他の出力が論理「1」となる。判定回路47,48,49,50の出力は、それぞれセレクタ53,54,55,56の入力1に入力され、半導体集積回路1の使用開始時にリセット信号91が論理「1」になると、セレクタ53,54,55,56の入力1の値が選択され、フリップフロップ59,60,61,62に出力される。フリップフロップ59,60,61,62は、クロック信号90に同期して、各セレクタ53,54,55,56が出力した値を入力して保持する。

【0037】

フリップフロップ59,60,61,62は、電源遮断制御信号65,66,67,68を出力する。セレクタ53,54,55,56は、リセット信号91が論理「0」である場合に、電源遮断制御信号11−1,11−2,11−3,11−4が入力される入力0の値を選択し、出力する。リセット信号91が倫理「1」の場合には、セレクタ53,54,55,56は入力1の値が0の固定値を選択し、これを出力する。

【0038】

タイミングレジスタ82は、クロック信号90に同期して、セレクタ83の出力を入力し、これを保持する。加算回路84は、タイミングレジスタ82の値に1を加えた値を出力する。リセット信号91が論理「0」である場合には、セレクタ83の入力0を選択し、加算回路84の値を出力する。ライト制御回路87は、タイミングレジスタ82の全てのビットのANDを求め、その結果を信号88として出力する。

【0039】

記憶回路5は、信号88が論理「1」である場合に、クロック信号90と同期して、信号76,77,78,79から経過時間レジスタ33,34,35,36の値を取り込み、各部分回路3の総通電時間として記憶する。尚、タイミングレジスタ82、加算回路84、及びセレクタ83のビット幅は、記憶回路5への総通電時間の書き込み周期を勘案して設定されることが好ましい。例えば、ビット幅を8ビットにすると、信号88には256秒周期で論理「1」が1クロック期間出力され、256秒に1回の頻度で記憶回路5の内容が更新される。本発明は、記憶回路5に記憶される情報のビット幅及び単位、クロック信号90の周波数等について、様々なバリエーションを許容するものである。

【0040】

上記構成の半導体集積回路1によれば、複数の部分回路3のそれぞれの総通電時間が記憶される。そして、各総通電時間に基づいて、最も総通電時間が短い部分回路3を除く部分回路3に対応する電源遮断回路4が遮断され、最も総通電時間が短い部分回路3にのみ電源供給が行われる。これにより、各部分回路3の総通電時間の均等化を図ることができる。これにより、各部分回路3の経時劣化の偏りを防止することができ、部分回路3全体としての寿命を長期化することができる。また、上記構成によれば、半導体集積回路1の遅延設計において、過剰な設計マージンを確保する必要がなくなり、半導体集積回路1を構成するトランジスタ本来のスイッチング性能を十分に活かしたハイスペックな回路を提供することができる。更に、上記構成においては、冗長的な部分回路3の存在が外部に対して隠蔽されるため、ユーザが半導体集積回路1を使用する上で、部分回路3の選択や電源供給の制御に対する特別な知識や手順を必要としない。

【0041】

実施の形態2

図4は、本実施の形態に係る半導体集積回路101の機能的な構成を示している。本実施の形態に係る部分回路3−1,3−2,3−3,・・,3−nは、それぞれ内部状態移送回路110−1,110−2,110−3,・・,110−nを備えている。また、本実施の形態に係る電源供給制御手段106は、上記実施の形態1で示したように電源遮断回路4−1,4−2,4−3,・・,4−nを制御すると共に、内部状態移送回路110−1,110−2,110−3,・・,110−nを制御する。

【0042】

電源供給制御手段106は、使用(電源供給)している部分回路3−1,3−2,3−3,・・,3−nの総通電時間と、他の部分回路3−1,3−2,3−3,・・,3−nの総通電時間とを比較し、使用している部分回路3−1,3−2,3−3,・・,3−nの総通電時間が、他の部分回路3−1,3−2,3−3,・・,3−nの総通電時間よりも大きくなった時に、最も総通電時間が少ない部分回路3−1,3−2,3−3,・・,3−nに電源供給されるように、電源遮断回路4−1,4−2,4−3,・・,4−nに電源遮断制御信号11−1,11−2,11−3,11−4を出力する。

【0043】

また、電源供給制御手段106は、上記のように使用する部分回路3−1,3−2,3−3,・・,3−nを切り替える処理を実行する際に、使用していた部分回路3−1,3−2,3−3,・・,3−nの内部状態を、その後使用する部分回路3−1,3−2,3−3,・・,3−nに移送するために、内部状態移送回路110−1,110−2,110−3,・・,110−nに移送制御信号115−1,115−2,115−3,・・,115−nを出力する。

【0044】

内部状態移送回路110−1,110−2,110−3,・・,110−nは、移送制御信号115−1,115−2,115−3,・・,115−nに従い、部分回路3−1,3−2,3−3,・・,3−nの内部状態を示す移送信号116−1,116−2,116−3,・・,116−nを出力し、又出力された移送信号116−1,116−2,116−3,・・,116−nを入力して部分回路3−1,3−2,3−3,・・,3−nの内部状態として設定する。

【0045】

図5は、内部状態移送回路110(110−1,110−2,110−3,・・,110−n)の具体的な構成を例示している。本例に係る内部状態移送回路110は、部分回路3−1,3−2,3−3,・・,3−nの論理機能を構成する全てのフリップフロップ120が、システムクロック信号121に同期して動作する。移送制御信号115−1,115−2,115−3,・・,115−nの何れかが論理「1」となると、スキャンモード信号124が論理「1」となる。スキャンモード信号124は、全てのセレクタ125の選択制御入力Sに入力される。セレクタ124は、スキャンモード信号124が論理「1」になると、入力1からデータを取り込んで出力する。その結果、全てのフリップフロップ120は、論理的に直鎖状に接続され、1つのシフトレジスタとして機能するスキャンパスを構成する。この時、フリップフロップ120の数がスキャンパスのスキャンビット長となる。

【0046】

移送制御信号115−1,115−2,115−3,・・,115−nは、排他的に制御され、ある時点で全ての信号が論理「0」となるか、又は論理「1」となる。移送信号116−1,116−2,116−3,・・,116−nは、それぞれ移送制御信号115−1,115−2,115−3,・・,115−nとAND演算によりマスク処理される。即ち、移送信号116−1,116−2,116−3,・・,116−nのうち、それぞれ対応する移送制御信号115−1,115−2,115−3,・・,115−nが論理「1」となっているものが、移送信号130として選択され、出力される。スキャンモード信号124が論理「1」である場合、移送信号130の値は、システムクロック信号121に同期して、逐次スキャンパスのフリップフロップ120に取り込まれる。同時に、フリップフロップ120が保持していたデータ、即ち内部状態は、スキャンパスの最後のフリップフロップ120から移送信号131として出力される。

【0047】

図6は、本実施の形態に係る半導体集積回路101の記憶回路105及び電源遮断回路106の具体的構成を例示している。この例は、半導体集積回路101が4つの部分回路3(3−1,3−2,3−3,3−4)を備える場合を示している。

【0048】

本実施の形態においては、判定回路47,48,49,50の出力は、クロック信号90に同期して動作するフリップフロップ140,141,142,143に保持され、更にそれらの出力は、次のクロックサイクルでフリップフロップ144,145,146,147に保持される。

【0049】

電源遮断制御信号11−1,11−2,11−3,11−4は、フリップフロップ140,141,142,143の出力と、フリップフロップ144,145,146,147の出力とをAND演算することにより生成される。これらの入力の両者が論理「1」である場合に、電源供給を遮断する指示である論理「1」の信号を出力する。移送モード信号150は、論理演算により、フリップフロップ140,141,142,143の出力と、フリップフロップ144,145,146,147の出力とを比較し、値が一致しないものが1つでもある場合に、論理「1」となる。

【0050】

フリップフロップ155,156及びスキャン制御レジスタ157は、システムクロック信号121と同期して動作する。システムクロック信号121は、部分回路3−1,3−2,3−3,3−4の論理機能を実現するために使用されるクロックであり、クロック信号90よりも高い周波数を有する。移送モード信号150は、システムクロック信号121に同期してフリップフロップ155に入力され、その出力は次のクロックサイクルでフリップフロップ156に保持される。フリップフロップ155の出力が論理「1」であり、且つフリップフロップ156の出力が論理「0」である場合に、移送起動信号159が論理「1」となる。

【0051】

セレクタ161は、選択制御入力S1に入力された移送起動信号159が論理「1」である場合に、入力1Xを選択する。入力1Xには、部分回路3−1,3−2,3−3,3−4に内蔵されるスキャンパスのスキャンビット長(固定値)を与える。例えば、部分回路3−1,3−2,3−3,3−4内に511ビットのフリップフロップが存在し、511ビット長のスキャンパスを構成する場合には、数値511を2進法で入力1Xに与える。セレクタ161の出力は、スキャン制御レジスタ157に入力され、保持される。

【0052】

減算回路163は、スキャン制御レジスタ157の値から1を引いた値を出力する。移送実行信号165は、スキャン制御レジスタ157の値が0以外の場合に、論理「1」となる。移送起動信号159が論理「0」の場合、移送実行信号165が論理「1」ならば、セレクタ161は入力01から減算回路163の値を取り込んで出力し、移送実行信号165が論理「0」ならば、入力00からスキャン制御レジスタ157の値を取り込んで出力する。これにより、スキャン制御レジスタ157の値は、システムクロック信号121に同期して減じられ、値が0に達すると、次に移送起動信号159が論理「1」となるまでその状態を保持する。

【0053】

図7は、本実施の形態に係る半導体集積回路101の動作を示している。クロックサイクルT0において、第1の部分回路3−1が使用されており、第1の判定回路47の出力が論理「0」となっている。この時、使用されていない第2〜第4の部分回路3−2,3−3,3−4に対応する第2〜第4の判定回路48,49,50の出力は、論理「1」となる。この状態がクロックサイクルT0以前から継続していたと仮定すると、第1の部分回路3−1に対応するフリップフロップ140,144の出力は論理「0」となり、その他のフリップフロップ141,142,143,145,146,147の出力は論理「1」となる。これにより、第1の電源遮断制御信号11−1は、論理「0」となり、第1の部分回路3−1への電源供給の実行を指示する状態となる。また、第2〜第4の電源遮断制御信号11−2,11−3,11−4は、論理「1」となり、第2〜第4の部分回路3−2,3−3,3−4への電源供給の遮断を指示する状態となる。

【0054】

クロックサイクルT1において、第1の経過時間レジスタ33が第2の経過時間レジスタ34よりも所定値以上大きくなり、第1の判定回路47の出力が論理「1」となり、第2の判定回路48の出力が論理「0」となる。

【0055】

次いで、クロックサイクルT2において、両判定回路47,48の値がフリップフロップ140,141に取り込まれ、それぞれの値が論理「1」,「0」となる。この時、フリップフロップ144は、論理「0」を保っているため、第1の電源遮断制御信号11−1は論理「0」の状態、即ち第1の部分回路3−1への電源供給を実行する指示を継続する。一方、第2の電源遮断制御信号11−2は、フリップフロップ141が論理「0」に変化したことにより、論理「1」から「0」に遷移する。即ち、第2の部分回路3−2にも電源供給が実行される。また、これと同時に、移送モード信号150が、論理「0」から「1」へ遷移し、第1の部分回路3−1の内部状態を第2の部分回路3−2へ移送する処理(内部状態移送処理)が開始される。内部状態移送処理は、クロックサイクルT2において完了する。

【0056】

次いで、クロックサイクルT3において、フリップフロップ140,141の値が、フリップフロップ144,145に取り込まれ、それぞれの状態が反転する。その結果、第1の電源遮断制御信号11−1の状態が、論理「0」から「1」に遷移し、第1の部分回路3−1への電源供給が遮断される。これと同時に、移送モード信号150は、論理「1」から「0」に遷移し、内部状態移送処理が終了する。その後、クロックサイクルT4以降に各部の状態変化は起こらない。

【0057】

図8は、図7に示すタイムチャートにおけるクロックサイクルT2の動作を詳細に示すタイムチャートである。同図におけるクロックサイクルは、システムクロック信号121に対応している。クロックサイクルT0においては、移送モード信号150が論理「0」であり、内部状態移送処理は開始されていない。この時、フリップフロップ155,156は論理「0」を保ち、移送起動信号159も論理「0」の状態にある。そのため、スキャン制御レジスタ157の値は0となり、移送実行信号165及び第1〜第4の移送制御信号115−1,115−2,115−3,115−4は論理「0」となる。これにより、内部状態移送処理は実行されない。

【0058】

次いで、クロックサイクルT1において、移送モード信号150が論理「0」から「1」に遷移し、クロックサイクルT2において、フリップフロップ155がこれを取り込むことにより、移送起動信号159が論理「0」から「1」に遷移する。これにより、内部状態移送処理が開始する。

【0059】

次いで、クロックサイクルT3において、セレクタ161の入力1Xから第1の部分回路3−1のスキャンビット長が取り込まれ、スキャン制御レジスタ157に設定される。この例におけるスキャンビット長は511である。これにより、移送実行信号165が論理「1」に遷移し、これまで使用していた第1の部分回路3−1に対応する第1の移送制御信号115−1も論理「1」に遷移する。この時、他の移送制御信号115−2,115−3,115−4は、論理「0」の状態を保つ。その結果、この時点で電源供給されている第1及び第2の部分回路3−1,3−2は、次のクロックサイクル以降、第1の部分回路3−1の内部状態が第2の部分回路3−2へ逐次移送されるように動作する。また、クロックサイクルT3においては、フリップフロップ156が、フリップフロップ155の値を取り込んで論理「1」に遷移するため、移送起動信号159は論理「0」へと戻る。

【0060】

そして、クロックサイクルT4以降においては、スキャン制御レジスタ157の値がクロックサイクル毎に1つずつ減じられ、クロックサイクルT514において0となる。その結果、移送実行信号165は論理「0」に遷移し、第1の移送制御信号115−1も論理「0」に戻り、内部状態遷移処理が終了する。クロックサイクルT516以降は、スキャン制御レジスタ157の値が0に保たれ、次の移送モード信号150が論理「1」に遷移するまで、その状態が維持される。

【0061】

上記構成の半導体集積回路101によれば、上記実施の形態1による効果に加え、使用する部分回路3を切り替える際に、初期化等の処理を行わなくても、不具合を生ずることなく処理を継続することができる。本実施の形態に係る半導体集積回路101は、例えば稼働開始後に製品寿命に達するまで連続して稼働することが求められる製品等に、好適に利用することができる。

【0062】

尚、本発明は、上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。

【符号の説明】

【0063】

1,101 半導体集積回路

2 電源

3(3−1,3−2,3−3,・・,3−n) 部分回路

4(4−1,4−2,4−3,・・,4−n) 電源遮断回路

5 記憶回路

6,106 電源供給制御回路

11(11−1,11−2,11−3,・・,11−n) 電源遮断制御信号

110(110−1,110−2,110−3,・・,110−n) 内部状態移送手段

115(115−1,115−2,115−3,・・,115−n) 移送制御信号

【技術分野】

【0001】

本発明は、半導体集積回路に関し、特に冗長性を有する構成を制御する技術に関するものである。

【背景技術】

【0002】

半導体集積回路に使用されるトランジスタは、通常、HCI(Hot Carrier Injection)、NGTI(Negative Bias Temperature Instability)等の経時劣化特性を有し、通電(使用)時間に応じてスイッチング性能(応答速度)が低下するものである。半導体集積回路の用途によっては、長期間に渡ってトランジスタのスイッチング性能を高度に維持する必要がある。このような場合、想定される製品寿命に応じた経時劣化に相当するマージンを半導体集積回路の設計時に確保したり、性能維持が必要な部分回路を冗長化させたりする対策が取られる。

【0003】

特許文献1において、複数のHDD(Hard Disk Drive)を含んで構成されるディスクアレイ装置であって、マイクロコンピュータとファームウェアとの協働により、各HDDの通電時間を管理し、最も通電時間の長いHDDを予備ディスクとして設定する構成が開示されている。

【0004】

また、特許文献2において、少なくとも2つの同じ又は同種の機能ユニットを備えた半導体回路のコンフィギュレーション方法であって、各機能ユニットの欠陥を検出する手段を備え、欠陥があると判定された機能ユニットの電気的な接続を遮断する構成が開示されている。

【0005】

更に、特許文献3において、稼働中であっても故障診断が可能な診断回路を備える集積回路であって、論理回路の内部状態を保持し、診断後復帰させる構成が開示されている。

【0006】

更にまた、特許文献4において、サーマルヘッド用集積回路であって、複数の発熱抵抗体への通電時間を個別に制御する構成が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−293315号公報

【特許文献2】特表2009−514064号公報

【特許文献3】特開2006−300650号公報

【特許文献4】特開平11−277786号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記のように、長期信頼性が要求される半導体集積回路においては、経時劣化に対処するマージンを設計時に組み込む必要があるため、トランジスタ本来のスイッチング性能を十分に活かしたハイスペックな回路を提供することができないといった問題がある。また、長期信頼性が要求される部分回路を冗長化させる場合には、複数の部分回路のうち使用する部分回路を適切に選択しなければ、同一の部分回路が使用され続けることとなり、上記経時劣化の問題を解消することができない。

【0009】

また、特許文献1に開示される構成は、各HDDの通電時間を管理するために、ファームウェアにより制御されるマイクロコンピュータを必要とする。このような構成は、1つのコンピュータシステム内においてメイン制御システムとは別体に且つ交換可能に設置されるHDDを対象とする構成に適合するものであり、1つ又は少数のチップ上に部分回路が基本的に交換不可能に設置された半導体集積回路に適用する場合には、設計、コスト等の面で様々な不具合を生ずるものである。

【0010】

更に、特許文献2に開示される構成は、欠陥のある回路を非アクティブ状態にすることができるものであるが、回路(トランジスタ)の経時劣化を遅らせ、長寿命化を図ることはできない。

【0011】

そこで、本発明は、長期信頼性が要求される部分回路を備える半導体集積回路の長寿命化を図ることを目的とする。

【課題を解決するための手段】

【0012】

上記課題の解決を図る本発明の一態様は、同一又は同様の機能を有する複数の部分回路と、前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路とを備える半導体集積回路である。

【0013】

また、本発明の他の態様は、同一又は同様の機能を有する複数の部分回路と、前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、第1の前記部分回路への前記電源供給時であって、前記第1の部分回路の前記総通電時間が第2の前記部分回路の前記総通電時間を超えた場合に、前記第1の部分回路の内部状態を前記第2の部分回路に移送する内部状態移送回路とを備える半導体集積回路である。

【発明の効果】

【0014】

上記本発明の一態様によれば、各部分回路に対応する総通電時間に基づいて、最も総通電時間が短い部分回路にのみ電源供給が行われる。これにより、各部分回路の総通電時間の均等化を図ることができ、各部分回路の経時劣化の偏りを防止することができる。これにより、部分回路全体の長寿命化を図ることができる。また、上記本発明の他の態様によれば、上記効果に加え、使用する部分回路を切り替える際に、初期化等の処理を行わなくても、不具合を生ずることなく処理を継続することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施の形態1に係る半導体集積回路の機能的な構成を示すブロック図である。

【図2】実施の形態1に係る電源遮断回路の具体的な構成を例示する図である。

【図3】実施の形態1に係る記憶回路及び電源遮断制御回路の具体的な構成を例示する図である。

【図4】本発明の実施の形態2に係る半導体集積回路の機能的な構成を示すブロック図である。

【図5】実施の形態2に係る内部状態移送回路の具体的な構成を例示する図である。

【図6】実施の形態2に係る記憶回路及び電源遮断制御回路の具体的な構成を例示する図である。

【図7】実施の形態2に係る半導体集積回路の動作を示すタイムチャートである。

【図8】図7に示すタイムチャートにおけるクロックサイクルT2の動作を詳細に示すタイムチャートである。

【発明を実施するための形態】

【0016】

以下に、添付した図面を参照して本発明の実施の形態を説明する。尚、異なる実施の形態において、同一又は同様の作用効果を奏する箇所については同一の符号を付してその説明を省略する。

【0017】

実施の形態1

図1は、本実施の形態に係る半導体集積回路1の機能的な構成を示している。半導体集積回路1は、電源(電源配線)2、部分回路3−1,3−2,3−3,・・,3−n、電源遮断回路4−1,4−2,4−3,・・,4−n、記憶回路5、及び電源供給制御回路6を含む。

【0018】

電源2は、電力を発生させるバッテリ等の機構、又はバッテリ等と接続する配線に相当する。

【0019】

複数の部分回路3−1,3−2,3−3,・・,3−nは、それぞれ電源2からの電力供給により作動し、全て同一又は同様の機能を有するものである。各部分回路3−1,3−2,3−3,・・,3−nは、それぞれ独立の接続経路10−1,10−2,10−3,・・,10−nにより電源2と接続している。

【0020】

複数の電源遮断回路4−1,4−2,4−3,・・,4−nは、各接続経路10−1,10−2,10−3,・・,10−n上に接続され、各部分回路3−1,3−2,3−3,・・,3−nへの電源供給を独立に遮断可能なものである。各電源遮断回路4−1,4−2,4−3,・・,4−nは、電源供給制御回路6が出力する電源遮断制御信号11−1,11−2,11−3,・・,11−nにより制御される。

【0021】

記憶回路5は、各部分回路3−1,3−2,3−3,・・,3−nの電源供給を受けた時間の総和を示す総通電時間を、部分回路3−1,3−2,3−3,・・,3−n毎に記憶するものである。総通電時間は、例えば各電源遮断回路4−1,4−2,4−3,・・,4−nが対応する部分経路3−1,3−2,3−3,・・,3−nへの電源供給を遮断した時間(若しくは許可した時間)を、電源供給制御回路6の制御経過から把握すること等により、検知することができる。

【0022】

電源供給制御回路6は、記憶回路5に記憶された各部分回路3−1,3−2,3−3,・・,3−nの総通電時間に基づいて、総通電時間が最も短い部分回路3−1,3−2,3−3,・・,3−nのみに電源供給されるように、電源遮断回路4−1,4−2,4−3,・・,4−nを制御する電源遮断制御信号11−1,11−2,11−3,・・,11−nを出力する。

【0023】

図2は、電源遮断回路4(4−1,4−2,4−3,・・,4−n)の具体的な構成を例示している。電源遮断回路4は、複数のp−MOSトランジスタ15を含んで構成される。各p−MOSトランジスタ15のゲートには、電源供給制御回路6と接続する信号線16が接続されている。p−MOSトランジスタ15は、信号線16から入力される電源遮断制御信号11−1,11−2,11−3,・・,11−nが論理「1」である場合にOFFとなり、部分回路3への電源供給を遮断する。逆に、電源遮断制御信号11−1,11−2,11−3,・・,11−nが論理「0」である場合に、p−MOSトランジスタ15はONとなり、部分回路3への電源供給が行われる。

【0024】

図3は、記憶回路5及び電源遮断制御回路6の具体的な構成を例示している。この例は、半導体集積回路1が4つの部分回路3(3−1,3−2,3−3,3−4)を備える場合を示している。

【0025】

この例に係る記憶回路5は、各部分回路3の秒単位で表された総通電時間を記憶する。各部分回路3に32ビット幅の記憶領域を割り当てることにより、約136年間に相当する時間を扱うことができる。記憶回路5が出力する4つの32ビット幅の信号21,22,23,24は、それぞれ部分回路3の総通電時間を示す。

【0026】

半導体集積回路1の初期化時に、記憶回路5から読み出された信号21,22,23,24は、それぞれセレクタ27,28,29,30を経由して、経過時間レジスタ33,34,35,36に保持される。経過時間レジスタ33,34,35,36の出力は、比較回路39,40,41,42,43,44により比較される。これらの比較結果は、判定回路47,48,49,50に入力され、判定回路47,48,49,50は、組み合わせ論理により何れの部分回路3の総通電時間が最も短いかを判定する。各判定回路47,48,49,50は、各部分回路3に対応付けられている。そして、総通電時間が最も短い部分回路3に対応する判定回路47,48,49,50の出力は論理「0」となり、その他の判定回路47,48,49,50の出力は論理「1」となる。判定回路47,48,49,50の出力は、それぞれセレクタ53,54,55,56を経由してフリップフロップ59,60,61,62に保持される。各フリップフロップ59,60,61,62は、上述した電源遮断制御信号11−1,11−2,11−3,11−4を出力する。

【0027】

半導体集積回路1の初期化終了後には、セレクタ53,54,55,56は、それぞれフリップフロップ59,60,61,62の出力である電源遮断制御信号11−1,11−2,11−3,11−4を入力として選択し、フリップフロップ59,60,61,62に出力する。これにより、フリップフロップ59,60,61,62の値はそれ以降変化せず、電源遮断信号11−1,11−2,11−3,11−4の状態は維持される。

【0028】

加算回路70,71,72,73は、各経過時間レジスタ33,34,35,36の値に1を加えた値を出力する。半導体集積回路1の初期化終了後には、各セレクタ27,28,29,30は、電源遮断制御信号11−1,11−2,11−3,11−4の値に応じて、経過時間レジスタ33,34,35,36への出力を変化させる。即ち、各セレクタ27,28,29,30は、電源制御信号11−1,11−2,11−3,11−4が論理「0」の場合には、加算回路70,71,72,73の出力を経過時間レジスタ33,34,35,36への出力とし、電源制御信号11−1,11−2,11−3,11−4が論理「1」の場合には、経過時間レジスタ33,34,35,36の出力を経過時間レジスタ33,34,35,36への出力とする。これにより、電源遮断制御信号11−1,11−2,11−3,11−4が論理「1」となり電源供給が遮断された部分回路3に対応する経過時間レジスタ33,34,35,36の値は、保持される。一方、電源遮断制御信号11−1,11−2,11−3,11−4が論理「0」となり電源供給された部分回路3に対応する経過時間レジスタ33,34,35,36の値は、クロック信号に同期してカウントアップされる。

【0029】

経過時間レジスタ33,34,35,36の値は、信号76,77,78,79として記憶回路5に入力され、書き込まれる。タイミングレジスタ82は、半導体集積回路1の初期化時に固定値「0」がセレクタ83を経由して入力され、これを保持する。初期化終了後には、加算回路84がタイミングレジスタ82の値に1を加えた値を出力し、セレクタ83が加算回路84の出力を選択してタイミングレジスタ82に出力する。これにより、タイミングレジスタ82の値は、クロック信号に同期してカウントアップされる。

【0030】

ライト制御回路87は、タイミングレジスタ82の全てのビットのAND演算により、記憶回路5への書き込み指示である信号88を生成する。記憶回路5は、信号88が論理「1」である場合に、クロック信号90に同期して、信号76,77,78,79から経過時間レジスタ33,34,35,36の値を取り込み、各部分回路3(3−1,3−2,3−3,3−4)の総通電時間として記憶する。

【0031】

上記構成において、電源供給制御回路6は、クロック信号90に同期して動作する。クロック信号90は、総通電時間を積算する際の基準時間としても使用され、例えばその周波数を1Hzとすることが好ましい。

【0032】

記憶回路5が出力する各信号21,22,23,24は、セレクタ27,28,29,30の入力1Xに入力される。半導体集積回路1の使用開始時にリセット信号91が論理「1」となると、セレクタ27,28,29,30の入力1Xの値が選択され、これらの値が各経過時間レジスタ33,34,35,36に入力される。経過時間レジスタ33,34,35,36は、クロック信号90に同期して、各セレクタ27,28,29,30が出力した値を入力して保持する。

【0033】

セレクタ27,28,29,30は、リセット信号91が論理「0」である場合に、入力S0に入力される電源遮断制御信号11−1,11−2,11−3,11−4が論理「1」であるならば、入力01に入力される経過時間レジスタ33,34,35,36の出力を選択して出力する。

【0034】

加算回路70,71,72,73は、経過時間レジスタ33,34,35,36の値に1を加算した値を出力する。セレクタ27,28,29,30は、リセット信号91が論理「0」である場合に、入力S0に入力された電源遮断制御信号11−1,11−2,11−3,11−4が論理「0」であるならば、入力00に入力された加算回路70,71,72,73の出力を選択して出力する。加算回路70,71,72,73、セレクタ27,28,29,30、及び経過時間レジスタ33,34,35,36は、記憶回路5が出力する信号21,22,23,24と同じビット幅のデータを扱うものとする。

【0035】

比較回路39,40,41,42,43,44は、経過時間レジスタ33,34,35,36の出力を比較し、入力Aの値が入力Bの値以下である場合に、論理「1」を出力する。比較回路39,40,41,42,43,44が比較するデータのビット幅を、経過時間レジスタ33,34,35,36のビット幅より小さくすることにより、回路規模を縮小することが可能となる。例えば、32ビットのデータのうち、上位16ビットを比較対象とすると、判定の粒度は、35536秒(約18時間)となる。

【0036】

判定回路47,48,49,50は、NAND回路で構成され、比較回路39,40,41,42,43,44の出力から最も総通電時間の短い部分回路3を判定する。判定回路47,48,49,50は、それぞれ部分回路3(3−1,3−2,3−3,3−4)に対応しており、最も総通電時間が短い部分回路3に対応する判定回路47,48,49,50の出力が論理「0」となり、その他の出力が論理「1」となる。判定回路47,48,49,50の出力は、それぞれセレクタ53,54,55,56の入力1に入力され、半導体集積回路1の使用開始時にリセット信号91が論理「1」になると、セレクタ53,54,55,56の入力1の値が選択され、フリップフロップ59,60,61,62に出力される。フリップフロップ59,60,61,62は、クロック信号90に同期して、各セレクタ53,54,55,56が出力した値を入力して保持する。

【0037】

フリップフロップ59,60,61,62は、電源遮断制御信号65,66,67,68を出力する。セレクタ53,54,55,56は、リセット信号91が論理「0」である場合に、電源遮断制御信号11−1,11−2,11−3,11−4が入力される入力0の値を選択し、出力する。リセット信号91が倫理「1」の場合には、セレクタ53,54,55,56は入力1の値が0の固定値を選択し、これを出力する。

【0038】

タイミングレジスタ82は、クロック信号90に同期して、セレクタ83の出力を入力し、これを保持する。加算回路84は、タイミングレジスタ82の値に1を加えた値を出力する。リセット信号91が論理「0」である場合には、セレクタ83の入力0を選択し、加算回路84の値を出力する。ライト制御回路87は、タイミングレジスタ82の全てのビットのANDを求め、その結果を信号88として出力する。

【0039】

記憶回路5は、信号88が論理「1」である場合に、クロック信号90と同期して、信号76,77,78,79から経過時間レジスタ33,34,35,36の値を取り込み、各部分回路3の総通電時間として記憶する。尚、タイミングレジスタ82、加算回路84、及びセレクタ83のビット幅は、記憶回路5への総通電時間の書き込み周期を勘案して設定されることが好ましい。例えば、ビット幅を8ビットにすると、信号88には256秒周期で論理「1」が1クロック期間出力され、256秒に1回の頻度で記憶回路5の内容が更新される。本発明は、記憶回路5に記憶される情報のビット幅及び単位、クロック信号90の周波数等について、様々なバリエーションを許容するものである。

【0040】

上記構成の半導体集積回路1によれば、複数の部分回路3のそれぞれの総通電時間が記憶される。そして、各総通電時間に基づいて、最も総通電時間が短い部分回路3を除く部分回路3に対応する電源遮断回路4が遮断され、最も総通電時間が短い部分回路3にのみ電源供給が行われる。これにより、各部分回路3の総通電時間の均等化を図ることができる。これにより、各部分回路3の経時劣化の偏りを防止することができ、部分回路3全体としての寿命を長期化することができる。また、上記構成によれば、半導体集積回路1の遅延設計において、過剰な設計マージンを確保する必要がなくなり、半導体集積回路1を構成するトランジスタ本来のスイッチング性能を十分に活かしたハイスペックな回路を提供することができる。更に、上記構成においては、冗長的な部分回路3の存在が外部に対して隠蔽されるため、ユーザが半導体集積回路1を使用する上で、部分回路3の選択や電源供給の制御に対する特別な知識や手順を必要としない。

【0041】

実施の形態2

図4は、本実施の形態に係る半導体集積回路101の機能的な構成を示している。本実施の形態に係る部分回路3−1,3−2,3−3,・・,3−nは、それぞれ内部状態移送回路110−1,110−2,110−3,・・,110−nを備えている。また、本実施の形態に係る電源供給制御手段106は、上記実施の形態1で示したように電源遮断回路4−1,4−2,4−3,・・,4−nを制御すると共に、内部状態移送回路110−1,110−2,110−3,・・,110−nを制御する。

【0042】

電源供給制御手段106は、使用(電源供給)している部分回路3−1,3−2,3−3,・・,3−nの総通電時間と、他の部分回路3−1,3−2,3−3,・・,3−nの総通電時間とを比較し、使用している部分回路3−1,3−2,3−3,・・,3−nの総通電時間が、他の部分回路3−1,3−2,3−3,・・,3−nの総通電時間よりも大きくなった時に、最も総通電時間が少ない部分回路3−1,3−2,3−3,・・,3−nに電源供給されるように、電源遮断回路4−1,4−2,4−3,・・,4−nに電源遮断制御信号11−1,11−2,11−3,11−4を出力する。

【0043】

また、電源供給制御手段106は、上記のように使用する部分回路3−1,3−2,3−3,・・,3−nを切り替える処理を実行する際に、使用していた部分回路3−1,3−2,3−3,・・,3−nの内部状態を、その後使用する部分回路3−1,3−2,3−3,・・,3−nに移送するために、内部状態移送回路110−1,110−2,110−3,・・,110−nに移送制御信号115−1,115−2,115−3,・・,115−nを出力する。

【0044】

内部状態移送回路110−1,110−2,110−3,・・,110−nは、移送制御信号115−1,115−2,115−3,・・,115−nに従い、部分回路3−1,3−2,3−3,・・,3−nの内部状態を示す移送信号116−1,116−2,116−3,・・,116−nを出力し、又出力された移送信号116−1,116−2,116−3,・・,116−nを入力して部分回路3−1,3−2,3−3,・・,3−nの内部状態として設定する。

【0045】

図5は、内部状態移送回路110(110−1,110−2,110−3,・・,110−n)の具体的な構成を例示している。本例に係る内部状態移送回路110は、部分回路3−1,3−2,3−3,・・,3−nの論理機能を構成する全てのフリップフロップ120が、システムクロック信号121に同期して動作する。移送制御信号115−1,115−2,115−3,・・,115−nの何れかが論理「1」となると、スキャンモード信号124が論理「1」となる。スキャンモード信号124は、全てのセレクタ125の選択制御入力Sに入力される。セレクタ124は、スキャンモード信号124が論理「1」になると、入力1からデータを取り込んで出力する。その結果、全てのフリップフロップ120は、論理的に直鎖状に接続され、1つのシフトレジスタとして機能するスキャンパスを構成する。この時、フリップフロップ120の数がスキャンパスのスキャンビット長となる。

【0046】

移送制御信号115−1,115−2,115−3,・・,115−nは、排他的に制御され、ある時点で全ての信号が論理「0」となるか、又は論理「1」となる。移送信号116−1,116−2,116−3,・・,116−nは、それぞれ移送制御信号115−1,115−2,115−3,・・,115−nとAND演算によりマスク処理される。即ち、移送信号116−1,116−2,116−3,・・,116−nのうち、それぞれ対応する移送制御信号115−1,115−2,115−3,・・,115−nが論理「1」となっているものが、移送信号130として選択され、出力される。スキャンモード信号124が論理「1」である場合、移送信号130の値は、システムクロック信号121に同期して、逐次スキャンパスのフリップフロップ120に取り込まれる。同時に、フリップフロップ120が保持していたデータ、即ち内部状態は、スキャンパスの最後のフリップフロップ120から移送信号131として出力される。

【0047】

図6は、本実施の形態に係る半導体集積回路101の記憶回路105及び電源遮断回路106の具体的構成を例示している。この例は、半導体集積回路101が4つの部分回路3(3−1,3−2,3−3,3−4)を備える場合を示している。

【0048】

本実施の形態においては、判定回路47,48,49,50の出力は、クロック信号90に同期して動作するフリップフロップ140,141,142,143に保持され、更にそれらの出力は、次のクロックサイクルでフリップフロップ144,145,146,147に保持される。

【0049】

電源遮断制御信号11−1,11−2,11−3,11−4は、フリップフロップ140,141,142,143の出力と、フリップフロップ144,145,146,147の出力とをAND演算することにより生成される。これらの入力の両者が論理「1」である場合に、電源供給を遮断する指示である論理「1」の信号を出力する。移送モード信号150は、論理演算により、フリップフロップ140,141,142,143の出力と、フリップフロップ144,145,146,147の出力とを比較し、値が一致しないものが1つでもある場合に、論理「1」となる。

【0050】

フリップフロップ155,156及びスキャン制御レジスタ157は、システムクロック信号121と同期して動作する。システムクロック信号121は、部分回路3−1,3−2,3−3,3−4の論理機能を実現するために使用されるクロックであり、クロック信号90よりも高い周波数を有する。移送モード信号150は、システムクロック信号121に同期してフリップフロップ155に入力され、その出力は次のクロックサイクルでフリップフロップ156に保持される。フリップフロップ155の出力が論理「1」であり、且つフリップフロップ156の出力が論理「0」である場合に、移送起動信号159が論理「1」となる。

【0051】

セレクタ161は、選択制御入力S1に入力された移送起動信号159が論理「1」である場合に、入力1Xを選択する。入力1Xには、部分回路3−1,3−2,3−3,3−4に内蔵されるスキャンパスのスキャンビット長(固定値)を与える。例えば、部分回路3−1,3−2,3−3,3−4内に511ビットのフリップフロップが存在し、511ビット長のスキャンパスを構成する場合には、数値511を2進法で入力1Xに与える。セレクタ161の出力は、スキャン制御レジスタ157に入力され、保持される。

【0052】

減算回路163は、スキャン制御レジスタ157の値から1を引いた値を出力する。移送実行信号165は、スキャン制御レジスタ157の値が0以外の場合に、論理「1」となる。移送起動信号159が論理「0」の場合、移送実行信号165が論理「1」ならば、セレクタ161は入力01から減算回路163の値を取り込んで出力し、移送実行信号165が論理「0」ならば、入力00からスキャン制御レジスタ157の値を取り込んで出力する。これにより、スキャン制御レジスタ157の値は、システムクロック信号121に同期して減じられ、値が0に達すると、次に移送起動信号159が論理「1」となるまでその状態を保持する。

【0053】

図7は、本実施の形態に係る半導体集積回路101の動作を示している。クロックサイクルT0において、第1の部分回路3−1が使用されており、第1の判定回路47の出力が論理「0」となっている。この時、使用されていない第2〜第4の部分回路3−2,3−3,3−4に対応する第2〜第4の判定回路48,49,50の出力は、論理「1」となる。この状態がクロックサイクルT0以前から継続していたと仮定すると、第1の部分回路3−1に対応するフリップフロップ140,144の出力は論理「0」となり、その他のフリップフロップ141,142,143,145,146,147の出力は論理「1」となる。これにより、第1の電源遮断制御信号11−1は、論理「0」となり、第1の部分回路3−1への電源供給の実行を指示する状態となる。また、第2〜第4の電源遮断制御信号11−2,11−3,11−4は、論理「1」となり、第2〜第4の部分回路3−2,3−3,3−4への電源供給の遮断を指示する状態となる。

【0054】

クロックサイクルT1において、第1の経過時間レジスタ33が第2の経過時間レジスタ34よりも所定値以上大きくなり、第1の判定回路47の出力が論理「1」となり、第2の判定回路48の出力が論理「0」となる。

【0055】

次いで、クロックサイクルT2において、両判定回路47,48の値がフリップフロップ140,141に取り込まれ、それぞれの値が論理「1」,「0」となる。この時、フリップフロップ144は、論理「0」を保っているため、第1の電源遮断制御信号11−1は論理「0」の状態、即ち第1の部分回路3−1への電源供給を実行する指示を継続する。一方、第2の電源遮断制御信号11−2は、フリップフロップ141が論理「0」に変化したことにより、論理「1」から「0」に遷移する。即ち、第2の部分回路3−2にも電源供給が実行される。また、これと同時に、移送モード信号150が、論理「0」から「1」へ遷移し、第1の部分回路3−1の内部状態を第2の部分回路3−2へ移送する処理(内部状態移送処理)が開始される。内部状態移送処理は、クロックサイクルT2において完了する。

【0056】

次いで、クロックサイクルT3において、フリップフロップ140,141の値が、フリップフロップ144,145に取り込まれ、それぞれの状態が反転する。その結果、第1の電源遮断制御信号11−1の状態が、論理「0」から「1」に遷移し、第1の部分回路3−1への電源供給が遮断される。これと同時に、移送モード信号150は、論理「1」から「0」に遷移し、内部状態移送処理が終了する。その後、クロックサイクルT4以降に各部の状態変化は起こらない。

【0057】

図8は、図7に示すタイムチャートにおけるクロックサイクルT2の動作を詳細に示すタイムチャートである。同図におけるクロックサイクルは、システムクロック信号121に対応している。クロックサイクルT0においては、移送モード信号150が論理「0」であり、内部状態移送処理は開始されていない。この時、フリップフロップ155,156は論理「0」を保ち、移送起動信号159も論理「0」の状態にある。そのため、スキャン制御レジスタ157の値は0となり、移送実行信号165及び第1〜第4の移送制御信号115−1,115−2,115−3,115−4は論理「0」となる。これにより、内部状態移送処理は実行されない。

【0058】

次いで、クロックサイクルT1において、移送モード信号150が論理「0」から「1」に遷移し、クロックサイクルT2において、フリップフロップ155がこれを取り込むことにより、移送起動信号159が論理「0」から「1」に遷移する。これにより、内部状態移送処理が開始する。

【0059】

次いで、クロックサイクルT3において、セレクタ161の入力1Xから第1の部分回路3−1のスキャンビット長が取り込まれ、スキャン制御レジスタ157に設定される。この例におけるスキャンビット長は511である。これにより、移送実行信号165が論理「1」に遷移し、これまで使用していた第1の部分回路3−1に対応する第1の移送制御信号115−1も論理「1」に遷移する。この時、他の移送制御信号115−2,115−3,115−4は、論理「0」の状態を保つ。その結果、この時点で電源供給されている第1及び第2の部分回路3−1,3−2は、次のクロックサイクル以降、第1の部分回路3−1の内部状態が第2の部分回路3−2へ逐次移送されるように動作する。また、クロックサイクルT3においては、フリップフロップ156が、フリップフロップ155の値を取り込んで論理「1」に遷移するため、移送起動信号159は論理「0」へと戻る。

【0060】

そして、クロックサイクルT4以降においては、スキャン制御レジスタ157の値がクロックサイクル毎に1つずつ減じられ、クロックサイクルT514において0となる。その結果、移送実行信号165は論理「0」に遷移し、第1の移送制御信号115−1も論理「0」に戻り、内部状態遷移処理が終了する。クロックサイクルT516以降は、スキャン制御レジスタ157の値が0に保たれ、次の移送モード信号150が論理「1」に遷移するまで、その状態が維持される。

【0061】

上記構成の半導体集積回路101によれば、上記実施の形態1による効果に加え、使用する部分回路3を切り替える際に、初期化等の処理を行わなくても、不具合を生ずることなく処理を継続することができる。本実施の形態に係る半導体集積回路101は、例えば稼働開始後に製品寿命に達するまで連続して稼働することが求められる製品等に、好適に利用することができる。

【0062】

尚、本発明は、上記実施の形態に限られるものではなく、趣旨を逸脱しない範囲で適宜変更することが可能なものである。

【符号の説明】

【0063】

1,101 半導体集積回路

2 電源

3(3−1,3−2,3−3,・・,3−n) 部分回路

4(4−1,4−2,4−3,・・,4−n) 電源遮断回路

5 記憶回路

6,106 電源供給制御回路

11(11−1,11−2,11−3,・・,11−n) 電源遮断制御信号

110(110−1,110−2,110−3,・・,110−n) 内部状態移送手段

115(115−1,115−2,115−3,・・,115−n) 移送制御信号

【特許請求の範囲】

【請求項1】

同一又は同様の機能を有する複数の部分回路と、

前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、

前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、

前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、

を備える半導体集積回路。

【請求項2】

同一又は同様の機能を有する複数の部分回路と、

前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、

前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、

前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、

第1の前記部分回路への前記電源供給時であって、前記第1の部分回路の前記総通電時間が第2の前記部分回路の前記総通電時間を超えた場合に、前記第1の部分回路の内部状態を前記第2の部分回路に移送する内部状態移送回路と、

を備える半導体集積回路。

【請求項3】

前記電源供給制御回路は、論理回路の組み合わせにより構成される、

請求項1又は2に記載の半導体集積回路。

【請求項1】

同一又は同様の機能を有する複数の部分回路と、

前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、

前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、

前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、

を備える半導体集積回路。

【請求項2】

同一又は同様の機能を有する複数の部分回路と、

前記部分回路が電源供給を受けた総通電時間を、前記部分回路毎に記憶する記憶回路と、

前記部分回路への前記電源供給を、前記部分回路毎に遮断可能な電源遮断回路と、

前記記憶回路に記憶された前記各総通電時間を参照し、前記総通電時間が最も短い前記部分回路を除く前記部分回路への前記電源供給を遮断するように、前記電源遮断回路を制御する電源供給制御回路と、

第1の前記部分回路への前記電源供給時であって、前記第1の部分回路の前記総通電時間が第2の前記部分回路の前記総通電時間を超えた場合に、前記第1の部分回路の内部状態を前記第2の部分回路に移送する内部状態移送回路と、

を備える半導体集積回路。

【請求項3】

前記電源供給制御回路は、論理回路の組み合わせにより構成される、

請求項1又は2に記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−141640(P2011−141640A)

【公開日】平成23年7月21日(2011.7.21)

【国際特許分類】

【出願番号】特願2010−989(P2010−989)

【出願日】平成22年1月6日(2010.1.6)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成23年7月21日(2011.7.21)

【国際特許分類】

【出願日】平成22年1月6日(2010.1.6)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]