半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路およびその検査方法に係り、特に、発振回路を有する半導体集積回路およびその検査方法に係る。

【背景技術】

【0002】

分周回路を含む発振回路を内蔵する半導体集積回路を製造するにあたって、この分周回路の特性を検査することが必要である。半導体集積回路に内蔵される分周回路を検査するにあたって、この分周回路が生成する分周信号を、半導体集積回路の外部に用意された検査装置が生成する理想的な信号と比較する方法がある。

【0003】

上記に関連して、特許文献1(特開2001−274337号公報)には、高周波用半導体装置に係る記載が開示されている。この高周波用半導体装置は、高周波信号発生回路と、分周回路と、第1外部端子と、第2外部端子と、第3外部端子とを有する。ここで、高周波信号発生回路は、高周波信号を発生する。分周回路は、入力される信号を所定の比で分周して出力する。第1外部端子は、この高周波信号発生回路で発生した高周波信号を外部に導出するためのものである。第2の外部端子は、分周回路の入力に接続され、且つ第1外部端子と接続可能に設けられている。第3外部端子は、分周回路の出力に接続され測定用端子となる。

【0004】

また、特許文献2(特開2001−298158号公報)には、半導体集積回路に係る記載が開示されている。ここで、特許文献2の半導体集積回路を従来技術として説明する。

【0005】

図1は、従来技術による半導体集積回路の構成を示すブロック図である。図1の半導体集積回路の構成について説明する。図1の半導体集積回路は、第1の信号入力部1と、第1の信号出力部2と、第2〜第5の信号入力部3〜6と、発振回路10と、判定回路30と、第2の信号出力部40とを具備している。判定回路30は、分周回路300と、サンプリング回路301と、期待値出力回路302と、検査信号発生回路303と、比較回路304とを具備している。

【0006】

図1の半導体集積回路の動作について説明する。第3の入力部4は、外部からリセット信号S4を入力する。分周回路300、期待値出力回路302および検査信号発生回路303は、リセット信号S4に応じてそれぞれリセットされて同期する。第1の入力部1は、外部から発振制御信号S1を入力する。発振回路10は、発振制御信号S1に基づく周波数を有する信号を生成し、入力クロック信号S10として出力する。第1の出力部2は、入力クロック信号S10を外部へ出力する。分周回路300は、発振信号S10を分周し、分周クロック信号S300として出力する。第4の入力部5は、外部からサンプリング制御信号S5を入力する。サンプリング回路301は、サンプリング制御信号S5に基づいて分周クロック信号S300をサンプリングし、サンプリングクロック信号S301として出力する。第2の入力部3は、外部から期待値制御信号S3を入力する。期待値出力回路302は、期待値制御信号S3に基づいて期待値信号S302を生成する。第5の入力部6は、外部から検査制御信号S6を入力する。検査信号発生回路303は、検査制御信号S6に基づいて検査信号S303を生成する。比較回路304は、サンプリングクロック信号S301および期待値信号S302の比較処理を行い、その結果を判定結果S40として出力する。ここで、比較回路304は、比較処理として、検査信号S303に応じて、一致比較処理または比較除外処理を行う。第2の出力部40は、判定結果S40を外部へ出力する。

【0007】

また、特許文献3(特開2002−41178号公報)には、半導体集積回路装置に係る記載が開示されている。この半導体集積回路装置は、PLL(Phase Locked Loop:位相同期ループ)回路と、分周器と、PLLシフトレジスタと、判定回路とを備えている。ここで、PLL回路は、入力クロック信号を入力とする。分周器は、PLL回路より出力されたPLL出力クロック信号を分周する。シフトレジスタは、分周器より出力された分周クロック信号をデータ入力とし、入力クロック信号をクロック入力とする。判定回路は、入力クロック信号に同期してシフトレジスタの各段よりそれぞれ出力されるデータ出力信号を入力とし、各データ出力信号の状態の組み合わせを基にPLL回路が正常に動作しているか否かを判定し、判定結果信号を外部へ出力する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2001−274337号公報

【特許文献2】特開2001−298158号公報

【特許文献3】特開2002−41178号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

従来技術では、PLL回路を含む発振回路の検査を行う前提として、この発振回路が生成する信号の周波数を検査対象としている。この場合、PLL回路の内部で生成され使用されるその他の信号、すなわちリファレンス周波数信号および比較周波数信号についても、従来技術では、その周波数のみが検査対象となるが、これでは十分な検査が出来ない。

【0010】

リファレンス周波数信号および比較周波数信号は、それぞれに対応する発振回路が生成する信号を分周することで生成される。この分周処理は、論理回路で構成したカウンタである分周回路を用いて行う。ただし、リファレンス周波数信号および比較周波数信号のそれぞれにおける、1周期ごとのいわゆるHigh区間長およびいわゆるLow区間長は、PLL回路が求める周波数ごとに設定変更する必要がある。そして、周波数のみを検査する従来技術では、High区間長およびLow区間長が異なる場合を考慮出来ない。したがって、従来技術では、PLL回路の内部においてリファレンス周波数信号および比較周波数信号が正しく生成されているかどうかを検査することが出来ない。

【0011】

また、従来技術では、検査対象である信号の比較対象として用いる制御信号を、外部から入力する必要がある。この制御信号は、検査対象である信号と位相などのタイミングを合わせて生成供給する必要があるため、結果的に高価な検査装置が必要となる。

【0012】

さらに、従来技術では、半導体集積回路の外部から制御信号を入力する必要があるので、半導体集積回路をプリント基板などに実装した状態での検査が不可能である。これは、従来技術が、半導体集積回路の製造工程での検査を前提としているからである。

【課題を解決するための手段】

【0013】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0014】

本発明による半導体集積回路は、発振回路(21または26)と、分周回路(22または27)と、自己診断回路(28)とを具備する。ここで、発振回路(21または26)は、発振周波数信号(SIG1またはSIG3)を生成する。分周回路(22または27)は、発振周波数信号(SIG1またはSIG3)を所定の係数(1/Rまたは1/N)で分周して、分周信号(SIG2またはSIG4)を生成する。自己診断回路(28)は、発振周波数信号(SIG1またはSIG3)、分周信号(21または26)および2つの基準値(SIG5およびSIG6)に基づいて分周回路(22または27)の特性を判定する。係数(1/Rまたは1/N)の逆数は、2つの基準値(SIG5およびSIG6)の和に等しい。自己診断回路(28)は、第1区間カウンタ回路(65)と、第1区間カウンタ回路(66)と、第1区間期待値比較回路(67)と、第2区間期待値比較回路(68)とを具備する。ここで、第1区間カウンタ回路(65)は、分周信号(21または26)の1周器の中で第1の論理状態である時間である第1区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントする。第2区間カウンタ回路(66)は、分周信号(21または26)の1周器の中で第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントする。第1区間期待値比較回路(67)は、第1のカウント結果を、2つの基準値(SIG5およびSIG6)の一方である第1区間期待値信号(SIG5)と比較する。第2区間期待値比較回路(68)は、第2区間のカウント結果を、2つの基準値(SIG5およびSIG6)の他方である第2区間期待値信号(SIG6)と比較する。

【0015】

本発明による半導体集積回路の検査方法は、発振周波数信号(SIG1またはSIG3)を生成するステップと、分周回路(22または26)が発振周波数信号(SIG1またはSIG3)を分周して、分周信号(SIG2またはSIG4)を生成するステップと、発振周波数信号(SIG1またはSIG3)、分周信号(SIG2またはSIG4)および2つの基準値(SIG5およびSIG6)に基づいて、分周回路(22または26)の特性を判定するステップとを具備する。分周回路(22または26)の特性を判定するステップは、分周信号(SIG2またはSIG4)の1周器の中で第1の論理状態である時間である第1区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントするステップと、分周信号(SIG2またはSIG4)の1周器の中で第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントするステップと、第1区間のカウント結果を、2つの基準値(SIG5およびSIG6)の一方である第1区間期待値信号(SIG5)と比較するステップと、第2区間のカウント結果を、2つの基準値(SIG5およびSIG6))の他方である第2区間期待値信号(SIG6)と比較するステップとを具備する。

【発明の効果】

【0016】

本発明によれば、分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわちいわゆるHigh区間およびいわゆるLow区間の比率、の2つに対して行うことが出来る。外部からはデューティー比を定義する2つの期待値を用い、比較対象となる理想的な信号を用いる高価な検査装置は不要である。

【図面の簡単な説明】

【0017】

【図1】図1は、従来技術による半導体集積回路の構成を示すブロック図である。

【図2】図2は、本発明の第1の実施形態による半導体集積回路の全体的な構成を概略的に示すブロック図である。

【図3】図3は、本発明でも用いる一般的なPLLシンセサイザ回路20の構成を示すブロック図である。

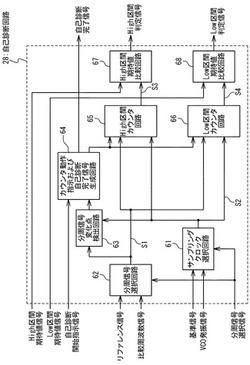

【図4】図4は、本発明の第1の実施形態による自己診断回路28の詳細な構成を示すブロック図である。

【図5】図5は、本発明の第1の実施形態による自己診断回路28の動作を示すタイミングチャートである。

【図6】図6は、本発明の第1の実施形態による半導体集積回路における、任意のクロック信号と、このクロック信号を一般的な分周回路で分周した分周信号との、時間軸上の関係を示すタイミングチャートである。

【図7】図7は、本発明の第2の実施形態による自己診断回路28の構成を示すブロック図である。

【発明を実施するための形態】

【0018】

添付図面を参照して、本発明による半導体集積回路およびその検査方法を実施するための形態を以下に説明する。

【0019】

(第1の実施形態)

本発明による半導体集積回路およびその検査方法は、PLL回路を含む分周信号を生成する論理回路を有する半導体集積回路に対して、分周機能が正しく動作しているかどうかを自己判定する機能を提供する。この自己判定する機能は、期待値を外部より入力し、半導体集積回路の内部で分周信号の波形の状態を測定し、判定結果を外部へ出力することを可能にする。

【0020】

この自己判定する方法について概略的に説明する。まず、発振信号および判定対象である分周信号を判定回路に入力する。次に、判定対象である分周信号のHigh区間およびLow区間のそれぞれを、発振信号でカウントする。これらのカウント結果と、半導体集積回路の外部より入力するHigh区間期待値およびLow区間期待値とが一致するかどうか、それぞれ比較する。これらの比較結果を、半導体集積回路の外部に向けて出力する。

【0021】

図2は、本発明の第1の実施形態による半導体集積回路の全体的な構成を概略的に示すブロック図である。図2の半導体集積回路の構成について説明する。図2の半導体集積回路は、PLLシンセサイザ回路20と、自己診断回路28と、外部とのインターフェイス29とを具備している。

【0022】

図2の半導体集積回路の構成の接続関係について説明する。自己診断回路28における第1〜第4の入力部は、PLLシンセサイザ回路20における第1〜第4の出力部に接続されている。自己診断回路28における第5〜第8の入力部は、インターフェイス29における第1〜第4の出力部にそれぞれ接続されている。インターフェイス29における第1〜第3の入力部は、自己診断回路28における第1〜3の出力部にそれぞれ接続されている。なお、インターフェイス29は、外部との接続を行う入出力部をさらに具備するが、本実施形態による半導体集積回路の本質とは関係が薄いので詳細な説明を省略する。インターフェイス29の具体例としては、パラレルインターフェイス、I2C−Busインターフェイスなどを用いることが可能であり、必要な信号の入出力さえ可能であれば特に限定は無い。

【0023】

図2の半導体集積回路の全体的な動作、すなわち本実施形態による半導体集積回路の検査方法について概略的に説明する。PLLシンセサイザ回路20は、基準信号SIG1、リファレンス信号SIG2、VCO(Voltage Controlled Oscillator:電圧制御発振器)発振信号SIG3および比較周波数信号SIG4を生成し、第1〜第4の出力部からそれぞれ出力する。自己診断回路28は、基準信号SIG1、リファレンス信号SIG2、VCO発振信号SIG3および比較周波数信号SIG4を、第1〜第4の入力部からそれぞれ入力する。また、自己診断回路28は、High区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7および自己診断開始指示信号SIG8を、第5〜第8の入力部からそれぞれ入力する。自己診断回路28は、上記8つの信号に基づいて、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11を生成し、第1〜第3の出力部からそれぞれ出力する。インターフェイス29は、High区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7および自己診断開始指示信号SIG8を外部から入力し、第1〜第4の出力部からそれぞれ出力する。また、インターフェイス29は、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11を第1〜第3の入力部から入力し、外部へ出力する。

【0024】

図2のPLLシンセサイザ回路20ならびに基準信号SIG1、リファレンス信号SIG2、VCO発振信号SIG3および比較周波数信号SIG4について詳細に説明する。図3は、本発明でも用いる一般的なPLLシンセサイザ回路20の構成を示すブロック図である。図3のPLLシンセサイザ回路20は、図2からPLLシンセサイザ回路20の部分を抜き出したものであって、同じ構成要素および同じ信号に同じ符号を用いている。図3のPLLシンセサイザ回路20の構成について説明する。図3のPLLシンセサイザ回路20は、発振器(OSC:OSCillator)21と、リファレンスディバイダ(1/R)22と、位相比較器23と、チャージポンプ24と、LPF(Low Pass Filter:ローパスフィルタ)25と、VCO26と、プログラマブルディバイダ(1/N)27とを具備している。

【0025】

図3のPLLシンセサイザ回路20における構成要素の接続関係について説明する。OSC21の出力部は、リファレンスディバイダ22の入力部に接続されている。リファレンスディバイダ22の出力部は、位相比較器23における第1の入力部に接続されている。位相比較器23における第1、第2の出力部は、チャージポンプ24における第1、第2の入力部にそれぞれ接続されている。チャージポンプ24における出力部は、LPF25の入力部に接続されている。LPF25の出力部は、VCO26の入力部に接続されている。VCO26の出力部は、プログラマブルディバイダ27の入力部に接続されている。プログラマブルディバイダ27の出力部は、位相比較器23における第2の入力部に接続されている。

【0026】

図3のPLLシンセサイザ回路20の動作について詳細に説明する。OSC21は、水晶発振子などを用いて、安定した所定の周波数を有する基準信号SIG1を生成する。リファレンスディバイダ22は、基準信号SIG1を所定の係数1/Rで分周し、リファレンス周波数信号SIG2を生成する。ここで、Rは1以上の整数である。位相比較器23は、リファレンス周波数信号SIG2および後述する比較周波数信号SIG4を入力し、両信号の位相差を表す直流電圧を生成する。チャージポンプ24は、位相比較器23から出力された直流電圧を、コンデンサの接続をスイッチ切り替えするなどの処理によって上昇させる。LPF25は、チャージポンプ24から出力された電圧を入力し、スイッチ切り替えなどの影響による高周波成分を抑圧し、直流成分を印加電圧VTとして出力する。VCO26は、印加電圧VTを入力し、印加電圧VTに対応する周波数を有するVCO発振信号SIG3を生成する。プログラマブルディバイダ27は、VCO発振信号SIG3を所定の係数1/Nで分周し、比較周波数信号SIG4を生成する。上述したように、比較周波数信号SIG4は位相比較器23に供給されることで、PLLシンセサイザ回路のループが形成される。

【0027】

図2の自己診断回路28ならびにHigh区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7、自己診断開始指示信号SIG8、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11について詳細に説明する。図4は、本発明の第1の実施形態による自己診断回路28の詳細な構成を示すブロック図である。図4の自己診断回路28は、図2で示した第1〜第8の入力部および第1〜第3の出力部に加えて、サンプリングクロック選択回路61と、分周信号選択回路62と、分周信号変化点検出回路63と、カウンタ動作指示および自己診断完了信号生成回路64と、High区間カウンタ回路65と、Low区間カウンタ回路66と、High区間期待値比較回路67と、Low区間期待値比較回路68とを具備している。

【0028】

図4の自己診断回路28の構成要素の接続関係について説明する。サンプリングクロック選択回路61における第1〜第3の入力部は、自己診断回路28における第1、第3および第7の入力部にそれぞれ接続されている。サンプリングクロック選択回路61における出力部は、分周信号変化点検出回路63における第1の入力部、High区間カウンタ回路65における第1の入力部およびLow区間カウンタ回路66における第1の入力部に共通接続されている。分周信号選択回路62における第1および第2の入力部は、自己診断回路28における第2、第4の入力部にそれぞれ接続されている。分周信号選択回路62における出力部は、分周信号変化点検出回路63における第2の入力部、High区間カウンタ回路65における第2の入力部およびLow区間カウンタ回路66における第2の入力部に共通接続されている。分周信号変化点検出回路63の出力部は、カウンタ動作指示および自己診断完了信号生成回路64における第1の入力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第2の入力部は、自己診断回路28における第8の入力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第1の出力部は、自己診断回路28における第1の出力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第2の出力部は、High区間カウンタ回路65における第3の入力部およびLow区間カウンタ回路66における第3の入力部に共通接続されている。High区間カウンタ回路65の出力部は、High区間期待値比較回路67における第1の入力部に接続されている。Low区間カウンタ回路66の出力部は、Low区間期待値比較回路68における第1の入力部に接続されている。High区間期待値比較回路67における第2の入力部は、自己診断回路28における第5の入力部に接続されている。High区間期待値比較回路67の出力部は、自己診断回路28における第2の出力部に接続されている。Low区間期待値比較回路68における第2の入力部は、自己診断回路28における第6の入力部に接続されている。Low区間期待値比較回路68の出力部は、自己診断回路28における第3の出力部に接続されている。

【0029】

図4の自己診断回路28の各構成要素の動作について概略的に説明する。サンプリングクロック選択回路61は、基準信号SIG1、VCO発振信号SIG3および分周信号選択信号SIG7を入力し、分周信号選択信号SIG7の値に応じて基準信号SIG1またはVCO発振信号SIG3のいずれかを選択し、信号S2として出力する。本実施形態では、分周信号選択信号SIG7がLowであるときには、サンプリングクロック選択回路61は基準信号SIG1を選択するものとする。反対に、分周信号選択信号SIG7がHighであるときには、サンプリングクロック選択回路61はVCO発振信号SIG3を選択するものとする。

【0030】

分周信号選択回路62は、リファレンス信号SIG2、比較周波数信号SIG4および分周信号選択信号SIG7を入力し、分周信号選択信号SIG7の値に応じてリファレンス信号SIG2または比較周波数信号SIG4のいずれかを選択し、信号S1として出力する。本実施形態では、分周信号選択信号SIG7がLowであるときには、分周信号選択回路62はリファレンス信号SIG2を選択するものとする。反対に、分周信号選択信号SIG7がHighであるときには、分周信号選択回路62は比較周波数信号を選択するものとする。

【0031】

分周信号変化点検出回路63は、信号S1および信号S2を入力し、信号S1がHighからLowへまたはLowからHighへ変更するタイミングを検出してその結果を分周信号変化点信号として出力する。このとき、分周信号変化点検出回路63は、分周信号変化点信号を、信号S2に同期して、すなわち信号S2がHighからLowへまたはLowからHigh変更するタイミングで、出力する。ここで、信号S1および信号S2のそれぞれにおいて、HighからLowへまたはLowからHighへ変更するタイミングのどちらを用いるかは、予め決定しておくことが好ましい。本実施形態では、信号S1および信号S2の両方について、LowからHighへ変化するタイミングを用いるものとする。

【0032】

カウンタ動作指示および自己診断完了信号生成回路64は、分周信号変化点信号および自己診断開始指示信号SIG8を入力し、これらの入力信号に基づいて、第1の出力部からは自己診断完了信号を出力し、第2の出力部からはリセット信号、開始信号または停止信号のいずれかをカウンタ動作指示信号として出力する。リセット信号は、High区間カウンタ回路65およびLow区間カウンタ回路66に向けて、カウントをリセットする、すなわち0に戻すタイミングを示すものである。開始信号は、High区間カウンタ回路65またはLow区間カウンタ回路66に向けて、カウントを開始するタイミングを示すものである。停止信号は、High区間カウンタ回路65またはLow区間カウンタ回路66に向けて、カウントを停止するタイミングを示すものである。自己診断完了信号は、必要なカウントが全て完了した際にそのことを示すものである。

【0033】

High区間カウンタ回路65は、信号S1、信号S2およびカウンタ動作指示信号を入力してカウントを行い、その結果をHigh区間カウント信号S3として出力する。ここで、High区間カウンタ回路65は、カウンタ動作指示信号としてリセット信号を入力した際には内部のカウントを0に戻す。また、High区間カウンタ回路65は、カウンタ動作指示信号として開始信号を入力してから同じく停止信号を入力するまでの期間、信号S1がLowからHighになる回数をカウントする。ただし、このカウントは、信号2に同期して、すなわち信号S2がHighからLowへまたはLowからHighへ変化するタイミングで行う。ここで、信号S2のどちらの変化に注目するかを、予め決定しておくことが好ましい。本実施形態では、信号S2がLowからHighへ変化するタイミングを用いるものとする。High区間カウンタ回路65は、カウンタ動作指示信号として停止信号を入力すると、内部のカウントを停止する。High区間カウンタ回路65は、そのカウント結果を、High区間期待値比較回路67に向けてHigh区間カウント信号S3として出力する。

【0034】

Low区間カウンタ回路66は、信号S1、信号S2およびカウンタ動作指示信号Bを入力してカウントを行い、その結果をLow区間カウント信号S4として出力する。ここで、Low区間カウンタ回路66は、カウンタ動作指示信号としてリセット信号を入力した際には内部のカウントを0に戻す。また、Low区間カウンタ回路66は、カウンタ動作指示信号として開始信号を入力してから同じく停止信号を入力するまでの期間、信号S1がHighからLowになる回数をカウントする。ただし、このカウントは、信号2に同期して、すなわち信号S2がHighからLowへまたはLowからHighへ変化するタイミングで行う。ここで、信号S2のどちらの変化に注目するかを、予め決定しておくことが好ましい。本実施形態では、信号S2がLowからHighへ変化するタイミングを用いるものとする。Low区間カウンタ回路66は、カウンタ動作指示信号として停止信号を入力すると、内部のカウントを停止する。Low区間カウンタ回路66は、そのカウント結果を、Low区間期待値比較回路68に向けてLow区間カウント信号S4として出力する。

【0035】

High区間期待値比較回路67は、High区間期待値信号SIG5およびHigh区間カウント信号S3を入力して両信号の値を比較し、その結果をHigh区間判定信号SIG10として出力する。なお、High区間期待値比較回路67は、High区間期待値信号SIG5およびHigh区間カウント信号S3の両方または片方を格納する記憶部を内蔵しても良い。

【0036】

同様に、Low区間期待値比較回路68は、Low区間期待値信号SIG6およびLow区間カウント信号S4を入力して両信号の値を比較し、その結果をLow区間判定信号SIG11として出力する。なお、Low区間期待値比較回路68は、Low区間期待値信号SIG6およびLow区間カウント信号S4の両方または片方を格納する記憶部を内蔵しても良い。

【0037】

ここで、High区間期待値信号SIG5の値およびLow区間期待値信号SIG6の値が、その和が分周の係数1/Rまたは1/Nの逆数に等しくなるように設定されることが重要である。このとき、High区間判定信号SIG11およびLow区間判定信号SIG11の両方において、期待値およびカウント値の一致を示していれば、そのときの検査対象である分周回路、すなわちリファレンスディバイダ22またはプログラマブルディバイダ27が、周波数およびデューティー比(High区間の長さおよびLow区間の長さの比率)の両方において、正常に動作していることが保証される。

【0038】

図4の自己診断回路28の全体的な動作について詳細に説明する。

図5は、本発明の第1の実施形態による自己診断回路28の動作を示すタイミングチャートである。

図5のタイミングチャートには、上から順に第1〜第13の波形図が描かれており、これらの波形図のそれぞれにおいて、横軸は時間の経過を示し、縦軸は信号の強度または値を簡略化して示している。

【0039】

図5のタイミングチャートにおいて、第1の波形図は、基準信号SIG1を示す。第2の波形図は、リファレンス信号SIG2を示す。第3の波形図は、VCO発振信号SIG3を示す。第4の波形図は、比較周波数信号SIG4を示す。第5の波形図は、High区間期待値信号SIG5を示す。第6の波形図は、Low区間期待値信号SIG6を示す。第7の波形図は、分周信号選択信号SIG7を示す。第8の波形図は、自己診断開始指示信号SIG8を示す。第9の波形図は、自己診断回路28の内部信号であるHigh区間カウント信号S3を示す。第10の波形図は、自己診断回路28の内部信号であるLow区間カウント信号S4を示す。第11の波形図は、自己診断完了信号SIG9を示す。第12の波形図は、High区間判定信号SIG10を示す。第13の波形図は、Low区間判定信号SIG11を示す。

【0040】

まず、自己診断を開始する前に、時刻t1において、High区間期待値比較回路67は、外部からHigh区間期待値信号SIG5を入力して、内部に設けられた記憶部に格納する。同様に、Low区間期待値比較回路68は、外部からLow区間期待値信号SIG6を入力して、内部に設けられた記憶部に格納する。なお、High区間期待値信号SIG5およびLow区間期待値信号SIG6の、時刻t1以前における値「X」は、いわゆる「don’t care」を示すものであって、いわゆる「不定状態」を示すものではない。

【0041】

次に、時刻t2において、外部から供給される自己診断開始指示信号SIG8が、LowからHighに切り替わる。自己診断開始指示信号SIG8がHighになることで、自己診断回路28は診断動作に入る。この時刻t2の次に基準信号SIG1がLowからHighに立ち上がる時刻t3において、High区間カウント信号S3およびLow区間カウント信号S4がリセットされてそれぞれのカウント値が「0」に戻る。ここで、時刻t3が基準信号SIG1に基づいて決定されるのは、時刻t2における分周信号選択信号SIG7がLowであり、すなわち基準信号SIG1が信号S2として用いられているからである。なお、このとき、信号S1としては、リファレンス信号SIG2が用いられる。

【0042】

また、時刻t3には、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11がLowに設定される。ここで、High区間カウント信号S3およびLow区間カウント信号S4は、自己診断回路28の内部でのみ用いられる信号であって、自己診断回路28の外部に出る必要は無い。また、High区間カウント信号、Low区間カウント信号、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11の、時刻t3以前における値「X」は、いわゆる「don’t care」を示すものであって、いわゆる「不定状態」を示すものではない。

【0043】

次に、時刻t4において、High区間カウント信号S3のカウントが始まり、その値が0から順に、信号S2として用いられる基準信号SIG1の1周期につき1つずつ繰り上がる。High区間カウント信号S3のカウントがこの時刻t4に始まる理由は、時刻t3の次にリファレンス信号SIG2がLowからHighに立ち上がり、さらにその次に基準信号SIG1がLowからHighに立ち上がるタイミングであるからである。

【0044】

リファレンス信号SIG2および基準信号SIG1の立ち上がりにこのようなずれが生じる原理について説明する。図6は、本発明の第1の実施形態による半導体集積回路における、任意のクロック信号と、このクロック信号を一般的な分周回路で分周した分周信号との、時間軸上の関係を示すタイミングチャートである。図6のタイミングチャートは、上から順に、第1および第2の波形図を示している。第1の波形図は、クロック信号Aを示している。第2の波形図は、分周信号を示している。一般的な分周回路としての論理回路において、クロック信号Aの立ち上がりエッジおよび立ち下がりエッジに基づいて分周信号を生成するとき、この生成される分周信号における変化点は、クロック信号Aの立ち上がりエッジよりも後に発生する。クロック信号Aの立ち上がりエッジと、分周信号の立ち上がり変化点の時間差を、図6ではTcrとして示している。同様に、クロック信号Aの立ち下がりエッジと、分周信号の立ち下がり変化点の時間差を、図6ではTcfとして示している。

【0045】

これらの時間差TcrおよびTcfは、実際の回路構成や、半導体集積回路の製造プロセスなどによって異なるが、いずれの場合も、分周信号の変化点は、その元となるクロック信号Aの立ち上がりエッジよりも後に発生する。本発明の第1の実施形態における図5では、分周信号であるリファレンス信号SIG2の変化点およびその元となる基準信号SIG1の変化点が、同じタイミングで発生しているかのように描かれている。同様に、分周信号である比較周波数信号SIG4の変化点およびその元となるVCO発振信号SIG3の変化点も、同じタイミングで発生しているかのように描かれている。しかし、図5は簡略化されており、実際には、図6のような時間差がある。このため、High区間カウント信号やLow区間カウント信号のカウント動作が、リファレンス信号SIG2(または比較周波数信号SIG4)が立ち上がってから基準信号SIG1(またはVCO発振信号SIG3)での1周期だけ遅れる。

【0046】

次に、時刻t5において、High区間カウント信号S3のカウントが終わり、Low区間カウント信号S4のカウントが始まる。ここで、時刻t5は、信号S1として用いられるリファレンス信号SIG2がHighからLowに立ち下がった後に初めて、信号S2として用いられる基準信号SIG1が立ち上がる時刻である。この時間差が発生する理由は図6で説明したとおりである。Low区間カウント信号S4のカウントは、High区間カウント信号S3の場合と同様に、0から始まり、信号S2として用いられる基準信号SIG1の1周期につき1つずつ繰り上がる。

【0047】

次に、時刻t6において、Low区間カウント信号S4のカウントが終わる。ここで、時刻t6は、信号S1として用いられるリファレンス信号SIG2がLowからHighに立ち上がった後に初めて、信号S2として用いられる基準信号SIG1が立ち上がる時刻である。この時間差が発生する理由は、図6で説明したとおりである。また、基準信号SIG1に基づくリファレンス信号SIG2のカウントが、High区間およびLow区間の両方で完了したので、カウンタ動作指示および自己診断完了信号生成回路64は、自己診断完了信号SIG9をHighに立ち上げる。

【0048】

さらに、時刻t6において、High区間期待値比較回路67は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値を比較し、その結果をHigh区間判定信号SIG10として出力する。図4の場合は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値がいずれも4で一致するので、High区間判定信号SIG10の値はこの一致を示すHighになる。

【0049】

同様に、時刻t6において、Low区間期待値比較回路68は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値を比較し、その結果をLow区間判定信号SIG11として出力する。図4の場合は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値がいずれも5で一致するので、Low区間判定信号SIG11の値はこの一致を示すHighになる。

【0050】

次に、時刻t7において、インターフェイス29は、自己診断完了信号SIG9がHighになったことを受けて、すなわちリファレンスディバイダ22に係る診断が完了したことを受けて、自己診断開始指示信号SIG8をLowに戻す。

【0051】

次に、時刻t8において、プログラマブルディバイダ27に係る診断を開始するために、分周信号選択信号SIG7がHighになる。その結果、サンプリングクロック選択回路61はVCO発振信号を選択して信号S2として出力し、分周信号選択回路62は比較周波数信号SIG4を選択して信号S1として出力する。

【0052】

次に、時刻t9において、High区間期待値信号SIG5およびLow区間期待値信号SIG6の値をそれぞれ変更する。なお、時刻t8および時刻t9における動作は、前後を入れ替えても構わない。

【0053】

次に、時刻t10において、インターフェイス29を介して自己診断開始指示信号SIG8がHighにすると、自己診断回路28が再び診断動作に入る。この時刻t10の次にVCO発振信号SIG3がLowからHighに立ち上がる時刻t11において、High区間カウント信号S3およびLow区間カウント信号S4がリセットされてそれぞれのカウント値が「0」に戻る。ここで、時刻t11がVCO発振信号SIG3に基づいて決定されるのは、時刻t10における分周信号選択信号SIG7がHighであり、すなわちVCO発振信号SIG3が信号S2として用いられているからである。なお、このとき、信号S1としては、比較周波数信号SIG2が用いられる。

【0054】

また、時刻t11には、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11がLowに設定される。

【0055】

次に、時刻t12において、High区間カウント信号S3のカウントが始まり、その値が0から順に、信号S2として用いられるVCO発振信号SIG3の1周期につき1つずつ繰り上がる。High区間カウント信号S3のカウントがこの時刻t12に始まる理由は、図6を用いて蒸気に説明したように、時刻t11の次に比較周波数信号SIG4がLowからHighに立ち上がり、さらにその次にVCO発振信号SIG3がLowからHighに立ち上がるタイミングであるからである。

【0056】

次に、時刻t13において、High区間カウント信号S3のカウントが終わり、Low区間カウント信号S4のカウントが始まる。ここで、時刻t13は、信号S1として用いられる比較周波数信号SIG4がHighからLowに立ち下がった後に初めて、信号S2として用いられるVCO発振信号SIG3が立ち上がる時刻である。この時間差が発生する理由は図6で説明したとおりである。Low区間カウント信号S4のカウントは、High区間カウント信号S3の場合と同様に、0から始まり、信号S2として用いられるVCO発振信号SIG1の1周期につき1つずつ繰り上がる。

【0057】

次に、時刻t14において、Low区間カウント信号S4のカウントが終わる。ここで、時刻t14は、信号S1として用いられる比較周波数信号SIG4がLowからHighに立ち上がった後に初めて、信号S2として用いられるVCO発振信号SIG3が立ち上がる時刻である。この時間差が発生する理由は、図6で説明したとおりである。また、VCO発振信号SIG3に基づく比較周波数信号SIG4のカウントが、High区間およびLow区間の両方で完了したので、カウンタ動作指示および自己診断完了信号生成回路64は、自己診断完了信号SIG9をHighに立ち上げる。

【0058】

さらに、時刻t14において、High区間期待値比較回路67は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値を比較し、その結果をHigh区間判定信号SIG10として出力する。図4の場合は、High区間期待値信号SIG5の値は5であり、High区間カウント信号S3の値は3であり、2つの値は異なるので、High区間判定信号SIG10の値はこの不一致を示すLowになる。

【0059】

同様に、時刻t14において、Low区間期待値比較回路68は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値を比較し、その結果をLow区間判定信号SIG11として出力する。図4の場合は、Low区間期待値信号SIG6の値は1であり、Low区間カウント信号S4の値は2であり、2つの値は異なるので、Low区間判定信号SIG11の値はこの一致を示すLowになる。

【0060】

最後に、時刻t15において、インターフェイス29は、自己診断完了信号SIG9がHighになったことを受けて、すなわちプログラマブルディバイダ27に係る診断が完了したことを受けて、自己診断開始指示信号SIG8をLowに戻す。以上で、本実施形態による検査方法が一通り完了する。

【0061】

以上に説明したメカニズムによって、本実施形態による半導体集積回路およびその検査方法は、分周回路が分周信号を正しく生成するかどうかの判定が可能である。ここで、PLL回路における出力周波数を決定する回路である、分周係数の変更や、分周信号におけるデューティー比、すなわちHigh区間およびLow区間の比率の変更を行った場合でも、外部からは2つの期待値信号およびどのカウントを行うかの選択信号を供給するだけで、半導体集積回路内部での判定が可能となっている。特に、制御用タイミング生成回路などを半導体集積回路の外部に用意する必要も無くなるので、従来の分周信号のテストに必要だった高価な検査装置も本発明なら不要となる。

【0062】

また、期待値制御信号や検査制御信号などの制御信号を半導体集積回路の外部から供給する必要が無いので、本発明による半導体集積回路は、プリント基板などに実装した後の、例えば完成した製品としての状態においても、検査機能を使用することが可能である。

【0063】

なお、図5のタイムチャートでは、リファレンス信号SIG2のHigh区間、リファレンス信号SIG2のLow区間、比較周波数信号SIG4のHigh区間、比較周波数信号SIG4のLow区間の順にカウント動作を行った。しかし、この順序はあくまでも一例に過ぎず、自由に変更可能であって、本発明を限定するものではない。

【0064】

また、図4のブロック図では、上記4つのカウントを1つずつ順次行ったが、回路規模を増やすことで2つ乃至4つのカウントを並行することも容易に可能である。この場合は、サンプリングクロック選択回路61および分周信号選択回路62を廃して、代わりにHigh区間カウンタ回路65、Low区間カウンタ回路66、High区間期待値比較回路67およびLow区間期待値比較回路68を増やして並列に接続し、カウンタ動作指示および自己診断完了信号生成回路64の動作を適宜に変更すれば良い。

【0065】

(第2の実施形態)

図7は、本発明の第2の実施形態による自己診断回路28の構成を示すブロック図である。本実施形態による自己診断回路28は、図4に示した本発明の第1の実施形態による自己診断回路28に、以下の変更を加えたものに等しい。すなわち、図4におけるサンプリングクロック選択回路61および分周信号選択回路62を、図7におけるサンプリングクロック選択回路71および分周信号選択回路72に置き換える。

【0066】

本実施形態によるサンプリングクロック選択回路71は、本発明の第1の実施形態によるサンプリング選クロック択回路61に、クロックB信号を入力するために用いられる第4の入力部を加えたものに等しい。また、本実施形態による分周信号選択回路72は、本発明の第1の実施形態による分周信号選択回路62に、分周信号A、分周信号Bおよび分周信号Cをそれぞれ入力するために用いられる第4、5および6の入力部を加えたものに等しい。

【0067】

本実施形態による半導体集積回路の他の構成および接続関係は、本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0068】

本実施形態による半導体集積回路の動作について説明する。本実施形態では、本発明の第1の実施形態における2つの分周信号であるリファレンス信号SIG2および比較周波数信号SIG4を使用する回路が半導体集積回路の内部にある場合を想定している。さらに、分周信号A、分周信号Bおよび分周信号Cが、クロックB信号を分周することで得られる場合を想定している。

【0069】

本実施形態によるサンプリングクロック選択回路71は、分周信号選択信号SIG7に応じて、基準信号SIG1、VCO発振信号SIG3またはクロックB信号の、合計3つの信号のいずれか1つを選択して信号S2として出力する機能を有する。ここで、分周信号選択信号SIG7は当然ながら少なくとも3種類の値を取り得る必要がある。本実施形態によるサンプリングクロック選択回路71のその他の動作は、本発明の第1の実施形態によるサンプリングクロック選択回路61の場合と同様であるので、さらなる詳細な説明を省略する。

【0070】

本実施形態による分周信号選択回路は、分周信号選択信号SIG7に応じて、リファレンス信号SIG2、比較周波数信号SIG4、分周信号A、分周信号Bまたは分周信号Cの、合計5つの信号のいずれか1つを選択して信号S1として出力する機能を有する。ここで、分周信号選択信号SIG7は当然ながら少なくとも5種類の値を取り得る必要がある。本実施形態による分周信号選択回路72のその他の動作は、本発明の第1の実施形態による分周信号選択回路62の場合と同様であるので、さらなる詳細な説明を省略する。

【0071】

本実施形態による半導体集積回路のその他の動作は、本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0072】

本実施形態による半導体集積回路およびその検査方法によれば、分周信号の元となるクロック信号およびこのクロック信号に対する複数の分周信号が半導体集積回路内で使われる場合でも、同じ1つの自己診断回路28を用いて複数の分周信号を判定することが可能となる。このことは、半導体集積回路における回路面積の低減に有効である。

【0073】

以上に説明した本発明の第1および第2の実施形態の構成は、技術的に矛盾しない限り、自由に組み合わせることが可能である。

【符号の説明】

【0074】

1 (第1の)信号入力部

2 (第1の)信号出力部

3 (第2の)信号入力部

4 (第3の)信号入力部

5 (第4の)信号入力部

6 (第5の)信号入力部

10 発振回路

20 PLLシンセサイザ回路

21 発振器(OSC)

22 リファレンスディバイダ(1/R)

23 位相比較器

24 チャージポンプ

25 ローパスフィルタ(LPF)

26 電圧制御発振器(VCO)

27 プログラマブルディバイダ(1/N)

28 自己診断回路

29 (外部との)インターフェイス

30 判定回路

300 分周回路

301 サンプリング回路

302 期待値出力回路

303 検査信号発生回路

304 比較回路

40 (第2の)信号出力部

61 サンプリングクロック選択回路

62 分周信号選択回路

63 分周信号変化点検出回路

64 カウンタ動作指示および自己診断完了信号生成回路

65 High区間カウンタ回路

66 Low区間カウンタ回路

67 High区間期待値比較回路

68 Low区間期待値比較回路

71 サンプリングクロック選択回路

72 分周信号選択回路

【技術分野】

【0001】

本発明は、半導体集積回路およびその検査方法に係り、特に、発振回路を有する半導体集積回路およびその検査方法に係る。

【背景技術】

【0002】

分周回路を含む発振回路を内蔵する半導体集積回路を製造するにあたって、この分周回路の特性を検査することが必要である。半導体集積回路に内蔵される分周回路を検査するにあたって、この分周回路が生成する分周信号を、半導体集積回路の外部に用意された検査装置が生成する理想的な信号と比較する方法がある。

【0003】

上記に関連して、特許文献1(特開2001−274337号公報)には、高周波用半導体装置に係る記載が開示されている。この高周波用半導体装置は、高周波信号発生回路と、分周回路と、第1外部端子と、第2外部端子と、第3外部端子とを有する。ここで、高周波信号発生回路は、高周波信号を発生する。分周回路は、入力される信号を所定の比で分周して出力する。第1外部端子は、この高周波信号発生回路で発生した高周波信号を外部に導出するためのものである。第2の外部端子は、分周回路の入力に接続され、且つ第1外部端子と接続可能に設けられている。第3外部端子は、分周回路の出力に接続され測定用端子となる。

【0004】

また、特許文献2(特開2001−298158号公報)には、半導体集積回路に係る記載が開示されている。ここで、特許文献2の半導体集積回路を従来技術として説明する。

【0005】

図1は、従来技術による半導体集積回路の構成を示すブロック図である。図1の半導体集積回路の構成について説明する。図1の半導体集積回路は、第1の信号入力部1と、第1の信号出力部2と、第2〜第5の信号入力部3〜6と、発振回路10と、判定回路30と、第2の信号出力部40とを具備している。判定回路30は、分周回路300と、サンプリング回路301と、期待値出力回路302と、検査信号発生回路303と、比較回路304とを具備している。

【0006】

図1の半導体集積回路の動作について説明する。第3の入力部4は、外部からリセット信号S4を入力する。分周回路300、期待値出力回路302および検査信号発生回路303は、リセット信号S4に応じてそれぞれリセットされて同期する。第1の入力部1は、外部から発振制御信号S1を入力する。発振回路10は、発振制御信号S1に基づく周波数を有する信号を生成し、入力クロック信号S10として出力する。第1の出力部2は、入力クロック信号S10を外部へ出力する。分周回路300は、発振信号S10を分周し、分周クロック信号S300として出力する。第4の入力部5は、外部からサンプリング制御信号S5を入力する。サンプリング回路301は、サンプリング制御信号S5に基づいて分周クロック信号S300をサンプリングし、サンプリングクロック信号S301として出力する。第2の入力部3は、外部から期待値制御信号S3を入力する。期待値出力回路302は、期待値制御信号S3に基づいて期待値信号S302を生成する。第5の入力部6は、外部から検査制御信号S6を入力する。検査信号発生回路303は、検査制御信号S6に基づいて検査信号S303を生成する。比較回路304は、サンプリングクロック信号S301および期待値信号S302の比較処理を行い、その結果を判定結果S40として出力する。ここで、比較回路304は、比較処理として、検査信号S303に応じて、一致比較処理または比較除外処理を行う。第2の出力部40は、判定結果S40を外部へ出力する。

【0007】

また、特許文献3(特開2002−41178号公報)には、半導体集積回路装置に係る記載が開示されている。この半導体集積回路装置は、PLL(Phase Locked Loop:位相同期ループ)回路と、分周器と、PLLシフトレジスタと、判定回路とを備えている。ここで、PLL回路は、入力クロック信号を入力とする。分周器は、PLL回路より出力されたPLL出力クロック信号を分周する。シフトレジスタは、分周器より出力された分周クロック信号をデータ入力とし、入力クロック信号をクロック入力とする。判定回路は、入力クロック信号に同期してシフトレジスタの各段よりそれぞれ出力されるデータ出力信号を入力とし、各データ出力信号の状態の組み合わせを基にPLL回路が正常に動作しているか否かを判定し、判定結果信号を外部へ出力する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2001−274337号公報

【特許文献2】特開2001−298158号公報

【特許文献3】特開2002−41178号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

従来技術では、PLL回路を含む発振回路の検査を行う前提として、この発振回路が生成する信号の周波数を検査対象としている。この場合、PLL回路の内部で生成され使用されるその他の信号、すなわちリファレンス周波数信号および比較周波数信号についても、従来技術では、その周波数のみが検査対象となるが、これでは十分な検査が出来ない。

【0010】

リファレンス周波数信号および比較周波数信号は、それぞれに対応する発振回路が生成する信号を分周することで生成される。この分周処理は、論理回路で構成したカウンタである分周回路を用いて行う。ただし、リファレンス周波数信号および比較周波数信号のそれぞれにおける、1周期ごとのいわゆるHigh区間長およびいわゆるLow区間長は、PLL回路が求める周波数ごとに設定変更する必要がある。そして、周波数のみを検査する従来技術では、High区間長およびLow区間長が異なる場合を考慮出来ない。したがって、従来技術では、PLL回路の内部においてリファレンス周波数信号および比較周波数信号が正しく生成されているかどうかを検査することが出来ない。

【0011】

また、従来技術では、検査対象である信号の比較対象として用いる制御信号を、外部から入力する必要がある。この制御信号は、検査対象である信号と位相などのタイミングを合わせて生成供給する必要があるため、結果的に高価な検査装置が必要となる。

【0012】

さらに、従来技術では、半導体集積回路の外部から制御信号を入力する必要があるので、半導体集積回路をプリント基板などに実装した状態での検査が不可能である。これは、従来技術が、半導体集積回路の製造工程での検査を前提としているからである。

【課題を解決するための手段】

【0013】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0014】

本発明による半導体集積回路は、発振回路(21または26)と、分周回路(22または27)と、自己診断回路(28)とを具備する。ここで、発振回路(21または26)は、発振周波数信号(SIG1またはSIG3)を生成する。分周回路(22または27)は、発振周波数信号(SIG1またはSIG3)を所定の係数(1/Rまたは1/N)で分周して、分周信号(SIG2またはSIG4)を生成する。自己診断回路(28)は、発振周波数信号(SIG1またはSIG3)、分周信号(21または26)および2つの基準値(SIG5およびSIG6)に基づいて分周回路(22または27)の特性を判定する。係数(1/Rまたは1/N)の逆数は、2つの基準値(SIG5およびSIG6)の和に等しい。自己診断回路(28)は、第1区間カウンタ回路(65)と、第1区間カウンタ回路(66)と、第1区間期待値比較回路(67)と、第2区間期待値比較回路(68)とを具備する。ここで、第1区間カウンタ回路(65)は、分周信号(21または26)の1周器の中で第1の論理状態である時間である第1区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントする。第2区間カウンタ回路(66)は、分周信号(21または26)の1周器の中で第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントする。第1区間期待値比較回路(67)は、第1のカウント結果を、2つの基準値(SIG5およびSIG6)の一方である第1区間期待値信号(SIG5)と比較する。第2区間期待値比較回路(68)は、第2区間のカウント結果を、2つの基準値(SIG5およびSIG6)の他方である第2区間期待値信号(SIG6)と比較する。

【0015】

本発明による半導体集積回路の検査方法は、発振周波数信号(SIG1またはSIG3)を生成するステップと、分周回路(22または26)が発振周波数信号(SIG1またはSIG3)を分周して、分周信号(SIG2またはSIG4)を生成するステップと、発振周波数信号(SIG1またはSIG3)、分周信号(SIG2またはSIG4)および2つの基準値(SIG5およびSIG6)に基づいて、分周回路(22または26)の特性を判定するステップとを具備する。分周回路(22または26)の特性を判定するステップは、分周信号(SIG2またはSIG4)の1周器の中で第1の論理状態である時間である第1区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントするステップと、分周信号(SIG2またはSIG4)の1周器の中で第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、発振周波数信号(SIG1またはSIG3)の周期でカウントするステップと、第1区間のカウント結果を、2つの基準値(SIG5およびSIG6)の一方である第1区間期待値信号(SIG5)と比較するステップと、第2区間のカウント結果を、2つの基準値(SIG5およびSIG6))の他方である第2区間期待値信号(SIG6)と比較するステップとを具備する。

【発明の効果】

【0016】

本発明によれば、分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわちいわゆるHigh区間およびいわゆるLow区間の比率、の2つに対して行うことが出来る。外部からはデューティー比を定義する2つの期待値を用い、比較対象となる理想的な信号を用いる高価な検査装置は不要である。

【図面の簡単な説明】

【0017】

【図1】図1は、従来技術による半導体集積回路の構成を示すブロック図である。

【図2】図2は、本発明の第1の実施形態による半導体集積回路の全体的な構成を概略的に示すブロック図である。

【図3】図3は、本発明でも用いる一般的なPLLシンセサイザ回路20の構成を示すブロック図である。

【図4】図4は、本発明の第1の実施形態による自己診断回路28の詳細な構成を示すブロック図である。

【図5】図5は、本発明の第1の実施形態による自己診断回路28の動作を示すタイミングチャートである。

【図6】図6は、本発明の第1の実施形態による半導体集積回路における、任意のクロック信号と、このクロック信号を一般的な分周回路で分周した分周信号との、時間軸上の関係を示すタイミングチャートである。

【図7】図7は、本発明の第2の実施形態による自己診断回路28の構成を示すブロック図である。

【発明を実施するための形態】

【0018】

添付図面を参照して、本発明による半導体集積回路およびその検査方法を実施するための形態を以下に説明する。

【0019】

(第1の実施形態)

本発明による半導体集積回路およびその検査方法は、PLL回路を含む分周信号を生成する論理回路を有する半導体集積回路に対して、分周機能が正しく動作しているかどうかを自己判定する機能を提供する。この自己判定する機能は、期待値を外部より入力し、半導体集積回路の内部で分周信号の波形の状態を測定し、判定結果を外部へ出力することを可能にする。

【0020】

この自己判定する方法について概略的に説明する。まず、発振信号および判定対象である分周信号を判定回路に入力する。次に、判定対象である分周信号のHigh区間およびLow区間のそれぞれを、発振信号でカウントする。これらのカウント結果と、半導体集積回路の外部より入力するHigh区間期待値およびLow区間期待値とが一致するかどうか、それぞれ比較する。これらの比較結果を、半導体集積回路の外部に向けて出力する。

【0021】

図2は、本発明の第1の実施形態による半導体集積回路の全体的な構成を概略的に示すブロック図である。図2の半導体集積回路の構成について説明する。図2の半導体集積回路は、PLLシンセサイザ回路20と、自己診断回路28と、外部とのインターフェイス29とを具備している。

【0022】

図2の半導体集積回路の構成の接続関係について説明する。自己診断回路28における第1〜第4の入力部は、PLLシンセサイザ回路20における第1〜第4の出力部に接続されている。自己診断回路28における第5〜第8の入力部は、インターフェイス29における第1〜第4の出力部にそれぞれ接続されている。インターフェイス29における第1〜第3の入力部は、自己診断回路28における第1〜3の出力部にそれぞれ接続されている。なお、インターフェイス29は、外部との接続を行う入出力部をさらに具備するが、本実施形態による半導体集積回路の本質とは関係が薄いので詳細な説明を省略する。インターフェイス29の具体例としては、パラレルインターフェイス、I2C−Busインターフェイスなどを用いることが可能であり、必要な信号の入出力さえ可能であれば特に限定は無い。

【0023】

図2の半導体集積回路の全体的な動作、すなわち本実施形態による半導体集積回路の検査方法について概略的に説明する。PLLシンセサイザ回路20は、基準信号SIG1、リファレンス信号SIG2、VCO(Voltage Controlled Oscillator:電圧制御発振器)発振信号SIG3および比較周波数信号SIG4を生成し、第1〜第4の出力部からそれぞれ出力する。自己診断回路28は、基準信号SIG1、リファレンス信号SIG2、VCO発振信号SIG3および比較周波数信号SIG4を、第1〜第4の入力部からそれぞれ入力する。また、自己診断回路28は、High区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7および自己診断開始指示信号SIG8を、第5〜第8の入力部からそれぞれ入力する。自己診断回路28は、上記8つの信号に基づいて、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11を生成し、第1〜第3の出力部からそれぞれ出力する。インターフェイス29は、High区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7および自己診断開始指示信号SIG8を外部から入力し、第1〜第4の出力部からそれぞれ出力する。また、インターフェイス29は、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11を第1〜第3の入力部から入力し、外部へ出力する。

【0024】

図2のPLLシンセサイザ回路20ならびに基準信号SIG1、リファレンス信号SIG2、VCO発振信号SIG3および比較周波数信号SIG4について詳細に説明する。図3は、本発明でも用いる一般的なPLLシンセサイザ回路20の構成を示すブロック図である。図3のPLLシンセサイザ回路20は、図2からPLLシンセサイザ回路20の部分を抜き出したものであって、同じ構成要素および同じ信号に同じ符号を用いている。図3のPLLシンセサイザ回路20の構成について説明する。図3のPLLシンセサイザ回路20は、発振器(OSC:OSCillator)21と、リファレンスディバイダ(1/R)22と、位相比較器23と、チャージポンプ24と、LPF(Low Pass Filter:ローパスフィルタ)25と、VCO26と、プログラマブルディバイダ(1/N)27とを具備している。

【0025】

図3のPLLシンセサイザ回路20における構成要素の接続関係について説明する。OSC21の出力部は、リファレンスディバイダ22の入力部に接続されている。リファレンスディバイダ22の出力部は、位相比較器23における第1の入力部に接続されている。位相比較器23における第1、第2の出力部は、チャージポンプ24における第1、第2の入力部にそれぞれ接続されている。チャージポンプ24における出力部は、LPF25の入力部に接続されている。LPF25の出力部は、VCO26の入力部に接続されている。VCO26の出力部は、プログラマブルディバイダ27の入力部に接続されている。プログラマブルディバイダ27の出力部は、位相比較器23における第2の入力部に接続されている。

【0026】

図3のPLLシンセサイザ回路20の動作について詳細に説明する。OSC21は、水晶発振子などを用いて、安定した所定の周波数を有する基準信号SIG1を生成する。リファレンスディバイダ22は、基準信号SIG1を所定の係数1/Rで分周し、リファレンス周波数信号SIG2を生成する。ここで、Rは1以上の整数である。位相比較器23は、リファレンス周波数信号SIG2および後述する比較周波数信号SIG4を入力し、両信号の位相差を表す直流電圧を生成する。チャージポンプ24は、位相比較器23から出力された直流電圧を、コンデンサの接続をスイッチ切り替えするなどの処理によって上昇させる。LPF25は、チャージポンプ24から出力された電圧を入力し、スイッチ切り替えなどの影響による高周波成分を抑圧し、直流成分を印加電圧VTとして出力する。VCO26は、印加電圧VTを入力し、印加電圧VTに対応する周波数を有するVCO発振信号SIG3を生成する。プログラマブルディバイダ27は、VCO発振信号SIG3を所定の係数1/Nで分周し、比較周波数信号SIG4を生成する。上述したように、比較周波数信号SIG4は位相比較器23に供給されることで、PLLシンセサイザ回路のループが形成される。

【0027】

図2の自己診断回路28ならびにHigh区間期待値信号SIG5、Low区間期待値信号SIG6、分周信号選択信号SIG7、自己診断開始指示信号SIG8、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11について詳細に説明する。図4は、本発明の第1の実施形態による自己診断回路28の詳細な構成を示すブロック図である。図4の自己診断回路28は、図2で示した第1〜第8の入力部および第1〜第3の出力部に加えて、サンプリングクロック選択回路61と、分周信号選択回路62と、分周信号変化点検出回路63と、カウンタ動作指示および自己診断完了信号生成回路64と、High区間カウンタ回路65と、Low区間カウンタ回路66と、High区間期待値比較回路67と、Low区間期待値比較回路68とを具備している。

【0028】

図4の自己診断回路28の構成要素の接続関係について説明する。サンプリングクロック選択回路61における第1〜第3の入力部は、自己診断回路28における第1、第3および第7の入力部にそれぞれ接続されている。サンプリングクロック選択回路61における出力部は、分周信号変化点検出回路63における第1の入力部、High区間カウンタ回路65における第1の入力部およびLow区間カウンタ回路66における第1の入力部に共通接続されている。分周信号選択回路62における第1および第2の入力部は、自己診断回路28における第2、第4の入力部にそれぞれ接続されている。分周信号選択回路62における出力部は、分周信号変化点検出回路63における第2の入力部、High区間カウンタ回路65における第2の入力部およびLow区間カウンタ回路66における第2の入力部に共通接続されている。分周信号変化点検出回路63の出力部は、カウンタ動作指示および自己診断完了信号生成回路64における第1の入力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第2の入力部は、自己診断回路28における第8の入力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第1の出力部は、自己診断回路28における第1の出力部に接続されている。カウンタ動作指示および自己診断完了信号生成回路64における第2の出力部は、High区間カウンタ回路65における第3の入力部およびLow区間カウンタ回路66における第3の入力部に共通接続されている。High区間カウンタ回路65の出力部は、High区間期待値比較回路67における第1の入力部に接続されている。Low区間カウンタ回路66の出力部は、Low区間期待値比較回路68における第1の入力部に接続されている。High区間期待値比較回路67における第2の入力部は、自己診断回路28における第5の入力部に接続されている。High区間期待値比較回路67の出力部は、自己診断回路28における第2の出力部に接続されている。Low区間期待値比較回路68における第2の入力部は、自己診断回路28における第6の入力部に接続されている。Low区間期待値比較回路68の出力部は、自己診断回路28における第3の出力部に接続されている。

【0029】

図4の自己診断回路28の各構成要素の動作について概略的に説明する。サンプリングクロック選択回路61は、基準信号SIG1、VCO発振信号SIG3および分周信号選択信号SIG7を入力し、分周信号選択信号SIG7の値に応じて基準信号SIG1またはVCO発振信号SIG3のいずれかを選択し、信号S2として出力する。本実施形態では、分周信号選択信号SIG7がLowであるときには、サンプリングクロック選択回路61は基準信号SIG1を選択するものとする。反対に、分周信号選択信号SIG7がHighであるときには、サンプリングクロック選択回路61はVCO発振信号SIG3を選択するものとする。

【0030】

分周信号選択回路62は、リファレンス信号SIG2、比較周波数信号SIG4および分周信号選択信号SIG7を入力し、分周信号選択信号SIG7の値に応じてリファレンス信号SIG2または比較周波数信号SIG4のいずれかを選択し、信号S1として出力する。本実施形態では、分周信号選択信号SIG7がLowであるときには、分周信号選択回路62はリファレンス信号SIG2を選択するものとする。反対に、分周信号選択信号SIG7がHighであるときには、分周信号選択回路62は比較周波数信号を選択するものとする。

【0031】

分周信号変化点検出回路63は、信号S1および信号S2を入力し、信号S1がHighからLowへまたはLowからHighへ変更するタイミングを検出してその結果を分周信号変化点信号として出力する。このとき、分周信号変化点検出回路63は、分周信号変化点信号を、信号S2に同期して、すなわち信号S2がHighからLowへまたはLowからHigh変更するタイミングで、出力する。ここで、信号S1および信号S2のそれぞれにおいて、HighからLowへまたはLowからHighへ変更するタイミングのどちらを用いるかは、予め決定しておくことが好ましい。本実施形態では、信号S1および信号S2の両方について、LowからHighへ変化するタイミングを用いるものとする。

【0032】

カウンタ動作指示および自己診断完了信号生成回路64は、分周信号変化点信号および自己診断開始指示信号SIG8を入力し、これらの入力信号に基づいて、第1の出力部からは自己診断完了信号を出力し、第2の出力部からはリセット信号、開始信号または停止信号のいずれかをカウンタ動作指示信号として出力する。リセット信号は、High区間カウンタ回路65およびLow区間カウンタ回路66に向けて、カウントをリセットする、すなわち0に戻すタイミングを示すものである。開始信号は、High区間カウンタ回路65またはLow区間カウンタ回路66に向けて、カウントを開始するタイミングを示すものである。停止信号は、High区間カウンタ回路65またはLow区間カウンタ回路66に向けて、カウントを停止するタイミングを示すものである。自己診断完了信号は、必要なカウントが全て完了した際にそのことを示すものである。

【0033】

High区間カウンタ回路65は、信号S1、信号S2およびカウンタ動作指示信号を入力してカウントを行い、その結果をHigh区間カウント信号S3として出力する。ここで、High区間カウンタ回路65は、カウンタ動作指示信号としてリセット信号を入力した際には内部のカウントを0に戻す。また、High区間カウンタ回路65は、カウンタ動作指示信号として開始信号を入力してから同じく停止信号を入力するまでの期間、信号S1がLowからHighになる回数をカウントする。ただし、このカウントは、信号2に同期して、すなわち信号S2がHighからLowへまたはLowからHighへ変化するタイミングで行う。ここで、信号S2のどちらの変化に注目するかを、予め決定しておくことが好ましい。本実施形態では、信号S2がLowからHighへ変化するタイミングを用いるものとする。High区間カウンタ回路65は、カウンタ動作指示信号として停止信号を入力すると、内部のカウントを停止する。High区間カウンタ回路65は、そのカウント結果を、High区間期待値比較回路67に向けてHigh区間カウント信号S3として出力する。

【0034】

Low区間カウンタ回路66は、信号S1、信号S2およびカウンタ動作指示信号Bを入力してカウントを行い、その結果をLow区間カウント信号S4として出力する。ここで、Low区間カウンタ回路66は、カウンタ動作指示信号としてリセット信号を入力した際には内部のカウントを0に戻す。また、Low区間カウンタ回路66は、カウンタ動作指示信号として開始信号を入力してから同じく停止信号を入力するまでの期間、信号S1がHighからLowになる回数をカウントする。ただし、このカウントは、信号2に同期して、すなわち信号S2がHighからLowへまたはLowからHighへ変化するタイミングで行う。ここで、信号S2のどちらの変化に注目するかを、予め決定しておくことが好ましい。本実施形態では、信号S2がLowからHighへ変化するタイミングを用いるものとする。Low区間カウンタ回路66は、カウンタ動作指示信号として停止信号を入力すると、内部のカウントを停止する。Low区間カウンタ回路66は、そのカウント結果を、Low区間期待値比較回路68に向けてLow区間カウント信号S4として出力する。

【0035】

High区間期待値比較回路67は、High区間期待値信号SIG5およびHigh区間カウント信号S3を入力して両信号の値を比較し、その結果をHigh区間判定信号SIG10として出力する。なお、High区間期待値比較回路67は、High区間期待値信号SIG5およびHigh区間カウント信号S3の両方または片方を格納する記憶部を内蔵しても良い。

【0036】

同様に、Low区間期待値比較回路68は、Low区間期待値信号SIG6およびLow区間カウント信号S4を入力して両信号の値を比較し、その結果をLow区間判定信号SIG11として出力する。なお、Low区間期待値比較回路68は、Low区間期待値信号SIG6およびLow区間カウント信号S4の両方または片方を格納する記憶部を内蔵しても良い。

【0037】

ここで、High区間期待値信号SIG5の値およびLow区間期待値信号SIG6の値が、その和が分周の係数1/Rまたは1/Nの逆数に等しくなるように設定されることが重要である。このとき、High区間判定信号SIG11およびLow区間判定信号SIG11の両方において、期待値およびカウント値の一致を示していれば、そのときの検査対象である分周回路、すなわちリファレンスディバイダ22またはプログラマブルディバイダ27が、周波数およびデューティー比(High区間の長さおよびLow区間の長さの比率)の両方において、正常に動作していることが保証される。

【0038】

図4の自己診断回路28の全体的な動作について詳細に説明する。

図5は、本発明の第1の実施形態による自己診断回路28の動作を示すタイミングチャートである。

図5のタイミングチャートには、上から順に第1〜第13の波形図が描かれており、これらの波形図のそれぞれにおいて、横軸は時間の経過を示し、縦軸は信号の強度または値を簡略化して示している。

【0039】

図5のタイミングチャートにおいて、第1の波形図は、基準信号SIG1を示す。第2の波形図は、リファレンス信号SIG2を示す。第3の波形図は、VCO発振信号SIG3を示す。第4の波形図は、比較周波数信号SIG4を示す。第5の波形図は、High区間期待値信号SIG5を示す。第6の波形図は、Low区間期待値信号SIG6を示す。第7の波形図は、分周信号選択信号SIG7を示す。第8の波形図は、自己診断開始指示信号SIG8を示す。第9の波形図は、自己診断回路28の内部信号であるHigh区間カウント信号S3を示す。第10の波形図は、自己診断回路28の内部信号であるLow区間カウント信号S4を示す。第11の波形図は、自己診断完了信号SIG9を示す。第12の波形図は、High区間判定信号SIG10を示す。第13の波形図は、Low区間判定信号SIG11を示す。

【0040】

まず、自己診断を開始する前に、時刻t1において、High区間期待値比較回路67は、外部からHigh区間期待値信号SIG5を入力して、内部に設けられた記憶部に格納する。同様に、Low区間期待値比較回路68は、外部からLow区間期待値信号SIG6を入力して、内部に設けられた記憶部に格納する。なお、High区間期待値信号SIG5およびLow区間期待値信号SIG6の、時刻t1以前における値「X」は、いわゆる「don’t care」を示すものであって、いわゆる「不定状態」を示すものではない。

【0041】

次に、時刻t2において、外部から供給される自己診断開始指示信号SIG8が、LowからHighに切り替わる。自己診断開始指示信号SIG8がHighになることで、自己診断回路28は診断動作に入る。この時刻t2の次に基準信号SIG1がLowからHighに立ち上がる時刻t3において、High区間カウント信号S3およびLow区間カウント信号S4がリセットされてそれぞれのカウント値が「0」に戻る。ここで、時刻t3が基準信号SIG1に基づいて決定されるのは、時刻t2における分周信号選択信号SIG7がLowであり、すなわち基準信号SIG1が信号S2として用いられているからである。なお、このとき、信号S1としては、リファレンス信号SIG2が用いられる。

【0042】

また、時刻t3には、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11がLowに設定される。ここで、High区間カウント信号S3およびLow区間カウント信号S4は、自己診断回路28の内部でのみ用いられる信号であって、自己診断回路28の外部に出る必要は無い。また、High区間カウント信号、Low区間カウント信号、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11の、時刻t3以前における値「X」は、いわゆる「don’t care」を示すものであって、いわゆる「不定状態」を示すものではない。

【0043】

次に、時刻t4において、High区間カウント信号S3のカウントが始まり、その値が0から順に、信号S2として用いられる基準信号SIG1の1周期につき1つずつ繰り上がる。High区間カウント信号S3のカウントがこの時刻t4に始まる理由は、時刻t3の次にリファレンス信号SIG2がLowからHighに立ち上がり、さらにその次に基準信号SIG1がLowからHighに立ち上がるタイミングであるからである。

【0044】

リファレンス信号SIG2および基準信号SIG1の立ち上がりにこのようなずれが生じる原理について説明する。図6は、本発明の第1の実施形態による半導体集積回路における、任意のクロック信号と、このクロック信号を一般的な分周回路で分周した分周信号との、時間軸上の関係を示すタイミングチャートである。図6のタイミングチャートは、上から順に、第1および第2の波形図を示している。第1の波形図は、クロック信号Aを示している。第2の波形図は、分周信号を示している。一般的な分周回路としての論理回路において、クロック信号Aの立ち上がりエッジおよび立ち下がりエッジに基づいて分周信号を生成するとき、この生成される分周信号における変化点は、クロック信号Aの立ち上がりエッジよりも後に発生する。クロック信号Aの立ち上がりエッジと、分周信号の立ち上がり変化点の時間差を、図6ではTcrとして示している。同様に、クロック信号Aの立ち下がりエッジと、分周信号の立ち下がり変化点の時間差を、図6ではTcfとして示している。

【0045】

これらの時間差TcrおよびTcfは、実際の回路構成や、半導体集積回路の製造プロセスなどによって異なるが、いずれの場合も、分周信号の変化点は、その元となるクロック信号Aの立ち上がりエッジよりも後に発生する。本発明の第1の実施形態における図5では、分周信号であるリファレンス信号SIG2の変化点およびその元となる基準信号SIG1の変化点が、同じタイミングで発生しているかのように描かれている。同様に、分周信号である比較周波数信号SIG4の変化点およびその元となるVCO発振信号SIG3の変化点も、同じタイミングで発生しているかのように描かれている。しかし、図5は簡略化されており、実際には、図6のような時間差がある。このため、High区間カウント信号やLow区間カウント信号のカウント動作が、リファレンス信号SIG2(または比較周波数信号SIG4)が立ち上がってから基準信号SIG1(またはVCO発振信号SIG3)での1周期だけ遅れる。

【0046】

次に、時刻t5において、High区間カウント信号S3のカウントが終わり、Low区間カウント信号S4のカウントが始まる。ここで、時刻t5は、信号S1として用いられるリファレンス信号SIG2がHighからLowに立ち下がった後に初めて、信号S2として用いられる基準信号SIG1が立ち上がる時刻である。この時間差が発生する理由は図6で説明したとおりである。Low区間カウント信号S4のカウントは、High区間カウント信号S3の場合と同様に、0から始まり、信号S2として用いられる基準信号SIG1の1周期につき1つずつ繰り上がる。

【0047】

次に、時刻t6において、Low区間カウント信号S4のカウントが終わる。ここで、時刻t6は、信号S1として用いられるリファレンス信号SIG2がLowからHighに立ち上がった後に初めて、信号S2として用いられる基準信号SIG1が立ち上がる時刻である。この時間差が発生する理由は、図6で説明したとおりである。また、基準信号SIG1に基づくリファレンス信号SIG2のカウントが、High区間およびLow区間の両方で完了したので、カウンタ動作指示および自己診断完了信号生成回路64は、自己診断完了信号SIG9をHighに立ち上げる。

【0048】

さらに、時刻t6において、High区間期待値比較回路67は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値を比較し、その結果をHigh区間判定信号SIG10として出力する。図4の場合は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値がいずれも4で一致するので、High区間判定信号SIG10の値はこの一致を示すHighになる。

【0049】

同様に、時刻t6において、Low区間期待値比較回路68は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値を比較し、その結果をLow区間判定信号SIG11として出力する。図4の場合は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値がいずれも5で一致するので、Low区間判定信号SIG11の値はこの一致を示すHighになる。

【0050】

次に、時刻t7において、インターフェイス29は、自己診断完了信号SIG9がHighになったことを受けて、すなわちリファレンスディバイダ22に係る診断が完了したことを受けて、自己診断開始指示信号SIG8をLowに戻す。

【0051】

次に、時刻t8において、プログラマブルディバイダ27に係る診断を開始するために、分周信号選択信号SIG7がHighになる。その結果、サンプリングクロック選択回路61はVCO発振信号を選択して信号S2として出力し、分周信号選択回路62は比較周波数信号SIG4を選択して信号S1として出力する。

【0052】

次に、時刻t9において、High区間期待値信号SIG5およびLow区間期待値信号SIG6の値をそれぞれ変更する。なお、時刻t8および時刻t9における動作は、前後を入れ替えても構わない。

【0053】

次に、時刻t10において、インターフェイス29を介して自己診断開始指示信号SIG8がHighにすると、自己診断回路28が再び診断動作に入る。この時刻t10の次にVCO発振信号SIG3がLowからHighに立ち上がる時刻t11において、High区間カウント信号S3およびLow区間カウント信号S4がリセットされてそれぞれのカウント値が「0」に戻る。ここで、時刻t11がVCO発振信号SIG3に基づいて決定されるのは、時刻t10における分周信号選択信号SIG7がHighであり、すなわちVCO発振信号SIG3が信号S2として用いられているからである。なお、このとき、信号S1としては、比較周波数信号SIG2が用いられる。

【0054】

また、時刻t11には、自己診断完了信号SIG9、High区間判定信号SIG10およびLow区間判定信号SIG11がLowに設定される。

【0055】

次に、時刻t12において、High区間カウント信号S3のカウントが始まり、その値が0から順に、信号S2として用いられるVCO発振信号SIG3の1周期につき1つずつ繰り上がる。High区間カウント信号S3のカウントがこの時刻t12に始まる理由は、図6を用いて蒸気に説明したように、時刻t11の次に比較周波数信号SIG4がLowからHighに立ち上がり、さらにその次にVCO発振信号SIG3がLowからHighに立ち上がるタイミングであるからである。

【0056】

次に、時刻t13において、High区間カウント信号S3のカウントが終わり、Low区間カウント信号S4のカウントが始まる。ここで、時刻t13は、信号S1として用いられる比較周波数信号SIG4がHighからLowに立ち下がった後に初めて、信号S2として用いられるVCO発振信号SIG3が立ち上がる時刻である。この時間差が発生する理由は図6で説明したとおりである。Low区間カウント信号S4のカウントは、High区間カウント信号S3の場合と同様に、0から始まり、信号S2として用いられるVCO発振信号SIG1の1周期につき1つずつ繰り上がる。

【0057】

次に、時刻t14において、Low区間カウント信号S4のカウントが終わる。ここで、時刻t14は、信号S1として用いられる比較周波数信号SIG4がLowからHighに立ち上がった後に初めて、信号S2として用いられるVCO発振信号SIG3が立ち上がる時刻である。この時間差が発生する理由は、図6で説明したとおりである。また、VCO発振信号SIG3に基づく比較周波数信号SIG4のカウントが、High区間およびLow区間の両方で完了したので、カウンタ動作指示および自己診断完了信号生成回路64は、自己診断完了信号SIG9をHighに立ち上げる。

【0058】

さらに、時刻t14において、High区間期待値比較回路67は、High区間期待値信号SIG5の値およびHigh区間カウント信号S3の値を比較し、その結果をHigh区間判定信号SIG10として出力する。図4の場合は、High区間期待値信号SIG5の値は5であり、High区間カウント信号S3の値は3であり、2つの値は異なるので、High区間判定信号SIG10の値はこの不一致を示すLowになる。

【0059】

同様に、時刻t14において、Low区間期待値比較回路68は、Low区間期待値信号SIG6の値およびLow区間カウント信号S4の値を比較し、その結果をLow区間判定信号SIG11として出力する。図4の場合は、Low区間期待値信号SIG6の値は1であり、Low区間カウント信号S4の値は2であり、2つの値は異なるので、Low区間判定信号SIG11の値はこの一致を示すLowになる。

【0060】

最後に、時刻t15において、インターフェイス29は、自己診断完了信号SIG9がHighになったことを受けて、すなわちプログラマブルディバイダ27に係る診断が完了したことを受けて、自己診断開始指示信号SIG8をLowに戻す。以上で、本実施形態による検査方法が一通り完了する。

【0061】

以上に説明したメカニズムによって、本実施形態による半導体集積回路およびその検査方法は、分周回路が分周信号を正しく生成するかどうかの判定が可能である。ここで、PLL回路における出力周波数を決定する回路である、分周係数の変更や、分周信号におけるデューティー比、すなわちHigh区間およびLow区間の比率の変更を行った場合でも、外部からは2つの期待値信号およびどのカウントを行うかの選択信号を供給するだけで、半導体集積回路内部での判定が可能となっている。特に、制御用タイミング生成回路などを半導体集積回路の外部に用意する必要も無くなるので、従来の分周信号のテストに必要だった高価な検査装置も本発明なら不要となる。

【0062】

また、期待値制御信号や検査制御信号などの制御信号を半導体集積回路の外部から供給する必要が無いので、本発明による半導体集積回路は、プリント基板などに実装した後の、例えば完成した製品としての状態においても、検査機能を使用することが可能である。

【0063】

なお、図5のタイムチャートでは、リファレンス信号SIG2のHigh区間、リファレンス信号SIG2のLow区間、比較周波数信号SIG4のHigh区間、比較周波数信号SIG4のLow区間の順にカウント動作を行った。しかし、この順序はあくまでも一例に過ぎず、自由に変更可能であって、本発明を限定するものではない。

【0064】

また、図4のブロック図では、上記4つのカウントを1つずつ順次行ったが、回路規模を増やすことで2つ乃至4つのカウントを並行することも容易に可能である。この場合は、サンプリングクロック選択回路61および分周信号選択回路62を廃して、代わりにHigh区間カウンタ回路65、Low区間カウンタ回路66、High区間期待値比較回路67およびLow区間期待値比較回路68を増やして並列に接続し、カウンタ動作指示および自己診断完了信号生成回路64の動作を適宜に変更すれば良い。

【0065】

(第2の実施形態)

図7は、本発明の第2の実施形態による自己診断回路28の構成を示すブロック図である。本実施形態による自己診断回路28は、図4に示した本発明の第1の実施形態による自己診断回路28に、以下の変更を加えたものに等しい。すなわち、図4におけるサンプリングクロック選択回路61および分周信号選択回路62を、図7におけるサンプリングクロック選択回路71および分周信号選択回路72に置き換える。

【0066】

本実施形態によるサンプリングクロック選択回路71は、本発明の第1の実施形態によるサンプリング選クロック択回路61に、クロックB信号を入力するために用いられる第4の入力部を加えたものに等しい。また、本実施形態による分周信号選択回路72は、本発明の第1の実施形態による分周信号選択回路62に、分周信号A、分周信号Bおよび分周信号Cをそれぞれ入力するために用いられる第4、5および6の入力部を加えたものに等しい。

【0067】

本実施形態による半導体集積回路の他の構成および接続関係は、本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0068】

本実施形態による半導体集積回路の動作について説明する。本実施形態では、本発明の第1の実施形態における2つの分周信号であるリファレンス信号SIG2および比較周波数信号SIG4を使用する回路が半導体集積回路の内部にある場合を想定している。さらに、分周信号A、分周信号Bおよび分周信号Cが、クロックB信号を分周することで得られる場合を想定している。

【0069】

本実施形態によるサンプリングクロック選択回路71は、分周信号選択信号SIG7に応じて、基準信号SIG1、VCO発振信号SIG3またはクロックB信号の、合計3つの信号のいずれか1つを選択して信号S2として出力する機能を有する。ここで、分周信号選択信号SIG7は当然ながら少なくとも3種類の値を取り得る必要がある。本実施形態によるサンプリングクロック選択回路71のその他の動作は、本発明の第1の実施形態によるサンプリングクロック選択回路61の場合と同様であるので、さらなる詳細な説明を省略する。

【0070】

本実施形態による分周信号選択回路は、分周信号選択信号SIG7に応じて、リファレンス信号SIG2、比較周波数信号SIG4、分周信号A、分周信号Bまたは分周信号Cの、合計5つの信号のいずれか1つを選択して信号S1として出力する機能を有する。ここで、分周信号選択信号SIG7は当然ながら少なくとも5種類の値を取り得る必要がある。本実施形態による分周信号選択回路72のその他の動作は、本発明の第1の実施形態による分周信号選択回路62の場合と同様であるので、さらなる詳細な説明を省略する。

【0071】

本実施形態による半導体集積回路のその他の動作は、本発明の第1の実施形態の場合と同様であるので、さらなる詳細な説明を省略する。

【0072】

本実施形態による半導体集積回路およびその検査方法によれば、分周信号の元となるクロック信号およびこのクロック信号に対する複数の分周信号が半導体集積回路内で使われる場合でも、同じ1つの自己診断回路28を用いて複数の分周信号を判定することが可能となる。このことは、半導体集積回路における回路面積の低減に有効である。

【0073】

以上に説明した本発明の第1および第2の実施形態の構成は、技術的に矛盾しない限り、自由に組み合わせることが可能である。

【符号の説明】

【0074】

1 (第1の)信号入力部

2 (第1の)信号出力部

3 (第2の)信号入力部

4 (第3の)信号入力部

5 (第4の)信号入力部

6 (第5の)信号入力部

10 発振回路

20 PLLシンセサイザ回路

21 発振器(OSC)

22 リファレンスディバイダ(1/R)

23 位相比較器

24 チャージポンプ

25 ローパスフィルタ(LPF)

26 電圧制御発振器(VCO)

27 プログラマブルディバイダ(1/N)

28 自己診断回路

29 (外部との)インターフェイス

30 判定回路

300 分周回路

301 サンプリング回路

302 期待値出力回路

303 検査信号発生回路

304 比較回路

40 (第2の)信号出力部

61 サンプリングクロック選択回路

62 分周信号選択回路

63 分周信号変化点検出回路

64 カウンタ動作指示および自己診断完了信号生成回路

65 High区間カウンタ回路

66 Low区間カウンタ回路

67 High区間期待値比較回路

68 Low区間期待値比較回路

71 サンプリングクロック選択回路

72 分周信号選択回路

【特許請求の範囲】

【請求項1】

発振周波数信号を生成する発振回路と、

前記発振周波数信号を所定の係数で分周して、分周信号を生成する分周回路と、

前記発振周波数信号、前記分周信号および2つの基準値に基づいて前記分周回路の特性を判定する自己診断回路と

を具備し、

前記係数の逆数は、前記2つの基準値の和に等しく、

前記自己診断回路は、

前記分周信号の1周器の中で第1の論理状態である時間である第1区間の長さを、前記発振周波数信号の周期でカウントする第1区間カウンタ回路と、

前記分周信号の1周器の中で前記第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、前記発振周波数信号の周期でカウントする第2区間カウンタ回路と、

前記第1区間のカウント結果を、前記2つの基準値の一方である第1区間期待値信号と比較する第1区間期待値比較回路と、

前記第2区間のカウント結果を、前記2つの基準値の他方である第2区間期待値信号と比較する第2区間期待値比較回路と

を具備する

半導体集積回路。

【請求項2】

請求項1に記載の半導体集積回路において、

他の発振周波数信号を生成する他の発振回路と、

前記他の発振周波数信号を所定の他の係数で分周して、他の分周信号を生成する他の分周回路と

をさらに具備し、

前記自己診断回路はさらに、前記他の発振周波数信号および他の2つの基準値に基づいて前記他の分周回路の特性を判定し、

前記他の係数の逆数は、前記他の2つの基準値の和に等しく、

前記第1区間カウンタ回路はさらに、前記他の分周信号の1周器の中で前記第1の論理状態である時間である他の第1区間の長さを、前記他の発振周波数信号の周期でカウントし、

前記第2区間カウンタ回路は、前記他の分周信号の1周器の中で前記第2の状態である時間である他の第2区間の長さを、前記他の発振周波数信号の周期でさらにカウントし、

前記第1区間期待値比較回路はさらに、前記他の第1区間のカウント結果を、前記他の2つの基準値の一方である他の第1区間期待値信号と比較し、

前記第2区間期待値比較回路はさらに、前記他の第2区間のカウント結果を、前記他の2つの基準値の他方である前記第2区間期待値信号と比較する

半導体集積回路。

【請求項3】

請求項2に記載の半導体集積回路において、

前記自己診断回路は、

分周信号選択信号を入力する分周信号選択信号入力部と、

前記発振回路の出力および前記他の発振回路の出力を入力し、前記発振周波数信号または前記他の発振周波数信号の一方を、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて出力するサンプリングクロック選択回路と、

前記分周回路の出力および前記他の分周回路の出力を入力し、前記分周信号または前記他の分周信号の一方を、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて出力する分周信号選択回路と

をさらに具備する

半導体集積回路。

【請求項4】

請求項2に記載の半導体集積回路において、

前記自己診断回路は、

分周信号選択信号を入力する分周信号選択信号入力部と、

前記発振回路の出力および前記他の発振回路の出力を入力し、前記発振周波数信号、前記他の発振周波数信号またはさらに他の発振周波数信号のいずれかを、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて前記発振周波数信号または前記他の発振周波数信号として出力するサンプリングクロック選択回路と、

前記分周回路の出力および前記他の分周回路の出力を入力し、前記分周信号、前記他の分周信号またはさらに他の分周信号のいずれかを、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて前記分周信号または前記他の分周信号として出力する分周信号選択回路と

をさらに具備する

半導体集積回路。

【請求項5】

請求項3または4に記載の半導体集積回路において、

前記自己診断回路は、

前記分周信号選択回路の出力が、前記第1の論理状態から前記第2の論理状態へまたは前記第2の論理状態から前記第1の論理状態へ変更するタイミングを、前記サンプリングクロック選択回路の出力に同期して検出する分周信号変化点検出回路と、

自己診断開始指示信号ならびに前記分周信号変化点検出回路の出力に基づいて前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けてカウントのリセット、開始または停止の動作を指示する信号および自己診断完了信号を生成するカウンタ動作指示および自己診断完了信号生成回路と

をさらに具備する

半導体集積回路。

【請求項6】

請求項2〜5のいずれかに記載の半導体集積回路において、

前記発振回路および他の発振回路ならびに前記分周回路および他の分周回路を有するPLL(Phase Locked Loop:位相同期ループ)回路

をさらに具備し、

前記発振回路は、

所定の固定周波数で発振して前記発振周波数信号を生成する発振器

を具備し、

前記分周回路は、

前記発振周波数信号を、前記係数で分周するプログラマブルディバイダ

を具備し、

前記PLLシンセサイザ回路は、

前記分周信号および前記他の分周信号の位相差に対応する電圧を生成する位相比較器と、

前記位相比較器の出力を昇圧するチャージポンプと、

前記チャージポンプの出力における直流成分を取り出すLPF(Low Pass Filter:ローパスフィルタ)と

をさらに具備し、

前記他の発振回路は、

前記LPFの出力電圧に対応する周波数で発振して前記他の発振周波数信号を生成するVCO(Voltage Controlled Oscillator:電圧制御発振器)

を具備し、

前記他の分周回路は、

前記他の発振周波数信号を前記他の係数で分周するリファレンスディバイダ

を具備する

半導体集積回路。

【請求項7】

発振周波数信号を生成するステップと、

分周回路が前記発振周波数信号を分周して、分周信号を生成するステップと、

前記発振周波数信号、前記分周信号および2つの基準値に基づいて、前記分周回路の特性を判定するステップと

を具備し、

前記分周回路の特性を判定するステップは、

前記分周信号の1周器の中で第1の論理状態である時間である第1区間の長さを、前記発振周波数信号の周期でカウントするステップと、

前記分周信号の1周器の中で前記第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、前記発振周波数信号の周期でカウントするステップと、

前記第1区間のカウント結果を、前記2つの基準値の一方である第1区間期待値信号と比較するステップと、

前記第2区間のカウント結果を、前記2つの基準値の他方である第2区間期待値信号と比較するステップと

を具備する

半導体集積回路の検査方法。

【請求項8】

請求項7に記載の半導体集積回路の検査方法において、

他の発振周波数信号を生成するステップと、

他の分周回路が前記他の発振周波数信号を分周して、他の分周信号を生成するステップと、

前記他の発振周波数信号、前記他の分周信号および他の2つの基準値に基づいて、前記他の分周回路の特性を判定するステップと

をさらに具備し、

前記他の分周回路の特性を判定するステップは、

前記他の分周信号の1周器の中で前記第1の論理状態である時間である他の第1区間の長さを、前記他の発振周波数信号の周期でカウントするステップと、

前記他の分周信号の1周器の中で前記第2の状態である時間である他の第2区間の長さを、前記他の発振周波数信号の周期でカウントするステップと、

前記他の第1区間のカウント結果を、前記他の2つの基準値の一方である他の第1区間期待値信号と比較するステップと、

前記他の第2区間のカウント結果を、前記他の2つの基準値の他方である他の第2区間期待値信号と比較するステップと

を具備する

半導体集積回路の検査方法。

【請求項9】

請求項8に記載の半導体集積回路の検査方法において、

前記第1区間の長さをカウントするステップ、前記第2区間の長さをカウントするステップ、前記他の第1区間の長さをカウントするステップおよび前記他の第2区間の長さをカウントするステップを実行する順序を制御するステップ

をさらに具備する

半導体集積回路の検査方法。

【請求項1】

発振周波数信号を生成する発振回路と、

前記発振周波数信号を所定の係数で分周して、分周信号を生成する分周回路と、

前記発振周波数信号、前記分周信号および2つの基準値に基づいて前記分周回路の特性を判定する自己診断回路と

を具備し、

前記係数の逆数は、前記2つの基準値の和に等しく、

前記自己診断回路は、

前記分周信号の1周器の中で第1の論理状態である時間である第1区間の長さを、前記発振周波数信号の周期でカウントする第1区間カウンタ回路と、

前記分周信号の1周器の中で前記第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、前記発振周波数信号の周期でカウントする第2区間カウンタ回路と、

前記第1区間のカウント結果を、前記2つの基準値の一方である第1区間期待値信号と比較する第1区間期待値比較回路と、

前記第2区間のカウント結果を、前記2つの基準値の他方である第2区間期待値信号と比較する第2区間期待値比較回路と

を具備する

半導体集積回路。

【請求項2】

請求項1に記載の半導体集積回路において、

他の発振周波数信号を生成する他の発振回路と、

前記他の発振周波数信号を所定の他の係数で分周して、他の分周信号を生成する他の分周回路と

をさらに具備し、

前記自己診断回路はさらに、前記他の発振周波数信号および他の2つの基準値に基づいて前記他の分周回路の特性を判定し、

前記他の係数の逆数は、前記他の2つの基準値の和に等しく、

前記第1区間カウンタ回路はさらに、前記他の分周信号の1周器の中で前記第1の論理状態である時間である他の第1区間の長さを、前記他の発振周波数信号の周期でカウントし、

前記第2区間カウンタ回路は、前記他の分周信号の1周器の中で前記第2の状態である時間である他の第2区間の長さを、前記他の発振周波数信号の周期でさらにカウントし、

前記第1区間期待値比較回路はさらに、前記他の第1区間のカウント結果を、前記他の2つの基準値の一方である他の第1区間期待値信号と比較し、

前記第2区間期待値比較回路はさらに、前記他の第2区間のカウント結果を、前記他の2つの基準値の他方である前記第2区間期待値信号と比較する

半導体集積回路。

【請求項3】

請求項2に記載の半導体集積回路において、

前記自己診断回路は、

分周信号選択信号を入力する分周信号選択信号入力部と、

前記発振回路の出力および前記他の発振回路の出力を入力し、前記発振周波数信号または前記他の発振周波数信号の一方を、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて出力するサンプリングクロック選択回路と、

前記分周回路の出力および前記他の分周回路の出力を入力し、前記分周信号または前記他の分周信号の一方を、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて出力する分周信号選択回路と

をさらに具備する

半導体集積回路。

【請求項4】

請求項2に記載の半導体集積回路において、

前記自己診断回路は、

分周信号選択信号を入力する分周信号選択信号入力部と、

前記発振回路の出力および前記他の発振回路の出力を入力し、前記発振周波数信号、前記他の発振周波数信号またはさらに他の発振周波数信号のいずれかを、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて前記発振周波数信号または前記他の発振周波数信号として出力するサンプリングクロック選択回路と、

前記分周回路の出力および前記他の分周回路の出力を入力し、前記分周信号、前記他の分周信号またはさらに他の分周信号のいずれかを、前記分周信号選択信号に応じて選択して前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けて前記分周信号または前記他の分周信号として出力する分周信号選択回路と

をさらに具備する

半導体集積回路。

【請求項5】

請求項3または4に記載の半導体集積回路において、

前記自己診断回路は、

前記分周信号選択回路の出力が、前記第1の論理状態から前記第2の論理状態へまたは前記第2の論理状態から前記第1の論理状態へ変更するタイミングを、前記サンプリングクロック選択回路の出力に同期して検出する分周信号変化点検出回路と、

自己診断開始指示信号ならびに前記分周信号変化点検出回路の出力に基づいて前記第1区間カウンタ回路および前記第2区間カウンタ回路に向けてカウントのリセット、開始または停止の動作を指示する信号および自己診断完了信号を生成するカウンタ動作指示および自己診断完了信号生成回路と

をさらに具備する

半導体集積回路。

【請求項6】

請求項2〜5のいずれかに記載の半導体集積回路において、

前記発振回路および他の発振回路ならびに前記分周回路および他の分周回路を有するPLL(Phase Locked Loop:位相同期ループ)回路

をさらに具備し、

前記発振回路は、

所定の固定周波数で発振して前記発振周波数信号を生成する発振器

を具備し、

前記分周回路は、

前記発振周波数信号を、前記係数で分周するプログラマブルディバイダ

を具備し、

前記PLLシンセサイザ回路は、

前記分周信号および前記他の分周信号の位相差に対応する電圧を生成する位相比較器と、

前記位相比較器の出力を昇圧するチャージポンプと、

前記チャージポンプの出力における直流成分を取り出すLPF(Low Pass Filter:ローパスフィルタ)と

をさらに具備し、

前記他の発振回路は、

前記LPFの出力電圧に対応する周波数で発振して前記他の発振周波数信号を生成するVCO(Voltage Controlled Oscillator:電圧制御発振器)

を具備し、

前記他の分周回路は、

前記他の発振周波数信号を前記他の係数で分周するリファレンスディバイダ

を具備する

半導体集積回路。

【請求項7】

発振周波数信号を生成するステップと、

分周回路が前記発振周波数信号を分周して、分周信号を生成するステップと、

前記発振周波数信号、前記分周信号および2つの基準値に基づいて、前記分周回路の特性を判定するステップと

を具備し、

前記分周回路の特性を判定するステップは、

前記分周信号の1周器の中で第1の論理状態である時間である第1区間の長さを、前記発振周波数信号の周期でカウントするステップと、

前記分周信号の1周器の中で前記第1の論理状態とは論理的に反転された第2の論理状態である時間である第2区間の長さを、前記発振周波数信号の周期でカウントするステップと、

前記第1区間のカウント結果を、前記2つの基準値の一方である第1区間期待値信号と比較するステップと、

前記第2区間のカウント結果を、前記2つの基準値の他方である第2区間期待値信号と比較するステップと

を具備する

半導体集積回路の検査方法。

【請求項8】

請求項7に記載の半導体集積回路の検査方法において、

他の発振周波数信号を生成するステップと、

他の分周回路が前記他の発振周波数信号を分周して、他の分周信号を生成するステップと、

前記他の発振周波数信号、前記他の分周信号および他の2つの基準値に基づいて、前記他の分周回路の特性を判定するステップと

をさらに具備し、

前記他の分周回路の特性を判定するステップは、

前記他の分周信号の1周器の中で前記第1の論理状態である時間である他の第1区間の長さを、前記他の発振周波数信号の周期でカウントするステップと、

前記他の分周信号の1周器の中で前記第2の状態である時間である他の第2区間の長さを、前記他の発振周波数信号の周期でカウントするステップと、

前記他の第1区間のカウント結果を、前記他の2つの基準値の一方である他の第1区間期待値信号と比較するステップと、

前記他の第2区間のカウント結果を、前記他の2つの基準値の他方である他の第2区間期待値信号と比較するステップと

を具備する

半導体集積回路の検査方法。

【請求項9】

請求項8に記載の半導体集積回路の検査方法において、

前記第1区間の長さをカウントするステップ、前記第2区間の長さをカウントするステップ、前記他の第1区間の長さをカウントするステップおよび前記他の第2区間の長さをカウントするステップを実行する順序を制御するステップ

をさらに具備する

半導体集積回路の検査方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−151617(P2012−151617A)

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願番号】特願2011−8190(P2011−8190)

【出願日】平成23年1月18日(2011.1.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願日】平成23年1月18日(2011.1.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]