半導体集積回路

【課題】クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【解決手段】実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

【解決手段】実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施の形態は、半導体集積回路に関する。

【背景技術】

【0002】

近年、半導体集積回路の微細化及び高性能化に伴い、回路の大規模化及び高速化が進んでいる。その結果、半導体集積回路内での消費電力の増加が問題となっている。このような半導体集積回路は、デジタル回路を備えたデジタル領域部と、アナログ回路を備えたアナログ領域部とを有しており、消費電力の増加に伴いデジタル領域部で発生したノイズがアナログ領域部に周り込んでしまい、誤動作等を発生させるという問題がある。

【0003】

デジタル領域部のデジタル回路は、複数のフリップフロップ及び複数の組み合わせ回路を有して構成されている。また、デジタル回路内の複数のフリップフロップには、PLL回路等から所定の周波数のクロック信号が供給されており、複数のフリップフロップは、このクロック信号に基づいて動作する。これらの複数のフリップフロップは、クロック信号の立ち上がりエッジ及び立ち下がりエッジにおいて、トランジスタのスイッチング動作による消費電流が発生するため、消費電力が大きくなる。

【0004】

特に、フリップフロップの動作時の消費電力は、クロック信号の立ち上がりエッジで発生する消費電力よりも、立ち下がりエッジで発生する消費電力が大きくなっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平10−63368号公報

【特許文献2】特開2005−33089号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の実施の形態が解決しようとする課題は、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【課題を解決するための手段】

【0007】

実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

【図面の簡単な説明】

【0008】

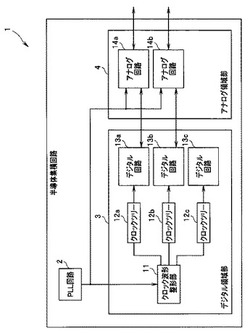

【図1】第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】クロック波形整形部の構成を説明するための図である。

【図3】フリップフロップの回路構成例を説明するための図である。

【図4】フリップフロップ内のインバータ回路で発生する消費電流について説明するための図である。

【図5】単一のクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【図6】デューティ比の異なるクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【図7】第2の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【図8】第3の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【発明を実施するための形態】

【0009】

以下、図面を参照して実施の形態の半導体集積回路について詳細に説明する。

(第1の実施の形態)

まず、図1に基づき、第1の実施の形態に係る半導体集積回路の構成について説明する。

図1は、第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【0010】

図1に示すように、半導体集積回路1は、PLL回路2と、デジタル領域部3と、アナログ領域部4とを有して構成されている。

【0011】

クロック信号生成部としてのPLL回路2は、所定の周波数のクロック信号を生成し、後述するデジタル領域部3のクロック波形整形部11と、アナログ領域部4のアナログ回路14a及び14bとに供給する。

【0012】

デジタル領域部3は、クロック波形整形部11と、3つのクロックツリー12a〜12cと、クロックツリー12a〜12cに接続された3つのデジタル回路13a〜13cとを有して構成される。デジタル回路13a〜13cは、それぞれ所定の機能を実行する機能ブロックであり、複数のフリップフロップ及び複数の組み合わせ回路等により構成されている。なお、デジタル領域部3は、3つのクロックツリー12a〜12c及びデジタル回路13a〜13cを有する構成であるが、例えば、2つ、あるいは、4つ以上のクロックツリー及びデジタル回路を有する構成であってもよい。

【0013】

また、アナログ領域部4は、複数、ここでは、2つのアナログ回路14a及び14bを有して構成される。アナログ回路14aは、例えば、アナログ信号をデジタル信号に変換するA/D変換器であり、アナログ回路14bは、例えば、デジタル信号をアナログ信号に変換するD/A変換器である。なお、アナログ回路14a及び14bは、A/D変換器及びD/A変換器に限定されることなく、例えば、高周波(RF)回路、メモリ回路等であってもよい。

【0014】

アナログ回路14aは、デジタル回路13aに接続されており、半導体集積回路1の外部から供給されたアナログ信号をデジタル信号に変換し、デジタル回路13aに出力する。また、アナログ回路14bは、デジタル回路13bに接続されており、デジタル回路13bから供給されたデジタル信号をアナログ信号に変換し、半導体集積回路1の外部に出力する。

【0015】

クロック波形整形部11は、供給されたクロック信号からそれぞれデューティ比の異なる複数、ここでは、3つのクロック信号を生成し、クロックツリー12a〜12cに供給する。具体的には、クロック波形整形部11は、供給されたクロック信号からそれぞれ立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成し、クロックツリー12a〜12cに供給する。

【0016】

クロックツリー12aは、複数のクロックバッファにより構成されており、ドライブ力、駆動するフリップフロップの数に応じて複数のクロックバッファがツリー上に分岐して構成されている。なお、クロックツリー12b及び12cも同様の構成である。クロックツリー12a〜12cは、それぞれクロック波形整形部11から供給されたデューティ比の異なるクロック信号をデジタル回路13a〜13cに供給する。

【0017】

デジタル回路13a〜13cは、それぞれ複数のフリップフロップ及び複数の組み合わせ回路等を有し、クロックツリー12a〜12cから供給されたデューティ比の異なるクロック信号に基づいて、所定の機能を実行する。

【0018】

ここで、デューティ比の異なる複数のクロック信号、本実施の形態では、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる複数のクロック信号を生成するクロック波形整形部11の構成について説明する。

【0019】

図2は、クロック波形整形部の構成を説明するための図である。

【0020】

クロック波形整形部11は、遅延回路21、22及び23と、OR回路24及び25と、インバータ回路26と、AND回路27とを有して構成されている。

【0021】

PLL回路2から供給されたクロック信号は、遅延回路21、22及び23に供給される。また、PLL回路2から供給されたクロック信号は、OR回路24、25及びAND回路27の一方の端子に供給される。遅延回路21〜23は、それぞれ異なる遅延量を有し、供給されたクロック信号を所定の時間遅延させる。本実施の形態では、遅延回路23、遅延回路22、遅延回路21の順に、大きな遅延量を有している。

【0022】

遅延回路21は、供給されたクロック信号を所定の時間遅延させ、OR回路24の他方の端子に供給する。OR回路24は、PLL回路2からのクロック信号と、遅延回路21で所定の時間遅延されたクロック信号とのOR演算を行う。これにより、OR回路24からは、デューティ比が約60%のクロック信号が出力され、クロックツリー12aに供給される。

【0023】

遅延回路22は、供給されたクロック信号を、遅延回路21より長い所定の時間遅延させ、OR回路25の他方の端子に出力する。OR回路25は、PLL回路2からのクロック信号と、遅延回路22で遅延回路21より長い所定の時間遅延されたクロック信号とのOR演算を行う。これにより、OR回路25からは、デューティ比が約70%のクロック信号が出力され、クロックツリー12bに供給される。

【0024】

遅延回路23は、供給されたクロック信号を、遅延回路22より長い所定の時間遅延させ、インバータ回路26に出力する。インバータ回路26は、遅延回路23からの信号を反転させ、AND回路27の他方の端子に出力する。AND回路27は、PLL回路2からのクロック信号と、遅延回路23で遅延回路22より長い所定の時間遅延され、インバータ回路26で反転されたクロック信号とのAND演算を行う。これにより、AND回路27からは、ディーティ比が約30%のクロック信号が出力され、クロックツリー12cに供給される。

【0025】

このように、クロック波形整形部11は、それぞれ、遅延回路21〜23及び論理ゲート、具体的には、遅延回路21及びOR回路24により構成される組み合わせ回路と、遅延回路22及びOR回路25により構成される組み合わせ回路と、遅延回路23、インバータ回路26及びAND回路27により構成される組み合わせ回路とにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成する。

【0026】

次に、このように構成される半導体集積回路1の消費電力について説明する。半導体集積回路1では、回路規模の増大に伴い、デジタル回路13a〜13cが有するフリップフロップでの消費電力が大きくなる。以下、フリップフロップの回路構成について説明する。

【0027】

図3は、フリップフロップの回路構成例を説明するための図である。

【0028】

図3に示すように、フリップフロップは、インバータ回路31及び32と、記憶素子33及び34とを有して構成されている。

【0029】

1段目のインバータ回路31には、クロック信号が入力される。インバータ回路31は、入力されたクロック信号を反転し、反転したクロック信号をインバータ回路32及び記憶素子33に供給する。2段目のインバータ回路32は、インバータ回路31からのクロック信号を反転し、反転したクロック信号を記憶素子34に供給する。記憶素子33及び34では、インバータ回路31及び32からのクロック信号に基づいて、入力データの取り込み及び保持が行われる。

【0030】

このように構成されるフリップフロップでは、インバータ回路31及び32のトランジスタのスイッチング動作による消費電流が問題となる。

【0031】

図4は、フリップフロップ内のインバータ回路で発生する消費電流について説明するための図である。ここでは、インバータ回路が電源から電流を引き込む量を下向き、つまり負の値で表している。

【0032】

図4に示すように、1段目のインバータ回路31では、クロック信号の立ち下がりエッジで消費する電流が支配的である。これは、クロックの値が1から0に変化する時にpチャネルトランジスタがOFFからONに変化し、電源から電流を引き込んで次段のインバータ回路の入力を充電するからである。一方、2段目のインバータ回路32には、インバータ回路31で反転されたクロック信号が供給されるため、クロック信号の立ち上がりエッジは、2段目のインバータ回路32では、立ち下がりエッジとなる。そのため、図4に示すように、2段目のインバータ回路32では、クロック信号の立ち上がりエッジで消費する電流が支配的である。

【0033】

ここで、1段目のインバータで消費する電流と2段目のインバータで消費する電流の最大値を比較すると、1段目の消費電流の方が大きい。これは、1段目のインバータの出力負荷容量が2段目のインバータの出力負荷容量よりも大きいことに起因している。従って、2つのインバータを含めた消費電力を観測すると、クロックの立ち上がりエッジで消費する電流よりも、クロックの立ち下がりエッジで消費する電流の方が大きくなる。

【0034】

図5は、単一のクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【0035】

図5は、デジタル回路13a〜13c内の全フリップフロップを、単一のクロック信号で動作させた場合に発生する消費電力を示している。デジタル回路13a〜13c内の全フリップフロップは、図4の関係から、クロック信号の立ち下がりエッジで発生する消費電力が立ち上がりエッジで発生する消費電力より大きくなる。

【0036】

図6は、デューティ比の異なるクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【0037】

本実施の形態では、図6に示すように、クロック波形整形部11によって、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号が生成される。これらの立ち下がりエッジの位相が異なる3つのクロック信号によって、デジタル回路13a〜13c内のフリップフロップが動作する。これにより、立ち下がりエッジで発生する消費電力が分散され、デューティ比の異なる3つのクロック信号の立ち下がりエッジで発生する消費電力は、単一のクロック信号の立ち下がりエッジで発生する消費電力よりも小さくなる。

【0038】

以上のように、半導体集積回路1は、クロック波形整形部11により、クロック信号の立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる複数のクロック信号を生成し、デジタル回路13a〜13cを動作させるようにした。これにより、半導体集積回路1は、立ち下がりエッジで発生する消費電力を分散させることができる。

【0039】

よって、本実施の形態の半導体集積回路によれば、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0040】

また、クロック信号の立ち下がりエッジでの消費電力が低減し、電源電圧変動(IR drop)が抑制されることにより、デジタル領域部3で発生したノイズ等がアナログ領域部4に周り込むことを防ぐことができる。また、電源電圧変動が抑制されることにより、電源ラインの太さを細くしたり、電源ラインの間隔を狭くすることができるため、電源ピン数の低減及びパッケージの小型化が可能となる。さらに、クロック信号の立ち上がりエッジの位相は従来と同一のため、タイミング設計への影響を少なくすることができる。

【0041】

(第2の実施の形態)

次に、第2の実施の形態について説明する。

【0042】

第2の実施の形態の半導体集積回路1aは、図1のクロック波形整形部11に代わり、クロック波形整形部11aを用いて構成されている。以下、図7を用いて、クロック波形整形部11aの構成について説明する。

【0043】

図7は、第2の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【0044】

図7に示すように、クロック波形整形部11aは、1.4GHzの周波数で動作する複数、ここでは、2つのフリップフロップ41及び42と、複数、ここでは、3つの組み合わせ回路43〜45とを有して構成されている。

【0045】

本実施の形態では、PLL回路2からは、デジタル回路13a〜13cのフリップフロップの動作周波数より高い周波数のクロック信号が出力される。具体的には、PLL回路2からは、デジタル回路13a〜13cのフリップフロップの動作周波数である350MHzの4倍速のとなる1.4GHzのクロック信号が出力される。このクロック信号は、クロック波形整形部11aのフリップフロップ41及び42に供給される。

【0046】

フリップフロップ41及び42は、2ビットのカウンタを構成し、クロック信号の立ち上がりでカウントアップを行い、カウント値として0〜3を順次出力する。このカウント値は、組み合わせ回路43〜45に供給される。

【0047】

組み合わせ回路43〜45は、供給されたカウント値に応じて、クロックツリー12a〜12cに特定の値を出力する回路である。例えば、組み合わせ回路43は、カウント値が0の場合には1を、カウント値が1〜3の場合には0をクロックツリー12aに出力する。また、組み合わせ回路44は、カウント値が0及び1の場合には1を、カウント値が2及び3の場合には0をクロックツリー12bに出力する。さらに、組み合わせ回路45は、カウント値が0〜2の場合には1を、カウント値が3の場合には0をクロックツリー12cに出力する。

【0048】

このように、半導体集積回路1aのクロック波形整形部11aは、カウンタを構成するフリップフロップ41及び42と、組み合わせ回路43〜45とにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成するようにした。この結果、本実施の形態の半導体集積回路1aによれば、第1の実施の形態と同様に、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0049】

なお、組み合わせ回路43〜45の出力段に、それぞれ1.4GHz動作のフリップフロップを設けるようにしてもよい。これらのフリップフロップを設けることにより、クロック波形整形部11aは、ヒゲ状のノイズが除去されたきれいなクロック信号を出力することができる。

【0050】

(第3の実施の形態)

次に、第3の実施の形態について説明する。

【0051】

第3の実施の形態の半導体集積回路1bは、図1のクロック波形整形部11に代わり、クロック波形整形部11bを用いて構成されている。また、第3の実施の形態の半導体集積回路1bは、図1のクロックツリー12a〜12cを削除して構成されている。以下、図8を用いて、クロック波形整形部11bの構成について説明する。

【0052】

図8は、第3の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【0053】

図8に示すように、クロック波形整形部11bは、クロックツリー51〜53を有して構成されている。クロックツリー51は、立ち上がり遷移時間と立ち下がり遷移時間が異なる複数のクロックバッファ54を有する。また、クロックツリー52は、立ち下がり遷移時間がクロックバッファ54とは異なる複数のクロックバッファ55を有する。さらに、クロックツリー53は、立ち下がり遷移時間がクロックバッファ54及び55とは異なる複数のクロックバッファ56を有する。

【0054】

クロック波形整形部11bに供給されたクロック信号は、これらのクロックツリー51〜53に供給される。クロックツリー51〜53に供給されたクロック信号は、それぞれ複数のクロックバッファ54〜56を伝搬することにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なるクロック信号を出力する。

【0055】

クロックツリー51から出力されたクロック信号は、デジタル回路13aのフリップフロップに供給される。同様に、クロックツリー52から出力されたクロック信号は、デジタル回路13bのフリップフロップに供給され、クロックツリー53から出力されたクロック信号は、デジタル回路13cのフリップフロップに供給される。

【0056】

なお、本実施の形態において、クロックツリー51、52及び53は、クロック信号のH期間が延びるクロックバッファを用いているが、クロック信号のL期間が延びるクロックバッファを用いるようにしてもよい。また、これらを組み合わせて、例えば、クロックツリー51及び52は、クロック信号のH期間が延びるクロックバッファを用い、クロックツリー53は、クロック信号のL期間が延びるクロックバッファを用いるようにしてもよい。

【0057】

このように、半導体集積回路1bのクロック波形整形部11bは、それぞれ立ち下がり遷移時間の異なるクロックバッファを複数備えたクロックツリー51〜53により、立ち下がりエッジの位相が異なる3つのクロック信号を生成するようにした。この結果、本実施の形態の半導体集積回路1bによれば、第1の実施の形態と同様に、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0058】

本発明のいくつかの実施の形態を説明したが、これらの実施の形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施の形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施の形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0059】

1,1a,1b…半導体集積回路、2…PLL回路、3…デジタル領域部、4…アナログ領域部、11,11a,11b…クロック波形整形部、12a〜12c…クロックツリー、13a〜13c…デジタル回路、14a,14b…アナログ回路、21〜23…遅延回路、24,25…OR回路、26…インバータ回路、27…AND回路、31,32…インバータ回路、33,34…記憶素子、41,42…フリップフロップ、43〜45…組み合わせ回路、51〜53…クロックツリー、54〜56…クロックバッファ。

【技術分野】

【0001】

本発明の実施の形態は、半導体集積回路に関する。

【背景技術】

【0002】

近年、半導体集積回路の微細化及び高性能化に伴い、回路の大規模化及び高速化が進んでいる。その結果、半導体集積回路内での消費電力の増加が問題となっている。このような半導体集積回路は、デジタル回路を備えたデジタル領域部と、アナログ回路を備えたアナログ領域部とを有しており、消費電力の増加に伴いデジタル領域部で発生したノイズがアナログ領域部に周り込んでしまい、誤動作等を発生させるという問題がある。

【0003】

デジタル領域部のデジタル回路は、複数のフリップフロップ及び複数の組み合わせ回路を有して構成されている。また、デジタル回路内の複数のフリップフロップには、PLL回路等から所定の周波数のクロック信号が供給されており、複数のフリップフロップは、このクロック信号に基づいて動作する。これらの複数のフリップフロップは、クロック信号の立ち上がりエッジ及び立ち下がりエッジにおいて、トランジスタのスイッチング動作による消費電流が発生するため、消費電力が大きくなる。

【0004】

特に、フリップフロップの動作時の消費電力は、クロック信号の立ち上がりエッジで発生する消費電力よりも、立ち下がりエッジで発生する消費電力が大きくなっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平10−63368号公報

【特許文献2】特開2005−33089号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の実施の形態が解決しようとする課題は、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【課題を解決するための手段】

【0007】

実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

【図面の簡単な説明】

【0008】

【図1】第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【図2】クロック波形整形部の構成を説明するための図である。

【図3】フリップフロップの回路構成例を説明するための図である。

【図4】フリップフロップ内のインバータ回路で発生する消費電流について説明するための図である。

【図5】単一のクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【図6】デューティ比の異なるクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【図7】第2の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【図8】第3の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【発明を実施するための形態】

【0009】

以下、図面を参照して実施の形態の半導体集積回路について詳細に説明する。

(第1の実施の形態)

まず、図1に基づき、第1の実施の形態に係る半導体集積回路の構成について説明する。

図1は、第1の実施の形態に係る半導体集積回路の構成を示すブロック図である。

【0010】

図1に示すように、半導体集積回路1は、PLL回路2と、デジタル領域部3と、アナログ領域部4とを有して構成されている。

【0011】

クロック信号生成部としてのPLL回路2は、所定の周波数のクロック信号を生成し、後述するデジタル領域部3のクロック波形整形部11と、アナログ領域部4のアナログ回路14a及び14bとに供給する。

【0012】

デジタル領域部3は、クロック波形整形部11と、3つのクロックツリー12a〜12cと、クロックツリー12a〜12cに接続された3つのデジタル回路13a〜13cとを有して構成される。デジタル回路13a〜13cは、それぞれ所定の機能を実行する機能ブロックであり、複数のフリップフロップ及び複数の組み合わせ回路等により構成されている。なお、デジタル領域部3は、3つのクロックツリー12a〜12c及びデジタル回路13a〜13cを有する構成であるが、例えば、2つ、あるいは、4つ以上のクロックツリー及びデジタル回路を有する構成であってもよい。

【0013】

また、アナログ領域部4は、複数、ここでは、2つのアナログ回路14a及び14bを有して構成される。アナログ回路14aは、例えば、アナログ信号をデジタル信号に変換するA/D変換器であり、アナログ回路14bは、例えば、デジタル信号をアナログ信号に変換するD/A変換器である。なお、アナログ回路14a及び14bは、A/D変換器及びD/A変換器に限定されることなく、例えば、高周波(RF)回路、メモリ回路等であってもよい。

【0014】

アナログ回路14aは、デジタル回路13aに接続されており、半導体集積回路1の外部から供給されたアナログ信号をデジタル信号に変換し、デジタル回路13aに出力する。また、アナログ回路14bは、デジタル回路13bに接続されており、デジタル回路13bから供給されたデジタル信号をアナログ信号に変換し、半導体集積回路1の外部に出力する。

【0015】

クロック波形整形部11は、供給されたクロック信号からそれぞれデューティ比の異なる複数、ここでは、3つのクロック信号を生成し、クロックツリー12a〜12cに供給する。具体的には、クロック波形整形部11は、供給されたクロック信号からそれぞれ立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成し、クロックツリー12a〜12cに供給する。

【0016】

クロックツリー12aは、複数のクロックバッファにより構成されており、ドライブ力、駆動するフリップフロップの数に応じて複数のクロックバッファがツリー上に分岐して構成されている。なお、クロックツリー12b及び12cも同様の構成である。クロックツリー12a〜12cは、それぞれクロック波形整形部11から供給されたデューティ比の異なるクロック信号をデジタル回路13a〜13cに供給する。

【0017】

デジタル回路13a〜13cは、それぞれ複数のフリップフロップ及び複数の組み合わせ回路等を有し、クロックツリー12a〜12cから供給されたデューティ比の異なるクロック信号に基づいて、所定の機能を実行する。

【0018】

ここで、デューティ比の異なる複数のクロック信号、本実施の形態では、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる複数のクロック信号を生成するクロック波形整形部11の構成について説明する。

【0019】

図2は、クロック波形整形部の構成を説明するための図である。

【0020】

クロック波形整形部11は、遅延回路21、22及び23と、OR回路24及び25と、インバータ回路26と、AND回路27とを有して構成されている。

【0021】

PLL回路2から供給されたクロック信号は、遅延回路21、22及び23に供給される。また、PLL回路2から供給されたクロック信号は、OR回路24、25及びAND回路27の一方の端子に供給される。遅延回路21〜23は、それぞれ異なる遅延量を有し、供給されたクロック信号を所定の時間遅延させる。本実施の形態では、遅延回路23、遅延回路22、遅延回路21の順に、大きな遅延量を有している。

【0022】

遅延回路21は、供給されたクロック信号を所定の時間遅延させ、OR回路24の他方の端子に供給する。OR回路24は、PLL回路2からのクロック信号と、遅延回路21で所定の時間遅延されたクロック信号とのOR演算を行う。これにより、OR回路24からは、デューティ比が約60%のクロック信号が出力され、クロックツリー12aに供給される。

【0023】

遅延回路22は、供給されたクロック信号を、遅延回路21より長い所定の時間遅延させ、OR回路25の他方の端子に出力する。OR回路25は、PLL回路2からのクロック信号と、遅延回路22で遅延回路21より長い所定の時間遅延されたクロック信号とのOR演算を行う。これにより、OR回路25からは、デューティ比が約70%のクロック信号が出力され、クロックツリー12bに供給される。

【0024】

遅延回路23は、供給されたクロック信号を、遅延回路22より長い所定の時間遅延させ、インバータ回路26に出力する。インバータ回路26は、遅延回路23からの信号を反転させ、AND回路27の他方の端子に出力する。AND回路27は、PLL回路2からのクロック信号と、遅延回路23で遅延回路22より長い所定の時間遅延され、インバータ回路26で反転されたクロック信号とのAND演算を行う。これにより、AND回路27からは、ディーティ比が約30%のクロック信号が出力され、クロックツリー12cに供給される。

【0025】

このように、クロック波形整形部11は、それぞれ、遅延回路21〜23及び論理ゲート、具体的には、遅延回路21及びOR回路24により構成される組み合わせ回路と、遅延回路22及びOR回路25により構成される組み合わせ回路と、遅延回路23、インバータ回路26及びAND回路27により構成される組み合わせ回路とにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成する。

【0026】

次に、このように構成される半導体集積回路1の消費電力について説明する。半導体集積回路1では、回路規模の増大に伴い、デジタル回路13a〜13cが有するフリップフロップでの消費電力が大きくなる。以下、フリップフロップの回路構成について説明する。

【0027】

図3は、フリップフロップの回路構成例を説明するための図である。

【0028】

図3に示すように、フリップフロップは、インバータ回路31及び32と、記憶素子33及び34とを有して構成されている。

【0029】

1段目のインバータ回路31には、クロック信号が入力される。インバータ回路31は、入力されたクロック信号を反転し、反転したクロック信号をインバータ回路32及び記憶素子33に供給する。2段目のインバータ回路32は、インバータ回路31からのクロック信号を反転し、反転したクロック信号を記憶素子34に供給する。記憶素子33及び34では、インバータ回路31及び32からのクロック信号に基づいて、入力データの取り込み及び保持が行われる。

【0030】

このように構成されるフリップフロップでは、インバータ回路31及び32のトランジスタのスイッチング動作による消費電流が問題となる。

【0031】

図4は、フリップフロップ内のインバータ回路で発生する消費電流について説明するための図である。ここでは、インバータ回路が電源から電流を引き込む量を下向き、つまり負の値で表している。

【0032】

図4に示すように、1段目のインバータ回路31では、クロック信号の立ち下がりエッジで消費する電流が支配的である。これは、クロックの値が1から0に変化する時にpチャネルトランジスタがOFFからONに変化し、電源から電流を引き込んで次段のインバータ回路の入力を充電するからである。一方、2段目のインバータ回路32には、インバータ回路31で反転されたクロック信号が供給されるため、クロック信号の立ち上がりエッジは、2段目のインバータ回路32では、立ち下がりエッジとなる。そのため、図4に示すように、2段目のインバータ回路32では、クロック信号の立ち上がりエッジで消費する電流が支配的である。

【0033】

ここで、1段目のインバータで消費する電流と2段目のインバータで消費する電流の最大値を比較すると、1段目の消費電流の方が大きい。これは、1段目のインバータの出力負荷容量が2段目のインバータの出力負荷容量よりも大きいことに起因している。従って、2つのインバータを含めた消費電力を観測すると、クロックの立ち上がりエッジで消費する電流よりも、クロックの立ち下がりエッジで消費する電流の方が大きくなる。

【0034】

図5は、単一のクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【0035】

図5は、デジタル回路13a〜13c内の全フリップフロップを、単一のクロック信号で動作させた場合に発生する消費電力を示している。デジタル回路13a〜13c内の全フリップフロップは、図4の関係から、クロック信号の立ち下がりエッジで発生する消費電力が立ち上がりエッジで発生する消費電力より大きくなる。

【0036】

図6は、デューティ比の異なるクロック信号でフリップフロップを動作させた場合の消費電力について説明するための図である。

【0037】

本実施の形態では、図6に示すように、クロック波形整形部11によって、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号が生成される。これらの立ち下がりエッジの位相が異なる3つのクロック信号によって、デジタル回路13a〜13c内のフリップフロップが動作する。これにより、立ち下がりエッジで発生する消費電力が分散され、デューティ比の異なる3つのクロック信号の立ち下がりエッジで発生する消費電力は、単一のクロック信号の立ち下がりエッジで発生する消費電力よりも小さくなる。

【0038】

以上のように、半導体集積回路1は、クロック波形整形部11により、クロック信号の立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる複数のクロック信号を生成し、デジタル回路13a〜13cを動作させるようにした。これにより、半導体集積回路1は、立ち下がりエッジで発生する消費電力を分散させることができる。

【0039】

よって、本実施の形態の半導体集積回路によれば、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0040】

また、クロック信号の立ち下がりエッジでの消費電力が低減し、電源電圧変動(IR drop)が抑制されることにより、デジタル領域部3で発生したノイズ等がアナログ領域部4に周り込むことを防ぐことができる。また、電源電圧変動が抑制されることにより、電源ラインの太さを細くしたり、電源ラインの間隔を狭くすることができるため、電源ピン数の低減及びパッケージの小型化が可能となる。さらに、クロック信号の立ち上がりエッジの位相は従来と同一のため、タイミング設計への影響を少なくすることができる。

【0041】

(第2の実施の形態)

次に、第2の実施の形態について説明する。

【0042】

第2の実施の形態の半導体集積回路1aは、図1のクロック波形整形部11に代わり、クロック波形整形部11aを用いて構成されている。以下、図7を用いて、クロック波形整形部11aの構成について説明する。

【0043】

図7は、第2の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【0044】

図7に示すように、クロック波形整形部11aは、1.4GHzの周波数で動作する複数、ここでは、2つのフリップフロップ41及び42と、複数、ここでは、3つの組み合わせ回路43〜45とを有して構成されている。

【0045】

本実施の形態では、PLL回路2からは、デジタル回路13a〜13cのフリップフロップの動作周波数より高い周波数のクロック信号が出力される。具体的には、PLL回路2からは、デジタル回路13a〜13cのフリップフロップの動作周波数である350MHzの4倍速のとなる1.4GHzのクロック信号が出力される。このクロック信号は、クロック波形整形部11aのフリップフロップ41及び42に供給される。

【0046】

フリップフロップ41及び42は、2ビットのカウンタを構成し、クロック信号の立ち上がりでカウントアップを行い、カウント値として0〜3を順次出力する。このカウント値は、組み合わせ回路43〜45に供給される。

【0047】

組み合わせ回路43〜45は、供給されたカウント値に応じて、クロックツリー12a〜12cに特定の値を出力する回路である。例えば、組み合わせ回路43は、カウント値が0の場合には1を、カウント値が1〜3の場合には0をクロックツリー12aに出力する。また、組み合わせ回路44は、カウント値が0及び1の場合には1を、カウント値が2及び3の場合には0をクロックツリー12bに出力する。さらに、組み合わせ回路45は、カウント値が0〜2の場合には1を、カウント値が3の場合には0をクロックツリー12cに出力する。

【0048】

このように、半導体集積回路1aのクロック波形整形部11aは、カウンタを構成するフリップフロップ41及び42と、組み合わせ回路43〜45とにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なる3つのクロック信号を生成するようにした。この結果、本実施の形態の半導体集積回路1aによれば、第1の実施の形態と同様に、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0049】

なお、組み合わせ回路43〜45の出力段に、それぞれ1.4GHz動作のフリップフロップを設けるようにしてもよい。これらのフリップフロップを設けることにより、クロック波形整形部11aは、ヒゲ状のノイズが除去されたきれいなクロック信号を出力することができる。

【0050】

(第3の実施の形態)

次に、第3の実施の形態について説明する。

【0051】

第3の実施の形態の半導体集積回路1bは、図1のクロック波形整形部11に代わり、クロック波形整形部11bを用いて構成されている。また、第3の実施の形態の半導体集積回路1bは、図1のクロックツリー12a〜12cを削除して構成されている。以下、図8を用いて、クロック波形整形部11bの構成について説明する。

【0052】

図8は、第3の実施の形態に係るクロック波形整形部の構成を説明するための図である。

【0053】

図8に示すように、クロック波形整形部11bは、クロックツリー51〜53を有して構成されている。クロックツリー51は、立ち上がり遷移時間と立ち下がり遷移時間が異なる複数のクロックバッファ54を有する。また、クロックツリー52は、立ち下がり遷移時間がクロックバッファ54とは異なる複数のクロックバッファ55を有する。さらに、クロックツリー53は、立ち下がり遷移時間がクロックバッファ54及び55とは異なる複数のクロックバッファ56を有する。

【0054】

クロック波形整形部11bに供給されたクロック信号は、これらのクロックツリー51〜53に供給される。クロックツリー51〜53に供給されたクロック信号は、それぞれ複数のクロックバッファ54〜56を伝搬することにより、立ち上がりエッジの位相が同一で、立ち下がりエッジの位相が異なるクロック信号を出力する。

【0055】

クロックツリー51から出力されたクロック信号は、デジタル回路13aのフリップフロップに供給される。同様に、クロックツリー52から出力されたクロック信号は、デジタル回路13bのフリップフロップに供給され、クロックツリー53から出力されたクロック信号は、デジタル回路13cのフリップフロップに供給される。

【0056】

なお、本実施の形態において、クロックツリー51、52及び53は、クロック信号のH期間が延びるクロックバッファを用いているが、クロック信号のL期間が延びるクロックバッファを用いるようにしてもよい。また、これらを組み合わせて、例えば、クロックツリー51及び52は、クロック信号のH期間が延びるクロックバッファを用い、クロックツリー53は、クロック信号のL期間が延びるクロックバッファを用いるようにしてもよい。

【0057】

このように、半導体集積回路1bのクロック波形整形部11bは、それぞれ立ち下がり遷移時間の異なるクロックバッファを複数備えたクロックツリー51〜53により、立ち下がりエッジの位相が異なる3つのクロック信号を生成するようにした。この結果、本実施の形態の半導体集積回路1bによれば、第1の実施の形態と同様に、クロック信号の立ち下がりエッジで発生する消費電力を低減することができる。

【0058】

本発明のいくつかの実施の形態を説明したが、これらの実施の形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施の形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施の形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0059】

1,1a,1b…半導体集積回路、2…PLL回路、3…デジタル領域部、4…アナログ領域部、11,11a,11b…クロック波形整形部、12a〜12c…クロックツリー、13a〜13c…デジタル回路、14a,14b…アナログ回路、21〜23…遅延回路、24,25…OR回路、26…インバータ回路、27…AND回路、31,32…インバータ回路、33,34…記憶素子、41,42…フリップフロップ、43〜45…組み合わせ回路、51〜53…クロックツリー、54〜56…クロックバッファ。

【特許請求の範囲】

【請求項1】

所定の周波数のクロック信号を生成するクロック信号生成部と、

前記クロック信号生成部で生成された前記クロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成するクロック波形整形部と、

それぞれが前記クロック波形整形部で生成された前記複数のクロック信号のいずれかで動作する複数のフリップフロップを有する複数の機能ブロックと、

を有することを特徴とする半導体集積回路。

【請求項2】

前記クロック波形整形部は、前記クロック信号をそれぞれ異なる遅延量で遅延させる複数の遅延回路と、前記複数の遅延回路で遅延された複数のクロック信号と前記クロック信号との論理演算を行う論理ゲートとにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記クロック波形整形部は、前記クロック信号の立ち上がりエッジでカウントアップするカウンタと、前記カウンタでカウントされたカウント値に応じて特定の値を出力する複数の組み合わせ回路とにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項4】

前記クロック波形整形部は、それぞれが立ち上がり遷移時間と立ち下がり遷移時間が異なる複数のクロックバッファを有する複数のクロックツリーにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項5】

前記クロック信号で動作し、かつ、前記複数の機能ブロックのそれぞれに接続される複数のアナログ回路を有することを特徴とする請求項1から請求項4のいずれか1つに記載の半導体集積回路。

【請求項1】

所定の周波数のクロック信号を生成するクロック信号生成部と、

前記クロック信号生成部で生成された前記クロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成するクロック波形整形部と、

それぞれが前記クロック波形整形部で生成された前記複数のクロック信号のいずれかで動作する複数のフリップフロップを有する複数の機能ブロックと、

を有することを特徴とする半導体集積回路。

【請求項2】

前記クロック波形整形部は、前記クロック信号をそれぞれ異なる遅延量で遅延させる複数の遅延回路と、前記複数の遅延回路で遅延された複数のクロック信号と前記クロック信号との論理演算を行う論理ゲートとにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項3】

前記クロック波形整形部は、前記クロック信号の立ち上がりエッジでカウントアップするカウンタと、前記カウンタでカウントされたカウント値に応じて特定の値を出力する複数の組み合わせ回路とにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項4】

前記クロック波形整形部は、それぞれが立ち上がり遷移時間と立ち下がり遷移時間が異なる複数のクロックバッファを有する複数のクロックツリーにより構成されていることを特徴とする請求項1に記載の半導体集積回路。

【請求項5】

前記クロック信号で動作し、かつ、前記複数の機能ブロックのそれぞれに接続される複数のアナログ回路を有することを特徴とする請求項1から請求項4のいずれか1つに記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−195689(P2012−195689A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−56890(P2011−56890)

【出願日】平成23年3月15日(2011.3.15)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月15日(2011.3.15)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]