半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路に関するものである。

【背景技術】

【0002】

制御信号に基づいて、IGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor field effect transistor)などの絶縁ゲート型半導体素子を駆動する半導体集積回路が知られている。

【0003】

この半導体集積回路においては、当該絶縁ゲート型半導体素子のゲート・エミッタ間の容量特性に起因して、不要なミラー電圧がターンオフ・ターンオン時にゲート端子に生じることがある。このミラー電圧の発生時間が長い場合には、スイッチング周波数を高くすることができないという問題があった。

【0004】

そこで、この問題を解決するために様々な技術が提案されている。例えば、特許文献1には、絶縁ゲート型半導体素子のゲート端子に第1及び第2駆動回路を接続し、当該第1及び第2駆動回路によって当該ゲート端子の電圧を段階的に上昇または下降させることにより、ミラー電圧の発生時間を短縮する技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−253646号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示の技術においては、第1及び第2駆動回路のオン、オフの切り替りのタイミングで、半導体集積回路内で消費電流となる貫通電流が発生してしまうという問題があった。

【0007】

そこで、本発明は、上記のような問題点を鑑みてなされたものであり、絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体集積回路は、制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路であって、各々が、高電位・低電位電源間にトーテムポール接続されたソース側及びシンク側のスイッチング素子の対からなる第1及び第2駆動回路を備える。前記第1及び第2駆動回路のそれぞれにおける前記ソース側及びシンク側のスイッチング素子同士の間の接続点は、前記絶縁ゲート型半導体素子のゲート端子と接続される。前記半導体集積回路は、前記絶縁ゲート型半導体素子のゲート端子の電圧と、基準電圧とを比較するコンパレータ回路と、前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第1出力信号を、前記第2駆動回路の前記ソース側のスイッチング素子のゲート端子に出力する第1演算回路とを備える。前記半導体集積回路は、前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第2出力信号を、前記第2駆動回路の前記シンク側のスイッチング素子のゲート端子に出力する第2演算回路と、前記制御信号を遅延させて得られる遅延信号を、前記第1駆動回路の前記ソース側及びシンク側のスイッチング素子のゲート端子に出力する遅延回路とを備える。前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くない。

【発明の効果】

【0009】

本発明によれば、第2駆動回路のシンク側のスイッチング素子がオンからオフするタイミングは、第1駆動回路のソース側のスイッチング素子がオフからオンするタイミングよりも遅くない。したがって、当該シンク側のスイッチング素子、及び、当該ソース側のスイッチング素子を通る貫通電流を抑制することができる。また、第2駆動回路のソース側のスイッチング素子がオンからオフするタイミングは、第1駆動回路のシンク側のスイッチング素子がオフからオンするタイミングよりも遅くない。したがって、当該シンク側のスイッチング素子、及び、当該ソース側のスイッチング素子を通る貫通電流を抑制することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1に係る半導体集積回路の構成を示す回路図である。

【図2】実施の形態1に係る半導体集積回路の動作を示すタイミングチャートである。

【図3】実施の形態2に係る半導体集積回路の構成を示す回路図である。

【発明を実施するための形態】

【0011】

<実施の形態1>

図1は、本発明の実施の形態1に係る半導体集積回路の構成を示す回路図である。この半導体集積回路は、互いに異なる電圧レベル(HIGH,LOW)を選択的にとる制御信号Vinに基づいて、絶縁ゲート型半導体素子31(ここではNMOS)を駆動する回路である。

【0012】

図1に示されるように、本実施の形態に係る半導体集積回路は、第1及び第2駆動回路11,12と、インバータ15と、コンパレータ回路16と、第1演算回路であるNAND回路17と、第2演算回路であるNOR回路18と、遅延回路19とを備えている。

【0013】

第1駆動回路11は、高電位(VCC)・低電位(VGND)電源間にトーテムポール接続されたPMOS1(ソース側のスイッチング素子)及びNMOS2(シンク側のスイッチング素子)の対から構成されている。PMOS1及びNMOS2のそれぞれのゲート端子は互いに接続されており、PMOS1のソース端子は電源電圧VCCと接続され、NMOS2のドレイン端子はグランド電圧VGNDと接続されている。そして、PMOS1のドレイン端子と、NMOS2のドレイン端子とは互いに接続されており、PMOS1及びNMOS2同士の間の接続点は、絶縁ゲート型半導体素子31のゲート端子と端子25を介して接続されている。

【0014】

第2駆動回路12は、高電位(VCC)・低電位(VGND)電源間にトーテムポール接続されたPMOS3(ソース側のスイッチング素子)及びNMOS4(シンク側のスイッチング素子)の対から構成されている。PMOS3及びNMOS4は、PMOS1及びNMOS2と同様に接続されており、PMOS3及びNMOS4同士の間の接続点は、絶縁ゲート型半導体素子31のゲート端子と端子25を介して接続されている。

【0015】

なお、以下においては、PMOS1及びNMOS2のゲート端子の電圧を「ゲート電圧VG1」とし、PMOS3のゲート端子の電圧を「ゲート電圧VG3」とし、NMOS4のゲート端子の電圧を「ゲート電圧VG4」として説明する。

【0016】

インバータ15は、制御信号Vinを反転して得られる反転信号を、NAND回路17の入力端子の一方、及び、NOR回路18の入力端子の一方にそれぞれ出力する。

【0017】

コンパレータ回路16は、絶縁ゲート型半導体素子31のゲート端子の電圧VGと、基準電圧Vrefとを比較する。そして、コンパレータ回路16は、その比較結果を、NAND回路17の入力端子の他方、及び、NOR回路18の入力端子の他方にそれぞれ出力する。本実施の形態では、コンパレータ回路16は、ゲート電圧VGが基準電圧Vrefより低い場合には出力電圧(以下、「電圧V16」と呼ぶ)としてLOWを出力し、ゲート電圧VGが基準電圧Vref以上の場合には電圧V16としてHIGHを出力するものとする。なお、ここでは、コンパレータ回路16の一例として、オペアンプ回路が用いられており、その基準電圧Vrefとして、絶縁ゲート型半導体素子31の閾値電圧Vthと同じ電圧が設定されているものとする。

【0018】

NAND回路17は、制御信号Vin(ここではインバータ15からの反転信号)と、コンパレータ回路16での比較結果(電圧V16)とに基づいて、それらの論理積の否定をとる演算を行い、当該演算結果を示す第1出力信号を、第2駆動回路12のPMOS3のゲート端子に出力する。つまり、NAND回路17は、反転信号及び電圧V16がいずれもHIGHである場合には、PMOS3のゲート電圧VG3をLOWにし、それ以外の場合にはゲート電圧VG3をHIGHにする。

【0019】

NOR回路18は、制御信号Vin(ここではインバータ15からの反転信号)と、コンパレータ回路16での比較結果(電圧V16)とに基づいて、それらの論理和の否定をとる演算を行い、当該演算結果を示す第2出力信号を、第2駆動回路12のNMOS4のゲート端子に出力する。つまり、NOR回路18は、反転信号及び電圧V16がいずれもLOWである場合には、NMOS4のゲート電圧VG4をHIGHにし、それ以外の場合にはゲート電圧VG4をLOWにする。

【0020】

遅延回路19は、制御信号Vinを遅延させて得られる遅延信号を、第1駆動回路11のPMOS1及びNMOS2のそれぞれのゲート端子に出力する。本実施の形態では、遅延回路19は、直列に接続された二つのインバータ19a,19bであり、比較的単純に構成されている。なお、この遅延回路19が、制御信号Vinをどれぐらい遅延させるかについては、次の動作の説明において述べる。

【0021】

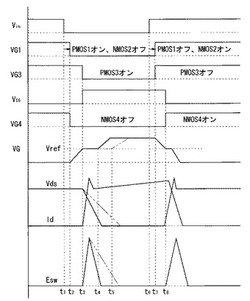

図2は、本実施の形態に係る半導体集積回路の動作を示すタイミングチャートである。この図には、上述の制御信号Vin等以外にも、絶縁ゲート型半導体素子31のソース端子とドレイン端子との間のソースドレイン電圧Vds、そのドレイン電流Id、スイッチング損失Eswが示されている。以下、この図2を用いて半導体集積回路の動作について説明する。なお、時点t1より前では、ゲート電圧VG1,VG3,VG4はHIGHであり、V16はLOWであり、PMOS1,3はオフ、NMOS2,4はオンであるものとする。

【0022】

まず、時点t1において、制御信号VinがHIGHから「LOW」に切り替えられる。制御信号Vinの変化は、入力信号を遅延させる遅延回路19を介してPMOS1及びNMOS2に伝達されることから、ゲート電圧VG1はLOWに切り替らない。したがって、PMOS1及びNMOS2のスイッチは切り替らない。同様に、制御信号Vinの変化は、遅延回路と同様に入力信号を遅延させるインバータ15及びNAND回路17を介してPMOS3に伝達されることから、ゲート電圧VG3,VG4は変化しない。したがって、PMOS3及びNMOS4のスイッチは切り替らない。

【0023】

時点t1後、NAND回路17及びNOR回路18には、制御信号Vin(LOW)の反転信号の「HIGH」と、電圧V16の「LOW」とが入力される。そうすると、NAND回路17は、次の時点t2においてもゲート電圧VG3を「HIGH」に維持するが、NOR回路18は、次の時点t2においてはゲート電圧VG4をHIGHから「LOW」に切り替えることになる。

【0024】

その後、時点t2において、制御信号Vinの遅延信号の「LOW」がPMOS1及びNMOS2のゲート端子に入力される。つまり、ゲート電圧VG1がHIGHから「LOW」に切り替えられる。したがって、PMOS1はオフからオン、NMOS2はオンからオフにそれぞれ切り替る。また、時点t2において、上述したようにゲート電圧VG3は「HIGH」に維持されるから、PMOS3はオフに維持される。一方、上述したようにゲート電圧VG4はNOR回路18により「LOW」に切り替えられるから、NMOS4はオンからオフに切り替えられる。

【0025】

ここで、仮に、遅延回路19が設けられていなければ、制御信号Vinが、遅延されずにPMOS1及びNMOS2のゲート端子に入力されることから、制御信号Vinが「LOW」になるのとほぼ同時にPMOS1及びNMOS2のゲート電圧VG1が「LOW」となる。その結果、PMOS1及びNMOS2のゲート電圧VG1が「LOW」になるタイミングのほうが、NMOS4のゲート電圧VG4が「LOW」になるタイミングよりも早くなる。この場合、PMOS1がオンに切り替ってから、NMOS4がオフに切り替るまでに時間差が生じることから、僅かな時間ではあるがPMOS1及びNMOS4がいずれもオンとなる。その結果、その時間にPMOS1及びNMOS4を介して消費電流となる貫通電流が流れてしまう。

【0026】

それに対して本実施の形態では、NMOS4が、時点t1での第2出力信号(ゲート電圧VG4)の変化に応じてオンからオフに切り替えられるタイミングと、PMOS1が、同時点t1での遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングとが、時点t2において互いに一致するように、遅延信号の遅延時間が設定されている。つまり、図2の左側の矢印に示されるように、ゲート電圧VG1がLOWに切り替るタイミングが、ゲート電圧VG4がLOWに切り替るタイミング(時点t2)に遅延するように構成されている。したがって、PMOS1及びNMOS4を介して、消費電流となる貫通電流が流れるのを抑制することができる。

【0027】

時点t2後、PMOS1はオン、NMOS2,4はオフとなっていることから、絶縁ゲート型半導体素子31のゲート電圧VGは上昇していく。

【0028】

そして、時点t3において、ゲート電圧VGが、絶縁ゲート型半導体素子31の閾値電圧Vth(つまり、基準電圧Vref)以上になると、コンパレータ回路16は電圧V16をLOWから「HIGH」にする。したがって、NAND回路17及びNOR回路18には、反転信号の「HIGH」と、電圧V16の「HIGH」とが入力される。そうすると、NOR回路18が、時点t3においてもゲート電圧VG4を「LOW」に維持することから、NMOS4はオフに維持される。一方、NAND回路17が、時点t3においてはゲート電圧V3をHIGHから「LOW」に切り替えることから、PMOS3はオフからオンに切り替えられる。

【0029】

このように、本実施の形態では、PMOS3が、第1出力信号(ゲート電圧VG3)の変化に応じてオフからオンに切り替えられるタイミングは、PMOS1が、遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングよりも遅い。これにより、絶縁ゲート型半導体素子31のゲート電圧VGが閾値電圧Vth以上になるまでは、弱いソース能力でゲート電圧VGをチャージ(充電)し、当該ゲート電圧VGが閾値電圧Vth以上になると、強いソース能力でゲート電圧VGをチャージすることになる。

【0030】

その結果、図2に示されるように、PMOS3をオンしたときのゲート電圧VGが立ち上がる(実線)までのミラー期間(t3〜t4)は、PMOS3をオンしないときのゲート電圧VGが立ち上がる(二点鎖線)までのミラー期間(t3〜t5)よりも短縮することができる。したがって、絶縁ゲート型半導体素子31のソースドレイン電圧Vdsが完全に立ち下がるまでの時間(実線)は、PMOS3がオンしないときのその時間(二点鎖線)よりも短縮することができることから、スイッチング損失Eswを小さくすることができる。

【0031】

次に、時点t6において、制御信号VinがLOWから「HIGH」に切り替えられる。この時点t6では、時点t1と同様の遅延が生じることから、PMOS1,3及びNMOS2,4のスイッチは切り替らない。

【0032】

時点t6後、NAND回路17及びNOR回路18には、制御信号Vin(HIGH)の反転信号の「LOW」と、電圧V16の「HIGH」とが入力される。そうすると、NOR回路18は、次の時点t7においてもゲート電圧VG4を「LOW」に維持するが、NAND回路17は、次の時点t7においてはゲート電圧VG3をLOWから「HIGH」に切り替えることになる。

【0033】

その後、時点t7において、制御信号Vinの遅延信号の「HIGH」がPMOS1及びNMOS2のゲート端子に入力される。つまり、ゲート電圧VG1がLOWから「HIGH」に切り替えられる。したがって、PMOS1はオンからオフ、NMOS2はオフからオンにそれぞれ切り替る。また、時点t7において、上述したようにゲート電圧VG4は「LOW」に維持されるから、NMOS4はオフに維持される。一方、上述したようにゲート電圧VG3はNAND回路17により「HIGH」に切り替えられるから、PMOS3はオンからオフに切り替えられる。

【0034】

ここで、仮に、遅延回路19が設けられていなければ、制御信号Vinが、遅延されずにPMOS1及びNMOS2のゲート端子に入力されることから、制御信号Vinが「HIGH」になるのとほぼ同時にPMOS1及びNMOS2のゲート電圧VG1が「HIGH」となる。その結果、PMOS1及びNMOS2のゲート電圧VG1が「HIGH」になるタイミングのほうが、PMOS3のゲート電圧が「HIGH」になるタイミングよりも早くなる。この場合、NMOS2がオンに切り替ってから、PMOS3がオフに切り替るまでに時間差が生じることから、僅かな時間ではあるがPMOS3及びNMOS2がいずれもオンとなる。その結果、その時間にPMOS3及びNMOS2を介して消費電流となる貫通電流が流れてしまう。

【0035】

それに対して本実施の形態では、PMOS3が、時点t6での第1出力信号(ゲート電圧VG3)の変化に応じてオンからオフに切り替えられるタイミングと、NMOS2が、同時点t6での遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングとが、時点t7において互いに一致するように、遅延信号の遅延時間が設定されている。つまり、図2の右側の矢印に示されるように、ゲートVG1がHIGHに切り替るタイミングが、ゲート電圧VG3がHIGHに切り替るタイミング(時点t7)に遅延するように構成されている。したがって、PMOS3及びNMOS2を介して、消費電流となる貫通電流が流れるのを抑制することができる。

【0036】

時点t7後、PMOS1,3はオフ、NMOS2はオンとなっていることから、絶縁ゲート型半導体素子31のゲート電圧VGは下降していく。

【0037】

そして、時点t8において、ゲート電圧VGが、絶縁ゲート型半導体素子31の閾値電圧Vth(Vref)より低くなると、コンパレータ回路16は電圧V16をHIGHから「LOW」にする。したがって、NAND回路17及びNOR回路18には、反転信号の「LOW」と、電圧V16の「LOW」とが入力される。そうすると、NAND回路17が、時点t8においてもゲート電圧VG3を「HIGH」に維持することから、PMOS3はオフに維持される。一方、NOR回路18が、時点t8においてはゲート電圧VG4をLOWから「HIGH」に切り替えることから、NMOS4はオフからオンに切り替えられる。

【0038】

このように、本実施の形態では、NMOS4が、第2出力信号(ゲート電圧VG4)の変化に応じてオフからオンに切り替えられるタイミングは、NMOS2が、遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングよりも遅い。これにより、絶縁ゲート型半導体素子31のゲート電圧VGが閾値電圧Vthより低くなるまでは、弱いシンク能力でゲート電圧VGをディスチャージ(放電)し、当該ゲート電圧VGが閾値電圧Vthより低くなると、強いシンク能力でゲート電圧VGをディスチャージすることになる。

【0039】

その結果、上述と同様に、NMOS4をオンしたときのゲート電圧VGが立ち下がるまでのミラー期間を、NMOS4をオンしないときのミラー期間よりも短縮することができる。したがって、スイッチング損失Eswを小さくすることができる。

【0040】

以上のような動作を行う本実施の形態に係る半導体集積回路によれば、NMOS4がオンからオフするタイミングと、PMOS1がオフからオンするタイミングとが互いに一致し、また、PMOS3がオンからオフするタイミングと、NMOS2がオフからオンするタイミングとが互いに一致している。したがって、消費電流となる貫通電流を抑制することができる。

【0041】

なお、貫通電流を抑制することだけを望むのであれば、以上の構成に限ったものではない。具体的には、NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなくすればよい。このようにした場合であっても、貫通電流を抑制することができる。ただし、以上の一連の処理を高速化したいのであれば、上述したように、各タイミングを一致させることが望ましい。

【0042】

また、本実施の形態に係る半導体集積回路によれば、PMOS3がオフからオンに切り替えられるタイミングは、PMOS1がオフからオンに切り替えられるタイミングよりも遅く、NMOS4がオフからオンに切り替えられるタイミングは、NMOS2がオフからオンに切り替えられるタイミングよりも遅い。したがって、ミラー期間を短縮することができ、スイッチング損失Eswを小さくすることができる。また、スイッチングの高周波数化の実現も期待できる。なお、第2駆動回路12(PMOS3及びNMOS4)の駆動能力を大きくすれば、ミラー期間を短縮する効果を高めることができる。

【0043】

また、本実施の形態では、遅延回路19として、直列に接続された二つのインバータ19a,19bを用いたが、図2に示すような遅延時間を遅延設定することができるものであれば、他の構成を採用してもよい。

【0044】

また、本実施の形態では、コンパレータ回路16の基準電圧Vrefを、絶縁ゲート型半導体素子31の閾値電圧Vthと同じ電圧とした。しかし、現実には製造バラツキが存在することから、閾値電圧Vth(ミラー電圧)はばらつくものとなっている。そこで、基準電圧Vrefとしては、閾値電圧Vth(ミラー電圧)が取り得ると予想される値のうち最小値に設定することが好ましい。

【0045】

また、本実施の形態では、第1演算回路をNAND回路17として説明したが、それと同様の演算を行うものであれば、他の演算回路を組み合わせたものであってもよい。同様に、本実施の形態では、第2演算回路をNOR回路18として説明したが、それと同様の演算を行うものであれば、他の演算回路を組み合わせたものであってもよい。

【0046】

<実施の形態2>

一般に、SiCのMOSFETの閾値電圧は、例えば2Vというように低くなっている。そのため、SiCのMOSFETを絶縁ゲート型半導体素子31に適用した場合において、絶縁ゲート型半導体素子31のゲート端子に入力されるLOW信号の電圧が、製造ばらつきなどにより閾値電圧以上となった場合には、実施の形態1で説明した所望の動作を行うことができない可能性がある。そこで、本発明の実施の形態2では、閾値電圧が低い半導体素子(例えばSiCのMOSFET)が、絶縁ゲート型半導体素子31に適用された場合であっても、所望の動作を確実に行うことが可能となっている。

【0047】

図3は、本実施の形態に係る半導体集積回路の構成を示す回路図である。以下、本実施の形態に係る半導体集積回路において、実施の形態1で説明した構成要素と類似するものについては同じ符号を付し、実施の形態1と異なる点を中心に説明する。

【0048】

図3に示されるように、本実施の形態では、実施の形態1の構成に内部電源回路41を加えたものとなっている。この内部電源回路41は、絶縁ゲート型半導体素子31のソース端子に端子26を介して接続され、当該ソース端子に負バイアスVEを印加する。この場合、絶縁ゲート型半導体素子31のソース端子にVxという電圧が印加されていたとしても、MOSFETの性質から、当該ソース端子に(Vx−VE)という電圧が印加されていることと等価となる。

【0049】

したがって、例えば、絶縁ゲート型半導体素子31の閾値電圧Vthが2V、負バイアスVEが7Vである場合、絶縁ゲート型半導体素子31の閾値電圧は実質的に9Vとなる。この場合において、絶縁ゲート型半導体素子31のゲート端子にLOW信号を入力した場合に、その電圧が元の閾値電圧の2Vより多少高い電圧(例えば3V)であっても、そのLOW信号を通常のLOW信号として扱うことができる。

【0050】

このように、本実施の形態によれば、閾値電圧が低い半導体素子が、絶縁ゲート型半導体素子31に適用された場合であっても、所望の動作を確実に行うことができる。

【0051】

なお、本実施の形態においても、実施の形態1と同様に第2駆動回路12を設けていることから、強いシンク能力でゲート電圧VGをディスチャージすることが可能である。したがって、この作用によりLOW信号の電圧を低くすることができることから、内部電源回路41の負バイアスVEを比較的低く設定することができる。よって、その分だけ寿命を延ばすことができ、半導体集積回路の信頼性を高めるという効果も期待できる。

【符号の説明】

【0052】

1,3 PMOS、2,4 NMOS、11 第1駆動回路、12 第2駆動回路、16 コンパレータ回路、17 NAND回路、18 NOR回路、19 遅延回路、31 絶縁ゲート型半導体素子、41 内部電源回路。

【技術分野】

【0001】

本発明は、制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路に関するものである。

【背景技術】

【0002】

制御信号に基づいて、IGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor field effect transistor)などの絶縁ゲート型半導体素子を駆動する半導体集積回路が知られている。

【0003】

この半導体集積回路においては、当該絶縁ゲート型半導体素子のゲート・エミッタ間の容量特性に起因して、不要なミラー電圧がターンオフ・ターンオン時にゲート端子に生じることがある。このミラー電圧の発生時間が長い場合には、スイッチング周波数を高くすることができないという問題があった。

【0004】

そこで、この問題を解決するために様々な技術が提案されている。例えば、特許文献1には、絶縁ゲート型半導体素子のゲート端子に第1及び第2駆動回路を接続し、当該第1及び第2駆動回路によって当該ゲート端子の電圧を段階的に上昇または下降させることにより、ミラー電圧の発生時間を短縮する技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−253646号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示の技術においては、第1及び第2駆動回路のオン、オフの切り替りのタイミングで、半導体集積回路内で消費電流となる貫通電流が発生してしまうという問題があった。

【0007】

そこで、本発明は、上記のような問題点を鑑みてなされたものであり、絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体集積回路は、制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路であって、各々が、高電位・低電位電源間にトーテムポール接続されたソース側及びシンク側のスイッチング素子の対からなる第1及び第2駆動回路を備える。前記第1及び第2駆動回路のそれぞれにおける前記ソース側及びシンク側のスイッチング素子同士の間の接続点は、前記絶縁ゲート型半導体素子のゲート端子と接続される。前記半導体集積回路は、前記絶縁ゲート型半導体素子のゲート端子の電圧と、基準電圧とを比較するコンパレータ回路と、前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第1出力信号を、前記第2駆動回路の前記ソース側のスイッチング素子のゲート端子に出力する第1演算回路とを備える。前記半導体集積回路は、前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第2出力信号を、前記第2駆動回路の前記シンク側のスイッチング素子のゲート端子に出力する第2演算回路と、前記制御信号を遅延させて得られる遅延信号を、前記第1駆動回路の前記ソース側及びシンク側のスイッチング素子のゲート端子に出力する遅延回路とを備える。前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くない。

【発明の効果】

【0009】

本発明によれば、第2駆動回路のシンク側のスイッチング素子がオンからオフするタイミングは、第1駆動回路のソース側のスイッチング素子がオフからオンするタイミングよりも遅くない。したがって、当該シンク側のスイッチング素子、及び、当該ソース側のスイッチング素子を通る貫通電流を抑制することができる。また、第2駆動回路のソース側のスイッチング素子がオンからオフするタイミングは、第1駆動回路のシンク側のスイッチング素子がオフからオンするタイミングよりも遅くない。したがって、当該シンク側のスイッチング素子、及び、当該ソース側のスイッチング素子を通る貫通電流を抑制することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1に係る半導体集積回路の構成を示す回路図である。

【図2】実施の形態1に係る半導体集積回路の動作を示すタイミングチャートである。

【図3】実施の形態2に係る半導体集積回路の構成を示す回路図である。

【発明を実施するための形態】

【0011】

<実施の形態1>

図1は、本発明の実施の形態1に係る半導体集積回路の構成を示す回路図である。この半導体集積回路は、互いに異なる電圧レベル(HIGH,LOW)を選択的にとる制御信号Vinに基づいて、絶縁ゲート型半導体素子31(ここではNMOS)を駆動する回路である。

【0012】

図1に示されるように、本実施の形態に係る半導体集積回路は、第1及び第2駆動回路11,12と、インバータ15と、コンパレータ回路16と、第1演算回路であるNAND回路17と、第2演算回路であるNOR回路18と、遅延回路19とを備えている。

【0013】

第1駆動回路11は、高電位(VCC)・低電位(VGND)電源間にトーテムポール接続されたPMOS1(ソース側のスイッチング素子)及びNMOS2(シンク側のスイッチング素子)の対から構成されている。PMOS1及びNMOS2のそれぞれのゲート端子は互いに接続されており、PMOS1のソース端子は電源電圧VCCと接続され、NMOS2のドレイン端子はグランド電圧VGNDと接続されている。そして、PMOS1のドレイン端子と、NMOS2のドレイン端子とは互いに接続されており、PMOS1及びNMOS2同士の間の接続点は、絶縁ゲート型半導体素子31のゲート端子と端子25を介して接続されている。

【0014】

第2駆動回路12は、高電位(VCC)・低電位(VGND)電源間にトーテムポール接続されたPMOS3(ソース側のスイッチング素子)及びNMOS4(シンク側のスイッチング素子)の対から構成されている。PMOS3及びNMOS4は、PMOS1及びNMOS2と同様に接続されており、PMOS3及びNMOS4同士の間の接続点は、絶縁ゲート型半導体素子31のゲート端子と端子25を介して接続されている。

【0015】

なお、以下においては、PMOS1及びNMOS2のゲート端子の電圧を「ゲート電圧VG1」とし、PMOS3のゲート端子の電圧を「ゲート電圧VG3」とし、NMOS4のゲート端子の電圧を「ゲート電圧VG4」として説明する。

【0016】

インバータ15は、制御信号Vinを反転して得られる反転信号を、NAND回路17の入力端子の一方、及び、NOR回路18の入力端子の一方にそれぞれ出力する。

【0017】

コンパレータ回路16は、絶縁ゲート型半導体素子31のゲート端子の電圧VGと、基準電圧Vrefとを比較する。そして、コンパレータ回路16は、その比較結果を、NAND回路17の入力端子の他方、及び、NOR回路18の入力端子の他方にそれぞれ出力する。本実施の形態では、コンパレータ回路16は、ゲート電圧VGが基準電圧Vrefより低い場合には出力電圧(以下、「電圧V16」と呼ぶ)としてLOWを出力し、ゲート電圧VGが基準電圧Vref以上の場合には電圧V16としてHIGHを出力するものとする。なお、ここでは、コンパレータ回路16の一例として、オペアンプ回路が用いられており、その基準電圧Vrefとして、絶縁ゲート型半導体素子31の閾値電圧Vthと同じ電圧が設定されているものとする。

【0018】

NAND回路17は、制御信号Vin(ここではインバータ15からの反転信号)と、コンパレータ回路16での比較結果(電圧V16)とに基づいて、それらの論理積の否定をとる演算を行い、当該演算結果を示す第1出力信号を、第2駆動回路12のPMOS3のゲート端子に出力する。つまり、NAND回路17は、反転信号及び電圧V16がいずれもHIGHである場合には、PMOS3のゲート電圧VG3をLOWにし、それ以外の場合にはゲート電圧VG3をHIGHにする。

【0019】

NOR回路18は、制御信号Vin(ここではインバータ15からの反転信号)と、コンパレータ回路16での比較結果(電圧V16)とに基づいて、それらの論理和の否定をとる演算を行い、当該演算結果を示す第2出力信号を、第2駆動回路12のNMOS4のゲート端子に出力する。つまり、NOR回路18は、反転信号及び電圧V16がいずれもLOWである場合には、NMOS4のゲート電圧VG4をHIGHにし、それ以外の場合にはゲート電圧VG4をLOWにする。

【0020】

遅延回路19は、制御信号Vinを遅延させて得られる遅延信号を、第1駆動回路11のPMOS1及びNMOS2のそれぞれのゲート端子に出力する。本実施の形態では、遅延回路19は、直列に接続された二つのインバータ19a,19bであり、比較的単純に構成されている。なお、この遅延回路19が、制御信号Vinをどれぐらい遅延させるかについては、次の動作の説明において述べる。

【0021】

図2は、本実施の形態に係る半導体集積回路の動作を示すタイミングチャートである。この図には、上述の制御信号Vin等以外にも、絶縁ゲート型半導体素子31のソース端子とドレイン端子との間のソースドレイン電圧Vds、そのドレイン電流Id、スイッチング損失Eswが示されている。以下、この図2を用いて半導体集積回路の動作について説明する。なお、時点t1より前では、ゲート電圧VG1,VG3,VG4はHIGHであり、V16はLOWであり、PMOS1,3はオフ、NMOS2,4はオンであるものとする。

【0022】

まず、時点t1において、制御信号VinがHIGHから「LOW」に切り替えられる。制御信号Vinの変化は、入力信号を遅延させる遅延回路19を介してPMOS1及びNMOS2に伝達されることから、ゲート電圧VG1はLOWに切り替らない。したがって、PMOS1及びNMOS2のスイッチは切り替らない。同様に、制御信号Vinの変化は、遅延回路と同様に入力信号を遅延させるインバータ15及びNAND回路17を介してPMOS3に伝達されることから、ゲート電圧VG3,VG4は変化しない。したがって、PMOS3及びNMOS4のスイッチは切り替らない。

【0023】

時点t1後、NAND回路17及びNOR回路18には、制御信号Vin(LOW)の反転信号の「HIGH」と、電圧V16の「LOW」とが入力される。そうすると、NAND回路17は、次の時点t2においてもゲート電圧VG3を「HIGH」に維持するが、NOR回路18は、次の時点t2においてはゲート電圧VG4をHIGHから「LOW」に切り替えることになる。

【0024】

その後、時点t2において、制御信号Vinの遅延信号の「LOW」がPMOS1及びNMOS2のゲート端子に入力される。つまり、ゲート電圧VG1がHIGHから「LOW」に切り替えられる。したがって、PMOS1はオフからオン、NMOS2はオンからオフにそれぞれ切り替る。また、時点t2において、上述したようにゲート電圧VG3は「HIGH」に維持されるから、PMOS3はオフに維持される。一方、上述したようにゲート電圧VG4はNOR回路18により「LOW」に切り替えられるから、NMOS4はオンからオフに切り替えられる。

【0025】

ここで、仮に、遅延回路19が設けられていなければ、制御信号Vinが、遅延されずにPMOS1及びNMOS2のゲート端子に入力されることから、制御信号Vinが「LOW」になるのとほぼ同時にPMOS1及びNMOS2のゲート電圧VG1が「LOW」となる。その結果、PMOS1及びNMOS2のゲート電圧VG1が「LOW」になるタイミングのほうが、NMOS4のゲート電圧VG4が「LOW」になるタイミングよりも早くなる。この場合、PMOS1がオンに切り替ってから、NMOS4がオフに切り替るまでに時間差が生じることから、僅かな時間ではあるがPMOS1及びNMOS4がいずれもオンとなる。その結果、その時間にPMOS1及びNMOS4を介して消費電流となる貫通電流が流れてしまう。

【0026】

それに対して本実施の形態では、NMOS4が、時点t1での第2出力信号(ゲート電圧VG4)の変化に応じてオンからオフに切り替えられるタイミングと、PMOS1が、同時点t1での遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングとが、時点t2において互いに一致するように、遅延信号の遅延時間が設定されている。つまり、図2の左側の矢印に示されるように、ゲート電圧VG1がLOWに切り替るタイミングが、ゲート電圧VG4がLOWに切り替るタイミング(時点t2)に遅延するように構成されている。したがって、PMOS1及びNMOS4を介して、消費電流となる貫通電流が流れるのを抑制することができる。

【0027】

時点t2後、PMOS1はオン、NMOS2,4はオフとなっていることから、絶縁ゲート型半導体素子31のゲート電圧VGは上昇していく。

【0028】

そして、時点t3において、ゲート電圧VGが、絶縁ゲート型半導体素子31の閾値電圧Vth(つまり、基準電圧Vref)以上になると、コンパレータ回路16は電圧V16をLOWから「HIGH」にする。したがって、NAND回路17及びNOR回路18には、反転信号の「HIGH」と、電圧V16の「HIGH」とが入力される。そうすると、NOR回路18が、時点t3においてもゲート電圧VG4を「LOW」に維持することから、NMOS4はオフに維持される。一方、NAND回路17が、時点t3においてはゲート電圧V3をHIGHから「LOW」に切り替えることから、PMOS3はオフからオンに切り替えられる。

【0029】

このように、本実施の形態では、PMOS3が、第1出力信号(ゲート電圧VG3)の変化に応じてオフからオンに切り替えられるタイミングは、PMOS1が、遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングよりも遅い。これにより、絶縁ゲート型半導体素子31のゲート電圧VGが閾値電圧Vth以上になるまでは、弱いソース能力でゲート電圧VGをチャージ(充電)し、当該ゲート電圧VGが閾値電圧Vth以上になると、強いソース能力でゲート電圧VGをチャージすることになる。

【0030】

その結果、図2に示されるように、PMOS3をオンしたときのゲート電圧VGが立ち上がる(実線)までのミラー期間(t3〜t4)は、PMOS3をオンしないときのゲート電圧VGが立ち上がる(二点鎖線)までのミラー期間(t3〜t5)よりも短縮することができる。したがって、絶縁ゲート型半導体素子31のソースドレイン電圧Vdsが完全に立ち下がるまでの時間(実線)は、PMOS3がオンしないときのその時間(二点鎖線)よりも短縮することができることから、スイッチング損失Eswを小さくすることができる。

【0031】

次に、時点t6において、制御信号VinがLOWから「HIGH」に切り替えられる。この時点t6では、時点t1と同様の遅延が生じることから、PMOS1,3及びNMOS2,4のスイッチは切り替らない。

【0032】

時点t6後、NAND回路17及びNOR回路18には、制御信号Vin(HIGH)の反転信号の「LOW」と、電圧V16の「HIGH」とが入力される。そうすると、NOR回路18は、次の時点t7においてもゲート電圧VG4を「LOW」に維持するが、NAND回路17は、次の時点t7においてはゲート電圧VG3をLOWから「HIGH」に切り替えることになる。

【0033】

その後、時点t7において、制御信号Vinの遅延信号の「HIGH」がPMOS1及びNMOS2のゲート端子に入力される。つまり、ゲート電圧VG1がLOWから「HIGH」に切り替えられる。したがって、PMOS1はオンからオフ、NMOS2はオフからオンにそれぞれ切り替る。また、時点t7において、上述したようにゲート電圧VG4は「LOW」に維持されるから、NMOS4はオフに維持される。一方、上述したようにゲート電圧VG3はNAND回路17により「HIGH」に切り替えられるから、PMOS3はオンからオフに切り替えられる。

【0034】

ここで、仮に、遅延回路19が設けられていなければ、制御信号Vinが、遅延されずにPMOS1及びNMOS2のゲート端子に入力されることから、制御信号Vinが「HIGH」になるのとほぼ同時にPMOS1及びNMOS2のゲート電圧VG1が「HIGH」となる。その結果、PMOS1及びNMOS2のゲート電圧VG1が「HIGH」になるタイミングのほうが、PMOS3のゲート電圧が「HIGH」になるタイミングよりも早くなる。この場合、NMOS2がオンに切り替ってから、PMOS3がオフに切り替るまでに時間差が生じることから、僅かな時間ではあるがPMOS3及びNMOS2がいずれもオンとなる。その結果、その時間にPMOS3及びNMOS2を介して消費電流となる貫通電流が流れてしまう。

【0035】

それに対して本実施の形態では、PMOS3が、時点t6での第1出力信号(ゲート電圧VG3)の変化に応じてオンからオフに切り替えられるタイミングと、NMOS2が、同時点t6での遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングとが、時点t7において互いに一致するように、遅延信号の遅延時間が設定されている。つまり、図2の右側の矢印に示されるように、ゲートVG1がHIGHに切り替るタイミングが、ゲート電圧VG3がHIGHに切り替るタイミング(時点t7)に遅延するように構成されている。したがって、PMOS3及びNMOS2を介して、消費電流となる貫通電流が流れるのを抑制することができる。

【0036】

時点t7後、PMOS1,3はオフ、NMOS2はオンとなっていることから、絶縁ゲート型半導体素子31のゲート電圧VGは下降していく。

【0037】

そして、時点t8において、ゲート電圧VGが、絶縁ゲート型半導体素子31の閾値電圧Vth(Vref)より低くなると、コンパレータ回路16は電圧V16をHIGHから「LOW」にする。したがって、NAND回路17及びNOR回路18には、反転信号の「LOW」と、電圧V16の「LOW」とが入力される。そうすると、NAND回路17が、時点t8においてもゲート電圧VG3を「HIGH」に維持することから、PMOS3はオフに維持される。一方、NOR回路18が、時点t8においてはゲート電圧VG4をLOWから「HIGH」に切り替えることから、NMOS4はオフからオンに切り替えられる。

【0038】

このように、本実施の形態では、NMOS4が、第2出力信号(ゲート電圧VG4)の変化に応じてオフからオンに切り替えられるタイミングは、NMOS2が、遅延信号(ゲート電圧VG1)の変化に応じてオフからオンに切り替えられるタイミングよりも遅い。これにより、絶縁ゲート型半導体素子31のゲート電圧VGが閾値電圧Vthより低くなるまでは、弱いシンク能力でゲート電圧VGをディスチャージ(放電)し、当該ゲート電圧VGが閾値電圧Vthより低くなると、強いシンク能力でゲート電圧VGをディスチャージすることになる。

【0039】

その結果、上述と同様に、NMOS4をオンしたときのゲート電圧VGが立ち下がるまでのミラー期間を、NMOS4をオンしないときのミラー期間よりも短縮することができる。したがって、スイッチング損失Eswを小さくすることができる。

【0040】

以上のような動作を行う本実施の形態に係る半導体集積回路によれば、NMOS4がオンからオフするタイミングと、PMOS1がオフからオンするタイミングとが互いに一致し、また、PMOS3がオンからオフするタイミングと、NMOS2がオフからオンするタイミングとが互いに一致している。したがって、消費電流となる貫通電流を抑制することができる。

【0041】

なお、貫通電流を抑制することだけを望むのであれば、以上の構成に限ったものではない。具体的には、NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなくすればよい。このようにした場合であっても、貫通電流を抑制することができる。ただし、以上の一連の処理を高速化したいのであれば、上述したように、各タイミングを一致させることが望ましい。

【0042】

また、本実施の形態に係る半導体集積回路によれば、PMOS3がオフからオンに切り替えられるタイミングは、PMOS1がオフからオンに切り替えられるタイミングよりも遅く、NMOS4がオフからオンに切り替えられるタイミングは、NMOS2がオフからオンに切り替えられるタイミングよりも遅い。したがって、ミラー期間を短縮することができ、スイッチング損失Eswを小さくすることができる。また、スイッチングの高周波数化の実現も期待できる。なお、第2駆動回路12(PMOS3及びNMOS4)の駆動能力を大きくすれば、ミラー期間を短縮する効果を高めることができる。

【0043】

また、本実施の形態では、遅延回路19として、直列に接続された二つのインバータ19a,19bを用いたが、図2に示すような遅延時間を遅延設定することができるものであれば、他の構成を採用してもよい。

【0044】

また、本実施の形態では、コンパレータ回路16の基準電圧Vrefを、絶縁ゲート型半導体素子31の閾値電圧Vthと同じ電圧とした。しかし、現実には製造バラツキが存在することから、閾値電圧Vth(ミラー電圧)はばらつくものとなっている。そこで、基準電圧Vrefとしては、閾値電圧Vth(ミラー電圧)が取り得ると予想される値のうち最小値に設定することが好ましい。

【0045】

また、本実施の形態では、第1演算回路をNAND回路17として説明したが、それと同様の演算を行うものであれば、他の演算回路を組み合わせたものであってもよい。同様に、本実施の形態では、第2演算回路をNOR回路18として説明したが、それと同様の演算を行うものであれば、他の演算回路を組み合わせたものであってもよい。

【0046】

<実施の形態2>

一般に、SiCのMOSFETの閾値電圧は、例えば2Vというように低くなっている。そのため、SiCのMOSFETを絶縁ゲート型半導体素子31に適用した場合において、絶縁ゲート型半導体素子31のゲート端子に入力されるLOW信号の電圧が、製造ばらつきなどにより閾値電圧以上となった場合には、実施の形態1で説明した所望の動作を行うことができない可能性がある。そこで、本発明の実施の形態2では、閾値電圧が低い半導体素子(例えばSiCのMOSFET)が、絶縁ゲート型半導体素子31に適用された場合であっても、所望の動作を確実に行うことが可能となっている。

【0047】

図3は、本実施の形態に係る半導体集積回路の構成を示す回路図である。以下、本実施の形態に係る半導体集積回路において、実施の形態1で説明した構成要素と類似するものについては同じ符号を付し、実施の形態1と異なる点を中心に説明する。

【0048】

図3に示されるように、本実施の形態では、実施の形態1の構成に内部電源回路41を加えたものとなっている。この内部電源回路41は、絶縁ゲート型半導体素子31のソース端子に端子26を介して接続され、当該ソース端子に負バイアスVEを印加する。この場合、絶縁ゲート型半導体素子31のソース端子にVxという電圧が印加されていたとしても、MOSFETの性質から、当該ソース端子に(Vx−VE)という電圧が印加されていることと等価となる。

【0049】

したがって、例えば、絶縁ゲート型半導体素子31の閾値電圧Vthが2V、負バイアスVEが7Vである場合、絶縁ゲート型半導体素子31の閾値電圧は実質的に9Vとなる。この場合において、絶縁ゲート型半導体素子31のゲート端子にLOW信号を入力した場合に、その電圧が元の閾値電圧の2Vより多少高い電圧(例えば3V)であっても、そのLOW信号を通常のLOW信号として扱うことができる。

【0050】

このように、本実施の形態によれば、閾値電圧が低い半導体素子が、絶縁ゲート型半導体素子31に適用された場合であっても、所望の動作を確実に行うことができる。

【0051】

なお、本実施の形態においても、実施の形態1と同様に第2駆動回路12を設けていることから、強いシンク能力でゲート電圧VGをディスチャージすることが可能である。したがって、この作用によりLOW信号の電圧を低くすることができることから、内部電源回路41の負バイアスVEを比較的低く設定することができる。よって、その分だけ寿命を延ばすことができ、半導体集積回路の信頼性を高めるという効果も期待できる。

【符号の説明】

【0052】

1,3 PMOS、2,4 NMOS、11 第1駆動回路、12 第2駆動回路、16 コンパレータ回路、17 NAND回路、18 NOR回路、19 遅延回路、31 絶縁ゲート型半導体素子、41 内部電源回路。

【特許請求の範囲】

【請求項1】

制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路であって、

各々が、高電位・低電位電源間にトーテムポール接続されたソース側及びシンク側のスイッチング素子の対からなる第1及び第2駆動回路を備え、

前記第1及び第2駆動回路のそれぞれにおける前記ソース側及びシンク側のスイッチング素子同士の間の接続点は、前記絶縁ゲート型半導体素子のゲート端子と接続され、

前記絶縁ゲート型半導体素子のゲート端子の電圧と、基準電圧とを比較するコンパレータ回路と、

前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第1出力信号を、前記第2駆動回路の前記ソース側のスイッチング素子のゲート端子に出力する第1演算回路と、

前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第2出力信号を、前記第2駆動回路の前記シンク側のスイッチング素子のゲート端子に出力する第2演算回路と、

前記制御信号を遅延させて得られる遅延信号を、前記第1駆動回路の前記ソース側及びシンク側のスイッチング素子のゲート端子に出力する遅延回路と

をさらに備え、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くない、半導体集積回路。

【請求項2】

請求項1に記載の半導体集積回路であって、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングと、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングとは互いに一致し、かつ、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングと、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングとは互いに一致する、半導体集積回路。

【請求項3】

請求項1または請求項2に記載の半導体集積回路であって、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオフからオンに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅く、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオフからオンに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅い、半導体集積回路。

【請求項4】

請求項1乃至請求項3のいずれかに記載の半導体集積回路であって、

前記絶縁ゲート型半導体素子のソース端子に接続され、当該ソース端子に負バイアスを印加する内部電源回路をさらに備える、半導体集積回路。

【請求項5】

請求項1乃至請求項4のいずれかに記載の半導体集積回路であって、

前記遅延回路は、互いに接続された二つのインバータである、半導体集積回路。

【請求項1】

制御信号に基づいて絶縁ゲート型半導体素子を駆動する半導体集積回路であって、

各々が、高電位・低電位電源間にトーテムポール接続されたソース側及びシンク側のスイッチング素子の対からなる第1及び第2駆動回路を備え、

前記第1及び第2駆動回路のそれぞれにおける前記ソース側及びシンク側のスイッチング素子同士の間の接続点は、前記絶縁ゲート型半導体素子のゲート端子と接続され、

前記絶縁ゲート型半導体素子のゲート端子の電圧と、基準電圧とを比較するコンパレータ回路と、

前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第1出力信号を、前記第2駆動回路の前記ソース側のスイッチング素子のゲート端子に出力する第1演算回路と、

前記制御信号と、前記コンパレータ回路での比較結果とに基づいて演算を行い、当該演算結果を示す第2出力信号を、前記第2駆動回路の前記シンク側のスイッチング素子のゲート端子に出力する第2演算回路と、

前記制御信号を遅延させて得られる遅延信号を、前記第1駆動回路の前記ソース側及びシンク側のスイッチング素子のゲート端子に出力する遅延回路と

をさらに備え、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くなく、かつ、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅くない、半導体集積回路。

【請求項2】

請求項1に記載の半導体集積回路であって、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオンからオフに切り替えられるタイミングと、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングとは互いに一致し、かつ、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオンからオフに切り替えられるタイミングと、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングとは互いに一致する、半導体集積回路。

【請求項3】

請求項1または請求項2に記載の半導体集積回路であって、

前記第2駆動回路の前記ソース側のスイッチング素子が、前記第1出力信号の変化に応じてオフからオンに切り替えられるタイミングは、前記第1駆動回路の前記ソース側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅く、

前記第2駆動回路の前記シンク側のスイッチング素子が、前記第2出力信号の変化に応じてオフからオンに切り替えられるタイミングは、前記第1駆動回路の前記シンク側のスイッチング素子が、前記遅延信号の変化に応じてオフからオンに切り替えられるタイミングよりも遅い、半導体集積回路。

【請求項4】

請求項1乃至請求項3のいずれかに記載の半導体集積回路であって、

前記絶縁ゲート型半導体素子のソース端子に接続され、当該ソース端子に負バイアスを印加する内部電源回路をさらに備える、半導体集積回路。

【請求項5】

請求項1乃至請求項4のいずれかに記載の半導体集積回路であって、

前記遅延回路は、互いに接続された二つのインバータである、半導体集積回路。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−244215(P2012−244215A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−109170(P2011−109170)

【出願日】平成23年5月16日(2011.5.16)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月16日(2011.5.16)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]