半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路に関する。

【背景技術】

【0002】

負荷となる論理回路に一定の電源電圧を供給するレギュレータを有する電子装置において,消費電力を抑制する方法が様々提案されている(特許文献1参照)。

【0003】

図1は,レギュレータを有する半導体集積回路の一例ブロック図である。半導体集積回路10のレギュレータA11は,電源配線PL1を介して論理回路A12に電源電圧を供給する。レギュレータB13は,電源配線PL2を介して論理回路B14に電源電圧を供給する。

【0004】

論理回路A12は,必要に応じて動作状態または停止状態になる論理回路である。論理回路B14は,常に動作状態にある論理回路である。

【0005】

レギュレータA11は,例えば論理回路B14の制御に基づき,論理回路A12に電源電圧を供給して論理回路A12を動作状態にする。また,レギュレータA11は,論理回路B14の制御に基づき,論理回路A12に対する電源電圧の供給を停止して論理回路A12を停止状態にする。この電源電圧の供給の停止により,半導体集積回路10の消費電力を削減する。

【0006】

レギュレータB13は,半導体集積回路10の起動時から常に動作状態になり,論理回路B14に対し電源電圧を常時供給する。

【0007】

レギュレータは,負荷となる論理回路による消費電流の変動を打ち消すように動作する。例えば,負荷となる論理回路の消費電流が増大することにより,レギュレータの出力電圧が降下する。

【0008】

すると,レギュレータは,出力電圧を一定に維持するため,この電圧降下に応答し出力電圧を上昇させる。

【0009】

このように,レギュレータは,負荷となる論理回路による消費電流の変動に追随し,その出力電圧を変動することにより,この変動を打ち消す。ところが,レギュレータは,ある周波数,例えば数百kHz以上の前記消費電流の変動に対しては追随することができない。

【0010】

そこで,レギュレータの出力端に平滑用の外部容量(パスコンとも言う)を接続し,この外部容量に電荷を蓄積させる。負荷となる論理回路により消費電流が変動すると,この外部容量に蓄積された電荷が論理回路に供給され,または,電荷がこの外部容量に再度蓄積されることにより,論理回路に一定の電圧が供給される。

【0011】

半導体集積回路10においては,レギュレータA11の出力端は,レギュレータA11用の外部容量C1と外部接続端子CT1,外部端子接続配線CL1を介して接続している。以下,外部容量に接続する外部接続端子をC端子と記す。

【0012】

同じく,レギュレータB13の出力端は,レギュレータB13用の外部容量C2とC端子CT2,外部端子接続配線CL2を介して接続している。すなわち,半導体集積回路10においては,レギュレータA11,レギュレータB13がそれぞれの外部容量C1,C2と接続するために,2つの外部接続端子CT1,CT2が必要になる。なお,抵抗RTは終端抵抗である。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2001-211640号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

ところで,半導体集積回路の面積を削減するため,外部接続端子数を削減する必要がある。特に,多数の論理回路と,これら多数の論理回路に電力を供給する多数のレギュレータとを1チップ上に搭載する場合には,これら多数のレギュレータに対応してそれぞれ,多数のC端子を設けなければならない。このように,C端子を設けると,半導体集積回路の面積が大きくなってしまう。また,外部接続端子の総数に対するC端子の総数が増えてしまい,他の機能を実現するために必要な外部接続端子の数が不足する。

【0015】

したがって,本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減することにある。

【課題を解決するための手段】

【0016】

半導体集積回路の第1の側面は,動作状態または停止状態になる第1の論理回路と,常に動作状態にある第2の論理回路と,第1の出力端から第1の電源電圧を前記第1の論理回路に供給して前記第1の論理回路を動作状態にし,前記第1の電源電圧の供給を停止し前記第1の論理回路を停止状態にする第1のレギュレータと,第2の出力端から第2の電源電圧を前記第2の論理回路に常に供給する第2のレギュレータとを有する半導体集積回路において,

前記第1,第2の出力端と,外部容量に接続する外部接続端子との間に設けられたスイッチ回路を有し,

前記スイッチ回路の一端は前記第1の出力端に接続され,当該スイッチ回路の他端は前記外部接続端子および前記第2の出力端に接続され,

前記スイッチ回路は,前記第1のレギュレータが前記第1の電源電圧を第1の論理回路に対して供給する期間はオンし,前記第1のレギュレータが前記第1の論理回路に対する電源電圧供給を停止する期間はオフする。

【発明の効果】

【0017】

第1の側面によれば,複数の論理回路に電源電圧をそれぞれ供給する複数のレギュレータを有する半導体集積回路において,これら複数のレギュレータがC端子を共用するので,C端子の数を削減できる。その結果,回路面積を削減できる。

【図面の簡単な説明】

【0018】

【図1】図1は,レギュレータを有する半導体集積回路の一例ブロック図である。

【図2】図2は,C端子の数を削減した半導体集積回路を説明する図である。

【図3】図3は,本実施の形態における半導体集積回路の一例ブロック図である。

【図4】図4は,半導体集積回路の詳細ブロック図である。

【図5】図5は,半導体集積回路の動作を説明するタイミングチャートである。

【図6】図6は,スイッチ回路の一例を説明する図である。

【図7】図7は,半導体集積回路の効果を説明する図である。

【発明を実施するための形態】

【0019】

C端子の数を削減する1つの手段を図2を用いて説明する。

【0020】

図2は,C端子の数を削減した半導体集積回路を説明する図である。

【0021】

図2(A)は,C端子の数を削減した半導体集積回路の一例ブロック図であり,図2(B)は,図2(A)の一部拡大図である。

【0022】

図2において,半導体集積回路20は,1つのレギュレータC21のみを有し,電源配線PL3を介して論理回路A22,論理回路B23に電源電圧を供給する。論理回路A22は図1の論理回路A12と同機能である。また,レギュレータC21の出力端は,レギュレータC21用の外部容量C3とC端子CT3,外部端子接続配線CL3を介して接続している。また,レギュレータC21から論理回路A22に対する電源電圧の供給をスイッチングする多数のスイッチユニットSaが論理回路A22の周囲に設けられている。

【0023】

論理回路B23は,図1の論理回路B14が有する機能に加えて,論理回路A22の周囲に設けられているスイッチユニットSaをオンにして,レギュレータC21から論理回路A22に対する電源電圧の供給を行い,論理回路A22を動作状態にする機能を有する。

【0024】

また,論理回路B23は,スイッチユニットSaをオフにして,レギュレータC21から論理回路A22に対する電源電圧供給を停止し,論理回路A22を停止状態にする機能を有する。

【0025】

ここで,論理回路A22の周囲にスイッチユニットSaを設ける理由を図2(B)を用いて説明する。通常,論理回路は,格子状(メッシュ状)に設けられた電源供給線を有する。

【0026】

図2(B)において,符号PMで示す電源供給線が,この格子状に設けられた電源供給線の一部分である。この格子状に設けられた電源供給線PMの一端には,レギュレータC21からの電源配線PL3が接続される。そして,この電源配線PL3から電源供給線PMに電源電圧が供給され,この電源供給線PMから論理回路A22を構成する論理素子などに電源電圧が供給される。

【0027】

論理回路の周囲に電源配線を配置する構成は論理回路B23についても同様である。

【0028】

このような配線構造において,レギュレータC21から論理回路A22に対する電源電圧供給のスイッチングを行うスイッチユニットSaを設ける場合,図2(B)に示したように,電源配線PL3と電源供給線PMとの間にスイッチユニットSaを設ける。ここで,スイッチユニットSaは,Nチャネル型のトランジスタTr1を有し,トランジスタTr1のドレインが電源配線PL3に接続され,ソースが電源供給線PMに接続され,ゲートには,論理回路B23からスイッチユニットSaをオンオフする制御信号が入力される。

【0029】

このように,電源供給線PMと電源配線PL3との間にスイッチユニットSaを設ける,換言すれば,スイッチユニットSaを論理回路A22の周囲に設けることで,以下の効果が生じる。すなわち,スイッチユニットSaがオンすると論理回路A22に電源電圧が即時供給され,スイッチユニットSaがオフするとこの電源電圧供給が即時停止する。この即応性を確保することが,スイッチユニットSaを論理回路A22の周囲に設ける理由である。

【0030】

しかし,スイッチユニットSaを論理回路A22の周囲に設ける場合,多数のスイッチユニットSa,例えば1920個ものスイッチユニットSaを設ける必要がある。そのため,回路面積が増大する。また,多数のスイッチユニットSaからのリーク電流により無駄な消費電力が増大する。

【0031】

[本実施の形態の半導体集積回路]

そこで,以下,回路面積,消費電力を抑制できる半導体集積回路について図3〜図5に基づいて説明する。

【0032】

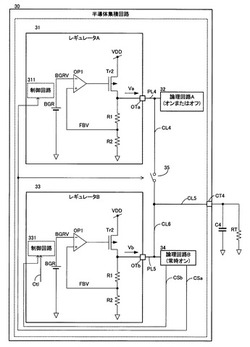

図3は,本実施の形態における半導体集積回路30の一例ブロック図である。

【0033】

図4は,半導体集積回路30の詳細ブロック図である。

【0034】

[論理回路]

半導体集積回路30の論理回路A32(第1の論理回路)は,必要に応じて動作状態または停止状態になる論理回路であり,例えば,記憶処理,演算処理,通信処理などの各種処理を行う回路である。

【0035】

論理回路B34(第2の論理回路)は,常に動作状態にある論理回路であり,レギュレータA31,レギュレータB33の制御処理,通信処理などの各種処理を行う回路である。

【0036】

[レギュレータ]

レギュレータA31(第1のレギュレータ)は,第1の出力端OTaから第1の電源電圧Vaを論理回路A32に供給して論理回路A32を動作状態にし,電源電圧Vaの供給を停止し論理回路A32を停止状態にする。すなわち,レギュレータA31は,電源配線PL4を介して電源電圧Va(第1の電源電圧)を論理回路A32に供給する。

【0037】

レギュレータB33(第2のレギュレータ)は,第2の出力端OTbから第2の電源電圧Vbを論理回路B34に常に供給する。すなわち,レギュレータB33は,半導体集積回路30の起動時から動作状態になり,電源配線PL5を介して電源電圧Vbを論理回路B34に供給する。

【0038】

[スイッチ回路]

スイッチ回路35は,レギュレータA31の出力端OTa(図4参照)およびレギュレータB33の出力端OTb(図4参照)と,外部容量C4に接続する外部接続端子CT4との間に設けられている。

【0039】

スイッチ回路35の一端は外部端子接続配線CL4を介してレギュレータA31の出力端OTaに接続されている。また,スイッチ回路35の他端は,外部端子接続配線CL5を介してC端子CT4に接続され,この他端は,外部端子接続配線CL6を介してレギュレータB33の出力端OTbに接続されている。

【0040】

すなわち,スイッチ回路35の一端はレギュレータA31の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4およびレギュレータB33の出力端OTbに接続されている。

【0041】

スイッチ回路35は,レギュレータA31が電源電圧Vaを論理回路A32に対して供給する期間はオンし,レギュレータA31が論理回路A32に対する電源電圧Vaの供給を停止する期間はオフする。

【0042】

このようなスイッチングを行うスイッチ回路35を設ける理由を説明する。図3,図4では,2つのレギュレータの出力端とC端子CT4とを接続,すなわち,レギュレータA31,レギュレータB33が1つのC端子CT4を共有することにより,図1に示した半導体集積回路に比べて外部容量に接続する外部接続端子の数を削減している。

【0043】

ここで,レギュレータA31,レギュレータB33が1つのC端子CT4を共有し,スイッチ回路35が無い状態を想定する。図3の例では,スイッチ回路35が無く,外部端子接続配線CL4,CL5,CL6が接続している状態である。このとき,レギュレータA31の出力端OTaとレギュレータB33の出力端OTbとがC端子CT4に共通接続される。

【0044】

この状態で,レギュレータA31,論理回路A32が停止し,レギュレータB33が動作していると,レギュレータB33の電源電圧Vbが停止中の論理回路A32に供給されてしまう。すなわち,スイッチ回路35がない場合,レギュレータB33からの電源電圧Vbが外部端子接続配線CL6,外部端子接続配線CL4を介して論理回路A32に供給されてしまい,無駄な消費電力が増大する。

【0045】

そこで,レギュレータA31が電源電圧Vaを論理回路A32に対して供給する期間はオンし,レギュレータA31が論理回路A32に対する電源電圧Vaの供給を停止する期間はオフするスイッチ回路35を設けている。

【0046】

レギュレータA31が停止状態に移行すると,スイッチ回路35がオフすることにより,レギュレータA31の出力端OTaとレギュレータB33の出力端OTbとの接続経路が遮断される。その結果,レギュレータB33からの電源電圧Vbが論理回路A32に供給されなくなり,無駄な消費電流が発生しなくなる。一方,レギュレータA31が動作状態の場合には,スイッチ回路35がオンすることにより,レギュレータAの出力端OTaと外部容量C4とが接続される。その結果,外部容量C4がレギュレータA31,レギュレータB33のパスコンとして機能する。

【0047】

[レギュレータの詳細]

レギュレータA31の詳細について図4を用いて説明する。なお,このレギュレータの構成は一例であり,様々な構成のレギュレータを採用することができる。

【0048】

レギュレータA31の増幅器OP1は,反転入力端子(−端子)に供給された基準電圧BGRVと,非反転入力端子(+端子)に供給されたフィードバック電圧FBVとの差分を増幅し,出力電圧をPチャネル型のトランジスタTr2のゲートに供給する。トランジスタTr2のソースは電源VDDに接続され,ドレインは分圧抵抗R1の一端に接続され,ゲートに供給された電圧により,この電圧に対応する電流をドレインから出力する。この出力電流の電圧が電源電圧Vaである。

【0049】

基準電圧源BGRは,基準電圧BGRVを増幅器OP1の反転入力端子に供給する。また,フィードバック電圧FBVは,直列に接続された分圧抵抗R1,R2により分圧された電源電圧Vaの分圧電圧である。

【0050】

なお,例えば,電源VDDの電圧は5V,基準電圧BGRVは1.2V,R1の抵抗値は0.6MΩ,R2の抵抗値は1.2MΩ,電源電圧Vaは1.8V,フィードバック電圧FBVは1.2Vである。

【0051】

レギュレータA31の動作を簡単に説明する。例えば,論理回路A32の負荷が増大(論理回路A32の負荷電流が増大)すると,電源電圧Vaが低下し,フィードバック電圧FBVも低下する。フィードバック電圧FBVが基準電圧BGRV以下に低下すると,増幅器OP1は,出力電圧を下げる。すると,トランジスタTr2のゲート電圧が低下し,トランジスタTr2のソース-ドレイン電流が増加する。その結果,電源電圧Vaが上昇する。この電源電圧Vaの電圧上昇は,電源電圧Vaのフィードバック電圧FBVが基準電圧BGRVと同電圧になると停止する。電源電圧Vaが上昇した場合も,前記したレギュレータA31の動作と逆の動作により,電源電圧Vaが下降する。

【0052】

制御回路311は,レギュレータA31の内部制御を行う回路であり,レギュレータA31を動作させる旨を指示する制御信号CSaが論理回路B34から入力されると,電源電圧Vaの出力を開始する。また,制御回路311は,レギュレータA31を停止させる旨を指示する制御信号CSaが論理回路B34から入力されると,電源電圧Vaの出力を停止する。

【0053】

レギュレータB33もレギュレータA31と同様の回路構成を有する。なお,制御回路331は,レギュレータB33の内部制御を行う回路である。

【0054】

[半導体集積回路の動作]

半導体集積回路30の動作を図5のタイミングチャートを用いて説明する。

【0055】

図5のタイミングチャートは,上からレギュレータA31の動作モード,スイッチ回路35のオン,オフ状態,レギュレータA31の動作,停止状態,レギュレータA31の出力電圧波形,レギュレータB33の動作,停止状態,レギュレータB33の出力電圧波形を示している。

【0056】

時刻T0〜T1:この期間では,レギュレータA32,レギュレータB33が共に動作状態になる。

【0057】

半導体集積回路30が時刻T0において起動すると,図示しない制御回路からの制御信号CtlがレギュレータB33の制御回路331(図4参照)に入力される。制御回路331は,制御信号Ctlの入力に応答して,増幅器OP1などを動作させ,電源電圧Vbを論理回路B34に供給する(レギュレータB,動作状態)。

【0058】

論理回路B34は,電源電圧Vbの供給により起動する。以後,論理回路B34は,レギュレータB33の制御を制御信号Csbにより行う。

【0059】

すると,論理回路B34は,レギュレータA31の制御回路311に対して論理回路A32に対する電源電圧Vaの供給を指示する制御信号CSaを出力する。この制御信号CSaは,例えばハイレベルである。レギュレータA31は,この制御信号CSaに応答して,電源電圧Vaを論理回路A32に供給する。

【0060】

論理回路A32は,電源電圧Vaの供給により起動する。

【0061】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オン状態になる。

【0062】

すなわち,論理回路B34は,レギュレータA31に対して論理回路A32に対する電源電圧Vaの供給を指示すると共にスイッチ回路35をオンする。

【0063】

その結果,レギュレータA31の出力端OTaおよびレギュレータB33の出力端OTbがC端子CT4を介して外部容量C4に接続する。すなわち,外部容量C4がレギュレータA31,レギュレータB33のパスコンとして機能する。

【0064】

時刻T0〜T1における半導体集積回路30の消費電流は,主にレギュレータA31,論理回路A32,レギュレータB33,論理回路B34,スイッチ回路35の消費電流である。

【0065】

時刻T1〜T2:この期間では,レギュレータA31が停止状態になる。

【0066】

論理回路B34は,レギュレータA31の制御回路311に対して論理回路A32に対する電源電圧Vaの供給停止を指示する制御信号CSaを出力する。この制御信号CSaは,例えばローレベルである。レギュレータA31は,この制御信号CSaに応答して,論理回路A32に対する電源電圧Vaの供給を停止する。

【0067】

論理回路A32は,電源電圧Vaの供給停止により停止する。

【0068】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オフ状態になる。

【0069】

すなわち,論理回路B34は,レギュレータA31に対して論理回路A32に対する電源電圧Vaの供給停止を指示すると共にスイッチ回路35をオフする。

【0070】

このように,レギュレータA31が停止状態に移行すると,スイッチ回路35がオフすることにより,レギュレータA31とレギュレータB33との接続経路が遮断される。その結果,レギュレータB33から電源電圧Vbが論理回路A32に供給されなくなり,無駄な消費電流が発生しなくなる。このとき,レギュレータB33の出力端OTbは,C端子CT4を介して外部容量C4に接続しており,外部容量C4は,レギュレータB33のパスコンとして機能している。

【0071】

時刻T1〜T2における半導体集積回路30の消費電流は,主にレギュレータB33,論理回路B34,スイッチ回路35の消費電流である。

【0072】

時刻T2〜T3: この期間では,レギュレータA31が動作状態になる。時刻T0〜T1で説明したように,論理回路B34は,論理回路A32に対する電源電圧Vaの供給再開を指示する制御信号CSaをレギュレータA31の制御回路311に出力する。レギュレータA31は,この制御信号CSaに応答して,電源電圧Vaを論理回路A32に供給する。

【0073】

論理回路A32は,電源電圧Vaの供給により起動する。

【0074】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オン状態になる。

【0075】

以降,レギュレータA31の停止,動作,スイッチ回路35のオフ,オンを繰り返す。

【0076】

[スイッチ回路]

さて,スイッチ回路35として様々な構成のスイッチを利用することができる。

【0077】

図6は,スイッチ回路35の一例を説明する図である。スイッチ回路35は,例えば,Nチャネル型のトランジスタTr3を63個有する。各トランジスタTr3のゲートGには制御信号CSaが入力される。トランジスタTr3のB端子はレギュレータA31の出力端OTaに並列接続され,トランジスタTr3のC端子は,外部接続端子CT4およびレギュレータB33の出力端OTbに並列接続される。なお,トランジスタTr3のB端子はドレインまたはソースであり,C端子はソースまたはドレインである。

【0078】

このように,各トランジスタTr3を並列接続するのは,スイッチ回路35の抵抗値を外部端子接続配線CL4の配線抵抗値以下にするためである。例えば,外部端子接続配線CL4の配線抵抗値が0.5106Ω,1個のトランジスタTr3のオン抵抗が63Ωの場合,トランジスタTr3を63個並列接続すれば((32Ω/0.5106Ω)),スイッチ回路35の抵抗値を外部端子接続配線CL4の配線抵抗値以下にすることができる。

【0079】

[効果]

本実施の形態の半導体集積回路30によれば,C端子の数を削減し,回路面積を削減できる。そして,スイッチ回路35のスイッチングにより,無駄な消費電力を削減できる。また,スイッチ回路35の回路面積が小さいので,さらなる回路面積の削減が可能になる。

【0080】

図7は,本実施の形態の半導体集積回路30の効果を説明する図である。図7において,図2の半導体集積回路20のスイッチユニットSaの総面積およびリーク電流を示し,さらに,本実施の形態の半導体集積回路30のスイッチ回路35および追加したレギュレータの総面積およびリーク電流を示している。

【0081】

図7に示したように,本実施の形態の半導体集積回路30では,図2の半導体集積回路20に比べて,回路面積では23%縮小し,リーク電流では76%削減されている。

【符号の説明】

【0082】

10,20,30…半導体集積回路,11,31…レギュレータA,12,22,32…論理回路A,13…レギュレータB,14,23,34…論理回路B,C1〜C4…外部容量,CT1〜CT4…外部接続端子,PL1〜PL…電源配線,CL1〜CL6…外部端子接続配線,PM…電源供給線,R1,R2…分圧抵抗,Tr1〜Tr3…トランジスタ,21…レギュレータC,311,331…制御回路,35…スイッチ回路。

【技術分野】

【0001】

本発明は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路に関する。

【背景技術】

【0002】

負荷となる論理回路に一定の電源電圧を供給するレギュレータを有する電子装置において,消費電力を抑制する方法が様々提案されている(特許文献1参照)。

【0003】

図1は,レギュレータを有する半導体集積回路の一例ブロック図である。半導体集積回路10のレギュレータA11は,電源配線PL1を介して論理回路A12に電源電圧を供給する。レギュレータB13は,電源配線PL2を介して論理回路B14に電源電圧を供給する。

【0004】

論理回路A12は,必要に応じて動作状態または停止状態になる論理回路である。論理回路B14は,常に動作状態にある論理回路である。

【0005】

レギュレータA11は,例えば論理回路B14の制御に基づき,論理回路A12に電源電圧を供給して論理回路A12を動作状態にする。また,レギュレータA11は,論理回路B14の制御に基づき,論理回路A12に対する電源電圧の供給を停止して論理回路A12を停止状態にする。この電源電圧の供給の停止により,半導体集積回路10の消費電力を削減する。

【0006】

レギュレータB13は,半導体集積回路10の起動時から常に動作状態になり,論理回路B14に対し電源電圧を常時供給する。

【0007】

レギュレータは,負荷となる論理回路による消費電流の変動を打ち消すように動作する。例えば,負荷となる論理回路の消費電流が増大することにより,レギュレータの出力電圧が降下する。

【0008】

すると,レギュレータは,出力電圧を一定に維持するため,この電圧降下に応答し出力電圧を上昇させる。

【0009】

このように,レギュレータは,負荷となる論理回路による消費電流の変動に追随し,その出力電圧を変動することにより,この変動を打ち消す。ところが,レギュレータは,ある周波数,例えば数百kHz以上の前記消費電流の変動に対しては追随することができない。

【0010】

そこで,レギュレータの出力端に平滑用の外部容量(パスコンとも言う)を接続し,この外部容量に電荷を蓄積させる。負荷となる論理回路により消費電流が変動すると,この外部容量に蓄積された電荷が論理回路に供給され,または,電荷がこの外部容量に再度蓄積されることにより,論理回路に一定の電圧が供給される。

【0011】

半導体集積回路10においては,レギュレータA11の出力端は,レギュレータA11用の外部容量C1と外部接続端子CT1,外部端子接続配線CL1を介して接続している。以下,外部容量に接続する外部接続端子をC端子と記す。

【0012】

同じく,レギュレータB13の出力端は,レギュレータB13用の外部容量C2とC端子CT2,外部端子接続配線CL2を介して接続している。すなわち,半導体集積回路10においては,レギュレータA11,レギュレータB13がそれぞれの外部容量C1,C2と接続するために,2つの外部接続端子CT1,CT2が必要になる。なお,抵抗RTは終端抵抗である。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2001-211640号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

ところで,半導体集積回路の面積を削減するため,外部接続端子数を削減する必要がある。特に,多数の論理回路と,これら多数の論理回路に電力を供給する多数のレギュレータとを1チップ上に搭載する場合には,これら多数のレギュレータに対応してそれぞれ,多数のC端子を設けなければならない。このように,C端子を設けると,半導体集積回路の面積が大きくなってしまう。また,外部接続端子の総数に対するC端子の総数が増えてしまい,他の機能を実現するために必要な外部接続端子の数が不足する。

【0015】

したがって,本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減することにある。

【課題を解決するための手段】

【0016】

半導体集積回路の第1の側面は,動作状態または停止状態になる第1の論理回路と,常に動作状態にある第2の論理回路と,第1の出力端から第1の電源電圧を前記第1の論理回路に供給して前記第1の論理回路を動作状態にし,前記第1の電源電圧の供給を停止し前記第1の論理回路を停止状態にする第1のレギュレータと,第2の出力端から第2の電源電圧を前記第2の論理回路に常に供給する第2のレギュレータとを有する半導体集積回路において,

前記第1,第2の出力端と,外部容量に接続する外部接続端子との間に設けられたスイッチ回路を有し,

前記スイッチ回路の一端は前記第1の出力端に接続され,当該スイッチ回路の他端は前記外部接続端子および前記第2の出力端に接続され,

前記スイッチ回路は,前記第1のレギュレータが前記第1の電源電圧を第1の論理回路に対して供給する期間はオンし,前記第1のレギュレータが前記第1の論理回路に対する電源電圧供給を停止する期間はオフする。

【発明の効果】

【0017】

第1の側面によれば,複数の論理回路に電源電圧をそれぞれ供給する複数のレギュレータを有する半導体集積回路において,これら複数のレギュレータがC端子を共用するので,C端子の数を削減できる。その結果,回路面積を削減できる。

【図面の簡単な説明】

【0018】

【図1】図1は,レギュレータを有する半導体集積回路の一例ブロック図である。

【図2】図2は,C端子の数を削減した半導体集積回路を説明する図である。

【図3】図3は,本実施の形態における半導体集積回路の一例ブロック図である。

【図4】図4は,半導体集積回路の詳細ブロック図である。

【図5】図5は,半導体集積回路の動作を説明するタイミングチャートである。

【図6】図6は,スイッチ回路の一例を説明する図である。

【図7】図7は,半導体集積回路の効果を説明する図である。

【発明を実施するための形態】

【0019】

C端子の数を削減する1つの手段を図2を用いて説明する。

【0020】

図2は,C端子の数を削減した半導体集積回路を説明する図である。

【0021】

図2(A)は,C端子の数を削減した半導体集積回路の一例ブロック図であり,図2(B)は,図2(A)の一部拡大図である。

【0022】

図2において,半導体集積回路20は,1つのレギュレータC21のみを有し,電源配線PL3を介して論理回路A22,論理回路B23に電源電圧を供給する。論理回路A22は図1の論理回路A12と同機能である。また,レギュレータC21の出力端は,レギュレータC21用の外部容量C3とC端子CT3,外部端子接続配線CL3を介して接続している。また,レギュレータC21から論理回路A22に対する電源電圧の供給をスイッチングする多数のスイッチユニットSaが論理回路A22の周囲に設けられている。

【0023】

論理回路B23は,図1の論理回路B14が有する機能に加えて,論理回路A22の周囲に設けられているスイッチユニットSaをオンにして,レギュレータC21から論理回路A22に対する電源電圧の供給を行い,論理回路A22を動作状態にする機能を有する。

【0024】

また,論理回路B23は,スイッチユニットSaをオフにして,レギュレータC21から論理回路A22に対する電源電圧供給を停止し,論理回路A22を停止状態にする機能を有する。

【0025】

ここで,論理回路A22の周囲にスイッチユニットSaを設ける理由を図2(B)を用いて説明する。通常,論理回路は,格子状(メッシュ状)に設けられた電源供給線を有する。

【0026】

図2(B)において,符号PMで示す電源供給線が,この格子状に設けられた電源供給線の一部分である。この格子状に設けられた電源供給線PMの一端には,レギュレータC21からの電源配線PL3が接続される。そして,この電源配線PL3から電源供給線PMに電源電圧が供給され,この電源供給線PMから論理回路A22を構成する論理素子などに電源電圧が供給される。

【0027】

論理回路の周囲に電源配線を配置する構成は論理回路B23についても同様である。

【0028】

このような配線構造において,レギュレータC21から論理回路A22に対する電源電圧供給のスイッチングを行うスイッチユニットSaを設ける場合,図2(B)に示したように,電源配線PL3と電源供給線PMとの間にスイッチユニットSaを設ける。ここで,スイッチユニットSaは,Nチャネル型のトランジスタTr1を有し,トランジスタTr1のドレインが電源配線PL3に接続され,ソースが電源供給線PMに接続され,ゲートには,論理回路B23からスイッチユニットSaをオンオフする制御信号が入力される。

【0029】

このように,電源供給線PMと電源配線PL3との間にスイッチユニットSaを設ける,換言すれば,スイッチユニットSaを論理回路A22の周囲に設けることで,以下の効果が生じる。すなわち,スイッチユニットSaがオンすると論理回路A22に電源電圧が即時供給され,スイッチユニットSaがオフするとこの電源電圧供給が即時停止する。この即応性を確保することが,スイッチユニットSaを論理回路A22の周囲に設ける理由である。

【0030】

しかし,スイッチユニットSaを論理回路A22の周囲に設ける場合,多数のスイッチユニットSa,例えば1920個ものスイッチユニットSaを設ける必要がある。そのため,回路面積が増大する。また,多数のスイッチユニットSaからのリーク電流により無駄な消費電力が増大する。

【0031】

[本実施の形態の半導体集積回路]

そこで,以下,回路面積,消費電力を抑制できる半導体集積回路について図3〜図5に基づいて説明する。

【0032】

図3は,本実施の形態における半導体集積回路30の一例ブロック図である。

【0033】

図4は,半導体集積回路30の詳細ブロック図である。

【0034】

[論理回路]

半導体集積回路30の論理回路A32(第1の論理回路)は,必要に応じて動作状態または停止状態になる論理回路であり,例えば,記憶処理,演算処理,通信処理などの各種処理を行う回路である。

【0035】

論理回路B34(第2の論理回路)は,常に動作状態にある論理回路であり,レギュレータA31,レギュレータB33の制御処理,通信処理などの各種処理を行う回路である。

【0036】

[レギュレータ]

レギュレータA31(第1のレギュレータ)は,第1の出力端OTaから第1の電源電圧Vaを論理回路A32に供給して論理回路A32を動作状態にし,電源電圧Vaの供給を停止し論理回路A32を停止状態にする。すなわち,レギュレータA31は,電源配線PL4を介して電源電圧Va(第1の電源電圧)を論理回路A32に供給する。

【0037】

レギュレータB33(第2のレギュレータ)は,第2の出力端OTbから第2の電源電圧Vbを論理回路B34に常に供給する。すなわち,レギュレータB33は,半導体集積回路30の起動時から動作状態になり,電源配線PL5を介して電源電圧Vbを論理回路B34に供給する。

【0038】

[スイッチ回路]

スイッチ回路35は,レギュレータA31の出力端OTa(図4参照)およびレギュレータB33の出力端OTb(図4参照)と,外部容量C4に接続する外部接続端子CT4との間に設けられている。

【0039】

スイッチ回路35の一端は外部端子接続配線CL4を介してレギュレータA31の出力端OTaに接続されている。また,スイッチ回路35の他端は,外部端子接続配線CL5を介してC端子CT4に接続され,この他端は,外部端子接続配線CL6を介してレギュレータB33の出力端OTbに接続されている。

【0040】

すなわち,スイッチ回路35の一端はレギュレータA31の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4およびレギュレータB33の出力端OTbに接続されている。

【0041】

スイッチ回路35は,レギュレータA31が電源電圧Vaを論理回路A32に対して供給する期間はオンし,レギュレータA31が論理回路A32に対する電源電圧Vaの供給を停止する期間はオフする。

【0042】

このようなスイッチングを行うスイッチ回路35を設ける理由を説明する。図3,図4では,2つのレギュレータの出力端とC端子CT4とを接続,すなわち,レギュレータA31,レギュレータB33が1つのC端子CT4を共有することにより,図1に示した半導体集積回路に比べて外部容量に接続する外部接続端子の数を削減している。

【0043】

ここで,レギュレータA31,レギュレータB33が1つのC端子CT4を共有し,スイッチ回路35が無い状態を想定する。図3の例では,スイッチ回路35が無く,外部端子接続配線CL4,CL5,CL6が接続している状態である。このとき,レギュレータA31の出力端OTaとレギュレータB33の出力端OTbとがC端子CT4に共通接続される。

【0044】

この状態で,レギュレータA31,論理回路A32が停止し,レギュレータB33が動作していると,レギュレータB33の電源電圧Vbが停止中の論理回路A32に供給されてしまう。すなわち,スイッチ回路35がない場合,レギュレータB33からの電源電圧Vbが外部端子接続配線CL6,外部端子接続配線CL4を介して論理回路A32に供給されてしまい,無駄な消費電力が増大する。

【0045】

そこで,レギュレータA31が電源電圧Vaを論理回路A32に対して供給する期間はオンし,レギュレータA31が論理回路A32に対する電源電圧Vaの供給を停止する期間はオフするスイッチ回路35を設けている。

【0046】

レギュレータA31が停止状態に移行すると,スイッチ回路35がオフすることにより,レギュレータA31の出力端OTaとレギュレータB33の出力端OTbとの接続経路が遮断される。その結果,レギュレータB33からの電源電圧Vbが論理回路A32に供給されなくなり,無駄な消費電流が発生しなくなる。一方,レギュレータA31が動作状態の場合には,スイッチ回路35がオンすることにより,レギュレータAの出力端OTaと外部容量C4とが接続される。その結果,外部容量C4がレギュレータA31,レギュレータB33のパスコンとして機能する。

【0047】

[レギュレータの詳細]

レギュレータA31の詳細について図4を用いて説明する。なお,このレギュレータの構成は一例であり,様々な構成のレギュレータを採用することができる。

【0048】

レギュレータA31の増幅器OP1は,反転入力端子(−端子)に供給された基準電圧BGRVと,非反転入力端子(+端子)に供給されたフィードバック電圧FBVとの差分を増幅し,出力電圧をPチャネル型のトランジスタTr2のゲートに供給する。トランジスタTr2のソースは電源VDDに接続され,ドレインは分圧抵抗R1の一端に接続され,ゲートに供給された電圧により,この電圧に対応する電流をドレインから出力する。この出力電流の電圧が電源電圧Vaである。

【0049】

基準電圧源BGRは,基準電圧BGRVを増幅器OP1の反転入力端子に供給する。また,フィードバック電圧FBVは,直列に接続された分圧抵抗R1,R2により分圧された電源電圧Vaの分圧電圧である。

【0050】

なお,例えば,電源VDDの電圧は5V,基準電圧BGRVは1.2V,R1の抵抗値は0.6MΩ,R2の抵抗値は1.2MΩ,電源電圧Vaは1.8V,フィードバック電圧FBVは1.2Vである。

【0051】

レギュレータA31の動作を簡単に説明する。例えば,論理回路A32の負荷が増大(論理回路A32の負荷電流が増大)すると,電源電圧Vaが低下し,フィードバック電圧FBVも低下する。フィードバック電圧FBVが基準電圧BGRV以下に低下すると,増幅器OP1は,出力電圧を下げる。すると,トランジスタTr2のゲート電圧が低下し,トランジスタTr2のソース-ドレイン電流が増加する。その結果,電源電圧Vaが上昇する。この電源電圧Vaの電圧上昇は,電源電圧Vaのフィードバック電圧FBVが基準電圧BGRVと同電圧になると停止する。電源電圧Vaが上昇した場合も,前記したレギュレータA31の動作と逆の動作により,電源電圧Vaが下降する。

【0052】

制御回路311は,レギュレータA31の内部制御を行う回路であり,レギュレータA31を動作させる旨を指示する制御信号CSaが論理回路B34から入力されると,電源電圧Vaの出力を開始する。また,制御回路311は,レギュレータA31を停止させる旨を指示する制御信号CSaが論理回路B34から入力されると,電源電圧Vaの出力を停止する。

【0053】

レギュレータB33もレギュレータA31と同様の回路構成を有する。なお,制御回路331は,レギュレータB33の内部制御を行う回路である。

【0054】

[半導体集積回路の動作]

半導体集積回路30の動作を図5のタイミングチャートを用いて説明する。

【0055】

図5のタイミングチャートは,上からレギュレータA31の動作モード,スイッチ回路35のオン,オフ状態,レギュレータA31の動作,停止状態,レギュレータA31の出力電圧波形,レギュレータB33の動作,停止状態,レギュレータB33の出力電圧波形を示している。

【0056】

時刻T0〜T1:この期間では,レギュレータA32,レギュレータB33が共に動作状態になる。

【0057】

半導体集積回路30が時刻T0において起動すると,図示しない制御回路からの制御信号CtlがレギュレータB33の制御回路331(図4参照)に入力される。制御回路331は,制御信号Ctlの入力に応答して,増幅器OP1などを動作させ,電源電圧Vbを論理回路B34に供給する(レギュレータB,動作状態)。

【0058】

論理回路B34は,電源電圧Vbの供給により起動する。以後,論理回路B34は,レギュレータB33の制御を制御信号Csbにより行う。

【0059】

すると,論理回路B34は,レギュレータA31の制御回路311に対して論理回路A32に対する電源電圧Vaの供給を指示する制御信号CSaを出力する。この制御信号CSaは,例えばハイレベルである。レギュレータA31は,この制御信号CSaに応答して,電源電圧Vaを論理回路A32に供給する。

【0060】

論理回路A32は,電源電圧Vaの供給により起動する。

【0061】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オン状態になる。

【0062】

すなわち,論理回路B34は,レギュレータA31に対して論理回路A32に対する電源電圧Vaの供給を指示すると共にスイッチ回路35をオンする。

【0063】

その結果,レギュレータA31の出力端OTaおよびレギュレータB33の出力端OTbがC端子CT4を介して外部容量C4に接続する。すなわち,外部容量C4がレギュレータA31,レギュレータB33のパスコンとして機能する。

【0064】

時刻T0〜T1における半導体集積回路30の消費電流は,主にレギュレータA31,論理回路A32,レギュレータB33,論理回路B34,スイッチ回路35の消費電流である。

【0065】

時刻T1〜T2:この期間では,レギュレータA31が停止状態になる。

【0066】

論理回路B34は,レギュレータA31の制御回路311に対して論理回路A32に対する電源電圧Vaの供給停止を指示する制御信号CSaを出力する。この制御信号CSaは,例えばローレベルである。レギュレータA31は,この制御信号CSaに応答して,論理回路A32に対する電源電圧Vaの供給を停止する。

【0067】

論理回路A32は,電源電圧Vaの供給停止により停止する。

【0068】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オフ状態になる。

【0069】

すなわち,論理回路B34は,レギュレータA31に対して論理回路A32に対する電源電圧Vaの供給停止を指示すると共にスイッチ回路35をオフする。

【0070】

このように,レギュレータA31が停止状態に移行すると,スイッチ回路35がオフすることにより,レギュレータA31とレギュレータB33との接続経路が遮断される。その結果,レギュレータB33から電源電圧Vbが論理回路A32に供給されなくなり,無駄な消費電流が発生しなくなる。このとき,レギュレータB33の出力端OTbは,C端子CT4を介して外部容量C4に接続しており,外部容量C4は,レギュレータB33のパスコンとして機能している。

【0071】

時刻T1〜T2における半導体集積回路30の消費電流は,主にレギュレータB33,論理回路B34,スイッチ回路35の消費電流である。

【0072】

時刻T2〜T3: この期間では,レギュレータA31が動作状態になる。時刻T0〜T1で説明したように,論理回路B34は,論理回路A32に対する電源電圧Vaの供給再開を指示する制御信号CSaをレギュレータA31の制御回路311に出力する。レギュレータA31は,この制御信号CSaに応答して,電源電圧Vaを論理回路A32に供給する。

【0073】

論理回路A32は,電源電圧Vaの供給により起動する。

【0074】

また,論理回路B34は,この制御信号CSaをスイッチ回路35に出力する。スイッチ回路35は,この制御信号CSaに応答して,オン状態になる。

【0075】

以降,レギュレータA31の停止,動作,スイッチ回路35のオフ,オンを繰り返す。

【0076】

[スイッチ回路]

さて,スイッチ回路35として様々な構成のスイッチを利用することができる。

【0077】

図6は,スイッチ回路35の一例を説明する図である。スイッチ回路35は,例えば,Nチャネル型のトランジスタTr3を63個有する。各トランジスタTr3のゲートGには制御信号CSaが入力される。トランジスタTr3のB端子はレギュレータA31の出力端OTaに並列接続され,トランジスタTr3のC端子は,外部接続端子CT4およびレギュレータB33の出力端OTbに並列接続される。なお,トランジスタTr3のB端子はドレインまたはソースであり,C端子はソースまたはドレインである。

【0078】

このように,各トランジスタTr3を並列接続するのは,スイッチ回路35の抵抗値を外部端子接続配線CL4の配線抵抗値以下にするためである。例えば,外部端子接続配線CL4の配線抵抗値が0.5106Ω,1個のトランジスタTr3のオン抵抗が63Ωの場合,トランジスタTr3を63個並列接続すれば((32Ω/0.5106Ω)),スイッチ回路35の抵抗値を外部端子接続配線CL4の配線抵抗値以下にすることができる。

【0079】

[効果]

本実施の形態の半導体集積回路30によれば,C端子の数を削減し,回路面積を削減できる。そして,スイッチ回路35のスイッチングにより,無駄な消費電力を削減できる。また,スイッチ回路35の回路面積が小さいので,さらなる回路面積の削減が可能になる。

【0080】

図7は,本実施の形態の半導体集積回路30の効果を説明する図である。図7において,図2の半導体集積回路20のスイッチユニットSaの総面積およびリーク電流を示し,さらに,本実施の形態の半導体集積回路30のスイッチ回路35および追加したレギュレータの総面積およびリーク電流を示している。

【0081】

図7に示したように,本実施の形態の半導体集積回路30では,図2の半導体集積回路20に比べて,回路面積では23%縮小し,リーク電流では76%削減されている。

【符号の説明】

【0082】

10,20,30…半導体集積回路,11,31…レギュレータA,12,22,32…論理回路A,13…レギュレータB,14,23,34…論理回路B,C1〜C4…外部容量,CT1〜CT4…外部接続端子,PL1〜PL…電源配線,CL1〜CL6…外部端子接続配線,PM…電源供給線,R1,R2…分圧抵抗,Tr1〜Tr3…トランジスタ,21…レギュレータC,311,331…制御回路,35…スイッチ回路。

【特許請求の範囲】

【請求項1】

動作状態または停止状態になる第1の論理回路と,常に動作状態にある第2の論理回路と,第1の出力端から第1の電源電圧を前記第1の論理回路に供給して前記第1の論理回路を動作状態にし,前記第1の電源電圧の供給を停止し前記第1の論理回路を停止状態にする第1のレギュレータと,第2の出力端から第2の電源電圧を前記第2の論理回路に常に供給する第2のレギュレータとを有する半導体集積回路において,

前記第1,第2の出力端と,外部容量に接続する外部接続端子との間に設けられたスイッチ回路を有し,

前記スイッチ回路の一端は前記第1の出力端に接続され,当該スイッチ回路の他端は前記外部接続端子および前記第2の出力端に接続され,

前記スイッチ回路は,前記第1のレギュレータが前記第1の電源電圧を第1の論理回路に対して供給する期間はオンし,前記第1のレギュレータが前記第1の論理回路に対する電源電圧供給を停止する期間はオフする

ことを特徴とする半導体集積回路。

【請求項2】

請求項1において,

前記第2の論理回路は,前記第1のレギュレータに対して前記第1の論理回路に対する前記第1の電源電圧の供給を指示すると共に前記スイッチ回路をオンし,前記供給の停止を指示すると共に前記スイッチ回路をオフする

ことを特徴とする半導体集積回路。

【請求項3】

請求項2において,

前記スイッチ回路は,複数のNチャネル型のトランジスタを有し,前記複数のトランジスタのゲートには,前記第2の論理回路から入力される前記スイッチ回路をオン,オフする制御信号が入力され,ドレインまたはソースは前記第1の出力端に並列接続され,ソースまたはドレインは前記外部接続端子および前記第2の出力端に並列接続される

ことを特徴とする半導体集積回路。

【請求項1】

動作状態または停止状態になる第1の論理回路と,常に動作状態にある第2の論理回路と,第1の出力端から第1の電源電圧を前記第1の論理回路に供給して前記第1の論理回路を動作状態にし,前記第1の電源電圧の供給を停止し前記第1の論理回路を停止状態にする第1のレギュレータと,第2の出力端から第2の電源電圧を前記第2の論理回路に常に供給する第2のレギュレータとを有する半導体集積回路において,

前記第1,第2の出力端と,外部容量に接続する外部接続端子との間に設けられたスイッチ回路を有し,

前記スイッチ回路の一端は前記第1の出力端に接続され,当該スイッチ回路の他端は前記外部接続端子および前記第2の出力端に接続され,

前記スイッチ回路は,前記第1のレギュレータが前記第1の電源電圧を第1の論理回路に対して供給する期間はオンし,前記第1のレギュレータが前記第1の論理回路に対する電源電圧供給を停止する期間はオフする

ことを特徴とする半導体集積回路。

【請求項2】

請求項1において,

前記第2の論理回路は,前記第1のレギュレータに対して前記第1の論理回路に対する前記第1の電源電圧の供給を指示すると共に前記スイッチ回路をオンし,前記供給の停止を指示すると共に前記スイッチ回路をオフする

ことを特徴とする半導体集積回路。

【請求項3】

請求項2において,

前記スイッチ回路は,複数のNチャネル型のトランジスタを有し,前記複数のトランジスタのゲートには,前記第2の論理回路から入力される前記スイッチ回路をオン,オフする制御信号が入力され,ドレインまたはソースは前記第1の出力端に並列接続され,ソースまたはドレインは前記外部接続端子および前記第2の出力端に並列接続される

ことを特徴とする半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−110337(P2013−110337A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−255790(P2011−255790)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]